## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2020/0186405 A1 RAPHAELI et al.

### (43) **Pub. Date:** Jun. 11, 2020

## (54) REDUCTION OF PEAK TO AVERAGE **POWER RATIO**

(71) Applicant: Ramot at Tel-Aviv University Ltd., Tel Aviv (IL)

Inventors: DANI RAPHAELI, Kfar Saba (IL); Or Levi, Tel Aviv (IL)

(21) Appl. No.: 16/706,838

(22) Filed: Dec. 9, 2019

## Related U.S. Application Data

(60) Provisional application No. 62/777,174, filed on Dec. 9, 2018.

## **Publication Classification**

(51) Int. Cl. H04L 27/26

H04L 27/38

(2006.01)(2006.01)

H04L 27/36 (2006.01)(2006.01)H04L 27/34

U.S. Cl.

CPC ..... H04L 27/2615 (2013.01); H04L 27/3411 (2013.01); H04L 27/366 (2013.01); H04L 27/3809 (2013.01)

#### (57)ABSTRACT

A method for Peak to Average Power Ratio (PAPR) reduction at an input of analog to digital converter (ADC) of the receiver, the method includes mapping, by a mapper, an input symbol to an output symbol that maintains a peak power constraint at the input of the ADC; wherein the mapping is responsive to previously transmitted symbols; transmitting the output symbol by the transmitter; receiving, by the receiver, a received symbol that represents the output symbol; and de-mapping the received symbol, by a demapper of the receiver, to a de-mapped symbol that represents the input symbol.

FIG. 1

Mapping, by a mapper, an input symbol to an output symbol that maintains a peak power constraint at the input of the ADC of the receiver. The wherein the mapping is responsive to previously transmitted symbols. 410

FIG. A

Selecting as the output symbol a selected candidate symbol out of a set of candidates symbols that when transmitted the peak power constraint at the ADC input is satisfied, when determining whether a transmission of an output symbol that equals the input symbol will cause to a deviation from the peak power constraint at the input of the ADC, 412

400

# REDUCTION OF PEAK TO AVERAGE POWER RATIO

## CROSS-REFERENCE

[0001] This application claims priority from U.S. provisional Ser. No. 62/777,174 filing date Dec. 9, 2018, which is incorporated herein by reference.

## BACKGROUND

[0002] Wireline communication channels such as, chipto-chip SerDes communication channels, optical communication channels, and magnetic recording channels, can be modeled by additive white gaussian noise (AWGN) channels with intersymbol interference (ISI)

[0003] Recently, advanced very high speed links are starting to employ ADCs at the receiver to convert the analog signal to a digital signal. An important parameter of an ADC device is the Signal to Noise and Distortion Ratio (SNDR) or equivalently effective number of bits (ENOB).

[0004] To avoid excessive signal distortion due to clipping, the ADC is required to have a large dynamic range to achieve the desired system performance. The demand of a large dynamic range translates to higher circuit design complexity and higher power consumption.

[0005] Signals at the ADC input are therefore backed-off (BO) with respect to the ADC saturation point.

[0006] For an ADC with a given input signal range and ENOB, the input signal power BO improves the signal to clipping distortion ratio but degrades the receiver signal to quantization noise ratio (RSQNR), as well as signal to thermal noise ratio of the ADC output, as the noise power due to quantization noise and thermal noise are independent in the input signal power. Thus, decreasing the signal to clipping distortion while keeping on both signal to quantization noise and signal to thermal noise ratios is a desired approach, which can be performed by decreasing the PAPR of the signal at the ADC input.

**[0007]** The ever increasing demand for higher data rates in wireline communication channels is not going to stop in the foreseen future. Raw data rates of 100 Gbps, 200 Gbps and 400 Gbps are intended to be used in the next Ethernet generation.

[0008] However, the PAPR is increased especially as the symbol rate gets higher on the same physical channel.

**[0009]** For example, when the transmission is over a SerDes channel (typical 50 cm chip to chip trace), and the transmitted symbols are chosen uniformly from 8-PAM constellation. The PAPR in these cases, depending on the transmission rate, may reach well over 10 dB.

[0010] The mainly reason of high PAPR is due to ISI at the receiver, which causes by the channel impulse response. Thus, several approaches for eliminating the ISI can be used for PAPR reduction at the receiver. One approach is Zero-Forcing (ZF) equalizer, which is a filter with spectral response inverse of the channel response, can be used on the analog signal, prior the ADC, in order to completely remove ISI and reduce the PAPR. However, the circuit design complexity of such an analog equalizer is high. Moreover, the equalizer generates high noise enhancement in frequencies where the channel response has high attenuation.

[0011] A possible solution to overcome the noise enhancement is by using the ZF filter in the transmitter. However, in this case the PAPR at the transmitter will be high. To avoid

saturation of the transmitted signal by the power amplifier, the transmitted signal at the power amplifier input is backed-off (BO), so that instantaneous high peak values will not result in saturation. The cost of the BO is that the average power of the signal is lower, thus compromising the error performance.

[0012] Another equalizer that can be used for ISI (or PAPR) reduction at the ADC input is a continues time linear equalizer (CTLE). The CTLE is an analog high pass filter, approximating the ZF, constructed from analog components, both passive (resistors, capacitors, inductors) and active (amplifier), used prior to ADC, that boost up high-frequencies to counter the channel attenuation and distortion.

[0013] Consequently, the impulse response of the equivalent channel, resulting from concatenating the channel and the CTLE filter impulse responses, spans over much lower symbol periods compared to the channel impulse response. Hence, both ISI and PAPR are lower at the ADC input.

[0014] There are two main disadvantages with passive CTLE. First, the RC network intro-duces large impedance discontinuity at the channel and equalizer interface. Impedance matching networks, often employing inductors, can be used to prevent the discontinuity. However, the large inductors make this approach less suitable for on-chip integration. Second, this method cannot improve SNR, since equalization is performed by attenuating low-frequency signal spectrum.

[0015] It is desirable therefore to have a gain greater than one at all frequencies to maximize the benefit from receiverside equalization. Hence, CTLE using active circuit elements rather than passive components are required. However, active CTLE amplifies the high frequency noise which potentially degrading the noise margin.

[0016] There is a growing need to provide an efficient system, method and a computer readable medium for maintaining a desired PAPR constrains an input of an ADC of a receiver.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0017] The embodiments of the disclosure will be understood and appreciated more fully from the following detailed description, taken in conjunction with the drawings in which:

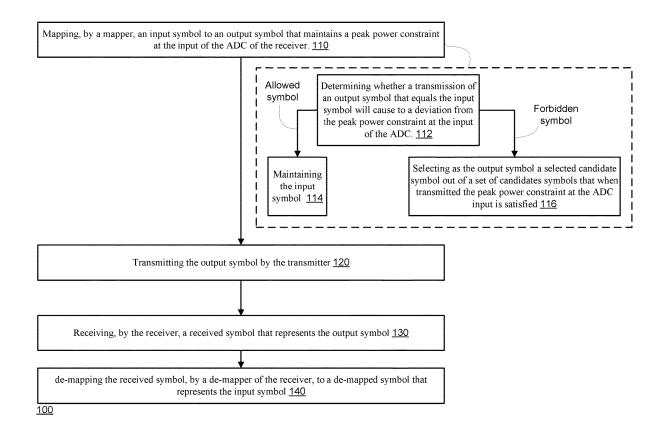

[0018] FIG. 1 is an example of a method;

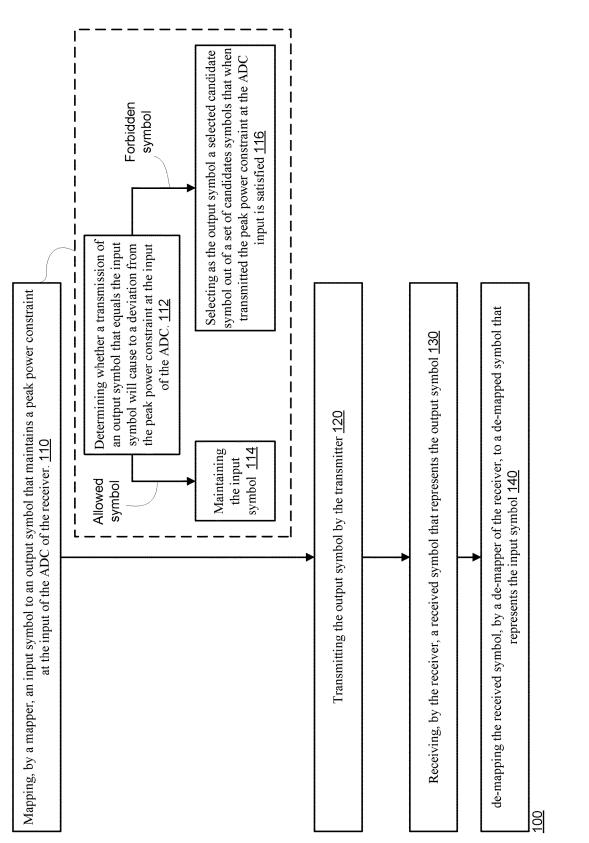

[0019] FIG. 2 is an example of a turbo encoder;

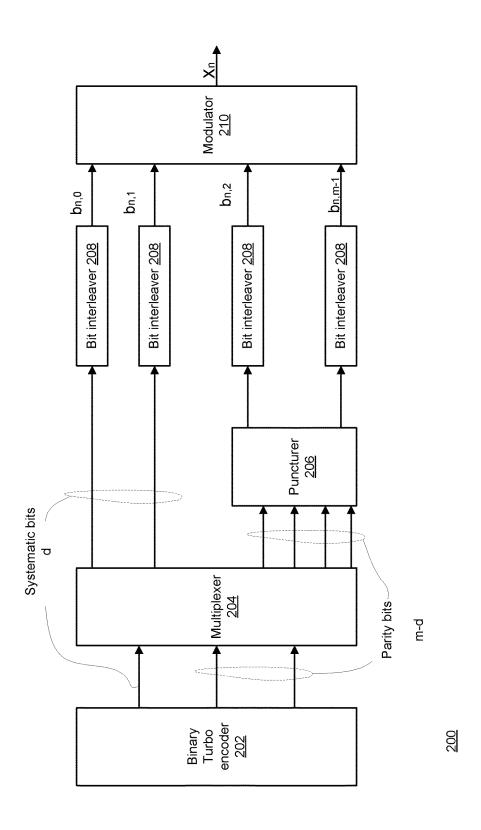

[0020] FIG. 3 is an example of a receiver;

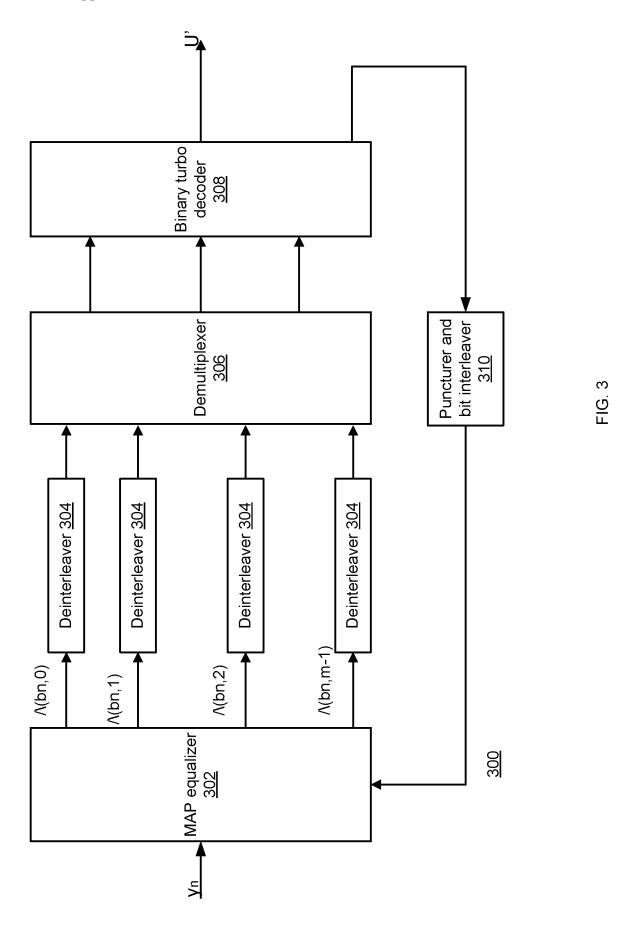

[0021] FIG. 4 is an example of a method;

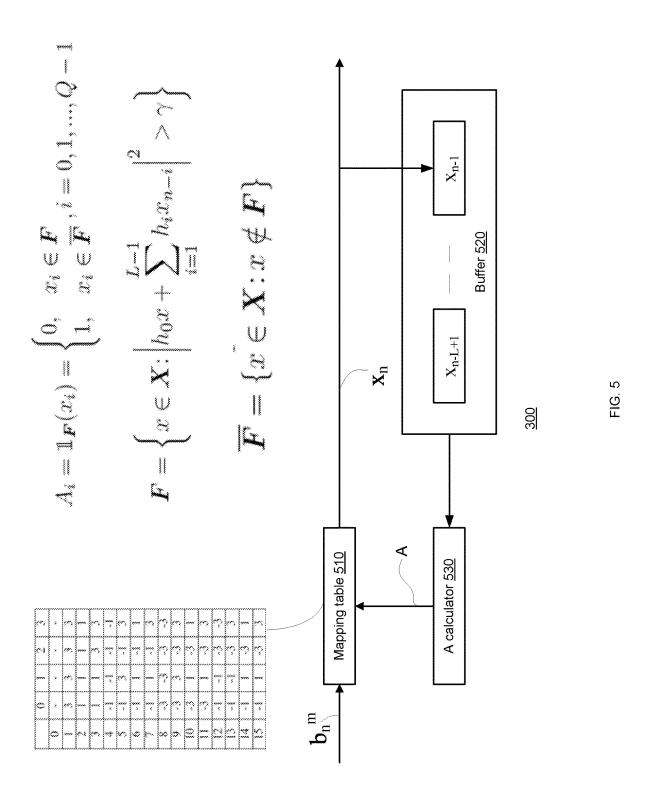

[0022] FIG. 5 is an example of a precoder;

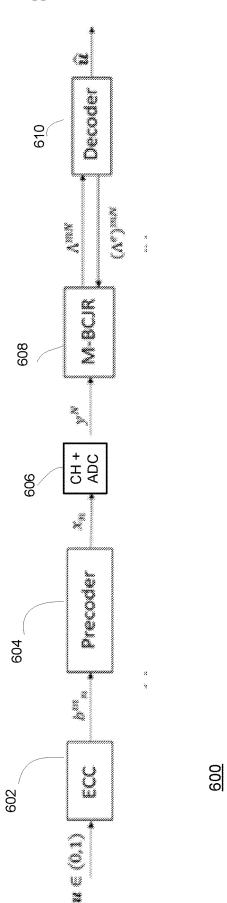

[0023] FIG. 6 is an example of a system; and

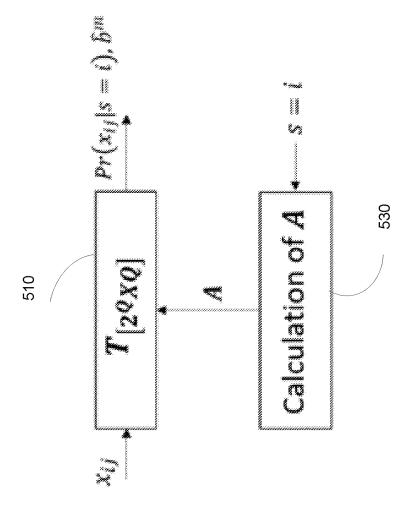

[0024] FIG. 7 is an example of a part of the precoder.

## DETAILED DESCRIPTION OF THE DRAWINGS

[0025] Any reference to a device should be applied, mutatis mutandis to a method that is executed by a device.

[0026] Any reference to method should be applied, mutatis mutandis to a device that is configured to execute the method.

[0027] The term "and/or" is additionally or alternatively. [0028] The terms "including", "comprising", "having", "consisting" and "consisting essentially of" are used in an interchangeable manner. For example—any method may

include at least the steps included in the figures and/or in the

specification, only the steps included in the figures and/or the specification. The same applies to the device.

[0029] It will be appreciated that for simplicity and clarity of illustration, elements shown in the figures have not necessarily been drawn to scale. For example, the dimensions of some of the elements may be exaggerated relative to other elements for clarity. Further, where considered appropriate, reference numerals may be repeated among the figures to indicate corresponding or analogous elements.

[0030] There may be provided a method for Peak to Average Power Ratio (PAPR) reduction at an input of analog to digital converter (ADC) of the receiver.

[0031] FIG. 1 is an example of method 100.

[0032] Method 100 may start by step 110 of mapping, by a mapper, an input symbol to an output symbol that maintains a peak power constraint at the input of the ADC of the receiver.

[0033] The mapping may be responsive to previously transmitted symbols.

[0034] The mapping may be set regardless of a maximization of entropy.

[0035] The mapping may be responsive to a channel impulse response and to a maximal power allowed by the input of the ADC. The ADC is a part of the receiver that converts analog signals from a channel to digital signals that then may digitally processed.

[0036] The mapping of an input symbol to an output symbol  $x_n$  depends on the channel impulse response and the peak power constraint according to the precoder of FIG. 5.

[0037] Step 110 may include step 112, 114 and 116.

[0038] Step 112 may include determining whether a transmission of an output symbol that equals the input symbol will cause to a deviation from the peak power constraint at the input of the ADC. In other words—step 112 may determine of a certain (for example—the n'th output signal) is forbidden or not.

[0039] The determination may be based on various parameters such as the channel state, the channel impulse response and probability  $P_{peak}$ . These parameters may be known, estimated, or evaluated over time.

**[0040]** The peak power constraint me be (or may be determined based on) probability  $P_{peak}$ . Denoting  $P_n$  as the instantaneous power of a signal at an input of an ADC then a peak Pr is defined as a value of  $P_n$  which exceeded with the probability  $P_{peak}$ .

[0041] PAPR stands for a peak to average power ratio. A PAPR gain ( $G_{PAPR}$ ) is the ratio between a PAPR of a system that implements method 100 to a PAPR of a system that does not implement method 100.

[0042] RSQNR stands for a receiver signal to quantization noise ratio. The RSQNR reflects the relationship between the average power of the received signal and the quantization noise introduced by the ADC.

[0043] A RSQNR gain ( $G_{PSQNR}$ ) is the reduction in a required power at the receiver for a given symbol rate—the reduction is measured in relation to a system that does not implement method 100.

[0044] The overall shaping gain  $G_T$  may equal the sum (when represented in dB) of  $G_{PAPR}$  and  $G_{PSQNR}$ .

[0045] The probability  $\mathbf{P}_{peak}$  may determine the overall shaping gain  $\mathbf{G}_{T}$

[0046] If the output signal is not forbidden—then step 112 may be followed by step 114 of maintaining the input symbol—determining that the output symbol may equal the input signal.

[0047] If the output signal is forbidden—then step 112 may be followed by step 116 of mapping the input symbol to an output symbol that differs from the output symbol—to an output symbol that is not forbidden.

[0048] Step 116 may include selecting as the output symbol a selected candidate symbol out of a set of candidates symbols that when transmitted the peak power constraint at the ADC input is satisfied.

**[0049]** Step 116 may perform the selecting in various manners—for example—by selecting a selected output symbol of the set that has a lowest Hamming distance from the input symbol, out of the set of candidates symbols. The output symbol should belong to set F. If set F contains many candidates then, the symbol with the lowest hamming distance is chosen.

[0050] Step 116 may include using a channel-state dependent mapping table comprising, for each current channel state, quantized values of probabilities of a next channel state to become sk, given that the current state is sk-1.

[0051] Method 100 may include calculating the set of candidate symbols.

**[0052]** Step **105** may be preceded by performing error correction coding (ECC) to provide codewords that are then undergo step **110**. The ECC may apply an iteratively decodable code that may handle erasures.(here we can explain that the operation of the precoder is similar to puncturing though a dynamic one, and each bit punctured is handled by the receiver as an erasure). An example is a turbo code. The codeword may be divided into m-tuples  $b^m$ . At time instance n the mapping may include mapping each  $b^m$ , into a symbol  $a^m$ .

[0053] LLR values computed by the BCJR may be used as a priori input to the ECC encoding.

[0054] In each iteration, the decoder produces extrinsic LLR values  $(\Lambda^e)^{mN}$  which are used as an a priory input to the BCJR module, which in turn calculates new extrinsic LLRs which are sent back to the code decoder. After a predetermined number of iterations has been reached, the bit estimations u are determined by performing hard decision on the decoder LLR values  $(\Lambda^e)^{Mn}$ . Initially, all  $(\Lambda^e)^{mN}$  may be set to zero. The decoding complexity may be reduced by saturating the BCJR extrinsic LLRs.

[0055] Step 110 may be followed by step 120 of transmitting the output symbol by the transmitter.

[0056] Steps 110 and 120 may be executed by the transmitter.

[0057] The mapping may include imposing a Markovian symbol distribution at an output of the transmitter. The Markovian symbol distribution may be optimal or non-optimal.

[0058] For example, the Markovian symbol distribution may be determined to be optimal for given values of RPQNR and Transmitter Signal to Thermal Noise Ratio (TSTNR).

[0059] This may include a first step of finding a maximal entropy Markovian distributions under peak constraints, and a second step of finding the Markovian distribution with the highest MI, among the Markovian distributions calculated in the first step.

**[0060]** The first step may include optimizing the MI with respect to probability  $P_{peak}$  while keeping TSTNR and PRQNR constant. This step may be implicit in the online precoder. The online precoder provides an approximation to the optimal distribution.

[0061] Step 120 may be followed by step 130 of receiving, by the receiver, a received symbol that represents the output symbol. The received symbol may be altered by the channel. [0062] The receiving may involve receiving the signal by an ADC of the receiver and generating digital signals.

[0063] Step 130 may be followed by step 140 of demapping the received symbol, by a de-mapper of the receiver, to a de-mapped symbol that represents the input symbol.

[0064] Step 140 may include reversing the mapping of step 110.

[0065] Step 140 may include applying a reduced complexity BJCR process on the received symbols, wherein the branches probabilities of each state in the trellis are calculated on the fly.

[0066] FIG. 2 illustrates an example of a turbo encoder 200 that is configured to implement at least a part of method 100.

[0067] The turbo encoder may include binary turbo encoder 202, multiplexer 204, puncturer 206, bit interleavers 208 and modulator 210.

[0068] A binary information stream u is firstly encoded (by binary turbo encoder 202) with a rate d/m systematic error correction code (ECC code) into a code word.

[0069] The code word is then divided into m-tuples, with  $m=\log_2(M)$ , where in each tuple the first d bits are information bits (denoted "systematic bits") and the last m-d bits are parity bits.

**[0070]** Then, at time instance n, the modulator **210** maps (step **110**) each m-tuple (of  $b_{n,0}$  till  $b_{n,m-1}$ ) into a symbol from Xn, using a mapping function.

**[0071]** According to the channel state at time n, the channel impulse response, and  $p_{peak}$ , the mapping function calculates a mapping table of size  $2^m$  by using a bit labeling algorithm. Then, the mapping table is used to map the m tuple to a symbol Xn.

[0072] Due to the astronomical number of states at high symbols rate, the maximal entropy Markovian distribution in may be hard to calculate.

[0073] Thus, in the practical scheme described above, the distribution may be actually calculated by the mapping function. The calculated distribution is designed to keep the peak constraint,  $\mathbf{p}_{peak}$ , at the ADC input, but not to maximize the entropy. Thus, the implementation may be sub-optimal and may result in an insignificant loss compared to optimal solution.

[0074] An example of the bit labeling calculation (and thus the symbol distribution), given a channel impulse response, a channel state, and  $P_{peak}$ , which performs by the mapping function, is describe in the following section. Note, the same mapping function is used in both transmitter and receiver.

[0075] The goal of the mapping function is to calculate the mapping table at step n, given channel state, channel impulse response, and  $P_{peak}$ . This calculation can be divided to two steps. Firstly, the forbidden symbols at step n (symbols that will result  $p_n > P_{peak}$ ) can easily be found since that the channel state, the channel impulse response, and  $P_{peak}$  are known.

[0076] The goal of the bit labeling process is to map all the possible 2<sup>m</sup> bit combinations at the modulator input, to a constellation symbol. If the set of non-forbidden symbols is empty then the mapping is the Gray mapping. Since that not always all the constellation symbols are allowed to be transmitted (set of non-forbidden symbols is not empty), all the Gray bit labels of the symbols in the set of non-forbidden symbols are actually free and should be assign to the symbols in the set of forbidden symbols. The assignment is according to the minimum hamming distance criterion, i.e., each free label should be assigned to a symbol in F, such that there are minimal different bits between the original Gray bit label of the symbol and the free label. The different bits among the labels are actually erased and should be decoded right by the receiver suggested in FIG. 3.

[0077] An example of a mapping table of 4-PAM constellation, is presented in table I.

**[0078]** In this example, symbol x=-1 is transmitted with probability 1/2, and symbols x=1 and x=3 are transmitted with probability 1/4 each. Note that in this case, symbol x=-3 is transmitted with zero probability and thus, 2 labels assigned to symbol x=-1. Therefore, the upper bit is actually erased (denoted by X). Note, in the case where all the constellation symbols can be transmitted, the mapping table is simply the Gray labeling of the constellation.

TABLE I

| Address | b0 | b1 | Symbol<br>Point | Pr  | Label         |

|---------|----|----|-----------------|-----|---------------|

| 0       | 0  | 0  | -1              | 1/2 | $\mathbf{X}0$ |

| 2       | 1  | 0  |                 |     |               |

| 1       | 0  | 1  | 1               | 1/4 | 01            |

| 3       | 1  | 1  | 3               | 1/4 | 11            |

[0079] The receiver 300 includes a maximum a posterior probability (MAP) equalizer 302, de-interleaver 304, demultiplexer 306, binary turbo decoder 308 and puncturer and bit interleaver 310. The MAP equalizer receives the output of the ADC.

[0080] FIG. 4 illustrates method 400 for Peak to Average Power Ratio (PAPR) reduction at an input of analog to digital converter (ADC) of the receiver.

[0081] Method 400 may start by step 410 of mapping, by a mapper, an input symbol to an output symbol that maintains a peak power constraint at the input of the ADC; wherein the mapping is responsive to previously transmitted symbols.

[0082] Step 410 may include selecting (412) as the output symbol a selected candidate symbol out of a set of candidates symbols that when transmitted the peak power constraint at the ADC input is satisfied, when determining whether a transmission of an output symbol that equals the input symbol will cause to a deviation from the peak power constraint at the input of the ADC.

[0083] Step 410 may be the same as step 110 or may differ from step 110.

[0084] FIG. 5 illustrates an example of a precoder 500. The precoder 500 include mapping table 510, buffer 520 and A calculator.

[0085] Element  $b_n^m$  is fed to mapping table 510 of size  $2^Q \times Q$  (Q is the contellation size) that outputs  $x_n$  that is an output signal of the precoder 500. In addition,  $x_n$  is fed to a

buffer **520** that stores L previous values  $x_{n-1}$  till  $x_{n-L+1}$  that are fed to calculator **530** that calculates A.

[0086] FIG. 5 also illustrates an example of a mapping table for a 4-PAM constellations. Other tables may be used for other constellations and even for the 4-PAM constellation. At the table -col index -index of an input symbol, row index-decimal representation of A and value-output symbol

[0087] FIG. 5 also illustrates an example of a calculation of A. Ai has zero of one value based on whether xi belongs to F or not.

**[0088]** F is calculated by an equation also illustrate din FIG. 5. In this equation X is a set of all constellation symbols,  $\gamma$  is a peak power constraint, and  $h0 \dots hL-1$  are -channel impulse responses.

[0089] FIG. 6 illustrates a system 600 that includes a receiver and a transmitter. The transmitter includes error correction encoder (ECC) 602 followed by a precoder 604.

[0090] The precoder 604 is followed by a channel (wired or wireless) that is followed by an ADC (or an analog front end of the receiver followed by the ADC)—in FIG. 600 the channel and ADC are collectively denoted CH+ADC 606.

[0091] The ADC is followed by M-BCJR module 608 and a decoder 610. The decoder outputs a reconstruction of input signals.

[0092] The precoder 604 of FIG. 5 is configured to recover erased bits during the BCJR and decoder operation.

[0093] FIG. 7 is an example of a process of calculating online the branch probability in the BCJR Trellis. The calculation involves mapping table and A calculator.

[0094] At the receiver side, shown in FIG. 3, the noisy symbol  $y_n$  is received by MAP equalizer 302. The MAP equalizer may be based on a M-BCJR algorithm, which keeps, at every step, T states with highest metric. The LLR values  $\Lambda^I(b_I)$ , where  $0 \le l \le m-1$ , are produced for each encoded bit. The LLR values are used, after appropriate bit de-interleaving (by de-interleaver 304), as an a priory input to a binary turbo decoder 308. In each iteration, the binary turbo decoder 308 produces extrinsic LLRs which fed via puncturer and bit interleaver 310 to MAP equalizer and are used as an a priory input of the calculation of new extrinsic LLRs which are sent back to the binary turbo decoder. After a pre-determined number of iterations has been reached, the bit estimations are determined by performing hard decision on the turbo decoder's a posterior LLRs.

[0095] The extrinsic LLRs  $\Lambda^1(b_i)$ , for each  $y_n$ , may be calculated using M-BCJR algorithm applied on the channel states Trellis diagram. For each  $y_n$ , the BCJR is producing m LLR values. Since the bit labeling of  $y_n$  depends on the channel state (i.e., the bit labeling of  $y_n$  can be different for each channel state) then, to produce LLR values, the bit label of each survivor state is calculated by using the same mapping function used at the transmitter.(see—FIG. 3)

**[0096]** Once the block of noisy symbols  $y=(y_0, \ldots, y_{N-1})$  has been received, the M-BCJR algorithm is running, and computes  $\sigma_{ijn}=\Pr(s_{n-1}=i;\ s_n=j;\ y)=\Pr(s_{n-1}=i;\ c_{ij};\ y)$  for all  $0\le n\le N-1$ , and for T states with the highest metrics at step n-1. The symbol that results to a transition from state i to state j, denoted by  $c_{ij}$ .

[0097] Next, the BCJR extrinsic LLRs, for each  $y_n$ , can be calculated by

$$\Lambda_n'(b_l) = \log \left( \sum_{(i,j) \in E_0} \frac{\sum\limits_{c_{ij}: b_l = 1} \sigma_{ij_n} + \sum\limits_{c_{ij}: b_l = 1} \sigma_{ij_n} \cdot P_0}{\sum\limits_{c_{ij}: b_l = 1} \sigma_{ij_n} + \sum\limits_{c_{ij}: b_l = 1} \sigma_{ij_n} \cdot P_1} \right) - \Lambda_n^{\epsilon}(b_l)$$

**[0098]** Where  $\Lambda^e(b_l)$  is the extrinsic LLR from the Turbo decoder,  $P_0$ =Pr( $b_l$ =0), and  $P_1$ =Pr( $b_l$ =1). Initially, all  $\Lambda^e(b_l)$  are set to 0. The bit probabilities, Pr( $b_l$ =0) and Pr( $b_l$ =1), are calculated from  $\Lambda^e(b_l)$ . Note, the BCJR module calculates the bit labeling of each  $c_{ij}$  by the mapping function used at transmitter(FIG. 3)

[0099] The decoding complexity can be reduced by manipulating the BCJR extrinsic LLRs, calculated above, according to

$$\Lambda_n(b_l) = \log \left( \frac{\max(P_n(b_l = 0), K_n(b_l))}{\max(P_n(b_l = 1), K_n(b_l))} \right)$$

**[0100]** For each bit the threshold value  $Kn(b_1)$  is computer as:

$$K_n(b_l) = \gamma \max_{b_l \in [0,1]} (P_n(b_l))$$

**[0101]** The bit probabilities  $P_n(b_i=0)$  and  $P_n(b_i=1)$  are calculated using the first equation for BCJR extrinsic LLRs, for each  $y_n$ , and the value of  $\gamma$  is optimized to yield the best BER performance.

**[0102]** In the foregoing specification, the invention has been described with reference to specific examples of embodiments of the invention. It will, however, be evident that various modifications and changes may be made therein without departing from the broader spirit and scope of the invention as set forth in the appended claims.

[0103] Moreover, the terms "front," "back," "top," "bottom," "over," "under" and the like in the description and in the claims, if any, are used for descriptive purposes and not necessarily for describing permanent relative positions. It is understood that the terms so used are interchangeable under appropriate circumstances such that the embodiments of the invention described herein are, for example, capable of operation in other orientations than those illustrated or otherwise described herein.

[0104] Those skilled in the art will recognize that the boundaries between logic blocks are merely illustrative and that alternative embodiments may merge logic blocks or circuit elements or impose an alternate decomposition of functionality upon various logic blocks or circuit elements. Thus, it is to be understood that the architectures depicted herein are merely exemplary, and that in fact many other architectures can be implemented which achieve the same functionality.

[0105] Any arrangement of components to achieve the same functionality is effectively "associated" such that the desired functionality is achieved. Hence, any two components herein combined to achieve a particular functionality can be seen as "associated with" each other such that the desired functionality is achieved, irrespective of architectures or intermedial components. Likewise, any two com-

ponents so associated can also be viewed as being "operably connected," or "operably coupled," to each other to achieve the desired functionality.

[0106] Furthermore, those skilled in the art will recognize that boundaries between the above described operations merely illustrative. The multiple operations may be combined into a single operation, a single operation may be distributed in additional operations and operations may be executed at least partially overlapping in time. Moreover, alternative embodiments may include multiple instances of a particular operation, and the order of operations may be altered in various other embodiments.

[0107] However, other modifications, variations and alternatives are also possible. The specifications and drawings are, accordingly, to be regarded in an illustrative rather than in a restrictive sense.

[0108] In the claims, any reference signs placed between parentheses shall not be construed as limiting the claim. The word 'comprising' does not exclude the presence of other elements or steps then those listed in a claim. Furthermore, the terms "a" or "an," as used herein, are defined as one as or more than one. Also, the use of introductory phrases such as "at least one" and "one or more" in the claims should not be construed to imply that the introduction of another claim element by the indefinite articles "a" or "an" limits any particular claim containing such introduced claim element to inventions containing only one such element, even when the same claim includes the introductory phrases "one or more" or "at least one" and indefinite articles such as "a" or "an." The same holds true for the use of definite articles. Unless stated otherwise, terms such as "first" and "second" are used to arbitrarily distinguish between the elements such terms describe. Thus, these terms are not necessarily intended to indicate temporal or other prioritization of such elements the mere fact that certain measures are recited in mutually different claims does not indicate that a combination of these measures cannot be used to advantage.

[0109] While certain features of the invention have been illustrated and described herein, many modifications, substitutions, changes, and equivalents will now occur to those of ordinary skill in the art. It is, therefore, to be understood that the appended claims are intended to cover all such modifications and changes as fall within the true spirit of the invention.

[0110] Any combination of any component of any device that is illustrated in any of the figures and/or specification and/or the claims may be provided.

[0111] Any combination of steps, operations and/or methods illustrated in any of the figures and/or specification and/or the claims may be provided.

[0112] Any combination of operations illustrated in any of the figures and/or specification and/or the claims may be provided.

[0113] Any combination of methods illustrated in any of the figures and/or specification and/or the claims may be provided.

1. A method for Peak to Average Power Ratio (PAPR) reduction at an input of analog to digital converter (ADC) of a receiver, the method comprising:

mapping, by a mapper, an input symbol to an output symbol that maintains a peak power constraint at the input of the ADC; wherein the mapping is responsive to previously transmitted symbols;

transmitting the output symbol by the transmitter;

- receiving, by the receiver, a received symbol that represents the output symbol; wherein the receiving may include analog to digital conversion by the ADC; and

- de-mapping the received symbol, by a de-mapper of the receiver, to a de-mapped symbol that represents the input symbol.

- 2. The method according to claim 1 wherein the mapping comprises imposing a Markovian symbol distribution at an output of the transmitter.

- 3. The method according to claim 1 wherein the mapping comprises:

- determining whether a transmission of an output symbol that equals the input symbol will cause to a deviation from the peak power constraint at the input of the ADC; and

- when determining that a deviation from the peak constraint then selecting as the output symbol a selected candidate symbol out of a set of candidates symbols that when transmitted the peak power constraint at the ADC input is satisfied.

- **4**. The method according to claim **3** comprising selecting the selected output symbol of the set, the selected output symbol of the set has a lowest Hamming distance from the input symbol, out of the set of candidates symbols.

- 5. The method according to claim 3 comprising calculating the set of candidates symbols.

- **6**. The method according to claim **1** wherein the mapping is set regardless of a maximization of entropy.

- 7. The method according to claim 1 wherein the mapping is responsive to a channel impulse response and to a maximal power allowed by the input of the ADC.

- 8. The method according to claim 1 wherein the demapping comprises applying a reduced complexity BJCR process on the received symbols, wherein the branches probabilities of each state in the trellis are calculated on the fly.

- 9. The method according to claim 1, wherein the selecting comprises using a channel-state dependent mapping table comprising, for each current channel state, quantized values of probabilities of a next channel state to become sk, given that the current state is sk-1.

- **10.** A method for Peak to Average Power Ratio (PAPR) reduction at an input of analog to digital converter (ADC) of the receiver, the method comprising:

- mapping, by a mapper, an input symbol to an output symbol that maintains a peak power constraint at the input of the ADC; wherein the mapping is responsive to previously transmitted symbols;

- wherein the mapping comprises selecting as the output symbol a selected candidate symbol out of a set of candidates symbols that when transmitted the peak power constraint at the ADC input is satisfied, when determining whether a transmission of an output symbol that equals the input symbol will cause to a deviation from the peak power constraint at the input of the ADC.

## 11. A system, comprising:

a transmitter that comprises (a) a mapper that is configured to map an input symbol to an output symbol that maintains a peak power constraint at an input of an analog to digital converter (ADC) of a receiver; wherein the mapping is responsive to previously transmitted symbols; and (b) a transmission circuit that is configured to transmit the output symbol; and

- a receiver that comprises (a) an interface that is configured to receive a received symbol that represents the output symbol; and (b) a de-mapper that is configured to de-map the received symbol, to a de-mapped symbol that represents the input symbol.

- 12. At least one non-transitory computer readable medium that stores instructions for Peak to Average Power Ratio (PAPR) reduction at an input of an analog to digital converter (ADC) of a receiver of a system, wherein the instructions, once executed by the system, cause the system to:

- map, by a mapper of a transmitter of the system, an input symbol to an output symbol that maintains a peak power constraint at the input of the ADC; wherein the mapping is responsive to previously transmitted symbols:

transmit the output symbol by the transmitter;

- receive, by the receiver, a received symbol that represents the output symbol; and

- de-map the received symbol, by a de-mapper of the receiver, to a de-mapped symbol that represents the input symbol.

- 13. The at least one non-transitory computer readable medium according to claim 12 wherein the mapping comprises imposing a Markovian symbol distribution at an output of the transmitter.

- 14. The at least one non-transitory computer readable medium according to claim 12 wherein the mapping comprises:

- determining whether a transmission of an output symbol that equals the input symbol will cause to a deviation from the peak power constraint at the input of the ADC; and

- when determining that a deviation from the peak constraint then selecting as the output symbol a selected candidate symbol out of a set of candidates symbols that when transmitted the peak power constraint at the ADC input is satisfied.

- 15. The at least one non-transitory computer readable medium according to claim 14 that stores instructions for selecting the selected output symbol of the set, the selected output symbol of the set has a lowest Hamming distance from the input symbol, out of the set of candidates symbols.

- **16**. The at least one non-transitory computer readable medium according to claim **14** that stores instructions for calculating the set of candidates symbols.

- 17. The at least one non-transitory computer readable medium according to claim 12 wherein the mapping is set regardless of a maximization of entropy.

- 18. The at least one non-transitory computer readable medium according to claim 12 wherein the mapping is responsive to a channel impulse response and to a maximal power allowed by the input of the ADC.

- 19. The at least one non-transitory computer readable medium according to claim 12 wherein the de-mapping comprises applying a reduced complexity BJCR process on the received symbols, wherein the branches probabilities of each state in the trellis are calculated on the fly.

- 20. The at least one non-transitory computer readable medium according to claim 12 wherein the selecting comprises using a channel-state dependent mapping table comprising, for each current channel state, quantized values of probabilities of a next channel state to become sk, given that a current state is sk-1.

\* \* \* \* \*