US 20190171246A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2019/0171246 A1

## Chu

#### (54) METHODS AND APPARATUSES INCLUDING A PROCESS, VOLTAGE, AND **TEMPERATURE INDEPENDENT CURRENT GENERATOR CIRCUIT**

- (71) Applicant: MICRON TECHNOLOGY, INC., Boise, ID (US)

- (72)Inventor: Wei Lu Chu, Shanghai (CN)

- (73) Assignee: MICRON TECHNOLOGY, INC.

- Appl. No.: 16/273,528 (21)

- (22) Filed: Feb. 12, 2019

#### **Related U.S. Application Data**

(63) Continuation of application No. 14/762,162, filed on Jul. 20, 2015, now Pat. No. 10,216,213, filed as application No. PCT/CN2015/078013 on Apr. 30, 2015.

# Jun. 6, 2019 (43) **Pub. Date:**

**Publication Classification**

| (51) | Int. Cl.  |           |

|------|-----------|-----------|

|      | G05F 3/30 | (2006.01) |

|      | G11C 5/14 | (2006.01) |

(52)U.S. Cl. CPC . G05F 3/30 (2013.01); G11C 5/14 (2013.01)

#### (57)ABSTRACT

Apparatuses, methods, and current generators that generate current are described. An example apparatus includes a current source configured to provide a current. The current source may be coupled to a voltage source via a transistor. The transistor may be configured to provide the voltage source to the current source based on a voltage of a gate of the transistor. The example apparatus may further include an amplifier configured to provide a voltage to the gate of the transistor based on a voltage differential between two inputs. The voltage differential between the two inputs may adjust due to process, voltage or temperature changes such that the current provided by the current source remains constant.

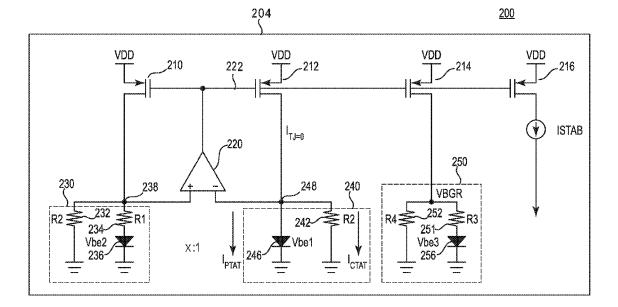

Fig. 2

### METHODS AND APPARATUSES INCLUDING A PROCESS, VOLTAGE, AND TEMPERATURE INDEPENDENT CURRENT GENERATOR CIRCUIT

#### CROSS REFERENCE TO RELATED APPLICATIONS

**[0001]** This application is a continuation of pending U.S. patent application Ser. No. 14/762,162 on Jul. 20, 2015, which application is a 371 National Stage Entry of International Application No. PCT/CN2015/078013 filed Apr. 30, 2015. The aforementioned applications are incorporated herein by reference, in their entirety, for any purpose.

#### DESCRIPTION OF RELATED ART

**[0002]** In many devices that incorporate analog, digital, and/or mixed-signal integrated circuits, current generators and voltage reference circuits are of critical importance to the proper functioning of the device. To that end, most conventional computing devices depend on stable, temperature-independent current and voltage references. As the critical dimensions of integrated circuits have decreased over time, the operating voltages of these integrated circuits have also decreased. With the decrease in operating voltages of integrated circuits has increased. Many of these voltage reference circuits provide a stable reference voltage output while operating at voltages at or below 1.3V.

**[0003]** One of the ways to reduce the costs associated with the manufacture of integrated circuits involves limiting the area used to implement circuits within the integrated circuit. In general, circuits that are less complex and require less area to implement are less expensive to manufacture. Further, by reducing the area required to implement some of the circuits within an integrated circuit, it may be possible to reduce the overall size of the integrated circuit, permitting the integrated circuit to be incorporated into smaller devices.

#### SUMMARY

[0004] Example apparatuses are disclosed herein. An example apparatus may include a plurality of transistors coupled to a voltage source. A gate of each of the plurality of transistors may be coupled to a bias line. The example apparatus may further include a first circuit coupled to a first transistor of the plurality of transistors, and a second circuit coupled to a second transistor of the plurality of transistors. The example apparatus may further include an output node coupled to a third transistor of the plurality of transistors, and an amplifier comprising a first input coupled to a node between the first transistor and the first circuit and a second input coupled to a node between the second transistor and the second circuit. The amplifier may be configured to provide an output voltage to the bias line responsive to a voltage differential between the first input and the second input. The output voltage may be applied to the bias line provides a current through the third transistor that remains substantially constant in temperature coefficient.

**[0005]** Example current generators are disclosed herein. An example current generator may include a first transistor configured to provide a current. The first transistor may be coupled to a voltage source, and may be configured to provide the voltage source to an output node based on a voltage of a gate of the first transistor. The example current generator may further include an amplifier configured to provide an output voltage to the gate of the first transistor based on a voltage differential between two inputs. The voltage differential between the two inputs may adjust due to process, voltage or temperature changes such that the current provided by the first transistor remains substantially constant in temperature coefficient.

**[0006]** Examples of methods are described herein. An example method may include providing an output voltage from an amplifier responsive to a voltage differential at inputs of the amplifier, and responsive to the output voltage, coupling a voltage source to an output node via a first transistor. The example method may further include providing a current through the first transistor based on the output voltage, and adjusting the output voltage based on a change in the voltage differential caused by a process, voltage, or temperature change such that the current provided by the first transistor remains substantially constant in temperature coefficient.

#### BRIEF DESCRIPTION OF THE DRAWINGS

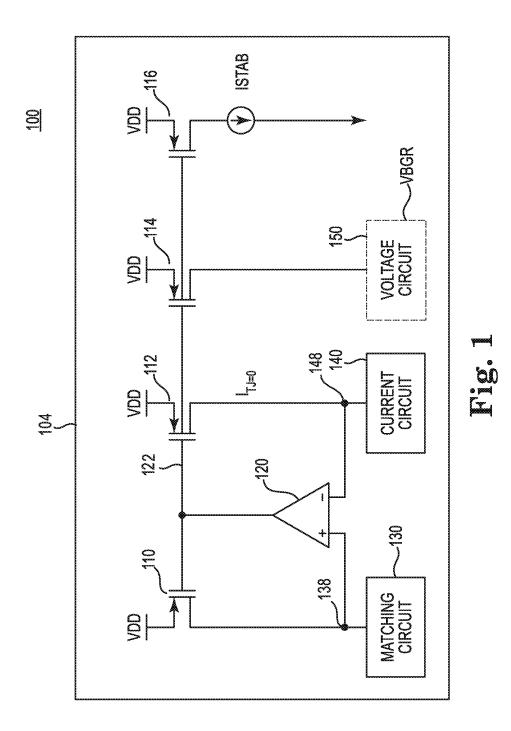

**[0007]** FIG. **1** is a block diagram of a particular illustrative embodiment of an apparatus including current generator according to an embodiment of the disclosure;

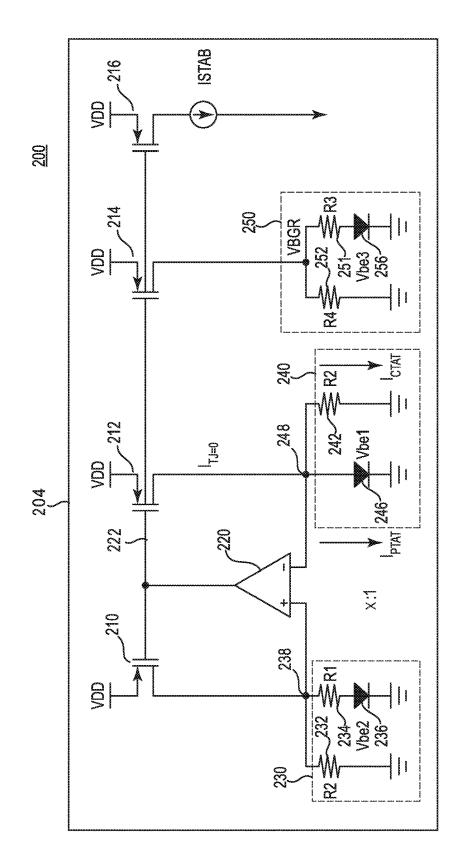

**[0008]** FIG. **2** is a block diagram of a particular illustrative embodiment of an apparatus including a current generator according to an embodiment of the disclosure; and

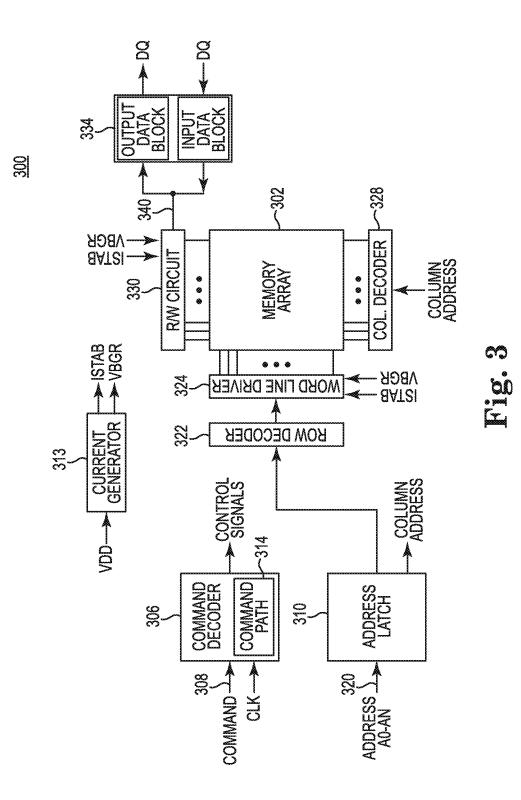

**[0009]** FIG. **3** is a block diagram of a memory including a current generator according to an embodiment of the disclosure.

#### DETAILED DESCRIPTION

**[0010]** Certain details are set forth below to provide a sufficient understanding of embodiments of the disclosure. However, it will be clear to one having skill in the art that embodiments of the disclosure may be practiced without these particular details. Moreover, the particular embodiments of the present disclosure described herein are provided by way of example and should not be used to limit the scope of the disclosure to these particular embodiments.

[0011] Referring to FIG. 1, a particular illustrative embodiment of an apparatus including a current generator 104 is disclosed and generally designated 100. As used herein, examples of apparatuses may include an integrated circuit, a memory device, a memory system, an electronic device or system, a smart phone, a tablet, a computer, a server, etc. The current generator 104 may include transistors 110, 112, 114, and 116 each having a gate coupled to a bias line 122. The transistors 110, 112, 114, and 116 may each couple a power supply VDD to a matching circuit 130, a current circuit 140, a voltage circuit 150, and an output node of the current generator 104, respectively. The voltage on the bias line 122 may be controlled by an output of an amplifier 120.

[0012] The amplifier 120 may include a first input coupled to a first node 138 between the transistor 110 and the matching circuit 130. The amplifier 120 may include a second input coupled to a second node 148 between the transistor 112 and the current circuit 140. The output of the amplifier 120 may be based on a voltage differential between the first input and the second input.

**[0013]** The matching circuit **130** and the current circuit **140** may include circuitry is configured to adjust to changes in process, voltage and/or temperature (PVT). The voltages at the first node **138** and the second node **148** may adjust based on the changes in the matching circuit **130** and the current circuit **140**, respectively, due to the PVT changes. Responsive to the adjusted voltages at the first node **130** and the second node **148**, the amplifier **120** may adjust an output voltage provided to the bias line **122**. Based on the relationship between circuitry of the matching circuit **130** and circuitry of the current circuit **140**, the output voltage driven by the amplifier **120** to the bias line **122** may result in the temperature slope of  $I_{T_{T=0}}$  current through the transistor **112** being equal to zero (e.g., or approximately zero).

[0014] In some embodiments, the current generator 104 may further include the voltage circuit 150. The voltage circuit 150 may be coupled the transistor 114 and a reference source. The voltage circuit 150 may be configured to provide a constant band-gap voltage VBGR responsive to a voltage received via the 114, which may be based on the bias line 122 voltage driven by the amplifier 120.

[0015] In operation, the amplifier 120 may receive voltages from the first node 138 and the second node 148 at respective inputs. Based on the received inputs, the amplifier 120 may provide the output voltage to the bias line 122. The voltage of the bias line 122 may control the gates of the transistors 110, 112, 114, and 116 to couple the VDD voltage to the matching circuit 130, the current circuit 140, the voltage circuit 150, and the output node of the current generator 104, respectively. In some embodiments, the VDD voltage may be equal to or greater than 0.9 V. For example, the VDD voltage may be between 1.0 and 1.35 volts. In some embodiments, voltages at the first node 138 and the second node 148 may adjust based on properties of the matching circuit 130 and the current circuit 140 caused by variation in PVT. Responsive to the changes in the voltages at the first node 138 and the second node 148, the amplifier 120 may adjust a voltage provided to the bias line 122. The coordinated adjustments of the voltage of the first node 138, the voltage of the second node 148, and the output voltage of the 120 may maintain a stable (e.g., substantially constant in temperature coefficient) current via the transistor 116. In some embodiments, the current generator 104 may also provide voltage circuit 150 that provides a constant VBGR voltage based on the output voltage provided by the amplifier 120 to the bias line 122.

[0016] The voltage of the first node 138 may be based on properties of the matching circuit 130 and the VDD voltage. The voltage of the second node 148 may be based on properties of the current circuit 140 and the VDD voltage. Operationally, changes in the voltage provided by the amplifier 120 may result in changes in voltages at the first node first node 238 and second node 148. The matching circuit 130 and the current circuit 140 may include circuitry that adjusts to variance in PVT in a predictable manner such that the voltage driven by the amplifier 120 on the bias line 122 results in the current through the transistor 116 remaining stable despite the variance in PVT. Thus, the inputs of the amplifier 120 (e.g., via the first node first node 138 and the second node 148, respectively) may be based on properties of the matching circuit 130 and current circuit 140. The matching circuit 130 and the current circuit 140 may be designed such that changes in respective properties due to variance in PVT may adjust in the inputs to the amplifier **120**. Responsive to the adjusted inputs to the amplifier **120**, the amplifier **120** may drive the output voltage to the **122** such that the temperature slope of  $I_{TJ=0}$  current between the transistor **112** and the current circuit **140** substantially remains equal to zero despite the PVT variance. By maintaining the temperature slope of  $I_{TJ=0}$  current at zero, the current through the transistor **116** and the VBGR voltage may remain substantially constant despite variance in PVT. [**0017**] A current generator **104** including only a single amplifier **120** may reduce power consumption and a footprint as compared with conventional current generators that include two or more amplifiers.

[0018] Referring to FIG. 2, a particular illustrative embodiment of an apparatus including a current generator 204 is disclosed and generally designated 200. The current generator 204 may include transistors 210, 212, 214, and 216 each having a gate coupled to a bias line 222. The transistors 210, 212, 214, and 216 may each couple a power supply VDD to a matching circuit 230, current circuit 240, voltage circuit 250, and an output node of the current generator 204, respectively. The output of the amplifier 220 may drive the voltage of the bias line 222. The current generator 204 may be implemented in the current generator 104 of FIG. 1.

[0019] The amplifier 220 may include a first input coupled to a first node 238 between the transistor 210 and the matching circuit 230. The amplifier 220 may include a second input coupled to a node second node 248 between the transistor 212 and the current circuit 240. The output of the amplifier 220 may be based on a voltage differential between the first input 238 and the second input 248.

[0020] The matching circuit 230 and the current circuit 240 may include circuitry that is configured to adjust to changes in PVT. Coupled between the first node 238 and a reference source, the matching circuit 230 may include a resistor 232 coupled in parallel with a serially coupled resistor 234 and diode 236. Coupled between the second node 248 and the reference source, the current circuit 240 may include a resistor 242 coupled in parallel with diode 246. In some embodiments, the size of the diode 236 may be greater than the size of the diode 246. For example, the diode 236 may be eight times larger than the diode 246. In some embodiments, the resistor 232 may has the same impedance as the resistor 242. The voltages at the nodes 238 and second node 248 may change responsive to changes in properties of the matching circuit 230 and the current circuit 240 due to the PVT variance. The amplifier **220** may adjust the output voltage responsive to the changes in the input voltages from the 238 and second node 248.

**[0021]** In some embodiments, the current generator **204** may include the voltage circuit **250** configured to provide a constant bandgap voltage VBGR at an output. The voltage circuit **250** may include a resistor **252** coupled in parallel with a serially coupled resistor **251** and diode **256**. The voltage circuit **250** may be coupled to the VDD via the transistor **214**.

[0022] In operation, the amplifier 220 may receive voltages from the first node 238 and the second node 248 at respective inputs. Based on the received inputs, the amplifier 220 may provide the output voltage to the bias line 222. The voltage of the bias line 222 may control the gates of the transistors 210, 212, 214, and 216 to couple the VDD voltage to the matching circuit 230, the current circuit 240, the voltage circuit 250, and the output node of the current

generator 204, respectively. In some embodiments, the VDD voltage may be equal to or greater than 0.9 V. For example, the VDD voltage may be between 1.0 and 1.35 volts. In some embodiments, voltages at the first node 238 and the second node 248 may adjust based on properties of the matching circuit 230 and the current circuit 240 caused by variation in PVT. Responsive to the changes in the voltages at the first node 238 and the second node 248, the amplifier 220 may adjust a voltage provided to the bias line 222. The coordinated adjustments of the voltage of the first node 238, the voltage of the second node 248, and the output voltage of the 220 may maintain a stable (e.g., substantially constant in temperature coefficient) current via the transistor 216. In some embodiments, the current generator 204 may also provide voltage circuit 250 that provides a constant VBGR voltage based on the output voltage provided by the amplifier 220 to the bias line 222.

[0023] The voltage of the first node 238 may be based on properties of the matching circuit 230 and the VDD voltage. The voltage of the second node 248 may be based on properties of the current circuit 240 and the VDD voltage. Operationally, changes in the voltage provided by the amplifier 220 may result in changes in voltages at the first node first node 238 and second node 248. The matching circuit 230 and the current circuit 240 may include circuitry that adjusts to variance in PVT in a predictable manner such that the voltage driven by the amplifier **220** on the bias line **222** results in the current through the transistor 216 remaining stable despite the variance in PVT. Thus, the inputs of the amplifier 220 (e.g., via the first node first node 238 and the second node 248, respectively) may be based on properties of the matching circuit 230 and current circuit 240. The matching circuit 230 and the current circuit 240 may be designed such that changes in respective properties due to variance in PVT may adjust in the inputs to the amplifier 220. Responsive to the adjusted inputs to the amplifier 220, the amplifier 220 may drive the output voltage to the 222 such that the temperature slope of  $I_{TJ=0}$  current between the transistor 212 and the current circuit 240 substantially remains equal to zero despite the PVT variance. By maintaining the temperature slope of  $I_{TJ=0}$  current at zero, the current through the transistor 216 and the VBGR voltage may remain substantially constant despite variance in PVT.

**[0024]** For example, a current proportional to absolute temperature IPTAT may flow through the diode **246**. The IPTAT current may change proportionately with temperature changes (e.g., an increase in temperature may result in an increase in IPTAT current, and vice versa). Further, a current complementary to absolute temperature ICTAT may flow through the resistor **242**. The ICTAT current may change proportionately inverse to temperature changes (e.g., an increase in temperature may result in a decrease in the ICTAT current, and vice versa). The I<sub>TJ=0</sub> current may be a sum of the IPTAT and the ICTAT currents. The relationship between the circuits of the matching circuit **230** and current circuit **240** may result in the temperature slope of sum of the IPTAT and ICTAT currents substantially being equal to zero.

**[0025]** Assuming a ratio of X to one in terms of size of the diode **236** relative to the size of the diode **246**, the impedance values for the resistor **232** (e.g., R2), resistor **234** (e.g., R1), resistor **242** (e.g., R2), resistor **251** (e.g., R3), and resistor **252** (e.g., R4) may be computed as follows:

$$I_{TJ=0} = \frac{Vbe1}{R2} + \frac{Vbe1 - Vbe2}{R1}$$

$$Vbe1 - Vbe2 = \Delta Vbe = Vt * \ln \frac{Id1}{Is1} - Vt * \ln \frac{Id2}{Is2} = Vt * \ln \frac{Id1}{Is1} * \frac{Is2}{Id2}$$

$$Id2 = Id1$$

$$Is2 = X * Is1$$

$$Vbe1 - Vbe2 = \Delta Vbe = Vt * \ln X = \frac{kT}{q} * \ln X$$

$$\therefore I_{TJ=0} = \frac{Vbe1}{R2} + \frac{kT}{q} * \frac{\ln X}{R1};$$

and

$$I_{TJ=0} = \frac{VBGR}{R4} + \frac{VBGR - Vbe3}{R3}$$

$$I_{TJ=0} = \frac{Vbe1 - Vbe2}{R1} = \frac{VBGR}{R4} + \frac{VBGR - Vbe3}{R3}$$

$$VBGR = \left(\frac{R3}{R2} * Vbe1 + Vbe3 + \frac{kT}{q} * \frac{R3}{R1} * \ln X\right) * \frac{R4}{R3 + R4}$$

[0026] where T is the absolute temperature, k is the Boltzmann constant, q is the magnitude of an electrical charge on an electron, and Vbe2 is a voltage across the diode 236, Vbe1 is a voltage across the diode 256. Id2 is a current run across the diode 236 and Id1 is a current run across the diode 236 and Is1 is the reverse saturate current of the diode 236 and Is1 is the reverse saturate current of the diode 246. The R1-R4 impedances may be calculated assuming that

$$\frac{\partial I_{TJ=0}}{\partial T} = 0 \text{ and } \frac{\partial VBGR}{\partial T} = 0.$$

In an example where the ratio of the size of the diode **236** relative to the size of the diode **246** is 8 to 1, exemplary R1-R4 impedances that may be used are: R1=20 K $\Omega$ , R2=625 K $\Omega$ , R3=250 K $\Omega$ , and R4=300 K $\Omega$ . Using these exemplary values, the VBGR may be maintained at a low power voltage of 0.7 volts. Further, the ISTAB current variation through the transistor **216** may be maintained within less than 1.5% variance across PVT changes.

**[0027]** By using a single amplifier **120** to generate a constant VBGR and ISTAB, the area and power consumption by the current generator **204** may be decreased relative to current generators that use multiple amplifiers.

[0028] Referring to FIG. 3, block diagram of a memory 300 including a delay line circuit according to an embodiment of the disclosure. The memory 300 may include an array 302 of memory cells, which may be, for example, dynamic random-access memory (DRAM) memory cells, static random-access memory (SRAM) memory cells, flash memory cells, or some other types of memory cells. The memory 300 includes a command decoder 306 that may receive memory commands through a command bus 308 and provide (e.g., generate) corresponding control signals within the memory 300 to carry out various memory operations. Row and column address signals may be provided (e.g., applied) to an address latch 310 in the memory 300 through an address bus 320. The address latch 310 may then provide (e.g., output) a separate column address and a separate row address.

[0029] The address latch 310 may provide row and column addresses to a row address decoder 322 and a column address decoder 328, respectively. The column address decoder 328 may select bit lines extending through the array 302 corresponding to respective column addresses. The row address decoder 322 may be connected to a word line driver 324 that activates respective rows of memory cells in the array 302 corresponding to received row addresses. The selected data line (e.g., a bit line or bit lines) corresponding to a received column address may be coupled to a read/write circuitry 330 to provide read data to an output data buffer 334 via an input-output data bus 340. Write data may be provided to the memory array 302 through an input data buffer 344 and the memory array read/write circuitry 330. The command decoder 306 may respond to memory commands provided to the command bus 308 to perform various operations on the memory array 302. In particular, the command decoder 306 may be used to provide internal control signals to read data from and write data to the memory array 302.

**[0030]** The memory **300** may include current generator **313** that is configured to generate a current ISTAB and a voltage VBGR. The ISTAB current may be used by input receivers of an example of active circuits in a semiconductor chip as bias current. The VBGR voltage may be used by power amps of an example of active circuits in a semiconductor chip as reference voltage.

**[0031]** Those of ordinary skill would further appreciate that the various illustrative logical blocks, configurations, modules, circuits, and algorithm steps described in connection with the embodiments disclosed herein may be implemented as electronic hardware, computer software executed by a processor, or combinations of both. Various illustrative components, blocks, configurations, modules, circuits, and steps have been described above generally in terms of their functionality. Skilled artisans may implement the described functionality in varying ways for each particular application, but such implementation decisions should not be interpreted as causing a departure from the scope of the present disclosure.

**[0032]** The previous description of the disclosed embodiments is provided to enable a person skilled in the art to make or use the disclosed embodiments. Various modifications to these embodiments will be readily apparent to those skilled in the art, and the principles defined herein may be applied to other embodiments without departing from the scope of the disclosure. Thus, the present disclosure is not intended to be limited to the embodiments shown herein but is to be accorded the widest scope possible consistent with the principles and novel features as defined by the following claims.

What is claimed is:

1. An apparatus comprising:

a current generator including:

- a plurality of transistors coupled to a voltage source, wherein a gate of each of the plurality of transistors is coupled to a bias line;

- a plurality of circuits coupled to the plurality of transistors, respectively, wherein one circuit of the plurality of circuits is coupled to one transistor of the plurality of transistors, the one circuit includes a plurality of resistors and a diode, and the one circuit

is configured to provide a bandgap voltage having a value based on the plurality of resistors and the diode to the bias line; and

- an amplifier including a first input and a second input, the amplifier configured to provide an output voltage to the bias line responsive to a voltage differential between the first input and the second input,

- wherein a current at an output of the current generator is provided responsive to the output voltage applied to the bias line and remains, based on the plurality of resistors and the diode providing the bandgap voltage, substantially constant in temperature coefficient.

2. The apparatus of claim 1, wherein the one transistor is included, as a first transistor, in the plurality of transistors, and the plurality of transistors further include second and third transistors,

- wherein the one circuit is included, as a voltage circuit, in the plurality of circuits, and the voltage circuit is coupled to the first transistor, and

- wherein the plurality of resistors in the voltage circuit include two resistors.

**3**. The apparatus of claim **1**, wherein the plurality of resistors include a first resistor and a second resistor, and

wherein the first resistor is coupled in parallel with the second resistor and the diode, and the second resistor is coupled in series with the diode.

**4**. The apparatus of claim **1**, wherein the one transistor is included, as a first transistor, in the plurality of transistors, and the plurality of transistors further include second through fourth transistors,

- wherein the one circuit is included, as a voltage circuit, in the plurality of circuits, and the plurality of circuits further include a matching circuit and a current circuit, and

- wherein the matching circuit is coupled to the first input of the amplifier via a first node, and the current circuit is coupled to the second input of the amplifier via a second node.

5. The apparatus of claim 1, wherein the one circuit is included, as a first circuit, in the plurality of circuits, and the plurality of circuits further include a second circuit and a third circuit,

- wherein the second circuit is configured to adjust a voltage at the first input responsive to a change in temperature, and the third circuit is configured to adjust a voltage at the second input responsive to the change in the temperature, and

- wherein the amplifier is configured to adjust the output voltage responsive to the voltage differential between the first input and the second input.

6. The apparatus of claim 1, wherein the one circuit is included, as a first circuit, in the plurality of circuits, and the plurality of circuits further include a second circuit and a third circuit,

- wherein the second circuit is coupled to the first input via a first node, and the third circuit is coupled to the second input via a second node, and

- wherein the output voltage is adjusted based on a change in the voltage differential caused by a process, voltage, or temperature change.

7. The apparatus of claim 1, wherein the one circuit is included, as a voltage circuit, in the plurality of circuits, and the plurality of circuits further include a matching circuit and a current circuit, and

- wherein the plurality of resistors in the voltage circuit include first and second resistors, and the one diode is included in the voltage circuit as a first diode,

- wherein the matching circuit includes third and fourth resistors, and a second diode, and

- wherein the current circuit includes a fifth resistor, and a third diode.

**8**. The apparatus of claim **7**, wherein the first resistor is coupled in parallel with the second resistor and the first diode, and

wherein the second resistor is coupled in series with the first diode.

**9**. The apparatus of claim **7**, wherein the third resistor is coupled in parallel with the fourth resistor and the second diode.

**10**. The apparatus of claim **7**, wherein the third resistor is equal to the fifth resistor.

**11**. A method, comprising:

- providing an output voltage from an amplifier responsive to a voltage differential at inputs of the amplifier;

- coupling, responsive to the output voltage, a voltage source to an output node;

- providing an output current based on the output voltage; providing a substantially constant bandgap voltage based on a voltage circuit including a pair of resistors and a

- diode; and adjusting the output voltage based on a change in the

- voltage differential such that the output current responsive, at least on part, to the bandgap voltage remains substantially constant in temperature coefficient based on the voltage circuit including the pair of resistors and the diode.

12. The method of claim 11, wherein the change in the voltage differential is caused by a process, voltage, or temperature change, and the output voltage is adjusted based on the voltage differential due to the process, voltage, or temperature change.

13. The method of claim 11, further comprising a plurality of transistors,

- wherein a gate of each of the plurality of transistors is coupled to a bias line, and

- wherein the output voltage is provided from the amplifier to the bias line, and the bandgap voltage has a value based on the output voltage provided to the bias line.14. The method of claim 13, further comprising:

- providing a first voltage to a first input of the amplifier via

- a matching circuit; and

- coupling the voltage source to the matching circuit via a second transistor of the plurality of transistors.

- 15. The method of claim 14, further comprising:

- providing a second voltage to a second input of the amplifier via a current circuit; and

- coupling the voltage source to the current circuit via a third transistor of the plurality of transistors.

16. The method of claim 15, wherein the output current is provided through a fourth transistor of the plurality of transistors based on the output voltage.

17. An apparatus comprising:

- a current generator including:

- a first circuit coupled to a first transistor, wherein the first circuit includes a plurality of resistors and a diode, and the first circuit is configured to provide a bandgap voltage having a value based on the plurality of resistors and the diode to a bias line; and

- an amplifier including a non-inverting input coupled to a node between a second transistor and a second circuit, the amplifier further including an inverting input coupled to a node between a third transistor and a third circuit, the amplifier configured to provide an output voltage to the bias line responsive to a voltage differential between the non-inverting input and the inverting input,

- wherein a current through a fourth transistor coupled to an output of the current generator is provided responsive to the output voltage applied to the bias line and remains, based on the plurality of resistors and the diode providing the bandgap voltage, substantially constant in temperature coefficient.

**18**. The apparatus of claim **17**, wherein the plurality of resistors in the first circuit include two resistors, and

wherein one resistor of the two resistors is coupled in parallel with another resistor of the two resistors and the diode, and the other resistor is coupled in series with the diode.

**19**. The apparatus of claim **17**, wherein the plurality of resistors in the first circuit include first and second resistors, and the one diode is included in the first circuit as a first diode,

- wherein the second circuit includes third and fourth resistors, and a second diode, and

- wherein the third circuit includes a fifth resistor and a third diode.

**20**. The apparatus of claim **17**, wherein the output voltage is adjusted based on a change in the voltage differential caused by a process, voltage, or temperature change.

\* \* \* \* \*