# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2019/0199226 A1

Huang Zhan et al.

Jun. 27, 2019 (43) **Pub. Date:**

## (54) VOLTAGE CONVERTING DEVICE AND METHOD OF CONTROLLING THE VOLTAGE CONVERTING DEVICE

(71) Applicant: XIAMEN KEHUA HENGSHENG LIMITED BY SHARE LTD., Xiamen

(72) Inventors: Jiangyong Huang Zhan, Xiamen (CN); Longqiang Yi, Xiamen (CN); Zhidong Wang, Xiamen (CN); Jinrong Wu, Xiamen (CN); Qingbin Wu, Xiamen (CN); Xiaofan Zhong, Xiamen (CN); Haiquan Lian, Xiamen (CN)

Appl. No.: 16/229,922

(22)Filed: Dec. 21, 2018

#### (30)Foreign Application Priority Data

| Dec. 22, 2017 | (CN) | 201711404269.6 |

|---------------|------|----------------|

| Dec. 22, 2017 | (CN) | 201711406133.9 |

| Dec. 22, 2017 | (CN) | 201711406162.5 |

| Dec. 22, 2017 | (CN) | 201711406600.8 |

| Dec. 22, 2017 | (CN) | <br>201711407593.3 |

|---------------|------|--------------------|

| Dec. 22, 2017 | (CN) | <br>201711407633.4 |

#### **Publication Classification**

(51) Int. Cl. H02M 3/335 (2006.01)H02J 3/38 (2006.01)H02J 7/35 (2006.01)H02M 1/08 (2006.01)

> U.S. Cl. CPC ...... H02M 3/33584 (2013.01); H02M 1/083 (2013.01); H02J 7/35 (2013.01); H02J 3/383

#### (57)**ABSTRACT**

A voltage converting device includes: a first power supply, having a first positive terminal and a first negative terminal; a first bridge circuit, coupled to the first positive terminal; a second bridge circuit, coupled between the first bridge circuit and the first negative terminal; a second power supply, having a second positive terminal and a second negative terminal; a third bridge circuit, coupled to the second positive terminal; a fourth bridge circuit, coupled between the third bridge circuit and the second negative terminal; and an inductive circuit, coupled between the first bridge circuit and the second bridge circuit.

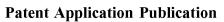

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

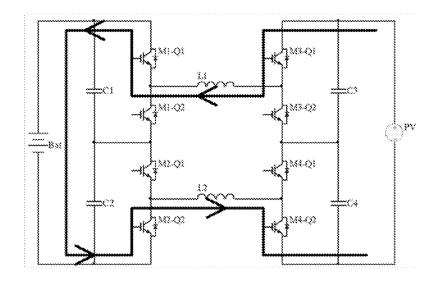

FIG. 8

FIG. 9

FIG. 11

FIG. 12

FIG. 15

FIG. 16

FIG. 17

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

FIG. 28

FIG. 29

FIG. 30

FIG. 31

FIG. 32

FIG. 33

## VOLTAGE CONVERTING DEVICE AND METHOD OF CONTROLLING THE VOLTAGE CONVERTING DEVICE

#### BACKGROUND

[0001] A DCDC converting device is arranged to convert a source of direct current (DC) from one voltage level to another voltage levels. The DCDC converting device may be used in the field of solar power to up-convert (i.e. Boost) or down-convert (i.e. Buck) the voltage level of the direct current. Currently, a DCDC converting device is either a Boost convert or a Buck converter. Moreover, in a system with a relatively high operating voltage level, e.g. 1000V or higher, the cost of the high-voltage switching device is relatively high.

[0002] In addition, for the example of a Buck converter, when the output loading is full, the Buck converter may operate in the continuous current mode (CCM). The output loading current may be the average current of the inductor current. When the loading current decreases, the average current of the inductor current also decreases. When the average current of the inductor current reaches a specific value, the Buck convert enter the threshold current mode. If the loading current further decreases, and the inductor current reaches zero and the switching cycle is not finished yet, then the inductor current may be kept on the zero current for some time due to the diode. When the switching cycle finishes, the Buck converter enter the next switching cycle, and the next switching cycle may be the discontinuous current mode (DCM). The conventional Boost converter or Buck converter only operates in the discontinuous current mode when the loading current is small. When the loading current is small, the sampling of the inductor current may be inaccurate due to the discontinuity of the inductor current. Accordingly, the loop bandwidth of the Buck converter is relatively small, and oscillation may occur in the system.

## SUMMARY

[0003] Embodiments of the present invention provide a voltage converting device. The voltage converting device comprises: a first power supply, having a first positive terminal and a first negative terminal; a first bridge circuit, coupled to the first positive terminal; a second bridge circuit, coupled between the first bridge circuit and the first negative terminal; a second power supply, having a second positive terminal and a second negative terminal; a third bridge circuit, coupled to the second positive terminal; a fourth bridge circuit, coupled between the third bridge circuit and the second negative terminal; and an inductive circuit, coupled between the first bridge circuit and the second bridge circuit.

[0004] In one embodiment, the first power supply is a power battery pack and the second power supply is a photovoltaic system.

[0005] In one embodiment, the first bridge circuit comprises: a first capacitor, having a first terminal coupled to the first positive terminal; a first switching transistor, having a first terminal coupled to the first terminal of the first capacitor; a second switching transistor, having a first terminal coupled to a second terminal of the first switching transistor, and a second terminal coupled to a second terminal of the first capacitor. The second bridge circuit comprises: a second capacitor, having a first terminal coupled to the second

terminal of the first capacitor, and a second terminal coupled to the first negative terminal of the first power supply; a third switching transistor, having a first terminal coupled to the first terminal of the second capacitor; a fourth switching transistor, having a first terminal coupled to a second terminal of the third switching transistor, and a second terminal coupled to the second terminal of the first capacitor. The third bridge circuit comprises: a third capacitor, having a first terminal coupled to the second positive terminal; a fifth switching transistor, having a first terminal coupled to the first terminal of the third capacitor; a sixth switching transistor, having a first terminal coupled to a second terminal of the fifth switching transistor, and a second terminal coupled to a second terminal of the third capacitor. The fourth bridge circuit comprises: a fourth capacitor, having a first terminal coupled to the second terminal of the third capacitor, and a second terminal coupled to the second negative terminal of the second power supply; a seventh switching transistor, having a first terminal coupled to the first terminal of the fourth capacitor; an eighth switching transistor, having a first terminal coupled to a second terminal of the seventh switching transistor, and a second terminal coupled to the second terminal of the fourth capacitor. The inductive circuit comprises: a first inductor, having a first terminal coupled to the second terminal of the first switching transistor, and a second terminal coupled to the second terminal of the fifth switching transistor; and a second inductor, having a first terminal coupled to the second terminal of the third switching transistor, and a second terminal coupled to the second terminal of the seventh switching transistor.

[0006] In one embodiment, the first capacitor, the second capacitor, the third capacitor, and the fourth capacitor have a first capacitance, a second capacitance, a third capacitance, and a fourth capacitance respectively, the first capacitance is equal to the second capacitance, and the third capacitance is equal to the fourth capacitance.

[0007] In one embodiment, the second terminal of the second switching transistor is coupled to the second terminal of the sixth switching transistor.

[0008] In one embodiment, the voltage converting device further comprises: a first connecting circuit, coupled to the first positive terminal, the first negative terminal, the first bridge circuit, and the second bridge circuit; and a second connecting circuit, coupled to the second positive terminal, the second negative terminal, the third bridge circuit, and the fourth bridge circuit.

[0009] In one embodiment, the first bridge circuit comprises: a first capacitor, having a first terminal coupled to the first positive terminal; a first switching transistor, having a first terminal coupled to the first terminal of the first capacitor, and a second terminal coupled to a second terminal of the first capacitor; a second capacitor, having a first terminal coupled to the second terminal of the first capacitor; a second switching transistor, having a first terminal coupled to the first terminal of the second capacitor, and a second terminal coupled to a second terminal of the first capacitor. The second bridge circuit comprises: a third capacitor, having a first terminal coupled to the second terminal of the second capacitor; a third switching transistor, having a first terminal coupled to the first terminal of the third capacitor, and a second terminal coupled to a second terminal of the third capacitor, a fourth capacitor, having a first terminal coupled to the second terminal of the third capacitor; a fourth switching transistor, having a first terminal coupled to

the first terminal of the fourth capacitor, and a second terminal coupled to a second terminal of the fourth capacitor. The third bridge circuit comprises: a fifth capacitor, having a first terminal coupled to the second positive terminal; a fifth switching transistor, having a first terminal coupled to the first terminal of the fifth capacitor, and a second terminal coupled to a second terminal of the fifth capacitor; a sixth capacitor, having a first terminal coupled to the second terminal of the fifth capacitor; a sixth switching transistor, having a first terminal coupled to the first terminal of the sixth capacitor, and a second terminal coupled to a second terminal of the sixth capacitor. The fourth bridge circuit comprises: a seventh capacitor, having a first terminal coupled to the second terminal of the sixth capacitor; a seventh switching transistor, having a first terminal coupled to the first terminal of the seventh capacitor, and a second terminal coupled to a second terminal of the seventh capacitor; an eighth capacitor, having a first terminal coupled to the second terminal of the seventh capacitor; an eighth switching transistor, having a first terminal coupled to the first terminal of the eighth capacitor, and a second terminal coupled to a second terminal of the eighth capacitor. The inductive circuit comprises: an inductor, having a first terminal coupled to the second terminal of the second switching transistor, and a second terminal coupled to the second terminal of the sixth switching transistor.

[0010] In one embodiment, the first capacitor, the second capacitor, the third capacitor, the fourth capacitor, the fifth capacitor, the sixth capacitor, the seventh capacitor, and the eighth capacitor have a first capacitance, a second capacitance, a third capacitance, a fourth capacitance, a fifth capacitance, a sixth capacitance, a seventh capacitance, and an eighth capacitance respectively, the first capacitance and the second capacitance are equal to the third capacitance and the fourth capacitance respectively, and the fifth capacitance and the sixth capacitance are equal to the seventh capacitance and the eighth capacitance respectively.

[0011] In one embodiment, the first connecting circuit comprises: a ninth capacitor, having a first terminal coupled to the first positive terminal; a tenth capacitor, having a first terminal coupled to a second terminal of the ninth capacitor, and a second terminal coupled to the first negative terminal; an eleventh capacitor, having a first terminal coupled to the second terminal of the first capacitor, and a second terminal coupled to the second terminal of the third capacitor; a first diode, having an anode coupled to the second terminal of the ninth capacitor, and a cathode coupled to the first terminal of the eleventh capacitor; and a second diode, having an anode coupled to the second terminal of the eleventh capacitor, and a cathode coupled to the second terminal of the ninth capacitor. The second connecting circuit comprises: a twelfth capacitor, having a first terminal coupled to the second positive terminal; a thirteenth capacitor, having a first terminal coupled to a second terminal of the twelfth capacitor, and a second terminal coupled to the second negative terminal; a fourteenth capacitor, having a first terminal coupled to the second terminal of the fifth capacitor and a second terminal coupled to the seventh capacitor; a third diode, having an anode coupled to the second terminal of the twelfth capacitor, and a cathode coupled to the first terminal of the fourteenth capacitor; and a fourth diode, having an anode coupled to the second terminal of the fourteenth capacitor, and a cathode coupled to the second terminal of the twelfth capacitor.

[0012] A method of controlling a voltage converting device is provided. The voltage converting device comprises: a first power supply, having a first positive terminal and a first negative terminal; a first bridge circuit, having a first switching transistor and a second switching transistor, coupled to the first positive terminal; a second bridge circuit, having a third switching transistor and a fourth switching transistor, coupled between the first bridge circuit and the first negative terminal; a second power supply, having a second positive terminal and a second negative terminal; a third bridge circuit, having a fifth switching transistor and a sixth switching transistor, coupled to the second positive terminal; a fourth bridge circuit, having a seventh switching transistor and an eight switching transistor, coupled between the third bridge circuit and the second negative terminal; and an inductive circuit, coupled between the first bridge circuit and the second bridge circuit. The method comprises: receiving a request for discharging current to the second power supply from the first power supply; detecting a first voltage level of the first power supply and a second voltage level of the second power supply; when the first voltage level is smaller than the second voltage level: controlling the voltage converting device to operate in a first cycle having a first time interval T1 and a second time interval T2; during the second time interval T2, detecting if a current of the inductive circuit crosses a zero current; when the current crosses the zero current in the second time interval T2, controlling the voltage converting device to operate in a second cycle having a third time interval T3 and a fourth time interval T4 or a third cycle having a seventh time interval T7 and an eighth interval T8 after the second time interval T2; when the first voltage level is higher than the second voltage level: controlling the voltage converting device to operate in a fourth cycle having a fifth time interval T5 and a sixth time interval T6; during the sixth time interval T6, detecting if the current of the inductive circuit crosses the zero current; when the current crosses the zero current in the sixth time interval T6, controlling the voltage converting device to operate in a fifth cycle having the third time interval T3 and the fourth time interval T4 or a sixth cycle having the seventh time interval T7 and the eighth interval T8, or a seventh cycle having the third time interval T3 and the fourth time interval T4 after the sixth time interval T6.

[0013] In one embodiment, wherein: during the first time interval T1, the first switching transistor and the sixth switching transistor are turned on, the second switching transistor and the fifth switching transistor are turned off; during the second time interval T2, the sixth switching transistor is turned off; during the third time interval T3, the fifth switching transistor is turned on, the second switching transistor and the sixth switching transistor are turned off; during the fourth time interval T4, the second switching transistor and the fifth switching transistor are turned off; during the fifth time interval T5, the first switching transistor is turned on, the second switching transistor and the sixth switching transistor are turned off; during the sixth time interval T6, the first switching transistor and the sixth switching transistor are turned off; during the seventh time interval T7, the second switching transistor and the fifth switching transistor are turned on, the first switching transistor and the sixth switching transistor are turned off; during the eighth time interval T8, the second switching transistor is turned off; wherein the fourth switching transistor and the first switching transistor are controlled by a first signal, the third switching transistor and the second switching transistor are controlled by a second signal, the eight switching transistor and the fifth switching transistor are controlled by a third signal, and the seventh switching transistor and the sixth switching transistor are controlled by a fourth signal. [0014] In one embodiment, wherein, during a cycle having time intervals T1, T2, T3, T4, the voltage converting device is arranged to operate in the third interval T3 before the current crosses the zero current; during a cycle having time intervals T1, T2, T7, T8, the voltage converting device is arranged to operate in the seventh interval T7 before the current crosses the zero current; during a cycle having time intervals T5, T6, T7, T8, the voltage converting device is arranged to operate in the seventh interval T7 before the current crosses the zero current; and during a cycle having time intervals T5, T6, T3, T4, the voltage converting device is arranged to operate in the third interval T3 before the current crosses the zero current.

[0015] In one embodiment, wherein, during a cycle having time intervals T1, T2, T3, T4, the fifth switching transistor is turned on and the second switching transistor is turned off in the second interval T2; during a cycle having time intervals T1, T2, T7, T8, the second switching transistor and the fifth switching transistor are turned on in the second interval T2; during a cycle having time intervals T5, T6, T7, T8, the second switching transistor and the fifth switching transistor are turned on in the sixth interval T6; and during a cycle having time intervals T5, T6, T3, T4, the fifth switching transistor is turned on and the second switching transistor is turned off in the sixth interval T6.

[0016] In one embodiment, wherein, during the cycle having time intervals T1, T2, T3, T4, the first switching transistor and the sixth switching transistor are turned on in the fourth interval T4; during the cycle having time intervals T1, T2, T7, T8, the first switching transistor and the sixth switching transistor are turned on in the eighth interval T8; during the cycle having time intervals T5, T6, T7, T8, the first switching transistor is turned on and the sixth switching transistor is turned off in the eighth interval T8; and during the cycle having time intervals T5, T6, T3, T4, the first switching transistor and the sixth switching transistor are turned off in the fourth interval T4.

[0017] In one embodiment, wherein the first switching transistor is turned off in the second interval T2, and the fifth switching transistor is turned off in the eighth interval T8.

[0018] In one embodiment, wherein the first switching

transistor is turned on in the third interval T3, and the fifth switching transistor is turned on in the fifth interval T5.

[0019] In one embodiment, wherein: during the first time interval T1, the first bridge circuit and the fourth bridge circuit are turned on, and the second bridge circuit and the third bridge circuit are turned off; during the second time interval T2, the fourth bridge circuit is turned off, and the first bridge circuit and the second bridge circuit are not turned on at the same time; during the third time interval T3, the third bridge circuit is turned on, and the second bridge circuit and the fourth bridge circuit are turned off; during the fourth time interval T4, the second bridge circuit and the third bridge circuit are turned off; during the fifth time interval T5, the first bridge circuit is turned on, and the second bridge circuit and the fourth bridge circuit are turned off; during the sixth time interval T6, the first bridge circuit and the fourth bridge circuit are turned off; during the seventh time interval T7, the second bridge circuit and the third bridge circuit are turned on, and the first bridge circuit and the fourth bridge circuit are turned off; during the eighth time interval T8, the second bridge circuit is turned off, and the third bridge circuit and the fourth bridge circuit are not turned on at the same time.

[0020] In one embodiment, wherein, during a cycle having time intervals T1, T2, T3, T4, the third bridge circuit is turned on and the second bridge circuit is turned off in the second interval T2; during a cycle having time intervals T1, T2, T7, T8, the second bridge circuit and the third bridge circuit are turned on in the second interval T2; during a cycle having time intervals T5, T6, T7, T8, the second bridge circuit and the third bridge circuit and the third bridge circuit are turned on in the sixth interval T6; and during a cycle having time intervals T5, T6, T3, T4, the third bridge circuit is turned on and the second bridge circuit is turned off in the sixth interval T6.

[0021] In one embodiment, wherein, during the cycle having time intervals T1, T2, T3, T4, the first bridge circuit and the fourth bridge circuit are turned on in the fourth interval T4; during the cycle having time intervals T1, T2, T7, T8, the first bridge circuit and the fourth bridge circuit are turned on and the third bridge circuit is turned off in the eighth interval T8; during the cycle having time intervals T5, T6, T7, T8, the first bridge circuit is turned on and the fourth bridge circuit is turned off in the eighth interval T8; and during the cycle having time intervals T5, T6, T3, T4, the first bridge circuit is turned on and the fourth bridge circuit is turned off in the fourth bridge circuit is turned off in the fourth bridge circuit is turned off in the fourth interval T4.

[0022] In one embodiment, wherein the first bridge circuit is turned off in the second interval T2, the third bridge circuit is turned off in the eighth interval T8, the first bridge circuit is turned on in the third interval T3, and the third bridge circuit is turned on in the fifth interval T5.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0023] Aspects of the present disclosure are best understood from the following detailed description when read with the accompanying figures. It is noted that, in accordance with the standard practice in the industry, various features are not drawn to scale. In fact, the dimensions of the various features may be arbitrarily increased or reduced for clarity of discussion.

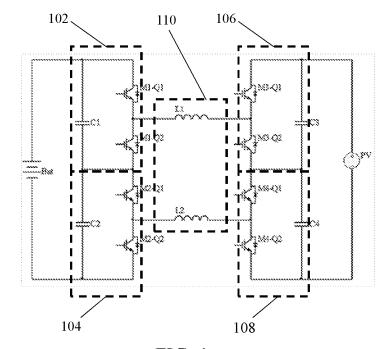

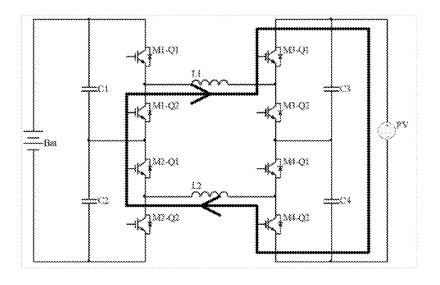

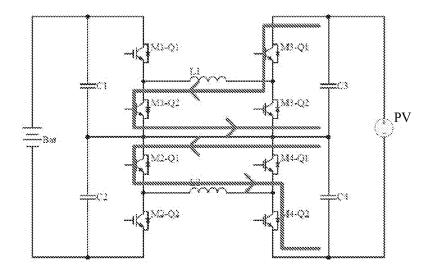

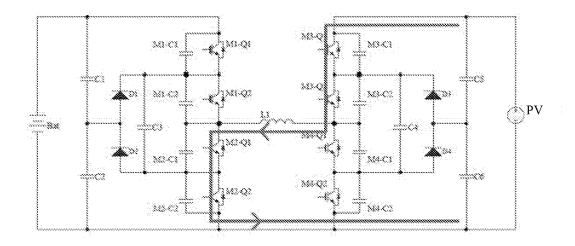

[0024] FIG. 1 is a diagram illustrating a DCDC (Direct Current to Direct Current) double-direction converting device in accordance with some embodiments.

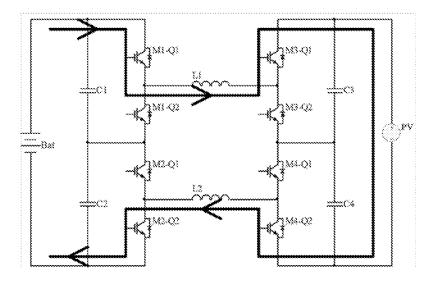

[0025] FIG. 2 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

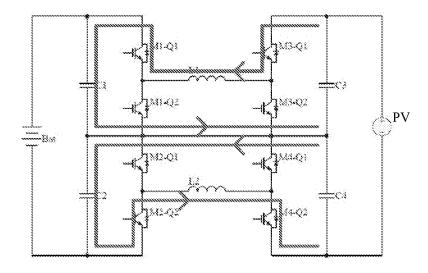

[0026] FIG. 3 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

[0027] FIG. 4 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

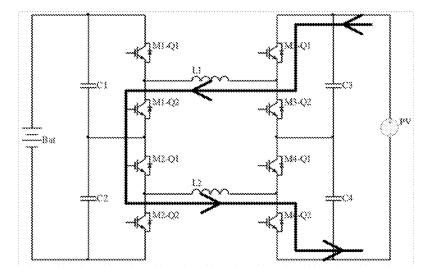

[0028] FIG. 5 is a diagram illustrating a second power supply discharging a first power supply Bat in accordance with some embodiments.

[0029] FIG. 6 is a diagram illustrating a second power supply discharging a first power supply in accordance with some embodiments.

[0030] FIG. 7 is a diagram illustrating a second power supply charging a first power supply in accordance with some embodiments.

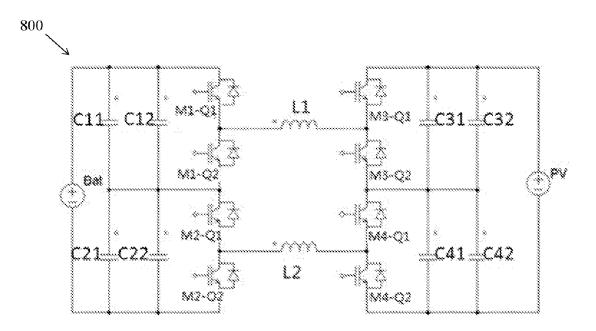

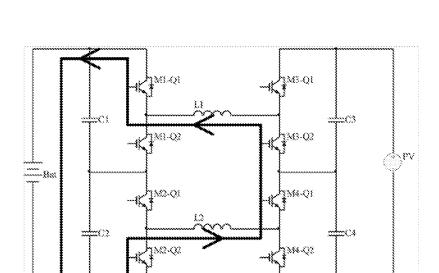

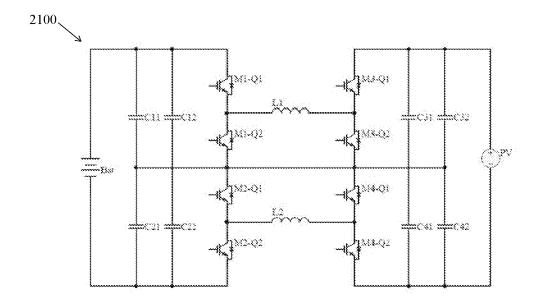

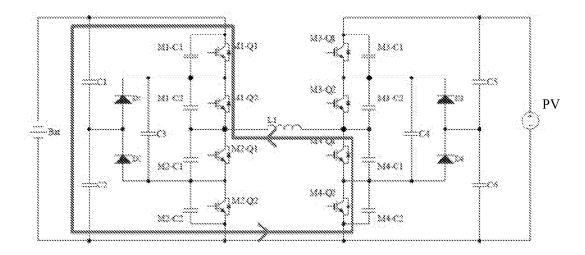

[0031] FIG. 8 is a diagram illustrating a DCDC double-direction converting device in accordance with some embodiments.

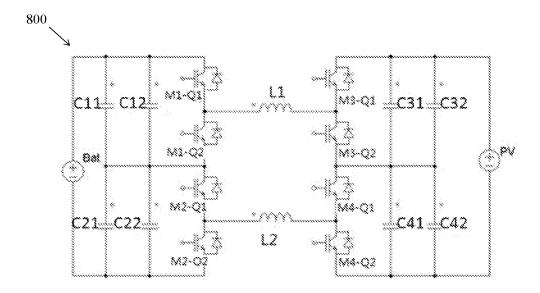

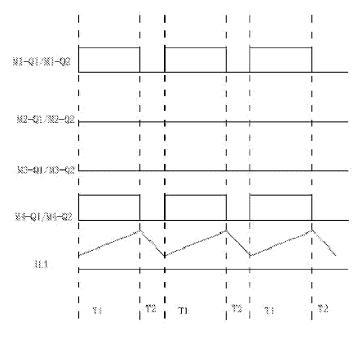

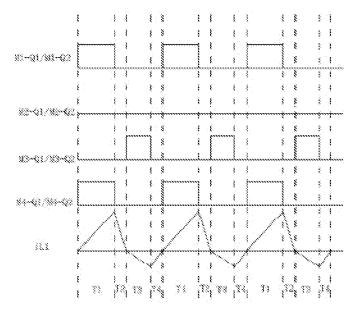

[0032] FIG. 9 is a timing diagram illustrating signals in the time intervals  $T1\sim T2$  in accordance with some embodiments

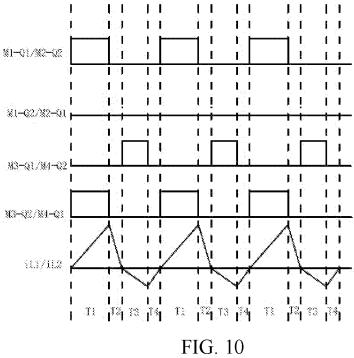

[0033] FIG. 10 is a timing diagram illustrating signals in the time intervals T1, T2, T3, and T4 in accordance with some embodiments.

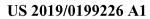

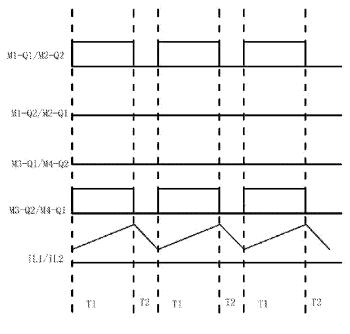

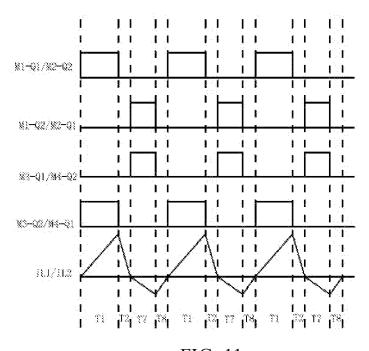

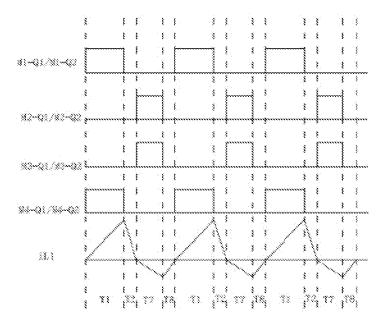

[0034] FIG. 11 is a timing diagram illustrating signals in the time intervals T1, T2, T7, and T8 in accordance with some embodiments.

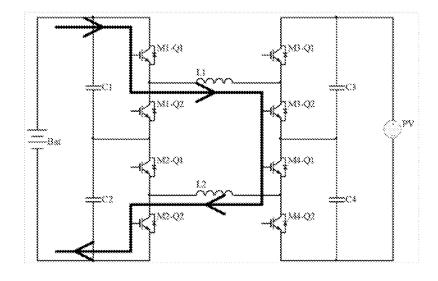

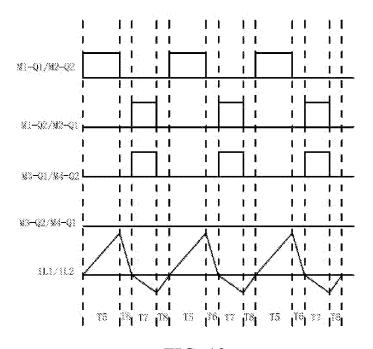

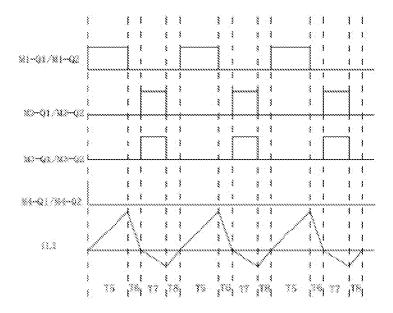

[0035] FIG. 12 is a timing diagram illustrating signals in the time intervals T5, T6, T7, and T8 in accordance with some embodiments.

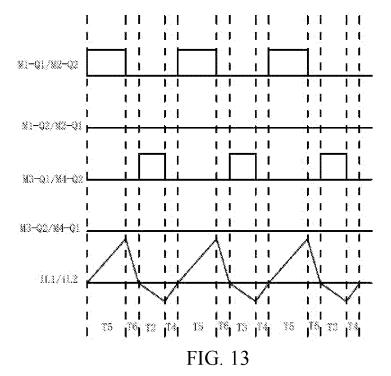

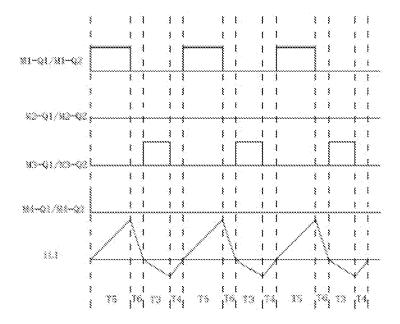

[0036] FIG. 13 is a timing diagram illustrating signals in the time intervals T5, T6, T3, and T4 in accordance with some embodiments.

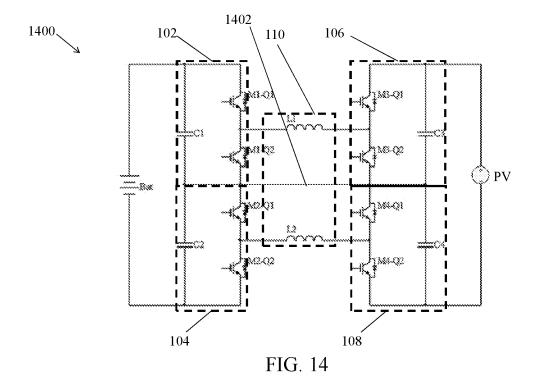

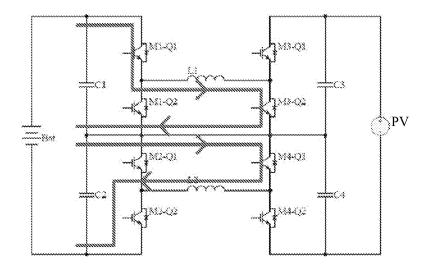

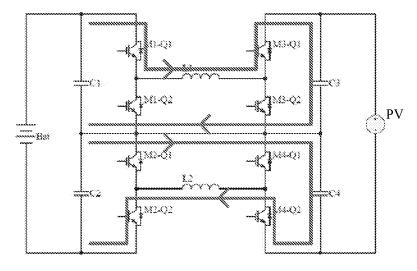

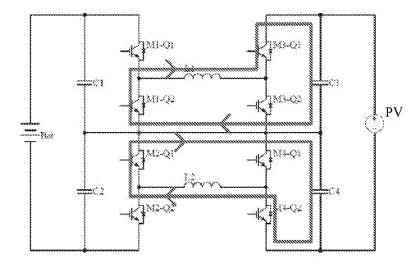

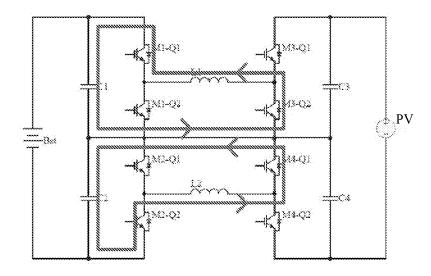

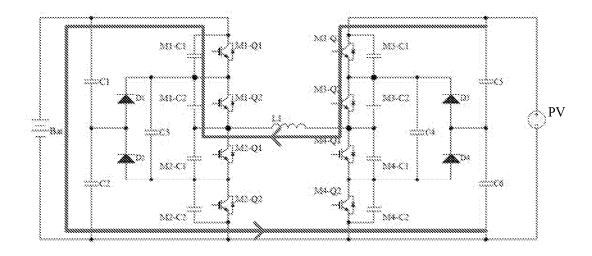

[0037] FIG. 14 is a diagram illustrating a DCDC (Direct Current to Direct Current) double-direction converting device in accordance with some embodiments.

[0038] FIG. 15 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

[0039] FIG. 16 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

[0040] FIG. 17 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

[0041] FIG. 18 is a diagram illustrating a first power supply charging a second power supply in accordance with some embodiments

[0042] FIG. 19 is a diagram illustrating a second power supply discharging a first power supply in accordance with some embodiments.

[0043] FIG. 20 is a diagram illustrating a second power supply charging a first power supply in accordance with some embodiments.

[0044] FIG. 21 is a diagram illustrating a DCDC doubledirection converting device in accordance with some embodiments.

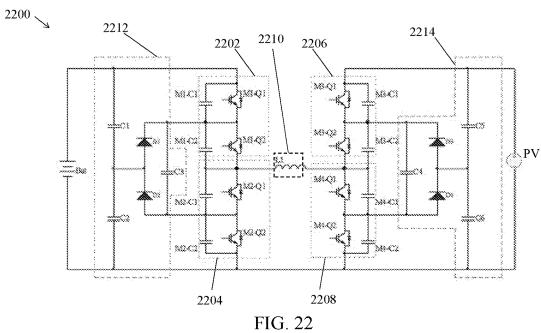

[0045] FIG. 22 is a diagram illustrating a DCDC (Direct Current to Direct Current) double-direction converting device in accordance with some embodiments.

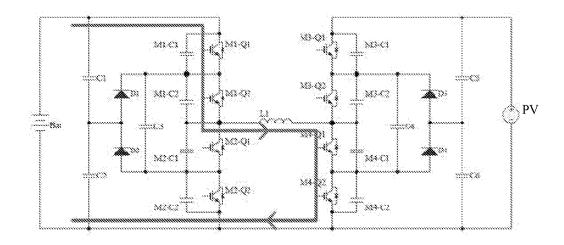

[0046] FIG. 23 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

[0047] FIG. 24 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

[0048] FIG. 25 is a diagram illustrating a first power supply discharging a second power supply in accordance with some embodiments.

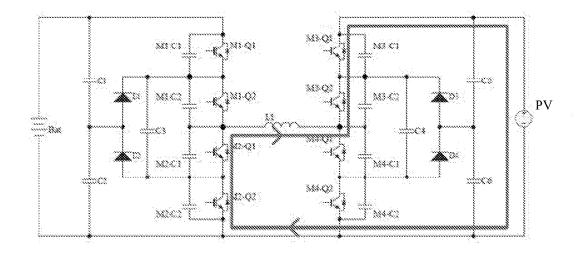

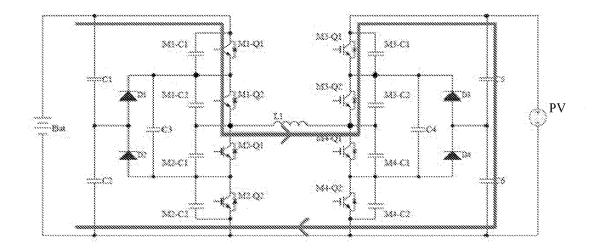

[0049] FIG. 26 is a diagram illustrating a second power supply charging a first power supply in accordance with some embodiments.

[0050] FIG. 27 is a diagram illustrating a second power supply discharging a first power supply in accordance with some embodiments.

[0051] FIG. 28 is a diagram illustrating a second power supply charging a first power supply in accordance with some embodiments.

[0052] FIG. 29 is a timing diagram illustrating the signals in the time intervals  $T1\sim T2$  in accordance with some embodiments.

[0053] FIG. 30 is a timing diagram illustrating signals in the time intervals T1, T2, T3, and T4 in accordance with some embodiments.

[0054] FIG. 31 is a timing diagram illustrating signals in the time intervals T1, T2, T7, and T8 in accordance with some embodiments.

[0055] FIG. 32 is a timing diagram illustrating signals in the time intervals T5, T6, T7, and T8 in accordance with some embodiments.

[0056] FIG. 33 is a timing diagram illustrating signals in the time intervals T5, T6 T3, T4 in accordance with some embodiments.

### DETAILED DESCRIPTION

[0057] The following disclosure provides many different embodiments, or examples, for implementing different features of the provided subject matter. Specific examples of components and arrangements are described below to simplify the present disclosure. These are, of course, merely examples and are not intended to be limiting. For example, the formation of a first feature over or on a second feature in the description that follows may include embodiments in which the first and second features are formed in direct contact, and may also include embodiments in which additional features may be formed between the first and second features, such that the first and second features may not be in direct contact. In addition, the present disclosure may repeat reference numerals and/or letters in the various examples. This repetition is for the purpose of simplicity and clarity and does not in itself dictate a relationship between the various embodiments and/or configurations discussed.

[0058] Further, spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element or feature's relationship to another element(s) or feature(s) as illustrated in the figures. The spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. The apparatus may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein may likewise be interpreted accordingly.

[0059] Notwithstanding that the numerical ranges and parameters setting forth the broad scope of the disclosure are approximations, the numerical values set forth in the specific examples are reported as precisely as possible. Any numerical value, however, inherently contains certain errors necessarily resulting from the standard deviation found in the respective testing measurements. Also, as used herein, the term "about" generally means within 10%, 5%, 1%, or 0.5% of a given value or range. Alternatively, the term "about" means within an acceptable standard error of the mean when considered by one of ordinary skill in the art. Other than in the operating/working examples, or unless otherwise expressly specified, all of the numerical ranges, amounts, values and percentages such as those for quantities of materials, durations of times, temperatures, operating conditions, ratios of amounts, and the likes thereof disclosed herein should be understood as modified in all instances by the term "about." Accordingly, unless indicated to the contrary, the numerical parameters set forth in the present disclosure and attached claims are approximations that can vary as desired. At the very least, each numerical parameter should at least be construed in light of the number of reported significant digits and by applying ordinary rounding techniques. Ranges can be expressed herein as from one end point to another end point or between two end points. All ranges disclosed herein are inclusive of the end points, unless specified otherwise.

[0060] FIG. 1 is a diagram illustrating a DCDC (Direct Current to Direct Current) double-direction converting device 100 in accordance with some embodiments. The DCDC double-direction converting device 100 is a voltage converter capable of generating a higher voltage level according to a lower voltage level or generating a lower voltage level according to a higher voltage level. The DCDC double-direction converting device 100 comprises a first power supply Bat, a first bridge circuit 102, a second bridge circuit 104, a second power supply PV, a third bridge circuit 106, a fourth bridge circuit 108, and an inductive circuit 110. The first power supply Bat has a first positive terminal and a first negative terminal. The first bridge circuit 102 is coupled to the first positive terminal. The second bridge circuit 104 is coupled between the first bridge circuit 102 and the first negative terminal. The second power supply PV has a second positive terminal and a second negative terminal. The third bridge circuit 106 is coupled to the second positive terminal. The fourth bridge circuit 108 is coupled between the third bridge circuit 106 and the second negative terminal. The inductive circuit 110 is coupled between the first bridge circuit 102 and the second bridge circuit 104.

[0061] According to some embodiments, the first power supply Bat is a power battery pack and the second power supply PV is a photovoltaic system.

[0062] Furthermore, the first bridge circuit 102 comprises a first capacitor C1, a first switching transistor M1-Q1, and a second switching transistor M1-Q2. The first capacitor C1 has a first terminal coupled to the first positive terminal. The first switching transistor M1-Q1 has a first terminal coupled to the first terminal of the first capacitor C1. The second switching transistor M1-Q2 has a first terminal coupled to a second terminal of the first switching transistor M1-Q1, and a second terminal coupled to a second terminal of the first capacitor C1.

[0063] The second bridge circuit 104 comprises a second capacitor C2, a third switching transistor M2-Q1, and a fourth switching transistor M2-Q1. The second capacitor C2 has a first terminal coupled to the second terminal of the first capacitor C1, and a second terminal coupled to the first negative terminal of the first power supply Bat. The third switching transistor M2-Q1 has a first terminal coupled to the first terminal of the second capacitor C2. The fourth switching transistor M2-Q2 has a first terminal coupled to a second terminal of the third switching transistor M2-Q1, and a second terminal coupled to the second terminal of the first capacitor C1.

[0064] The third bridge circuit 106 comprises a third capacitor C3, a fifth switching transistor M3-Q1, and a sixth switching transistor M3-Q2. The third capacitor C3 has a first terminal coupled to the second positive terminal. The fifth switching transistor M3-Q1 has a first terminal coupled to the first terminal of the third capacitor C3. The sixth switching transistor M3-Q2 has a first terminal coupled to a

second terminal of the fifth switching transistor M3-Q1, and a second terminal coupled to a second terminal of the third capacitor C3.

[0065] The fourth bridge circuit 108 comprises a fourth capacitor C4, a seventh switching transistor M4-Q1, an eighth switching transistor M4-Q2. The fourth capacitor C4 has a first terminal coupled to the second terminal of the third capacitor C3, and a second terminal coupled to the second negative terminal of the second power supply PV. The seventh switching transistor M4-Q1 has a first terminal coupled to the first terminal of the fourth capacitor C4. The eighth switching transistor M4-Q2 has a first terminal coupled to a second terminal of the seventh switching transistor M4-Q1, and a second terminal coupled to the second terminal of the fourth capacitor C4.

[0066] The inductive circuit 110 comprises a first inductor L1 and a second inductor L2. The first inductor L1 has a first terminal coupled to the second terminal of the first switching transistor M1-Q1, and a second terminal coupled to the second terminal of the fifth switching transistor M3-Q1. The second inductor L2 has a first terminal coupled to the second terminal of the third switching transistor M2-Q1, and a second terminal coupled to the second terminal of the seventh switching transistor M4-Q1.

[0067] According to some embodiments, the switching transistors M1-Q1, M1-Q2, M2-Q1, M2-Q2, M3-Q1, M3-Q2, M4-Q1, M4-Q2 are N-channel (or P-channel) Insulated Gate Bipolar Transistor (IGBT). However, this is not a limitation of the present invention. The switching transistors M1-Q1, M1-Q2, M2-Q1, M2-Q2, M3-Q1, M3-Q2, M4-Q1, and M4-Q2 may be N-channel (or P-channel) metal-oxide-semiconductor field-effect transistor (MOS-FET). Moreover, when the switching transistor M1-Q1, as well as the switching transistors M1-Q2, M2-Q1, M2-Q2, M3-Q1, M3-Q2, M4-Q1, M4-Q2, are N-channel IGBT, the first terminal of the switching transistor M1-Q1 is the collector and the second terminal of the switching transistor M1-Q1 is the emitter. When the switching transistor M1-Q1, as well as the switching transistors M1-Q2, M2-Q1, M2-Q2, M3-Q1, M3-Q2, M4-Q1, M4-Q2, are N-channel MOSFET, the first terminal of the switching transistor M1-Q1 is the drain and the second terminal of the switching transistor M1-Q1 is the source.

[0068] In addition, for one bridge circuit (e.g. 102), the switching transistors (e.g. M1-Q1 and M1-Q2) may be implemented as two discrete transistors device or implemented as an integrated transistor having two IGBTs.

[0069] According to some embodiments, for the first bridge circuit 102, the emitter of the first switching transistor M1-Q1 is connected to the collector of the second switching transistor M1-Q2 to form a common terminal of the first bridge circuit 102. The capacitor C1 is a polarized capacitor, in which the first terminal of the capacitor C1 is the positive plate (or anode) and the second terminal of the capacitor C1 is the negative plate (or cathode). The positive plate of the capacitor C1 is connected to the collector of the first switching transistor M1-Q1, and the negative plate of the capacitor C1 is connected to the emitter of the second switching transistor M1-Q2.

[0070] For the second bridge circuit 104, the emitter of the third switching transistor M2-Q1 is connected to the collector of the fourth switching transistor M2-Q2 to form a common terminal of the second bridge circuit 104. The capacitor C2 is a polarized capacitor, in which the first

terminal of the capacitor C2 is the positive plate (or anode) and the second terminal of the capacitor C2 is the negative plate (or cathode). The positive plate of the capacitor C2 is connected to the collector of the third switching transistor M2-Q1, and the negative plate of the capacitor C2 is connected to the emitter of the fourth switching transistor M2-Q2.

[0071] For the third bridge circuit 106, the emitter of the fifth switching transistor M3-Q1 is connected to the collector of the sixth switching transistor M3-Q2 to form a common terminal of the third bridge circuit 106. The capacitor C3 is a polarized capacitor, in which the first terminal of the capacitor C3 is the positive plate (or anode) and the second terminal of the capacitor C3 is the negative plate (or cathode). The positive plate of the capacitor C3 is connected to the collector of the fifth switching transistor M3-Q1, and the negative plate of the capacitor C3 is connected to the emitter of the sixth switching transistor M3-Q2.

[0072] For the fourth bridge circuit 108, the emitter of the seventh switching transistor M4-Q1 is connected to the collector of the eighth switching transistor M4-Q2 to form a common terminal of the fourth bridge circuit 108. The capacitor C4 is a polarized capacitor, in which the first terminal of the capacitor C4 is the positive plate (or anode) and the second terminal of the capacitor C4 is the negative plate (or cathode). The positive plate of the capacitor C4 is connected to the collector of the seventh switching transistor M4-Q1, and the negative plate of the capacitor C4 is connected to the emitter of the eighth switching transistor M4-Q2.

[0073] The first inductor L1 is connected between the common terminal of the first bridge circuit 102 and the common terminal of the third bridge circuit 106. The second inductor L2 is connected between the common terminal of the second bridge circuit 104 and the common terminal of the fourth bridge circuit 108.

[0074] It is noted that, the first power supply Bat is a power battery pack and the second power supply PV is a photovoltaic system. However, this is not a limitation of the present invention. In another embodiment, the first power supply Bat may be a photovoltaic system and the second power supply PV may be a power battery pack.

[0075] The following paragraphs describes the operation of the DCDC double-direction converting device 100. According to some embodiments, the DCDC double-direction converting device 100 is configured to have four operating modes, i.e. two Boost modes and two Buck modes. However, this is not a limitation of the present invention.

[0076] 1. The first Boost mode, i.e. the first power supply Bat (i.e. the power battery pack) discharges the second power supply PV (i.e. the photovoltaic system):

[0077] FIG. 2 is a diagram illustrating the first power supply Bat discharging the second power supply PV in accordance with some embodiments. FIG. 2 shows an equivalent model of storing energy in a Boost mode.

[0078] During the storing energy, the switching transistors M1-Q1, M3-Q2, M4-Q1, and M2-Q2 are turned on. As shown in FIG. 2, the current flows from the positive terminal (i.e. the first terminal of capacitor C1) of the first power supply Bat to the negative terminal (i.e. the second terminal of capacitor C2) of the first power supply Bat through the switching transistor M1-Q1, the first inductor L1, the switching transistor M3-Q2, the switching transistor

M4-Q1, the second inductor L2, and the switching transistor M2-Q2. During the process, the energy of the capacitor C1 and capacitor C2 is discharged, and the energy of the first inductor L1 and the second inductor L2 is charged or stored. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the discharging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also discharges.

[0079] FIG. 3 is a diagram illustrating the first power supply Bat discharging the second power supply PV in accordance with some embodiments. FIG. 3 shows an equivalent model of current flyback in a Boost mode.

[0080] During the flyback, the switching transistors M1-Q1, M3-Q2, M4-Q1, and M2-Q2 are turned off. As shown in FIG. 3, the current flows from the first terminal of the first inductor L1 to the second terminal of the first inductor L1 through the body diode of the switching transistor M3-Q1, the capacitor C3 (i.e. the positive terminal of the photovoltaic system), the capacitor C4 (i.e. the negative terminal of the photovoltaic system), the body diode of the switching transistor M4-Q2, the second inductor L2, the body diode of the switching transistor M2-Q1, and the body diode of the switching transistor M1-Q2. During the process, the energy of the first inductor L1 and the second inductor L2 is released or discharged, and the energy of the capacitor C3 and the capacitor C4 is charged. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the charging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also charges.

[0081] Accordingly, the equivalent models of FIG. 2 and FIG. 3 are capable of discharging current to the capacitor C3 and the capacitor C4 from the capacitor C1 and the capacitor C2. Accordingly, the first power supply Bat may discharge current to the second power supply PV during the first Boost mode, i.e. the voltage up-converting mode.

[0082] 2. The first Buck mode, i.e. the first power supply Bat (i.e. the power battery pack) discharges the second power supply PV (i.e. the photovoltaic system):

[0083] FIG. 4 is a diagram illustrating the first power supply Bat discharging the second power supply PV in accordance with some embodiments. FIG. 4 shows an equivalent model of storing energy in a Buck mode.

[0084] During the storing energy, the switching transistors M1-Q1 and M2-Q2 are turned on, and the switching transistors M3-Q2 and M4-Q1 are turned off. As shown in FIG. 4, the current flows from the positive terminal (i.e. the first terminal of capacitor C1) of the first power supply Bat to the negative terminal (i.e. the second terminal of capacitor C2) of the first power supply Bat through the switching transistor M1-Q1, the first inductor L1, the body diode of the switching transistor M3-Q1, the capacitor C3 (i.e. the positive terminal of the photovoltaic system), the capacitor C4 (i.e. the negative terminal of the photovoltaic system), the body diode of the switching transistor M4-Q2, the second inductor L2, and the switching transistor M2-Q2. During the process, the energy of the capacitor C1 and capacitor C2 is discharged, the energy of the capacitor C3 and capacitor C4 is charged, and the energy of the first inductor L1 and the second inductor L2 is charged or stored. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the discharging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also discharges. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the charging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also charges.

[0085] As shown in FIG. 3, the first power supply Bat may also discharge the second power supply PV based on the operation in the following paragraph, which is an equivalent model of current flyback in a Buck mode.

[0086] During the flyback, the switching transistors M1-Q1, M3-Q2, M4-Q1, and M2-Q2 are turned off. As shown in FIG. 3, the current flows from the first terminal of the first inductor L1 to the second terminal of the first inductor L1 through the body diode of the switching transistor M3-Q1, the capacitor C3 (i.e. the positive terminal of the photovoltaic system), the capacitor C4 (i.e. the negative terminal of the photovoltaic system), the body diode of the switching transistor M4-Q2, the second inductor L2, the body diode of the switching transistor M2-Q1, and the body diode of the switching transistor M1-Q2. During the process, the energy of the first inductor L1 and the second inductor L2 is released or discharged, and the energy of the capacitor C3 and the capacitor C4 is charged. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the charging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also charges.

[0087] Accordingly, the equivalent models of FIG. 3 and FIG. 4 are capable of discharging current to the capacitor C3 and the capacitor C4 from the capacitor C1 and the capacitor C2. Accordingly, the first power supply Bat may discharge current to the second power supply PV during the first Buck mode, i.e. the voltage down-converting mode.

[0088] 3. The second Boost mode, i.e. the second power supply PV (i.e. the photovoltaic system) discharges the first power supply Bat (i.e. the power battery pack):

[0089] FIG. 5 is a diagram illustrating the second power supply PV discharging the first power supply Bat in accordance with some embodiments. FIG. 2 shows an equivalent model of storing energy in a Boost mode.

[0090] During the storing energy, the switching transistors M3-Q1, M1-Q2, M2-Q1, and M4-Q2 are turned on. As shown in FIG. 5, the current flows from the capacitor C3 (i.e. the positive terminal of the second power supply PV) to the capacitor C4 (i.e. the negative terminal of the second power supply PV) through the switching transistor M3-Q1, the first inductor L1, the switching transistor M1-Q2, the switching transistor M2-Q1, the second inductor L2, and the switching transistor M4-Q2. During the process, the energy of the capacitor C3 and capacitor C4 is discharged, and the energy of the first inductor L1 and the second inductor L2 is charged or stored. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the discharging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also discharges.

[0091] FIG. 6 is a diagram illustrating the second power supply PV discharging the first power supply Bat in accordance with some embodiments. FIG. 6 shows an equivalent model of current flyback in a Boost mode.

[0092] During the flyback, the switching transistors M3-Q1, M1-Q2, M2-Q1, and M4-Q2 are turned off. As shown in FIG. 6, the current flows from the first terminal of the first inductor L1 to the second terminal of the first inductor L1 through the body diode of the switching transistor M1-Q1, the capacitor C1 (i.e. the positive terminal of the first power supply Bat), the capacitor C2 (i.e. the negative terminal of the first power supply Bat), the body diode of the switching transistor M2-Q2, the second inductor L2, the body diode of the switching transistor M4-Q1, and the body diode of the switching transistor M3-Q2. During the process, the energy of the first inductor L1 and the second inductor L2 is released or discharged, and the energy of the capacitor C1 and the capacitor C2 is charged. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the charging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also charges.

[0093] Accordingly, the equivalent models of FIG. 5 and FIG. 6 are capable of charging current to the capacitor C1 and the capacitor C2 from the capacitor C3 and the capacitor C4. Accordingly, the second power supply PV may charge current to the first power supply Bat during the second Boost mode, i.e. the voltage up-converting mode.

[0094] 4. The second Buck mode, i.e. the second power supply PV (i.e. the photovoltaic system) discharges the first power supply Bat (i.e. the power battery pack):

[0095] FIG. 7 is a diagram illustrating the second power supply PV charging the first power supply Bat in accordance with some embodiments. FIG. 7 shows an equivalent model of storing energy in a Buck mode.

[0096] During the storing energy, the switching transistors M3-Q1 and M4-Q2 are turned on, and the switching transistors M1-Q2 and M2-Q1 are turned off. As shown in FIG. 7, the current flows from the positive terminal (i.e. capacitor C3) of the second power supply PV to the negative terminal (i.e. the capacitor C4) of the second power supply PV through the switching transistor M3-O1, the first inductor L1, the body diode of the switching transistor M1-Q1, the capacitor C1 (i.e. the positive terminal of the first power supply Bat), the capacitor C2 (i.e. the negative terminal of the first power supply Bat), the body diode of the switching transistor M2-Q2, the second inductor L2, and the switching transistor M4-Q2. During the process, the energy of the capacitor C3 and capacitor C4 is discharged, the energy of the capacitor C1 and capacitor C1 is charged, and the energy of the first inductor L1 and the second inductor L2 is charged or stored. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the charging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also discharges. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the discharging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also discharges.

[0097] As shown in FIG. 6, the second power supply PV may also charge the first power supply Bat based on the operation in the following paragraph, which is an equivalent model of current flyback in a Buck mode.

[0098] During the flyback, the switching transistors M3-Q1, M1-Q2, M2-Q1, and M4-Q2 are turned off. As shown in FIG. 6, the current flows from the first terminal of the first inductor L1 to the second terminal of the first inductor L1 through the body diode of the switching transistor M1-Q1, the capacitor C1 (i.e. the positive terminal of the first power supply Bat), the capacitor C2 (i.e. the negative terminal of the first power supply Bat), the body diode of the switching transistor M2-Q2, the second inductor L2, the body diode of the switching transistor M4-Q1, and the body diode of the switching transistor M3-Q2. During the process, the energy of the first inductor L1 and the second inductor L2 is released or discharged, and the energy of the capacitor C1 and the capacitor C2 is charged. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the charging of the capacitor C1 and the capacitor C2 means that the energy of the second power supply PV also charges.

[0099] Accordingly, the equivalent models of FIG. 6 and FIG. 7 are capable of discharging current to the capacitor C3 and the capacitor C4 from the capacitor C1 and the capacitor C2. Accordingly, the second power supply PV may discharge current to the first power supply Ba during the second Buck mode, i.e. the voltage down-converting mode.

[0100] The DCDC double-direction converting device 100 is controlled to turn on or turn off the first bridge circuit 102, the second bridge circuit 104, the third bridge circuit 104, and the fourth bridge circuit 108 to provide an up-convert or down-convert voltage level. In comparison to the related art, the DCDC double-direction converting device 100 is capable of selectively switching between the Buck mode and the Boost mode. The DCDC double-direction converting device 100 is also configured to have double direction depending on the charging or discharging of the first power supply Bat (or the second power supply PV). Accordingly, the DCDC double-direction converting device 100 may be applied in different application fields, such as the high voltage field.

[0101] FIG. 8 is a diagram illustrating a DCDC double-direction converting device 800 in accordance with some embodiments. In comparison to the DCDC double-direction converting device 100 of FIG. 1, the DCDC double-direction converting device 800 comprises more capacitors in the bridge circuits.

[0102] In FIG. 8, the first capacitor C1 of the DCDC double-direction converting device 100 is replaced with two capacitors C11, C12 connected in parallel. The second capacitor C2 of the DCDC double-direction converting device 100 is replaced with two capacitors C21, C22 connected in parallel. The third capacitor C3 of the DCDC double-direction converting device 100 is replaced with two capacitors C31, C32 connected in parallel. The fourth capacitor C4 of the DCDC double-direction converting device 100 is replaced with two capacitors C41, C42 connected in parallel. The operation and benefit of the DCDC double-direction converting device 800 is similar to the DCDC double-direction converting device 100, thus the detailed description is omitted here for brevity.

[0103] Moreover, according to some embodiments, the capacitance of the capacitor C1 is equal to the capacitance of the capacitor C3 is equal to the capacitance of the capacitor C3.

[0104] According to some embodiments, the DCDC double-direction converting device 100 may be operated in the following four modes:

[0105] 1. When the voltage level of the first power supply Bat is lower than the voltage level of the second power supply PV, the first power supply Bat discharges current to the second power supply PV.

[0106] 2. When the voltage level of the first power supply Bat is higher than the voltage level of the second power supply PV, the first power supply Bat discharges current to the second power supply PV.

[0107] 3. When the voltage level of the first power supply Bat is lower than the voltage level of the second power supply PV, the second power supply PV discharges current to the first power supply Bat.

[0108] 4. When the voltage level of the first power supply Bat is higher than the voltage level of the second power supply PV, the second power supply PV discharges current to the first power supply Bat.

[0109] The above mentioned four controlling methods of the DCDC double-direction converting device 100 is described in detail in the following paragraphs and diagrams.

**[0110]** 1. When the voltage level of the first power supply Bat is lower than the voltage level of the second power supply PV, the first power supply Bat discharges current to the second power supply PV, and the controlling method is as followed:

[0111] When the first power supply Bat is arranged to discharge current to the second power supply PV, and when the voltage level of the first power supply Bat is lower than the voltage level of the second power supply PV, the DCDC double-direction converting device 100 is controlled to operate in a switching cycle having a first time interval T1 and a second time interval T2, wherein the first time interval T1 and the second time interval T2 are two consecutive time intervals, and the first time interval T1 is followed by the second time interval T2. During T2, detecting if the current of the first inductor L1 and/or the current of the second inductor L2 crosses the zero current, if yes, controlling the DCDC double-direction converting device 100 to operate in the time intervals T3, T4, or the time intervals T7, T8 after time interval T2. FIG. 9 is a timing diagram illustrating the signals in the time intervals T1~T2 in accordance with some embodiments.

[0112] During the time interval T1, the switching transistors M1-Q1, M3-Q2, M2-Q2, and M4-Q1 are turned on, the switching transistors M1-Q2, M3-Q1, M2-Q1, and M4-Q2 are turned off. The current flow during the time interval T1 has been shown in FIG. 2, and the detailed description is omitted here for brevity. When the current of the first inductor L1 flows to the bridge circuit 106 from the bridge circuit 102, the current is defined as "positive" current. When the current of the second inductor L2 flows to the bridge circuit 104 from the bridge circuit 108, the current is defined as "negative" current. During the time interval T1, the current of the first inductor L1 and the currents gradually increase. Accordingly, the first inductor L1 and the second inductor L2 store energy until the time interval T2.

[0113] During the time interval T2, the switching transistors M3-Q2 and M4-Q1 are turned off, the switching transistors M1-Q1 and M1-Q2 are not turned on at the same time, the switching transistors M2-Q1 and M2-Q2 are not turned on at the same time. During the time interval T2, the currents may have two directions.

[0114] The first current direction is happened when the switching transistors M1-Q1 and M2-Q2 are turned on, and the switching transistors M1-Q2 and M2-Q1 are turned off. In this process, the energy of the inductor L1 is released. The current flow of this process has been shown in FIG. 4, and the detailed description is omitted here for brevity.

[0115] The second current direction is happened when the switching transistors M1-Q1, M1-Q2, M2-Q1, and M2-Q2 are turned off. In this process, the energy of the inductor L1 is released. The current flow of this process has been shown in FIG. 3, and the detailed description is omitted here for brevity.

[0116] In the above mentioned first current direction and the second current direction, the energy of the inductors L1 and L2 is released, the currents are positive current, and the currents gradually decrease. Meanwhile, the capacitors C3 and C4 are charged by currents. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the charging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also charges.

[0117] During the time interval T2, when the switching transistors M1-Q1 and M2-Q2 are turned off, the current flows through the body diode of the switching transistors M2-Q1 and the body diode of the switching transistors M1-Q2. During the time interval T1, the current flows through the switching transistors M1-Q1 and M2-Q2. Accordingly, during the time intervals T1 and T2, the currents flow through different switching transistors respectively. Therefore, the DCDC double-direction converting device 100 may have better heat dissipation effect. According to some embodiments, the second current direction may be the better option in the time interval T2.

[0118] Moreover, during the time intervals T1 and T2, the first power supply Bat is arranged to boost the voltage level of the second power supply PV. The switching transistor M3-Q2 and M4-Q1 may be regarded as the high frequency transistors of the Boost circuit. When the switching transistor M3-Q2 and M4-Q1 have greater duty cycle (i.e. when T1 is greater than T2), the current of the first inductor L1 and the current of the second inductor L2 are continuous, and the currents are positive current. As shown in FIG. 9, when the duty cycle decreases to reach a specific value, the inductor current reaches the zero when the cycle is finished, and the next cycle begins at the same time. Then, the inductors may store energy again, and the inductor currents increase, i.e. the threshold current mode. When the duty cycle is further reduced, i.e. the inductor currents reach zero in the time interval T2, and the cycle is not finished yet, the DCDC double-direction converting device 100 may enter the time intervals T3 and T4 or T7 and T8. FIG. 10 is a timing diagram illustrating the signals in the time intervals T1, T2, T3, and T4 in accordance with some embodiments.

[0119] During the time interval T3, the switching transistors M3-Q1 and M4-Q2 are turned on, the switching transistors M1-Q2, M2-Q1, M3-Q2, M4-Q1 are turned off. The

current flow of this process has been shown in FIG. 7, and the detailed description is omitted here for brevity.

[0120] In this process, the capacitors C3 and C4 are discharged, and the capacitors C1 and C2 are charged. The energy of inductors L1 and L2 is stored, and the currents increase. However, the inductor currents are negative current. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the charging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also charges. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the discharging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also discharges.

[0121] During the time interval T4, the switching transistors M3-Q1, M1-Q2, M2-Q1, and M4-Q2 are turned off. The energy of the inductor L1 is released. The current flow of this process has been shown in FIG. 6, and the detailed description is omitted here for brevity. In this process, the energy of the inductors L1 and L2 is released, the currents are negative current, and the currents gradually decrease. Meanwhile, the capacitors C1 and C2 are charged by currents. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the charging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also charges.

[0122] According to the time intervals T1~T4, during the switching cycles, the currents of the inductors are continuous. In one cycle, if the first power supply Bat is arranged to discharge current to the second power supply PV, then the area formed by the positive current of the first inductor L1 and/or the positive current of the second inductor L2 may be designed to be greater than the area formed by the negative current of the first inductor L1 and/or the negative current of the second inductor L2. The different value of the two areas may be the discharging energy from the first power supply Bat to the second power supply PV.

[0123] Furthermore, when the voltage level of the first power supply Bat is lower than the voltage level of the second power supply PV, the DCDC double-direction converting device 100 is arranged to operate in the time interval T3 before the currents of the inductors L1 and/or L2 cross the zero current. Specifically, during the time interval T2, the switching transistors M3-Q1 and M4-Q2 are turned on, and the switching transistors M1-Q2 and M2-Q1 are turned off. Meanwhile, the current of the inductor L1 or L2 is positive current, and the current flows through the body diode of the switching transistor M3-Q1 or the body diode of the switching transistor M4-Q2 to form a loop. As shown in FIG. 3 and FIG. 4, the direction of the current is similar to the current direction in the time interval T2. When the current of the inductor L1 or L2 reaches zero, the next time interval T3 may start immediately to avoid the switching discontinuity when the time interval T2 proceeds to the next time interval

[0124] Furthermore, during the time interval T4, the switching transistors M1-Q1, M3-Q2, M2-Q2, and M4-Q1 are turned on. Meanwhile, the current of the inductor L1 or L2 is negative current, the direction of the current is similar

to the current direction in the time interval T4. As shown in FIG. 6, when the current of the inductor L1 or L2 reaches zero, the time interval T1 in the next cycle may start immediately to avoid the switching discontinuity when the time interval T4 proceeds to the next time interval T1.

[0125] In addition, during the time intervals T2 and T3, the switching transistors M1-Q1 and M2-Q2 are turned off. According to the time intervals T1~T4, the switching transistors M1-Q2 and M2-Q1 are turned off in the whole switching cycle; the switching transistors M1-Q1, M3-Q2, M2-Q2, and M4-Q1 are controlled by the first control signal; the switching transistors M3-Q1 and M4-Q2 are controlled by the second control signal. To reduce the circuit complexity and to extend the lifetime of transistors, the second control signal may be the voltage inverted from the first control signal.

[0126] In another embodiment, during the time intervals T2 and T3, the switching transistors M1-Q1 and M2-Q2 are turned on. According to the time intervals T1~T4, the switching transistors M1-Q1 and M2-Q2 are turned on in the whole switching cycle, the switching transistors M1-Q2 and M2-Q1 are turned off in the whole switching cycle; the switching transistors M3-Q2 and M4-Q1 are controlled by the first control signal; the switching transistors M3-Q1 and M4-Q2 are controlled by the second control signal. To reduce the circuit complexity and to extend the lifetime of transistors, the second control signal may be the voltage inverted from the first control signal.

[0127] After the time intervals T1, T2, the DCDC double-direction converting device 100 may be operated in the time intervals T7, T8. FIG. 11 is a timing diagram illustrating the signals in the time intervals T1, T2, T7, and T8 in accordance with some embodiments.

[0128] During the time interval T7, the switching transistors M3-Q1, M1-Q2, M2-Q1, and M4-Q2 are turned on, the switching transistors M1-Q1 and M4-Q1 are turned off. The current flow of this process has been shown in FIG. 5, and the detailed description is omitted here for brevity. In this process, the capacitors C3 and C4 are discharged, and the inductors L1 and L2 are energy stored, and the currents increase. However, the inductor currents are negative current. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the discharging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also discharges.

[0129] During the time interval T8, the switching transistors M1-Q2 and M2-Q1 are turned off, the switching transistors M3-Q1 and M3-Q2 are not turned on at the same time, the switching transistors M4-Q1 and M4-Q2 are not turned on at the same time. During the time interval T8, the currents may have two directions.

[0130] The first current direction is happened when the switching transistors M3-Q1 and M4-Q2 are turned on, and the switching transistors M3-Q2 and M4-Q1 are turned off as shown in FIG. 7. In this process, the energy of the inductor L1 is released. The current flow of this process has been shown in FIG. 7, and the detailed description is omitted here for brevity. In this process, the capacitors C3 and C4 are discharged, the capacitors C1 and C2 are charged, the inductors L1 and L2 are energy stored, and the currents increase. However, the inductor currents are negative current. As the capacitor C1 and the capacitor C2 are serially

connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the charging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also charges. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the discharging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also discharges.

[0131] The second current direction is happened when the switching transistors M3-Q1 and M4-Q2 are turned off. In this process, the energy of the inductor L1 is released. The current flow of this process has been shown in FIG. 6, and the detailed description is omitted here for brevity. In this process, the inductors L1 and L2 are energy released, the capacitors C1 and C2 are charged. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the charging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also charges.

[0132] In the above mentioned first current direction and the second current direction, the energy of the inductors L1 and L2 is released, the currents are negative current, and the currents gradually decrease.

[0133] During the time interval T8, the switching transistors M3-Q1 and M4-Q2 are turned off such that the current flows through the body diodes of the switching transistors M3-Q2 and M4-Q1. During the time interval T7, the current flows through the switching transistors M3-Q1 and M4-Q2. When the time intervals T7 and T8 are combined, the currents flow through different switching transistors respectively. Therefore, the DCDC double-direction converting device 100 may have better heat dissipation effect. According to some embodiments, the second current direction may be the better option in the time interval T8.

[0134] According to the time intervals T1, T2, T7, T8, during the switching cycles, the currents of the inductors are continuous.

[0135] Furthermore, the DCDC double-direction converting device 100 is arranged to operate in the time interval T7 before the currents of the inductors L1 and/or L2 cross the zero current. Specifically, during the time interval T2, the switching transistors M1-Q2, M3-Q1, M2-Q1, and M4-Q2 are turned on, and the switching transistors M1-Q1 and M2-Q2 are turned off. Meanwhile, when the current of the inductor L1 or L2 is positive current, the direction of the current is similar to the current direction in the time interval T2 as shown in FIG. 3 and FIG. 4. When the current of the inductor L1 or L2 reaches zero, the time interval T7 may start immediately to avoid the switching discontinuity when the time interval T2 proceeds to the next time interval T7. [0136] Furthermore, during the time interval T8, the switching transistors M1-Q1, M3-Q2, M2-Q2, and M4-Q1 are turned on, and the switching transistors M3-Q1 and M4-Q2 are turned off. Meanwhile, when the current of the inductor L1 or L2 is negative current, the direction of the current is similar to the current direction in the time interval T8 as shown in FIG. 11 or FIG. 12. FIG. 11 is a timing diagram illustrating the signals in the time intervals T1, T2, T7, and T8 in accordance with some embodiments. FIG. 12 is a timing diagram illustrating the signals in the time intervals T5, T6, T7, and T8 in accordance with some embodiments. When the current of the inductor L1 or L2 reaches zero, the time interval T1 in the next cycle may start immediately to avoid the switching discontinuity when the time interval T8 proceeds to the next time interval T1.

[0137] According to the time intervals T1, T2, T3, and T4, the switching transistors M1-Q1, M3-Q2, M2-Q2, and M4-Q1 are controlled by the first control signal; the switching transistors M1-Q2, M3-Q1, M2-Q1, and M4-Q2 are controlled by the second control signal. To reduce the circuit complexity and to extend the lifetime of transistors, the second control signal may be the voltage inverted from the first control signal.

[0138] 2. When the voltage level of the first power supply Bat is higher than the voltage level of the second power supply PV, the first power supply Bat is arranged to discharge current to the second power supply PV according to the following method:

[0139] When the first power supply Bat is arranged to discharge current to the second power supply PV, and when the voltage level of the first power supply Bat is higher than the voltage level of the second power supply PV, the DCDC double-direction converting device 100 is controlled to operate in a switching cycle having the time interval T5 and the time interval T6, wherein the time interval T5 and the time interval T6 are two consecutive time intervals, and the time interval T5 is followed by the time interval T6. During T6, detecting if the current of the first inductor L1 and/or the current of the second inductor L2 crosses the zero current, if yes, controlling the DCDC double-direction converting device 100 to operate in the time intervals T7, T8, or the time intervals T3. T4 after time interval T6. After the time intervals T5, T6, the DCDC double-direction converting device 100 may be controlled to operate in the time intervals T7, T8 as shown in FIG. 12.

[0140] During the time interval T5, the switching transistors M1-Q1 and M2-Q2 are turned on, and the switching transistors M1-Q2, M3-Q2, M4-Q1, and M2-Q1 are turned off. The current flow during the time interval T5 has been shown in FIG. 4, and the detailed description is omitted here for brevity. In this process, the capacitors C1, C2, C3, and C4 are charged, and the inductors L1 and L2 are energy stored. As the capacitor C1 and the capacitor C2 are serially connected between the positive terminal of the first power supply Bat and the negative terminal of the first power supply Bat, the discharging of the capacitor C1 and the capacitor C2 means that the energy of the first power supply Bat also discharges. As the capacitor C3 and the capacitor C4 are serially connected between the positive terminal of the second power supply PV and the negative terminal of the second power supply PV, the charging of the capacitor C3 and the capacitor C4 means that the energy of the second power supply PV also discharges. In this process, the currents of the inductors L1 and L2 are positive current, the currents gradually increase, and the energy of the inductors L1 and L2 is stored until the time interval T6.

[0141] During the time interval T6, the switching transistors M1-Q1, M3-Q2, M4-Q1, and M2-Q2 are turned off. The energy of the inductors L1 is released. The current flow during the time interval T6 has been shown in FIG. 3, and the detailed description is omitted here for brevity. In this process, the inductors L1 and L2 are energy released, the currents of the inductors L1 and L2 are positive current, and the currents gradually decrease.

[0142] During the time intervals T5, T6, the first power supply Bat is arranged to generate the reduced voltage level to the second power supply PV. The switching transistor M1-Q1 and M2-Q2 may be regarded as the high frequency transistors of the Buck circuit. When the switching transistor M1-Q1 and M2-Q2 have greater duty cycle (i.e. when T5 is greater than T6), the current of the first inductor L1 and the current of the second inductor L2 are continuous, and the currents are positive current. When the duty cycle decreases to reach a specific value, the inductor current reaches the zero when the cycle finishes, and the next cycle begins at the same time. Then, the inductors may store energy again, and the inductor currents increase, i.e. the threshold current mode. When the duty cycle is further reduced, i.e. the inductor currents reach zero in the time interval T6, and the cycle is not finished yet, the DCDC double-direction converting device 100 may enter the time intervals T7 and T8 as shown in FIG. 12.

[0143] The time intervals T7 and T8 has been described, and the detailed description is omitted here for brevity.

[0144] According to the time intervals T5~T8, during the switching cycles, the currents of the inductors are continuous.

[0145] Furthermore, when the voltage level of the first power supply Bat is higher than the voltage level of the second power supply PV, the DCDC double-direction converting device 100 is arranged to operate in the time interval T7 before the currents of the inductors L1 and/or L2 cross the zero current. Specifically, during the time interval T6, the switching transistors M1-Q2, M3-Q1, M2-Q1, and M4-Q2 are turned on. Meanwhile, the current of the inductor L1 or L2 is positive current, the direction of the current is similar to the current direction in the time interval T6 as shown in FIG. 3. When the current of the inductor L1 or L2 reaches zero, the time interval T7 may start immediately to avoid the switching discontinuity when the time interval T6 proceeds to the next time interval T7.

[0146] Furthermore, during the time interval T8, the switching transistors M1-Q1 and M2-Q2 are turned on, and the switching transistors M3-Q2 and M4-Q1 are turned off. Meanwhile, the current of the inductor L1 or L2 is negative current, the direction of the current is similar to the current direction in the time interval T8. As shown in FIG. 6 or FIG. 7, when the current of the inductor L1 or L2 reaches zero, the time interval T5 in the next cycle may start immediately to avoid the switching discontinuity when the time interval T8 proceeds to the next time interval T5.