US 20130320526A1

## (19) United States(12) Patent Application Publication

#### Wakisaka et al.

#### (54) SEMICONDUCTOR CONSTRUCT AND MANUFACTURING METHOD THEREOF AS WELL AS SEMICONDUCTOR DEVICE AND MANUFACTURING METHOD THEREOF

- (71) Applicants: Shinji Wakisaka, Ome-shi (JP); Takeshi Wakabayashi, Sayama-shi (JP)

- (72) Inventors: Shinji Wakisaka, Ome-shi (JP); Takeshi Wakabayashi, Sayama-shi (JP)

- (21) Appl. No.: **13/960,485**

- (22) Filed: Aug. 6, 2013

#### **Related U.S. Application Data**

(63) Continuation of application No. 12/828,492, filed on Jul. 1, 2010, now Pat. No. 8,525,335.

#### (30) Foreign Application Priority Data

| Jul. 3, 2009 | (JP) | <br>2009-158618 |

|--------------|------|-----------------|

| Jul. 3, 2009 | (JP) | <br>2009-158622 |

| Jul. 3, 2009 | (JP) | <br>2009-158629 |

#### (10) Pub. No.: US 2013/0320526 A1 (43) Pub. Date: Dec. 5, 2013

#### **Publication Classification**

#### (57) **ABSTRACT**

A semiconductor construct includes a semiconductor substrate and connection pads provided on the semiconductor substrate. Some of the connection pads are connected to a common wiring and at least one of the remaining of the connection pads are connected to a wiring. The construct also includes a first columnar electrode provided to be connected to the common wiring and a second columnar electrode provided to be connected to a connection pad portion of the wiring.

.

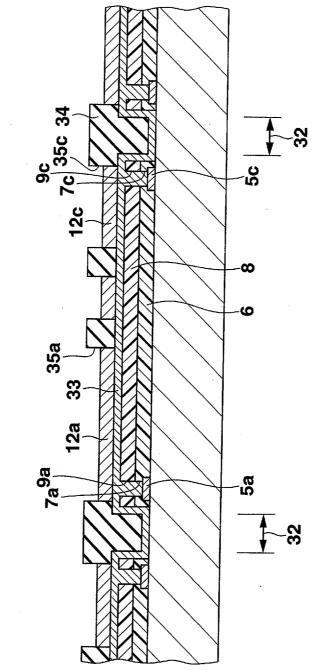

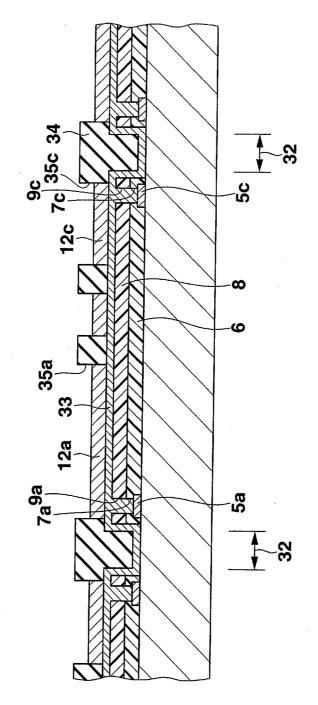

**FIG.25**

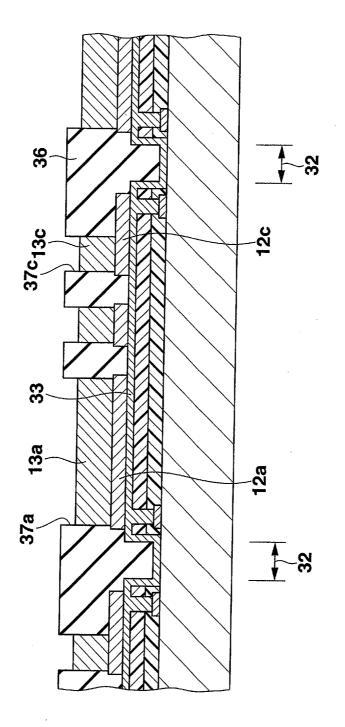

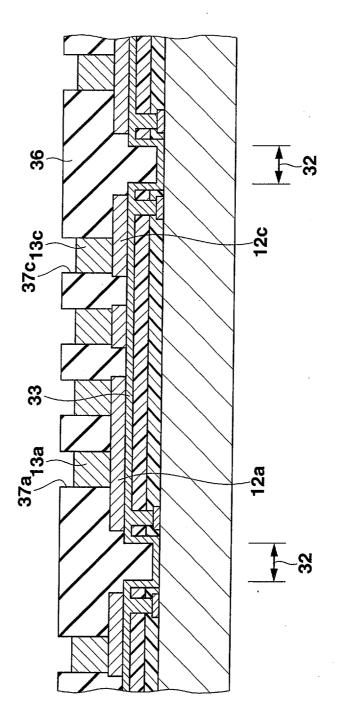

FIG.26

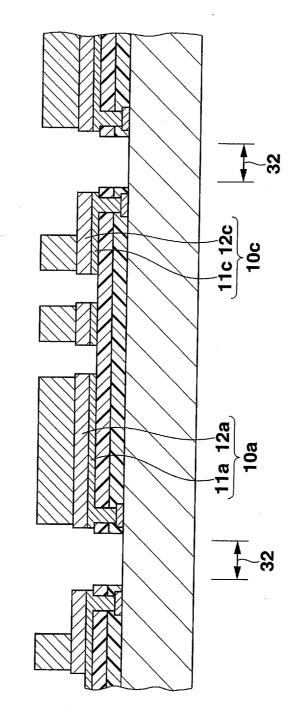

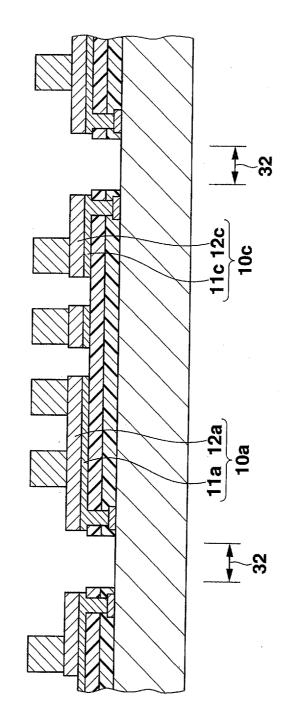

**FIG.32**

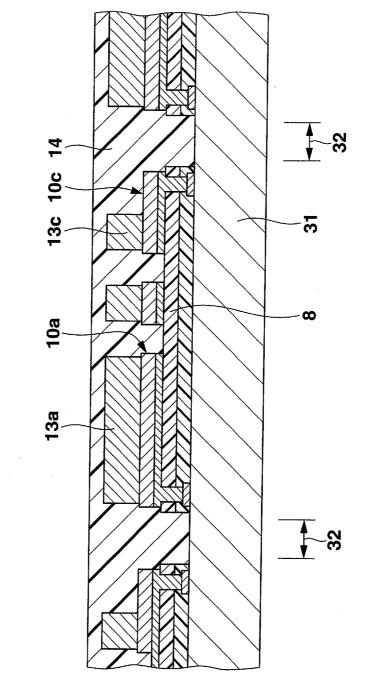

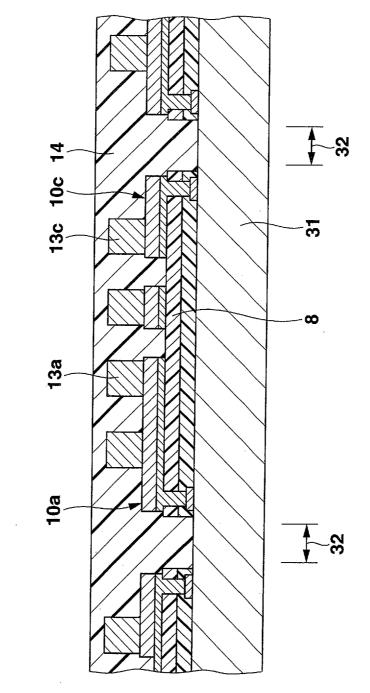

FIG.42

#### SEMICONDUCTOR CONSTRUCT AND MANUFACTURING METHOD THEREOF AS WELL AS SEMICONDUCTOR DEVICE AND MANUFACTURING METHOD THEREOF

#### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This is a Continuation of U.S. application Ser. No. 12/828,492, filed Jul. 1, 2010, which is based upon and claims the benefit of priority from prior Japanese Patent Applications No. 2009-158618, filed Jul. 3, 2009; No. 2009-158622, filed Jul. 3, 2009; and No. 2009-158629, filed Jul. 3, 2009, the entire contents of all of which are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] This invention relates to a semiconductor construct.

[0004] 2. Description of the Related Art

**[0005]** Conventional semiconductor devices include a semiconductor device having a semiconductor construct called a chip size package (CSP) that is fixedly attached to a base plate greater in size than the semiconductor construct (e.g., see Jpn. Pat. Appln. KOKAI Publication No. 2006-12885). In this case, the semiconductor construct called the CSP has a structure that includes a semiconductor substrate, wirings provided on the semiconductor substrate, columnar electrodes respectively provided on connection pads of the wirings, and a sealing film provided around the columnar electrodes.

**[0006]** Furthermore, the lower surface of the semiconductor substrate of the semiconductor construct is fixedly attached to the base plate. An insulating layer is provided on the base plate around the semiconductor construct. An upper insulating film is provided over the semiconductor construct and the insulating layer. Upper wirings are provided on the upper insulating film so as to be connected to the columnar electrodes of the semiconductor construct. The upper wirings, except for its connection pads, are covered with an overcoat film. Solder balls are provided on the connection pads of the upper wirings (e.g., see Jpn. Pat. Appln. KOKAI Publication No. 2006-12885).

[0007] In the meantime, the columnar electrodes are respectively provided on the connection pads of the wirings in the semiconductor construct of the above-mentioned conventional semiconductor device. Thus, the relation between the wirings and the columnar electrodes is one-to-one. This is a disadvantage when the line width of the wirings is reduced to about 20  $\mu$ m or less due to an increase in the number of the wirings and columnar electrodes. In this case, when an excessively high current originating from, for example, a power supply voltage, runs through the wirings, the wirings are burned off and broken.

#### BRIEF SUMMARY OF THE INVENTION

**[0008]** According to an aspect of embodiments, a semiconductor construct includes a semiconductor substrate, connection pads provided on the semiconductor substrate, a common wiring provided in a region including a predetermined number of connection pads among the connection pads so as to be connected to the predetermined number of connection pads, a wiring provided to be connected to the remaining of the connection pads, a first columnar electrode provided to be connected to the common wiring, and a second columnar electrode provided to be connected to a connection pad portion of the wiring.

**[0009]** According to another aspect of embodiments, a method of manufacturing a semiconductor construct includes forming a common wiring and a wiring on a semiconductor substrate provided with connection pads, the common wiring being formed in a region including common voltage connection pads among the connection pads so as to be connected to the common voltage connected to the remaining of the connection pads, and forming a first columnar electrode on the common wiring, and forming a second columnar electrode on a connection pad portion of the wiring.

**[0010]** Advantages of the invention will be set forth in the description which follows, and in part will be obvious from the description, or may be learned by practice of the invention. The advantages of the invention may be realized and obtained by means of the instrumentalities and combinations particularly pointed out hereinafter.

#### BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

**[0011]** The accompanying drawings, which are incorporated in and constitute a part of the specification, illustrate embodiments of the invention, and together with the general description given above and the detailed description of the embodiments given below, serve to explain the principles of the invention.

**[0012]** The present invention will be fully understood by the following detailed description and the accompanying drawings, which only serve to explain the invention and do not limit the scope of the invention. In the drawings:

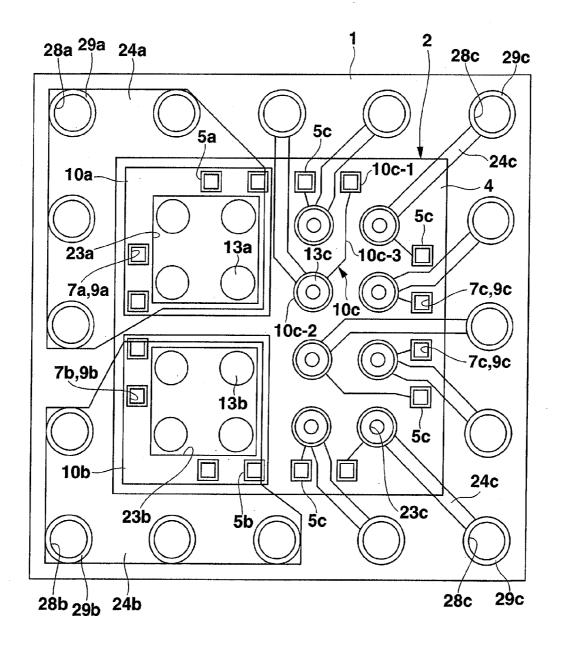

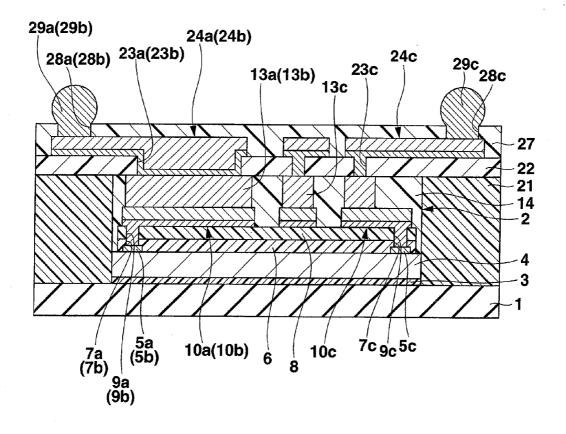

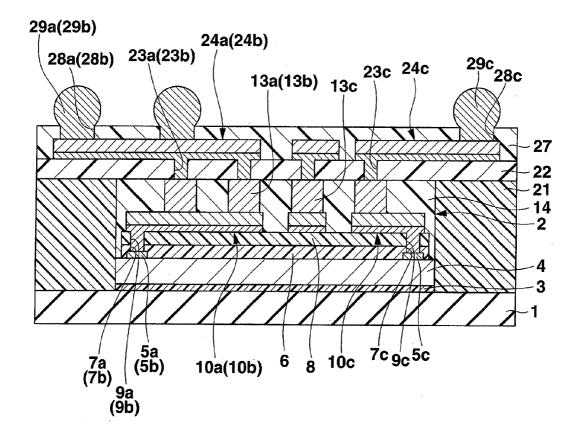

**[0013]** FIG. **1** is a transmitted plan view of a semiconductor device according to a first embodiment of the invention;

**[0014]** FIG. **2** is a sectional view of a proper part of the semiconductor device shown in FIG. **1**;

**[0015]** FIG. **3** is a sectional view of an initially prepared assembly in one example of a method of manufacturing the semiconductor device shown in FIG. **1** and FIG. **2**;

[0016] FIG. 4 is a sectional view of a step following FIG. 3;

- [0017] FIG. 5 is a sectional view of a step following FIG. 4;

- [0018] FIG. 6 is a sectional view of a step following FIG. 5;

- [0019] FIG. 7 is a sectional view of a step following FIG. 6;

- [0020] FIG. 8 is a sectional view of a step following FIG. 7;

- [0021] FIG. 9 is a sectional view of a step following FIG. 8;

- **[0022]** FIG. **10** is a sectional view of a step following FIG. **9**.

- [0023] FIG. 11 is a sectional view of a step following FIG. 10:

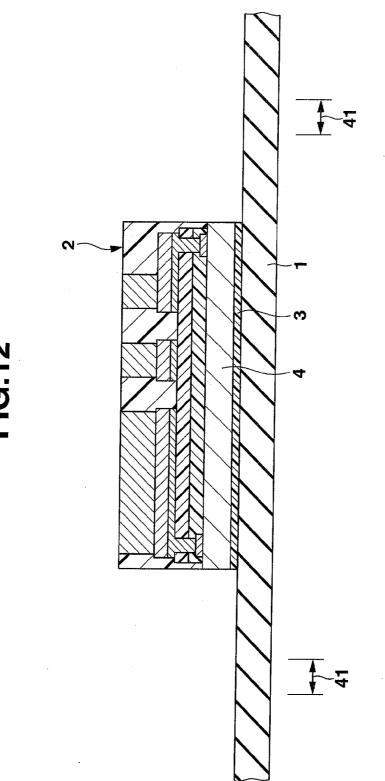

[0024] FIG. 12 is a sectional view of a step following FIG.

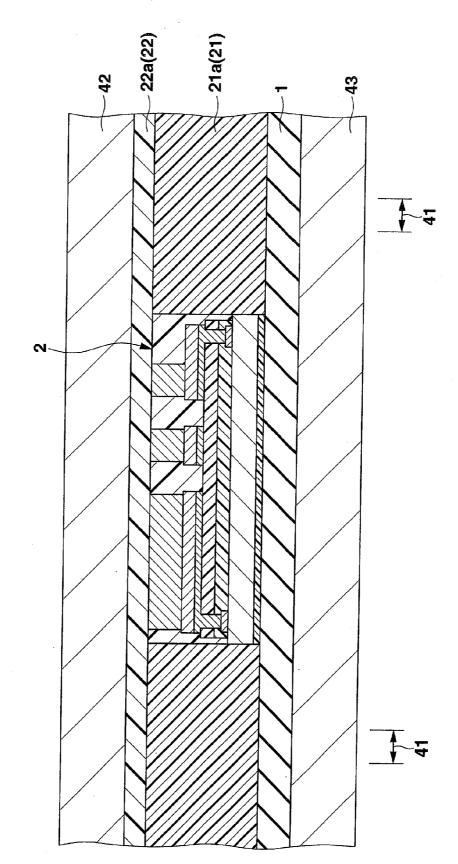

- **11**; **[0025]** FIG. **13** is a sectional view of a step following FIG.

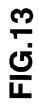

- 12;[0026] FIG. 14 is a sectional view of a step following FIG.13;

[0027] FIG. 15 is a sectional view of a step following FIG. 14;

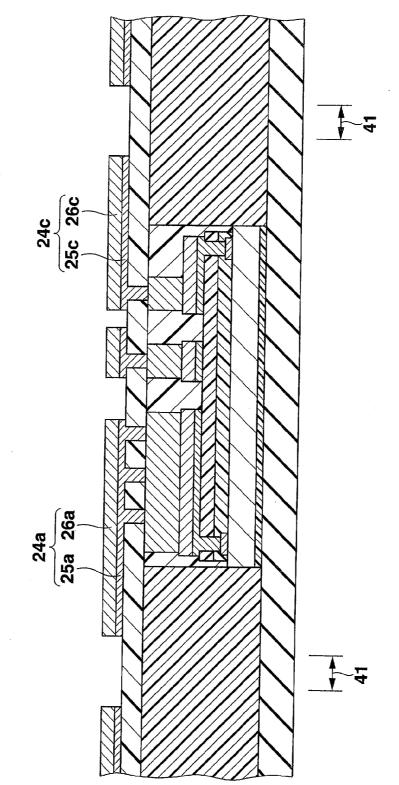

[0028] FIG. 16 is a sectional view of a step following FIG. 15;

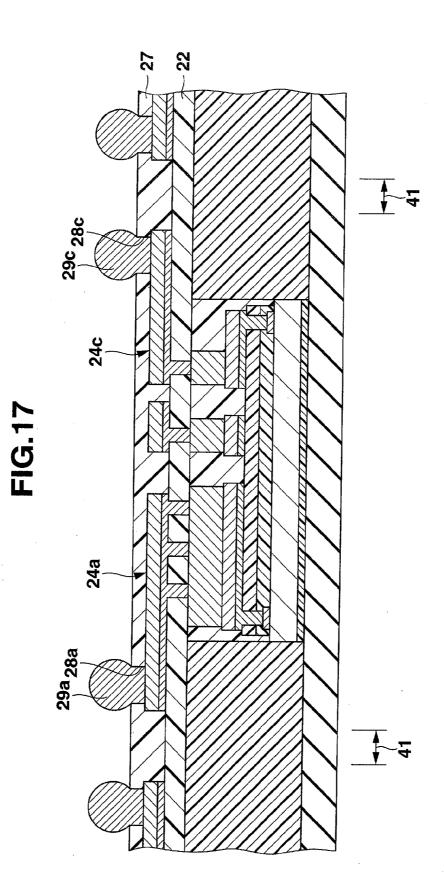

[0029] FIG. 17 is a sectional view of a step following FIG.

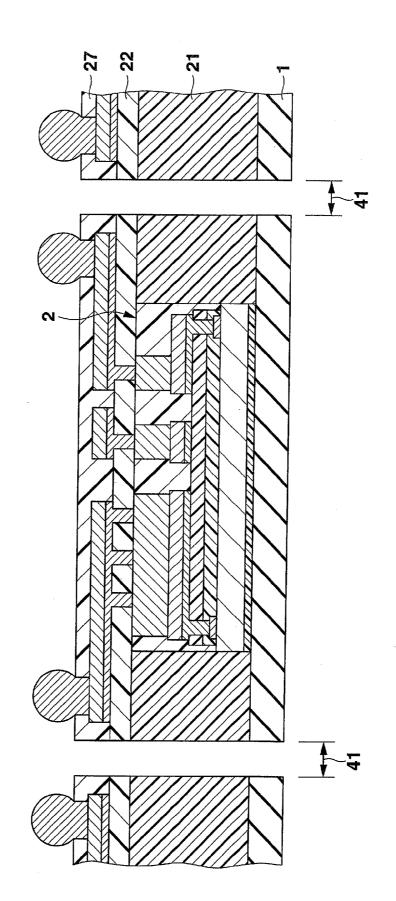

[0030] FIG. 18 is a sectional view of a step following FIG. 17;

16;

**[0032]** FIG. **20** is a sectional view of a proper part of the semiconductor device shown in FIG. **19**;

**[0033]** FIG. **21** is a sectional view of an initially prepared assembly in one example of a method of manufacturing the semiconductor device shown in FIG. **19** and FIG. **20**;

[0034] FIG. 22 is a sectional view of a step following FIG.21;

[0035] FIG. 23 is a sectional view of a step following FIG. 22;

[0036] FIG. 24 is a sectional view of a step following FIG. 23;

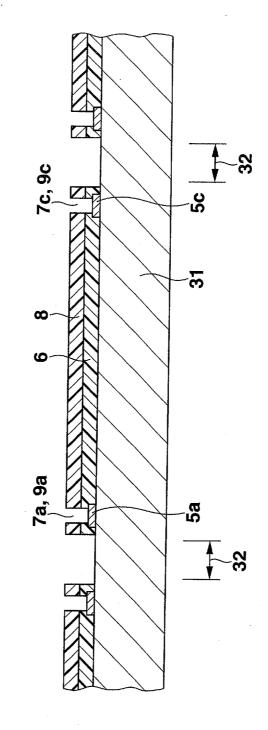

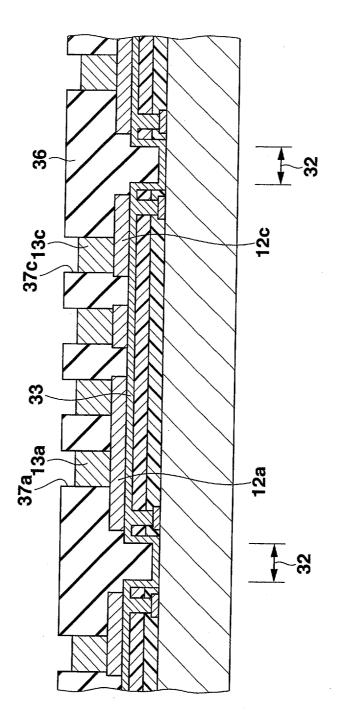

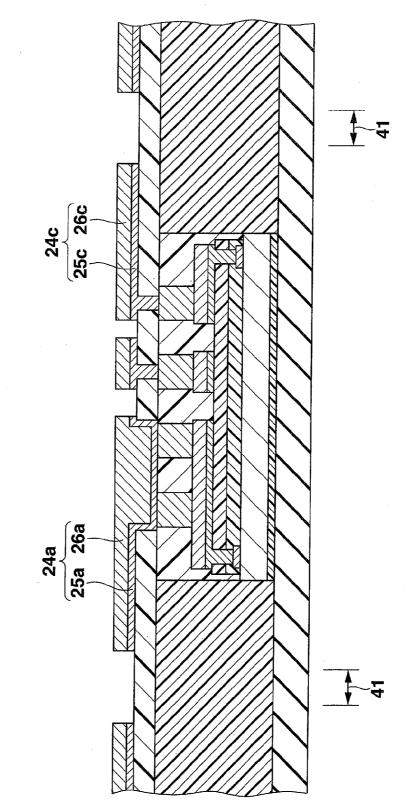

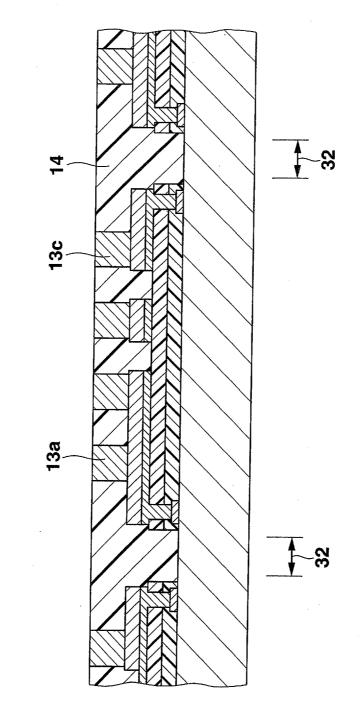

[0037] FIG. 25 is a sectional view of a step following FIG. 24;

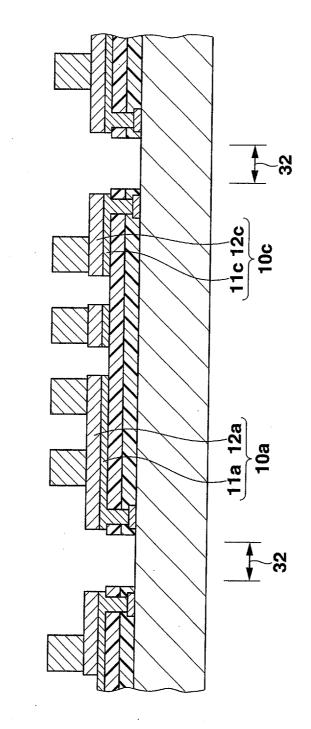

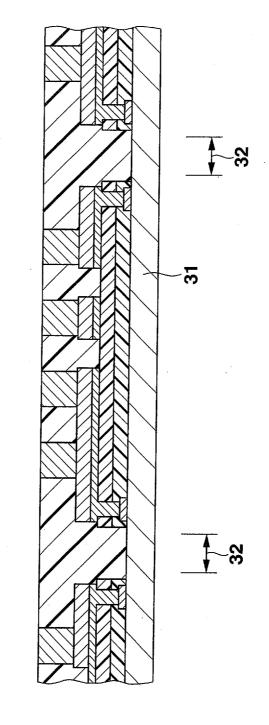

[0038] FIG. 26 is a sectional view of a step following [0039] FIG. 25;

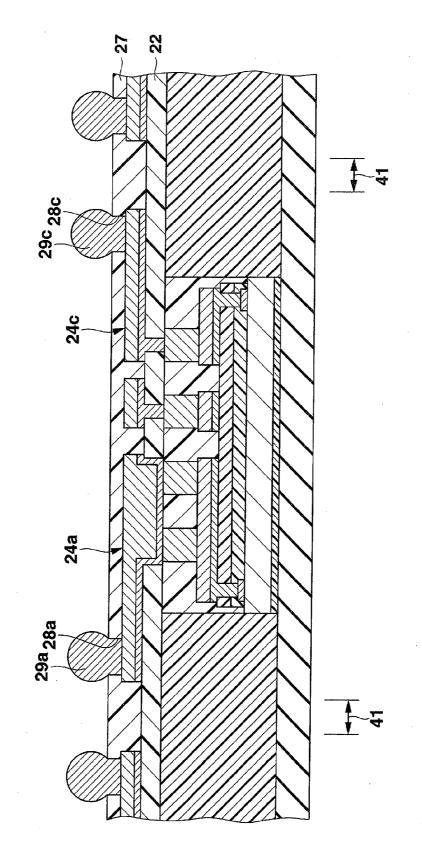

[0040] FIG. 27 is a sectional view of a step following FIG. 26;

[0041] FIG. 28 is a sectional view of a step following FIG. 27;

[0042] FIG. 29 is a sectional view of a step following FIG.

28;[0043] FIG. 30 is a sectional view of a step following FIG.

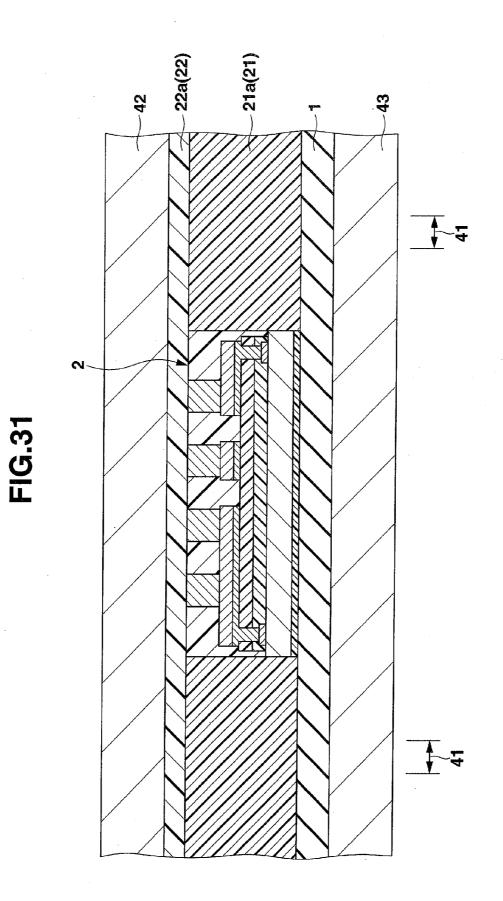

29;[0044] FIG. 31 is a sectional view of a step following FIG.

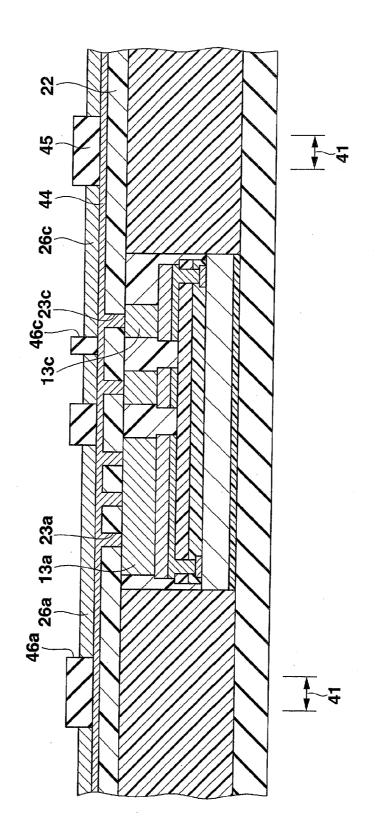

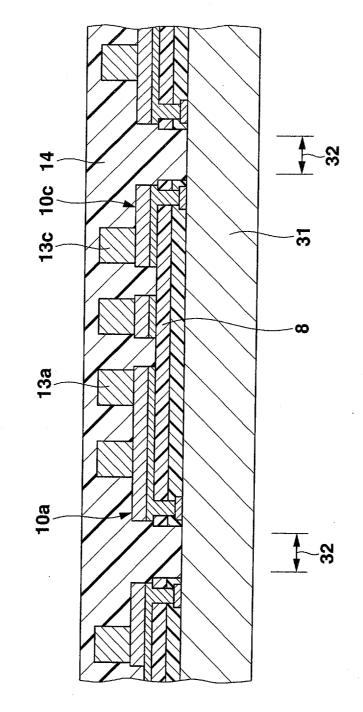

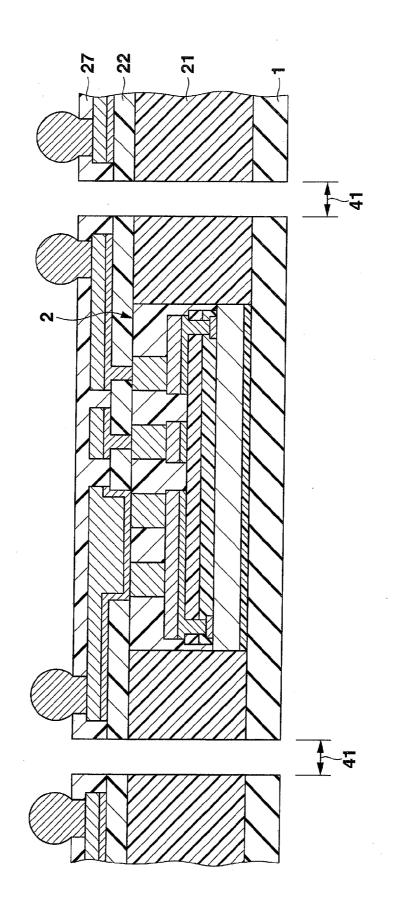

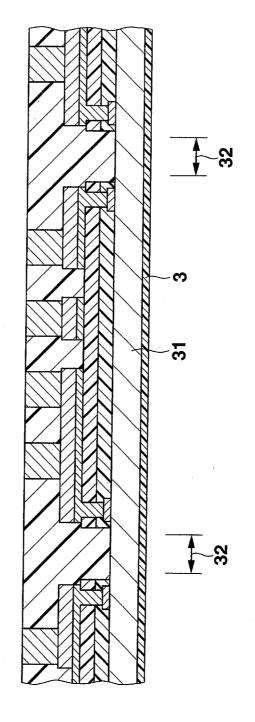

30;[0045] FIG. 32 is a sectional view of a step following FIG.

31;[0046] FIG. 33 is a sectional view of a step following FIG.32:

[0047] FIG. 34 is a sectional view of a step following FIG. 33:

[0048] FIG. 35 is a sectional view of a step following FIG. 34;

[0049] FIG. 36 is a sectional view of a step following FIG. 35;

[0050] FIG. 37 is a sectional view of a step following FIG. 36;

[0051] FIG. 38 is a transmitted plan view of a semiconductor device according to a third embodiment of the invention; [0052] FIG. 39 is a sectional view of a proper part of the semiconductor device shown in FIG. 38;

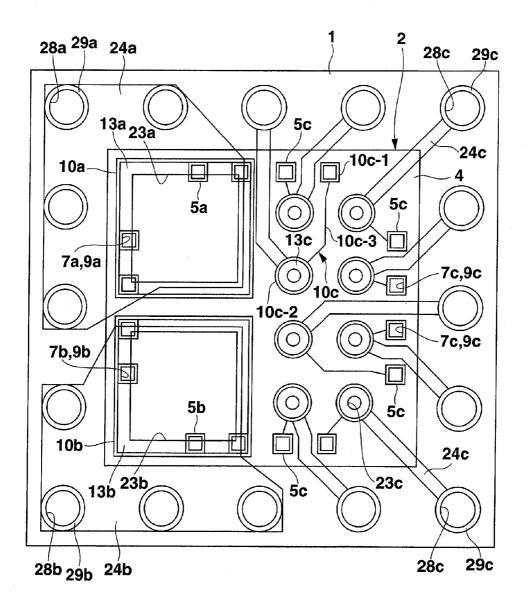

[0053] FIG. 40 is a transmitted plan view of a semiconductor device according to a fourth embodiment of the invention; [0054] FIG. 41 is a sectional view of a proper part of the semiconductor device shown in FIG. 40;

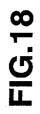

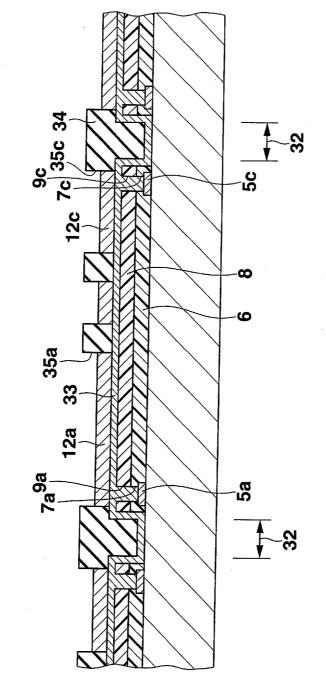

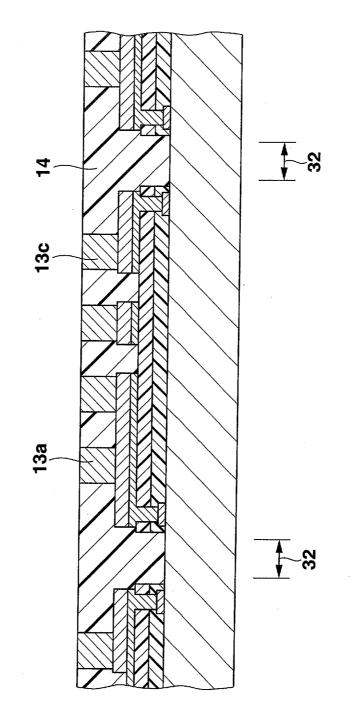

**[0055]** FIG. **42** is a sectional view of an initially prepared assembly in one example of a method of manufacturing the semiconductor device shown in FIG. **40** and FIG. **41**;

[0056] FIG. 43 is a sectional view of a step following FIG. 42;

[0057] FIG. 44 is a sectional view of a step following FIG. 43;

**[0058]** FIG. **45** is a sectional view of a step following FIG. **44**;

**[0059]** FIG. **46** is a sectional view of a step following FIG. **45**;

[0060] FIG. 47 is a sectional view of a step following FIG. 46;

[0061] FIG. 48 is a sectional view of a step following FIG. 47;

**[0062]** FIG. **49** is a sectional view of a step following FIG. **48**:

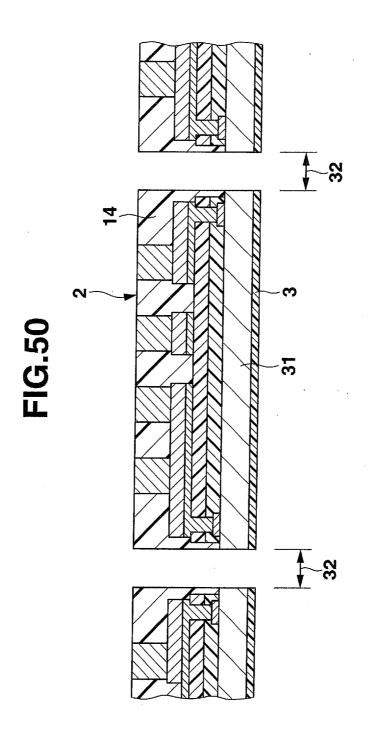

[0063] FIG. 50 is a sectional view of a step following FIG.

**49**; **[0064]** FIG. **51** is a sectional view of a step following FIG.

- **50**; **[0065]** FIG. **52** is a sectional view of a step following FIG.

- 51; [0066] FIG. 53 is a sectional view of a step following FIG.

52; [0067] FIG. 54 is a sectional view of a step following FIG.

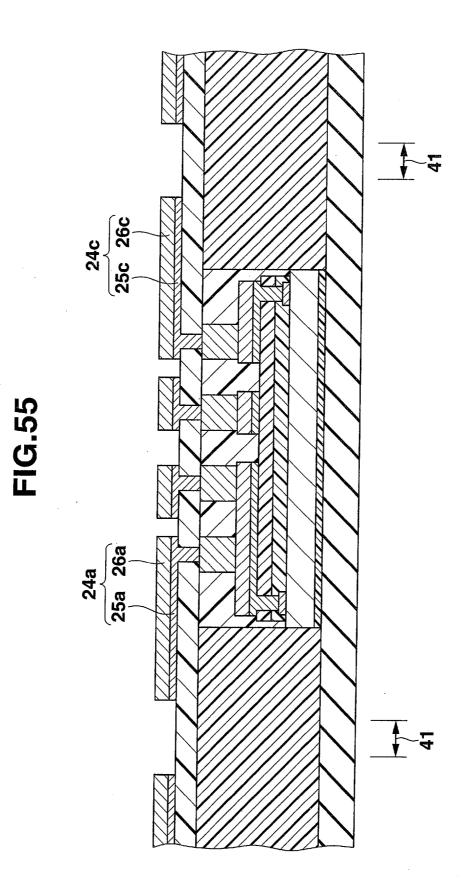

53;[0068] FIG. 55 is a sectional view of a step following FIG.54;

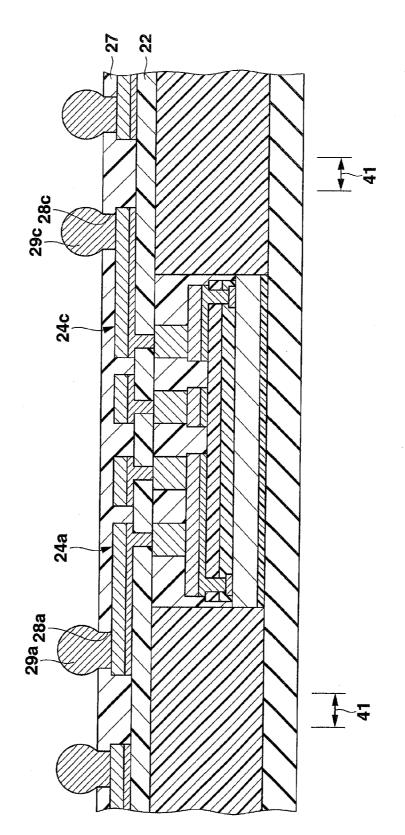

[0069] FIG. 56 is a sectional view of a step following FIG. 55:

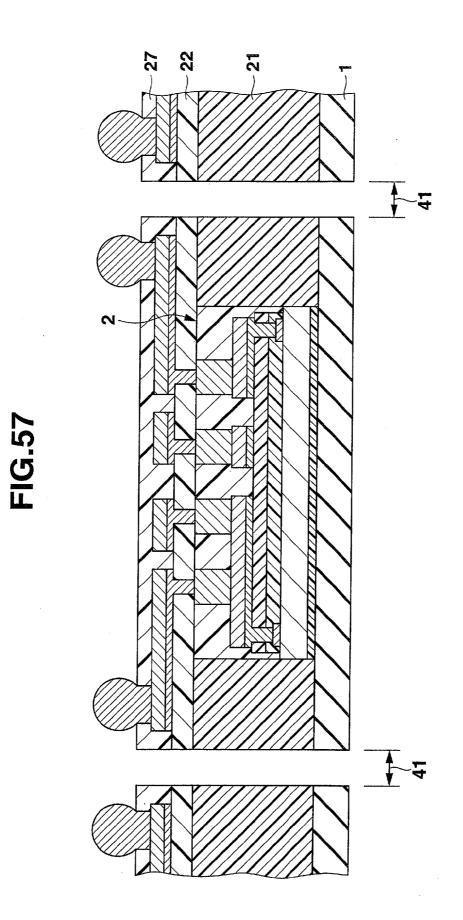

[0070] FIG. 57 is a sectional view of a step following FIG. 56;

[0071] FIG. 58 is a transmitted plan view of a semiconductor device according to a fifth embodiment of the invention; [0072] FIG. 59 is a sectional view of a proper part of the semiconductor device shown in FIG. 58;

**[0073]** FIG. **60** is a transmitted plan view of a semiconductor device according to a sixth embodiment of the invention; and

**[0074]** FIG. **61** is a sectional view of a semiconductor device according to a seventh embodiment of the invention.

#### DETAILED DESCRIPTION OF THE INVENTION

#### First Embodiment

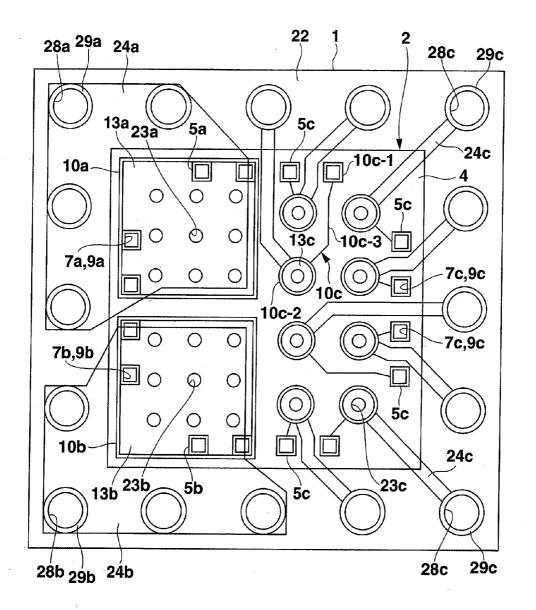

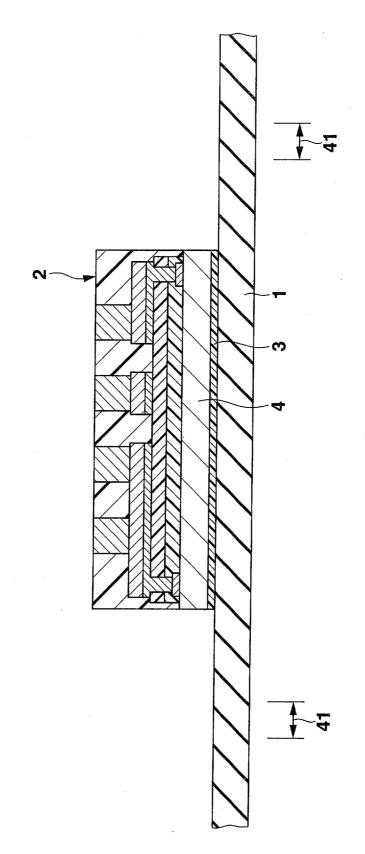

**[0075]** FIG. 1 shows a transmitted plan view of a semiconductor device according to a first embodiment of the invention. FIG. 2 shows a sectional view of a proper part of the semiconductor device shown in FIG. 1. This semiconductor device includes a base plate 1. The base plate 1 has a square planar shape, and made of, for example, an epoxy resin containing glass fabric as a base material. The lower surface of a semiconductor construct 2 is bonded to the center of the upper surface of the base plate 1 through a bonding layer 3 made of a die bond material. The semiconductor construct 2 has a square planar shape, and is slightly smaller in size than the base plate 1.

[0076] The semiconductor construct 2, which is generally called a CSP, includes a silicon substrate (semiconductor substrate) 4. The lower surface of the silicon substrate 4 is bonded to the center of the upper surface of the base plate 1 through the bonding layer 3. Elements (not shown) such as a transistor, diode, resistor, and condenser that constitute an integrated circuit having a predetermined function are formed on the upper surface of the silicon substrate 4. Connection pads 5a, 5b, 5c are provided on the peripheral portion of the upper surface of the silicon substrate 4. The connection pads 5a, 5b, 5c are made of, for example, an aluminum-based metal, and connected to the elements of the integrated circuit. [0077] Here, by way of example, the four connection pads indicated by the sign 5a and arranged on the upper left part of the silicon substrate 4 in FIG. 1 are for a common power supply voltage. The four connection pads indicated by the sign 5b and arranged on the lower left part of the silicon substrate 4 are for a common ground voltage. The four connection pads indicated by the sign 5c and arranged on the upper right part of the silicon substrate 4 and the four connection pads indicated by the sign 5c and arranged on the

lower right part of the silicon substrate 4 are for a normal voltage. Here, in FIG. 2, the ground voltage connection pads 5b and associated parts are substantially similar to the power supply voltage connection pads 5a and associated parts, and are therefore indicated by signs in parentheses.

**[0078]** A passivation film (insulating film) **6** made of, for example, silicon oxide is provided on the upper surface of the silicon substrate **4** except for the peripheral portion of the silicon substrate **4** and the centers of the connection pads 5a, 5b, 5c. The centers of the connection pads 5a, 5b, 5c are exposed through openings 7a, 7b, 7c provided in the passivation film **6**. A protective film (insulating film) **8** made of, for example, a polyimide resin is provided on the upper surface of the passivation film **6**. Openings 9a, 9b, 9c are provided in parts of the protective film **8** that correspond to the openings 7a, 7b, 7c of the passivation film **6**.

[0079] Wirings 10a, 10b, 10c are provided on the upper surface of the protective film 8. The wirings 10a, 10b, 10c have a double-layer structure composed of foundation metal layers 11a, 11b, 11c and upper metal layers 12a, 12b, 12c. The foundation metal layers 11a, 11b, 11c and upper metal layers 12a, 12b, 12c. The foundation metal layers 11a, 11b, 11c are made of, for example, copper and provided on the upper surface of the protective film 8. The upper metal layers 12a, 12b, 12c are made of copper and provided on the upper surfaces of the foundation metal layers 11.

**[0080]** In this case, as shown in FIG. **1**, the wiring indicated by the sign 10a (common wiring) is solidly disposed on the upper left part of the silicon substrate **4** in a region that has a square planar shape and includes the four power supply voltage connection pads **5***a*. The wiring 10a is connected to all of the four power supply voltage connection pads **5***a* via the openings **7***a*, **9***a* of the passivation film **6** and the protective film **8**.

**[0081]** The wiring indicated by the sign 10b (common wiring) is solidly disposed on the lower left part of the silicon substrate 4 in a region that has a square planar shape and includes the four ground voltage connection pads 5b. The wiring 10b is connected to all of the four ground voltage connection pads 5b via the openings 7b, 9b of the passivation film 6 and the protective film 8.

[0082] The wirings indicated by the sign 10c are disposed in the right region of the silicon substrate 4. Each wiring 10chas a connection portion 10c-1 connected to the normal voltage connection pad 5c via the openings 7c, 9c of the passivation film 6 and the protective film 8, a connection pad portion 10c-2 having a circular planar shape, and an extension line 10c-3 extending between the connection portion 10c-1 and the connection pad portion 10c-2.

[0083] Similarly to the wiring 10a, a columnar electrode (common columnar electrode, first columnar electrode) 13a is solidly provided in the region of the upper surface, except for its peripheral portion, of the wiring indicated by the sign 10a and having a square planar shape. The columnar electrode 13a is made of copper and has a square planar shape. Similarly to the wiring 10b, a columnar electrode (common columnar electrode, first columnar electrode) 13b is solidly provided in the region of the upper surface, except for the peripheral portion, of the wiring indicated by the sign 10b and having a square planar shape. The columnar electrode 13b is made of copper and has a square planar shape. Columnar electrodes (second columnar electrodes) 13c are provided on the upper surface of the connection pad portions 10c-2 of the wirings indicated by the sign 10c. The columnar electrodes 13c are made of copper and have a circular planar shape.

Here, as shown in FIG. 1, eight columnar electrodes 13c having a circular planar shape are arranged in matrix form.

[0084] A sealing film 14 made of, for example, an epoxy resin is provided around the columnar electrodes 13a, 13b, 13c on the upper surface of the protective film 8 including the wirings 10a, 10b, 10c. The columnar electrodes 13a, 13b, 13c are provided so that the upper surfaces thereof are flush with or several µm lower than the upper surface of the sealing film 14. The explanation of the structure of the semiconductor construct 2 is completed now.

**[0085]** An insulating layer **21** in a square frame shape is provided on the upper surface of the base plate **1** around the semiconductor construct **2**. For example, the insulating layer **21** is made of a thermosetting resin such as an epoxy resin in which a reinforcer of an inorganic material such as silica fuller is dispersed. Alternatively, the insulating layer **21** is only made of a thermosetting resin such as an epoxy resin.

[0086] An upper insulating film 22 is provided on the upper surfaces of the semiconductor construct 2 and the insulating layer 21. The upper insulating film 22 is made of, for example, a base glass fabric impregnated with a thermosetting resin such as an epoxy resin. Alternatively, the upper insulating film 22 is only made of a thermosetting resin such as an epoxy resin. Openings (first openings) 23a, 23b having a circular planar shape are provided in parts of the upper insulating film 22 that correspond to predetermined nine points on the surface of the columnar electrodes 13a, 13b of the semiconductor construct 2 having a square planar shape. Openings (second openings) 23c having a circular planar shape are provided in parts of the upper insulating film 22 that correspond to the centers of the upper surfaces of the columnar electrodes 13c of the semiconductor construct 2 having a circular planar shape.

[0087] In this case, the planar shape of the openings 23a, 23b is the same as the planar shape of the opening 23c. Moreover, both the number of the openings 23a and the number of the openings 23b are nine, and are greater than the number (four) of the power supply voltage and ground voltage connection pads 5a, 5b of the semiconductor construct 2. [0088] Upper wirings 24a, 24b, 24c are provided on the upper surface of the upper insulating film 22. The upper wirings 24a, 24b, 24c have a double-layer structure composed of foundation metal layers 25a, 25b, 25c and upper metal layers 26a, 26b, 26c. The foundation metal layers 25a, 25b, 25c are made of, for example, copper and provided on the upper surface of the upper insulating film 22. The upper metal layers 26a, 26b, 26c are made of copper and provided on the upper surfaces of the foundation metal layers 25a, 25b, 25c

**[0089]** In this case, as shown in FIG. 1, the upper wiring indicated by the sign 24a (common upper wiring, first upper wiring) is solidly disposed on the upper left part of the upper insulating film 22 in a region of the upper insulating film 22 including nine openings 23a. The upper wiring 24a is connected, via all of the nine openings 23a of the upper insulating film 22, to the predetermined nine points on the surface of the columnar electrode 13a of the semiconductor construct 2 having a square planar shape.

[0090] The upper wiring indicated by the sign 24b (common upper wiring, first upper wiring) is solidly disposed on the lower left part of the upper insulating film 22 in a region of the upper insulating film 22 including nine openings 23b. The upper wiring 24b is connected, via all of the nine openings 23b of the upper insulating film 22, to the predetermined

nine points on the surface of the ground voltage columnar electrode 13b of the semiconductor construct 2 having a square planar shape.

[0091] Similarly to the wiring of the semiconductor construct 2 indicated by the sign 10c, each upper wiring indicated by the sign 24c (second upper wiring) has a connection portion, a connection pad portion, and an extension line extending therebetween. The upper wiring 24c is connected, via the opening 23c of the upper insulating film 22, to the center of the upper surface of the columnar electrode 13c of the semiconductor construct 2 having a circular planar shape.

[0092] An overcoat film 27 made of, for example, a solder resist is provided on the upper surface of the upper insulating film 22 including the upper wirings 24a, 24b, 24c. Openings 28a, 28b are provided in parts of the overcoat film 27 that correspond to predetermined four points in the peripheral portions of the upper wirings 24a, 24b. An opening 28c is provided in a part of the overcoat film 27 that corresponds to the connection pad portion of the upper wiring 24c.

[0093] Solder balls 29a, 29b, 29c are provided in and above the openings 28a, 28b, 28c of the overcoat film 27 so that these solder balls are connected to the upper wirings 24a, 24b, 24c. In this case, as shown in FIG. 1, the solder balls 29a, 29b, 29c are only disposed around the semiconductor construct 2. Moreover, both the number of the solder balls 29a and the number of the solder balls 29b are four, and are the same as the number (four) of the power supply voltage and ground voltage connection pads 5a, 5b of the semiconductor construct 2. [0094] As described above, in this semiconductor device, the power supply voltage wiring 10a and the ground voltage

wiring 10b of the semiconductor construct 2 are solidly formed in a square planar shape, and each connected to all of the four connection pads 5a, 5b. This allows the power supply voltage wiring 10a and the ground voltage wiring 10b not to be burned off even if an excessively high current runs through these wirings.

[0095] Furthermore, since the power supply voltage columnar electrode 13a and the ground voltage columnar electrode 13b of the semiconductor construct 2 are solidly formed, the columnar electrodes 13a, 13b can be reduced in resistance, and current capacity can thus be improved. Moreover, since the power supply voltage upper wiring 24a and the ground voltage upper wiring 24b are solidly formed, the upper wirings 24a, 24b can be reduced in resistance, and current capacity can thus be improved.

[0096] Still further, since the number (nine) of the openings 23a, 23b provided in the upper insulating film 22 on the power supply voltage and ground voltage columnar electrodes 13a, 13b of the semiconductor construct 2 is greater than the number (four) of the power supply voltage and ground voltage connection pads 5a, 5b, the connection portions of the openings 23a, 23b can be reduced in resistance as a whole, and current capacity can thus be further improved.

[0097] Here, the sizes of the parts of this semiconductor device are mentioned. The size of the base plate 1 is  $3\times3$  mm. The size of the semiconductor construct 2 is  $2\times2$  mm. The line width of the extension line 10*c*-3 of the wiring 10*c* of the semiconductor construct 2 is 20 µm. The diameter of the columnar electrode 13*c* of the semiconductor construct 2 having a circular planar shape is 0.2 mm. The pitch of the columnar electrodes 13*c* is 0.4 mm. The diameter of the opening 23*a*, 23*b*, 23*c* of the upper insulating film 22 is 100 µm. The diameter of the solder balls 29*a*, 29*b*, 29*c* is 0.3 mm. The pitch of the solder balls 29*a*, 29*b*, 29*c* is 0.65 mm.

**[0098]** Now, one example of a method of manufacturing this semiconductor device is described. First, one example of a method of manufacturing the semiconductor construct 2 is described. In this case, the ground voltage connection pad 5b and associated parts are substantially similar to the power supply voltage connection pads 5a and associated parts, and are therefore not described.

[0099] First, as shown in FIG. 3, an assembly is prepared. In this assembly, connection pads 5a, 5c, a passivation film 6 and a protective film 8 are formed on the upper surface of a silicon substrate in a wafer state (hereinafter referred to as a semiconductor wafer 31). Further, the centers of the connection pads 5a, 5c are exposed through openings 7a, 7c of the passivation film 6 and through openings 9a, 9c of the protective film 8.

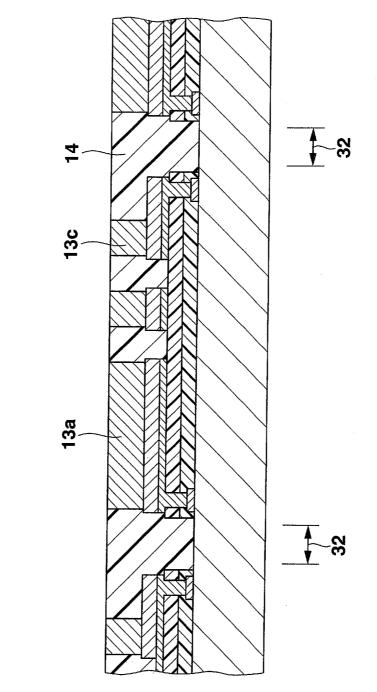

**[0100]** In this case, the thickness of the semiconductor wafer **31** is greater than the thickness of a silicon substrate **4** shown in FIG. **2**. In FIG. **3**, zones indicated by the sign **32** are dicing streets. The parts of the passivation film **6** and the protective film **8** corresponding to the dicing street **32** and both its sides are removed.

**[0101]** Then, as shown in FIG. 4, a foundation metal layer **33** is formed on the entire upper surface of the protective film **8** including the upper surfaces of the connection pads 5a, 5c exposed through openings 7a, 7c of the passivation film **6** and through openings 9a, 9c of the protective film **8**. In this case, the foundation metal layer **33** may only be a copper layer formed by electroless plating, may only be a copper layer formed by sputtering, or may be a copper layer formed by sputtering on a thin film layer of, for example, titanium formed by sputtering.

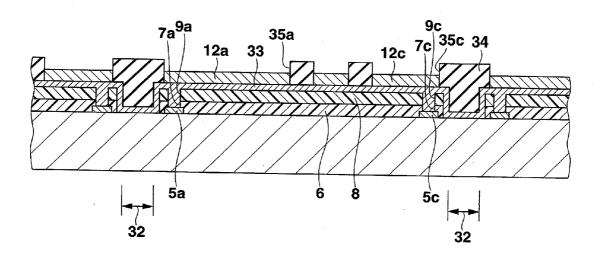

[0102] Then, a plating resist film 34 made of a positive liquid resist is patterned and formed on the upper surface of the foundation metal layer 33. In this case, openings 35a, 35c are formed in parts of the plating resist film 34 corresponding to regions where upper metal layers 12a, 12c are to be formed. Further, electrolytic plating with copper is carried out using the foundation metal layer 33 as a plating current path, thereby forming the upper metal layers 12a, 12c on the upper surface of the foundation metal layer 33 within the openings 35a, 35c in the plating resist film 34. Subsequently, the plating resist film 34 is released.

**[0103]** Then, as shown in FIG. **5**, a plating resist film **36** made of a negative dry film resist is patterned and formed on the upper surface of the foundation metal layer **33**. In this case, openings **37***a*, **37***c* are formed in parts of the plating resist film **36** corresponding to parts of the upper metal layer **12***a* except for its peripheral portion (a region where a columnar electrode **13***a* is to be formed) and corresponding to the connection pad portion of the upper metal layer **12***c* (a region where a columnar electrode **13***c* is to be formed).

**[0104]** Then, electrolytic plating with copper is carried out using the foundation metal layer **33** as a plating current path. As a result, the columnar electrode 13a is formed on the upper surface of the upper metal layer 12a within the openings 37a in the plating resist film **36**. Moreover, the columnar electrode 13c is formed on the upper surface of the connection pad portion of the upper metal layer 12c within the openings 37c in the plating resist film **36**. Subsequently, the plating resist film **36** is released.

[0105] Then, using the upper metal layers 12a, 12c as masks, the foundation metal layer 33 located in parts other than parts under the upper metal layers 12a, 12c is etched and removed. Thus, as shown in FIG. 6, foundation metal layers

11*a*, 11*c* remain under the upper metal layers 12a, 12c alone. In this state, wirings 10a, 10c having a double-layer structure are formed by the upper metal layers 12a, 12c and the foundation metal layers 11a, 11c remaining thereunder.

[0106] Then, as shown in FIG. 7, a sealing film 14 made of, for example, an epoxy resin is formed by, for example, a spin coat method on the upper surface of the semiconductor wafer 31 corresponding to the dicing street 32 and both its sides and on the upper surface of the protective film 8 including the wirings 10a, 10c and the columnar electrodes 13a, 13c so that the thickness of this sealing film 14 is slightly greater than the height of the columnar electrodes 13a, 13c are covered with the sealing film 14.

[0107] Then, the upper side of the sealing film 14 is properly ground to expose the upper surfaces of the columnar electrodes 13a, 13c as shown in FIG. 8, and the upper surface of the sealing film 14 including the exposed upper surfaces of the columnar electrodes 13a, 13c is planarized. Further, as shown in FIG. 9, the lower side of the semiconductor wafer 31 is properly ground to reduce the thickness of the semiconductor wafer 31.

**[0108]** Then, as shown in FIG. **10**, a bonding layer **3** is bonded to the lower surface of the semiconductor wafer **31**. The bonding layer **3** is made of a die bond material such as an epoxy resin, and is fixedly attached in a semi-cured state by heating and pressurization to the lower surface of the semiconductor wafer **31**. Further, as shown in FIG. **11**, the sealing film **14**, the semiconductor wafer **31** and the bonding layer **3** are cut along the dicing streets **32**, thereby obtaining semiconductor constructs **2** having the bonding layers **3** on the lower surface.

**[0109]** Now, one example of how to manufacture the semiconductor device shown in FIG. 2 using the semiconductor construct 2 shown in FIG. 11 is described. In this case as well, parts associated with the ground voltage connection pad 5bare substantially similar to parts associated with the power supply voltage connection pads 5a, and are therefore not described.

**[0110]** First, as shown in FIG. **12**, a base plate **1** is prepared. This base plate **1** is made of, for example, an epoxy resin containing glass fabric as a base material, and has an area that allows the completed semiconductor devices shown in FIG. **2** to be formed thereon. For example, the base plate **1** has, but not exclusively, a square planar shape. In addition, zones indicated by the sign **41** in FIG. **12** correspond to cut lines for division.

**[0111]** Then, the bonding layers **3** fixedly attached to the lower surfaces of the silicon substrates **4** of the semiconductor constructs **2** are bonded to semiconductor construct placement regions on the upper surface of the base plate **1** to leave space in between. In this bonding, the bonding layers **3** are fully cured by heating and pressurization.

[0112] Then, as shown in FIG. 13, a lattice-shaped insulating layer formation sheet 21a is positioned by, for example, pins and thus disposed on the upper surface of the base plate 1 around the semiconductor construct 2. The lattice-shaped insulating layer formation sheet 21a is prepared by dispersing a reinforcer in a thermosetting resin such as an epoxy resin, semi-curing the thermosetting resin into a sheet form, and forming square holes in the sheet by, for example, punching. [0113] Then, an upper insulating film formation sheet 22ais disposed on the upper surfaces of the semiconductor construct 2 and the insulating layer formation sheet 21a. The upper insulating film formation sheet **22***a* is prepared by impregnating, for example, glass fabric with a thermosetting resin such as an epoxy resin, and semi-curing the thermosetting resin into a sheet form.

[0114] Then, the insulating layer formation sheet 21a and the upper insulating film formation sheet 22a are heated and pressurized from the top and bottom using a pair of heating/ pressurization plates 42, 43. By subsequent cooling, an insulating layer 21 in a square frame shape is formed on the upper surface of the base plate 1 around the semiconductor construct 2, and an upper insulating film 22 is formed on the upper surfaces of the semiconductor construct 2 and the insulating layer 21. In this case, the upper surface of the upper insulating film 22 is pressed by the lower surface of the upper heating/pressurization plate 42, and is therefore a flat surface. [0115] Then, as shown in FIG. 14, by laser processing to radiate a laser beam, openings 23a are formed in parts of the upper insulating film 22 that correspond to predetermined nine points on the upper surface of the columnar electrode 13a of the semiconductor construct 2. Also, an opening 23c is formed in a part of the upper insulating film 22 that corresponds to the center of the upper surface of the columnar electrode 13c of the semiconductor construct 2.

**[0116]** Then, as shown in FIG. **15**, a foundation metal layer **44** is formed on the entire upper surface of the upper insulating film **22** including the upper surfaces of the columnar electrodes 13a, 13c of the semiconductor construct **2** that are exposed through the openings 23a, 23c of the upper insulating film **22**. In this case as well, the foundation metal layer **44** may only be a copper layer formed by electroless plating, may only be a copper layer formed by sputtering, or may be a copper layer formed by sputtering, or may be a copper layer formed by sputtering.

[0117] Then, a plating resist film 45 is patterned and formed on the upper surface of the foundation metal layer 44. In this case, openings 46*a*, 46*c* are formed in parts of the plating resist film 45 corresponding to regions where upper metal layers 26*a*, 26*c* are to be formed. Further, electrolytic plating with copper is carried out using the foundation metal layer 44 as a plating current path, thereby forming the upper metal layers 26*a*, 26*c* on the upper surface of the foundation metal layer 44 within the openings 46*a*, 46*c* in the plating resist film 45.

**[0118]** Then, the plating resist film **45** is released. Further, using the upper metal layers **26***a*, **26***c* as masks, the foundation metal layer **44** located in parts other than parts under the upper metal layers **26***a*, **26***c* is etched and removed. Thus, as shown in FIG. **16**, foundation metal layers **25***a*, **25***c* remain under the upper metal layers **26***a*, **26***c* alone. In this state, upper wirings **24***a*, **24***b* are formed by the upper metal layers **26***a*, **26***c* remaining thereunder.

**[0119]** Then, as shown in FIG. **17**, an overcoat film **27** made of, for example, a solder resist is formed by, for example, a screen printing method or spin coat method on the upper surface of the upper insulating film **22** including the upper wirings **24***a*, **24***c*. In this case, openings **28***a*, **28***b* are formed in parts of the overcoat film **27** that correspond to predetermined four points of the upper surface of the upper wiring **24***a* and to the connection pad portion of the upper wiring **24***c*.

**[0120]** Then, solder balls 29a, 29c are formed in and above the openings 28a, 28c of the overcoat film 27 so that these solder balls are connected to the predetermined four points of the upper surface of the upper wiring 24a and to the connec-

6

tion pad portion of the upper wiring 24*c*. Further, as shown in FIG. 18, the overcoat film 27, the upper insulating film 22, the insulating layer 21 and the base plate 1 are cut along the cut lines 41 between adjacent semiconductor constructs 2, thereby obtaining semiconductor devices shown in FIG. 2.

#### Second Embodiment

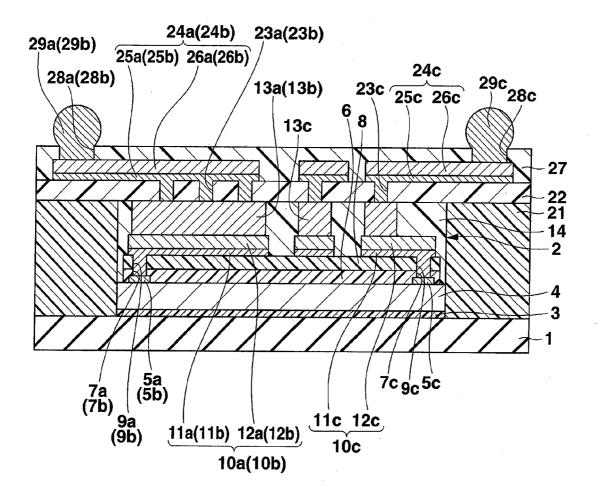

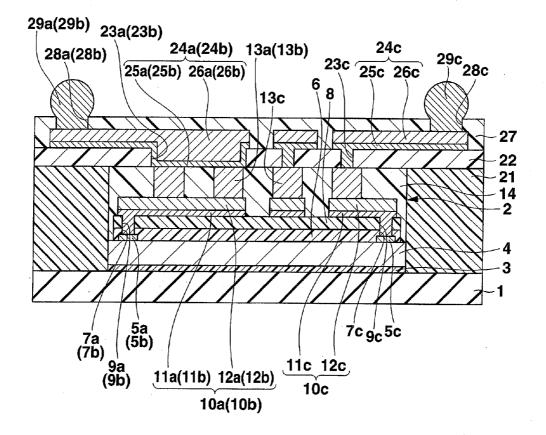

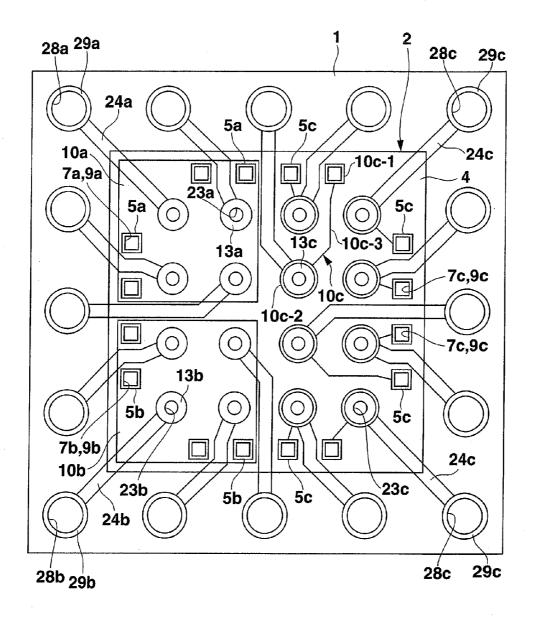

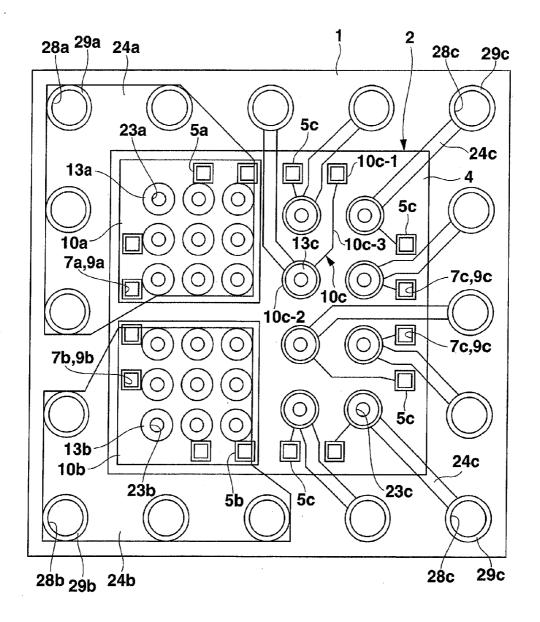

**[0121]** FIG. **19** shows a transmitted plan view of a semiconductor device according to a second embodiment of the invention. FIG. **20** shows a sectional view of a proper part of the semiconductor device shown in FIG. **19**. This semiconductor device includes a base plate **1**. The base plate **1** has a square planar shape, and made of, for example, an epoxy resin containing glass fabric as a base material. The lower surface of a semiconductor construct **2** is bonded to the center of the upper surface of the base plate **1** through a bonding layer **3** made of a die bond material. The semiconductor construct **2** has a square planar shape, and is slightly smaller in size than the base plate **1**.

**[0122]** The semiconductor construct 2, which is generally called a CSP, includes a silicon substrate (semiconductor substrate) 4. The lower surface of the silicon substrate 4 is bonded to the center of the upper surface of the base plate 1 through the bonding layer 3. Elements (not shown) such as a transistor, diode, resistor, and condenser that constitute an integrated circuit having a predetermined function are formed on the upper surface of the silicon substrate 4. Connection pads 5a, 5b, 5c are provided on the peripheral portion of the upper surface of the silicon substrate 4. The connection pads 5a, 5b, 5c are made of, for example, an aluminum-based metal, and connected to the elements of the integrated circuit.

**[0123]** Here, by way of example, the four connection pads indicated by the sign 5a and arranged on the upper left part of the silicon substrate 4 in FIG. 19 are for a common power supply voltage. The four connection pads indicated by the sign 5b and arranged on the lower left part of the silicon substrate 4 are for a common ground voltage. The four connection pads indicated by the sign 5c and arranged on the upper right part of the silicon substrate 4 and the four connection pads indicated by the sign 5c and arranged on the upper right part of the silicon substrate 4 and the four connection pads indicated by the sign 5c and arranged on the lower right part of the silicon substrate 4 are for a normal voltage. Here, in FIG. 20, the ground voltage connection pads 5b and associated parts are substantially similar to the power supply voltage connection pads 5a and associated parts, and are therefore indicated by signs in parentheses.

**[0124]** A passivation film (insulating film) **6** made of, for example, silicon oxide is provided on the upper surface of the silicon substrate **4** except for the peripheral portion of the silicon substrate **4** and the centers of the connection pads 5a, 5b, 5c. The centers of the connection pads 5a, 5b, 5c are exposed through openings 7a, 7b, 7c provided in the passivation film **6**. A protective film (insulating film) **8** made of, for example, a polyimide resin is provided on the upper surface of the passivation film **6**. Openings 9a, 9b, 9c are provided in parts of the protective film **8** that correspond to the openings 7a, 7b, 7c of the passivation film **6**.

**[0125]** Wirings 10a, 10b, 10c are provided on the upper surface of the protective film **8**. The wirings 10a, 10b, 10c have a double-layer structure composed of foundation metal layers 11a, 11b, 11c and upper metal layers 12a, 12b, 12c. The foundation metal layers 11a, 11b, 11c are made of, for example, copper and provided on the upper surface of the

protective film 8. The upper metal layers 12a, 12b, 12c are made of copper and provided on the upper surfaces of the foundation metal layers 11.

**[0126]** In this case, as shown in FIG. **19**, the wiring indicated by the sign **10***a* (common wiring) is solidly disposed on the upper left part of the silicon substrate **4** in a region that has a square planar shape and includes the four power supply voltage connection pads **5***a*. The wiring **10***a* is connected to all of the four power supply voltage connection pads **5***a* via the openings **7***a*, **9***a* of the passivation film **6** and the protective film **8**.

**[0127]** The wiring indicated by the sign 10b (common wiring) is solidly disposed on the lower left part of the silicon substrate **4** in a region that has a square planar shape and includes the four ground voltage connection pads **5***b*. The wiring **10***b* is connected to all of the four ground voltage connection pads **5***b* via the openings **7***b*, **9***b* of the passivation film **6** and the protective film **8**.

**[0128]** The wirings indicated by the sign 10c are disposed in the right region of the silicon substrate 4. Each wiring 10chas a connection portion 10c-1 connected to the normal voltage connection pad 5c via the openings 7c, 9c of the passivation film 6 and the protective film 8, a connection pad portion 10c-2 having a circular planar shape, and an extension line 10c-3 extending between the connection portion 10c-1 and the connection pad portion 10c-2.

**[0129]** Columnar electrodes (common columnar electrodes, first columnar electrodes) 13a are provided at predetermined four points on the upper surface of the wiring indicated by the sign 10a and having a square planar shape. The columnar electrodes 13a are made of copper and have a circular planar shape. Columnar electrodes (common columnar electrodes, first columnar electrodes) 13b are provided at predetermined four points on the upper surface of the wiring indicated by the sign 10b and having a square planar shape. The columnar electrodes 13b are made of copper and have a circular planar shape. Columnar electrodes) 13c are provided at predetermined four points on the upper surface of the wiring indicated by the sign 10b and having a square planar shape. The columnar electrodes 13b are made of copper and have a circular planar shape. Columnar electrodes (second columnar electrodes) 13c are provided on the upper surface of the connection pad portions 10c-2 of the wirings indicated by the sign 10c. The columnar electrodes 13c are made of copper and have a circular planar shape.

[0130] Here, the number of the columnar electrodes 13a and the number of the columnar electrodes 13b are the same as the number of the power supply voltage connection pads 5a and the number of the ground voltage connection pads 5b, respectively. Moreover, the columnar electrodes 13a, 13b have the same shape as the columnar electrodes 13c. In addition, as shown in FIG. 19, a total of 16 columnar electrodes 13a, 13b, 13c are arranged in matrix form.

[0131] A sealing film 14 made of, for example, an epoxy resin is provided around the columnar electrodes 13a, 13b, 13c on the upper surface of the protective film 8 including the wirings 10a, 10b, 10c. The columnar electrodes 13a, 13b, 13c are provided so that the upper surfaces thereof are flush with or several µm lower than the upper surface of the sealing film 14. The explanation of the structure of the semiconductor construct 2 is completed now.

**[0132]** An insulating layer **21** in a square frame shape is provided on the upper surface of the base plate **1** around the semiconductor construct **2**. For example, the insulating layer **21** is made of a thermosetting resin such as an epoxy resin in which a reinforcer of an inorganic material such as silica fuller is dispersed. Alternatively, the insulating layer **21** is only made of a thermosetting resin such as an epoxy resin.

**[0133]** An upper insulating film **22** is provided on the upper surfaces of the semiconductor construct **2** and the insulating layer **21**. The upper insulating film **22** is made of, for example, a base glass fabric impregnated with a thermosetting resin such as an epoxy resin. Alternatively, the upper insulating film **22** is only made of a thermosetting resin such as an epoxy resin.

[0134] Openings (first openings) 23a, 23b having a square planar shape are provided in parts of the upper insulating film 22 that correspond to regions that have a square planar shape and include four columnar electrodes 13a, 13b of the semiconductor construct 2. An opening (second opening) 23c having a circular planar shape is provided in a part of the upper insulating film 22 that corresponds to the center of the upper surface of the columnar electrode 13c of the semiconductor construct 2.

[0135] Upper wirings 24*a*, 24*b*, 24*c* are provided on the upper surface of the upper insulating film 22. The upper wirings 24*a*, 24*b*, 24*c* have a double-layer structure composed of foundation metal layers 25*a*, 25*b*, 25*c* and upper metal layers 26*a*, 26*b*, 26*c*. The foundation metal layers 25*a*, 25*b*, 25*c* are made of, for example, copper and provided on the upper surface of the upper insulating film 22. The upper metal layers 26*a*, 26*b*, 26*c* are made of copper and provided on the upper surfaces of the foundation metal layers 25*a*, 25*b*, 25*c*.

[0136] In this case, as shown in FIG. 19, the upper wiring indicated by the sign 24a (common upper wiring, first upper wiring) is solidly disposed on the upper left part of the upper insulating film 22 in a region of the upper insulating film 22 including an opening 23a having a square planar shape. The upper wiring 24a is connected, via one opening 23a of the upper insulating film 22 having a square planar shape, to the upper surfaces of all the four power supply voltage columnar electrodes 13a of the semiconductor construct 2. Here, within the opening 23a of the upper insulating film 22, the upper wiring 24a is provided on the upper surfaces of the four columnar electrodes 13a of the semiconductor construct 2 and on the upper surface of the sealing film 14 therearound. [0137] The upper wiring indicated by the sign 24b (common upper wiring, first upper wiring) is solidly disposed on the lower left part of the upper insulating film 22 in a region of the upper insulating film 22 including the opening 23bhaving a square planar shape. The upper wiring 24b is connected, via one opening 23b of the upper insulating film 22 having a square planar shape, to the upper surfaces of all the four ground voltage columnar electrodes 13b of the semiconductor construct 2. In this case as well, within the opening 23bof the upper insulating film 22, the upper wiring 24b is provided on the upper surfaces of the four columnar electrodes 13b of the semiconductor construct 2 and on the upper surface of the sealing film 14 therearound.

**[0138]** Similarly to the wiring of the semiconductor construct 2 indicated by the sign 10c, each upper wiring indicated by the sign 24c (second upper wiring) has a connection portion, a connection pad portion, and an extension line extending therebetween. The upper wiring 24c is connected to the center of the upper surface of the columnar electrode 13c of the semiconductor construct 2 via the opening 23c of the upper insulating film 22 having a circular planar shape. Here, as shown in FIG. 20, the upper surfaces of the upper wirings 24a, 24b, 24c are flush.

**[0139]** An overcoat film **27** made of, for example, a solder resist is provided on the upper surface of the upper insulating

film 22 including the upper wirings 24a, 24b, 24c. Openings 28a, 28b are provided in parts of the overcoat film 27 that correspond to predetermined four points of the peripheral portion of the upper wirings 24a, 24b. An opening 28c is provided in a part of the overcoat film 27 that corresponds to the connection pad portion of the upper wiring 24c.

[0140] Solder balls 29a, 29b, 29c are provided in and above the openings 28a, 28b, 28c of the overcoat film 27 so that these solder balls are connected to the upper wirings 24a, 24b, 24c. In this case, as shown in FIG. 19, the solder balls 29a, 29b, 29c are only disposed around the semiconductor construct 2. Moreover, both the number of the solder balls 29aand the number of the solder balls 29b are four, and are the same as the number (four) of the power supply voltage and ground voltage connection pads 5a, 5b of the semiconductor construct 2.

**[0141]** As described above, in this semiconductor device, the power supply voltage wiring 10a and the ground voltage wiring 10b of the semiconductor construct 2 are solidly formed in a square planar shape, and each connected to all of the four connection pads 5a, 5b. This allows the power supply voltage wiring 10a and the ground voltage wiring 10b not to be burned off even if an excessively high current runs through these wirings.

**[0142]** Furthermore, since one opening 23a, 23b having a square planar shape is provided in each of the parts of the upper insulating film 22 that correspond to the four power supply voltage columnar electrodes 13a and the four ground voltage columnar electrodes 13b of the semiconductor construct 2. The solidly-formed upper wirings 24a, 24b are provided on the upper insulating film 22 so that these upper wirings are connected to all the four columnar electrodes 13a of the semiconductor construct 2 via the opening 23a, 23b of the upper insulating film 22, the parts corresponding to the opening 23a, 23b of the upper insulating film 22 can be reduced in resistance, and current capacity can thus be improved.

**[0143]** Here, the sizes of the parts of this semiconductor device are mentioned. The size of the base plate 1 is  $3\times3$  mm. The size of the semiconductor construct 2 is  $2\times2$  mm. The line width of the extension line 10c-3 of the wiring 10c of the semiconductor construct 2 is  $20 \ \mu\text{m}$ . The diameter of the columnar electrode 13a, 13b, 13c of the semiconductor construct 2 is  $0.2 \ \text{mm}$ . The pitch of the columnar electrode 13a, 13b, 13c of the opening 23c of the upper insulating film 22 having a circular planar shape is  $100 \ \mu\text{m}$ . The diameter of the solder balls 29a, 29b, 29c is  $0.3 \ \text{mm}$ .

**[0144]** Now, one example of a method of manufacturing this semiconductor device is described. First, one example of a method of manufacturing the semiconductor construct **2** is described. In this case, the ground voltage connection pad 5b and associated parts are substantially similar to the power supply voltage connection pads 5a and associated parts, and are therefore not described.

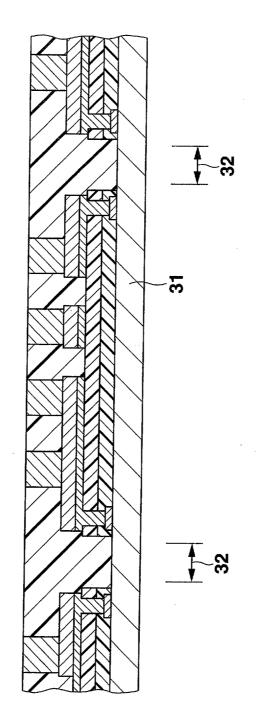

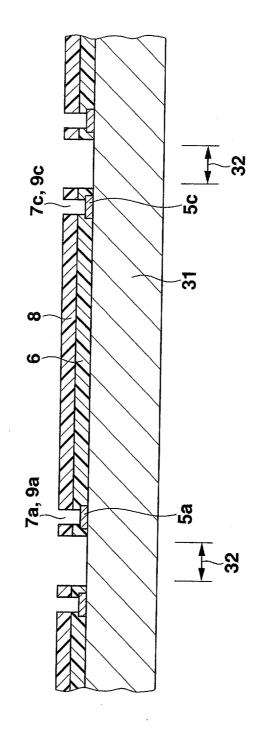

**[0145]** First, as shown in FIG. **21**, an assembly is prepared. In this assembly, connection pads 5a, 5c, a passivation film **6** and a protective film **8** are formed on the upper surface of a silicon substrate in a wafer state (hereinafter referred to as a semiconductor wafer **31**). Further, the centers of the connection pads 5a, 5c are exposed through openings 7a, 7c of the passivation film **6** and through openings 9a, 9c of the protective film **8**. **[0146]** In this case, the thickness of the semiconductor wafer **31** is greater than the thickness of a silicon substrate **4** shown in FIG. **20**. In FIG. **21**, zones indicated by the sign **32** are dicing streets. The parts of the passivation film **6** and the protective film **8** corresponding to the dicing street **32** and both its sides are removed.

[0147] Then, as shown in FIG. 22, a foundation metal layer 33 is formed on the entire upper surface of the protective film 8 including the upper surfaces of the connection pads 5a, 5c exposed through openings 7a, 7c of the passivation film 6 and through openings 9a, 9c of the protective film 8. In this case, the foundation metal layer 33 may only be a copper layer formed by electroless plating, may only be a copper layer formed by sputtering, or may be a copper layer formed by sputtering on a thin film layer of, for example, titanium formed by sputtering.

[0148] Then, a plating resist film 34 made of a positive liquid resist is patterned and formed on the upper surface of the foundation metal layer 33. In this case, openings 35a, 35c are formed in parts of the plating resist film 34 corresponding to regions where upper metal layers 12a, 12c are to be formed. Further, electrolytic plating with copper is carried out using the foundation metal layer 33 as a plating current path, thereby forming the upper metal layers 12a, 12c on the upper surface of the foundation metal layer 33 within the openings 35a, 35c in the plating resist film 34. Subsequently, the plating resist film 34 is released.

**[0149]** Then, as shown in FIG. **23**, a plating resist film **36** made of a negative dry film resist is patterned and formed on the upper surface of the foundation metal layer **33**. In this case, openings **37***a*, **37***c* are formed in parts of the plating resist film **36** corresponding to predetermined four points of the upper metal layer **12***a* (a region where a columnar electrode **13***a* is to be formed) and corresponding to the connection pad portion of the upper metal layer **12***c* (a region where a columnar electrode **13***c* is to be formed).

**[0150]** Then, electrolytic plating with copper is carried out using the foundation metal layer **33** as a plating current path. As a result, the columnar electrode 13a is formed on the upper surface of the upper metal layer 12a within the openings 37a in the plating resist film **36**. Moreover, the columnar electrode 13c is formed on the upper surface of the connection pad portion of the upper metal layer 12c within the openings 37c in the plating resist film **36**. Subsequently, the plating resist film **36** is released.

[0151] Then, using the upper metal layers 12a, 12c as masks, the foundation metal layer 33 located in parts other than parts under the upper metal layers 12a, 12c is etched and removed. Thus, as shown in FIG. 24, foundation metal layers 11a, 11c remain under the upper metal layers 12a, 12c alone. In this state, wirings 10a, 10c having a double-layer structure are formed by the upper metal layers 12a, 12c and the foundation metal layers 11a, 11c remaining thereunder.

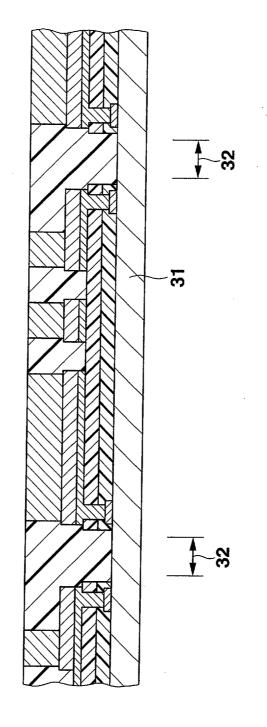

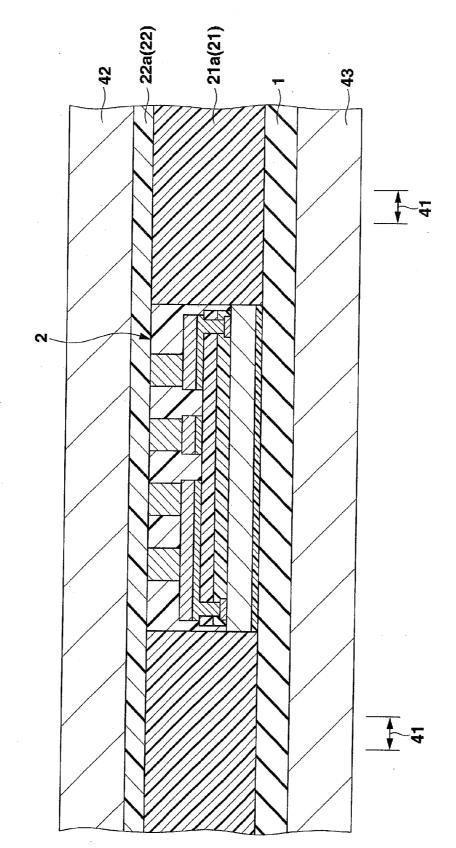

[0152] Then, as shown in FIG. 25, a sealing film 14 made of, for example, an epoxy resin is formed by, for example, the spin coat method on the upper surface of the semiconductor wafer 31 corresponding to the dicing street 32 and both its sides and on the upper surface of the protective film 8 including the wirings 10a, 10c and the columnar electrodes 13a, 13c so that the thickness of this sealing film 14 is slightly greater than the height of the columnar electrodes 13a, 13c. Thus, in this state, the upper surfaces of the columnar electrodes 13a, 13c are covered with the sealing film 14.

[0153] Then, the upper side of the sealing film 14 is properly ground to expose the upper surfaces of the columnar electrodes 13a, 13c as shown in FIG. 26, and the upper surface of the sealing film 14 including the exposed upper surfaces of the columnar electrodes 13a, 13c is planarized. Further, as shown in FIG. 27, the lower side of the semiconductor wafer 31 is properly ground to reduce the thickness of the semiconductor wafer 31.

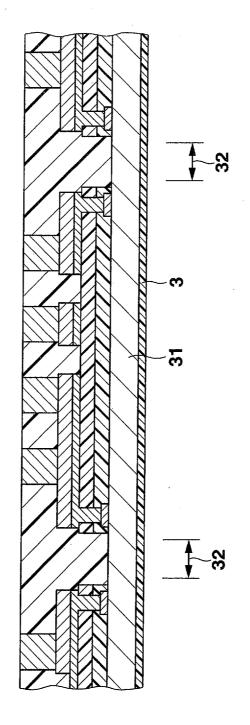

**[0154]** Then, as shown in FIG. **28**, a bonding layer **3** is bonded to the lower surface of the semiconductor wafer **31**. The bonding layer **3** is made of a die bond material such as an epoxy resin, and is fixedly attached in a semi-cured state by heating and pressurization to the lower surface of the semiconductor wafer **31**. Further, as shown in FIG. **29**, the sealing film **14**, the semiconductor wafer **31** and the bonding layer **3** are cut along the dicing streets **32**, thereby obtaining semiconductor constructs **2** having the bonding layers **3** on the lower surface.

**[0155]** Now, one example of how to manufacture the semiconductor device shown in FIG. **20** using the semiconductor construct **2** shown in FIG. **29** is described. In this case as well, parts associated with the ground voltage connection pad 5bare substantially similar to parts associated with the power supply voltage connection pads 5a, and are therefore not described.

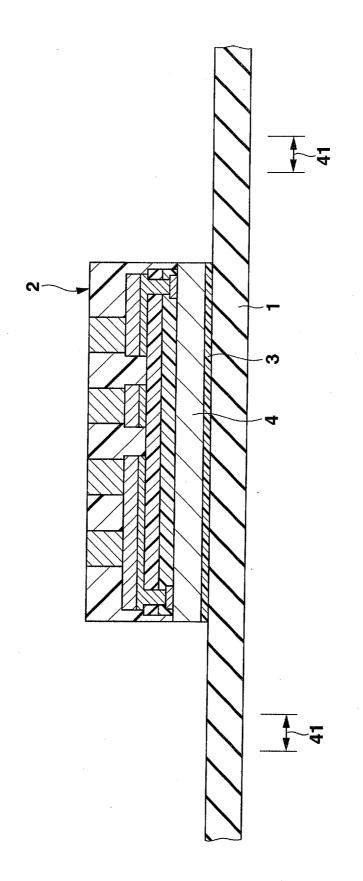

**[0156]** First, as shown in FIG. **30**, a base plate **1** is prepared. This base plate **1** is made of, for example, an epoxy resin containing glass fabric as a base material, and has an area that allows the completed semiconductor devices shown in FIG. **20** to be formed thereon. For example, the base plate **1** has, but not exclusively, a square planar shape. In addition, zones indicated by the sign **41** in FIG. **30** correspond to cut lines for division.

[0157] Then, the bonding layers **3** fixedly attached to the lower surfaces of the silicon substrates **4** of the semiconductor constructs **2** are bonded to semiconductor construct placement regions on the upper surface of the base plate **1** to leave space in between. In this bonding, the bonding layers **3** are fully cured by heating and pressurization.

**[0158]** Then, as shown in FIG. **31**, a lattice-shaped insulating layer formation sheet 21a is positioned by, for example, pins and thus disposed on the upper surface of the base plate **1** around the semiconductor construct **2**. The lattice-shaped insulating layer formation sheet 21a is prepared by dispersing a reinforcer in a thermosetting resin such as an epoxy resin, semi-curing the thermosetting resin into a sheet form, and forming square holes in the sheet by, for example, punching.

**[0159]** Then, an upper insulating film formation sheet 22a is disposed on the upper surfaces of the semiconductor construct 2 and the insulating layer formation sheet 21a. The upper insulating film formation sheet 22a is prepared by impregnating, for example, glass fabric with a thermosetting resin such as an epoxy resin, and semi-curing the thermosetting resin into a sheet form.

[0160] Then, the insulating layer formation sheet 21a and the upper insulating film formation sheet 22a are heated and pressurized from the top and bottom using a pair of heating/ pressurization plates 42, 43. By subsequent cooling, an insulating layer 21 in a square frame shape is formed on the upper surface of the base plate 1 around the semiconductor construct 2, and an upper insulating film 22 is formed on the upper surfaces of the semiconductor construct 2 and the insulating layer 21. In this case, the upper surface of the upper surface of

insulating film 22 is pressed by the lower surface of the upper heating/pressurization plate 42, and is therefore a flat surface.

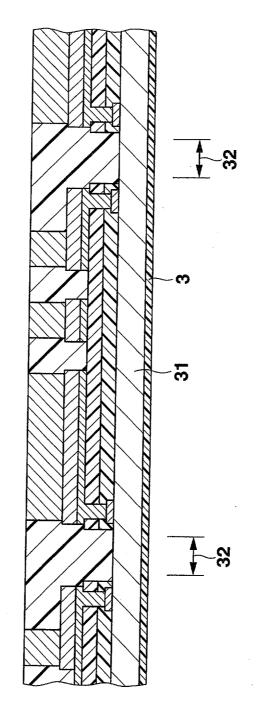

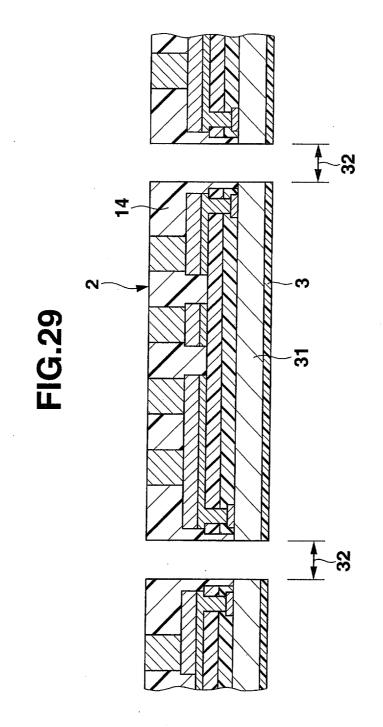

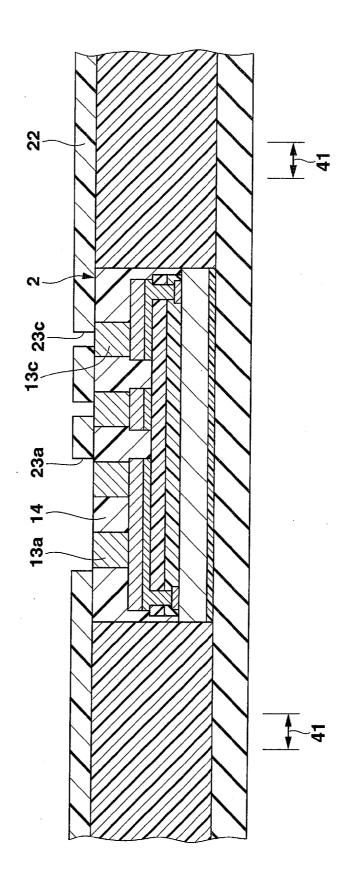

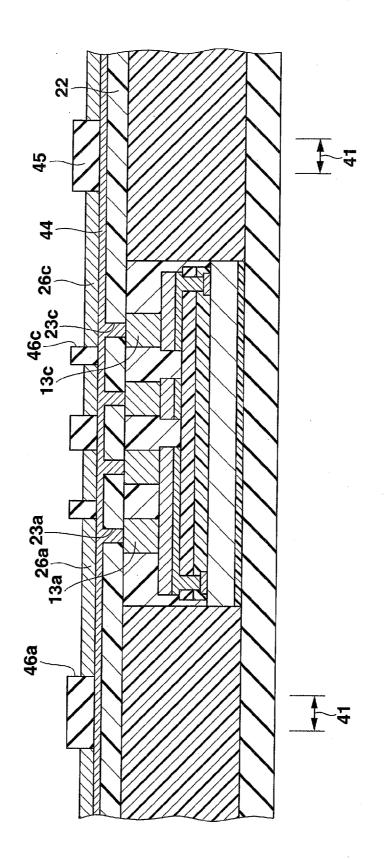

**[0161]** Then, as shown in FIG. **32**, by laser processing to radiate a laser beam, an opening 23a having a square planar shape is formed in a part of the upper insulating film **22** that corresponds to a region of the semiconductor construct **2** having a square planar shape and including the four columnar electrodes **13***a*. Also, an opening **23***c* having a circular planar shape is formed in a part of the upper insulating film **22** that corresponds to the center of the upper surface of the columnar electrode **13***c* of the semiconductor construct **2**.

[0162] In this state, the upper surface of the sealing film 14 around the columnar electrodes 13a is exposed through the opening 23a having a square planar shape.

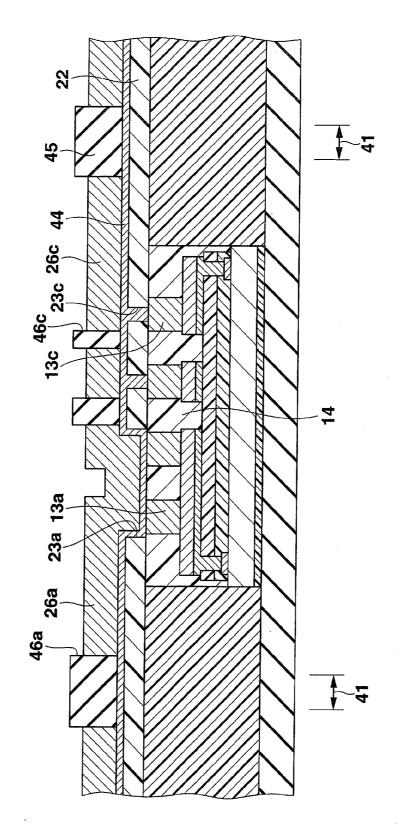

[0163] Then, as shown in FIG. 33, a foundation metal layer 44 is formed on the entire upper surface of the upper insulating film 22 including the upper surfaces of the columnar electrodes 13a and the sealing film 14 of the semiconductor construct 2 that are exposed through the opening 23a of the upper insulating film 22 and including the upper surface of the columnar electrode 13c of the semiconductor construct 2 exposed through the opening 23c of the upper insulating film 22. In this case as well, the foundation metal layer 44 may only be a copper layer formed by electroless plating, may only be a copper layer formed by sputtering, or may be a copper layer formed by sputtering, or may be a copper layer formed by sputtering.

[0164] Then, a plating resist film 45 is patterned and formed on the upper surface of the foundation metal layer 44. In this case, openings 46*a*, 46*c* are formed in parts of the plating resist film 45 corresponding to regions where upper metal layers 26*a*, 26*c* are to be formed. Further, electrolytic plating with copper is carried out using the foundation metal layer 44 as a plating current path, thereby forming the upper metal layers 26*a*, 26*c* on the upper surface of the foundation metal layer 44 within the openings 46*a*, 46*c* in the plating resist film 45.

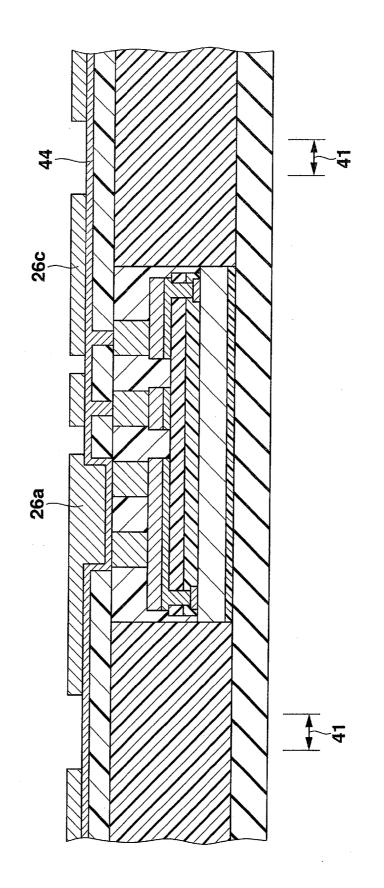

**[0165]** In this case, since the copper plating is isotropically formed on the upper surface of the foundation metal layer **44**, the thinnest portion of the upper metal layer **26***a* formed on the upper surface of the foundation metal layer **44** within the opening **23***a* of the upper insulating film **22** is set at a thickness equal to or greater than the thickness of the upper metal layer **26***a* shown in FIG. **20**. Then, the plating resist film **45** is released. Further, the upper side of the upper metal layers **26***a*, **26***c* is properly ground so that the upper surfaces of the upper metal layers **26***a*, **26***c* may be flush, as shown in FIG. **34**.

[0166] Then, using the upper metal layers 26a, 26c as masks, the foundation metal layer 44 located in parts other than parts under the upper metal layers 26a, 26c is etched and removed. Thus, as shown in FIG. 35, foundation metal layers 25a, 25c remain under the upper metal layers 26a, 26c alone. In this state, upper wirings 24a, 24c are formed by the upper metal layers 25a, 25c remaining thereunder.

[0167] Then, as shown in FIG. 36, an overcoat film 27 made of, for example, a solder resist is formed by, for example, the screen printing method or spin coat method on the upper surface of the upper insulating film 22 including the upper wirings 24*a*, 24*c*. In this case, openings 28*a*, 28*b* are formed in parts of the overcoat film 27 that correspond to predetermined four points of the upper surface of the upper wiring 24*a* and to the connection pad portion of the upper wiring 24*c*.

[0168] Then, solder balls 29a, 29c are formed in and above the openings 28a, 28c of the overcoat film 27 so that these solder balls are connected to the predetermined four points of the upper surface of the upper wiring 24a and to the connection pad portion of the upper wiring 24c. Further, as shown in FIG. 37, the overcoat film 27, the upper insulating film 22, the insulating layer 21 and the base plate 1 are cut along the cut lines 41 between adjacent semiconductor constructs 2, thereby obtaining semiconductor devices shown in FIG. 20.

#### Third Embodiment

**[0169]** FIG. **38** shows a transmitted plan view of a semiconductor device according to a third embodiment of the invention. FIG. **39** shows a sectional view of a proper part of the semiconductor device shown in FIG. **38**. This semiconductor device is different from the semiconductor device shown in FIG. **19** and FIG. **20** in that, in a semiconductor construct **2**, columnar electrodes **13***a*, **13***b* having a square planar shape are solidly provided, in similar fashion to power supply voltage and ground voltage wirings that are indicated by the signs **10***a*, **10***b* and have a square planar shape, in regions of the upper surfaces of the wirings **10***a*, **10***b* except for the peripheral portions thereof.

[0170] In this case, openings 23a, 23b of an upper insulating film 22 are provided in parts corresponding to the upper surfaces of the columnar electrodes 13a, 13b except for the peripheral portions thereof. Further, upper wirings 24a, 24b are connected, via the openings 23a, 23b of the upper insulating film 22, to the upper surfaces of the columnar electrodes 13a, 13b except for the peripheral portions thereof.

[0171] As described above, since the power supply voltage columnar electrode 13a and the ground voltage columnar electrode 13 of the semiconductor construct 2 are solidly formed in this semiconductor device, the columnar electrodes 13a, 13b can be reduced in resistance, and current capacity can thus be further improved.

#### Fourth Embodiment

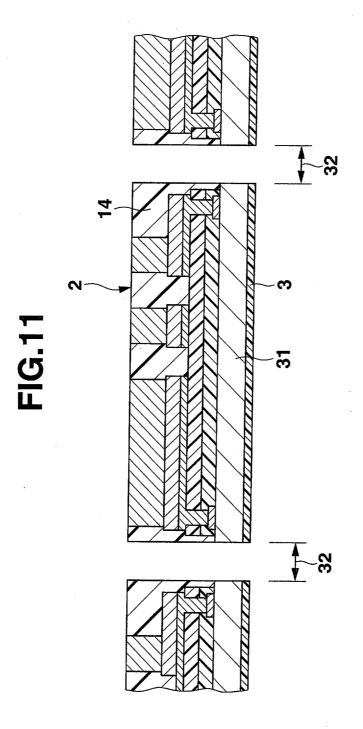

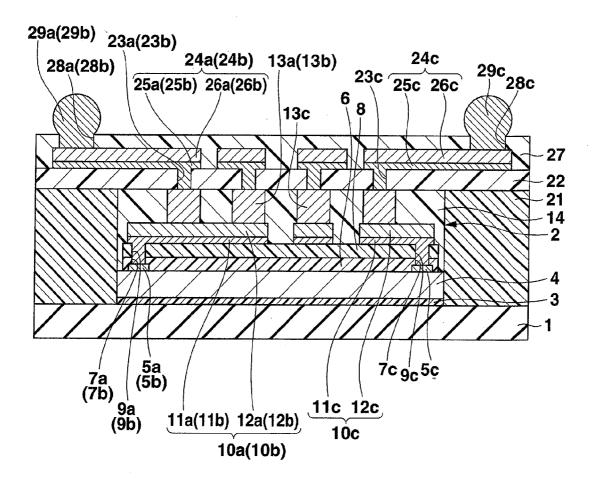

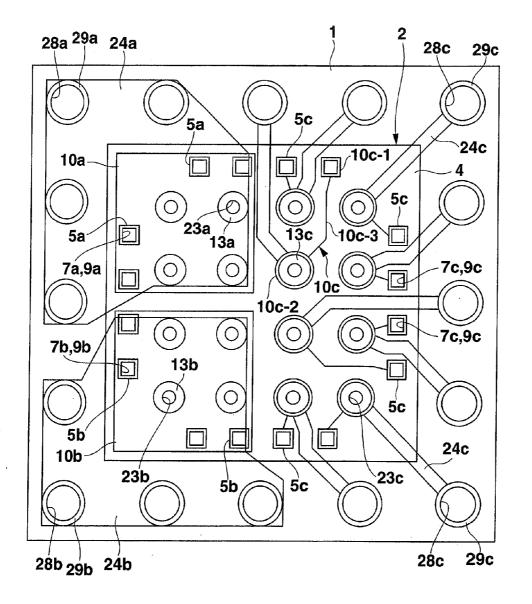

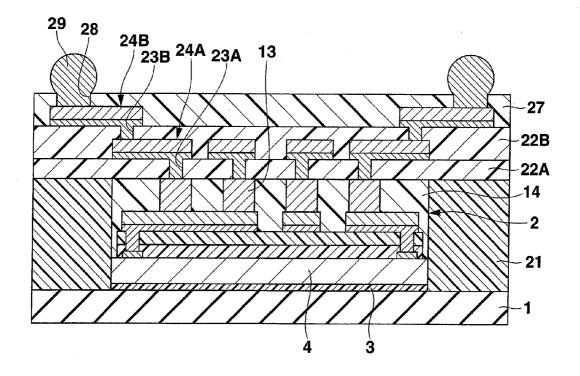

**[0172]** FIG. **40** shows a transmitted plan view of a semiconductor device according to a fourth embodiment of the invention. FIG. **41** is a sectional view of a proper part of the semiconductor device shown in FIG. **41**. This semiconductor device includes a base plate **1**. The base plate **1** has a square planar shape, and made of, for example, an epoxy resin containing glass fabric as a base material. The lower surface of a semiconductor construct **2** is bonded to the center of the upper surface of the base plate **1** through a bonding layer **3** made of a die bond material. The semiconductor construct **2** has a square planar shape, and is slightly smaller in size than the base plate **1**.

[0173] The semiconductor construct 2, which is generally called a CSP, includes a silicon substrate (semiconductor substrate) 4. The lower surface of the silicon substrate 4 is bonded to the center of the upper surface of the base plate 1 through the bonding layer 3. Elements (not shown) such as a transistor, diode, resistor, and condenser that constitute an integrated circuit having a predetermined function are formed on the upper surface of the silicon substrate 4. Connection pads 5a, 5b, 5c are provided on the peripheral portion of the upper surface of the silicon substrate 4. The connection pads 5a, 5b, 5c are made of, for example, an aluminum-based metal, and connected to the elements of the integrated circuit.

**[0174]** Here, by way of example, the four connection pads indicated by the sign 5a and arranged on the upper left part of the silicon substrate 4 in FIG. 40 are for a common power supply voltage. The four connection pads indicated by the sign 5b and arranged on the lower left part of the silicon substrate 4 are for a common ground voltage. The four connection pads indicated by the sign 5c and arranged on the upper right part of the silicon substrate 4 and the four connection pads indicated by the sign 5c and arranged on the upper right part of the silicon substrate 4 and the four connection pads indicated by the sign 5c and arranged on the lower right part of the silicon substrate 4 are for a normal voltage. Here, in FIG. 41, the ground voltage connection pads 5b and associated parts are substantially similar to the power supply voltage connection pads 5a and associated parts, and are therefore indicated by signs in parentheses.

**[0175]** A passivation film (insulating film) **6** made of, for example, silicon oxide is provided on the upper surface of the silicon substrate **4** except for the peripheral portion of the silicon substrate **4** and the centers of the connection pads 5a, 5b, 5c. The centers of the connection pads 5a, 5b, 5c are exposed through openings 7a, 7b, 7c provided in the passivation film **6**. A protective film (insulating film) **8** made of, for example, a polyimide resin is provided on the upper surface of the passivation film **6**. Openings 9a, 9b, 9c are provided in parts of the protective film **8** that correspond to the openings 7a, 7b, 7c of the passivation film **6**.

[0176] Wirings 10a, 10b, 10c are provided on the upper surface of the protective film 8. The wirings 10a, 10b, 10c have a double-layer structure composed of foundation metal layers 11a, 11b, 11c and upper metal layers 12a, 12b, 12c. The foundation metal layers 11a, 11b, 11c are made of, for example, copper and provided on the upper surface of the protective film 8. The upper metal layers 12a, 12b, 12c are made of copper and provided on the upper surfaces of the foundation metal layers 11a.

**[0177]** In this case, as shown in FIG. **40**, the wiring indicated by the sign **10***a* (common wiring) is solidly disposed on the upper left part of the silicon substrate **4** in a region that has a square planar shape and includes the four power supply voltage connection pads **5***a*. The wiring **10***a* is connected to all of the four power supply voltage connection pads **5***a* via the openings **7***a*, **9***a* of the passivation film **6** and the protective film **8**.

**[0178]** The wiring indicated by the sign 10b (common wiring) is solidly disposed on the lower left part of the silicon substrate **4** in a region that has a square planar shape and includes the four ground voltage connection pads **5***b*. The wiring **10***b* is connected to all of the four ground voltage connection pads **5***b* via the openings **7***b*, **9***b* of the passivation film **6** and the protective film **8**.

[0179] The wirings indicated by the sign 10c are disposed in the right region of the silicon substrate 4. Each wiring 10chas a connection portion 10c-1 connected to the normal voltage connection pad 5c via the openings 7c, 9c of the passivation film 6 and the protective film 8, a connection pad portion 10c-2 having a circular planar shape, and an extension line 10c-3 extending between the connection portion 10c-1 and the connection pad portion 10c-2.

**[0180]** Columnar electrodes (common columnar electrodes, first columnar electrodes) 13a made of copper are provided at predetermined four points on the upper surface of the wiring indicated by the sign 10a and having a square planar shape. Columnar electrodes (common columnar electrodes, first columnar electrodes) 13b made of copper are provided at predetermined four points on the upper surface of

the wiring indicated by the sign 10b and having a square planar shape. A columnar electrode (second columnar electrode) 13c made of copper is provided on the upper surface of the connection pad portion 10c-2 of the wiring indicated by the sign 10c. Here, as shown in FIG. 40, a total of 16 columnar electrodes 13a, 13b, 13c are arranged in matrix form.

**[0181]** A sealing film 14 made of, for example, an epoxy resin is provided around the columnar electrodes 13a, 13b, 13c on the upper surface of the protective film 8 including the wirings 10a, 10b, 10c. The columnar electrodes 13a, 13b, 13c are provided so that the upper surfaces thereof are flush with or several µm lower than the upper surface of the sealing film 14. The explanation of the structure of the semiconductor construct 2 is completed now.

**[0182]** An insulating layer **21** in a square frame shape is provided on the upper surface of the base plate **1** around the semiconductor construct **2**. For example, the insulating layer **21** is made of a thermosetting resin such as an epoxy resin in which a reinforcer of an inorganic material such as silica fuller is dispersed. Alternatively, the insulating layer **21** is only made of a thermosetting resin such as an epoxy resin.

[0183] An upper insulating film 22 is provided on the upper surfaces of the semiconductor construct 2 and the insulating layer 21. The upper insulating film 22 is made of, for example, a base glass fabric impregnated with a thermosetting resin such as an epoxy resin. Alternatively, the upper insulating film 22 is only made of a thermosetting resin such as an epoxy resin. Openings 23*a*, 23*b*, 23*c* are provided in parts of the upper insulating film 22 that correspond to the centers of the upper surfaces of the columnar electrodes 13a, 13b, 13c of the semiconductor construct 2.

[0184] Upper wirings 24*a*, 24*b*, 24*c* are provided on the upper surface of the upper insulating film 22. The upper wirings 24*a*, 24*b*, 24*c* have a double-layer structure composed of foundation metal layers 25*a*, 25*b*, 25*c* and upper metal layers 26*a*, 26*b*, 26*c*. The foundation metal layers 25*a*, 25*b*, 25*c* are made of, for example, copper and provided on the upper surface of the upper insulating film 22. The upper metal layers 26*a*, 26*b*, 26*c* are made of copper and provided on the upper surfaces of the foundation metal layers 25*a*, 25*b*, 25*c*.

[0185] In this case, similarly to the wiring of the semiconductor construct 2 indicated by the sign 10c, each of the upper wirings 24a, 24b, 24c includes a connection portion, a connection pad portion, and an extension line extending therebetween. The connection portions of the upper wirings (common upper wirings, first upper wirings) 24a, 24b are connected to the upper surfaces of the columnar electrodes 13a, 13b of the semiconductor construct 2 via the openings 23a, 23b of the upper insulating film 22. The connection portion of the upper surface of the columnar electrode 13cof the semiconductor construct 2 via the opening 23c of the upper insulating film 22.

[0186] An overcoat film 27 made of, for example, a solder resist is provided on the upper surface of the upper insulating film 22 including the upper wirings 24*a*, 24*b*, 24*c*. Openings 28*a*, 28*b*, 28*c* are provided in parts of the overcoat film 27 that correspond to the connection pad portions of the upper wirings 24*a*, 24*b*, 24*c*. Solder balls 29*a*, 29*b*, 29*c* are provided in and above the openings 28*a*, 28*b*, 28*c* so that these solder balls are connected to the connection pad portions of the upper wirings 24*a*, 24*b*, 24*c*. Here, as shown in FIG. 40, the connection pad portions of the upper wirings 24*a*, 24*b*, 24*c*.

and the solder balls **29***a*, **29***b*, **29***c* are only disposed around the semiconductor construct **2**.

**[0187]** As described above, in this semiconductor device, the power supply voltage wiring 10a and the ground voltage wiring 10b of the semiconductor construct 2 are solidly formed in a square planar shape, and each connected to all of the four connection pads 5a, 5b. This allows the power supply voltage wiring 10a and the ground voltage wiring 10b not to be burned off even if an excessively high current runs through these wirings.

**[0188]** Here, the sizes of the parts of this semiconductor device are mentioned. The size of the base plate 1 is  $3\times3$  mm. The size of the semiconductor construct 2 is  $2\times2$  mm. The line width of the extension line 10c-3 of the wiring 10c of the semiconductor construct 2 is  $20 \ \mu\text{m}$ . The diameter of the columnar electrode 13a, 13b, 13c of the semiconductor construct 2 is  $0.2 \ \text{mm}$ . The pitch of the columnar electrode 13a, 13b, 13c of the semiconductor construct 2 is  $0.4 \ \text{mm}$ . The diameter of the opening 23 of the upper insulating film 22 is  $100 \ \mu\text{m}$ . The diameter of the connection pad portion of the upper wiring is  $0.3 \ \text{mm}$ . The pitch of the connection pad portion of the upper wiring is  $0.65 \ \text{mm}$ .

**[0189]** In the meantime, since the base plate 1 is greater in size than the semiconductor construct 2, even if the extension line 10c-3 of the normal voltage wiring 10c of the semiconductor construct 2 has a relatively small line width of 20 µm, the extension line of the upper wiring 24*a*, 24*b*, 24*c* can have a relatively great line width of about 100 µm. This makes it possible to prevent the power supply voltage upper wiring 24*a* and the ground voltage upper wiring 24*b* from being easily burned off even if an excessively high current runs through these upper wirings.

**[0190]** Now, one example of a method of manufacturing this semiconductor device is described. First, one example of a method of manufacturing the semiconductor construct 2 is described. In this case, the ground voltage connection pad 5b and associated parts are substantially similar to the power supply voltage connection pads 5a and associated parts, and are therefore not described.

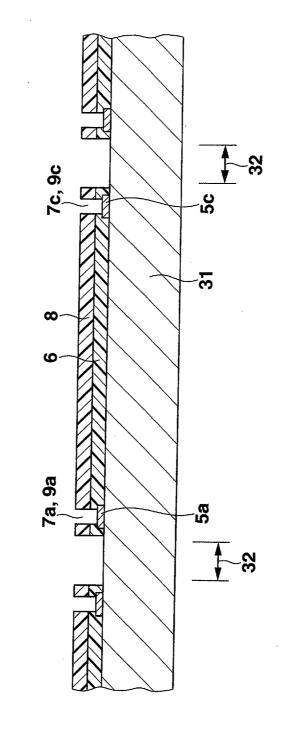

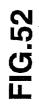

**[0191]** First, as shown in FIG. **42**, an assembly is prepared. In this assembly, connection pads 5a, 5c, a passivation film **6** and a protective film **8** are formed on the upper surface of a silicon substrate in a wafer state (hereinafter referred to as a semiconductor wafer **31**). Further, the centers of the connection pads 5a, 5c are exposed through openings 7a, 7c of the passivation film **6** and through openings 9a, 9c of the protective film **8**.

**[0192]** In this case, the thickness of the semiconductor wafer **31** is greater than the thickness of a silicon substrate **4** shown in FIG. **41**. In FIG. **42**, zones indicated by the sign **32** are dicing streets. The parts of the passivation film **6** and the protective film **8** corresponding to the dicing street **32** and both its sides are removed.

**[0193]** Then, as shown in FIG. **43**, a foundation metal layer **33** is formed on the entire upper surface of the protective film **8** including the upper surfaces of the connection pads 5a, 5c exposed through openings 7a, 7c of the passivation film **6** and through openings 9a, 9c of the protective film **8**. In this case, the foundation metal layer **33** may only be a copper layer formed by electroless plating, may only be a copper layer formed by sputtering, or may be a copper layer formed by sputtering on a thin film layer of, for example, titanium formed by sputtering.

[0194] Then, a plating resist film 34 made of a positive liquid resist is patterned and formed on the upper surface of the foundation metal layer 33. In this case, openings 35a, 35c are formed in parts of the plating resist film 34 corresponding to regions where upper metal layers 12a, 12c are to be formed. Further, electrolytic plating with copper is carried out using the foundation metal layer 33 as a plating current path, thereby forming the upper metal layers 12a, 12c on the upper surface of the foundation metal layer 33 within the openings 35a, 35c in the plating resist film 34. Subsequently, the plating resist film 34 is released.

**[0195]** Then, as shown in FIG. **44**, a plating resist film **36** made of a negative dry film resist is patterned and formed on the upper surface of the foundation metal layer **33**. In this case, openings **37***a*, **37***c* are formed in parts of the plating resist film **36** corresponding to predetermined four points of the upper metal layer **12***a* (a region where a columnar electrode **13***a* is to be formed) and corresponding to the connection pad portion of the upper metal layer **12***c* (a region where a columnar electrode **13***c* is to be formed).

**[0196]** Then, electrolytic plating with copper is carried out using the foundation metal layer **33** as a plating current path. As a result, the columnar electrodes 13a, 13c are formed on the upper surface of the upper metal layer 12a within the openings 37a in the plating resist film **36** and on the upper surface of the connection pad portion of the upper metal layer 12c within the openings 37c in the plating resist film **36**. Subsequently, the plating resist film **36** is released.