## (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 111200437 B (45) 授权公告日 2024.05.10

(21)申请号 201911124958.0

(22)申请日 2019.11.18

(65) 同一申请的已公布的文献号 申请公布号 CN 111200437 A

(43) 申请公布日 2020.05.26

(30) 优先权数据 2018-217264 2018.11.20 JP

(73)专利权人 株式会社电装 地址 日本爱知县

(72) 发明人 中村邦彦 藤本悠 根塚智裕

(74) 专利代理机构 永新专利商标代理有限公司 72002

专利代理师 邬少俊

(51) Int.CI.

**HO3M** 1/12 (2006.01)

#### (56) 对比文件

CN 102893528 A.2013.01.23

CN 107925415 A, 2018.04.17

US 2002063650 A1,2002.05.30

US 2005151680 A1,2005.07.14

US 2011095930 A1,2011.04.28

US 2011254716 A1,2011.10.20

US 2016043733 A1,2016.02.11

US 7268718 B1,2007.09.11

US 7489263 B1,2009.02.10

审查员 张自童

权利要求书2页 说明书14页 附图12页

#### (54) 发明名称

A/D转换器

### (57) 摘要

当采样电容器 (Cs) 的第一端子连接到节点 (Ni)并且采样电容器的第二端子连接到模拟地 时,对输入信号Vin进行采样。当采样电容器的第 一端子连接到模拟地并且采样电容器的第二端 子连接到运算放大器(9)的反相输入端子时,执 行电荷转移操作。当运算放大器的输出被输入到 量化器(4)时,执行量化。通过基于量化结果将电 荷减法单元(6)减去在积分电容器(Cf1,Cf2)中 累积的电荷的减法运算重复预定次数来生成最 高有效位。在生成最高有效位之后,当通过放大 与积分电容器中剩余电荷相对应的电压来提供 的电压被输入到子A/D转换器(7)时,生成最低有 四 效位。最高有效位和最低有效位之和作为输出信 号(DOUT)输出。在生成最高有效位之后,与子A/D 转换器(7)中的A/D转换并行地执行积分电容器 的电荷的初始化、用于下一次A/D转换的电荷转 移操作以及最高有效位的生成。

1.一种A/D转换器,用于将作为输入信号施加的模拟信号转换为数字值,所述A/D转换器包括:

采样电容器(Cs,Csp,Csm),用于对所述模拟信号进行采样;

积分器 (3,23),包括运算放大器 (9,29) 和在所述运算放大器的第一输入端子和输出端子之间提供的积分电容器 (Cf1,Cf2,Cf1p,Cf1m,Cf2p,Cf2m);

量化器(4,24),用于输出通过对所述运算放大器的输出信号进行量化而提供的量化结果:

电荷减法单元(6,26),包括D/A转换器(10,10p,10m)和DAC电容器(Cd,Cdp,Cdm),所述D/A转换器基于所述量化结果确定用于减去所述积分电容器的电荷的DAC电压,所述DAC电容器用于存储与所述DAC电压相对应的电荷;以及

子A/D转换器(7,27,51,61,71,81),与所述量化器并联连接到所述运算放大器的输出端子,并且在其输入级具有采样和保持配置,

其中

当所述采样电容器的第一端子连接到所述模拟信号的输入节点(Ni,Nip,Nim),并且所述采样电容器的第二端子连接到所述A/D转换器中的模拟地时,对所述模拟信号进行采样;

当所述采样电容器的所述第一端子连接到模拟地,并且所述采样电容器的所述第二端 子连接到所述运算放大器的所述第一输入端子时,执行用于将所述电荷从所述采样电容器 转移到所述积分电容器的电荷转移操作;

通过将所述运算放大器的所述输出信号输入到所述量化器来执行量化;

通过重复减法运算预定次数来生成所述数字值的最高有效位,在所述减法运算中,所述电荷减法单元基于所述量化结果减去所述积分电容器中累积的电荷;

在生成所述最高有效位之后,当通过放大与所述积分电容器中剩余的电荷相对应的电压来提供的电压被输入到所述子A/D转换器时,生成所述数字值的最低有效位;

将所述最高有效位和所述最低有效位之和作为所述数字值输出,

在生成所述最高有效位之后,与所述子A/D转换器中的所述A/D转换并行地执行所述积分电容器的电荷的初始化、以及用于下一次A/D转换的电荷转移操作和用于下一次A/D转换的最高有效位的生成,并且

与通过所述采样电容器对所述模拟信号的所述采样并行地执行所述最高有效位的生成。

2.根据权利要求1所述的A/D转换器,其中:

所述放大器具有差分输入配置,所述差分输入配置用于转换彼此互补的两个模拟信号 之间的差;并且

当所述电荷从所述采样电容器转移到所述积分电容器时,所述采样电容器的所述第一端子连接到所述两个模拟信号的公共电压,而不是连接到所述模拟地。

3.根据权利要求1所述的A/D转换器,其中:

所述放大器具有差分输入配置,所述差分输入配置用于转换彼此互补的两个模拟信号 之间的差;并且

当所述电荷从对所述模拟信号中的一个进行采样的所述采样电容器中的一个转移到所述积分电容器时,所述采样电容器中的所述一个的第一端子连接到所述模拟信号中的另

- 一个的输入节点,而不是连接到所述模拟地。

- 4.根据权利要求1所述的A/D转换器,其中:

所述放大器具有差分输入配置,所述差分输入配置用于转换彼此互补的两个模拟信号 之间的差;并且

当所述电荷从对所述模拟信号中的一个进行采样的所述采样电容器中的一个转移到 所述积分电容器时,所述采样电容器中的所述一个的第一端子连接到对所述模拟信号中的 另一个进行采样的所述采样电容器中的另一个的第一端子,而不是连接到所述模拟地。

5.根据权利要求1至4中的任一项所述的A/D转换器,其中:

所述子A/D转换器(51,71,81)被配置为循环型A/D转换器。

6.根据权利要求1至4中的任一项所述的A/D转换器,其中:

所述子A/D转换器(61)被配置为双速循环型A/D转换器,其在操作时钟的每个周期中执行两次所述A/D转换。

7.根据权利要求5所述的A/D转换器,其中:

所述子A/D转换器(71)被配置为通过使用所述量化器来执行所述量化。

8.根据权利要求5所述的A/D转换器,其中:

所述子A/D转换器(81)具有放大功能,所述放大功能用于放大与所述积分电容器中剩余的电荷相对应的电压。

# A/D转换器

## 技术领域

[0001] 本发明涉及一种用于将作为输入信号的模拟信号转换为数字值的A/D转换器。

## 背景技术

[0002] 常规地,提出了各种A/D转换器。例如,JP 2017-50776A(专利文献1)公开了一种A/D转换器,该A/D转换器被配置为通过使用积分电容器对输入信号进行采样并根据比较器的输出从该积分电容器中循序地减去电荷来生成A/D转换结果。US 6,999,014(专利文献2)公开了一种通过模拟量化器来改变反馈量的增量 Δ 型A/D转换器。

[0003] 在专利文献1中公开的配置中,不能输入超过放大器的操作范围的输入电压。出于这个原因,不允许将电源电压降低到输入电压以下,并且因此不能通过降低电压来加速处理。此外,在专利文献2中公开的配置中,在用在差分配置中时,除非输入信号的公共端子和转换器的公共端子不匹配,否则放大器的输入公共端子改变。处于这个原因,使得要输入的信号受到限制。因此,没有既实现高速处理又允许宽范围的输入信号的常规A/D转换器。

#### 发明内容

[0004] 本发明解决了上述问题,并且目的是提供一种能够实现加速处理并且扩宽输入电压范围的A/D转换器。

[0005] 提供了根据本发明的A/D转换器以用于将作为输入信号的模拟信号转换为数字值,并且其包括采样电容器、积分器、量化器、电荷减法单元和子A/D转换器。积分器包括运算放大器和在该运算放大器的第一输入端子和输出端子之间提供的积分电容器。量化器输出通过对运算放大器的输出信号进行量化而提供的量化结果。电荷减法单元包括D/A转换器和DAC电容器,D/A转换器基于该量化结果来确定用于减去积分电容器的电荷的DAC电压,DAC电容器存储与该DAC电压相对应的电荷。子A/D转换器与量化器并联连接到运算放大器的输出端子,并在其输入级具有采样和保持结构。

[0006] 具有上述配置的A/D转换器执行以下操作。即,当采样电容器的第一端子连接到模拟信号的输入节点,并且采样电容器的第二端子连接到A/D转换器中的模拟地时,对模拟信号进行采样。当采样电容器的第一端子连接到模拟地,并且采样电容器的第二端子连接到运算放大器的第一输入端子时,由此执行将电荷从采样电容器转移到积分电容器的电荷转移操作。通过将运算放大器的输出输入到量化器来执行量化。

[0007] 通过重复减法运算来生成数字值的最高有效位,在该减法运算中,电荷减法单元基于量化结果减去积分电容器中累积的电荷预定次数。在生成最高有效位之后与积分电容器中剩余的电荷相对应的电压被放大并被输入到子A/D转换器,从而生成数字值的最低有效位。最高有效位和最低有效位之和作为数字值输出。在上述配置中,在生成所述最高有效位之后,与子A/D转换器中的A/D转换并行地初始化积分电容器的电荷,与下一次A/D转换相关的电荷转移操作以及生成最高有效位。

[0008] 在这种情况下,采样电容器不与积分电容器共享,而是单独地提供积分电容器。因

此,根据上述配置,可以以采样电容器和积分电容器之比来放大和衰减输入信号,并且可以实现宽的输入范围。在上述配置中,通过执行如上所述的操作,即流水线操作,提高了信号处理操作速度。因此,根据上述配置,可以提供优异的效果,可以实现处理的加速和输入范围的扩展。

## 附图说明

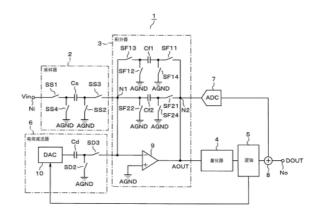

[0009] 图1是示意性地示出根据第一实施例的A/D转换器的配置的电路图:

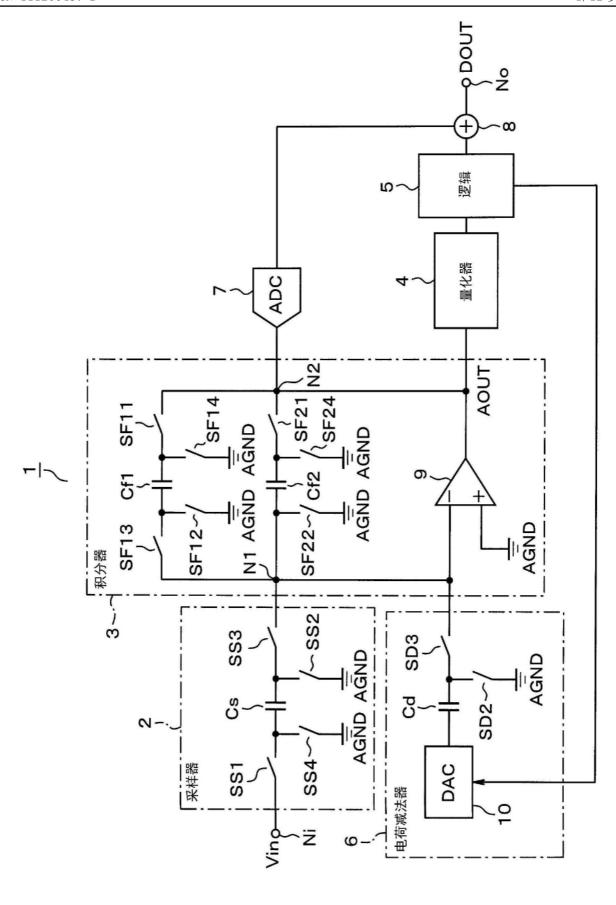

[0010] 图2是示意性地示出第一实施例中的每个电路单元的操作状态的时序图;

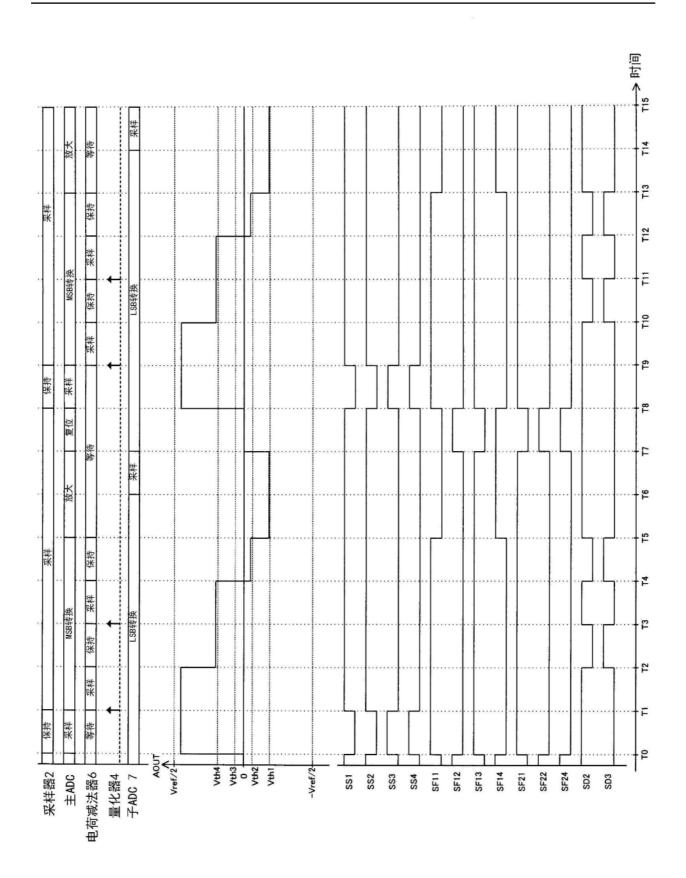

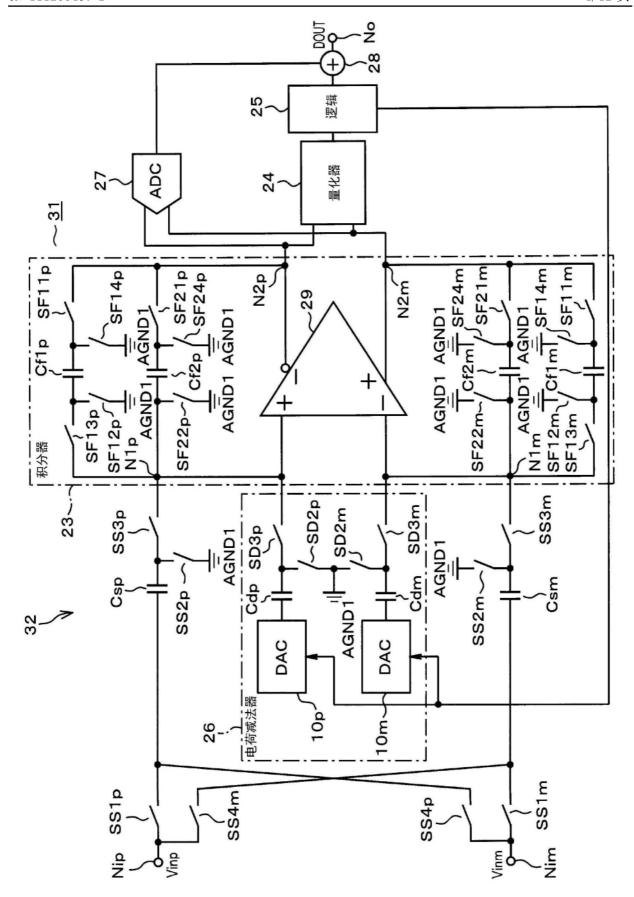

[0011] 图3是示意性地示出根据第二实施例的A/D转换器的配置的电路图;

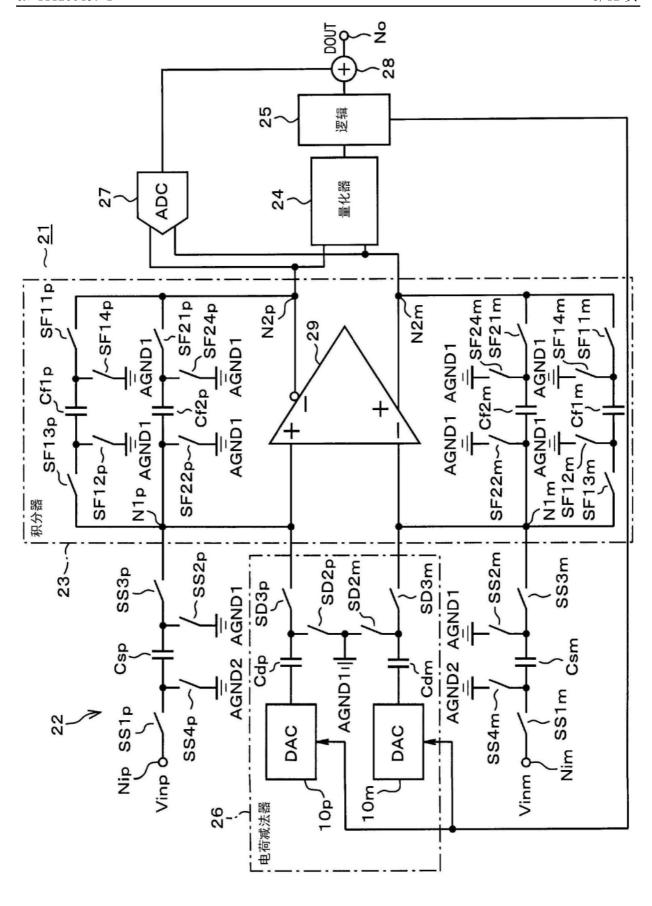

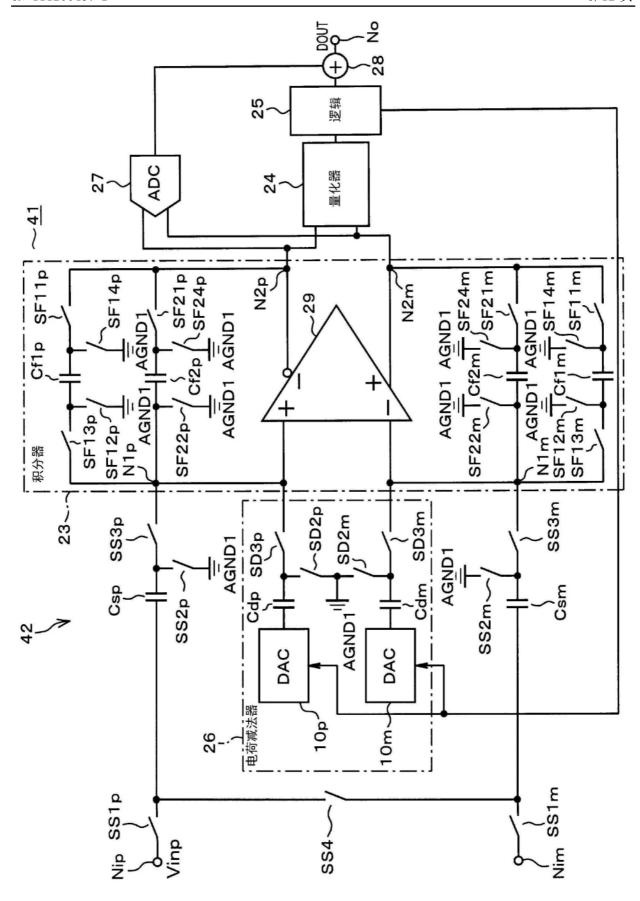

[0012] 图4是示意性地示出根据第三实施例的A/D转换器的配置的电路图;

[0013] 图5是示意性地示出根据第四实施例的A/D转换器的配置的电路图;

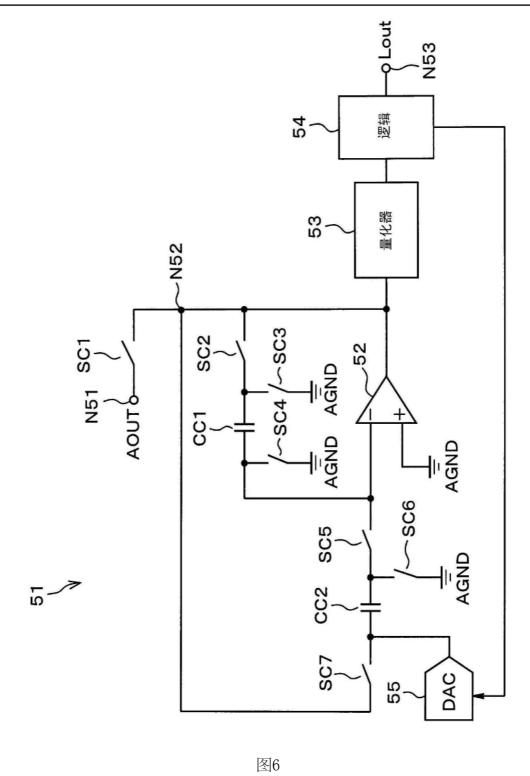

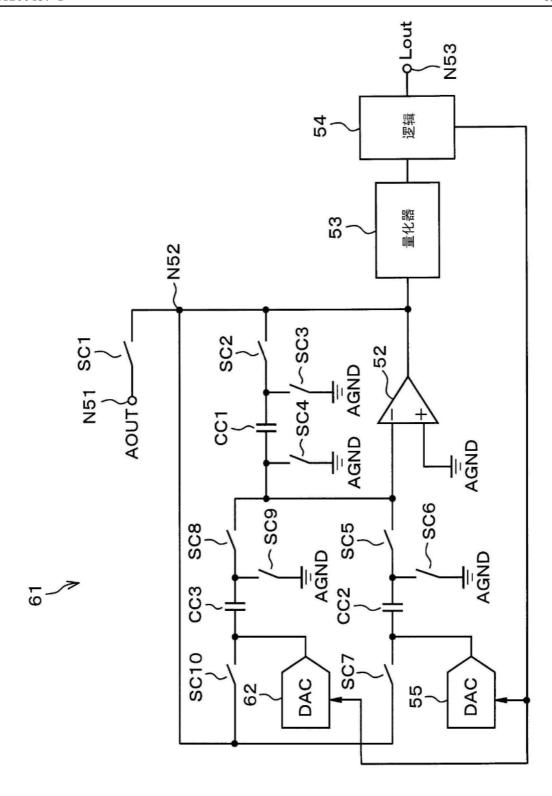

[0014] 图6是示意性地示出根据第五实施例的子A/D转换器的第一配置示例的电路图;

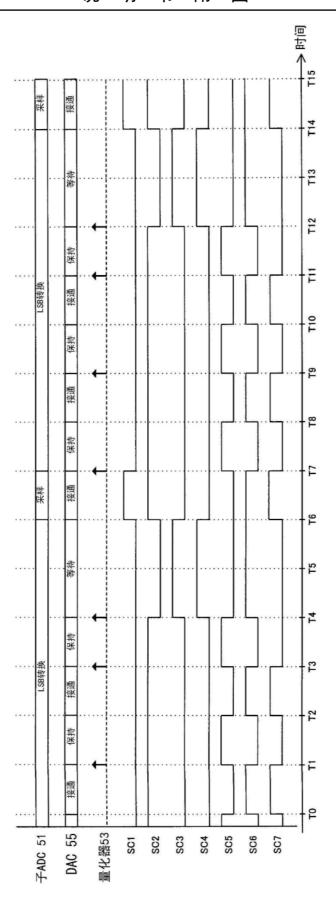

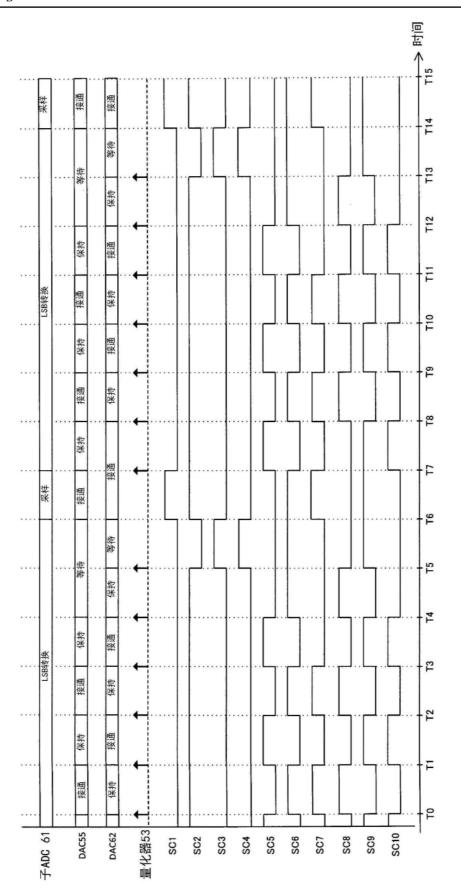

[0015] 图7是示意性地示出第一配置示例的子A/D转换器中的每个电路单元的操作状态的时序图;

[0016] 图8是示意性示出根据第五实施例的子A/D转换器的第二配置示例的电路图;

[0017] 图9是示意性地示出第二配置示例的子A/D转换器中的每个电路单元的操作状态的时序图:

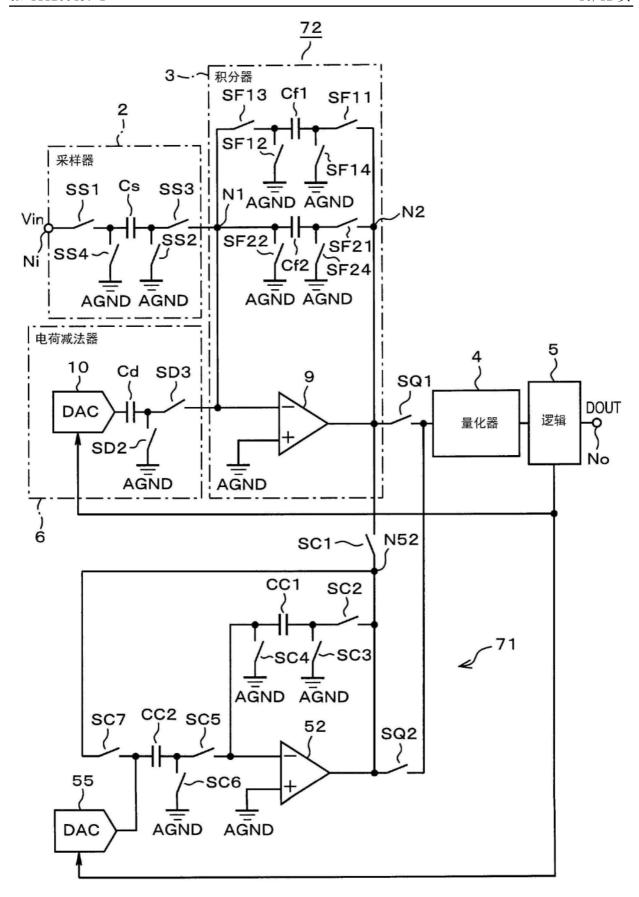

[0018] 图10是示意性地示出应用了根据第五实施例的第三配置示例的子A/D转换器的A/D转换器的配置的电路图;

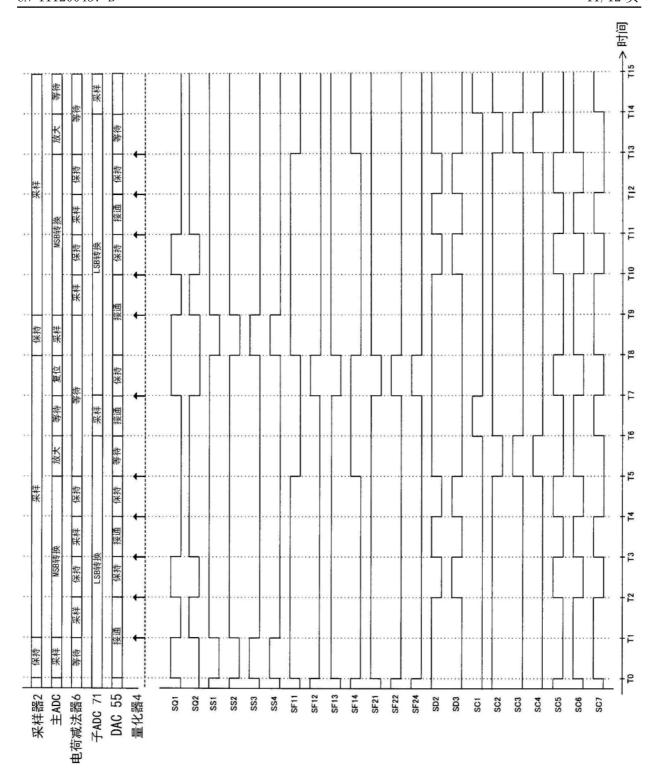

[0019] 图11是示意性地示出应用了第三配置示例的子A/D转换器的A/D转换器中的每个电路单元的操作状态的时序图;以及

[0020] 图12是示意性示出根据第五实施例的子A/D转换器的第四配置示例的电路图。

#### 具体实施方式

[0021] 在下文中,将参考附图描述多个实施例。在下面描述的各个实施例中,由相同的符号和参考附图标记表示基本相同的配置,从而简化了重复性的描述。

[0022] (第一实施例)

[0023] 将参照图1和图2描述第一实施例。

[0024] 图1所示的A/D转换器1被配置为将作为模拟电压的输入信号Vin转换为作为数字值的输出信号DOUT。A/D转换器1包括采样器2、积分器3、量化器4、逻辑电路5、电荷减法单元6、子A/D转换器7、加法器8等。在下文中,将A/D转换器简称为ADC。

[0025] 采样器2包括用于采样输入信号Vin的采样电容器Cs、开关SS1、SS2、SS3、SS4等。开关SS1至SS4的接通/断开状态由开关控制电路(未示出)控制。应当指出,稍后描述的开关的每个接通/断开状态也由开关控制电路控制。采样电容器Cs的第一端子通过开关SS1连接到输入节点Ni,输入信号Vin被施加到输入节点Ni,并且采样电容器Cs的第一端子通过开关SS4连接到ADC 1中的模拟地。模拟地被简单表示为和称为AGND。

[0026] AGND是ADC 1中的参考电势,并且不一定为0V。采样电容器Cs的第二端子通过开关SS2连接到AGND,并且通过开关SS3连接到积分器3的节点N1。

[0027] 在如上所述的配置的采样器2中,当开关SS1和SS2接通并且开关SS3和SS4断开时,

采样电容器Cs的第一端子连接到输入节点Ni,并且采样电容器Cs的第二端子连接到AGND。结果,采样器2执行用于对输入信号Vin进行采样的采样操作。

[0028] 此外,当开关SS1和SS2断开并且开关SS3和SS4接通时,采样电容器Cs的第一端子连接到AGND,并且采样电容器Cs的第二端子连接到积分器3的节点N1。结果,在采样器2中,执行将采样电容器Cs的电荷从采样电容器Cs转移到积分器3的电荷转移操作。

[0029] 积分器3包括运算放大器(以下称为0P放大器)9、积分电容器Cf1和Cf2、开关SF11、SF12、SF13、SF14、SF21、SF22和SF24。与0P放大器9的第一输入端子相对应的反相输入端子连接到节点N1。即,采样电容器Cs的第二端子通过开关SS3连接到0P放大器9的反相输入端子。0P放大器9的同相输入端子连接到AGND。

[0030] 积分电容器Cf1的第一端子通过开关SF13连接到节点N1,并且通过开关SF12连接到AGND。积分电容器Cf1的第二端子通过开关SF11连接到节点N2,并且通过开关SF14连接到AGND。节点N2连接到0P放大器9的输出端子。

[0031] 积分电容器Cf2的第一端子连接到节点N1,并通过开关SF22连接到AGND。积分电容器Cf2的第二端子通过开关SF21连接到节点N2,并且通过开关SF24连接到AGND。如上所述,积分电容器Cf1和Cf2彼此并联连接,并且两者都设置在0P放大器9的反相输入端子和输出端子之间。

[0032] 量化器4接收积分器3的输出,即0P放大器9的输出信号A0UT。量化器4对作为模拟值的输出信号A0UT进行量化,并输出作为量化的结果的量化结果。量化器4的输出被输入到逻辑电路5。逻辑电路5将量化器4的量化结果输出到电荷减法单元6。此外,逻辑电路5基于量化器4的量化结果生成并输出与输出信号D0UT的最高有效位相对应的数字值,最高有效位是输出信号D0UT中的高位数字位。

[0033] 电荷减法单元6包括D/A转换器10、DAC电容器Cd、开关SD2和SD3等。在下文中,D/A转换器10缩写为DAC 10。DAC 10基于从逻辑电路5提供的量化结果来确定要从积分电容器Cf1和Cf2减去的电荷量。即,DAC10确定用于减去积分电容器Cf1和Cf2中累积的电荷的DAC电压。DAC 10是三电平DAC,其具有设置为例如AGND的Vm、设置为高于AGND的电势的Vrefp、和设置为低于AGND的电势作为参考电压的Vrefm。在AGND为0V的情况下,Vrefp和Vrefm被设置为绝对值相同且符号相反。

[0034] DAC电容器Cd的第一端子连接到DAC 10的输出端子。DAC电容器Cd的第二端子通过 开关SD2连接到AGND,并且通过开关SD3连接到积分器3的节点N1。在这样的配置中,当开关 SD3断开并且开关SD2接通时,执行在DAC电容器Cd中累积与DAC电压相对应的电荷的采样操作。即,DAC电容器Cd根据从DAC 10输出的DAC电压来累积电荷。

[0035] 在电荷累积在DAC电容器Cd中的状态下,当开关SD2断开并且开关SD3接通时,DAC 10输出与量化器4的量化结果相对应的DAC电压。此时,执行电荷转移操作,在其中与采样时段中的DAC电压和保持时段中的DAC电压之间的电势差相对应的电荷被转移到积分器3的积分电容器Cf1和Cf2。即,电荷减法单元6执行这样的电荷转移操作,从而从积分电容器Cf1和Cf2中累积的电荷中减去基于量化结果的电荷。采样时段是指在电荷减法单元6中执行采样操作的时段。保持时段是指在电荷减法单元6中执行保持操作的时段。

[0036] 子ADC 7的输入端子连接到积分器3的节点N2。即,子ADC 7与量化器4并联连接到积分器3的0P放大器9的输出端子。子ADC 7生成并输出与输出信号DOUT的最低有效位相对

应的数字值,最低有效位是输出信号DOUT中的低位数字位。从子ADC 7输出的数字值与从逻辑电路5输出的数字值一起被输入到加法器8。加法器8生成通过将数字值相加而生成的输出信号DOUT。输出信号DOUT通过节点No输出。作为子ADC 7,可以采用在其输入级具有采样和保持结构的通用ADC。

[0037] 如上所述,通过改变常规ADC(例如,JP 2017-50776A)的采样配置来提供本实施例的ADC 1。因此,由于除与采样有关的操作以外的操作与常规ADC相似,因此省略了其详细描述,因为它是常规的。

[0038] 将参考图2的时序图描述如上配置的第一实施例的操作。此处描述的操作仅是示例,并且可以任意地设置各种特定的数值,例如每个阶段中的循环数、最高有效位的数目和最低有效位的数目。在图2中,将包括用于生成输出信号DOUT的包括最高有效位的积分器3的配置称为主ADC。

[0039] 在图2等的时序图中,附有每个开关的符号的部分处的信号指示相应开关的接通/断开状态。具体地,信号处于高电平的时段代表相应的开关的接通时段,并且信号处于低电平的时段代表相应的开关的断开时段。

[0040] 在这种情况下,采样电容器Cs、积分电容器Cf1、Cf2和DAC电容器Cd具有满足以下等式(1)和(2)表示的关系的电容值。在以下等式中,Cs、Cf1、Cf2和Cd分别表示电容器Cs、Cf1、Cf2和Cd的电容值。

[0041]  $Cf1 = 2 \times Cd...(1)$

[0042]  $Cf2=6\times C_S\cdots (2)$

[0043] 在这种情况下,量化器4包括四个比较器,四个比较器输入0P放大器9的输出信号 AOUT以及四个阈值电压Vth1、Vth2、Vth3和Vth4。基于参考电压Vref生成上述阈值电压Vth1至Vth4。参考电压Vref和阈值电压Vth1至Vth4分别由以下等式(3)至(7)表示。

[0044] Vref=Vrefp-Vrefm...(3)

[0045]  $Vth1 = (-3/16) \times Vref \cdots (4)$

[0046]  $Vth2 = (-1/16) \times Vref...(5)$

[0047]  $Vth3 = (1/16) \times Vref...(6)$

[0048]  $Vth4 = (3/16) \times Vref...(7)$

[0049] 因此,在这种情况下,由DAC 10产生的积分电容器Cf1和Cf2的电荷的减法宽度,即 0P放大器9的输出信号AOUT的改变量被设置为五种值,其为 $(+1/4) \times Vref$ 、 $(-1/4) \times Vref$ 、 $(+1/8) \times Vref$ 、 $(-1/8) \times Vref$ 和0。

[0050] 由于在时间T0到时间T1的时段期间开关SS1和SS2断开并且开关SS3和SS4接通,所以采样器2执行电荷转移操作。在图2和其他图中,电荷转移操作被表示为保持。此外,在时间T0到时间T1的时段期间,开关SD3断开并且开关SD2接通。此时,DAC 10的输出端子在内部连接到Vm。因此,在从时间T0到时间T1的时段期间,电荷减法单元6处于复位状态,其中DAC电容器Cd被复位。在图2和其他图中,该复位状态被指示为"等待"。

[0051] 此外,在时间T0到时间T1的时段期间,开关SF12、SF14、SF22和SF24断开,并且开关SF11、SF13和SF21接通。从而,在积分器3中,积分电容器Cf1和Cf2并联连接在0P放大器9的反相输入端子和输出端子之间。因此,在从时间T0到时间T1的时段期间,主ADC的操作是采样操作,其中从采样电容器Cs转移的电荷被累积在积分电容器Cf1和Cf2中。在图2和其他附

图中,采样操作被指示为"采样"。然后,在时间T1由量化器4执行量化。在图2和其他图中,执行量化的时机由向上的箭头指示。

[0052] 此外,在从时间T0到时间T6的时段期间,子ADC 7执行A/D转换操作,以用于生成与输出信号D0UT的最低有效位相对应的数字值。子ADC7进行的A/D转换操作包括诸如复位之类的一系列操作。在图2和其他图中,子ADC 7进行的A/D转换操作被指示为"LSB转换"。由于在从时间T1到时间T8的时段期间开关SS3和SS4断开并且开关SS1和SS2接通,所以采样器2执行采样操作。

[0053] 此外,在从时间T1到时间T5的时段期间,主ADC执行A/D转换操作,与用于生成与输出信号D0UT的最高有效位相对应的数字值。在图2和其他图中,由主ADC进行的A/D转换操作被指示为"MSB转换"。具体地,在从时间T1到时间T5的时段期间,开关SF12、SF13、SF14、SF21、SF22和SF24处于与从时间T0到时间T1的时段期间相同的状态,因此积分电容器Cf1和Cf2并联连接在0P放大器9的反相输入端子和输出端子之间。

[0054] 在从时间T1到时间T2的时段期间,开关SD2和SD3处于与从时间T0到时间T1的时段期间相同的状态,但是DAC 10输出基于量化器4在时间T1输出的量化结果而确定的DAC电压。因此,在从时间T1到时间T2的时段期间,电荷减法单元6执行采样操作,以用于在DAC电容器Cd中累积与DAC电压相对应的电荷。

[0055] 随后,在从时间T2到时间T3的时段期间,开关SD2断开并且开关SD3接通,并且DAC 10输出基于量化器4在时间T1输出的量化结果而确定的DAC电压。因此,通过电荷减法单元6 执行电荷转移操作,并且从而,执行用于减去累积在积分电容器Cf1和Cf2中的电荷的减法运算。因此,在时间T2,在上述减法运算中,输出信号AOUT根据减法宽度而改变。然后,在时间T3由量化器4执行量化。

[0056] 在从时间T3到时间T4的时段期间,开关SD2和SD3处于与从时间T1到时间T2的时段期间相同的状态,并且DAC 10输出基于量化器4在时间T3输出的量化结果而确定的DAC电压。因此,在从时间T3到时间T4的时段期间,电荷减法单元6与从时间T1到时间T2的时段期间一样执行采样操作。随后,在从时间T4到时间T5的时段期间,开关SD2和SD3处于与从时间T2到时间T3的时段期间相同的状态。DAC 10输出基于量化器4在时间T3输出的量化结果而确定的DAC电压,并且通过电荷减法单元6执行电荷转移操作并且因此执行减法运算。因此,在时间T4,输出信号AOUT根据上述减法运算中的减法宽度而改变。

[0057] 以这种方式,电荷减法单元6基于量化器4的量化结果重复减法运算预定次数,以用于减去累积在积分电容器Cf1和Cf2中的电荷。减法单元6因而生成与输出信号DOUT的最高有效位相对应的数字值。在这种情况下,减法运算执行两次,从而生成与3位相对应的数字值。

[0058] 在从时间T5到时间T7的时段内,主ADC执行放大操作,以用于放大积分电容器Cf1和Cf2中剩余的电荷。在图2和其他附图中,放大操作被表示为"放大"。此外,在从时间T5到时间T7的时段中,开关SF11、SF12、SF22和SF24断开并且开关SF13、SF14和SF21接通。

[0059] 结果,积分电容器Cf1和Cf2串联连接在节点N2和AGND之间。结果,在生成最高有效位之后在积分电容器Cf1中剩余的所有电荷都被转移到积分电容器Cf2并被输入到子ADC7。因此,在时间T5,输出信号AOUT根据上面描述的放大操作中的积分电容器Cf1和Cf2的电容之比而改变。然后,在从时间T6到时间T7的时段期间,子ADC7执行用于对输入电荷进行

采样的采样操作。此外,在从时间T7到时间T14的时段期间,子ADC 7执行A/D转换操作,以用于生成与输出信号DOUT的最低有效位相对应的数字值。

[0060] 在从时间T7到时间T8的时段期间,主ADC执行重置操作以初始化积分电容器Cf1和Cf2的电荷。在图2和其他图中,复位操作被表示为"复位"。具体地,在从时间T7到时间T8的时段期间,开关SF11、SF13和SF21断开并且开关SF12、SF14、SF22和SF24接通。结果,积分电容器Cf1和Cf2的两个端子都连接到AGND,并且积分电容器Cf1和Cf2的电荷被初始化。

[0061] 此外,在从时间T5到时间T8的时段期间,开关SD3断开并且开关SD2接通,使得DAC 10的输出端子在内部连接到Vm。因此,在从时间T5到时间T8的时段期间,电荷减法单元6处于DAC电容器Cd被复位的复位状态。在时间T8之后,重复与上述从时间T0到时间T8的时段的操作相似的操作。

[0062] 如上所述,在根据本实施例的ADC 1中执行以下操作。即,通过将采样电容器Cs的第一端子连接到输入节点Ni并且将采样电容器Cs的第二端子连接到AGND,来对输入电压Vin进行采样。另外,通过将采样电容器Cs的第一端子连接到AGND并且将采样电容器Cs的第二端子连接到0P放大器9的反相输入端子,将电荷从采样电容器Cs转移到积分电容器Cf1和Cf2。通过将0P放大器9的输出输入到量化器4来执行量化。

[0063] 此外,由电荷减法单元6生成与输出信号DOUT的最高有效位相对应的数字值,电荷减法单元6基于量化结果将减去在积分电容器Cf1和Cf2中累积的电荷的减法运算重复预定次数。此外,通过在生成最高有效位之后,将在积分电容器Cf1中剩余的所有电荷转移到积分电容器Cf2,根据电容之比对输出信号AOUT进行放大,和将积分电容器Cf2中累积的电荷输入到子ADC7,来生成与输出信号的最低有效位相对应的数字值。这些数字值的和作为输出信号DOUT从输出节点No输出。此外,在上述配置中,在最高有效位的生成之后,与子A/D转换器7中的A/D转换并行执行积分电容器Cf1和Cf2的电荷的初始化、与下一次A/D转换相关的电荷转移操作以及最高有效位的生成。

[0064] 在本实施例的ADC 1中,单独地提供采样电容器Cs,并且采样电容器Cs不与积分电容器共享。因此,根据上述配置,可以以采样电容器Cs的电容与积分电容器Cf1和Cf2的并联组合电容之比来放大和衰减输入信号Vin,并且可以扩宽输入范围。即,根据上述配置,可以根据上述电容之比,将施加在0P放大器9的端子之间的电压设定为任意的电压值,而与输入信号Vin的电平无关。因此,根据上述配置,可以输入具有较高电压值的信号作为输入信号Vin。在上述配置中,通过执行上述操作,即流水线操作,提高了操作速度。因此,根据上述配置,可以提供优异的效果,可以实现对处理的加速和对输入范围的扩展。

[0065] 在上述配置中,如上所述,采样电容器Cs不与积分电容器共享,而是单独地提供。因此,可以在主ADC的A/D转换操作期间执行由采样器2进行的采样操作。因此,与采样电容器与积分电容器共享的配置相比,根据上述配置可以延长用于执行采样操作的采样周期。因此,根据上述配置,即使在输出输入信号Vin的电路或传感器的电流供应能力较低的情况下,也能够在期望的采样时段期间可靠地完成采样操作,即由输入信号Vin对采样电容器Cs的充电。即,根据上述配置,放宽了对输出输入信号Vin的电路或传感器的输出阻抗的要求。

[0066] (第二实施例)

[0067] 下面将参考图3描述第二实施例。

[0068] 如图3所示,本实施例的ADC 21具有第一实施例的ADC 1的差分配置。即,ADC 21具

有差分输入配置,该差分输入配置将作为彼此互补的两个模拟信号的输入信号Vinp和Vinm之间的差转换为作为数字值的输出信号DOUT。

[0069] ADC 21包括采样器22、积分器23、量化器24、逻辑电路25、电荷减法单元26、子ADC 27、加法器28等。采样器22相对于采样器2具有差分配置,并且包括与采样器2中所包括的配置相似的两组配置。在采样器22中所包括的配置中,与输入信号Vinp相对应的配置在符号的末尾用"m"指示,并且与输入信号Vinm相对应的配置在符号的末尾用"m"指示。

[0070] 积分器23具有与积分器3不同的差分配置,并且包括具有完全差分配置的0P放大器29来代替0P放大器9。除了0P放大器9,积分器23还具有与积分器3的配置相同的两组配置。在积分器23中所包括的配置中,与输入信号Vinp相对应的配置在符号的末尾用"p"指示,并且与输入信号Vinm相对应的配置在符号末尾用"m"指示。0P放大器29具有用于将输出共模电压调整为任意的恒定值的共模反馈功能。在以下描述中,共模反馈缩写为CMFB。

[0071] 量化器24接收积分器23的输出,即,从0P放大器29输出的差分信号。量化器24对这些差分信号之间的差进行量化,并输出量化结果。量化器24的输出被输入到逻辑电路25。逻辑电路25将量化器24的量化结果输出到电荷减法单元26。此外,逻辑电路25基于量化器24的量化结果生成并输出与输出信号DOUT的最高有效位相对应的数字值。

[0072] 电荷减法单元26相对于电荷减法单元6具有差分配置,并且包括两组配置,每组配置与电荷减法单元6的配置相似。在电荷减法单元26中包括的配置中,与输入信号Vinp相对应的配置在符号的末尾用"p"指示,并且与输入信号Vinm相对应的配置在符号的末尾用"m"指示。

[0073] 子ADC 27的输入端子连接到积分器23的节点N2p和N2m。即,子ADC 27与量化器24并联连接到积分器23的0P放大器29的输出端子。子ADC 27生成并输出与输出信号DOUT的最低有效位相对应的数字值。从子ADC 27输出的数字值与从逻辑电路25输出的数字值一起被输入到加法器28。加法器28生成通过将数字值相加而生成的输出信号DOUT。

[0074] 在图3和以下描述,作为ADC 21中的参考电势的模拟地被称为AGND1。在这种情况下,采样电容器Csp和Csm的第一端子分别经由开关SS4p和SS4m连接到两个输入信号Vinp和Vinm的公共电压而不是AGND1。在图在图3和以下描述中,上述公共电压被称为AGND2。

[0075] 在如上所述的配置的采样器22中,当开关SS1p和SS2p接通并且开关SS3p和SS4p断开时,采样电容器Csp的第一端子连接到输入节点Nip,并且采样电容器Csp的第二端子连接到AGND1。结果,采样器22执行用于对输入信号Vinp进行采样的采样操作。应当注意,对输入信号Vinm的采样操作类似于对输入信号Vinp的采样操作,并且将省略其描述。

[0076] 此外,当开关SS1p和SS2p断开并且开关SS3p和SS4p接通时,采样电容器Csp的第一端子连接到AGND2,并且采样电容器Csp的第二端子连接到积分器23的节点N1p。结果,在采样器22中,执行将电荷从采样电容器Csp转移到积分器23的积分电容器Cf1p和Cf2p的电荷转移操作。

[0077] 应当注意,对输入信号Vinm的电荷转移操作类似于对输入信号Vinp的电荷转移操作,并且将省略其描述。因此,在上述配置中,当电荷从采样电容器转移到积分电容器时,采样电容器的第一端子连接到作为两个输入信号Vinp和Vinm的公共电压的AGND2,而不是连接到AGND1。

[0078] 根据上述配置,由于以下原因,0P放大器29的输入公共电压不变。首先,从电荷守

恒定律和CMFB的功能推导出以下等式(21)、(22)和(23)。在以下等式中,Cs指示采样电容器Csp和Csm的电容,Vinp和Vinm指示采样时采样电容器Csp和Csm的第一端子的电压,Vs1p和Vs1m指示采样时采样电容器Csp和Csm的第二端子的电压,并且Vs2p和Vs2m指示电荷转移时采样电容器Csp和Csm的第一端子的电压,并且Vx指示电荷转移时采样电容器Csp和Csm的第二端子的电压。

[0079] Cf指示积分电容器Cf1p和Cf2p的并联组合电容以及积分电容器Cf1m和Cf2m的并联组合电容,Vf1p和Vf2p指示采样时积分电容器Cf1p和Cf2p的第一端子和第二端子的电压,并且Vf1m和Vf2m指示采样时积分电容器Cf1m和Cf2m的第一端子和第二端子的电压。此外,Voutm指示电荷转移时0P放大器29的同相输出端子的电压,Voutp指示电荷转移时0P放大器29的反相输出端子的电压,并且Vcm指示AGND1的电压。在这种情况下,CMFB是可调节的,以使得0P放大器29的输出公共电压变为AGND1。

[0080]  $C_S(V_{inp}-V_{sip})+C_f(V_{f2p}-V_{f1p})=C_S(V_{s2p}-V_x)+C_f(V_{outm}-V_x)\cdots(21)$

[0081]  $Cs(Vinm-Vsim)+Cf(Vf2m-Vf1m) = Cs(Vs2m-Vx)+Cf(Voutp-Vx)\cdots(22)$

[0082] (Voutp+Voutm)/2=Vcm...(23)

[0083] 求解上面的等式(21)至(23)中的Vx,推导出下面的等式(24)。

[0084]  $VX = Cf \left( Vcm - Cs \left( Vinp + Vinm \right) / 2Cf - \left( Vf2p + Vf2m - Vf1P - Vf1m \right) / 2 \right)$

[0085]  $+C_{S}(V_{S}1p+V_{S}1m+V_{S}2p+V_{S}2m)/(C_{S}+C_{f})$

[0086] =  $CfxVcm/(Cs+Cf) - Cs\{(Vinp+Vinm)/2\}/(Cs+Cf)$

[0087]  $+Cs\{(Vs1p+Vs1m)/2+(Vs2p+Vs2m)/2\}/(Cs+Cf)$

[0088]  $-Cf\{(Vf2p+Vf2m)/2-(Vf1p+Vf1m)/2\}/(Cs+Cf)...(24)$

[0089] 为了使上面的等式 (24) 中的电压Vx与输出公共电压Vcm—致,即,建立Vx=Vcm,需要以下操作 (a) 和 (b) 。

[0090] (a) 在采样之前,通过将积分电容器(Cf1p,Cf1m,Cf2p,Cf2m)的两个端子都连接到 AGND1来复位积分电容器。

[0091] (b) 在采样期间,将采样电容器(Csp,Csm)的第二端子连接到AGND1,并且在电荷转移期间,将采样电容器的第一端子连接到AGND2。

[0092] 代替上述操作(b),可以执行以下操作(c)。

[0093] (c) 在采样期间,将采样电容器的第二端子连接到AGND2,并且在电荷转移期间,将采样电容器的第一端子连接到AGND1。

[0094] 然而,当对具有相对高的电压的输入信号Vinp和Vinm进行采样时,即在高电压采样的情况下,需要待连接到AGND2的开关具有高耐受电压。因此,优选采用操作(b)。

[0095] 如上所述,本实施例的ADC 21具有第一实施例的ADC 1的差分配置。因此,本实施例可以提供与第一实施例相同的操作和效果。如上所述,在本实施例的配置中,0P放大器29的输入公共电压是恒定的,而与输入信号Vinp和Vinm的电压电平无关,并且不波动。因此,根据本实施例,可以输入具有相对较高电压的输入信号Vinp和Vinm。此外,根据本实施例,ADC 21可以被配置有低压电路元件,并且结果,可以提高信号处理操作速度。

[0096] (第三实施例)

[0097] 下面将参考图4描述第三实施例。

[0098] 如图4所示,本实施例的ADC 31与第二实施例的ADC 21的不同之处在于,提供了采

样器32来代替采样器22。采样器32在开关SS4p和SS4m的布置上与采样器22不同。

[0099] 在这种情况下,采样电容器Csp的第一端子通过开关SS1p连接到输入节点Nip,并通过开关SS4p连接到输入节点Nim。此外,采样电容器Csm的第一端子通过开关SS1m连接到输入节点Nim,并且通过开关SS4m连接到输入节点Nip。

[0100] 在如上所述的配置的采样器32中,当开关SS1p和SS2p接通并且开关SS3p和SS4p断开时,采样电容器Csp的第一端子连接到输入节点Nip,而且采样电容器Csp的第二端子连接到AGND1。结果,采样器32执行用于对输入信号Vinp进行采样的采样操作。应当注意,对输入信号Vinm的采样操作类似于对输入信号Vinp的采样操作,并且将省略其描述。

[0101] 此外,当开关SS1p和SS2p断开并且开关SS3p和SS4p接通时,采样电容器Csp的第一端子连接到输入节点Nim,并且采样电容器Csp的第二端子连接到积分器23的节点N1p。结果,在采样器32中,执行将电荷从采样电容器Csp转移到积分器23的积分电容器Cf1p和Cf2p的电荷转移操作。

[0102] 此外,当开关SS1m和SS2m断开并且开关SS3m和SS4m接通时,采样电容器Csm的第一端子连接到输入节点Nip,并且采样电容器Csm的第二端子连接到积分器23的节点N1m。结果,在采样器32中,执行将电荷从采样电容器Csm转移到积分器23的积分电容器Cf1m和Cf2m的电荷转移操作。

[0103] 因此,在上述配置中,当电荷从其中对输入信号Vinp和Vinm中的一个进行采样的采样电容器转移到积分电容器时,该采样电容器的第一端子连接到输入信号Vinp和Vinm中的另一个的输入节点,而不是AGND1。即,在上述配置中,在电荷转移时,输入在差分之间进行切换。

[0104] 根据上述配置,由于以下原因,0P放大器29的输入公共电压不变。首先,从电荷守恒定律等推导出以下等式(31)、(32)、(33)和(34)。在以下等式中,Cs指示采样电容器Csp和Csm的电容,Vinp和Vinm指示输入信号Vinp和Vinm的电压,并且Vx指示电荷转移期间采样电容器Csp和Csm的第二端子的电压。

[0105] 此外,Cf指示积分电容器Cf1p和Cf2p的并联组合电容以及积分电容器Cf1m和Cf2m的并联组合电容,Voutm指示电荷转移时0P放大器29的同相输出端子的电压,Voutp指示电荷转移时0P放大器29的同相输出端子的电压。Vcm指示AGND1的电压,Voutcm指示0P放大器29的输出公共电压。在这种情况下,CMFB是可调节的,以使得0P放大器29的输出公共电压变为AGND1。

[0106]  $(Vinp-Vcm)Cs = (Vinm-Vx)Cs+(Voutp-Vx)Cf\cdots(31)$

[0107]  $V_{\text{outp}} = C_S (V_{\text{inp}} - V_{\text{inm}} - V_{\text{cm}} + V_X) / C_f + V_X \cdots (32)$

[0108]  $Voutm = Cs (Vinm-Vinp-Vcm+Vx) / Cf+Vx \cdots (33)$

[0109]  $Voutcm = (Voutp+Voutm)/2 = Cs(Vx-Vcm)/Cf+Vx\cdots(34)$

[0110] 由于CMFB的功能,输出公共电压Voutcm与AGND1的电压Vcm匹配,即,Voutcm=Vcm成立。然后,从上述等式(34)导出下面的等式(35)和(36)。

[0111]  $(1+C_S/C_f)V_X = (1+C_S/C_f)V_{cm} \cdots (35)$

[0112]  $V_X = V_{Cm} \cdots (36)$

[0113] 如上述等式(36)所示,0P放大器29的输入公共电压恒定在电压Vcm,而与输入信号 Vinp和Vinm的电压电平无关。

[0114] 如上所述,本实施例的ADC 31具有第一实施例的ADC 1的差分配置。因此,本实施例可以提供与第一实施例相同的操作和效果。如上所述,在本实施例的配置中,0P放大器29的输入公共电压是恒定的,而与输入信号Vinp和Vinm的电压电平无关,并且不波动。因此,根据本实施例,可以输入具有相对较高电压的输入信号Vinp和Vinm。

[0115] 此外,根据本实施例,ADC 31可以被配置有低压电路元件,并且结果,可以提高操作速度。此外,在本实施例中,与第二实施例的ADC 21不同,不必将采样电容器Csp和Csm连接到输入信号Vinp和Vinm的公共电压。因此,在本实施例中,不需要提供诸如用于单独地生成这样的公共电压的电源的配置,并且因此,与第二实施例相比,可以减小电路尺寸。

[0116] (第四实施例)

[0117] 下面将参考图5描述第四实施例。

[0118] 如图5所示,本实施例的ADC 41与第二实施例的ADC 21的不同之处在于,提供了采样器42来代替采样器22。采样器42与采样器22的不同之处在于,提供了开关SS4来代替开关SS4p和SS4m。

[0119] 在这种情况下,采样电容器Csp的第一端子通过开关SS1p连接到输入节点Nip,并且通过开关SS4连接到采样电容器Csm的第一端子。此外,采样电容器Csm的第一端子通过开关SS1m连接到输入节点Nim,并且通过开关SS4连接到采样电容器Csp的第一端子。

[0120] 在如上所述的配置的采样器42中,当开关SS1p和SS2p接通并且开关SS3p和SS4断开时,采样电容器Csp的第一端子连接到输入节点Nip,并且采样电容器Csp的第二端子连接到AGND1。结果,采样器42执行用于对输入信号Vinp进行采样的采样操作。注意,对输入信号Vinm的采样操作类似于对输入信号Vinp的采样操作,并且将省略其描述。

[0121] 此外,当开关SS1p和SS2p断开并且开关SS3p和SS4接通时,采样电容器Csp的第一端子连接到采样电容器Csm的第一端子,并且采样电容器Csp的第二端子连接到积分器23的节点N1p。结果,在采样器42中,执行其中电荷从采样电容器Csp转移到积分器23的积分电容器Cf1p和Cf2p的电荷转移操作。

[0122] 此外,当开关SS1m和SS2m断开并且开关SS3m和SS4接通时,采样电容器Csm的第一端子连接到采样电容器Csp的第一端子,并且采样电容器Csm的第二端子连接到积分器23的节点N1m。由此,在采样器42中,执行将电荷从采样电容器Csm转移到积分器23的积分电容器Cf1m和Cf2m的电荷转移操作。

[0123] 因此,在上述配置中,当电荷从对输入信号Vinp和Vinm中的一个进行采样的采样电容器转移到积分电容器时,该采样电容器的第一端子不连接到AGND1,而是连接到对输入信号Vinp和Vinm中的另一个进行采样的采样电容器的第一端子。即,在上述配置中,在电荷转移期间,输入在差分之间被短路。

[0124] 根据上述配置,由于以下原因,0P放大器29的输入公共电压不变。首先,从电荷守恒定律推导出以下等式(41)、(42)、(43)和(44)。在以下等式中,Cs指示采样电容器Csp和Csm的电容,Vinp和Vinm指示输入信号Vinp和Vinm的电压,Vi指示电荷转移时采样电容器Csp和Csm的电压,并且Vx指示电荷转移时采样电容器Csp和Csm的每个第二端子的电压。

[0125] 此外,Cf指示积分电容器Cf1p和Cf2p的并联组合电容以及积分电容器Cf1m和Cf2m的并联组合电容,Voutm指示电荷转移时0P放大器29的同相输出端子的电压,Voutp指示电荷转移时0P放大器29的反相输出端子的电压,Vcm指示AGND1的电压,Vincm指示0P放大器29

的输入公共电压,并且Voutcm指示OP放大器29的输出公共电压。在这种情况下,CMFB是可调节的,以使得OP放大器29的输出公共电压变为AGND1。

[0126]  $(Vinp-Vcm)Cs = (Vi-Vx)Cs+(Voutp-Vx)Cf\cdots(41)$

[0127]  $V_{\text{outp}} = C_{\text{S}} \left( V_{\text{inp}} - V_{\text{i}} - V_{\text{cm}} + V_{\text{X}} \right) / C_{\text{f}} + V_{\text{X}} \cdots (42)$

[0128]  $Voutm = Cs (Vinm-Vi-Vcm+Vx) / Cf+Vx \cdots (43)$

[0129] Voutcm=  $(Voutp+Voutm)/2=Cs(Vincm-Vi+Vx-Vcm)/Cf+Vx\cdots(44)$

[0130] 由于CMFB的功能,输出公共电压Voutcm与AGND1的电压Vcm一致,即,Voutcm=Vcm成立。然后,从上述等式(44)导出以下等式(45)。

[0131]  $(1+C_S/C_f)V_X = (1+C_S/C_f)V_{cm}-C_S(V_{inm}-V_i)/C_f\cdots(45)$

[0132] 由于ADC 41具有差分配置,因此假设采样电容器Csp和Csm两端的阻抗基本以差分方式匹配,则建立以下等式(46),从而建立以下等式(47)。

[0133] Vincm≈Vi···(46)

[0134]  $V_X \approx V_{CM} \cdots (47)$

[0135] 如上述等式(47)所示,0P放大器29的输入公共电压恒定在电压Vcm,而与输入信号 Vinp和Vinm的电压电平无关。

[0136] 如上所述,根据本实施例的ADC 41具有第一实施例的ADC 1的差分配置。因此,本实施例提供与第一实施例类似的操作和效果。如上所述,在本实施例的配置中,0P放大器29的输入公共电压是恒定的,而与输入信号Vinp和Vinm的电压电平无关,并且不波动。因此,根据本实施例,可以输入具有相对较高电压的输入信号Vinp和Vinm。

[0137] 此外,根据本实施例,构成ADC 41的每个电路元件可以被配置有低压元件,并且结果,可以提高操作速度。另外,在本实施例中,与第二实施例的ADC 21不同,不必将采样电容器Csp和Csm连接到输入信号Vinp和Vinm的公共电压。因此,在本实施例中,不需要提供诸如电源的配置以单独地生成这样的公共电压,并且因此,与第二实施例相比,可以减小电路尺寸。

[0138] (第五实施例)

[0139] 下面将参考图6至图12描述第五实施例。

[0140] 如上述实施例中所描述的,采用在其输入级具有采样和保持配置的通用ADC作为子ADC。在本实施例中,将描述可以应用于第一实施例的配置的子ADC的四个具体配置示例。

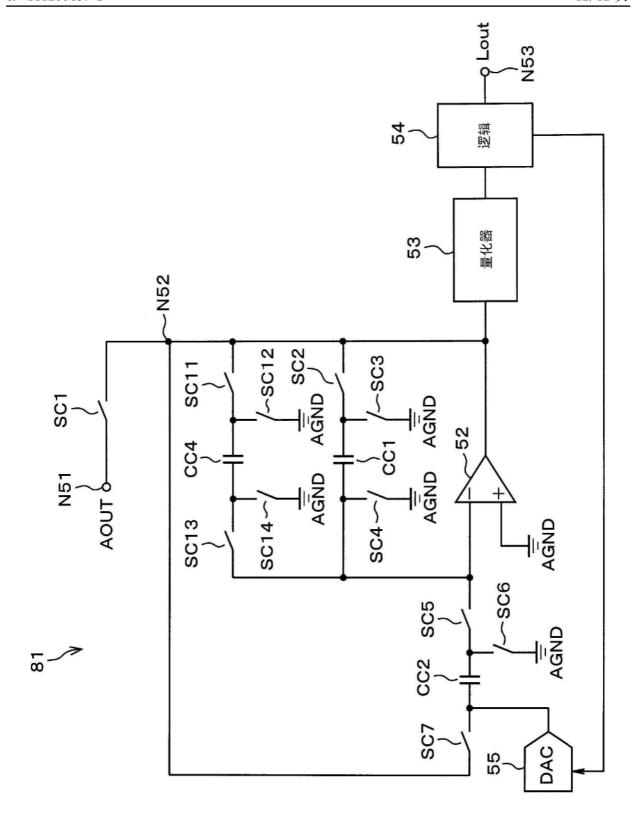

[0141] [1]第一配置示例

[0142] 图6中所示的第一配置示例的子ADC 51被配置为通用循环型ADC,其包括开关SC1 至SC7、电容器CC1、CC2、0P放大器52、量化器53、逻辑电路54、DAC 55等。开关SC1连接在输入 节点N51和节点N52之间,0P放大器9的输出信号AOUT被输入到输入节点N51。节点N2连接到 0P放大器9的输出端子。电容器CC1的第一端子连接到0P放大器52的反相输入端子,并且通过开关SC4连接到AGND。

[0143] 电容器CC1的第二端子通过开关SC2连接到节点N52,并且通过开关SC3连接到AGND。0P放大器52的同相输入端子连接到AGND。电容器CC2的第一端子通过开关SC7连接到节点N52。电容器CC2的第二端子通过开关SC5连接到0P放大器52的反相输入端子,并且通过开关SC6连接到AGND。

[0144] 0P放大器52的输出信号被输入到量化器53。量化器53对0P放大器52的输出信号进

行量化,并且输出作为量化的结果的量化结果。量化器53的输出被输入到逻辑电路54。逻辑电路54将量化器53的量化结果输出到DAC 55。此外,逻辑电路54基于量化器53的量化结果生成对应于输出信号DOUT的最低有效位的数字值Lout,并通过节点N53输出数字值Lout。DAC 55输出基于从逻辑电路54提供的量化结果而确定的DAC电压。DAC55的输出端子连接到电容器CC2的第一端子。

[0145] 如上所述的配置的子ADC 51的操作例如在图7的时序图中示出。虽然省略了该操作的详细描述,但是子ADC 51被配置为执行与通用循环型ADC相同的操作。循环型ADC具有诸如高操作速度和小尺寸的优点。因此,如果采用具有这种配置的子ADC 51作为第一实施例的子ADC 7,则可以提高处理速度并且可以减小电路尺寸。

[0146] [2]第二配置示例

[0147] 图8中所示的第二配置示例的子ADC 61被配置为通用双速循环型ADC。即,子ADC 61被配置为在操作时钟的每个周期中执行两次A/D转换的双速循环型ADC。在子ADC 61中,将开关SC8至SC10、电容器CC3和DAC 62添加到第一配置示例的子ADC 51。

[0148] 电容器CC3的第一端子通过开关SC10连接到节点N52。电容器CC3的第二端子通过开关SC8连接到0P放大器52的反相输入端子,并且通过开关SC9连接到AGND。在这种情况下,从逻辑电路54输出的量化器53的量化结果也被提供给DAC 62。DAC 62输出基于从逻辑电路54提供的量化结果而确定的DAC电压。DAC 62的输出端子连接到电容器CC3的第一端子。

[0149] 如上所述的配置的子ADC 61的操作例如在图9的时序图中示出。虽然省略了对该操作的详细描述,但是子ADC 61被配置为执行与通用双速循环型ADC相同的操作。由于双速循环型ADC在一个时钟周期内由两个DAC执行两次转换,因此其优点是操作速度高于单速循环型ADC。因此,如果采用具有这种配置的子ADC 61作为第一实施例的子ADC 7,则与采用第一配置示例的子ADC 51的情况相比,可以进一步提高信号处理速度。

[0150] [3]第三配置示例

[0151] 与第一配置示例的子ADC 51类似,图10中所示的第三配置示例的子ADC 71也被配置为通用循环型ADC。然而,子ADC 71与第一配置示例的子ADC 51的不同之处在于,添加了开关SQ2,并且省略了量化器53和逻辑电路54。图10示出了当将这种子ADC 71应用于与第一实施例的ADC 1类似的ADC 72时的总体配置。

[0152] 尽管ADC 72与ADC 1的不同之处在于添加了开关SQ1并省略了加法器8,但是基本配置与ADC 1的基本配置的相同。在这种情况下,ADC 72中所包括的量化器4和逻辑电路5由 ADC 72和子ADC 71两者使用,即由ADC 72和子ADC 71共享。即,子ADC 71被配置为使用ADC 72中所包括的量化器4来执行量化。

[0153] 具体地,积分器3的0P放大器9的输出信号通过开关SQ1被输入到量化器4,并且子ADC 71的0P放大器52的输出信号通过开关SQ2输入。在执行ADC 72(即,主ADC)中的量化的时段期间开关SQ1接通,并且在其他时段中断开。此外,在执行子ADC 71中的量化的时段期间开关SQ2接通,而在其他时段中开关SQ2断开。

[0154] 在这种情况下,逻辑电路5基于从量化器4输出的量化结果生成与输出信号DOUT的最高有效位相对应的数字值,以及与输出信号DOUT的最低有效位相对应的数字值。然后,逻辑电路5通过节点No输出通过将所生成的数字值相加而生成的输出信号DOUT。

[0155] 例如,在图11的时序图中示出了如上所述的配置的ADC 72的操作。在这种情况下,

ADC 72执行与第一实施例的ADC 1类似的操作,并且子ADC 71执行与第一配置示例的子ADC 51类似的操作。然而,子ADC 71与ADC 72(即主ADC)的操作并行地执行其A/D转换操作。因此,量化器4不仅在时间T1、T3、T9和T11而且也在时间T2、T4、T5、T7、T10、T12和T13执行量化。

[0156] 根据这种配置,如在采用第一配置示例的子ADC 51作为第一实施例的子ADC 7的情况一样,可以加速处理操作并且可以减小电路尺寸。此外,在这种情况下,子ADC 71被配置为共享ADC 72中所包括的量化器4,并且电路尺寸可以相应地减小。因此,根据上述配置,可以整体上进一步减小ADC 72的尺寸。

[0157] 在上述配置中,在用于ADC 72中的量化的阈值电压和用于子ADC 71中的量化的阈值电压相同的情况下,量化器4可以被配置为使用固定的阈值电压。另一方面,在用于ADC 72中的量化的阈值电压和用于子ADC 71中的量化的阈值电压不同的情况下,量化器4可以被配置为能够切换阈值电压。

[0158] [4]第四配置示例

[0159] 根据图12所示的第四配置示例的子ADC 81被配置为通用循环型ADC。然而,子ADC 81具有用于放大与在积分电容器中剩余的电荷相对应的电压的放大功能。即,子ADC 81与第一配置示例的子ADC 51的不同之处在于添加了电容器CC4和开关SC11至SC14。

[0160] 电容器CC4的第一端子通过开关SC13连接到0P放大器52的反相输入端子,并且通过开关SC14连接到AGND。电容器CC4的第二端子通过开关SC11连接到节点N52,并且通过开关SC12连接到AGND。即,子ADC 81的0P放大器52、电容器CC1和CC4以及开关SC2至SC4和SC11至SC14的连接形式与积分器3的0P放大器9、积分电容器Cf1和Cf2、开关SF11至SF14、SF21、SF22和SF24的连接形式类似。在这种配置中,通过以与第一实施例中所述的主ADC中的放大操作相同的方式切换每个开关来实现放大功能。

[0161] 在采取具有上述配置的子ADC 81作为第一实施例的子ADC 7的情况下,如采取第一配置示例的子ADC 51作为第一实施例的子ADC7的情况一样,可以提高处理速度并且可以减小电路尺寸。此外,在这种情况下,子ADC 81被配置为具有用于放大与在积分电容器中剩余的电荷相对应的电压的放大功能。因此,根据上述配置,在从时间T5到时间T7、从时间T13到时间T15等的时段内执行主ADC中的放大操作。

[0162] 在不执行主ADC中的放大操作的情况下,可以将主ADC的A/D转换操作的周期延长这种放大操作所需的周期并提高分辨率,或者将整个操作周期缩短这种放大操作所需的时间量。此外,在这种情况下,可以消除用于在ADC 1中实现放大操作的配置,并且可以将电路尺寸减小这种消除的配置的量。

[0163] (其他实施方式)

[0164] 本发明不限于上述和附图所示的每个实施例,并且可以任意地修改、组合或扩展。

[0165] 在上述实施例中所引用的数值等是示例,并且不限于此。

[0166] 在第一实施例中,为了简化描述,将具有单端电路配置的ADC 1作为图1中所示的示例进行描述。然而,在第一实施例中描述的本发明独有的配置也可以应用于具有差分电路配置的ADC。

[0167] 尽管基于实施例描述了本发明,但是应当理解,本发明不应限于上述示例和结构。本发明包括等效范围内的各种修改和变化。另外,各种组合和形式、以及仅包括一个要素、

更多或更少的要素的其他组合和形式,都在本发明的范围和精神内。

图1

图2

图4

图5

图7

图8

图9

图10

图11

图12