### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2020/0212085 A1

(43) Pub. Date:

Jul. 2, 2020

### (54) SOLID-STATE IMAGING DEVICE, MANUFACTURING METHOD OF SOLID-STATE IMAGING DEVICE AND **ELECTRONIC APPARATUS**

(71) Applicant: Sony Semiconductor Solutions Corporation, Kanagawa (JP)

(72) Inventor: Takahiro Kawamura, Kanagawa (JP)

Appl. No.: 16/811,671

(22) Filed: Mar. 6, 2020

### Related U.S. Application Data

(63) Continuation of application No. 16/028,818, filed on Jul. 6, 2018, now Pat. No. 10,615,215, which is a continuation of application No. 15/470,535, filed on Mar. 27, 2017, now Pat. No. 10,020,339, which is a continuation of application No. 14/831,328, filed on Aug. 20, 2015, now Pat. No. 9,608,036, which is a continuation of application No. 14/331,742, filed on Jul. 15, 2014, now Pat. No. 9,129,881.

#### (30)Foreign Application Priority Data

Sep. 9, 2013 (JP) ...... 2013-185945

#### **Publication Classification**

(51) Int. Cl. H01L 27/146 (2006.01)H01L 27/148 (2006.01)

U.S. Cl. CPC .... H01L 27/1464 (2013.01); H01L 27/14689 (2013.01); H01L 27/14638 (2013.01); H01L 27/14623 (2013.01); H01L 27/14818 (2013.01); H01L 27/14605 (2013.01); H01L 27/14643 (2013.01); H01L 27/14683 (2013.01); H01L 27/14614 (2013.01)

#### (57)ABSTRACT

A solid-state imaging device includes a pixel having a photoelectric conversion element which generates a charge in response to incident light, a first transfer gate which transfers the charge from the photoelectric conversion element to a charge holding section, and a second transfer gate which transfers the charge from the charge holding section to a floating diffusion. The first transfer gate includes a trench gate structure having at least two trench gate sections embedded in a depth direction of a semiconductor substrate, and the charge holding section includes a semiconductor region positioned between adjacent trench gate sections.

FIG. 1

FIG. 3

而 (2) (4)

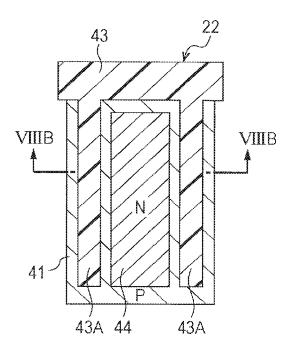

FIG. 5A

FIG. 5B

FIG. 5C

) 41

FIG. 5D

FIG. 78

St. 7

FIG. 8A

FIG. 8B

N-TYPE ION INJECTION 3 9 9 62 (B3) 62 ر ق ÷ N-TYPE ION INJECTION 8 **で** の の の 8 4 N-TYPE ION INJECTION 8 9 9 1 9 62 62 4

FIG. 10

FIG. 11

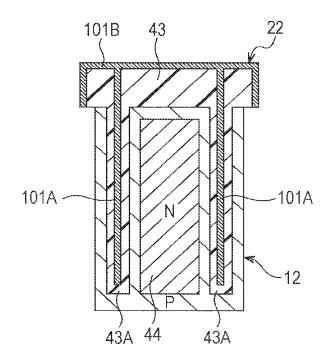

FIG. 12

FIG. 13

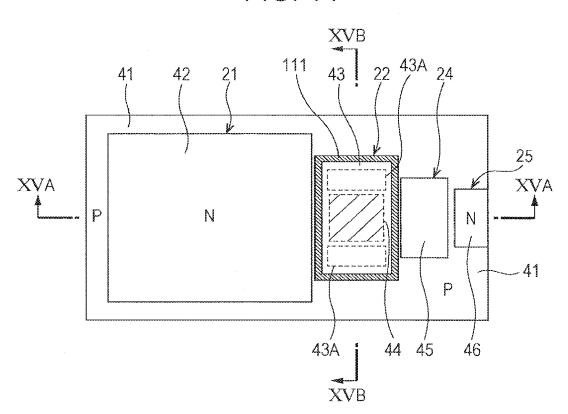

FIG. 14

FIG. 16

### SOLID-STATE IMAGING DEVICE, MANUFACTURING METHOD OF SOLID-STATE IMAGING DEVICE AND ELECTRONIC APPARATUS

## CROSS REFERENCE TO RELATED APPLICATIONS

[0001] The present application is a Continuation of application Ser. No. 16/028,818, filed Jul. 6, 2018, which is a Continuation of application Ser. No. 15/470,535, filed Mar. 27, 2017, now U.S. Pat. No. 10,020,339, issued Jul. 10, 2018, which is a Continuation of application Ser. No. 14/831,328, filed Aug. 20, 2015, now U.S. Pat. No. 9,608, 036, issued Mar. 28, 2017, which is a Continuation of application Ser. No. 14/331,742, filed Jul. 15, 2014, now U.S. Pat. No. 9,129,881, issued Sep. 8, 2015, which claims the benefit of Japanese Priority Patent Application JP 2013-185945 filed Sep. 9, 2013, the entire contents of which are incorporated herein by reference.

#### BACKGROUND

[0002] The present technology relates to a solid-state imaging device, a manufacturing method of the solid-state imaging device and an electronic apparatus, and specifically, relates to a solid-state imaging device that can increase an amount of a saturated charges in a solid-state imaging device capable of realizing a global shutter, a manufacturing method of the solid-state imaging device and an electronic apparatus.

[0003] In recent years, a CMOS solid-state imaging device (CMOS imaging sensor) is mounted on many electronic apparatuses such as a digital camera, a video camera, a surveillance camera, a copying machine and a facsimile.

[0004] In the CMOS solid-state imaging device, in order to read charges accumulated in a photodiode for each row, a gap occurs at a time for accumulating optical charges and distortion occurs in an object that is photographed when the object moves.

[0005] In order to prevent the distortion in the object, an all-pixel simultaneous electronic shutter in which exposure periods of each of pixels are the same as each other is being developed. The all-pixel simultaneous electronic shutter performs an operation in which the exposure is simultaneously started in all effective pixels in imaging and the exposure is simultaneously completed, and is also referred to as a global shutter (global exposure).

[0006] As a method for realizing the global shutter, for example, there is a method in which in each pixel, a charge holding region is provided between the photodiode as a charge accumulation region and a floating diffusion region (FD: Floating Diffusion), and the charges accumulated in the photodiode are simultaneously and temporarily transferred to the charge holding region for all pixels, and the charges accumulated in the charge holding region are read by performing sequential scanning for each row.

[0007] For the charge holding region, a structure is used which has a PN junction in which first conductivity type and second conductivity type semiconductor regions are laminated in a semiconductor substrate, and a planar type gate electrode that controls charge transfer through an insulating film on an upper section of the PN junction (for example, Japanese Unexamined Patent Application Publication No. 2009-268083).

**[0008]** In the CMOS solid-state imaging device realizing the global shutter, it is necessary to hold a maximum amount (amount of saturated charges) of a charge signal that is accumulated in the photodiode in the charge holding region.

#### **SUMMARY**

[0009] However, in order to increase a holding capacity of the charge holding region, when increasing an area of the charge holding region, an area of the photodiode is reduced, on the contrary. Thus, the area of the photodiode for unit pixel size is reduced and light reception sensitivity thereof or the amount of the saturated charges of the photodiode is lowered compared to that of a non-global shutter type CMOS solid-state imaging device.

[0010] In the present technology, it is desirable to increase an amount of saturated charges in a solid-state imaging device capable of realizing a global shutter.

[0011] According to an embodiment of the present technology, there is provided a solid-state imaging device comprising: a pixel including a photoelectric conversion element configured to generate a charge in response to incident light, a first transfer gate configured to transfer the charge from the photoelectric conversion element to a charge holding section, and a second transfer gate configured to transfer the charge from the charge holding section to a floating diffusion, wherein the first transfer gate includes a trench gate structure having at least two trench gate sections embedded in a depth direction of a semiconductor substrate, and the charge holding section includes a semiconductor region positioned between adjacent ones of the plurality of trench gate sections.

[0012] According to another embodiment of the present technology, there is provided a manufacturing method of a solid-state imaging device, comprising: providing a semiconductor substrate; forming a pixel on the semiconductor substrate, the pixel including a photoelectric conversion element configured to generate a charge in response to incident light, a first transfer gate configured to transfer the charge from the photoelectric conversion element to a charge holding section, and a second transfer gate configured to transfer the charge from the charge holding section to a floating diffusion, wherein the first transfer gate includes a trench gate structure having at least two trench gate sections embedded in a depth direction of a semiconductor substrate, and the charge holding section includes a semiconductor region positioned between adjacent ones of the plurality of trench gate sections.

[0013] According to still another embodiment of the present technology, there is provided an electronic apparatus comprising: an optical section; a solid-state imaging device; and a digital signal processor circuit, wherein the solid-state imaging device includes: a pixel including a photoelectric conversion element configured to generate a charge in response to incident light, a first transfer gate configured to transfer the charge from the photoelectric conversion element to a charge holding section, and a second transfer gate configured to transfer the charge from the charge holding section to a floating diffusion, wherein the first transfer gate includes a trench gate structure having at least two trench gate sections embedded in a depth direction of a semiconductor substrate, and the charge holding section includes a semiconductor region positioned between adjacent ones of the plurality of trench gate sections.

[0014] In the above embodiments of the present technology, the gate electrode of the first transfer transistor is configured to have two or more trench gate sections embedded from the interface of the semiconductor substrate to the predetermined depth, and the charge accumulation section is formed vertically long between the two trench gate sections of the first transfer transistor embedded in the semiconductor substrate

[0015] The solid-state imaging device and the electronic apparatus may be an independent device or may be a module to be incorporated into other devices.

[0016] According to the above embodiments of the present technology, it is possible to increase the amount of the saturated charges in the solid-state imaging device capable of realizing the global shutter.

[0017] Moreover, the effects described here are not necessarily limited and any of effects may be effective in the disclosure.

#### BRIEF DESCRIPTION OF THE DRAWINGS

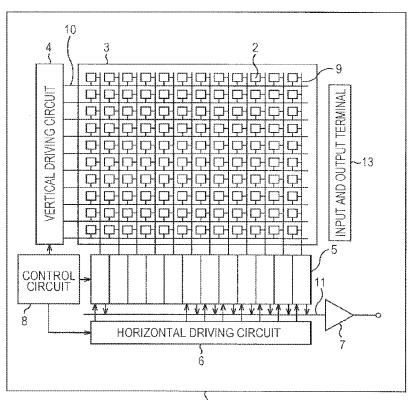

[0018] FIG. 1 is a view illustrating a schematic configuration of a solid-state imaging device to which the present technology is applied;

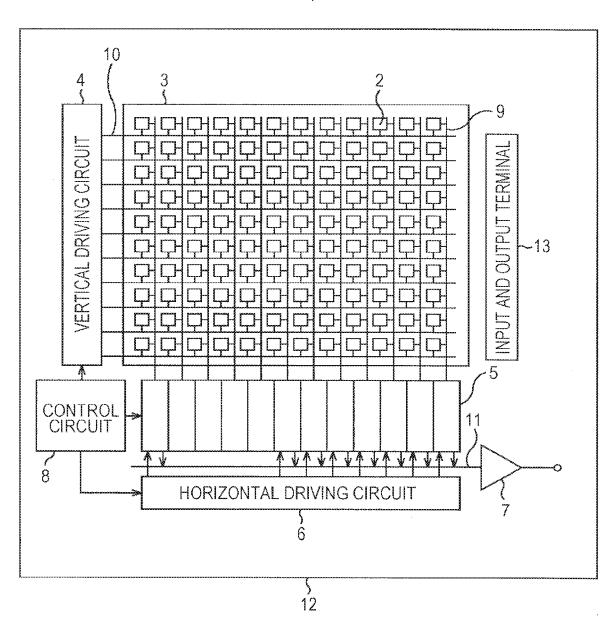

[0019] FIG. 2 is a view illustrating an equivalent circuit of a pixel;

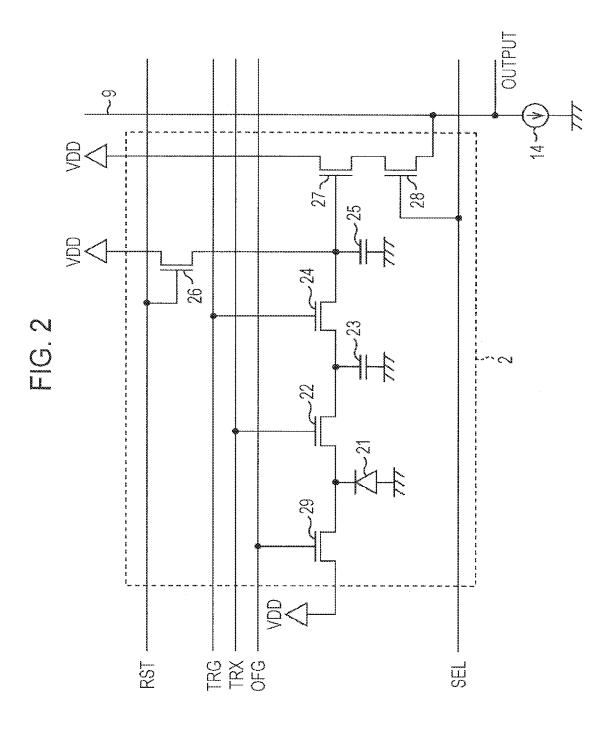

[0020] FIG. 3 is a plan view illustrating a schematic configuration of the pixel in a first embodiment;

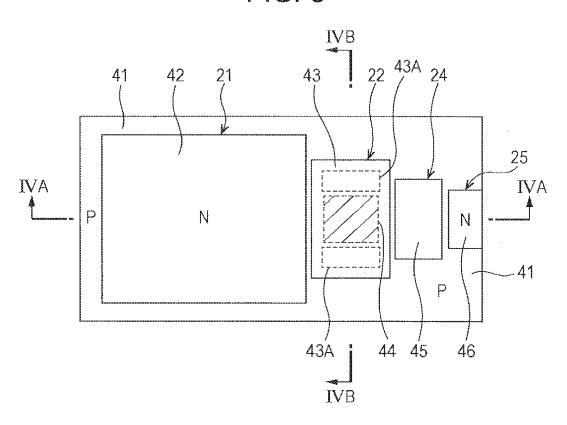

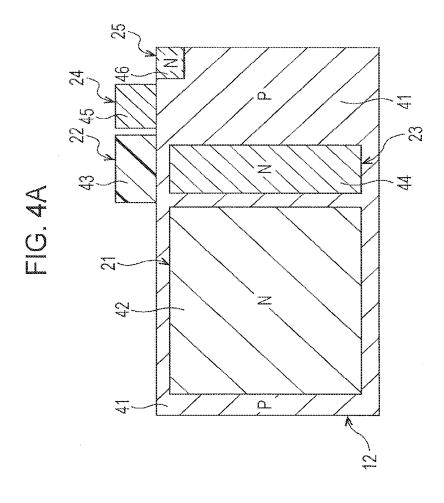

[0021] FIGS. 4A and 4B are cross-sectional views illustrating a schematic configuration of the pixel in the first embodiment:

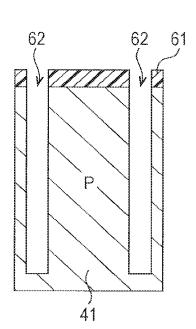

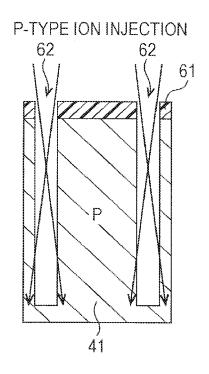

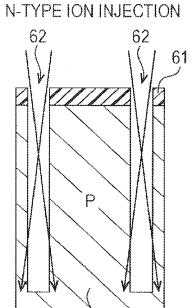

[0022] FIGS. 5A to 5D are views describing a forming method of a memory section;

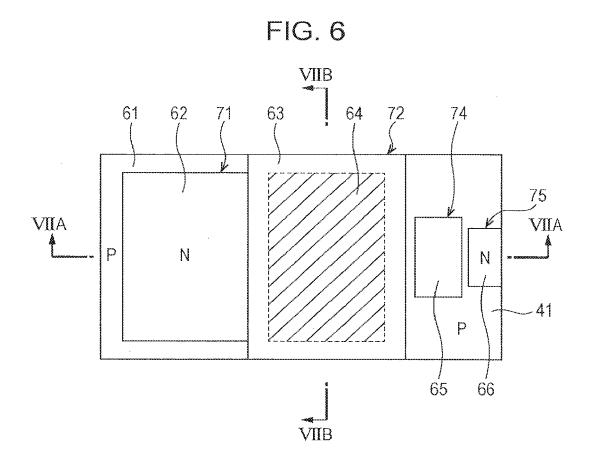

[0023] FIG. 6 is a plan view illustrating a pixel structure of a planar type first transfer transistor;

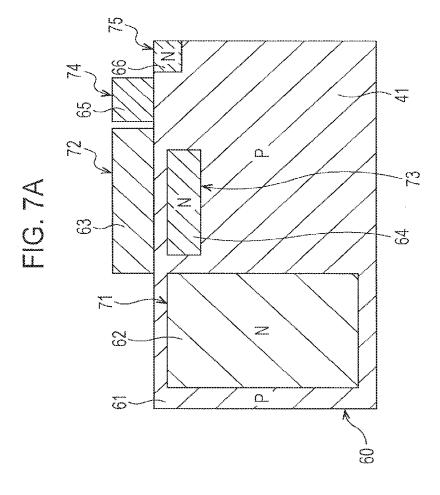

[0024] FIGS. 7A and 7B are cross-sectional views illustrating the pixel structure of the planar type first transfer transistor;

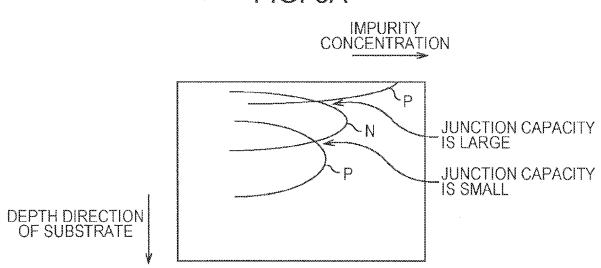

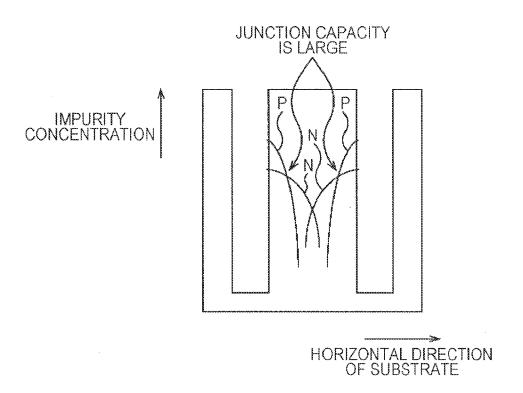

[0025] FIGS. 8A and 8B are views illustrating an impurity concentration profile;

[0026] FIGS. 9A to 9C are views describing a modification example of a forming method of a memory section;

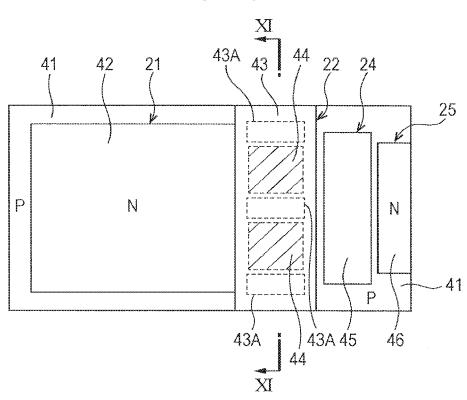

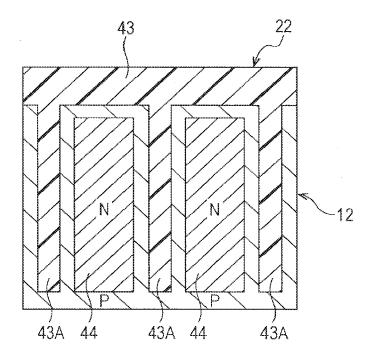

[0027] FIG. 10 is a plan view illustrating a schematic configuration of a pixel in a second embodiment;

[0028] FIG. 11 is a cross-sectional view illustrating a schematic configuration of the pixel in the second embodiment:

[0029] FIG. 12 is a plan view illustrating a schematic configuration of a pixel in a third embodiment;

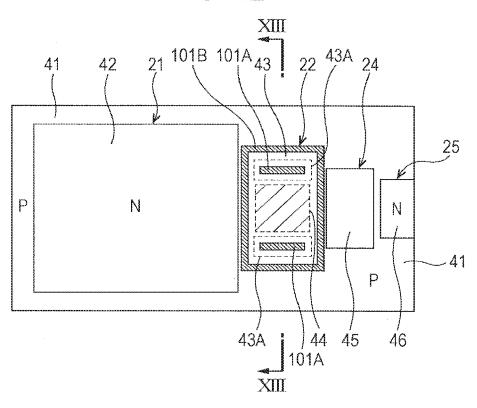

[0030] FIG. 13 is a cross-sectional view illustrating a schematic configuration of the pixel in the third embodiment:

[0031] FIG. 14 is a plan view illustrating a schematic configuration of a pixel in a fourth embodiment;

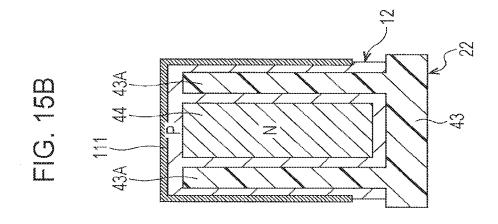

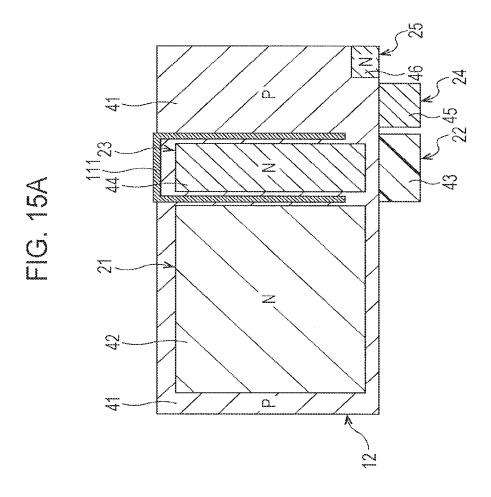

[0032] FIGS. 15A and 15B are cross-sectional views illustrating a schematic configuration of the pixel in the fourth embodiment;

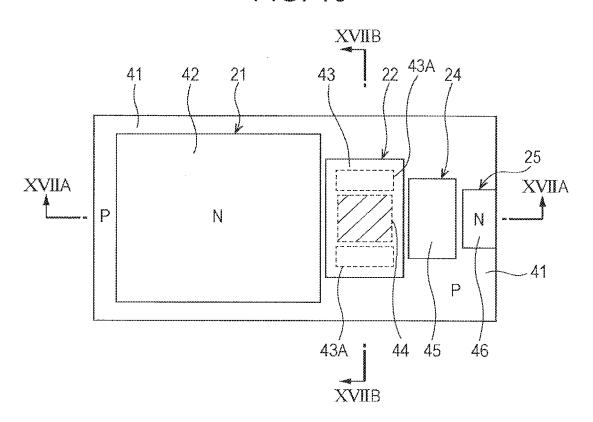

[0033] FIG. 16 is a plan view illustrating a schematic configuration of a pixel in a fifth embodiment;

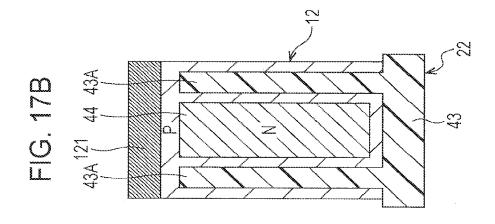

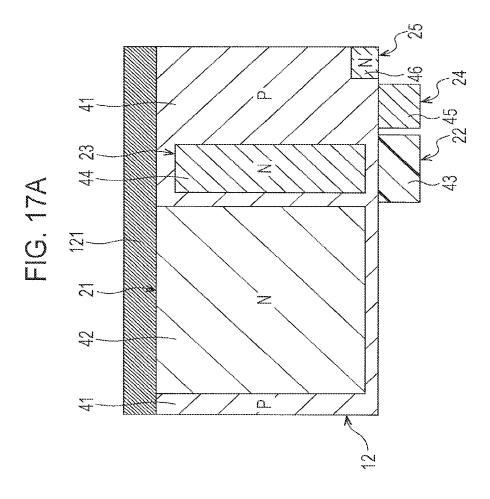

[0034] FIGS. 17A and 17B are cross-sectional views illustrating a schematic configuration of the pixel in the fifth embodiment; and

[0035] FIG. 18 is a block diagram illustrating a configuration example of an imaging apparatus as an electronic apparatus to which the present technology is applied.

#### DETAILED DESCRIPTION OF EMBODIMENTS

[0036] Hereinafter, an embodiment of the present technology is described. Moreover, the description is made in the following order.

[0037] 1. Schematic Configuration Example of Solid-State Imaging Device

[0038] 2. Circuit Configuration Example of Pixel

[0039] 3. First Embodiment (Configuration Example Having Two Trench Gate Sections) of Pixel

[0040] 4. Second Embodiment (Configuration Example Having Three Trench Gate Sections) of Pixel

[0041] 5. Third Embodiment (Configuration Example Having Light-Shielding Material Inside Trench Gate Section) of Pixel

[0042] 6. Fourth Embodiment (Configuration Example of Back Surface Irradiation Type) of Pixel

[0043] 7. Fifth Embodiment (Configuration Example Having Photoelectric Conversion Film of Back Surface Irradiation Type) of Pixel

[0044] 8. Application Example to Electronic Apparatus

## 1. Schematic Configuration Example of Solid-State Imaging Device

[0045] FIG. 1 illustrates a schematic configuration of a solid-state imaging device to which the present technology is applied.

[0046] A solid-state imaging device 1 in FIG. 1 is configured to have a pixel array section 3 in which each pixel 2 is arranged in a two-dimensional array and peripheral circuit sections in the periphery thereof in a semiconductor substrate 12 using, for example, silicon (Si) as a semiconductor. The peripheral circuit sections include a vertical driving circuit 4, a column signal processing circuit 5, a horizontal driving circuit 6, an output circuit 7, a control circuit 8 and the like.

[0047] The pixel 2 is configured to have a photodiode as a photoelectric conversion element and a plurality of pixel transistors. A configuration example of the pixel 2 is described below with reference to FIG. 2.

[0048] Further, the pixel 2 can also be a shared pixel structure. The shared pixel structure is configured of a plurality of photodiodes, a plurality of transfer transistors, one floating diffusion (floating diffusion region) that is shared, and each of other pixel transistors that are shared. That is, in the shared pixel, the photodiode and the transfer transistor configuring a plurality of unit pixels are configured to share another pixel transistor.

[0049] The control circuit 8 receives data for instructing an input clock, an operation mode and the like, and outputs data such as internal information of the solid-state imaging device 1 and the like. That is, the control circuit 8 generates a clock signal or a control signal as a reference for the operation of the vertical driving circuit 4, the column signal processing circuit 5, the horizontal driving circuit 6 and the like, based on a vertical synchronization signal, a horizontal synchronization signal and a master clock. Then, the control circuit 8 outputs the clock signal or the control signal that is generated to the vertical driving circuit 4, the column signal processing circuit 5, the horizontal driving circuit 6 and the like.

[0050] For example, the vertical driving circuit 4 is configured of a shift register and selects a pixel driving wiring 10, and supplies a pulse for driving the pixel 2 to the pixel

driving wiring 10 that is selected, and drives the pixels 2 on a row-by-row basis. That is, the vertical driving circuit 4 selectively scans each pixel 2 of the pixel array section 3 sequentially in a vertical direction on a row-by-row basis and supplies the pixel signal to the column signal processing circuit 5 through a vertical signal line 9, based on signal charges generated depending on an amount of received light in the photoelectric conversion section of each pixel 2.

[0051] The column signal processing circuit 5 is disposed for each column of the pixels 2 and performs a signal process such as noise removal for each pixel column with respect to the signal output from the pixels 2 of one row. For example, the column signal processing circuit 5 performs the signal process such as a Correlated Double Sampling (CDS) for removing fixed pattern noise unique to the pixel, and AD conversion.

[0052] For example, the horizontal driving circuit 6 is configured of the shift register and selects in turn each of the column signal processing circuits 5 by sequentially outputting horizontal scanning pulses, and outputs the pixel signal from each of the column signal processing circuits 5 to a horizontal signal line 11.

[0053] The output circuit 7 outputs the signal by performing the signal process with respect to the signals sequentially supplied from each of the column signal processing circuits 5 through the horizontal signal line 11. For example, the output circuit 7 may perform only buffering or may perform black level adjustment, column variation correction, various types of digital signal processes and the like. An input and output terminal 13 exchanges a signal to and from the outside

[0054] The solid-state imaging device 1 configured as described above is a CMOS image sensor called a column AD type in which the column signal processing circuit 5 performing a CDS process and an AD conversion process is disposed for each pixel column.

#### 2. Circuit Configuration Example of Pixel 2

[0055] FIG. 2 illustrates an equivalent circuit of the pixel 2.

[0056] The pixel 2 has a photodiode 21 as a photoelectric conversion element, a first transfer transistor 22, a memory section (MEM) 23, a second transfer transistor 24, a floating diffusion (FD) 25, a reset transistor 26, an amplification transistor 27, a selection transistor 28, and a discharge transistor 29.

[0057] The photodiode 21 is a photoelectric conversion section that generates and accumulates charges (signal charges) depending on an amount of received light. An anode terminal of the photodiode 21 is grounded and a cathode terminal is connected to the memory section 23 through the first transfer transistor 22. Further, the cathode terminal of the photodiode 21 is also connected to the discharge transistor 29.

[0058] When the first transfer transistor 22 is turned ON by a transfer signal TRX, the first transfer transistor 22 reads the charges generated in the photodiode 21 and transfers the charges to the memory section 23. The memory section 23 is a charge holding section that temporarily holds the charges until the charges are transferred to the FD 25. When the second transfer transistor 24 is turned ON by a transfer signal TRG, the second transfer transistor 24 transfers the charges held in the memory section 23 to the FD 25.

[0059] The FD 25 is a charge holding section that holds the charges that are read from the memory section 23 for reading the charges as a signal. When the reset transistor 26 is turned ON by a reset signal RST, a potential of the FD 25 is reset by discharging the charges held in the FD 25 to a constant voltage source VDD.

[0060] The amplification transistor 27 outputs the pixel signal depending on the potential of the FD 25. That is, the amplification transistor 27 configures a source follower circuit with a load MOS 14 as the constant voltage source, and the pixel signal indicating a level depending on the charges held in the FD 25 is output from the amplification transistor 27 to the column signal processing circuit 5 (FIG. 1) through the selection transistor 28. For example, the load MOS 14 is provided inside the column signal processing circuit 5.

[0061] The selection transistor 28 is turned ON when the pixel 2 is selected by a select signal SEL and outputs the pixel signal of the pixel 2 to the column signal processing circuit 5 through the vertical signal line 9. The discharge transistor 29 discharges unnecessary charges that are accumulated in the photodiode 21 to the constant voltage source VDD when turned ON by a discharge signal OFG. The transfer signals TRX and TRG, the reset signal RST, the select signal SEL, and a discharge signal OFG are controlled by the vertical driving circuit 4 and are supplied through the horizontal signal line 11 (FIG. 1).

[0062] An operation of the pixel 2 is simply described.

[0063] First, the discharge transistor 29 is turned ON by supplying the discharge signal OFG of High level to the discharge transistor 29 before the exposure is started, and the charges accumulated in the photodiode 21 are discharged to the constant voltage source VDD, and the photodiode 21 is

[0064] When the discharge transistor 29 is turned OFF by the discharge signal OFG of Low level after the photodiode 21 is reset, the exposure is started in all pixels.

[0065] When a predetermined exposure time that is determined in advance has elapsed, the first transfer transistor 22 is turned ON by a first transfer signal TRX in all pixels of the pixel array section 3, and the charges accumulated in the photodiode 21 are transferred to the memory section 23.

[0066] The charges held in the memory section 23 of each pixel 2 are sequentially read to an ADC 15 on a row-by-row basis after the first transfer transistor 22 is turned OFF. In the reading operation, the second transfer transistor 24 of the pixel 2 of a reading row is turned ON by a second transfer signal TRG and the charges held in the memory section 23 are transferred to the FD 25. Then, the signal indicating the level depending on the charges held in the FD 25 are output from the amplification transistor 27 to the ADC 15 through the selection transistor 28 by the selection transistor 28 being turned ON by the select signal SEL.

#### 3. First Embodiment of Pixel 2

[0067] Schematic Configuration View of Pixel 2

[0068] Structures of the photodiode 21, the first transfer transistor 22, the memory section 23, the second transfer transistor 24 and the FD 25 inside the pixel 2 are described with reference to FIGS. 3 to 4B.

[0069] FIG. 3 is a plan view illustrating a positional relationship between the photodiode 21, the first transfer transistor 22, the memory section 23, the second transfer transistor 24 and the FD 25 inside the pixel 2.

[0070] FIG. 4A illustrates a cross-sectional view taken along line IVA-IVA of FIG. 3 and FIG. 4B illustrates a cross-sectional view taken along line IVB-IVB of FIG. 3.

[0071] Moreover, FIG. 3 is a plan view that is viewed from a surface side of the semiconductor substrate 12 that is an incident side of the light. In FIGS. 4A and 4B, an upper side of each view is the surface of the semiconductor substrate 12 on which the light is incident.

[0072] As illustrated in FIG. 3, in each pixel 2 of the pixel array section 3, the photodiode 21, the first transfer transistor 22, the second transfer transistor 24 and the FD 25 are arranged in a predetermined direction. In FIG. 3, a lateral direction in which the photodiode 21, the first transfer transistor 22, the second transfer transistor 24 and the FD 25 are arranged is referred to as a first direction.

[0073] In the left side inside the pixel 2 of the semiconductor substrate 12, the photodiode 21 is formed by forming an N-type semiconductor region 42 that is a second conductivity type inside a P-type semiconductor region 41 that is a first conductivity type.

[0074] Then, as illustrated in FIGS. 3 and 4A, a gate electrode 43 of the first transfer transistor 22 is formed on the right side of the photodiode 21, and an N-type semiconductor region 44 that is a charge holding region of the memory section 23 is formed on a lower side of the gate electrode 43. The N-type semiconductor region 42 that is a charge accumulation region of the photodiode 21 also serves as one side of a source/drain region of the first transfer transistor 22, and the N-type semiconductor region 44 that is a charge holding region of the memory section 23 also serves as the other side of the source/drain region of the first transfer transistor 22.

[0075] Further, as illustrated in FIG. 4B, the gate electrode 43 of the first transfer transistor 22 has a trench gate structure in which two trench gate sections 43A are embedded in a depth direction of the semiconductor substrate 12. As illustrated in FIG. 3, the two trench gate sections 43A are disposed so as to sandwich the N-type semiconductor region 44 that is the memory section 23 from the second direction perpendicular to the first direction that is the transfer direction of the charges. As illustrated in FIG. 4B, the depth of the trench gate section 43A that is embedded is substantially the same as that of the N-type semiconductor region 44 of the memory section 23.

[0076] In other words, the N-type semiconductor region 44 that is the charge holding region of the memory section 23 is formed vertically long along a side wall of the two trench gate sections 43A of the first transfer transistor 22. Then, P-type/N-type/P-type semiconductor regions are formed in the horizontal direction between the two trench gate sections 43A.

[0077] Moreover, in FIG. 3, the two trench gate sections 43A of the gate electrode 43 of the first transfer transistor 22 and the N-type semiconductor region 44 (the memory section 23) that is formed on the lower side of the gate electrode 43 are illustrated in broken lines.

[0078] Then, as illustrated in FIGS. 3 and 4A, a gate electrode 45 of the second transfer transistor 24 is formed on the opposite side to the side on which the photodiode 21 is formed with respect to the gate electrode 43 of the first transfer transistor 22, and an N-type semiconductor region 46 that is the FD 25 is formed on the surface side of the substrate further on the right side thereof. The N-type semiconductor region 44 that is the charge holding region of

the memory section 23 also serves as one side of the source/drain region of the second transfer transistor 24 and the N-type semiconductor region 46 that is the FD 25 also serves as the other side of the source/drain region of the second transfer transistor 24.

[0079] Moreover, in FIGS. 4A and 4B, a multilayered wiring layer formed of a plurality of wiring layers and an interlayer insulating film, a color filter, an on-chip lens or the like is formed on an upper surface of the gate electrode 43 of the first transfer transistor 22 or the gate electrode 45 of the second transfer transistor 24, which is the side of the light incident surface.

[0080] As described above, in the first embodiment of the pixel 2, the gate electrode 43 of the first transfer transistor 22 has the transfer gate structure in which the two trench gate sections 43A are embedded in the depth direction of the semiconductor substrate 12. On the other hand, the gate electrode 45 of the second transfer transistor 24 has the planar type gate structure that is formed only on the surface of the semiconductor substrate.

[0081] Then, the N-type semiconductor region 44 as the memory section 23 is formed vertically long between the two trench gate sections 43A of the first transfer transistor 22 and the memory section 23 has a PN junction surface in the vertical direction that is the depth direction of the substrate. [0082] Therefore, it is possible to provide the N-type semiconductor region 44 as the memory section 23 without reducing the charge accumulation region of the photodiode 21 and it is possible to prevent the light reception sensitivity or the amount of the saturated charges from being lowered according to reduction of the area of the photodiode.

[0083] Manufacturing Method

[0084] A forming method of the gate electrode 43 of the first transfer transistor 22 and the N-type semiconductor region 44 that is the memory section 23 is described with reference to FIGS. 5A to 5D.

[0085] First, as illustrated in FIG. 5A, a resist mask 61 is patterned so as to open regions which form the two trench gate sections 43A and then the P-type semiconductor region 41 is etched to a predetermined depth. Therefore, two trench sections 62 which become the trench gate sections 43A of the first transfer transistor 22 are formed.

[0086] Then, as illustrated in FIG. 5B, for example, P-type ions such as boron (B) are injected at low acceleration energy to the immediate vicinity of the side wall of the trench section 62.

[0087] Next, as illustrated in FIG. 5C, for example, N-type ions such as phosphorus (P) or arsenic (As) are injected. At this time, the ions are injected at higher acceleration energy than that when P-type ions are injected so as to inject the N-type ions into the inside from the side wall of the trench section 62.

[0088] Moreover, the P-type ions and the N-type ions are injected with a predetermined tilt (tilt angle) so as to be incident obliquely to the side wall of the trench section 62. [0089] Then, as illustrated in FIG. 5D, the resist mask 61 is peeled off and then the gate electrode 43 of the first transfer transistor 22 is embedded in the trench sections 62 and is also formed on the surface of the semiconductor substrate 12. As a material of the gate electrode 43, for example, it is possible to employ polysilicon.

[0090] Through the above process, the gate electrode 43 of the first transfer transistor 22 including the two trench gate sections 43A is completed and the N-type semiconductor

region 44 that is the charge holding region of the memory section 23 is formed between the two trench gate sections 43A.

[0091] Moreover, in the example of FIGS. 5A to 5D, the injection of the P-type ions is performed and then the injection of the N-type ions is performed, but the order of the injection of the P-type ions and the injection of the N-type ions may be reversed.

[0092] Pixel Structure of Planar Type First Transfer Transistor

[0093] In order to facilitate understanding of the effects of the pixel structure to which the present technology is applied, the pixel structure having the planar type first transfer transistor is described with reference to FIGS. 6 to 7B

[0094] FIG. 6 is a plan view illustrating a positional relationship between a photodiode 71, a first transfer transistor 72, a memory section 73, a second transfer transistor 74, and a FD 75 of a pixel having a planar type first transfer transistor that is illustrated so as to correspond to FIG. 3.

[0095] Further, FIG. 7A illustrates a cross-sectional view taken along line VIIA-VIIA of FIG. 6 and FIG. 7B illustrates a cross-sectional view taken along line VIIB-VIIB of FIG. 6.

[0096] As illustrated in FIG. 6, the photodiode 71, the first

transfer transistor 72, the second transfer transistor 74 and the FD 75 are arranged in a first direction similar to FIG. 3. [0097] In the left side inside the pixel of a semiconductor

substrate **60**, the photodiode **71** is formed by forming an N-type semiconductor region **62** that is a second conductivity type inside a P-type semiconductor region **61** that is a first conductivity type.

[0098] Then, as illustrated in FIGS. 6 and 7A, a gate electrode 63 of the first transfer transistor 72 is formed in a plane only on the surface of the semiconductor substrate having an area greater than a light receiving area of the photodiode 71 on the right side object photodiode 71, and an N-type semiconductor region 64 that is a charge holding region of the memory section 73 is formed to have a plane area at the same level as the light receiving area of the photodiode 71 in the vicinity of the lower side of the gate electrode 63.

[0099] The N-type semiconductor region 62 that is a charge accumulation region of the photodiode 71 also serves as one side of a source/drain region of the first transfer transistor 72 and the N-type semiconductor region 64 that is a charge holding region of the memory section 73 also serves as the other side of the source/drain region of the first transfer transistor 72.

[0100] Then, as illustrated in FIGS. 6 and 7A, the gate electrode 65 of the second transfer transistor 74 is formed on the opposite side to the side on which the photodiode 71 is formed with respect to the gate electrode 63 of the first transfer transistor 72, and an N-type semiconductor region 66 that is the FD 75 is formed on the surface side of the substrate further on the right side thereof. The N-type semiconductor region 64 that is the charge holding region of the memory section 73 also serves as one side of the source/drain region of the second transfer transistor 74 and the N-type semiconductor region 66 that is the FD 75 also serves as the other side of the source/drain region of the second transfer transistor 74.

[0101] As described above, in the pixel structure having the planar type first transfer transistor 72, since the N-type semiconductor region 64 that is the charge holding region of

the memory section 73 is formed in a plane having a plane area at the same level as the light receiving area of the photodiode 71, the charge accumulation region of the photodiode 71 is small compared to the charge accumulation region of the photodiode 21 described above. Thus, there is a problem that the light reception sensitivity or the amount of the saturated charges of the photodiode is lowered.

[0102] It is possible to increase a potential amplitude when the charges are depleted and saturated and it is possible to increase the amount of the saturated charges of the memory section 73 by increasing the impurity concentration of the N-type semiconductor region 64 instead of increasing the area of the N-type semiconductor region 64 that is the charge holding region of the memory section 73, but in this case, disadvantage occurs that the charge transfer is difficult.

[0103] Otherwise, it is possible to increase a junction capacity per unit area and to increase the amount of the saturated charges of the memory section 73 without changing the potential when the charges are depleted and accumulated by designing largely a junction electric field of the P-type and the N-type semiconductor regions of the memory section 73 instead of increasing the area of the N-type semiconductor region 64 that is the charge holding region of the memory section 73, but in this case, a disadvantage occurs that the noise is increased when dark by a strong junction electric field.

[0104] FIG. 8A illustrates an impurity concentration profile of a case where the N-type semiconductor region 64 of the memory section 73 is formed in a plane and the PN junction is formed on a horizontal surface as illustrated in FIGS. 7A and 7B.

[0105] The PN junction of the upper side of the N-type semiconductor region 64 that is the charge holding region of the memory section 73 and the P-N-P junction that is the PN junction of the lower side of the N-type semiconductor region 64 are formed in the depth direction of the substrate by injecting the ions from the surface side of the semiconductor substrate 12. In this case, in principle, since the impurity concentration profile spreads as the acceleration energy increases, a junction capacity per unit area of the PN junction on the lower side of the memory section 73 is smaller than that of the PN junction on the upper side of the memory section 73.

[0106] FIG. 8B is an impurity concentration profile in a case where, as illustrated in FIGS. 4A and 4B, the N-type semiconductor region 44 of the memory section 23 is vertically formed and the PN junction is formed on the vertical surface, and illustrates the impurity concentration profile between two trench gate sections 43A in line VIIIB-VIIIB of FIG. 5D.

[0107] In the P-N-P junction between the two trench gate sections 43A, both the PN junction near the side wall of the trench section 62 of the right side and the PN junction near the side wall of the trench section 62 of the left side are configured of an impurity profile that is formed by low acceleration energy. Thus, both the PN junction of the right side and the PN junction of the left side can realize high junction capacity.

[0108] Therefore, according to the pixel structure of the pixel 2 having the PN junction surface in the vertical direction to which the present technology is applied, it is also possible to increase the amount of the saturated charges of the memory section 23 without lowering the amount of the saturated charges of the photodiode 21.

#### Modification Example of Manufacturing Method

[0109] A modification example of a forming method of an N-type semiconductor region 44 that is a memory section 23 is described with reference to FIGS. 9A to 9C.

[0110] When the injection of the N-type ions is performed, it is possible to change the impurity concentration of the N-type semiconductor region 44 that is the memory section 23 depending on the depth thereof by changing the tilt angle of the injection of the ions depending on the depth of the substrate of the trench section 62.

[0111] For example, the injection of the N-type ions is performed so that a relationship of  $\theta_1 < \theta_2 < \theta_3$  is satisfied when the tilt angle of the injection of the ions in a deep position of the trench section 62 illustrated in FIG. 9A is  $\theta_1$ , the tilt angle of the injection of the ions in an intermediate position of the trench section 62 illustrated in FIG. 9B is  $\theta_2$  and the tilt angle of the injection of the ions in a shallow position of the trench section 62 illustrated in FIG. 9C is  $\theta_3$ .

[0112] Therefore, the impurity concentration of the N-type semiconductor region 44 of the memory section 23 becomes thick in the shallow position of the surface side of the substrate and becomes thin in the deep position. In other words, the potential of the N-type semiconductor region 44 of the memory section 23 is high in the shallow position of the surface side of the substrate and is low in the deep position thereof.

[0113] By doing so, when reading the charges from the memory section 23, it is possible to generate the electric field to assist the charge transfer and to facilitate the reading of the charges from the memory section 23.

[0114] Moreover, the impurity concentration of the N-type semiconductor region 44 of the memory section 23 may not change in proportion to the depth but the semiconductor region 44 may be divided into a plurality of regions in the depth direction and the impurity concentration may become thick as moving to the surface side of the substrate.

#### 4. Second Embodiment of Pixel 2

[0115] A second embodiment of the pixel  $\bf 2$  is described with reference to FIGS.  $\bf 10$  and  $\bf 11$ .

[0116] FIG. 10 is a plan view illustrating a positional relationship between a photodiode 21, a first transfer transistor 22, a memory section 23, a second transfer transistor 24 and a FD 25 inside the pixel 2 in the second embodiment. [0117] FIG. 11 illustrates a cross-sectional view taken along line XI-XI of FIG. 10.

[0118] In FIGS. 10 and 11, the same reference numerals are given to the same portions corresponding to FIGS. 3 to 4B in the first embodiment and description of portions duplicating those of the first embodiment is omitted.

[0119] As illustrated in FIG. 11, the two trench gate sections 43A of the gate electrode 43 of the first transfer transistor 22 are formed in the first embodiment, but three trench gate sections 43A thereof are formed in the second embodiment. Therefore, two regions are formed between the two trench gate sections 43A and the N-type semiconductor region 44 that is the charge holding region of the memory section 23 is formed in each region. That is, two N-type semiconductor regions 44 are formed as the charge holding region of the memory section 23.

[0120] Further, as illustrated in FIG. 10, the area of the N-type semiconductor region 46 in the plane direction that

is the FD **25** is also formed largely corresponding to two N-type semiconductor regions **44**.

[0121] It is possible to further increase the amount of the saturated charges of the memory section 23 by having the configuration as described above.

[0122] Moreover, the number of the trench gate sections 43A of the gate electrode 43 of the first transfer transistor 22 may be four or more.

#### 5. Third Embodiment of Pixel 2

[0123] A third embodiment of the pixel 2 is described with reference to FIGS. 12 and 13.

[0124] FIG. 12 is a plan view illustrating a positional relationship between a photodiode 21, a first transfer transistor 22, a memory section 23, a second transfer transistor 24 and a FD 25 inside the pixel 2 in the third embodiment. [0125] FIG. 13 illustrates a cross-sectional view taken along line XIII-XIII of FIG. 12.

[0126] In FIGS. 12 and 13, the same reference numerals are given to the same portions corresponding to FIGS. 3 to 4B in the first embodiment and description of portions duplicating those of the first embodiment is omitted.

[0127] In the pixel structure to which the present technology is applied, since the N-type semiconductor region 44 of the memory section 23 is formed to a deep position of the semiconductor substrate 12, the light incident to the photodiode 21 may come around the memory section 23 and noise may be generated by the light that is incident coming around.

[0128] Thus, in the third embodiment, a structure that prevents the light from coming around the N-type semiconductor region 44 of the memory section 23 is added to the structure that is illustrated as the first embodiment.

[0129] Specifically, as illustrated in FIG. 13, a light-shielding section 101A is formed by embedding a light-shielding material such as tungsten (W) inside two trench gate sections 43A of the gate electrode 43 of the first transfer transistor 22.

[0130] Further, as illustrated in FIGS. 12 and 13, a light-shielding section 101B is formed by a light-shielding material similar to the light-shielding section 101A so as to cover an upper surface and side surfaces of the gate electrode 43 of the first transfer transistor 22.

[0131] Moreover, in the plan view of FIG. 12, illustration of the light-shielding section 101B formed on the upper surface of the gate electrode 43 of the first transfer transistor 22 is omitted.

[0132] It is possible to prevent the light from coming around the N-type semiconductor region 44 of the memory section 23 and to suppress occurrence of the noise by having the configuration as described above.

[0133] Further, it is possible to increase the amount of the saturated charges of the memory section 23 without lowering the amount of the saturated charges of the photodiode 21 by forming vertically long the N-type semiconductor region 44 as the memory section 23 between the two trench gate sections 43A of the first transfer transistor 22.

#### 6. Fourth Embodiment of Pixel 2

[0134] A fourth embodiment of the pixel 2 is described with reference to FIGS. 14 to 15B.

[0135] The pixel structure of the first to third embodiments described above is described as the surface irradiation type

pixel structure, but it is possible to be applied to any of the surface irradiation type and a back surface irradiation type.

[0136] Meanwhile, hereinafter, a pixel structure that is the pixel structure to which the present technology is applied and is specified as having the back surface irradiation type is described.

[0137] FIG. 14 is a plan view illustrating a positional relationship between a photodiode 21, a first transfer transistor 22, a memory section 23, a second transfer transistor 24 and a FD 25 inside the pixel 2 in the fourth embodiment. However, FIG. 14 is different from the plan views in the first to third embodiments described above in that the plan view is viewed from a surface of the opposite side to the surface on which the light of the semiconductor substrate 12 is incident.

[0138] FIG. 15A illustrates a cross-sectional view taken along line XVA-XVA of FIG. 14 and FIG. 15B illustrates a cross-sectional view taken along line XVB-XVB of FIG. 14.

[0139] In FIGS. 14 to 15B, the same reference numerals are given to the same portions corresponding to FIGS. 3 to 4B in the first embodiment and description of portions duplicating those of the first embodiment is omitted.

[0140] In FIGS. 15A and 15B, the upper side of the view is the back surface side of the semiconductor substrate 12 on which the light is incident and a color film, an on-chip lens or the like is laminated on the upper side of the view of the semiconductor substrate 12.

[0141] Meanwhile, as illustrated in FIGS. 15A and 15B, the gate electrode 43 of the first transfer transistor 22, the gate electrode 45 of the second transfer transistor 24 or the like is formed on the lower side of the view of the semi-conductor substrate 12. Further, although not illustrated, a multilayered wiring layer that is formed of a plurality of wiring layers and an interlayer insulation film is formed on the lower side of the gate electrode 43 of the first transfer transistor 22 and the gate electrode 45 of the second transfer transistor 24

[0142] The fourth embodiment is similar to the first embodiment described above in that two trench gate sections 43A of the gate electrode 43 of the first transfer transistor 22 are embedded in the depth direction of the semiconductor substrate 12, and the N-type semiconductor region 44 of the memory section 23 is formed vertically long between the two trench gate sections 43A.

[0143] However, since the pixel of the fourth embodiment is the back surface irradiation type pixel, the two trench gate sections 43A of the gate electrode 43 of the first transfer transistor 22 extend upward from the back surface side of the semiconductor substrate 12 of the lower side of the view.

[0144] Further, also in the fourth embodiment, the structure to prevent the light from coming around the N-type semiconductor region 44 of the memory section 23 is employed. That is, as illustrated in FIGS. 15A and 15B, in order to prevent the light from coming around the memory section 23, a light-shielding section 111 is formed on the back surface that is the side of the light incident surface, and side surfaces to surround the two trench gate sections 43A of the first transfer transistor 22 and the memory section 23.

[0145] In the back surface irradiation type pixel structure, it is possible to prevent the light from coming around the N-type semiconductor region 44 that is the memory section 23 and to suppress occurrence of the noise by having the configuration described above.

[0146] Further, it is also possible to increase the amount of the saturated charges of the memory section 23 without lowering the amount of the saturated charges of the photodiode 21 by forming vertically long the N-type semiconductor region 44 as the memory section 23 between the two trench gate sections 43A of the first transfer transistor 22.

#### 7. Fifth Embodiment of Pixel 2

[0147] A fifth embodiment of the pixel 2 is described with reference to FIGS. 16 to 17B.

[0148] The pixel structure of the fifth embodiment is also an example of the back surface irradiation type similar to the fourth embodiment.

[0149] FIG. 16 is a plan view illustrating a positional relationship between a photodiode 21, a first transfer transistor 22, a memory section 23, a second transfer transistor 24 and a FD 25 inside the pixel 2 viewed from the surface of the opposite side to the light incident side of the semiconductor substrate 12 in the fifth embodiment.

[0150] FIG. 17A illustrates a cross-sectional view taken along line XVIIA-XVIIA of FIG. 16 and FIG. 17B illustrates a cross-sectional view taken along line XVIIB-XVIIB of FIG. 16.

[0151] In FIGS. 16 to 17B, the same reference numerals are given to the same portions corresponding to FIGS. 3 to 4B in the first embodiment and description of portions duplicating those of the first embodiment is omitted.

[0152] In the fifth embodiment, as illustrated in FIGS. 17A and 17B, a light-shielding photoelectric conversion film 121 is formed on an entire surface of the back surface side of the semiconductor substrate 12 that is a surface on which the light is incident. Moreover, a color filter or an on-chip lens (not illustrated) is formed on further upper surface of the photoelectric conversion film 121.

[0153] For example, the photoelectric conversion film 121 can be formed of a compound semiconductor having a chalcopyrite structure formed of copper-aluminum-gallium-indium-sulfur-selenium-based mixed crystal.

[0154] In the pixel structure of the fifth embodiment, since the photoelectric conversion film 121 functions as the light-shielding film, it is possible to prevent the light from coming around the N-type semiconductor region 44 as the memory section 23 and to suppress occurrence of the noise by a further simpler configuration without necessity to provide the light-shielding section 111 as in the fourth embodiment. [0155] Further, it is also possible to increase the amount of

[0155] Further, it is also possible to increase the amount of the saturated charges of the memory section 23 without lowering the amount of the saturated charges of the photodiode 21 by forming vertically long the N-type semiconductor region 44 as the memory section 23 between the two trench gate sections 43A of the first transfer transistor 22.

#### 8. Application Example to Electronic Apparatus

[0156] The present technology is not limited to the application to the solid-state imaging device. That is, the present technology may be applied to an electronic apparatus in general using a solid-state imaging device in an image capturing section (photoelectric convertor) such as an imaging device such as a digital still camera or a digital video camera, a mobile terminal device having an imaging function, and a copy machine using a solid-state imaging device in the image reading unit. The solid-state imaging device may have a form that is formed as one chip or may be a form

of a module having the imaging function which is packaged with the imaging section, the signal processor or an optical system.

[0157] FIG. 18 is a block diagram illustrating a configuration example of an imaging apparatus as an electronic apparatus to which the present technology is applied.

[0158] An imaging apparatus 200 illustrated in FIG. 18 includes an optical section 201 formed of a lens group and the like, a solid-state imaging device (imaging device) 202 in which the configuration of the solid-state imaging device 1 of FIG. 1 is employed, and a Digital Signal Processor (DSP) circuit 203 that is a camera signal process circuit. Further, the imaging apparatus 200 includes a frame memory 204, a display section 205, a recording section 206, an operation section 207, and a power supply section 208. The DSP circuit 203, the frame memory 204, the display section 205, the recording section 206, the operation section 207, and the power supply section 208 are connected to each other through a bus line 209.

[0159] The optical section 201 forms an image on an imaging surface of the solid-state imaging device 202 by capturing incident light (image light) from an object. The solid-state imaging device 202 converts an amount of the incident light in which the image is formed on the imaging surface by the optical section 201 into an electric signal in pixel units and then outputs the electric signal as the pixel signal. As the solid-state imaging device 202, it is possible to use a solid-state imaging device such as the solid-state imaging device that has the pixel structure in which the first transfer transistor 22 has the trench gate structure and the memory section 23 having the vertical PN junction is included between a plurality of trench gate sections 43A which are embedded in the depth direction of the substrate.

[0160] For example, the display section 205 is formed of a panel type display device such as a liquid crystal panel or an electro-luminescence (EL) panel, and displays a moving image or a still image that is imaged in the solid-state imaging device 202. The recording section 206 records the moving image or the still image that is captured in the solid-state imaging device 202 on a recording medium such as a hard disk or a semiconductor memory.

[0161] The operation section 207 issues operation commands with respect to various functions held in the imaging apparatus 200 under the operation of a user. The power supply section 208 appropriately supplies various powers which are operation powers of the DSP circuit 203, the frame memory 204, the display section 205, the recording section 206, and the operation section 207 to the objects to be supplied.

[0162] As described above, as the solid-state imaging device 202, it is possible to increase the area of the photodiode and to realize high sensitivity by using the solid-state imaging device 1 according to the embodiments described above. Therefore, also in the imaging apparatus 200 such as the video camera, the digital still camera, or a camera module for a mobile device such as a mobile phone, it is possible to achieve high image quality in a captured image. [0163] In the embodiment described above, the solid-state imaging device is described in which the first conductivity type is the P-type, the second conductivity type is the N-type and electrons are the signal charges, but the present technology can be also applied to a solid-state imaging device in which positive holes are the signal charges. That is, it is

possible to configure each semiconductor region described above as a reversed conductivity type semiconductor region in which the first conductivity type is the N-type and the second conductivity type is the P-type.

[0164] Further, the present technology is not limited to the application to the solid-state imaging device that captures the image by detecting the distribution of the incident quantity of light of visible light and may be applied to a solid-state imaging device that captures distribution of an incident quantity of infrared rays, X-rays, particles and the like as an image, or, in a broader sense, a solid-state imaging device (a physical quantity distribution detection device) in general such as a fingerprint detection sensor that captures an image by detecting distribution of other physical quantities such as a pressure or an electrostatic capacitance.

[0165] An applicable embodiment of the present technology is not limited to the embodiment described above and may be variously modified without departing from the scope of the present technology.

[0166] For example, it is possible to employ a form that combines all or a portion of a plurality of embodiments described above.

[0167] Moreover, the effects described in the specification are only illustrative and are not intended to be limited, and there may be effects other than those described in the specification.

[0168] Further, the present technology may be configured as described below.

[0169] (1) A solid-state imaging device including: a pixel having a photoelectric conversion section that generates and accumulates charges depending on an amount of received light, a charge accumulation section that accumulates the charges that are generated by the photoelectric conversion section, a first transfer transistor that transfers the charges of the photoelectric conversion section to the charge accumulation section, a charge holding section that holds the charges for reading the charges as a signal, and a second transfer transistor that transfers the charges of the charge accumulation section to the charge holding section, in which a gate electrode of the first transfer transistor has two or more trench gate sections embedded from an interface of a semiconductor substrate to a predetermined depth, and in which the charge accumulation section is formed vertically long between two trench gate sections of the first transfer transistor embedded in the semiconductor substrate.

[0170] (2) The solid-state imaging device according to (1), in which the charge accumulation section has a PN junction surface in a vertical direction that is a depth direction of the semiconductor substrate.

[0171] (3) The solid-state imaging device according to (1) or (2), in which a first conductivity type/a second conductivity type/the first conductivity type semiconductor regions are formed between the two trench gate sections of the first transfer transistor.

[0172] (4) The solid-state imaging device according to any one of (1) to (3), in which the charge accumulation section has a semiconductor region having different impurity concentrations in the depth direction of the semiconductor substrate.

[0173] (5) The solid-state imaging device according to any one of (1) to (4), in which the gate electrode of the first transfer transistor has two trench gate sections embedded from the interface of the semiconductor substrate to a predetermined depth.

[0174] (6) The solid-state imaging device according to any one of (1) to (5), in which the gate electrode of the first transfer transistor has three trench gate sections embedded from the interface of the semiconductor substrate to a predetermined depth.

[0175] (7) The solid-state imaging device according to any one of (1) to (6), in which a light-shielding material is embedded inside the trench gate section of the first transfer transistor.

[0176] (8) The solid-state imaging device according to any one of (1) to (7), in which the solid-state imaging device has back surface irradiation type device in which light is incident from a back surface of the semiconductor substrate.

[0177] (9) The solid-state imaging device according to (8), in which a light-shielding section is formed in a back surface and side surfaces surrounding the two or more trench gate sections and the charge accumulation section therebetween.

[0178] (10) The solid-state imaging device according to

[0178] (10) The solid-state imaging device according to (8), in which a light-shielding photoelectric conversion film is formed on the back surface that is a side of a light incident surface of the semiconductor substrate.

[0179] (11) A manufacturing method of a solid-state imaging device, in a case where a pixel which has a photoelectric conversion section that generates and accumulates charges depending on an amount of received light, a charge accumulation section that accumulates the charges that are generated by the photoelectric conversion section, a first transfer transistor that transfers the charges of the photoelectric conversion section to the charge accumulation section, a charge holding section that holds the charges for reading the charges as a signal, and a second transfer transistor that transfers the charges of the charge accumulation section to the charge holding section, and in which a gate electrode of the first transfer transistor has two or more trench gate sections embedded from an interface of a semiconductor substrate to a predetermined depth is formed, including: forming a trench section that is formed of trench gate sections; and forming a PN junction surface in a vertical direction that is a depth direction of the semiconductor substrate between the two trench sections by injecting a second conductivity type ion at a predetermined tilt angle after injecting a first conductivity type ion at a predetermined tilt angle with respect to the trench section.

**[0180]** (12) The manufacturing method of a solid-state imaging device according to (11), in which acceleration energy is different between the first conductivity type ion injection and the second conductivity type ion injection.

[0181] (13) The manufacturing method of a solid-state imaging device according to (11) or (12), in which in the first or second conductivity type ion injection for forming a semiconductor region becoming the charge accumulation section, the predetermined tilt angle varies with depth of the semiconductor substrate.

[0182] (14) An electronic apparatus including a solid-state imaging device including a pixel having a photoelectric conversion section that generates and accumulates charges depending on an amount of received light, a charge accumulation section that accumulates the charges that are generated by the photoelectric conversion section, a first transfer transistor that transfers the charges of the photoelectric conversion section section, a charge holding section that holds the charges for reading the charges as a signal, and a second transfer transistor that transfers the charges of the charge accumulation section to

the charge holding section, in which a gate electrode of the first transfer transistor has two or more trench gate sections embedded from an interface of a semiconductor substrate to a predetermined depth, and in which the charge accumulation section is formed vertically long between two trench gate sections of the first transfer transistor embedded in the semiconductor substrate.

[0183] (1') A solid-state imaging device, comprising: a pixel including a photoelectric conversion element configured to generate a charge in response to incident light, a first transfer gate configured to transfer the charge from the photoelectric conversion element to a charge holding section, and a second transfer gate configured to transfer the charge from the charge holding section to a floating diffusion, wherein the first transfer gate includes a trench gate structure having at least two trench gate sections embedded in a depth direction of a semiconductor substrate, and the charge holding section includes a semiconductor region positioned between adjacent ones of the plurality of trench gate sections.

[0184] (2') The solid-state imaging device according to (1'), wherein respective ones of the at least two trench gate sections have a dimension in the depth direction which is larger than a dimension in a direction perpendicular to the depth direction.

[0185] (3') The solid-state imaging device according to (1') or (2'), wherein a depth of respective ones of the at least two trench gate sections is substantially the same as a depth of the semiconductor region.

[0186] (4') The solid-state imaging device according to any one of (1') to (3'), wherein the semiconductor substrate has a first conductivity type and the semiconductor region has a second conductivity type which is opposite the first conductivity type.

[0187] (5') The solid-state imaging device according to (4'), wherein a portion of the semiconductor substrate is disposed between the semiconductor region and respective ones of the at least two trench gate sections.

[0188] (6') The solid-state imaging device according to (5'), wherein the first conductivity type is P-type, and the second conductivity type is N-type.

[0189] (7') The solid-state imaging device according to (5'), wherein the first conductivity type is N-type, and the second conductivity type is P-type.

**[0190]** (8') The solid-state imaging device according to any one of (1') to (7'), wherein the semiconductor region also serves as one of a source or a drain of the second transfer gate.

[0191] (9') The solid-state imaging device according to any one of (1') to (8'), wherein the first transfer gate further includes a light-shielding section.

[0192] (10') The solid-state imaging device according to (9'), wherein the light-shielding section includes a portion embedded in respective ones of the at least two trench gate sections.

[0193] (11') The solid-state imaging device according to (9'), wherein the light-shielding section includes a portion covering an upper surface and side surfaces of the first transfer gate.

[0194] (12') The solid-state imaging device according to (9'), wherein a material of the light-shielding section is tungsten.

[0195] (13') The solid-state imaging device according to any one of (1') to (12'), wherein the at least two trench gate sections is at least three trench gate sections.

[0196] (14') The solid-state imaging device according to any one of (1') to (13'), wherein a material of the first transfer gate is polysilicon.

[0197] (15') The solid-state imaging device according to any one of (1') to (14'), wherein the pixel further comprises a discharge gate configured to discharge charges accumulated in the photoelectric conversion element.

[0198] (16') The solid-state imaging device according to any one of (1') to (15'), wherein the pixel further comprises a reset gate configured to discharge charges held in the floating diffusion.

[0199] (17') The solid-state imaging device according to any one of (1') to (16'), wherein the pixel is a back-side illumination type.

[0200] (18') A method of manufacturing a solid-state imaging device, comprising: providing a semiconductor substrate; forming a pixel on the semiconductor substrate, the pixel including a photoelectric conversion element configured to generate a charge in response to incident light, a first transfer gate configured to transfer the charge from the photoelectric conversion element to a charge holding section, and a second transfer gate configured to transfer the charge from the charge holding section to a floating diffusion, wherein the first transfer gate includes a trench gate structure having at least two trench gate sections embedded in a depth direction of a semiconductor substrate, and the charge holding section includes a semiconductor region positioned between adjacent ones of the plurality of trench gate sections.

[0201] (19') An electronic apparatus, comprising: an optical section; a solid-state imaging device; and a digital signal processor circuit, wherein the solid-state imaging device includes: a pixel including a photoelectric conversion element configured to generate a charge in response to incident light, a first transfer gate configured to transfer the charge from the photoelectric conversion element to a charge holding section, and a second transfer gate configured to transfer the charge from the charge holding section to a floating diffusion, wherein the first transfer gate includes a trench gate structure having at least two trench gate sections embedded in a depth direction of a semiconductor substrate, and the charge holding section includes a semiconductor region positioned between adjacent ones of the plurality of trench gate sections.

**[0202]** It should be understood by those skilled in the art that various modifications, combinations, sub-combinations and alterations may occur depending on design requirements and other factors insofar as they are within the scope of the appended claims or the equivalents thereof.

What is claimed is:

- 1. A pixel circuit, comprising:

- a gate electrode disposed on a first surface of a semiconductor substrate;

- a photoelectric conversion film disposed on a second surface of the semiconductor substrate opposite the first surface;

- a source region; and

- a drain region, wherein

- the gate electrode has a trench gate structure including at least two trench gate sections embedded in a depth

- direction of the semiconductor substrate and a connecting portion connecting the at least two trench gate sections, and

- one of the source region or the drain region is disposed between adjacent ones of the at least two trench gate sections and underneath the connecting portion.

- 2. The pixel circuit according to claim 1, wherein respective ones of the at least two trench gate sections have a dimension in the depth direction that is larger than a dimension in a direction perpendicular to the depth direction.

- 3. The pixel circuit according to claim 1, wherein a depth of respective ones of the at least two trench gate sections is substantially the same as a depth of the one of the source region or the drain region.

- **4**. The pixel circuit according to claim **1**, wherein the semiconductor has a first conductivity type and the one of the source region or the drain region has a second conductivity type that is opposite the first conductivity type.

- **5**. The pixel circuit according to claim **4**, wherein the first conductivity type is P-type, and the second conductivity type is N-type.

- **6**. The pixel circuit according to claim **4**, wherein the first conductivity type is N-type, and the second conductivity type is P-type.

- 7. The pixel circuit according to claim 1, wherein the semiconductor substrate includes a first portion disposed between a first trench gate section of the at least two trench gate sections and the one of the source region or the drain region, and a second portion disposed between a second trench gate section of the at least two trench gate sections and the one of the source region or the drain region.

- **8**. The pixel circuit according to claim **1**, wherein the photoelectric conversion film is formed of a compound semiconductor having a chalcopyrite structure.

- **9**. The pixel circuit according to claim **8**, wherein the compound semiconductor is formed of a copper-aluminum-gallium-indium-sulfur-selenium-based mixed crystal.

- 10. The pixel circuit according to claim 1, wherein the second surface is a light-incident surface.

- 11. The pixel circuit according to claim 1, further comprising a color filter on an upper surface of the photoelectric conversion film.

- 12. The pixel circuit according to claim 1, further comprising an on-chip lens formed on an upper surface of the photoelectric conversion film.

- 13. The pixel circuit according to claim 1, wherein a material of the gate electrode is polysilicon.

- 14. The pixel circuit according to claim 1, wherein the at least two trench gate sections is at least three trench gate sections.

- 15. A method of manufacturing a pixel circuit, comprising:

- providing a semiconductor substrate, the semiconductor substrate having a first surface and a second surface opposite the first surface;

- forming a transistor on the first surface of the semiconductor substrate, the transistor including a gate electrode disposed on the semiconductor substrate, a source region, and a drain region; and

- forming a photoelectric conversion film on the second surface of the semiconductor substrate, wherein

- the gate electrode has a trench gate structure including at least two trench gate sections embedded in a depth

direction of the semiconductor substrate and a connecting portion connecting the at least two trench gate sections, and

- one of the source region or the drain region is disposed between adjacent ones of the at least two trench gate sections and underneath the connecting portion.

- **16**. The method according to claim **15**, wherein the photoelectric conversion film is formed of a compound semiconductor having a chalcopyrite structure.

- 17. The method according to claim 16, wherein the compound semiconductor is formed of a copper-aluminum-gallium-indium-sulfur-selenium-based mixed crystal.

- **18**. The method according to claim **15**, wherein the second surface is a light-incident surface.

- 19. The method according to claim 15, further comprising forming a color filter on an upper surface of the photoelectric conversion film.

- 20. The method according to claim 15, further comprising forming an on-chip lens on an upper surface of the photoelectric conversion film.

\* \* \* \* \*