US 20160231950A

### (19) United States

# (12) Patent Application Publication KIM et al.

### (10) Pub. No.: US 2016/0231950 A1

### (43) **Pub. Date:** Aug. 11, 2016

### (54) METHOD OF MANAGING MESSAGE TRANSMISSION FLOW AND STORAGE DEVICE USING THE METHOD

(71) Applicant: Samsung Electronics Co., Ltd.,

Suwon-si (KR)

- (72) Inventors: **Seong-yeon KIM**, Hwaseong-si (KR); **Jin-woo KIM**, Seoul (KR)

- (21) Appl. No.: 14/978,174

- (22) Filed: Dec. 22, 2015

- (30) Foreign Application Priority Data

Feb. 11, 2015 (KR) ...... 10-2015-0020965

### Publication Classification

(51) **Int. Cl.** *G06F 3/06* (2006.01)

*3/0659* (2013.01)

### (57) ABSTRACT

A method of managing a message transmission flow and a storage device using the method are provided. The method of managing a message transmission flow includes receiving, at a storage device, response transmission type information in at least one of a command phase and a data phase, and transmitting response information to a host in at least one of a normal mode and a fast mode based on the received response transmission type information. The normal mode and the fast mode have different latencies.

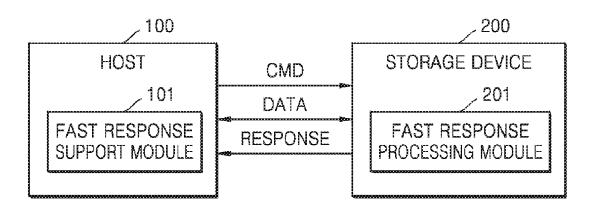

### 1000

FIG. 1

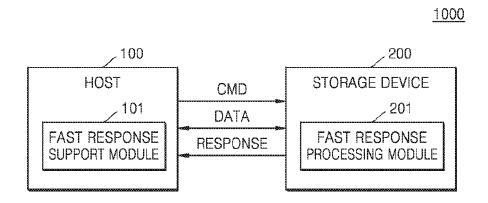

FIG. 2

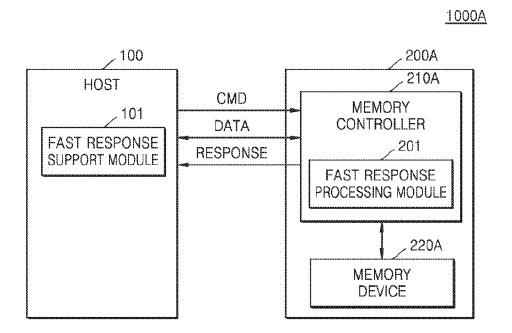

FIG. 3

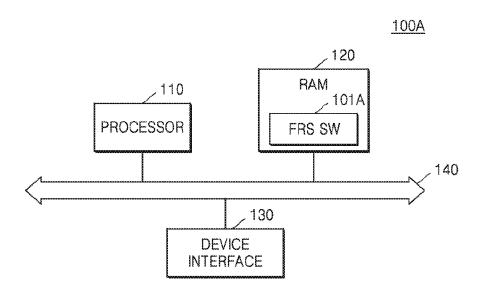

FIG. 4

FIG. 5

FIG. 6

FIG. 7

S E

FIG. 9

| Basic UPIU Header Format                                |  |                                         |          |        |  |  |  |

|---------------------------------------------------------|--|-----------------------------------------|----------|--------|--|--|--|

| Transaction Type Flags LUN Task Ta                      |  |                                         |          |        |  |  |  |

| Resered Command Set<br>Type                             |  | Query Function,<br>Task Manag, Function | Response | Status |  |  |  |

| Total EHS Lenght Device Information Data Segment Lenght |  |                                         |          |        |  |  |  |

FIG. 10

| UPIU Type                          | Op    | eration | nal Fla | gs    | Reserved |       | Task Attribute |       |

|------------------------------------|-------|---------|---------|-------|----------|-------|----------------|-------|

|                                    | Bit 7 | Bit 6   | Bit 5   | Bit 4 | Bit 3    | Bit 2 | Bit 1          | Bit 0 |

| NOP Out                            |       |         |         |       |          |       |                | -     |

| NOP In                             |       |         |         |       |          |       |                |       |

| Command                            | -     | R       | W       |       |          |       | AT             | TR    |

| Response                           |       | 0       | U       | D     |          |       |                |       |

| Data Out                           | _     |         |         |       |          |       | -              | -     |

| Data In                            |       |         |         |       |          |       |                |       |

| Ready to Transfer                  | ***   | URBI    | E.E.S.  |       |          | 34.5  |                |       |

| Reject                             |       |         |         |       |          |       |                |       |

| Query Request                      |       |         |         |       |          |       |                |       |

| Query Response                     |       |         | -       |       |          |       | -              | -     |

| Task Management Request            |       |         |         |       |          | ****  |                |       |

| Task Management Response           |       | CHAIL . |         | CHES  |          | ***   |                |       |

| NOTE 1 "-"denotes reserved values. |       |         |         |       |          |       |                |       |

FIG. 11

| UPIU Type                               | Op    | Operational Flags |       |       | Reserved |          | Task Attribute |       |

|-----------------------------------------|-------|-------------------|-------|-------|----------|----------|----------------|-------|

| *************************************** | Bit 7 | Bit 6             | Bit 5 | Bit 4 | Bit 3    | Bit 2    | Bit 1          | Bit 0 |

| NOP Out                                 |       |                   |       |       |          |          |                |       |

| NOP In                                  |       |                   |       |       |          |          |                |       |

| Command                                 |       | R                 | W     |       |          | F        | AT             | TR    |

| Response                                |       | 0                 | U     | D     |          |          |                |       |

| Data Out                                |       | -                 | _     | -     |          | F        | -              | -     |

| Data In                                 | ***   |                   |       |       |          | F        |                |       |

| Ready to Transfer                       |       |                   |       |       |          |          |                |       |

| Reject                                  |       |                   |       |       |          |          | -              |       |

| Query Request                           |       | _                 |       |       |          |          | -              |       |

| Query Response                          | ****  |                   |       | unus  |          | ataman . |                |       |

| Task Management Request                 |       |                   |       |       |          |          |                |       |

| Task Management Response                |       |                   |       |       |          |          |                |       |

| NOTE 1 "-"denotes reserved values.      |       |                   |       |       |          |          |                |       |

FIG. 12

| UPIU Type                          | Op    | eratio | nal Fla | gs    | Reserved |       | Task Attribute |       |

|------------------------------------|-------|--------|---------|-------|----------|-------|----------------|-------|

|                                    | Bit 7 | Bit 6  | Bit 5   | Bit 4 | Bit 3    | Bit 2 | Bit 1          | Bit 0 |

| NOP Out                            |       |        |         |       |          |       |                |       |

| NOP in                             |       |        | -       |       |          |       |                |       |

| Command                            |       | R      | W       |       | F        |       | AT             | TR    |

| Response                           |       | 0      | U       | D     |          |       |                |       |

| Data Out                           | ***   |        |         |       | F        |       | ****           |       |

| Data In                            |       |        |         |       | F        |       |                |       |

| Ready to Transfer                  |       |        |         |       |          |       |                |       |

| Reject                             |       |        |         |       |          |       |                |       |

| Query Request                      |       |        |         |       |          |       |                |       |

| Query Response                     |       |        |         |       |          |       |                |       |

| Task Management Request            |       |        |         |       |          |       |                |       |

| Task Management Response           |       |        |         |       |          |       |                |       |

| NOTE 1 "-"denotes reserved values. |       |        |         |       |          |       |                |       |

FIG. 13

|             | COMMAND UPIU                            |    |                                         |       |                                         |       |                                         |

|-------------|-----------------------------------------|----|-----------------------------------------|-------|-----------------------------------------|-------|-----------------------------------------|

| 0           |                                         | 1  |                                         | 2     |                                         | 3     |                                         |

| xx00        | 0001b                                   |    | Flags                                   |       | LUN                                     |       | Task Tag                                |

| 4           | Command                                 | 5  |                                         | 6     |                                         | 7     |                                         |

| Resered     | Set Type                                |    | Resered                                 |       | Resered                                 |       | Resered                                 |

| 8           |                                         | 9  |                                         | 10    | (MSB)                                   | 11    | (MSB)                                   |

| Total EHS I | _enght (00h)                            |    | Resered                                 |       | Data Segment                            | Lengl | ht (0000h)                              |

| 12 (M       | SB)                                     | 13 |                                         | 14    |                                         | 15    | (LSB)                                   |

|             |                                         |    | Expected Data                           | Trans | sfer Lenght                             |       |                                         |

| 16          |                                         | 17 |                                         | 18    |                                         | 19    |                                         |

| CDI         | 3[0]                                    |    | CDB[1]                                  |       | CDB[2]                                  |       | CDB[3]                                  |

| 20          |                                         | 21 |                                         | 22    | *************************************** | 23    | *************************************** |

| CD          | 3[4]                                    |    | CDB[5]                                  |       | CDB[6]                                  |       | CDB[7]                                  |

| 24          |                                         | 25 |                                         | 26    |                                         | 27    |                                         |

| CDI         | 3[8]                                    |    | CDB[9]                                  |       | CDB[10]                                 |       | CDB[11]                                 |

| 28          | ononomonanomonanomonanomo               | 29 | *************************************** | 30    |                                         | 31    |                                         |

| CDE         | 8[12]                                   |    | CDB[13]                                 |       | CDB[14]                                 |       | CDB[15]                                 |

|             | *************************************** | }  | Header E2ECRC                           | (om   | it if HD = 0)                           |       | *************************************** |

FIG. 14

| Ready to Transfer UPIU |                    |                  |                |  |  |  |

|------------------------|--------------------|------------------|----------------|--|--|--|

| 0                      | 1                  | 2                | 3              |  |  |  |

| xx11 0001b             | Flags              | LUN              | Task Tag       |  |  |  |

| 4                      | 5                  | 6                | 7              |  |  |  |

| Resered                | Resered            | Resered          | Resered        |  |  |  |

| 8                      | 9                  | 10 (MSB)         | 11 (MSB)       |  |  |  |

| Total EHS Lenght (00h) | Resered            | Data Segment     | Lenght (0000h) |  |  |  |

| 12 (MSB)               | 13                 | 14               | 15 (LSB)       |  |  |  |

|                        | Data Buffer Offset |                  |                |  |  |  |

| 16 (MSB)               | 17                 | 18               | 19 (LSB)       |  |  |  |

|                        | Data Tran          | sfer Count       |                |  |  |  |

| 20                     | 21                 | 22               | 23             |  |  |  |

|                        | Res                | ered             |                |  |  |  |

| 24                     | 25                 | 26               | 27             |  |  |  |

|                        | Resered            |                  |                |  |  |  |

| 28                     | 29                 | 30               | 31             |  |  |  |

| Resered                |                    |                  |                |  |  |  |

|                        | Header E2ECRC      | (omit if HD = 0) |                |  |  |  |

FIG. 15

| Data Out UPIU                           |                |                |                                         |  |  |  |

|-----------------------------------------|----------------|----------------|-----------------------------------------|--|--|--|

| 0                                       | 1              | 2              | 3                                       |  |  |  |

| xx00 0010b                              | Flags          | LUN            | Task Tag                                |  |  |  |

| 4                                       | 5              | 6 7            |                                         |  |  |  |

| Resered                                 | Resered        | Resered        | Resered                                 |  |  |  |

| 8                                       | 9              | 10 (MSB)       | <sup>11</sup> (MSB)                     |  |  |  |

| Total EHS Lenght (00h)                  | Resered        | Data Segm      | nent Lenght                             |  |  |  |

| 12 (MSB)                                | 13             | 14             | 15 (LSB)                                |  |  |  |

|                                         | Data Buf       | fer Offset     | '                                       |  |  |  |

| 16 (MSB)                                | 17             | 18             | <sup>19</sup> (LSB)                     |  |  |  |

| Data Transfer Count                     |                |                |                                         |  |  |  |

| 20                                      | 21             | 22             | 23                                      |  |  |  |

|                                         | Res            | ered           |                                         |  |  |  |

| 24                                      | 25             | 26             | 27                                      |  |  |  |

|                                         | Res            | ered           |                                         |  |  |  |

| 28                                      | 29             | 30             | 31                                      |  |  |  |

| *************************************** | Res            | ered           | *************************************** |  |  |  |

|                                         | Header E2ECR0  |                | _                                       |  |  |  |

| k                                       | k+1            | k+2            | k+3                                     |  |  |  |

| Data[0]                                 | Data[1]        | Data[2]        | Data[3]                                 |  |  |  |

|                                         |                |                | ,                                       |  |  |  |

| k+Lenght-4                              | k+Lenght-3     | k+Lenght-2     | k+Lenght-1                              |  |  |  |

| Data[Lenght-4]                          | Data[Lenght-3] | Data[Lenght-2] | Data[Lenght-1]                          |  |  |  |

| Data E2ECRC (omit if DD = 0)            |                |                |                                         |  |  |  |

| NOTE 1 k=32 if H                        | <b>)</b> = 0   |                |                                         |  |  |  |

FIG. 16

| Data In UPIU           |                                                  |                  |            |  |  |  |

|------------------------|--------------------------------------------------|------------------|------------|--|--|--|

| 0                      | 1                                                | 2                | 3          |  |  |  |

| xx10 0010b             | Flags                                            | LUN              | Task Tag   |  |  |  |

| 4                      | 5                                                | 6                | 7          |  |  |  |

| Resered                | Resered                                          | Resered          | Resered    |  |  |  |

| 8                      | 9                                                | 10 (MSB)         | 11 (MSB)   |  |  |  |

| Total EHS Lenght (00h) | Resered                                          | Data Segm        | ent Lenght |  |  |  |

| 12                     | 13                                               | 14               | 15 (LSB)   |  |  |  |

| ·                      | Data Buf                                         | fer Offset       | •          |  |  |  |

| 16 (MSB)               | 17                                               | 18               | 19 (LSB)   |  |  |  |

|                        | Data Tran                                        | sfer Count       | '          |  |  |  |

| 20                     | 21                                               | 22               | 23         |  |  |  |

| ·                      | Res                                              | ered             | •          |  |  |  |

| 24                     | 25                                               | 26               | 27         |  |  |  |

| ·                      | Res                                              | ered             | ,          |  |  |  |

| 28                     | 29                                               | 30               | 31         |  |  |  |

|                        | Res                                              | ered             |            |  |  |  |

|                        | Header E2ECR0                                    | C (omit if HD=0) |            |  |  |  |

| k                      | k+1                                              | k+2              | k+3        |  |  |  |

| Data[0]                | Data[1]                                          | Data[2]          | Data[3]    |  |  |  |

| r e e                  | * * *                                            | •••              | пп 1       |  |  |  |

| k+Lenght-4             | k+Lenght-3                                       | k+Lenght-2       | k+Lenght-1 |  |  |  |

| Data[Lenght-4]         | -4] Data[Lenght-3] Data[Lenght-2] Data[Lenght-1] |                  |            |  |  |  |

|                        | Data E2ECRC (omit if DD = 0)                     |                  |            |  |  |  |

| NOTE 1 k=32 if HD = 0  |                                                  |                  |            |  |  |  |

|                        |                                                  |                  |            |  |  |  |

FIG. 17

| RESPONSE UPIU                |                                                             |                  |               |  |  |  |

|------------------------------|-------------------------------------------------------------|------------------|---------------|--|--|--|

| 0                            | 1                                                           | 2                | 3             |  |  |  |

| xx10 0001b                   | xx10 0001b Flags                                            |                  | Task Tag      |  |  |  |

| 4 Command                    | 5                                                           | 6                | 7             |  |  |  |

| Resered Set Type             | Resered                                                     | Resered          | Resered       |  |  |  |

| 8                            | 9                                                           | 10 (MSB)         | 11 (MSB)      |  |  |  |

| Total EHS Lenght (00h)       | Device Information                                          | Data Segm        | ent Lenght    |  |  |  |

| 12 (MSB)                     | 13                                                          | 14               | 15 (LSB)      |  |  |  |

|                              | Residual Tra                                                | insfer Count     | •             |  |  |  |

| 16                           | 17                                                          | 18               | 19            |  |  |  |

|                              | Res                                                         | ered             | •             |  |  |  |

| 20                           | 21                                                          | 22               | 23            |  |  |  |

|                              | Resi                                                        | ered             | '             |  |  |  |

| 24                           | 25                                                          | 26               | 27            |  |  |  |

|                              | Resi                                                        | ered             | ,             |  |  |  |

| 28                           | 29                                                          | 30               | 31            |  |  |  |

|                              | Res                                                         | ered             | •             |  |  |  |

|                              | Header E2ECR0                                               | C (omit if HD=0) |               |  |  |  |

| k (MSB)                      | k+1 (LSB)                                                   | k+2              | k+3           |  |  |  |

| Sense Da                     | ita Lenght                                                  | Sense Data[0]    | Sense Data[1] |  |  |  |

| * n n                        | · · •                                                       |                  | n x .         |  |  |  |

| k+16                         | k+17                                                        | k+18             | k+19          |  |  |  |

| Sense Data[14]               | Sense Data[14] Sense Data[15] Sense Data[16] Sense Data[17] |                  |               |  |  |  |

| Data E2ECRC (omit if DD = 0) |                                                             |                  |               |  |  |  |

| NOTE 1 k=32 if HD = 0        |                                                             |                  |               |  |  |  |

FIG. 18

FIG. 19

FIG. 20

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

### METHOD OF MANAGING MESSAGE TRANSMISSION FLOW AND STORAGE DEVICE USING THE METHOD

# CROSS-REFERENCE TO RELATED APPLICATION

[0001] This U.S. non-provisional application claims the benefit of priority under 35 U.S.C. §119 to Korean Patent Application No. 10-2015-0020965 filed in the Korean Intellectual Property Office on Feb. 11, 2015, the disclosure of which is incorporated herein in its entirety by reference.

#### BACKGROUND

[0002] 1. Field

[0003] Example embodiments of the inventive concepts relate to a method and an apparatus for transmitting a message between a host and a device, and to a method of managing a message transmission flow and a storage device using the method.

[0004] 2. Description of Related Art

[0005] In general, interface standards that are used for message transmission between a host and a device have transmission flow including a command phase, a data phase, and a status phase. The status phase is a period for transmitting response information to the host after the device transmits or receives data. Accordingly, research into a method of minimizing latency between the data phase and the status phase is needed to improve system performance.

#### **SUMMARY**

[0006] According to an example embodiment of inventive concepts provides a method of managing a message transmission flow to reduce latency between a data phase and a status phase.

[0007] An example embodiment of inventive concepts provides a storage device that manages a message transmission flow to reduce latency between a data phase and a status phase.

[0008] According to an example embodiment of inventive concepts, there is provided a method of managing a message transmission flow, the method including receiving, at a storage device, response transmission type information in at least one selected from a command phase and a data phase, and transmitting response information to a host during at least one of a normal mode and a fast mode having based on the received response transmission type information, the normal and fast mode having different latencies. The response transmission type information is a reserved bit, the reserved bit is included in at least one of a header of command information and in a header of data, and the host is configured to transmit the reserved bit

**[0009]** The method of managing the message transmission flow further comprising interfacing between the host and the storage device based on a transmission flow, the transmission flow including a command phase, a data phase and a status phase.

[0010] The receiving of the response transmission type information is through a reserved bit included in a universal flash storage (UFS) protocol information unit (UPIU) header, if the host and the storage device interface with each other using the UFS. In an example embodiment, the receiving of the response transmission type information is in a read data transmission flow and/or in a write data transmission flow, the

storage device is configured to receive the response transmission type information through a reserved bit, the reserved bit is included in a header of command information and/or in a header of data. The reserved bit is included in a header of final data in the data phase.

[0011] The transmitting of the response information to the house further comprises, determining whether a response transmission mode is at least one of the normal mode and the fast mode based on the received response transmission type information; loading the response information on final data; transmitting to the host the response information and the final data in the data phase if it is determined that the response transmission mode in a read data transmission flow is the fast mode; transmitting the response information to the host after receiving final data from the host if it is determined that the transmission mode in a write data transmission flow is the fast mode; and receiving the final data if the response information of the fast mode is received through a reserved bit included in a header of the final data of the data phase in the write data transmission flow.

[0012] The transmitting of the response information and the final data to the host further comprises, setting a reserved bit and loading the response information on the final data to transmit both the response information and the final data to the host. The reserved bit is configured to indicate the response transmission type information included in a header of final data in the data phase, and assign a value indicating the response transmission type information of the fast mode if it is determined that in the read data transmission flow the mode is the fast mode.

[0013] According to another non-limiting example embodiment of inventive concepts, there is provided a storage device including a memory device, and a memory controller configured to write data to the memory device or reading data from the memory device based on command received from a host, transmit a response information to the host in format least one of a normal mode and a fast mode based on a response transmission type information received from the host, the normal mode and the fast mode having different latencies, interfacing between the host and the memory device based at least one of a command phase and a data phase.

[0014] The memory controller is further configured to receive the response transmission type information through a reserved bit; the reserved bit is included in at least one of a header of command information and data transmitted from the host.

[0015] The memory controller of the example embodiment further comprises a command queue configured to store command information received from the host; a buffer memory configured to store data, the data stored is either received from the host or read from the memory device; and a controller. The controller is configured to load the response information on final data read from the buffer memory based on a read command when the response transmission type information set to the fast mode in a read data transmission flow is received, and transmit the response information and the final data to the host. The controller is also configured to set a reserved bit and load the response information on the final data to transmit both the response information and the final data to the host. According to another non-limiting example embodiment of inventive concepts, there is provided a computing system including a host and a storage device. The host is configured to transmit response transmission type information to a storage device in at least one of a command phase and a data phase. The storage device is configured to transmit response information to the host in at least one of a normal mode and/or a fast mode based on the response transmission type information received from the host. The normal mode and the fast mode having different latencies.

[0016] In some example embodiments, in accordance with inventive concept, when it is determined that a response transmission mode in a read data transmission flow is the fast mode, the storage device loads the response information on final data to be transmitted to the host in the data phase and transmits both the response information and the final data to the host.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0017] The foregoing and other features of the inventive concepts will be apparent from the more particular description of non-limiting example embodiments of the inventive concepts, as illustrated in the accompanying drawings in which like reference characters refer to like parts throughout the different views. The drawings are not necessarily to scale, emphasis instead being placed upon illustrating principles of the inventive concepts. In the drawings:

[0018] FIG. 1 is a diagram illustrating a structure of a computing system according to an example embodiment of inventive concepts;

[0019] FIG. 2 is a diagram of a computing system showing a detailed structure of a storage device illustrated in FIG. 1; [0020] FIG. 3 is a diagram illustrating a structure of a host illustrated in FIG. 1;

[0021] FIG. 4 is a diagram illustrating a program and data which are stored in RAM illustrated in FIG. 3;

[0022] FIG. 5 is a diagram illustrating a detailed structure of a memory controller illustrated in FIG. 2;

[0023] FIG. 6 is a diagram illustrating a detailed structure of a memory device illustrated in FIG. 2;

[0024] FIG. 7 is a diagram illustrating a memory cell array illustrated in FIG. 6;

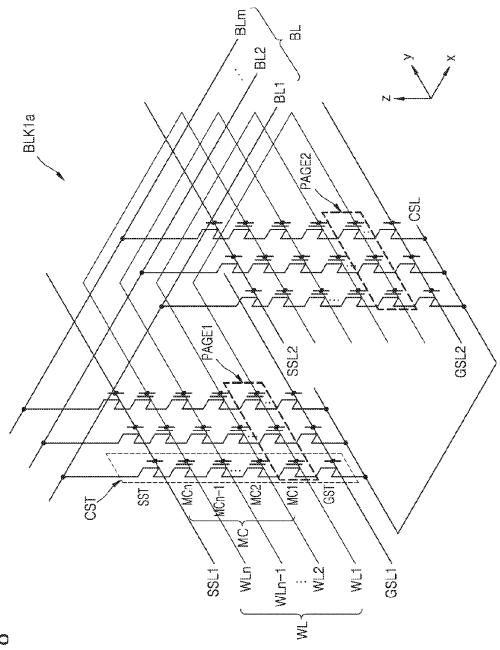

[0025] FIG. 8 is a circuit diagram of a first memory block included in a memory cell array illustrated in FIG. 6;

[0026] FIG. 9 is a diagram illustrating a universal flash storage (UFS) protocol information unit (UPIU) header format according to an example embodiment of inventive concepts;

[0027] FIG. 10 is a diagram illustrating content of a flag field of a UPIU header according to a JEDEC standard;

[0028] FIG. 11 is a diagram illustrating the definition of a flag field of a UPIU header according to an example embodiment of inventive concepts;

[0029] FIG. 12 is a diagram illustrating the definition of a flag field of a UPIU header according to another example embodiment of inventive concepts;

[0030] FIG. 13 is a diagram illustrating content of a command UPIU according to an example embodiment of inventive concepts;

[0031] FIG. 14 is a diagram illustrating content of a ready to transfer (RTT) UPIU according to an example embodiment of inventive concepts;

[0032] FIG. 15 is a diagram illustrating content of a data out UPIU according to an example embodiment of inventive concepts:

[0033] FIG. 16 is a diagram illustrating content of a data in UPIU according to an example embodiment of inventive concepts;

[0034] FIG. 17 is a diagram illustrating content of a response UPIU according to an example embodiment of inventive concepts;

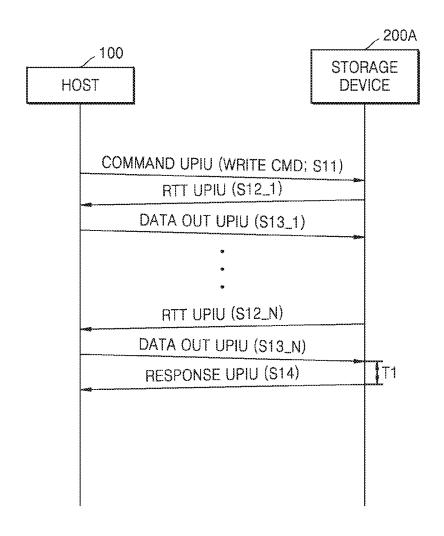

[0035] FIG. 18 is a flowchart illustrating a write message transmission flow for transmitting response information in a normal mode, according to an example embodiment of inventive concepts;

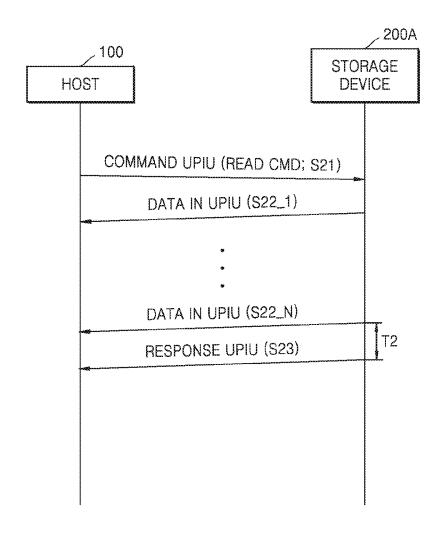

[0036] FIG. 19 is a flowchart illustrating a read message transmission flow for transmitting response information in a normal mode, according to an example embodiment of inventive concepts;

[0037] FIG. 20 is a flowchart illustrating a write message transmission flow for transmitting response information in a fast mode, according to an example embodiment of inventive concepts;

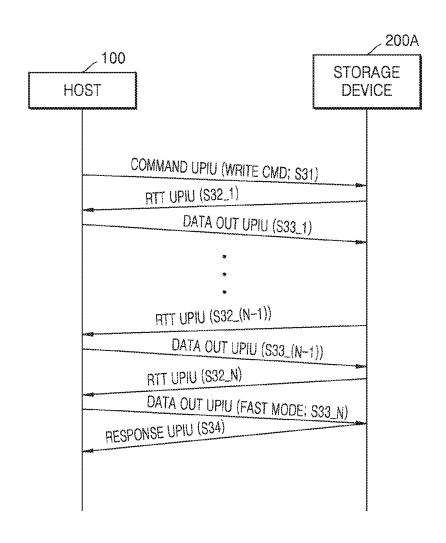

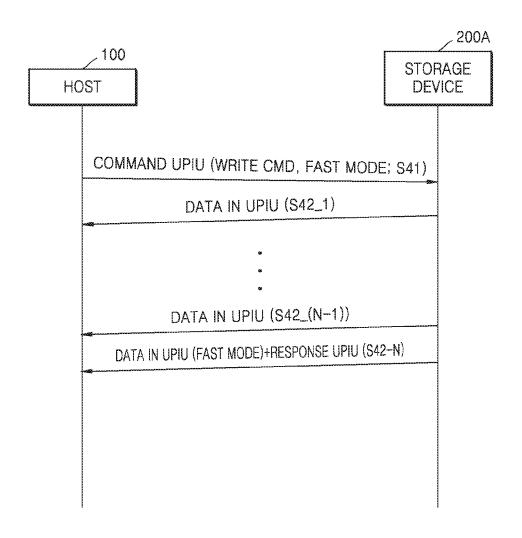

[0038] FIG. 21 is a flowchart illustrating a read message transmission flow for transmitting response information in a fast mode, according to an example embodiment of inventive concepts;

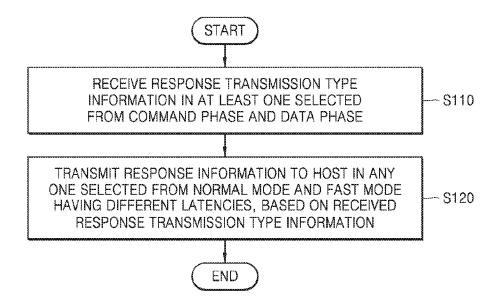

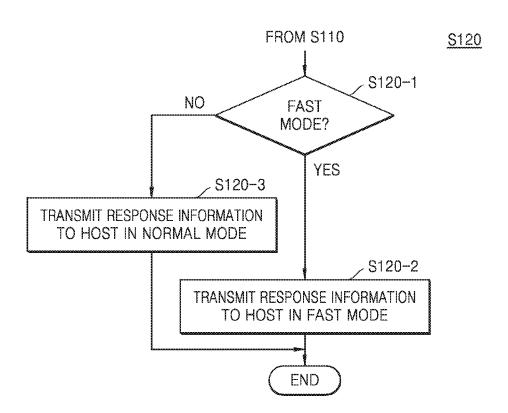

[0039] FIG. 22 is a flowchart illustrating a method of managing a message transmission flow, according to an example embodiment of inventive concepts;

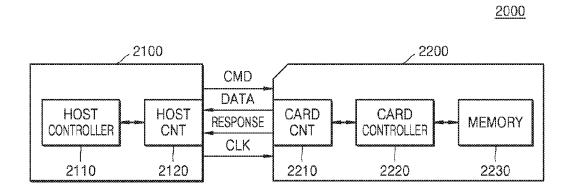

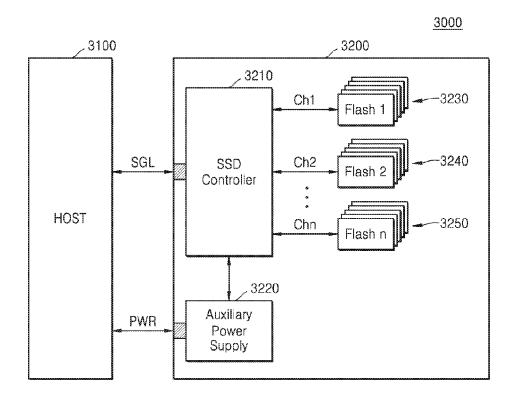

[0040] FIG. 23 is a flowchart illustrating a response information transmission operation illustrated in FIG. 22 in detail; [0041] FIG. 24 is a block diagram of a memory card system using the method of managing a message transmission flow, according to an example embodiment of inventive concepts; [0042] FIG. 25 is a block diagram of a solid state drive (SSD) system using the method of managing a message transmission flow, according to an example embodiment of inventive concepts; and

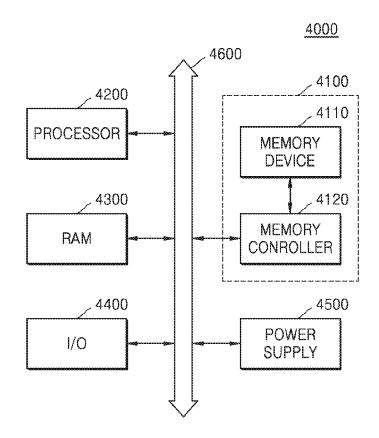

[0043] FIG. 26 is a diagram illustrating a structure of a computing system using the method of managing a message transmission flow, according to an example embodiment of inventive concepts.

## DETAILED DESCRIPTION OF EXAMPLE EMBODIMENTS

[0044] The inventive concept now will be described more fully hereinafter with reference to the accompanying drawings, in which elements of the inventive concepts are shown. The inventive concepts may, however, be embodied in many different forms and should not be construed as limited to the exemplary embodiments set forth herein. Rather, these example embodiments, in accordance with the inventive concepts, are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the inventive concepts to one of ordinary skill in the art. As the inventive concepts allow for various changes and numerous embodiments, particular embodiments will be illustrated in the drawings and described in detail in the written description. However, this is not intended to limit the inventive concepts to particular modes of practice, and it is to be appreciated that all changes, equivalents, and substitutes that do not depart from the spirit and technical scope of the inventive concepts are encompassed in the inventive concepts. Like reference numerals refer to like elements throughout. Sizes of structures may be greater or less than real structures for clarity of the inventive concepts.

[0045] The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of exemplary embodiments. As used herein, the singular forms "a", "an", and "the" are intended to include the plural forms as well, unless the context clearly indicates oth-

erwise. It will be further understood that the terms "comprises", "comprising", "includes", and/or "including" when used herein, specify the presence of stated features, integers, steps, operations, elements, components, or combinations thereof but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, or combinations thereof.

[0046] It will be understood that when an element is referred to as being "connected" or "coupled" to another element, it can be directly connected or coupled to the other element or intervening elements may be present. In contrast, when an element is referred to as being "directly connected" or "directly coupled" to another element, there are no intervening elements present. Other words used to describe the relationship between elements or layers should be interpreted in a like fashion (e.g., "between" versus "directly between," "adjacent" versus "directly adjacent," "on" versus "directly on"). As used herein the term "and/or" includes any and all combinations of one or more of the associated listed items.

[0047] Unless otherwise defined, all terms (including technical and scientific terms) used herein have the same meaning as commonly understood by one of ordinary skill in the art to which exemplary embodiments belong. It will be further understood that terms, such as those defined in commonly used dictionaries, should be interpreted as having a meaning that is consistent with their meaning in the context of the relevant art and will not be interpreted in an idealized or overly formal sense unless expressly so defined herein. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items.

[0048] FIG. 1 is a diagram illustrating a structure of a computing system 1000 according to an example embodiment of the inventive concept.

[0049] As illustrated in FIG. 1, the computing system 1000 includes a host 100 and a storage device 200.

[0050] The host 100 and the storage device 200 are electrically connected to each other. A standard of an interface that is used between the host 100 and the storage device 200 has a transmission flow including a command phase, a data phase, and a status phase. Response information is transmitted in the status phase.

[0051] For example, interfaces including, but not limited to, may be applied to the example embodiments of the inventive concepts between the host 100 and the storage device 200: a universal flash storage (UFS) interface, an embedded multi-media card (eMMC) interface, a serial advanced technology attachment (SATA) interface, a serial advanced technology attachment express (SATAe) interface, a small computer system interface (SCSI), a small computer system interface express (SCSIe) interface, and/or a non-volatile memory express (NVMe).

[0052] The host 100 transmits a command CMD, which is issued based on a task to be performed, to the storage device 200. For example, the command CMD issued from the host 100 may include a write command and/or a read command. The host 100 transmits data DATA to be stored in the storage device 200 and/or receives data DATA read from the storage device 200. The storage device 200 transmits response information RESPONSE, which indicates a result of command execution, to the host 100.

[0053] In an example embodiment of the inventive concepts, when data to be processed is stored in the storage device 200, the host 100 transmits a read command to the

storage device 200. The host 100 transmits a write command to the storage device 200 to store processed data in the storage device 200.

[0054] In another example embodiment of the inventive concepts, the host 100 transmits a read command and/or a write command, which is used for performing at least one selected from a page-in operation and a page-out operation for a memory swapping operation when a page fault occurs, to the storage device 200. The page fault occurs when a page, which is required to be read to perform an application process in the host 100, is not stored in the host 100.

[0055] The storage device 200 performs a read operation and/or a program operation according to a command received from the host 100. In other words, the storage device 200 performs a read operation for reading data in response to a read command received from the host 100. The storage device 200 performs a program operation for storing data in response to a write command received from the host 100.

[0056] The storage device 200 transmits the response information RESPONSE, which indicates a result of the execution of a command received from the host 100, to the host 100. For example, in response to a write command received from the host 100, the storage device 200 receives data from the host 100, processes the data according to the write command, and then transmits response information RESPONSE, which indicates whether the write command was normally executed, to the host 100. In another example embodiment of the inventive concepts, in response to a read command received from the host 100, the storage device 200 transmits data read therefrom to the host 100 and then transmits response information RESPONSE, which indicates whether the read command was normally executed, to the host 100.

[0057] In example embodiment of the inventive concepts, the host 100 includes a fast response support module 101, and the storage device 200 includes a fast response processing module 201.

[0058] The fast response support module 101 and the fast response processing module 201 are modules for reducing latency between a data phase and a status phase and may be implemented with software and/or hardware.

[0059] The fast response support module 101 supports an operation of setting response transmission type information in at least one selected from a command phase and/or a data phase. For example, a reserved bit included in a header of command information or a header of data may be allocated as a bit for determining a response transmission type.

[0060] The fast response support module 101 may set response transmission type information by using a reserved bit included in a header of command information or a header of data, to be transmitted to the storage device 200. In other words, the response transmission type information may be set by using a reserved bit allocated for the response transmission type information.

[0061] In an example embodiment of the inventive concepts, the fast response support module 101 may set response transmission type information of a fast mode to a default value. As another example of the inventive concepts, the fast response support module 101 may also set response transmission type information of a normal mode to a default value. As another example of the inventive concepts, the fast response support module 101 may also set response transmission type information of the normal mode or the fast mode based on a vendor's selection and/or a user's selection.

[0062] In an example embodiment of the inventive concepts, the fast response support module 101 may set response transmission type information by using a reserved bit included in a header of command information in a command phase of a read data transmission flow. In detail, the fast mode may be set when a bit allocated to define a response transmission type from among reserved bits included in a header of command information in a command phase of a read data transmission flow is set to a first logic value, and the normal mode may be set when the bit is set to a second logic value.

[0063] In an example embodiment of the inventive concepts, the fast response support module 101 may set response transmission type information by using a reserved bit included in a header of command information in a data phase of write data transmission flow. The fast mode may be set when a bit allocated to define a response transmission type from among reserved bits included in a header of final data that is transmitted to the storage device 200 in a data phase of a write data transmission flow is set to a first logic value, and the normal mode may be set when the bit is set to a second logic value.

[0064] In an example embodiment of the inventive concepts, the fast response support module 101 supports a function of parsing response information received after data and processing parsed information when a bit allocated to determine a response transmission type from among reserved bits included in a header of data that is received from the storage device 200 in a data phase of a read data transmission flow is set to a value indicating the fast mode.

[0065] The fast response processing module 201 supports a function of transmitting response information to the host 100 in any one selected from the normal mode and the fast mode having different latencies, based on response transmission type information received in at least one selected from a command phase and/or a data phase.

[0066] In an example embodiment of the inventive concepts, when response transmission type information set to a fast mode in a write data transmission flow is received from the host 100, the fast response processing module 201 directly generates response information when the fast response processing module 201 receives final data from the host 100 and transmits the generated response information to the host 100.

[0067] In an example embodiment of the inventive concepts, when response transmission type information set to a fast mode in a read data transmission flow is received from the host 100, the fast response processing module 201 loads response information on final data that is transmitted to the host 100 in a data phase, and transmits the data loaded with the response information to the host 100. In detail, when response transmission type information set to a fast mode in a read data transmission flow is received from the host 100, the fast response processing module 201 sets a bit, allocated to define a response transmission type from among reserved bits included in a header of final data to be transmitted to the host 100, to a value indicating the fast mode, and loads response information on the final data and transmits the final data loaded with the response information to the host 100.

[0068] FIG. 2 is a diagram of a computing system 1000a showing a detailed structure of the storage device 200 illustrated in FIG. 1.

[0069] As illustrated in FIG. 2, the computing system 1000A includes a host 100 and a storage device 200A. The host 100 and the storage device 200A correspond to the host

100 and the storage device 200, respectively, of FIG. 1. The storage device  $200\mathrm{A}$  includes a memory controller  $210\mathrm{A}$  and a memory device  $220\mathrm{A}$ .

[0070] In an example embodiment of the inventive concepts, the computing system  $1000\mathrm{A}$  may be including, but not limited to, a personal computer, a set-top-box, a digital camera, a navigation device, a mobile device, and/or a smart card system.

[0071] The host 100 has been described above with reference to FIG. 1, and thus, repeated descriptions thereof are omitted.

[0072] The memory device 220A may be any one of various types of memory devices. In addition, the memory device 220A may be a flash memory device that is a type of nonvolatile memory device. Examples of non-volatile memory devices include, but are not limited to, phase change RAM (PRAM), ferroelectric RAM (FRAM), magnetic RAM (MRAM) as well as a flash memory device may be used as the memory device 220A. In an example embodiment of the inventive concepts, the memory device 220A may have a structure obtained by combining at least one non-volatile memory device with at least one volatile memory device, and the memory device 220A may also have a structure obtained by combining at least two types of non-volatile memory devices with each other.

[0073] The memory controller 210A performs an input/output (IO) processing operation in response to a command received from the host 100 so that the memory device 220A performs a read operation and/or a write operation.

[0074] The memory controller 210A transmits response information RESPONSE, which indicates a result of the execution of a command received from the host 100, to the host 100. In an example embodiment of the inventive concepts, in response to a write command received from the host 100, the storage device 200A receives data from the host 100, processes the data according to the write command, and then transmits response information RESPONSE, which indicates whether the write command was normally executed, to the host 100. In an example embodiment of inventive concepts, in response to a read command received from the host 100, the storage device 200A transmits data read therefrom to the host 100 and then transmits response information RESPONSE, which indicates whether the read command was normally executed, to the host 100.

[0075] The memory controller 210A includes a fast response processing module 201. The fast response processing module 201 has been described above, and thus, repeated descriptions thereof are omitted.

[0076] When response transmission type information set to a fast mode in a read data transmission flow is received from the host 100, the memory controller 210A loads response information RESPONSE on final data, which is transmitted to the host 100 in a data phase, by using the fast response processing module 201, and transmits the data loaded with the response information to the host 100. In an example embodiment of the inventive concepts, the memory controller 210A sets a bit, allocated to define a response transmission type from among reserved bits included in a header of final data to be transmitted to the host 100, to a value indicating the fast mode, and loads response information on the final data and transmits the final data loaded with the response information to the host 100.

[0077] When response transmission type information set to a fast mode in a write data transmission flow is received from

the host 100, the memory controller 210A directly generates response information by using the fast response processing module 201 when the memory controller 210A receives final data from the host 100, and transmits the generated response information to the host 100.

[0078] FIG. 3 is a diagram illustrating a structure of a host 100A corresponding to the host 100 illustrated in FIG. 1.

[0079] Referring to FIG. 3, the host 100A includes a processor 110, random access memory (RAM) 120, a device interface 130, and a bus 140.

[0080] The processor 110, the RAM 120, and the device interface 130 are electrically connected to each other via the bus 140. The processor 110, the RAM 120, and the device interface 130 may send and receive data and various control signals to and from each other via the bus 140.

[0081] The processor 110 may include, but not limited to, circuits for processing data and controlling operations of elements of the host 100A, interface circuits, and/or program codes. In an example embodiment of the inventive concepts, the processor 110 may include, but not limited to, a central processing unit (CPU), an advanced RISC machine (ARM), and/or an application specific integrated circuit (ASIC).

[0082] The RAM 120 may include SRAM and/or DRAM for storing data, commands, and/or program codes that are needed for an operation of the host 100A. The RAM 120 functions as a main memory. The RAM 120 stores a fast response support software (FRS SW) 101A. The FRS SW 101A includes program codes for performing a function of the fast response support module 101 described above with reference to FIG. 1.

[0083] The device interface 130 includes a data exchange protocol for exchanging data with a device connected to the host 100A and performs an interface between the host 100A and the device. In an example embodiment of the inventive concepts, the device connected to the host 100A may be a storage device.

[0084] Example embodiments of the device interface 130 may include, but are not limited to, a UFS interface, an advanced technology attachment (ATA) interface, a SATA interface, a SATA interface, a SATA interface, a parallel advanced technology attachment (PATA) interface, a universal serial bus (USB), a serial attached small computer system (SAS) interface, a small computer system interface (SCSI), a SCSIe, an embedded multimedia card (eMMC) interface, and/or a non-volatile memory express (NVMe) interface. However, the inventive concept is not limited thereto. Various standard interfaces having a transmission flow including a command phase, a data phase, and a status phase may be applied to the device interface 130.

[0085] The device interface 130 may transmit a command and data to a device and/or receive data and response information from the device, according to the control of the processor 110.

[0086] The processor 110 transmits response transmission type information to a device, connected to the device interface 130, in at least one of a command phase and a data phase by using program codes stored in the RAM 120. In an example embodiment of the inventive concepts, the processor 110 may drive the FRS SW 101A stored in the RAM 120 to perform a message transmission flow management operation by using a method as illustrated in FIGS. 18 through 23.

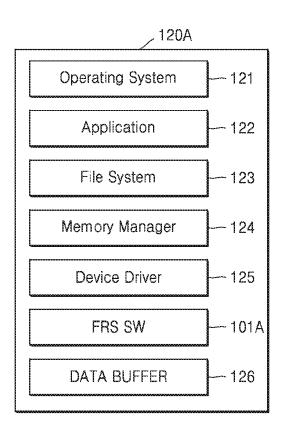

[0087] FIG. 4 is a diagram illustrating a program and data which are stored in RAM 120A that corresponds to the RAM 120 illustrated in FIG. 3.

[0088] Referring to FIG. 4, the RAM 120A may store an operating system 121, an application 122, a file system 123, a memory manager 124, a device driver 125, and a fast response support software (FRS SW) 101A. In addition, a region for a data buffer 126 may be assigned in the RAM 120A.

[0089] The operating system 121 is a program for controlling hardware and/or software resources of the host 100A. The operating system 121 functions as an interface between hardware and an application program, and manages resources of the host 100A.

[0090] The application 122 includes various application programs that are executed in the host 100A. In an example embodiment of the inventive concepts, the application 122 may include programs that support an operation for processing files and/or data.

[0091] The file system 123 is a program that manages logical addresses and storage locations to store files and/or data in the RAM 120A of the host 110A, and/or the storage device 200A connected to the host 100A, and/or to search for files and/or data.

[0092] The memory manager 124 is a program that controls a memory access operation for the RAM 120A, and/or a memory access operation for the storage device  $200\mathrm{A}$  connected to the host  $100\mathrm{A}$ .

[0093] The device driver 125 is a program that supports communication with the storage device 200A connected to the host 100A.

[0094] The FRS SW 101A has been described above, and thus repeated descriptions thereof are omitted.

[0095] The data buffer 126 is a storage region assigned to store data received from the storage device  $200\mathrm{A},$  and/or data to be transmitted to the storage device  $200\mathrm{A}.$

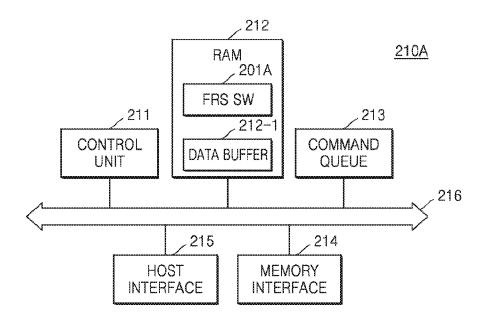

[0096] FIG. 5 is a diagram illustrating a detailed structure of the memory controller 210A illustrated in FIG. 2.

[0097] As illustrated in FIG. 5, the memory controller 210A includes a control unit 211, RAM 212, a command queue 213, a memory interface 214, a host interface 215, and a bus 216.

[0098] The control unit 211, the RAM 212, the command queue 213, the memory interface 214, and the host interface 215 are electrically connected to each other via the bus 216. Accordingly, data, addresses, and/or various control signals may be transmitted or received between the components of the memory controller 210A via the bus 216.

[0099] The RAM 212 may include an SRAM and/or DRAM for storing data, commands, and/or program codes that are necessary for an operation of the memory controller 210A.

[0100] A region for a data buffer 212-1, in which data transmitted from the host 100, and/or data to be transmitted to the host 100, is temporarily stored, and is assigned in the RAM 212. Data to be stored in the memory device 220A connected through the memory interface 214, and/or data read from the memory device 220A, is temporarily stored in the data buffer 212-1 of the RAM 212. An FRP SW 201A is stored in the RAM 212. The FRP SW 201A includes program codes for performing a function of the fast response processing module 201 illustrated in FIG. 1.

[0101] Commands received from the host 100 through the host interface 215, are sequentially stored in the command queue 213.

[0102] The control unit 211 controls an overall operation of the storage device 200A. The control unit 211 performs a

write operation, and/or read operation processing based on a command received from the host 100.

[0103] In an example embodiment of the inventive concepts, the control unit 211 stores a command received from the host 100 in the command queue 213. Also, the control unit 211 stores data received from the host 100, and/or data transmitted to the host 100 in the data buffer 212-1 of the RAM 212

[0104] In response to a write command received from the host 100, the control unit 211 assigns a buffer region, in which host data will be stored. Upon assigning a buffer region by the control unit 211, the data buffer 212-1 then transmits a message, which informs the host 100 that it is ready to receive data, to the host 100. The control unit 211 stores data received from the host 100 in an assigned region of the data buffer 212-1. The control unit 211 transmits response information indicating a processing state of the write command received from the host 100 to the host 100.

[0105] In response to a read command received from the host 100, the control unit 211 reads data from the memory device 220A, according to the read command, and stores the read data to the data buffer 212-1. Then, the control unit 211 reads data from the data buffer 212-1 and transmits the read data to the host 100 through the host interface 215. The control unit 211 transmits response information indicating a processing state of the read command received from the host 100 to the host 100.

[0106] The control unit 211 transmits response information to the host 100 in any one selected from the normal mode and/or the fast mode having different latencies, based on response transmission type information received in at least one selected from a command phase and a data phase.

[0107] In an example embodiment of the inventive concepts, when response transmission type information set to a fast mode in a write data transmission flow is received from the host 100, the control unit 211 drives the FRP SW 201A stored in the RAM 212, and transmits the response information to the host 100 in the fast mode. In detail, in a fast mode of write data transmission flow, the control unit 211 directly generates response information when receiving final data from the host 100, and transmits the generated response information to the host 100.

[0108] In an example embodiment of the inventive concepts, when response transmission type information set to a fast mode in a read data transmission flow is received from the host 100, the control unit 211 drives the FRP SW 201A stored in the RAM 212, and transmits the response information to the host 100 in the fast mode. In detail, in a fast mode of a read data transmission flow, the control unit 211 loads response information on final data to be transmitted to the host 100 in a data phase, and transmits the data loaded with the response information to the host 100. Accordingly, when response transmission type information set to a fast mode in a read data transmission flow is received from the host 100, the control unit 211 sets a bit, allocated to define a response transmission type from among reserved bits included in a header of final data to be transmitted to the host 100, to a value indicating the fast mode, and loads response information on the final data, and transmits the final data loaded with the response information to the host 100.

[0109] When response transmission type information set to a fast mode in a write data transmission flow, and/or a read

data transmission flow, is not received from the host 100, the control unit 211 transmits the response information to the host 100 in a normal mode.

[0110] In an example embodiment of the inventive concepts, when response transmission type information set to a normal mode in a write data transmission flow is received from the host 100, the control unit 211 receives final data from the host 100 and stores the received final data in the data buffer 212-1. Furthermore, the control unit 211 transmits response information indicating a processing state of a write command to the host 100 after completing an operation of writing data stored in the data buffer 212-1 to the memory device 220A connected through the memory interface 214.

[0111] In an example embodiment of the inventive concepts, when response transmission type information set to a normal mode in a write data transmission flow is received from the host 100, the control unit 211 receives final data from the host 100 and stores the received final data in the data buffer 212-1. Then, the control unit 211 completes the storing of host data in the data buffer 212-1, and then generates response information indicating a processing state of a write command and transmits the generated response information to the host 100. That is, the control unit 211 may transmit response information indicating a processing state of a write command to the host 100 before performing an operation of writing host data stored in the data buffer 212-1 to the memory device 220A.

[0112] In an example embodiment of the inventive concepts, when response transmission type information set to a normal mode in a read data transmission flow is received from the host 100, the control unit 211 completes a process of reading data, requested by the host 100, from the data buffer 212-1, and transmitting the read data to the host 100, and then generates response information indicating a processing state of a read command and transmits the generated response information to the host 100.

[0113] In an example embodiment of the inventive concepts, when response transmission type information set to a normal mode in a read data transmission flow is received from the host 100, the control unit 211 completes a process of reading data, requested by the host 100, from the data buffer 212-1, and transmitting the read data to the host 100, and then may generate response information indicating a processing state of a read command after emptying the data buffer 212-1 to transmit the generated response information to the host 100.

[0114] The memory interface 214 is electrically connected to the memory device 220A. The memory interface 214 may transmit a command, an address, and data to the memory device 220A under the control of the control unit 211, and/or may receive data from the memory device 220A. The memory interface 214 may be configured to support NAND flash memory and/or NOR flash memory. The memory interface 214 may be configured to perform software, and/or hardware interleaving operations, via a plurality of channels.

[0115] The host interface 215 includes a protocol for exchanging data with the host 100, and interfaces the storage device 200A with the host 100. The host interface 215 may be implemented by using interfaces including, but not limited to, a UFS interface, an ATA interface, a SATA interface, a SATAe interface, a PATA interface, a USB or SAS interface, a SCSI, a SCSIe, an eMMC interface, and/or an NVMe interface. The various standard interfaces having a transmission flow

including a command phase, a data phase, and/or a status phase may be applied to the host interface 215.

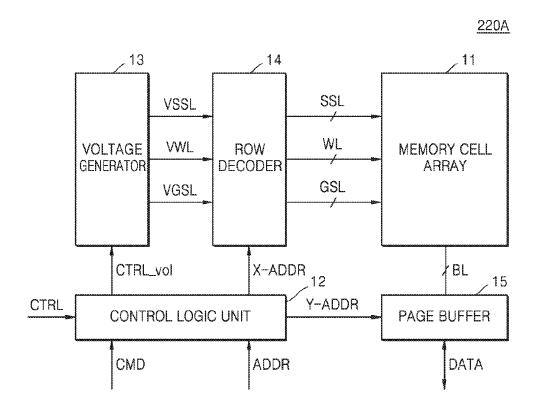

[0116] FIG. 6 is a diagram illustrating a detailed structure of the memory device  $220\mathrm{A}$  illustrated in FIG. 2.

[0117] Referring to FIG. 6, the memory device 220A may include a memory cell array 11, a control logic unit 12, a voltage generator 13, a row decoder 14, and a page buffer 15. The components included in the memory device 220A will now be described in detail.

[0118] The memory cell array 11 may be connected to at least one string selection line SSL, a plurality of word lines WL, and at least one ground selection line GSL, and may also be connected to a plurality of bit lines BL. The memory cell array 11 may include a plurality of memory cells MC (refer to FIG. 8) that are disposed at intersections of the plurality of bit lines BL and the plurality of word lines WL.

[0119] When an erasure voltage is applied to the memory cell array 11, the plurality of memory cells MC enter an erasure state. When a programming voltage is applied to the memory cell array 11, the plurality of memory cells MC enter a program state. At this time, each memory cell MC may have one selection from an erasure state, and first through n-th program states, P1 through Pn that are distinguished from each other according to a threshold voltage.

[0120] In the first through n-th program states P1 through Pn, n may be a natural number equal to or greater than 2. For example, when each memory cell MC is a 2-bit level cell, n may be 3. In an example embodiment of the inventive concepts, when each memory cell MC is a 3-bit level cell, n may be 7. In another example, when each memory cell MC is a 4-bit level cell, n may be 15. As such, the plurality of memory cells MC may include multi-level cells. However, exemplary embodiments of the inventive concept are not limited thereto, and the plurality of memory cells MC may include single-level cells.

[0121] The control logic unit 12 may receive a command signal CMD, an address signal ADDR, and a control signal CTRL from the memory controller 210A to output various control signals for writing the data DATA to the memory cell array 11 or for reading the data from the memory cell array 11. In this way, the control logic unit 12 may control overall operations of the memory device 220A.

[0122] The various control signals output by the control logic unit 12 may be provided to the voltage generator 13, the row decoder 14, and the page buffer 15. In detail, the control logic unit 12 may provide a voltage control signal CTRL\_vol to the voltage generator 13, may provide a row address signal X\_ADDR to the row decoder 14, and may provide a column address signal Y\_ADDR to the page buffer 15.

[0123] The voltage generator 13 may receive the voltage control signal CTRL\_vol to generate various voltages for executing a program operation, a read operation and an erasure operation with respect to the memory cell array 11. In detail, the voltage generator 13 may generate a first drive voltage VWL for driving the plurality of word lines WL, a second drive voltage VSSL for driving the at least one string selection line SSL, and a third drive voltage VGSL for driving the at least one ground selection line GSL.

[0124] The first drive voltage VWL may be a program (or write) voltage, a read voltage, an erasure voltage, a pass voltage, and/or a program verification voltage. The second drive voltage VSSL may be a string selection voltage SSL, including but not limited to, an on voltage or an off voltage.

The third drive voltage VGSL may be a ground selection voltage GSL, including but not limited to, an on voltage or an off voltage.

[0125] According to an example embodiment of the inventive concepts, the voltage generator 13 may receive the voltage control signal CTRL\_vol to generate a program start voltage as a program voltage, when a program loop starts, when the number of program loops performed is 1. As the number of program loops performed increases, the voltage generator 13 may generate a voltage that increases from the program start voltage by a step voltage in stages, as the program voltage.

[0126] The row decoder 14 may be connected to the memory cell array 11 through the plurality of word lines WL and may activate some of the plurality of word lines WL in response to the row address signal X\_ADDR received from the control logic unit 12. In detail, during a read operation, the row decoder 14 may apply a read voltage to a word line selected from the plurality of word lines WL, and apply a pass voltage to the remaining unselected word lines.

[0127] During a program operation, the row decoder 14 may apply a program voltage to the selected word line, and apply the pass voltage to the unselected word lines. According to an example embodiment of the inventive concepts, the row decoder 14 may apply a program voltage to the selected word line and an additionally selected word line, in at least one selected from a plurality of program loops.

[0128] The page buffer 15 may be connected to the memory cell array 11 via the plurality of bit lines BL. In detail, during a read operation, the page buffer 15 may operate as a sense amplifier so as to output data DATA stored in the memory cell array 11. During a program operation, the page buffer 15 may operate as a write driver so as to input the data DATA desired to be stored in the memory cell array 11.

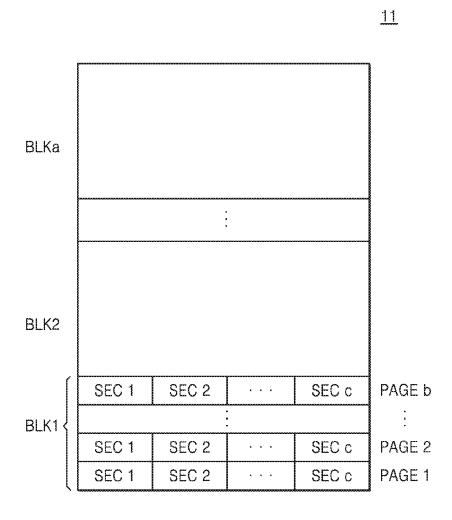

[0129] FIG. 7 is a diagram illustrating the memory cell array illustrated in FIG. 6.

[0130] Referring to FIG. 7, the memory cell array 11 may be a flash memory cell array. In this case, the memory cell array 11 may include a plurality of memory blocks BLK1, . . ., and BLKa (where "a" denotes a positive integer which is equal to or greater than two) and each of the memory blocks BLK1, . . . , and BLKa may include a plurality of pages PAGE1,..., and PAGEb (where "b" denotes a positive integer which is equal to or greater than two). In addition, each of the pages PAGE1, . . . , and PAGEb may include a plurality of sectors SEC1, . . . , and SECc (where "c" denotes a positive integer which is equal to or greater than two). Although only the pages PAGE1 through PAGEb and the sectors SEC1 through SECc of the memory block BLK1 are illustrated for convenience of explanation in FIG. 7, the other memory blocks BLK2 through BLKa may have the same structures as that of the memory block BLK1.

[0131] FIG. 8 is a circuit diagram of a first memory block BLK1a, which is an example embodiment of the memory block BLK1 included in the memory cell array 11 of FIG. 6.

[0132] Referring to FIG. 8, the first memory block BLK1a may be a NAND flash memory having a vertical structure. Each of the memory blocks BLK1 to BLKa may be implemented as shown in FIG. 8. In FIG. 8, a first direction is referred to as an x-direction, a second direction is referred to as a y-direction, and a third direction is referred to as a z-direction. However, example embodiments of the inventive concepts are not limited thereto, and the first through third directions may vary.

[0133] The first memory block BLK1a may include a plurality of cell strings CST, a plurality of word lines WL, a plurality of bit lines BL, a plurality of ground selection lines GSL1 and GSL2, a plurality of string selection lines SSL1 and SSL2, and a common source line CSL. The number of cell strings CST, the number of word lines WL, the number of bit lines BL, the number of ground selection lines GSL1 and GSL2, and the number of string selection lines SSL1 and SSL2 may vary according to example embodiments of the inventive concepts.

[0134] Each of the cell strings CST may include a string selection transistor SST, a plurality of memory cells MC, and a ground selection transistor GST that are serially connected to each other between a bit line BL corresponding to the cell string CST, and the common source line CSL. However, example embodiments of the inventive concepts are not limited thereto. According to another example embodiment, each cell string CST may further include at least one dummy cell. According to another example embodiment, each cell string CST may include at least two string selection transistors SST, or at least two ground selection transistors GST.

[0135] Each cell string CST may extend in the third direction (z-direction). In detail, each cell string CST may extend on a substrate in a vertical direction (z-direction). Accordingly, the first memory block BLK1a including the cell strings CST may be referred to as a vertical-direction NAND flash memory. As such, by extending each cell string CST in the vertical direction (z-direction) on a substrate, the integration density of the memory cell array 11 may increase.

[0136] The plurality of word lines WL may each extend in the first x-direction, and in the second y-direction y, and each word line WL may be connected to memory cells MC corresponding thereto. Accordingly, a plurality of memory cells MC arranged adjacent to each other on the same plane in the first x-direction, and the second y-direction, may be connected to each other by an identical word line WL. In detail, each word line WL may be connected to gates of memory cells MC to control the memory cells MC. In this case, the plurality of memory cells MC may store data and may be programmed, read, and/or erased under the control of the connected word line WL.

[0137] The plurality of bit lines BL may extend in the first x-direction, and may be connected to the string selection transistors SST. Accordingly, a plurality of string selection transistors SST arranged adjacent to each other in the first x-direction may be connected to each other by an identical bit line BL. In detail, each bit line BL may be connected to drains of the plurality of string selection transistors SST.

[0138] The plurality of string selection lines SSL1 and SSL2 may each extend in the second y-direction, and may be connected to the string selection transistors SST. Accordingly, a plurality of string selection transistors SST arranged adjacent to each other in the second y-direction may be connected to each other by an identical string selection line SSL1 or SSL2. In detail, each string selection line SSL1 or SSL2 may be connected to gates of the plurality of string selection transistors SST to control the plurality of string selection transistors SST.

[0139] The plurality of ground selection lines GSL1 and GSL2 may each extend in the second y-direction, and may be connected to the ground selection transistors GST. Accordingly, a plurality of ground selection transistors GST arranged adjacent to each other in the second y-direction may be connected to each other by an identical ground selection line

GSL1 or GSL2. In detail, each ground selection line GSL1 or GSL2 may be connected to gates of the plurality of ground selection transistors GST to control the plurality of ground selection transistors GST.

**[0140]** The ground selection transistors GST respectively included in the cell strings CST may be connected to each other by the common source line CSL. In detail, the common source line CSL may be connected to sources of the ground selection transistors GST.

[0141] A plurality of memory cells MC connected to an identical word line WL, and to an identical string selection line SSL1 or SSL2, and arranged adjacent to each other in the second y-direction may be referred to as a page PAGE. For example, a plurality of memory cells MC that are connected to a first word line WL1, and to a first string selection line SSL1, and are arranged adjacent to each other in the second y-direction may be referred to as a first page PAGE1. A plurality of memory cells MC that are connected to the first word line WL1, and to a second string selection line SSL2, and are arranged adjacent to each other in the second direction y may be referred to as a second page PAGE2.

[0142] To perform a program operation with respect to a memory cell MC, 0V may be applied to a bit line BL, an "on" voltage may be applied to a string selection line SSL, and an "off" voltage may be applied to a ground selection line GSL. The "on" voltage may be equal to or greater than the threshold voltage so that a string selection transistor SST is turned on, and the "off" voltage may be smaller than the threshold voltage so that the ground selection transistor GST is turned off. A program voltage may be applied to a memory cell selected from the memory cells MC, and a pass voltage may be applied to the remaining unselected memory cells. In response to the program voltage, electric charges may be injected into the memory cells MC due to F-N tunneling. The pass voltage may be greater than the threshold voltage of the memory cells MC.

**[0143]** To perform an erasure operation with respect to the memory cells MC, an erasure voltage may be applied to the body of the memory cells MC, and 0V may be applied to the word lines WL. Accordingly, data stored in the memory cells MC may be temporarily erased.