US 20150255518A1

### (19) United States

## (12) Patent Application Publication Watanabe et al.

## (10) **Pub. No.: US 2015/0255518 A1**(43) **Pub. Date:** Sep. 10, 2015

# (54) TOUCH SENSOR, TOUCH PANEL, AND MANUFACTURING METHOD OF TOUCH PANEL

(71) Applicant: Semiconductor Energy Laboratory

Co., Ltd., Kanagawa-ken (JP)

(72) Inventors: **Kazunori Watanabe**, Atsugi (JP); **Hiroyuki MIYAKE**, Atsugi (JP);

Shunpei YAMAZAKI, Tokyo (JP)

(73) Assignee: Semiconductor Energy Laboratory Co., Ltd., Kanagawa-ken (JP)

(21) Appl. No.: 14/639,336

(22) Filed: Mar. 5, 2015

#### (30) Foreign Application Priority Data

#### **Publication Classification**

(51) Int. Cl. *H01L 27/32* (2006.01) *H01L 27/12* (2006.01) (52) U.S. Cl.

#### (57) ABSTRACT

To provide a touch sensor including a transistor and a capacitor in which the transistor and the capacitor are electrically connected to each other, the capacitor includes a pair of electrodes and a dielectric layer, the dielectric layer is located between the pair of electrodes, and one of the pair of electrodes includes an oxide conductor layer. To provide a touch panel including the touch sensor, a light-blocking layer, and a display element in which the touch sensor is located more on the display surface side of the touch panel than on the display element side, the light-blocking layer is located more on the display surface side than on the touch sensor side, the display element includes a portion overlapping with the capacitor, and the light-blocking layer includes a portion overlapping with the transistor.

FIG. 2

FIG. 4A

FIG. 4B

FIG. 4C

FIG. 4D

FIG. 5B

FIG. 6B FIG. 6A 141 X1 X2 X1 X2 3Ó2 338a 338b 338 FIG. 6C FIG. 6D X1 X2 X1 X2 FIG. 6E FIG. 6F 306 306a 306b 308a 305 **X**1 X1 X2 X2 FIG. 6G 304 FIG. 6H 145 304a 304b 305 308a 338b X1 X2 X1 X2

FIG. 18A

FIG. 18B

FIG. 18C

FIG. 18D

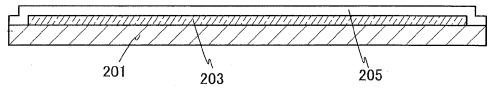

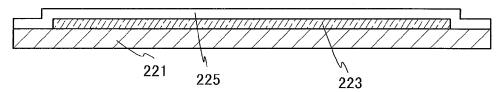

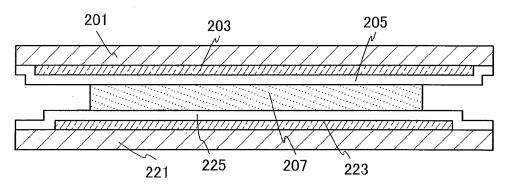

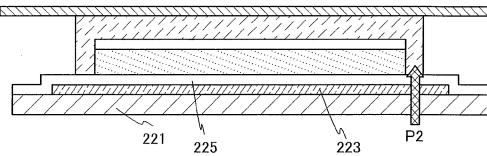

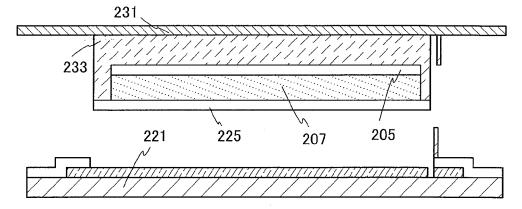

FIG. 19A 203 205 P1 201 221 225 207 223

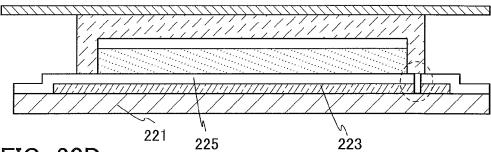

FIG. 20B

FIG. 20C

FIG. 20D

FIG. 23A FIG. 23B FIG. 23C 56 58 ∽55a -55b ~55c 53b 53c 53a 51c -51a 51b FIG. 23D FIG. 23E FIG. 23F 51b 51c ,51b 53b .53c \_\_55c 55b 58 <sub>~</sub>57 57 ≤ 59a -59b `55b -56 ~56 <del>- 5</del>6 51a 51a `51a FIG. 23G FIG. 23H 60b 51c 59c 53c .55c .55c -58 -57 58 -57 -55a 59c -56 ₹60a `51a

FIG. 26A

FIG. 26B

FIG. 26C

FIG. 26D

FIG. 26E

FIG. 26F

FIG. 26G

FIG. 26H

FIG. 26I

<u>345</u>

325

322

FIG. 27A

FIG. 27B

FIG. 27C

FIG. 27D

FIG. 28A

1 nm

1 nm

FIG. 29A out-of-plane method GAAC-OS

FIG. 29B in-plane method CAAC-OS

FIG. 29C in-plane method single crystal OS

FIG. 30A

FIG. 30B

FIG. 32A

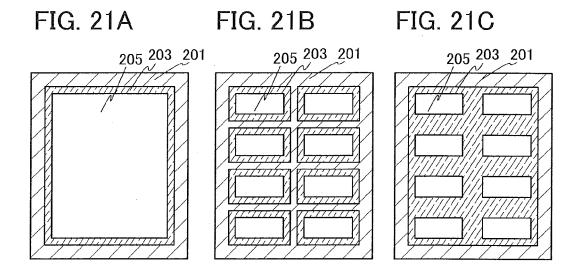

FIG. 32B

FIG. 32C

FIG. 33

### FIG. 34

FIG. 36A

FIG. 36B

InGaZnO<sub>4</sub>

In: O Ga: O Zn: O O: O

FIG. 40A

Ga-Zn-O layer

In-O layer

Ga-Zn-O layer

FIG. 40B

0-0.3psec after Ar entrance

0-0.3psec after O entrance

FIG. 41A

FIG. 41B

FIG. 42

FIG. 43A

FIG. 43B

FIG. 44

FIG. 45A

FIG. 45B

FIG. 46

FIG. 47

# TOUCH SENSOR, TOUCH PANEL, AND MANUFACTURING METHOD OF TOUCH PANEL

#### TECHNICAL FIELD

[0001] One embodiment of the present invention relates to a touch sensor, particularly to a touch sensor having flexibility. One embodiment of the present invention relates to a touch panel, particularly to a touch panel having flexibility.

[0002] Note that one embodiment of the present invention is not limited to the above technical field. One embodiment of the invention disclosed in this specification and the like relates to an object, a method, or a manufacturing method. One embodiment of the present invention relates to a process, a machine, manufacture, or a composition of matter. Specifically, examples of the technical field of one embodiment of the present invention disclosed in this specification include a semiconductor device, a display device, a light-emitting device, a power storage device, a storage device, an electronic device, a lighting device, a method for driving any of them, and a method for manufacturing any of them.

[0003] In this specification and the like, a semiconductor device generally means a device that can function by utilizing semiconductor characteristics. A semiconductor element such as a transistor, a semiconductor circuit, an arithmetic device, and a memory device are each an embodiment of a semiconductor device. An imaging device, a display device, a liquid crystal display device, a light-emitting device, an electro-optical device, a power generation device (including a thin film solar cell, an organic thin film solar cell, and the like), and an electronic device may each include a semiconductor device.

#### BACKGROUND ART

[0004] Attention has been focused on a technique for forming a transistor using a semiconductor thin film formed over a substrate having an insulating surface (also referred to as a field-effect transistor (FET) or a thin film transistor (TFT)). Such transistors are applied to a wide range of electronic devices such as an integrated circuit (IC) and an image display device (display device). A semiconductor material typified by silicon is widely known as a material for a semiconductor thin film that can be used for a transistor. As another material, an oxide semiconductor has been attracting attention.

[0005] For example, a technique in which a transistor is manufactured using an amorphous oxide containing In, Zn, Ga, Sn, and the like as an oxide semiconductor is disclosed in Patent Document 1. Furthermore, a technique in which a transistor using an oxide thin film and a self-aligned top-gate structure is manufactured is disclosed in Patent Document 2.

[0006] Furthermore, a flexible device in which a functional element such as a semiconductor element, a display element, or a light-emitting element is provided over a substrate having flexibility (hereinafter also referred to as a flexible substrate) has been developed. Typical examples of the flexible device include, as well as a lighting device and an image display device, a variety of semiconductor circuits including a semiconductor element such as a transistor.

[0007] Patent Document 3 discloses a flexible active matrix light-emitting device in which an organic electroluminescence (EL) element and a transistor serving as a switching element are provided over a film substrate.

[0008] Display devices are expected to be applied to a variety of uses and become diversified. For example, a smartphone and a tablet terminal with a touch panel are being developed as portable information appliances.

#### REFERENCES

#### Patent Documents

[Patent Document 1] Japanese Published Patent Application No. 2006-165529

[Patent Document 2] Japanese Published Patent Application No. 2009-278115

[Patent Document 3] Japanese Published Patent Application No. 2003-174153

#### DISCLOSURE OF INVENTION

[0009] What is desirable is a flexible touch panel in which a display panel having flexibility is provided with a function of inputting data with a finger or the like touching a screen as a user interface.

[0010] One object of one embodiment of the present invention is to provide a touch sensor having flexibility or a touch panel having flexibility. Another object of one embodiment of the present invention is to provide a lightweight touch panel. Another object of one embodiment of the present invention is to provide a touch panel having a small thickness. Another object of one embodiment of the present invention is to provide a touch panel with high detection sensitivity. Another object of one embodiment of the present invention is to achieve both thickness reduction and high detection sensitivity of a touch sensor or a touch panel. Another object of one embodiment of the present invention is to provide a touch sensor that can be used in a large-sized touch panel. Another object of one embodiment of the present invention is to provide a large-sized touch panel.

[0011] Another object of one embodiment of the present invention is to provide a manufacturing method of a touch sensor or a touch panel that has a small number of steps.

[0012] Another object of one embodiment of the present invention is to provide a touch panel in which reduction in display quality is suppressed. Another object of one embodiment of the present invention is to provide a touch panel with high reliability. Another object of one embodiment of the present invention is to provide a touch panel with high resistance to repeated bending. Another object of one embodiment of the present invention is to provide a novel semiconductor device, a novel light-emitting device, a novel display device, a novel touch sensor, a novel touch panel, a novel electronic device, or a novel lighting device.

[0013] Note that the descriptions of these objects do not disturb the existence of other objects. In one embodiment of the present invention, there is no need to achieve all the objects. Other objects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

$[0\bar{0}14]$  One embodiment of the present invention is an active matrix touch sensor including a transistor and a capacitor. The transistor and the capacitor are electrically connected to each other.

[0015] Specifically, one embodiment of the present invention is a touch sensor including a transistor and a capacitor,

the transistor and the capacitor are electrically connected to each other, the capacitor includes a pair of electrodes and a dielectric layer, the dielectric layer is located between the pair of electrodes, and one of the pair of electrodes includes an oxide conductor layer.

[0016] In the above structure, it is preferable that the transistor include an oxide semiconductor layer and that the oxide conductor layer and the oxide semiconductor layer be located over the same surface. In the transistor, it is preferable that a channel region be included in the oxide semiconductor layer.

[0017] In the above structure, a source or a drain of the transistor and one of the pair of electrodes (i.e., the oxide conductor layer) of the capacitor may be electrically connected to each other. In the above structure, the source or the drain of the transistor and the other of the pair of electrodes of the capacitor may be electrically connected to each other.

[0018] It is preferable that the touch sensor having any of the above structures have flexibility.

[0019] One embodiment of the present invention is a touch sensor including a first transistor, a second transistor, a third transistor, and a capacitor. A gate of the first transistor is electrically connected to a first wiring, one of a source and a drain of the first transistor is electrically connected to a second wiring, the other of the source and the drain of the first transistor is electrically connected to a gate of the second transistor and one electrode of the capacitor, one of a source and a drain of the second transistor is electrically connected to a third wiring, the other of the source and the drain of the second transistor is electrically connected to one of a source and a drain of the third transistor, a gate of the third transistor is electrically connected to a fourth wiring, the other of the source and the drain of the third transistor is electrically connected to a fifth wiring, the other electrode of the capacitor is electrically connected to a sixth wiring, and the one electrode or the other electrode of the capacitor includes an oxide conductor layer.

[0020] In the above structure, it is preferable that any one of the first transistor, the second transistor, and the third transistor include an oxide semiconductor layer located over a surface over which the oxide conductor layer is formed. It is particularly preferable that the first transistor include the oxide semiconductor layer.

[0021] In the above structure, the one electrode of the capacitor may include the oxide conductor layer. In the above structure, the other electrode of the capacitor may include the oxide conductor layer.

[0022] One embodiment of the present invention is a touch panel including the touch sensor having any of the above structures, a light-blocking layer, and a display element. The light-blocking layer is located between the touch sensor and the display element, the light-blocking layer includes a portion overlapping with the transistor, and the display element includes a portion overlapping with the capacitor. Note that the light-blocking layer includes a portion overlapping with at least one of a plurality of transistors, and preferably includes a portion overlapping with a plurality of transistors (e.g., the first transistor, the second transistor, and the third transistor).

[0023] One embodiment of the present invention is a touch panel including the touch sensor having any of the above structures, a light-blocking layer, and a display element. The touch sensor is located more on a display surface side of the touch panel than a display element side, the light-blocking layer is located more on the display surface side than the touch sensor side, the display element includes a portion

overlapping with the capacitor, and the light-blocking layer includes a portion overlapping with the transistor.

[0024] In the above structure, it is preferable that the transistor include an oxide semiconductor layer. In the above structure, it is preferable that the capacitor include a dielectric layer and a pair of electrodes, that the dielectric layer be located between the pair of electrodes, and that one of the pair of electrodes include an oxide conductor layer.

[0025] In any of the above structures, the oxide semiconductor layer and the oxide conductor layer may be located over the same surface. In the transistor, it is preferable that a channel region be included in the oxide semiconductor layer.

[0026] In any of the above structures, the source or the drain of the transistor and the oxide conductor layer may be electrically connected to each other.

[0027] In the touch panel having any of the above structures, a first electrode, a second electrode, and a layer including a light-emitting organic compound (such a layer is also referred to as an EL layer) may be included in the display element, an insulating film covering an end portion of the first electrode may be included, the layer including a light-emitting organic compound may be located between the first electrode and the second electrode, and the insulating film may include a portion overlapping with the transistor.

[0028] It is preferable that the touch panel having any of the above structures have flexibility.

[0029] One embodiment of the present invention is a method for manufacturing a touch panel, including a first step of forming a first separation layer, a first insulating layer, and a display element in this order over a first formation substrate, a second step of forming a second separation layer, a second insulating layer, and a touch sensor in this order over a second formation substrate, a third step of forming a third separation layer, a third insulating layer, and a light-blocking layer in this order over a third formation substrate, a fourth step of bonding the display element over the first formation substrate and the touch sensor over the second formation substrate to each other using a first bonding layer, a fifth step of separating the second formation substrate and the second insulating layer using the second separation layer to expose the second insulating layer, a sixth step of bonding the exposed second insulating layer and the light-blocking layer over the third formation substrate using a second bonding layer, a seventh step of separating the third formation substrate and the third insulating layer using the third separation layer to expose the third insulating layer, an eighth step of bonding the exposed third insulating layer and a first flexible substrate to each other using a third bonding layer, a ninth step of separating the first formation substrate and the first insulating layer using the first separation layer to expose the first insulating layer, and a tenth step of bonding the exposed first insulating layer and a second flexible substrate using a fourth bonding layer. In the second step, a transistor and a capacitor are formed as the touch sensor. The transistor and the capacitor are electrically connected to each other, the transistor includes an oxide semiconductor layer, the capacitor includes a dielectric layer and a pair of electrodes, the dielectric layer is located between the pair of electrodes, and one of the pair of electrodes includes an oxide conductor layer. There is no limitation on the order of the first step and the second step. The fourth and subsequent steps are performed after the first step and the second step. The third step is performed before the sixth step. There is no limitation on the order of the seventh step and the ninth step.

The seventh step and the eighth step are preferably performed in succession. The ninth step and the tenth step are preferably performed in succession.

[0030] In the above manufacturing method, the display element and the touch sensor are preferably bonded to each other in the fourth step so that a portion where the display element and the capacitor overlap with each other is formed.

[0031] In any of the above manufacturing methods, the second insulating layer and the light-blocking layer are preferably bonded to each other in the sixth step so that a portion where the light-blocking layer and the transistor overlap with each other is provided.

[0032] Note that the light-emitting device in this specification includes, in its category, a display device using a light-emitting element. In some cases, a light-emitting device is included in a module in which a light-emitting element is provided with a connector such as an anisotropic conductive film or a tape carrier package (TCP); a module in which a printed wiring board is provided at the end of a TCP; and a module in which an integrated circuit (IC) is directly mounted on a light-emitting element by a chip on glass (COG) method. A light-emitting device may be included in lighting equipment or the like.

[0033] One embodiment of the present invention can provide a touch sensor having flexibility or a touch panel having flexibility. One embodiment of the present invention can provide a lightweight touch sensor or a lightweight touch panel. One embodiment of the present invention can provide a touch sensor or a touch panel having a small thickness. One embodiment of the present invention can provide a touch sensor or a touch panel with high detection sensitivity. One embodiment of the present invention can achieve both thickness reduction and high detection sensitivity of a touch sensor or a touch panel, can provide a touch sensor that can be used in a large-sized touch panel, or can provide a large-sized touch panel.

[0034] One embodiment of the present invention can provide a manufacturing method of a touch sensor or a touch panel that has a small number of steps.

[0035] One embodiment of the present invention can provide a touch panel in which reduction in display quality is suppressed. One embodiment of the present invention can provide a touch panel with high reliability. One embodiment of the present invention can provide a touch panel with high resistance to repeated bending. One embodiment of the present invention can provide a novel semiconductor device, a novel light-emitting device, a novel display device, a novel touch sensor, a novel touch panel, a novel electronic device, or a novel lighting device.

[0036] Note that the description of these effects does not disturb the existence of other effects. One embodiment of the present invention does not necessarily achieve all the effects listed above. Other effects will be apparent from and can be derived from the description of the specification, the drawings, the claims, and the like.

#### BRIEF DESCRIPTION OF DRAWINGS

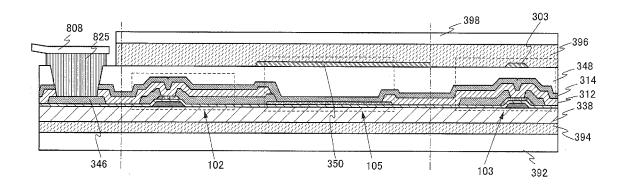

$\boldsymbol{[0037]}\quad FIGS.\ 1A$  and 1B illustrate an example of a touch sensor.

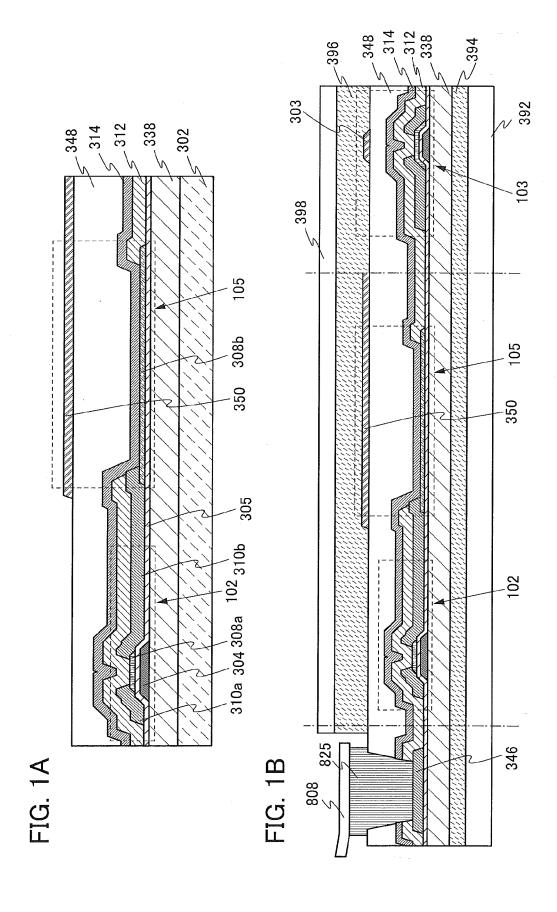

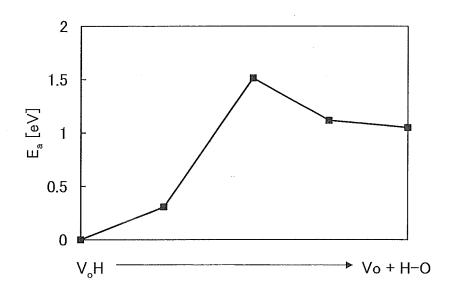

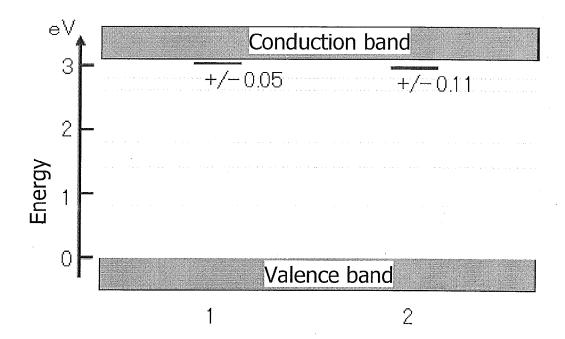

[0038] FIG. 2 shows dependence of resistivity on temperature.

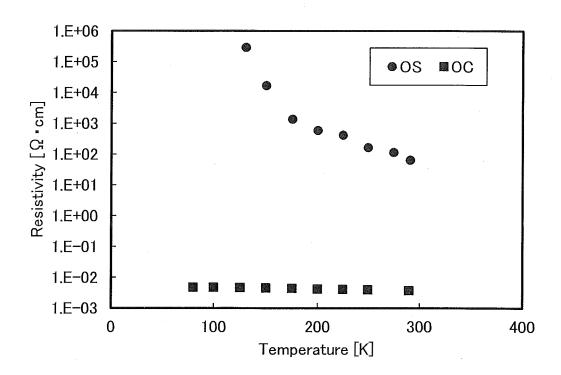

$\ensuremath{[0039]}$  FIGS. 3A to 3E illustrate an example of a touch sensor.

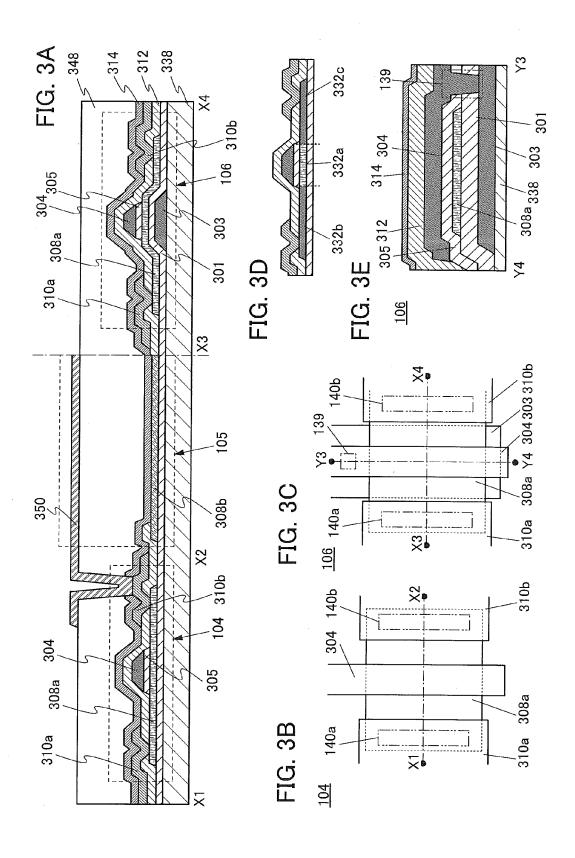

[0040] FIGS. 4A to 4D illustrate an example of a method for manufacturing a touch sensor.

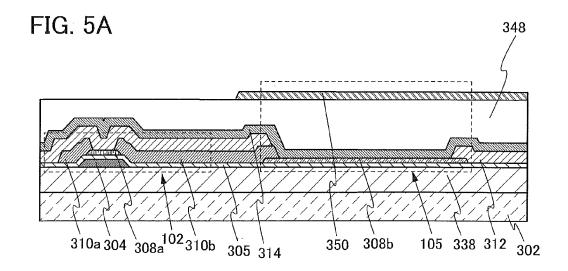

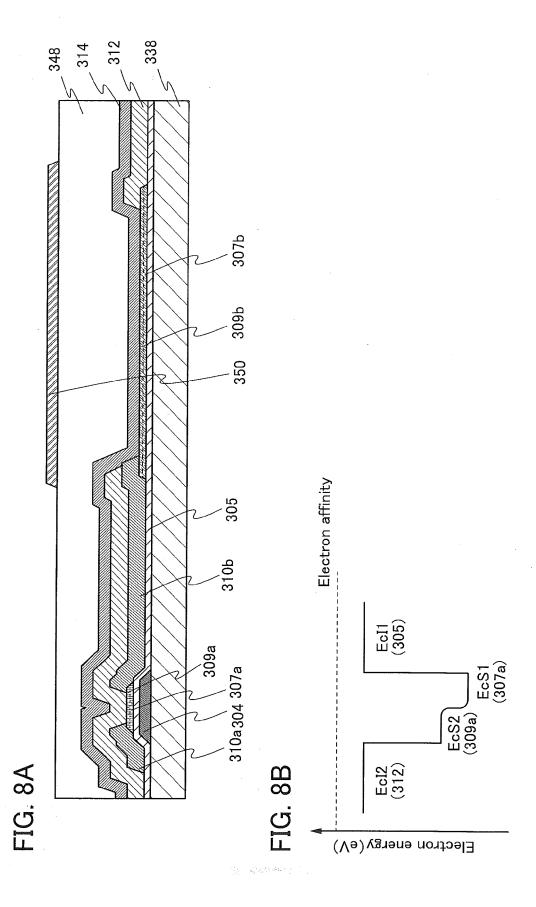

[0041] FIGS. 5A and 5B illustrate an example of the method for manufacturing a touch sensor.

[0042] FIGS. 6A to 6H illustrate an example of a method for manufacturing a touch sensor.

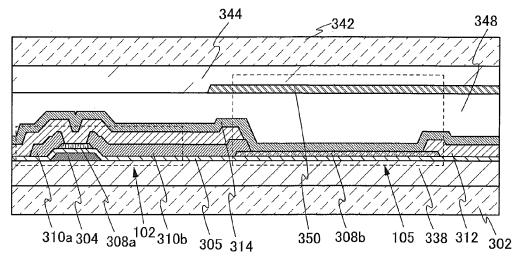

[0043] FIGS. 7A to 7G illustrate an example of the method for manufacturing a touch sensor.

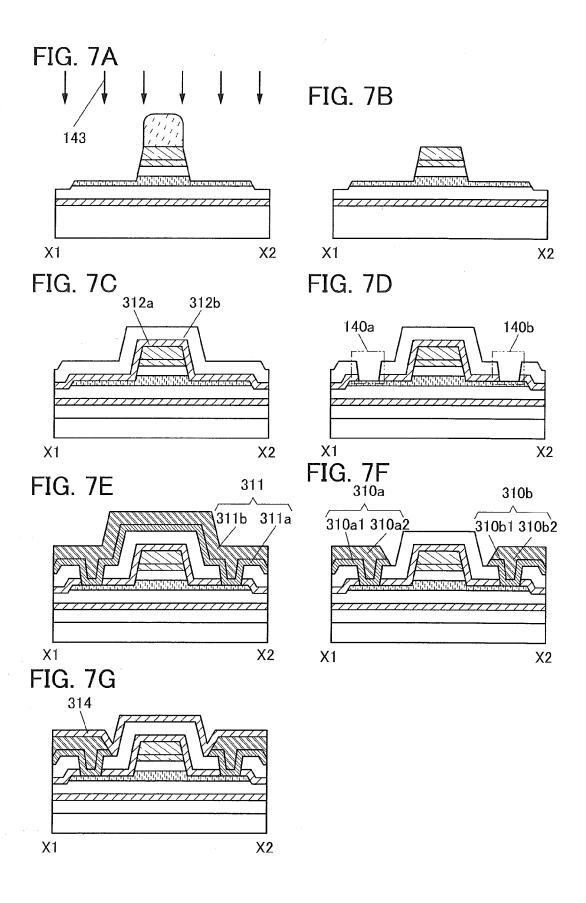

[0044] FIGS. 8A and 8B illustrate an example of a touch sensor and an example of a band structure.

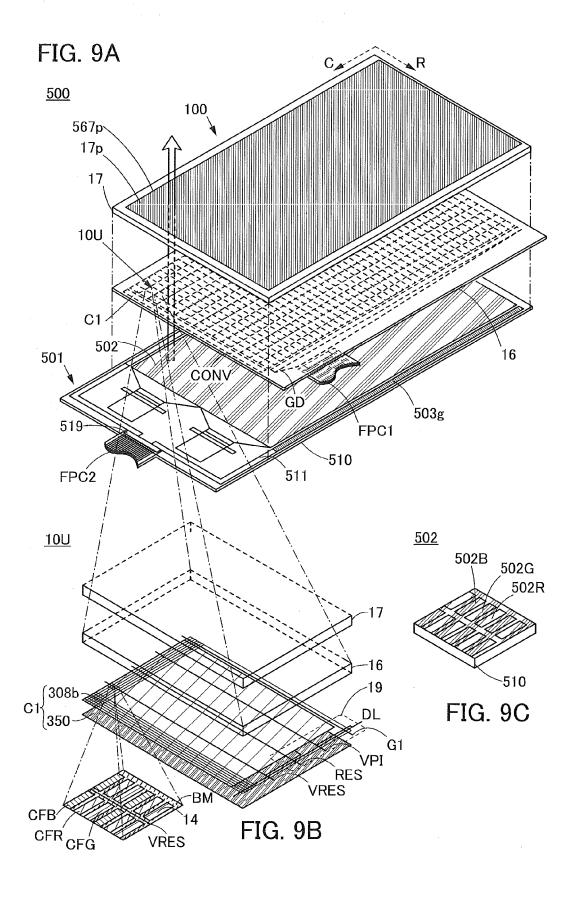

[0045] FIGS. 9A to 9C illustrate an example of a touch panel.

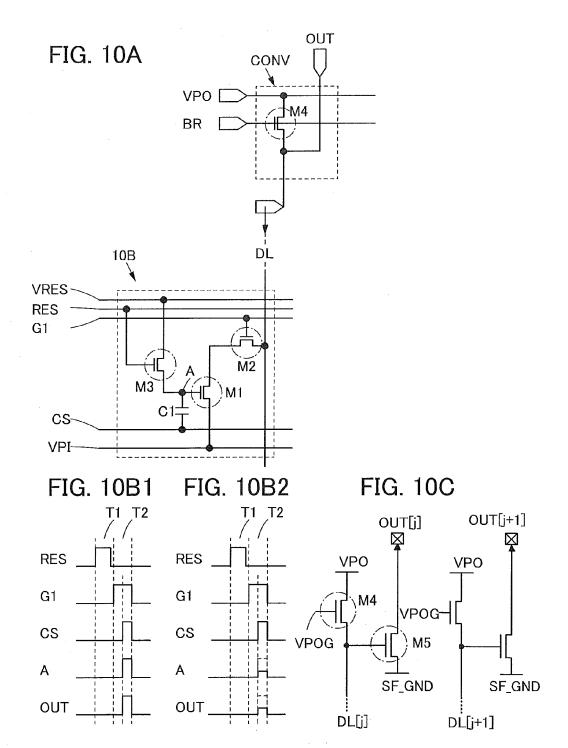

[0046] FIGS. 10A, 10B1, 10B2, and 10C illustrate examples of structures of a sensor circuit and a converter and an example of a driving method thereof.

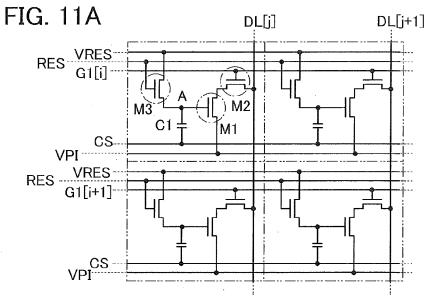

[0047] FIGS. 11A to 11C illustrate an example of a sensor circuit.

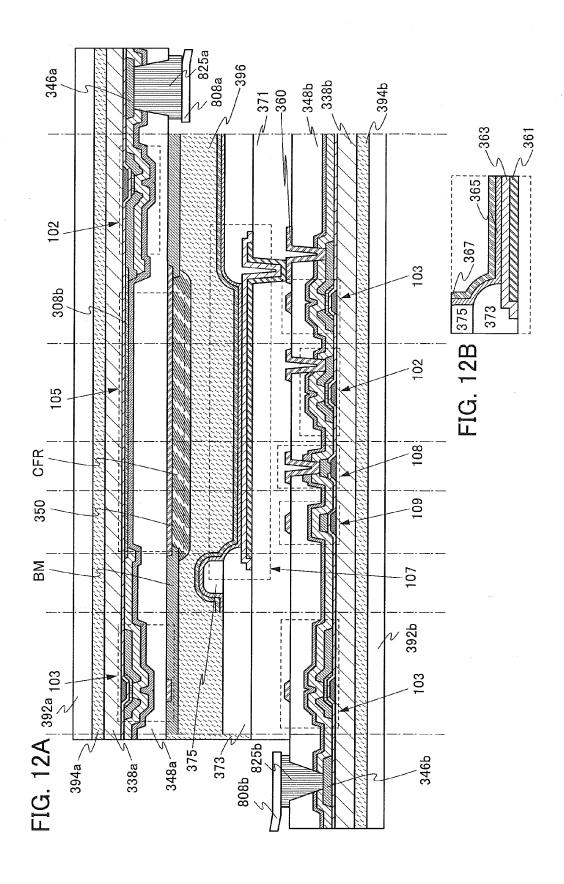

[0048] FIGS. 12A and 12B illustrate an example of a touch panel.

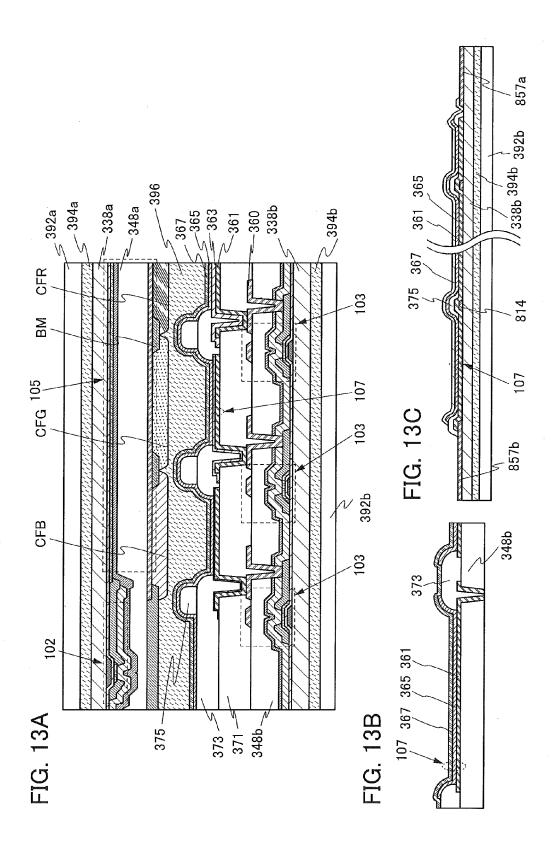

[0049] FIGS. 13A to 13C illustrate an example of a touch panel.

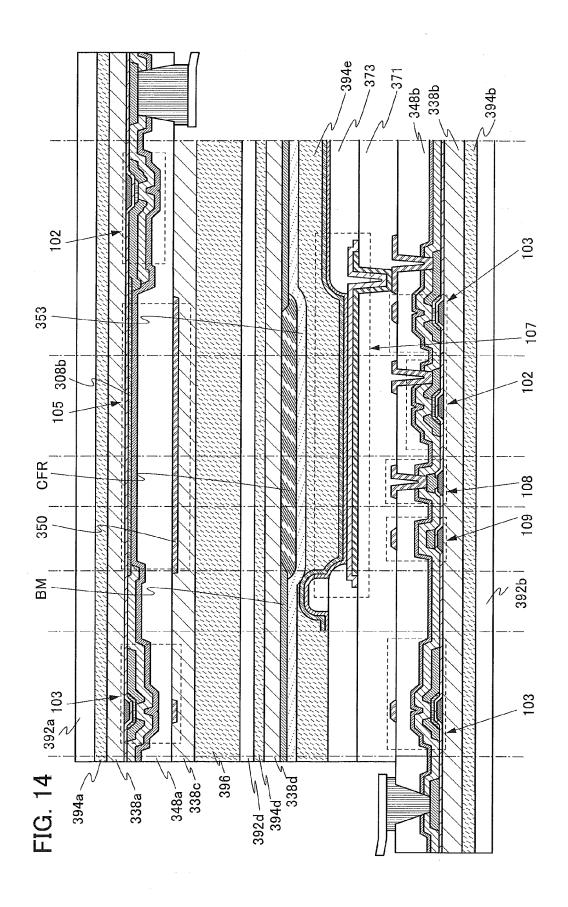

[0050] FIG. 14 illustrates an example of a touch panel.

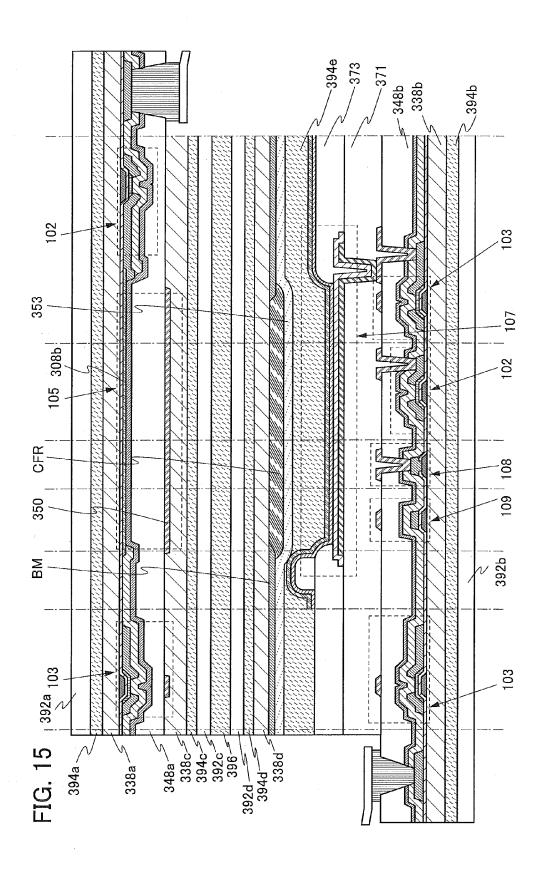

[0051] FIG. 15 illustrates an example of a touch panel.

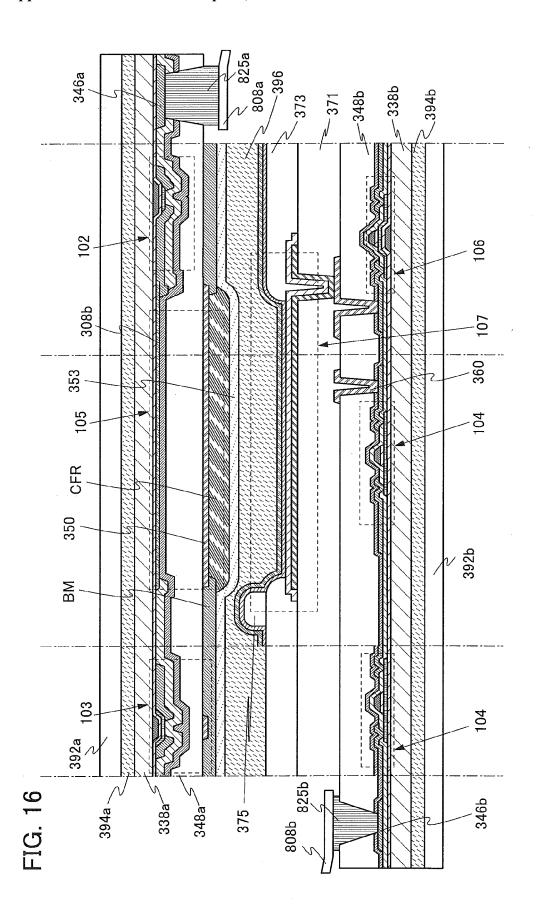

[0052] FIG. 16 illustrates an example of a touch panel.

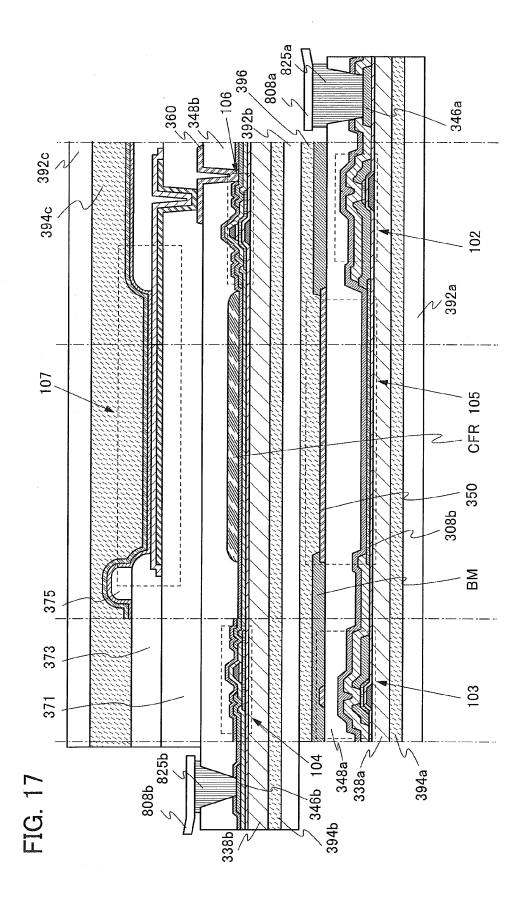

[0053] FIG. 17 illustrates an example of a touch panel.

[0054] FIGS. 18A to 18D illustrate an example of a method for manufacturing a touch panel.

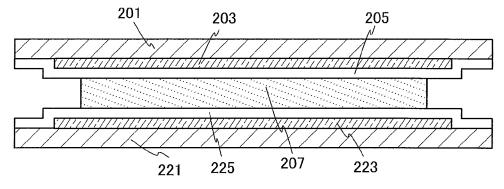

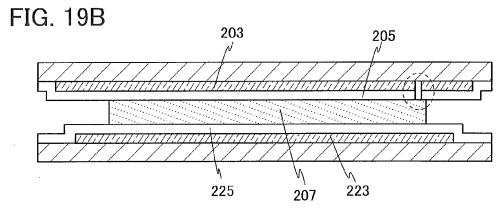

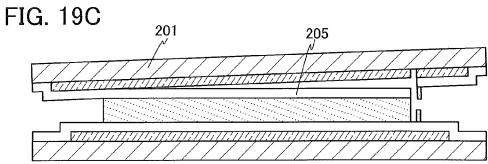

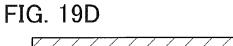

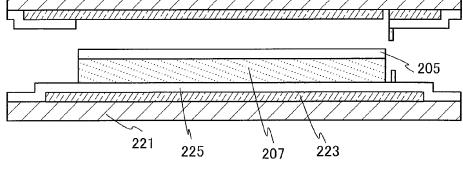

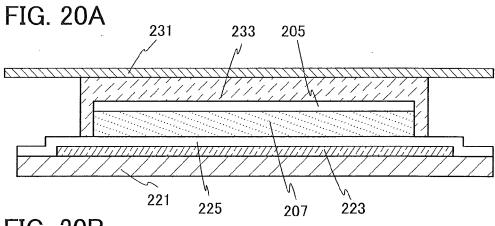

[0055] FIGS. 19A to 19D illustrate an example of the method for manufacturing a touch panel.

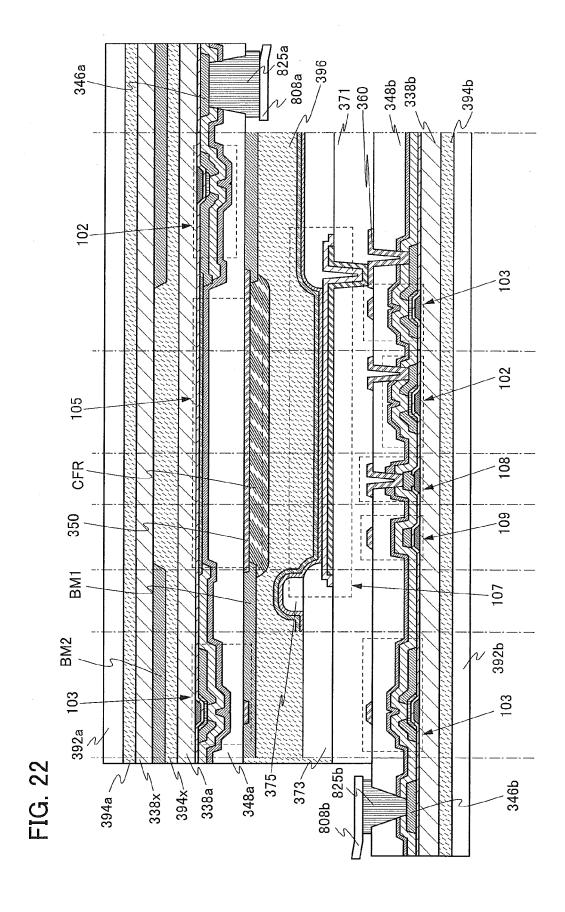

[0056] FIGS. 20A to 20D illustrate an example of the method for manufacturing a touch panel.

[0057] FIGS. 21A to 21C illustrate an example of a method for manufacturing a touch panel.

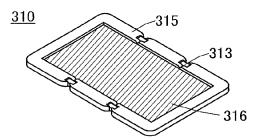

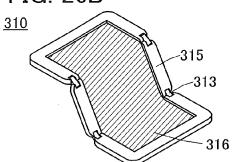

[0058] FIG. 22 illustrates an example of a touch panel.

[0059] FIGS. 23A to 23H illustrate an example of a method for manufacturing a touch panel.

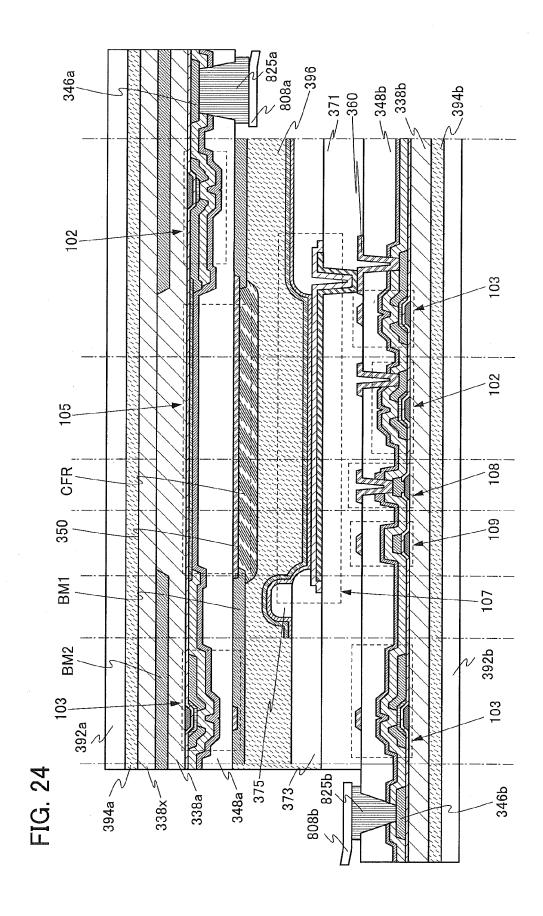

[0060] FIG. 24 illustrates an example of a touch panel.

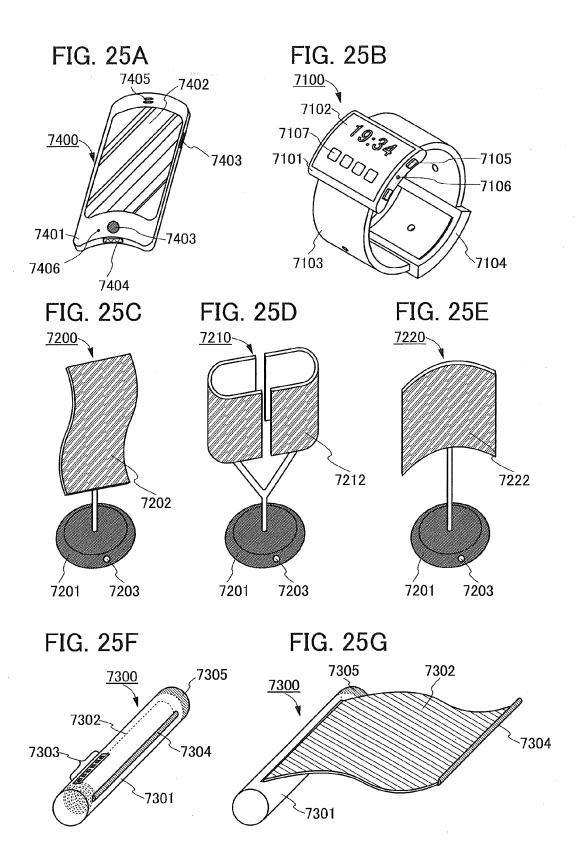

[0061] FIGS. 25A to 25G illustrate examples of electronic devices and lighting devices.

[0062] FIGS. 26A to 261 illustrate examples of electronic devices.

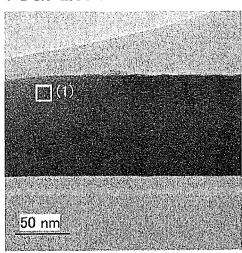

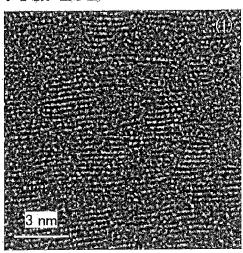

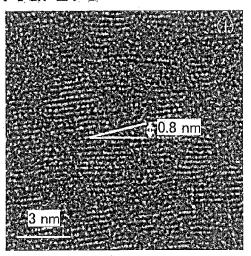

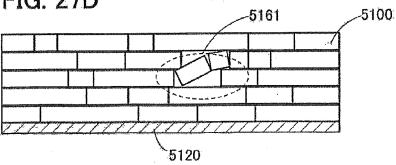

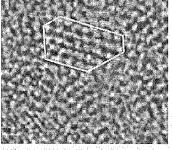

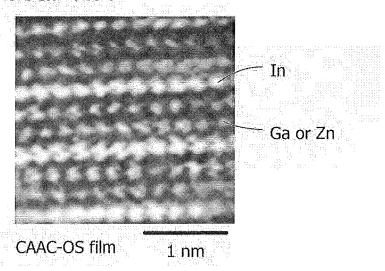

[0063] FIGS. 27A to 27D are Cs-corrected high-resolution TEM images of a cross section of a CAAC-OS and a cross-sectional schematic view of the CAAC-OS.

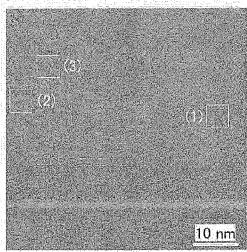

[0064] FIGS. 28A to 28D are Cs-corrected high-resolution TEM images of a plane of a CAAC-OS.

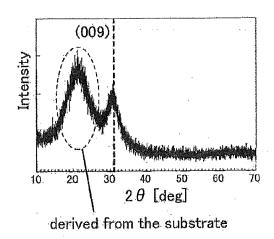

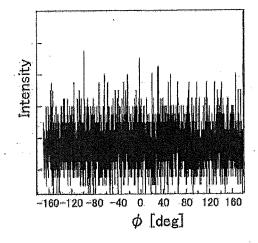

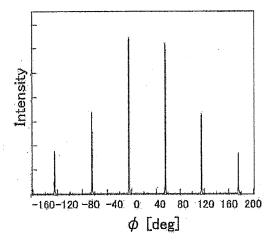

[0065] FIGS. 29A to 29C show structural analysis of a CAAC-OS and a single crystal oxide semiconductor by)(RD.

[0066] FIGS.  $30\mathrm{A}$  and  $30\mathrm{B}$  show electron diffraction patterns of a CAAC-OS.

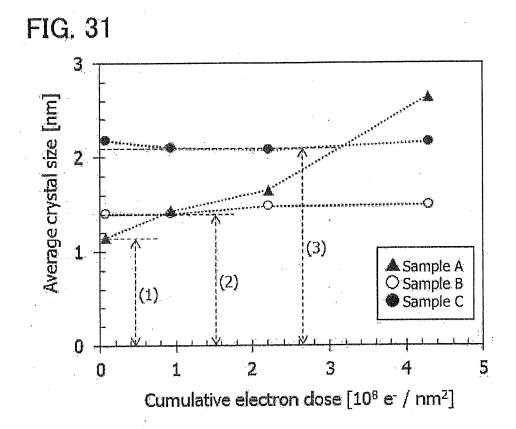

[0067] FIG. 31 shows a change in crystal part of an In—Ga—Zn oxide induced by electron irradiation.

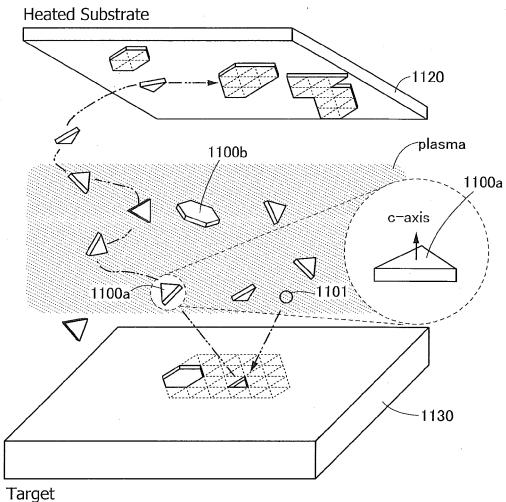

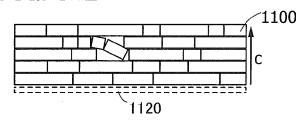

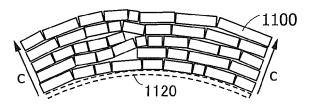

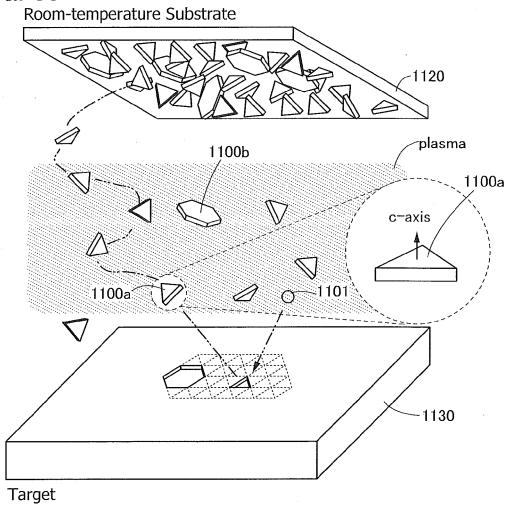

[0068] FIG. 32A schematically illustrates a CAAC-OS deposition model, and FIGS. 32B and 32C are cross-sectional views of pellets and a CAAC-OS.

[0069] FIG. 33 illustrates a deposition model of an nc-OS schematically and a pellet.

[0070] FIG. 34 illustrates a pellet.

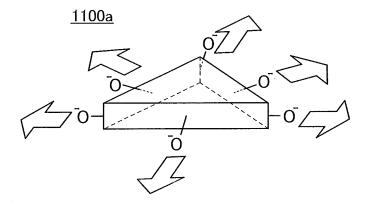

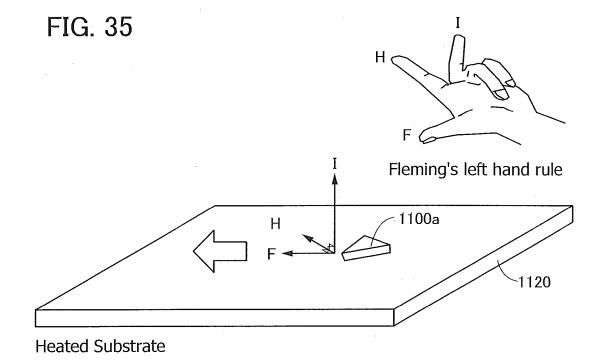

[0071] FIG. 35 illustrates force applied to a pellet on a formation surface.

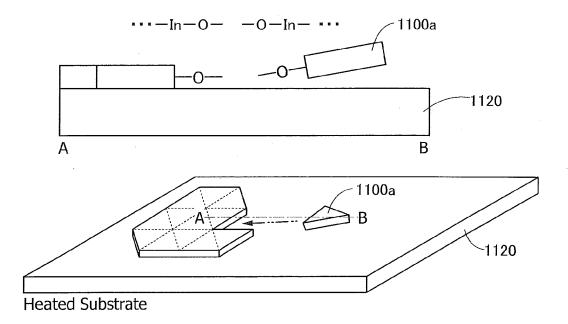

[0072] FIGS. 36A and 36B illustrate movement of a pellet on a formation surface.

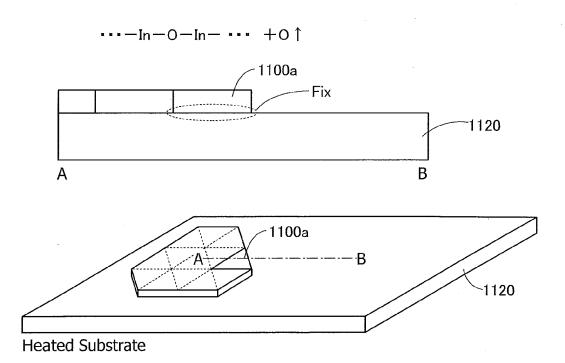

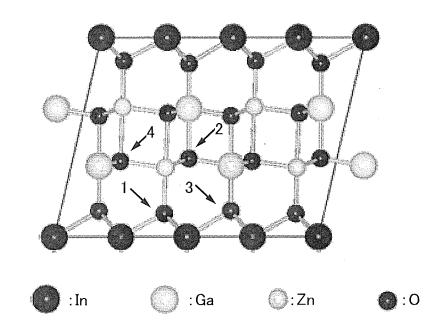

[0073] FIGS. 37A and 37B show an InGaZnO<sub>4</sub> crystal.

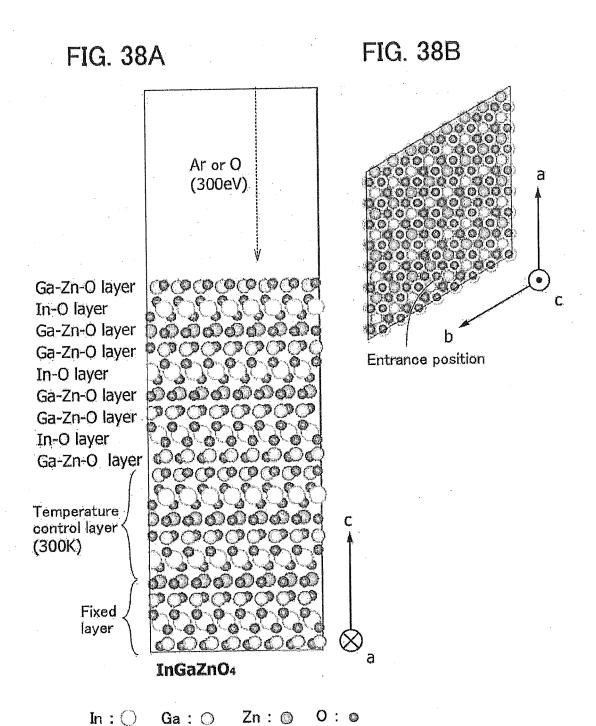

[0074] FIGS. 38A and 38B illustrate a structure of InGaZnO<sub>4</sub> and the like before collision of an atom.

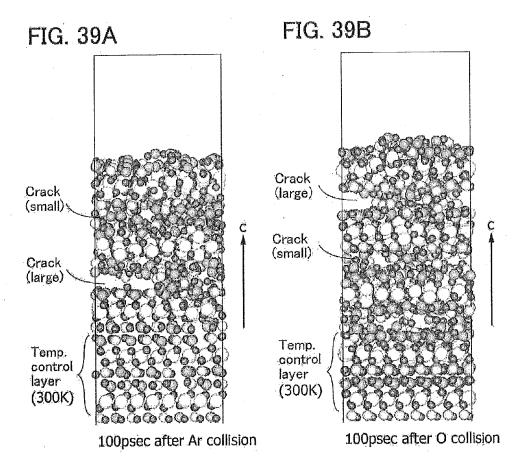

[0075] FIGS. 39A and 39B show a structure of  $InGaZnO_4$  and the like after collision of an atom.

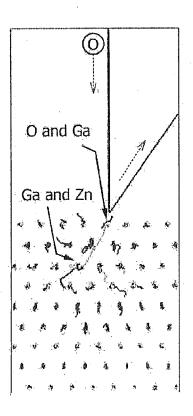

[0076] FIGS. 40A and 40B show trajectories of atoms after collision of atoms.

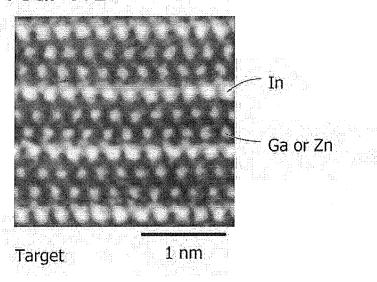

[0077] FIGS. 41A and 41B are cross-sectional HAADF-STEM images of a CAAC-OS and a target.

[0078] FIG. 42 shows a calculation model.

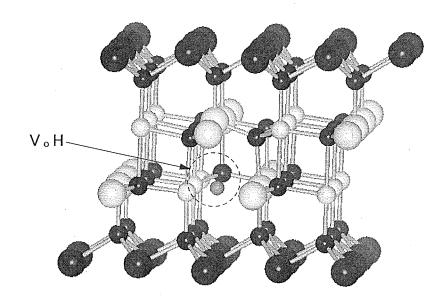

[0079] FIGS. 43A and 43B show an initial state and a final state, respectively.

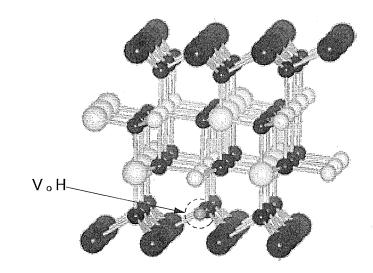

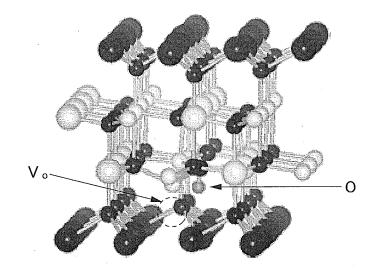

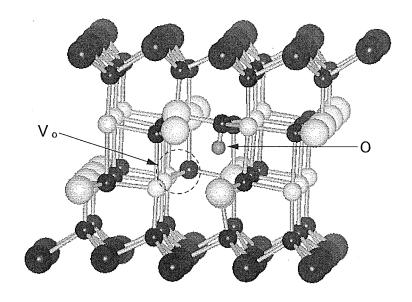

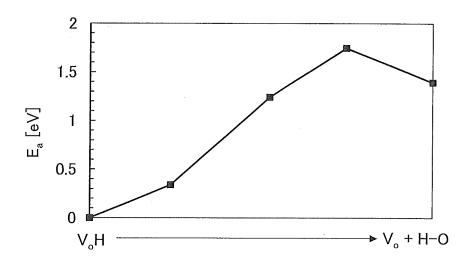

[0080] FIG. 44 shows an activation barrier.

[0081] FIGS. 45A and 45B illustrate an initial state and a final state, respectively.

[0082] FIG. 46 shows an activation barrier.

[0083] FIG. 47 shows the transition levels of  $V_oH$ .

## BEST MODE FOR CARRYING OUT THE INVENTION

[0084] Embodiments will be described in detail with reference to drawings. Note that the present invention is not limited to the description below, and it is easily understood by those skilled in the art that various changes and modifications can be made without departing from the spirit and scope of the present invention. Accordingly, the present invention should not be interpreted as being limited to the content of the embodiments below.

[0085] Note that in the structures of the invention described below, the same portions or portions having similar functions are denoted by the same reference numerals in different drawings, and description of such portions is not repeated. Further, the same hatching pattern is applied to portions having similar functions, and the portions are not especially denoted by reference numerals in some cases.

[0086] In addition, the position, size, range, or the like of each structure illustrated in drawings and the like is not accurately represented in some cases for easy understanding. Therefore, the disclosed invention is not necessarily limited to the position, the size, the range, or the like disclosed in the drawings and the like.

[0087] Note that in this specification, ordinal numbers such as "first", "second", and "third" are used in order to avoid confusion among components, and the terms do not limit the components numerically.

[0088] Note that in this specification, terms for describing arrangement, such as "over" "above", "under", and "below", are used for convenience in describing a positional relation between components with reference to drawings. Further, the positional relation between components is changed as appropriate in accordance with a direction in which each component is described. Thus, there is no limitation on terms used in this specification, and description can be made appropriately depending on the situation.

[0089] In this specification and the like, a transistor is an element having at least three terminals of a gate, a drain, and a source. The transistor includes a channel region between the drain (a drain terminal, a drain region, or a drain electrode) and the source (a source terminal, a source region, or a source electrode) and current can flow through the drain, the channel region, and the source. Note that in this specification and the like, a channel region refers to a region through which current mainly flows.

[0090] Further, functions of a source and a drain might be switched when transistors having different polarities are employed or a direction of current flow is changed in circuit

operation, for example. Therefore, the terms "source" and "drain" can be switched in this specification and the like.

[0091] Note that in this specification and the like, the expression "electrically connected" includes the case where components are connected through an "object having any electric function". There is no particular limitation on an "object having any electric function" as long as electric signals can be transmitted and received between components that are connected through the object. Examples of an "object having any electric function" are a switching element such as a transistor, a resistor, an inductor, a capacitor, and elements with a variety of functions as well as an electrode and a wiring.

#### Embodiment 1

[0092] In this embodiment, a touch sensor of one embodiment of the present invention is described.

[0093] One embodiment of the present invention is an active matrix touch sensor including a transistor and a capacitor. The transistor and the capacitor are electrically connected to each other.

[0094] Specifically, one embodiment of the present invention is a touch sensor including a transistor and a capacitor. In the touch sensor, the transistor and the capacitor are electrically connected to each other, the capacitor includes a pair of electrodes and a dielectric layer, the dielectric layer is located between the pair of electrodes, and one of the pair of electrodes includes an oxide conductor layer.

[0095] Note that in this specification and the like, the oxide conductor layer can also be referred to as an oxide semiconductor layer having a high carrier density and a low resistance, an oxide semiconductor layer having conductivity, an oxide semiconductor layer having high conductivity, or the like

[0096] An oxide semiconductor layer has a high light-transmitting property. By increasing oxygen vacancies and/or impurities such as hydrogen or water in the oxide semiconductor layer, an oxide semiconductor layer having a high carrier density and a low resistance (hereinafter also referred to as an oxide conductor layer) can be obtained. Such an oxide semiconductor layer can be favorably used as an electrode of the capacitor of the touch sensor.

[0097] In the above structure, it is preferable that the transistor include an oxide semiconductor layer that is located over a surface over which the oxide conductor layer is formed. Furthermore, it is preferable that the oxide semiconductor layer include a channel region.

[0098] It is preferable that the semiconductor layer of the transistor and the electrode of the capacitor be formed in the same step because the touch sensor can be manufactured in a small number of steps.

[0099] Note that a layer that is formed in the same step as that of the electrode of the capacitor is not limited to the semiconductor layer of the transistor. For example, a gate electrode, a source electrode, or a drain electrode of the transistor, a wiring, or the like may be formed using a material having a high light-transmitting property in the same step as that of the electrode of the capacitor.

[0100] Examples of a structure and a manufacturing method of a touch sensor of one embodiment of the present invention are described below.

<Structure Example 1 of Touch Sensor>

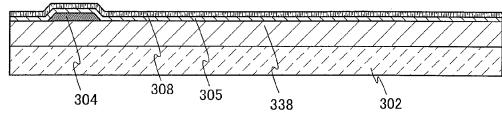

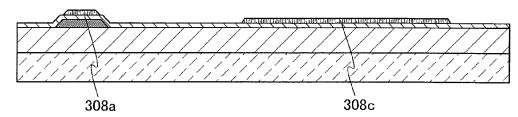

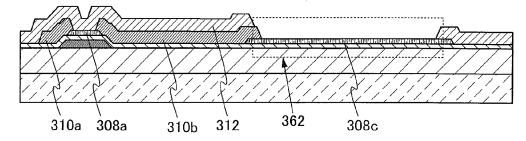

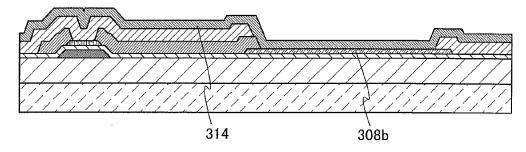

[0101] FIG. 1A illustrates a transistor 102 and a capacitor 105 included in a touch sensor of one embodiment of the present invention. The transistor 102 and the capacitor 105 are provided in a sensor portion of the touch sensor, for example. The transistor included in the touch sensor of one embodiment of the present invention has a bottom-gate structure. In FIG. 1A, the transistor 102 and the capacitor 105 are formed over a substrate 302 with an insulating film 338 provided between the substrate 302, and the transistor 102 and the capacitor 105.

[0102] The transistor 102 includes a conductive film 304 that functions as the gate electrode, an insulating film 305 that is over the conductive film 304 and functions as a gate insulating film, an oxide semiconductor layer 308a over the insulating film 305, and conductive films 310a and 310b that are over the oxide semiconductor layer 308a and function as a source electrode and a drain electrode. Insulating films 312 and 314 are provided as protective films over the transistor 102, more in details, over the oxide semiconductor layer 308a and the conductive films 310a and 310b. Furthermore, an insulating film 348 is provided over the insulating film 314. [0103] The capacitor 105 includes a dielectric layer between a pair of electrodes. The capacitor 105 includes a conductive film 350 as one of the pair of electrodes and an oxide conductor layer 308b as the other of the pair of electrodes. The insulating films 314 and 348 serve a dielectric layer of the capacitor 105. In other words, the insulating films 314 and 348 are provided for both the transistor 102 and the capacitor 105. Although FIG. 1A illustrates a layered structure of the insulating films 314 and 348 as the dielectric layer, this layered structure is not necessarily employed and a single-layer structure or a layered structure including three or more layers may be employed.

[0104] The oxide conductor layer 308b is formed in the same step as the oxide semiconductor layer 308a so as to be over the insulating film 305 that functions as the gate insulating film. The conductive film 310b that functions as the drain electrode of the transistor 102 is electrically connected to the oxide conductor layer 308b. In the example illustrated here, part of the conductive film 310b is in contact with the oxide conductor layer 308b; however, the conductive film 310b may be electrically connected to the oxide conductor layer 308b through another conductive film. The conductive film 310b may be electrically connected to the conductive film 350b.

[0105] Note that the structure of the transistor included in the touch sensor of one embodiment of the present invention is not particularly limited. For example, a forward staggered transistor or an inverted staggered transistor may be used. A top-gate transistor or a bottom-gate transistor may be used. A semiconductor material used for the transistor is not particularly limited, and for example, an oxide semiconductor, silicon, or germanium can be used.

[0106] There is no particular limitation on the crystallinity of a semiconductor material used for the transistor, and an amorphous semiconductor or a semiconductor having crystallinity (a microcrystalline semiconductor, a polycrystalline semiconductor, a single-crystal semiconductor, or a semiconductor partly including crystal regions) may be used. It is preferable that a semiconductor having crystallinity be used, in which case deterioration of the transistor characteristics can be suppressed.

[0107] The oxide semiconductor layer 308a and the oxide conductor layer 308b are layers processed into island-like

shapes through the same film formation step and the same etching step. An oxide semiconductor is a semiconductor material whose resistance can be controlled by oxygen vacancies in the film of the semiconductor material and/or the concentration of impurities such as hydrogen or water in the film of the semiconductor material. Therefore, to control the resistivity of each of the oxide semiconductor layer 308a and the oxide conductor layer 308b formed in the same step, treatment to be performed on the oxide semiconductor layers processed into island-like shapes is selected from the following: treatment for increasing oxygen vacancies and/or impurity concentration and treatment for reducing oxygen vacancies and/or impurity concentration.

[0108] Specifically, plasma treatment is performed on the island-like oxide semiconductor layer that is to be the oxide conductor layer 308b functioning as the electrode of the capacitor to increase oxygen vacancies and/or impurities such as hydrogen or water in the oxide semiconductor layer, so that the oxide semiconductor layer can have a high carrier density and a low resistance. Alternatively, an insulating film containing hydrogen is formed in contact with the oxide semiconductor layer to diffuse hydrogen from the insulating film containing hydrogen to the oxide semiconductor layer, so that the oxide semiconductor layer can have a high carrier density and a low resistance.

[0109] The insulating film 312 is provided over the transistor 102 to prevent the oxide semiconductor layer 308a from being subjected to the plasma treatment. Since the insulating film 312 is provided, the oxide semiconductor layer 308a is not in contact with the insulating film 314 containing hydrogen. The insulating film 312 can be formed using an insulating film capable of releasing oxygen, in which case oxygen can be supplied to the oxide semiconductor layer 308a. The oxide semiconductor layer 308a to which oxygen is supplied is an oxide semiconductor in which oxygen vacancies in the film or at the interface are reduced and which has a high resistance. Note that as the insulating film capable of releasing oxygen, a silicon oxide film or a silicon oxynitride film can be used, for example.

[0110] As the plasma treatment to be performed on the oxide conductor layer 308b, plasma treatment using a gas containing one of a rare gas (He, Ne, Ar, Kr, or Xe), phosphorus, boron, hydrogen, and nitrogen is typical. Specifically, plasma treatment in an Ar atmosphere, plasma treatment in a mixed gas atmosphere of Ar and hydrogen, plasma treatment in an ammonia atmosphere, plasma treatment in a mixed gas atmosphere of Ar and ammonia, plasma treatment in a nitrogen atmosphere, or the like can be employed.

[0111] By the plasma treatment, an oxygen vacancy is formed in a lattice from which oxygen is released (or in a portion from which oxygen is released) in the oxide conductor layer 308b. This oxygen vacancy can cause carrier generation. Further, when hydrogen is supplied from an insulating film that is in the vicinity of the oxide conductor layer 308b, specifically, that is in contact with the lower surface or the upper surface of the oxide conductor layer 308b, and hydrogen enters the oxygen vacancy, an electron serving as a carrier might be generated. Accordingly, the oxide conductor layer 308b whose oxygen vacancies are increased by the plasma treatment has a higher carrier density than the oxide semiconductor layer 308a.

[0112] The oxide semiconductor layer 308a in which oxygen vacancies are reduced and the hydrogen concentration is reduced can be referred to as a highly purified intrinsic or

substantially highly purified intrinsic oxide semiconductor layer. The term "substantially intrinsic" refers to the state where an oxide semiconductor has a carrier density lower than 1×10<sup>17</sup>/cm<sup>3</sup>, preferably lower than 1×10<sup>15</sup>/cm<sup>3</sup>, further preferably lower than 1×10<sup>13</sup>/cm<sup>3</sup>. Furthermore, the state in which an impurity concentration is low and the density of defect states is low (the amount of oxygen vacancies is small) is referred to as "highly purified intrinsic" or "substantially highly purified intrinsic". A highly purified intrinsic or substantially highly purified intrinsic oxide semiconductor has few carrier generation sources, and thus has a low carrier density in some cases. Thus, a transistor including the oxide semiconductor film in which a channel region is formed is likely to have positive threshold voltage (normally-off characteristics). The highly purified intrinsic or substantially highly purified intrinsic oxide semiconductor layer 308a has a low density of defect states and accordingly can have a low density of trap states.

[0113] Furthermore, the highly purified intrinsic or substantially highly purified intrinsic oxide semiconductor layer 308a has an extremely low off-state current; even when an element has a channel width of  $1\times10^6$  µm and a channel length L of 10 µm, the off-state current can be less than or equal to the measurement limit of a semiconductor parameter analyzer, i.e., less than or equal to  $1\times10^{-13}$  A, at a voltage (drain voltage) between a source electrode and a drain electrode in the range from 1 V to 10 V. Thus, the transistor 102 whose channel region is formed in the oxide semiconductor layer 308a has a small change in electrical characteristics and is highly reliable.

[0114] The insulating film 312 in FIG. 1A is formed in such a manner that the insulating film that overlaps with the oxide conductor layer 308b functioning as the electrode of the capacitor is selectively removed. The insulating film 314 formed in contact with the oxide conductor layer 308b may be removed from the oxide conductor layer 308b. For example, an insulating film containing hydrogen, that is, an insulating film capable of releasing hydrogen, typically, a silicon nitride film, is used as the insulating film 314, whereby hydrogen can be supplied to the oxide conductor layer 308b. The insulating film capable of releasing hydrogen preferably has a hydrogen concentration of 1×10<sup>22</sup> atoms/cm<sup>3</sup> or higher. Such an insulating film is formed in contact with the oxide conductor layer 308b, whereby hydrogen can be effectively contained in the oxide conductor layer 308b. In this manner, the above-described plasma treatment is performed and the structure of the insulating film in contact with the oxide semiconductor layer (or the oxide conductor layer) is changed, whereby the resistance of the oxide semiconductor layer (or the oxide conductor layer) can be appropriately adjusted.

[0115] Hydrogen contained in the oxide conductor layer 308b reacts with oxygen bonded to a metal atom to be water, and in addition, an oxygen vacancy is formed in a lattice from which oxygen is released (or a portion from which oxygen is released). Due to entry of hydrogen into the oxygen vacancy, an electron serving as a carrier is generated. Further, in some cases, bonding of part of hydrogen to oxygen bonded to a metal element causes generation of an electron serving as a carrier. Thus, the oxide conductor layer 308b containing hydrogen has a higher carrier density than the oxide semiconductor layer 308a.

[0116] Hydrogen in the oxide semiconductor layer 308a of the transistor 102 in which a channel region is formed is preferably reduced as much as possible. Specifically, in the

oxide semiconductor layer **308***a*, the hydrogen concentration measured by secondary ion mass spectrometry (SIMS) is set to lower than or equal to  $2\times10^{20}$  atoms/cm³, preferably lower than or equal to  $5\times10^{19}$  atoms/cm³, more preferably lower than or equal to  $1\times10^{19}$  atoms/cm³, more preferably lower than  $5\times10^{18}$  atoms/cm³, more preferably lower than or equal to  $1\times10^{18}$  atoms/cm³, more preferably lower than or equal to  $5\times10^{17}$  atoms/cm³, more preferably lower than or equal to  $1\times10^{16}$  atoms/cm³, more preferably lower than or equal to  $1\times10^{16}$  atoms/cm³.

[0117] On the other hand, the oxide conductor layer 308b functioning as the electrode of the capacitor is a low-resistance oxide conductor layer having a high hydrogen concentration and/or a large amount of oxygen vacancies as compared to the oxide semiconductor layer 308a.

[0118] The oxide semiconductor layer 308a and the oxide conductor layer 308b are typically formed using a metal oxide such as an In—Ga oxide, an In—Zn oxide, or an In-M-Zn oxide (M is Mg, Al, Ti, Ga, Y, Zr, La, Ce, Nd, or Hf). Note that oxide semiconductor layer 308a and the oxide conductor layer 308b have a light-transmitting property.

[0119] Note that in the case where the oxide semiconductor layer 308a is an In-M-Zri oxide, when the summation of In and M is assumed to be 100 atomic %, the proportions of In and Mare preferably set to be greater than or equal to 25 atomic % and less than 75 atomic %, respectively, or greater than or equal to 34 atomic % and less than 66 atomic %, respectively.

[0120] The energy gap of the oxide semiconductor layer 308a is 2 eV or more, 2.5 eV or more, or 3 eV or more.

[0121] The thickness of the oxide semiconductor layer 308a can be greater than or equal to 3 nm and less than or equal to 200 nm, greater than or equal to 3 nm and less than or equal to 100 nm, or greater than or equal to 3 nm and less than or equal to 60 nm.

[0122] Further, in the case where the oxide semiconductor layer 308a is an In-M-Zn oxide, the atomic ratio of metal elements of a sputtering target used for forming the In-M-Zn oxide preferably satisfies In≥M and Zn≥M. As the atomic ratio of metal elements of such a sputtering target, In:MZn=1: 1:1, In:M:Zn=2:1:1.2, In:M:Zn=2:1:1.5, In:M:Zn=2:1:2.3, In:M:Zn=2:1:3, In:MZn=3:1:2, or the like is preferable. Note that the atomic ratio of metal elements in the formed oxide semiconductor layer 308a varies from the above atomic ratio of metal elements of the sputtering target within a range of ±40% as an error.

[0123] Note that other components of the touch sensor shown in FIG. 1A are described in detail in the description of the manufacturing method of a touch sensor, for example.

[0124] When hydrogen is added to an oxide semiconductor in which an oxygen vacancy is generated, hydrogen enters an oxygen vacant site and forms a donor level in the vicinity of the conduction band. As a result, the conductivity of the oxide semiconductor is increased, so that the oxide semiconductor becomes a conductor. An oxide semiconductor having become a conductor can be referred to as an oxide conductor. Oxide semiconductors generally have a visible light transmitting property because of their large energy gap. An oxide conductor is an oxide semiconductor having a donor level in the vicinity of the conduction band. Therefore, the influence of absorption due to the donor level is small, and an oxide conductor has a visible light transmitting property comparable to that of an oxide semiconductor.

[0125] Here, the temperature dependence of resistivity of a film formed using an oxide semiconductor (hereinafter

referred to as an oxide semiconductor film (OS)) and that of a film formed using an oxide conductor (hereinafter referred to as an oxide conductor film (OC)) are described with reference to FIG. 2. In FIG. 2, the horizontal axis represents measurement temperature, and the vertical axis represents resistivity. Measurement results of the oxide semiconductor film (OS) are plotted as circles, and measurement results of the oxide conductor film (OC) are plotted as squares.

[0126] Note that a sample including the oxide semiconductor film (OS) is prepared by forming a 35-nm-thick In—Ga—Zn oxide film over a glass substrate by a sputtering method using a sputtering target with an atomic ratio of In:Ga:Zn=1: 1:1.2, forming a 20-nm-thick IGZO film over the 35-nm-thick In—Ga—Zn oxide film by a sputtering method using a sputtering target with an atomic ratio of In:Ga:Zn=1:4:5, performing heat treatment at 450° C. in a nitrogen atmosphere and then performing heat treatment at 450° C. in an atmosphere of a mixed gas of nitrogen and oxygen, and forming a silicon oxynitride film over the oxide films by a plasma CVD method.

[0127] A sample including the oxide conductor film (OC) is prepared by forming a 100-nm-thick In—Ga—Zn oxide film over a glass substrate by a sputtering method using a sputtering target with an atomic ratio of In:Ga:Zn=1:1:1, performing heat treatment at 450° C. in a nitrogen atmosphere and then performing heat treatment at 450° C. in an atmosphere of a mixed gas of nitrogen and oxygen, and forming a silicon nitride film over the oxide film by a plasma CVD method.

[0128] As can be seen from FIG. 2, the temperature dependence of resistivity of the oxide conductor film (OC) is lower than the temperature dependence of resistivity of the oxide semiconductor film (OS). Typically, variation of the resistivity of the oxide conductor film (OC) at temperatures from 80 K to 290 K is more than -20% and less than +20%. Alternatively, the range of variation of resistivity at temperatures from 150 K to 250 K is from more than -10% to less than +10%. In other words, the oxide conductor is a degenerate semiconductor and it is suggested that the conduction band edge agrees with or substantially agrees with the Fermi level. Therefore, the oxide conductor film can be used as the electrode of the capacitor, for example.

<Modification Example 1 of Touch Sensor>

[0129] A touch sensor of one embodiment of the present invention has flexibility.

[0130] A layer to be separated can be formed over a formation substrate, separated from the formation substrate, and then transferred to another substrate. With this method, for example, a layer to be separated which is formed over a substrate having a high heat resistance can be transferred to a substrate having a low heat resistance. Therefore, the forming temperature of the layer to be separated is not limited by the substrate having a low heat resistance.

[0131] For example, after the transistor 102, the capacitor 105, and the like are formed over a formation substrate, these elements are separated from the formation substrate. Then, these elements are transferred onto the flexible substrate by being bonded to the flexible substrate using an adhesive. Thus, a touch sensor shown in FIG. 1B can be manufactured. In FIG. 1B, the transistor 102 and the capacitor 105 are located between a flexible substrate 392 and a flexible substrate 398. The flexible substrate 392 and the insulating film 338 are bonded to each other with a bonding layer 394. The

flexible substrate 398, the conductive film 350, and the insulating film 348 are bonded together using a bonding layer 396. [0132] Furthermore, in FIG. 1B, structure examples of a terminal portion of the touch sensor and a driver circuit portion including the transistor 103 are illustrated. Structures of the transistor 102 and the capacitor 105 in a sensor portion are not described because they are similar to those in FIG. 1A. [0133] A transistor 103 included in the driver circuit portion differs from the transistor 102; in the transistor 103, a conductive film 303 is provided over the insulating film 312. The conductive film 303 can function as a second gate electrode. As compared with the transistor 102, the transistor 103 can have a high field-effect mobility and thus have high on-state current. As a result, a driver circuit portion that can operate at high speed can be formed. Furthermore, a touch sensor including a driver circuit portion occupying a small area can be formed. Note that in the example illustrated here, the transistor included in the driver circuit portion and the transistor included in the sensor portion have different structures. However, the transistor included in the driver circuit portion and the transistor included in the sensor portion may have the same structure. All of a plurality of transistors included in the driver circuit portion may have the same structure, or the plurality of transistors included in the driver circuit portion may have two or more kinds of structures. All of a plurality of transistors included in the sensor portion may have the same structure, or the plurality of transistors included in the sensor portion may have two or more kinds of structures. A transistor including one gate electrode may be used for the driver circuit portion, and a transistor including

[0134] The conductive film 303 as the second gate electrode of the transistor 103 and the conductive film 350 as the electrode of the capacitor 105 are preferably located over the same surface.

two gate electrodes may be used for the sensor portion.

**[0135]** It is preferable that the electrode of the transistor and the electrode of the capacitor be formed in the same step because the touch sensor can be manufactured in a small number of steps.

[0136] The conductive film 346 is electrically connected to an external input terminal through which a signal or a potential from the outside is transmitted to the driver circuit portion. Here, an example is described in which a flexible printed circuit (FPC) 808 is provided as the external input terminal. To prevent an increase in the number of manufacturing steps, the conductive film 346 is preferably formed using the same material step as those of the electrode or the wiring in the sensor portion or the driver circuit portion. Here, an example in which the conductive film 346 is formed using the same material and step as those of the electrodes included in the transistors 102 and 103 is described.

[0137] A connector 825 is connected to the FPC 808. The FPC 808 is electrically connected to the conductive film 346 through the connector 825.

[0138] In the touch sensor of one embodiment of the present invention, in the case where external light is delivered from the flexible substrate 392 side, the conductive film 304 is preferably formed using a light-blocking material so that the oxide semiconductor layer 308a of the transistor 102 provided in the sensor portion is not irradiated with light. Furthermore, it is preferable that a whole bottom surface (a surface in contact with the insulating film 305) of the oxide semiconductor layer 308a overlap with the conductive film 304. Note that for example, in the case where external light is

not delivered from the flexible substrate 392 side, the structures of the oxide semiconductor layer 308a and the conductive film 304 are not limited thereto, and a size relation of the oxide semiconductor layer 308a and the conductive film 304 in a top view thereof is not limited thereto. Also in the transistor 103 of the driver circuit portion, a whole bottom surface of the oxide semiconductor layer 308a may overlap with the conductive film 304.

#### Structure Example 2 of Touch Sensor>

[0139] FIG. 3A illustrates transistors 104 and 106 and the capacitor 105 in a touch sensor of one embodiment of the present invention. The transistor included in the touch sensor of one embodiment of the present invention has a top-gate structure. The transistor 104 and the capacitor 105 are provided in the sensor portion of the touch sensor, for example. The transistor 106 is provided in the driver circuit portion of the touch sensor, for example.

[0140] FIG. 3B is a top view of the transistor 104. A crosssectional view of the transistor 104 shown in FIG. 3A corresponds to a cross-sectional view along the dashed-dotted line X1-X2 in FIG. 3B. FIG. 3C is a top view of the transistor 106. A cross-sectional view of the transistor 106 shown in FIG. 3A corresponds to a cross-sectional view along the dashed-dotted line X3-X4 in FIG. 3C. FIG. 3E corresponds to a crosssectional view along the dashed-dotted line Y3-Y4 in FIG. 3C. Note that in FIGS. 3A and 3E, the substrate and some other components are not illustrated. Furthermore, in FIGS. 3B and 3C, the substrate, the insulating film, and some other components are not illustrated for the sake of clarity. Furthermore, the direction of the dashed dotted line X1-X2 may be called a channel length direction, and the direction of the dashed dotted line Y3-Y4 may be called a channel width direction.

[0141] The transistor 104 shown in FIGS. 3A and 3B includes the oxide semiconductor layer 308a over an insulating surface, the insulating film 305 over the oxide semiconductor layer 308a, the conductive film 304 overlapping with the oxide semiconductor layer 308a with the insulating film 305 provided therebetween, the insulating film 312 covering the oxide semiconductor layer 308a, the insulating film 305, and the conductive film 304, and the conductive films 310a and 310b connected to the oxide semiconductor layer 308a in an opening portion provided in the insulating film 312. Note that the insulating films 314 and 348 covering the insulating film 312, the conductive film 310a, and the conductive film 310b may be provided over the transistor 104.

[0142] In the transistor 104, the conductive film 304 functions as a gate electrode (also referred to as a top-gate electrode), the conductive film 310a functions as one of a source electrode and a drain electrode, and the conductive film 310b functions as the other of the source electrode and the drain electrode. Furthermore, in the transistor 104, the insulating film 338 functions as a base film of the oxide semiconductor layer 308a and the insulating film 305 functions as a gate insulating film.

[0143] The capacitor 105 includes the conductive film 350 as one of the pair of electrodes and the oxide conductor layer 308b as the other of the pair of electrodes. The insulating films 314 and 348 serve a dielectric layer of the capacitor 105. In other words, the insulating films 314 and 348 are provided for both the transistor 104 and the capacitor 105. In the example illustrated in FIG. 3A, the conductive film 310b and the conductive film 350 are in contact with each other. The con-

ductive film 310b and the conductive film 350 may be electrically connected to each other through another conductive film.

[0144] The oxide semiconductor layer 308a and the oxide conductor layer 308b are layers processed into island-like shapes through the same film formation step and the same etching step. It is preferable that the semiconductor layer of the transistor and the electrode of the capacitor be formed in the same step because the touch sensor can be manufactured in a small number of steps. Thus, a manufacturing cost can be reduced.

[0145] Next, the oxide semiconductor layer 308a included in the transistor 104 is described in detail below.

[0146] An element which forms an oxygen vacancy is contained in a region that does not overlap with the conductive film 304 in the oxide semiconductor layer 308a of the transistor 104. The element which feints an oxygen vacancy will be described as an impurity element. Typical examples of impurity elements are hydrogen, boron, carbon, nitrogen, fluorine, aluminum, silicon, phosphorus, chlorine, and rare gas elements. Typical examples of rare gas elements are helium, neon, argon, krypton, and xenon.

[0147] When the impurity element is added to the oxide semiconductor film, a bond between a metal element and oxygen in the oxide semiconductor film is cut, whereby an oxygen vacancy is formed. Alternatively, when the impurity element is added to the oxide semiconductor film, oxygen bonded to a metal element in the oxide semiconductor film is bonded to the impurity element, and the oxygen is released from the metal element, whereby an oxygen vacancy is formed. Thus, the carrier density is increased in the oxide semiconductor film, and the conductivity of the oxide semiconductor film is increased as a result.

[0148] A region in which the carrier density of the oxide semiconductor film is increased and the conductivity thereof is increased (hereinafter such a region is referred to as a low-resistance region) is formed in a cross section of the oxide semiconductor layer 308a in the channel length direction. The low-resistance region formed in the oxide semiconductor layer 308a has a plurality of structures. FIG. 3D shows an example of the plurality of structures. Note that in FIG. 3D, a channel length L corresponds to a length of a region between a pair of low-resistance regions.

[0149] As illustrated in FIG. 3D, the oxide semiconductor layer 308a includes a channel region 332a formed in a region overlapping with the conductive film 304 and low-resistance regions 332b and 332c between which the channel region 332a is provided and which contain the impurity elements. Note that as illustrated in FIG. 3D, in the cross-sectional shape in the channel length direction, the boundaries between the channel region 332a and the low-resistance regions 332b and 332c coincide with or substantially coincide with bottom end portions of the conductive film 304, with the insulating film 305 provided between the conductive film 304 and the boundaries. That is, in a top surface shape, the boundaries between the channel region 332a and the low-resistance regions 332b and 332c coincide with or substantially coincide with the bottom end portions of the conductive film 304.

[0150] In some cases, the oxide semiconductor layer 308a includes a region that does not overlap with the insulating film 305 and the conductive film 304 and is thinner than a region overlapping with insulating film 305 and the conductive film 304 (see FIG. 7G, for example). The thin region is thinner than the region of the oxide semiconductor film overlapping

with the insulating film 305 and the conductive film 304 by 0.1 nm or more and 5 nm or less, for example.

[0151] Note that the low-resistance regions 332b and 332c in the oxide semiconductor layer 308a function as a source region and a drain region. The impurity element is contained in the low-resistance regions 332b and 332c.

[0152] In the case where the impurity element is a rare gas element and the oxide semiconductor layer 308a is formed by a sputtering method, the channel region 332a and the low-resistance regions 332b and 332c each contain a rare gas element. Note that the concentrations of the rare gas elements in the low-resistance regions 332b and 332c are higher than the concentration of the rare gas element in the channel region 332a.

[0153] The reasons for this are as follows: in the case where the oxide semiconductor layer 308a is formed by a sputtering method, a rare gas is used as a sputtering gas, so that the oxide semiconductor layer 308a contains the rare gas; and a rare gas is intentionally added to the low-resistance regions 332b and 332c in order to form oxygen vacancies in the low-resistance regions 332b and 332c.

[0154] In the case where the impurity element is boron, carbon, nitrogen, fluorine, aluminum, silicon, phosphorus, or chlorine, the low-resistance regions 332b and 332c contain the above-described impurity element. Therefore, the concentrations of the above-described impurity elements in the low-resistance regions 332b and 332c are higher than the concentration of the above-described impurity element in the channel region 332a. Note that the concentrations of the impurity elements in the low-resistance regions 332b and 332c which are measured by secondary ion mass spectrometry can be greater than or equal to  $5\times10^{18}$  atoms/cm<sup>3</sup> and less than or equal to  $1\times10^{22}$  atoms/cm<sup>3</sup>, greater than or equal to  $1\times10^{21}$  atoms/cm<sup>3</sup>, or greater than or equal to  $5\times10^{19}$  atoms/cm<sup>3</sup> and less than or equal to  $5\times10^{19}$  atoms/cm<sup>3</sup> and less

[0155] In the case where the impurity element is hydrogen, the impurity element concentrations in the low-resistance regions 332b and 332c are higher than the impurity element concentration in the channel region 332a. Note that the concentrations of hydrogen in the low-resistance regions 332b and 332c which are measured by secondary ion mass spectrometry can be higher than or equal to  $8\times10^{19}$  atoms/cm³, higher than or equal to  $1\times10^{20}$  atoms/cm³, or higher than or equal to  $5\times10^{20}$  atoms/cm³.

[0156] Since the low-resistance regions 332b and 332c contain the impurity elements, oxygen vacancies and carrier densities are increased. As a result, the low-resistance regions 332b and 332c have higher conductivity.

[0157] Note that as the impurity element, a rare gas and one or more of hydrogen, boron, carbon, nitrogen, fluorine, aluminum, silicon, phosphorus, and chlorine may be used. In that case, in the low-resistance regions 332b and 332c, by interaction between oxygen vacancies formed by the rare gas and one or more of hydrogen, boron, carbon, nitrogen, fluorine, aluminum, silicon, phosphorus, and chlorine which is added, the conductivity of the low-resistance regions 332b and 332c is further increased in some cases.

[0158] The low-resistance regions 332b and 332c can be regarded as regions formed of an oxide conductor (or including an oxide conductor). In other words, the oxide conductor is a degenerate semiconductor and it is suggested that the conduction band edge agrees with or substantially agrees with the Fermi level. For that reason, an ohmic contact is

made between the oxide conductor and the conductive films functioning as a source electrode and a drain electrode; thus, contact resistance between the oxide conductor and the conductive films functioning as a source electrode and a drain electrode can be reduced.

[0159] When the impurity element in the oxide semiconductor layer 308a, in particular, the channel region 332a, is reduced, the carrier density of the oxide semiconductor film can be lowered. Therefore, in the oxide semiconductor layer 308a, in particular, the channel region 332a, carrier density can be less than or equal to  $1\times10^{17}$ /cm<sup>3</sup>, less than or equal to  $1\times10^{13}$ /cm<sup>3</sup>, or less than or equal to  $1\times10^{13}$ /cm<sup>3</sup>, or less than or equal to  $1\times10^{11}$ /cm<sup>3</sup>.

[0160] Note that an oxide semiconductor film with a low impurity concentration and a low density of defect states can be used for the oxide semiconductor layer 308a, in which case the transistor can have more excellent electrical characteristics

[0161] The oxide semiconductor layer 308a may have a non-single crystal structure, for example. The non-single-crystal structure includes a c-axis aligned crystalline oxide semiconductor (CAAC-OS) which is described later, a polycrystalline structure, a microcrystalline structure which is described later, or an amorphous structure, for example. Among the non-single crystal structure, the amorphous structure has the highest density of defect levels, whereas CAAC-OS has the lowest density of defect levels.

[0162] Note that the oxide semiconductor layer 308a may be a mixed film including two or more of the following: a region having an amorphous structure, a region having a microcrystalline structure, a region having a polycrystalline structure, a region of CAAC-OS, and a region having a singlecrystal structure. The mixed film has a single-layer structure including, for example, two or more of a region having an amorphous structure, a region having a microcrystalline structure, a region having a polycrystalline structure, a region of CAAC-OS, and a region having a single-crystal structure in some cases. Furthermore, the mixed film has a stackedlayer structure of two or more of a region having an amorphous structure, a region having a microcrystalline structure, a region having a polycrystalline structure, a region of CAAC-OS, and a region having a single-crystal structure in some cases.

[0163] Note that in the oxide semiconductor layer 308a, the crystallinity of the channel region 332a is different from the crystallinity of each of the low-resistance regions 332b and 332c in some cases. Specifically, in the oxide semiconductor layer 308a, the crystallinity of the channel region 332a is higher than the crystallinity of each of the low-resistance regions 332b and 332c. This is because, when the impurity element is added to the low-resistance regions 332b and 332c, the low-resistance regions 332b and 332c are damaged and thus have lower crystallinity.

[0164] In the transistor 104 described in this embodiment, the channel region 332a is sandwiched between the low-resistance regions 332b and 332c functioning as a source region and a drain region. Therefore, the on-state current and field-effect mobility of the transistor 104 are high. In addition, in the transistor 104, the impurity element is added to the oxide semiconductor layer 308a using the conductive film 304 as a mask. That is, the low-resistance region can be formed in a self-aligned manner.

[0165] Furthermore, in the transistor 104, the conductive film 304 functioning as a gate electrode does not overlap with

the conductive films 310a and 310b functioning as a source electrode and a drain electrode. Therefore, parasitic capacitance between the conductive film 304 and the conductive films 310a and 310b can be reduced. As a result, in the case where a large-area substrate is used as the substrate, signal delay in the conductive films 304 and the conductive films 310a and 310b can be reduced.

[0166] The transistor 106 shown in FIGS. 3A, 3C, and 3E includes the conductive film 303 over the insulating film 338, an insulating film 301 over the insulating film 338 and the conductive film 303, the oxide semiconductor layer 308a overlapping with the conductive film 303 with the insulating film 301 provided therebetween, the insulating film 305 over the oxide semiconductor layer 308a, the conductive film 304 overlapping with the oxide semiconductor layer 308a with the insulating film 305 provided therebetween, the insulating film 312 covering the oxide semiconductor layer 308a, the insulating film 305, and the conductive film 304, and the conductive films 310a and 310b connected to the oxide semiconductor layer 308a in opening portions 140a and 140bprovided in the insulating film 312. Note that the insulating films 314 and 348 covering the insulating film 312, the conductive film 310a, and the conductive film 310b may be provided over the transistor 106.

[0167] In the transistor 106, the conductive film 303 functions as a first gate electrode (also referred to as a bottom-gate electrode), the conductive film 304 functions as a second gate electrode (also referred to as a top-gate electrode), the conductive film 310a functions as one of a source electrode and a drain electrode, and the conductive film 310b functions as the other of the source electrode and the drain electrode. Furthermore, in the transistor 106, the insulating film 301 functions as a first gate insulating film, and the insulating film 305 functions as a second gate insulating film.

[0168] Note that the transistor 106 shown in FIGS. 3A, 3C, and 3E is different from the transistor 104 described above and has a structure in which the conductive film functioning as a gate electrode is provided over and under the oxide semiconductor layer 308a. As shown in the transistor 106, a transistor included in a touch sensor of one embodiment of the present invention may have two or more gate electrodes.

[0169] As illustrated in FIG. 3E, the conductive film 304 functioning as a second gate electrode is connected to the conductive film 303 functioning as a first gate electrode in an opening portion 139 provided in the insulating film 301 and the insulating film 305.

[0170] Therefore, the same potential is applied to the conductive film 304 and the conductive film 303. Note that the opening portion 139 is not necessarily provided, so that different potentials are supplied to the conductive film 304 and the conductive film 303.

[0171] As illustrated in FIG. 3E, the oxide semiconductor layer 308a is positioned to face each of the conductive film 303 functioning as a first gate electrode and the conductive film 304 functioning as a second gate electrode, and is sandwiched between the two conductive films functioning as gate electrodes. The length in the channel width direction of the conductive film 304 functioning as a second gate electrode is longer than the length in the channel width direction of the oxide semiconductor layer 308a. In the channel width direction, the whole oxide semiconductor layer 308a is covered with the conductive film 304 with the insulating film 305 provided therebetween. Since the conductive film 304 functioning as a second gate electrode is connected to the conductive

tive film 303 functioning as a first gate electrode in the opening portion 139 provided in the insulating film 305, a side surface of the oxide semiconductor layer 308a in the channel width direction faces the conductive film 304 functioning as a second gate electrode with the insulating film 305 provided therebetween.

[0172] In other words, in the channel width direction of the transistor 106, the conductive film 303 functioning as a first gate electrode and the conductive film 304 functioning as a second gate electrode are connected to each other in the opening portion provided in the insulating film 301 functioning as a first gate insulating film and the insulating film 305 functioning as a second gate insulating film; and the conductive film 303 and the conductive film 304 surround the oxide semiconductor layer 308a with the insulating film 301 functioning as a first gate insulating film and the insulating film 305 functioning as a second gate insulating film provided therebetween.

[0173] Such a structure enables electric fields of the conductive film 303 functioning as a first gate electrode and the conductive film 304 functioning as a second gate electrode to electrically surround the oxide semiconductor layer 308a included in the transistor 106. A device structure of a transistor, like that of the transistor 106, in which electric fields of a first gate electrode and a second gate electrode electrically surround an oxide semiconductor film where a channel region is formed can be referred to as a surrounded channel (s-channel) structure.

[0174] Since the transistor 106 has the s-channel structure, an electric field for inducing a channel can be effectively applied to the oxide semiconductor layer 308a by the conductive film 303 functioning as a first gate electrode or the conductive film 304 functioning as a second gate electrode; therefore, the current drive capability of the transistor 106 can be improved and high on-state current characteristics can be obtained. Since the on-state current can be increased, it is possible to reduce the size of the transistor 106. In addition, since the transistor 106 has a structure in which the oxide semiconductor layer 308a is surrounded by the conductive film 303 functioning as a first gate electrode and the conductive film 304 functioning as a second gate electrode, the mechanical strength of the transistor 106 can be increased.

[0175] Note that in the channel width direction of the transistor 106, an opening portion which is different from the opening portion 139 may be formed on the side of the oxide semiconductor layer 308a where the opening portion 139 is not formed.

<Modification Example 2 of Touch Sensor>

[0176] A touch sensor of one embodiment of the present invention includes an oxide semiconductor layer having a stacked-layer structure.

[0177] Next, in an example of a touch sensor illustrated in FIG. 8A, a stacked-layer structure of an oxide semiconductor layer 307a and an oxide semiconductor layer 309a is used instead of the oxide semiconductor layer 308a used for the transistor 102. Furthermore, in the example of the touch sensor illustrated in FIG. 8A, a stacked-layer structure of the oxide semiconductor layer 307a and the oxide semiconductor layer 309a is used instead of the oxide conductor layer 308b used for the capacitor 105. Thus, the other components are the same as those of the touch sensor illustrated in FIG. 1A; hence, the above description can be referred to. Note that the oxide semiconductor layer 307b and the oxide semiconductor

layer 309b can also be called oxide conductor layers. Therefore, in FIG. 8A, the oxide semiconductor layer 307b and the oxide semiconductor layer 309b are hatched like the oxide conductor layer 308b in FIG. 1A or the like. Note that in FIG. 8A, the substrate and other components are not illustrated.

[0178] A metal oxide of the oxide semiconductor layers 307a and 307b (in this specification below, also referred to as the oxide semiconductor layer 307) and a metal oxide of the oxide semiconductor layers 309a and 309b (in this specification below, also referred to as an oxide semiconductor layer 309) preferably have at least one constituent element in common. Furthermore, the constituent elements of the oxide semiconductor layer 307 and the oxide semiconductor layer 309 may be the same and the compositions of the constituent elements of the oxide semiconductor layer 307 and the oxide semiconductor layer 309 may be different from each other.

[0179] In the case where the oxide semiconductor layer 307 is an In-M-Zn oxide (M represents Al, Ga, Ge, Y, Zr, Sn, La, Ce, or Hf), it is preferable that the atomic ratio of metal elements of a sputtering target used for forming a film of the In-M-Zn oxide satisfy In≥M and Zn≥M As the atomic ratio of metal elements of such a sputtering target, In:M:Zn=1:1:1, In:MZn=5:5:6 (1:1:1.2), and In:MZn=3:1:2 are preferable. Note that the atomic ratio of metal elements in the formed oxide semiconductor layer 307 varies from the above atomic ratio of metal elements of the sputtering target within a range of ±20% as an error.

[0180] When the oxide semiconductor layer 307 is an In-M-Zn oxide, the atomic ratio of In to M when the summation of In and M is assumed to be 100 at. % is preferably as follows: the atomic percentage of In is higher than or equal to 25 at. % and the atomic percentage of M is lower than 75 at. %; more preferably, the atomic percentage of In is higher than or equal to 34 at. % and the atomic percentage of M is lower than 66 at. %.

[0181] The energy gap of the oxide semiconductor layer 307 is 2 eV or more, preferably 2.5 eV or more, more preferably 3 eV or more. In this manner, off-state current of a transistor can be reduced by using an oxide semiconductor having an energy gap.

[0182] The thickness of the oxide semiconductor layer 307 is greater than or equal to 3 nm and less than or equal to 200 nm, preferably greater than or equal to 3 nm and less than or equal to  $100 \, \text{nm}$ , more preferably greater than or equal to  $3 \, \text{nm}$  and less than or equal to  $50 \, \text{nm}$ .

[0183] The oxide semiconductor layer 309 is typically an In—Ga oxide, an In—Zn oxide, or an In-M-Zn oxide (M is Al, Ga, Ge, Y, Zr, Sn, La, Ce, or Hf). The energy of the bottom of the conduction band in the oxide semiconductor layer 309 is closer to a vacuum level than that of the oxide semiconductor layer 307 is, and typically, the difference between the energy of the bottom of the conduction band in the oxide semiconductor layer 309 and the energy of the bottom of the conduction band in the oxide semiconductor layer 307 is 0.05 eV or more, 0.07 eV or more, or 0.1 eV or more, or 0.15 eV or more, and 2 eV or less, 1 eV or less, 0.5 eV or less, or 0.4 eV or less. That is, the difference between the electron affinity of the oxide semiconductor layer 309 and the electron affinity of the oxide semiconductor layer 307 is 0.05 eV or more, 0.07 eV or more, 0.1 eV or more, or 0.15 eV or more, and 2 eV or less, 1 eV or less, 0.5 eV or less, or 0.4 eV or less.

[0184] The oxide semiconductor layer 309 containing a larger amount of the element M in an atomic ratio than the amount of In in an atomic ratio may have any of the following

effects: (1) the energy gap of the oxide semiconductor layer 309 is wide; (2) the electron affinity of the oxide semiconductor layer 309 is low; (3) an impurity from the outside is blocked; (4) the insulating property is more excellent than that of the oxide semiconductor layer 307. Further, oxygen vacancies are less likely to be generated in the oxide semiconductor layer 309 containing a larger amount of M in an atomic ratio than the amount of In in an atomic ratio because M is a metal element which is strongly bonded to oxygen.

[0185] When an In-M-Zn oxide is used for the oxide semi-conductor layer 309, the proportions of In and M when the summation of In and M is assumed to be 100 atomic % is preferably as follows: the atomic percentage of In is less than 50 at. % and the atomic percentage of M is greater than or equal to 50 at. %; further preferably, the atomic percentage of In is less than 25 at. % and the atomic percentage of M is greater than or equal to 75 at. %.