US 20210293083A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2021/0293083 A1

## Tarng et al.

#### (54) SMART WINDOW FOR GREEN ENERGY SMART HOME AND SMART GRID WITH FIELD PROGRAMMABLE SYSTEM ON CHIP FPSOC OF ANLINX, MILINX AND ZILINX

- (71) Applicant: Min Ming Tarng, San Jose, CA (US)

- (72) Inventors: Min Ming Tarng, San Jose, CA (US); Mei-Jech Lin, San Jose, CA (US); Eric Yu-Shiao Tarng, San Jose, CA (US); Alfred Yu-Chi Tamg, San Jose, CA (US); Angela Yu-Shiu Tarng, San Jose, CA (US); Huang-Chang Tarng, San Jose, CA (US)

- (73) Assignees: PDcGA: Professional Disclub Golf Association, San Jose, CA (US); Tang System, San Jose, CA (US)

- (21)Appl. No.: 17/193,263

- (22)Filed: Mar. 5, 2021

#### **Related U.S. Application Data**

Continuation-in-part of application No. 12/752,121, (63) filed on Apr. 1, 2010, now Pat. No. 9,520,827, Continuation-in-part of application No. 12/422,719, filed on Apr. 13, 2009, now Pat. No. 8,487,653, Continuation-in-part of application No. 15/810,005, filed on Nov. 11, 2017, now Pat. No. 10,328,357, Continuation-in-part of application No. 12/317,973, filed on Dec. 31, 2008, now Pat. No. 8,089,324, Continuation-

#### (Continued)

#### **Publication Classification**

(51) Int. Cl.

| I) |

|----|

| ĺ) |

| ĺ) |

| I) |

|    |

### Sep. 23, 2021 (43) **Pub. Date:**

|      | H02J 50/12<br>H04W 4/33 | (2006.01)<br>(2006.01)                                                                       |

|------|-------------------------|----------------------------------------------------------------------------------------------|

| (52) | U.S. Cl.                | (2000.01)                                                                                    |

| ( )  |                         | E06B 9/24 (2013.01); G02F 1/163                                                              |

|      |                         | 01); G02F 1/1533 (2013.01); F24F                                                             |

|      |                         | 8.01); <i>F24F 11/83</i> (2018.01); <i>E06B</i><br>5 (2013.01); <i>F24F 11/89</i> (2018.01); |

|      |                         | (2014.12); <i>H02J 50/12</i> (2016.02);                                                      |

H04W 4/33 (2018.02): E06B 2009/2464 (2013.01); F24F 11/88 (2018.01)

#### (57)ABSTRACT

The smart window for the smart home and smart grid can harvest energy and supply power to the home, grid and window itself. The smart window for the smart home and smart grid has all the Electrochromic panel, Solar panel and Multimedia panel been the same full window wide view and aligned with each other in IGU. To be a home automation system, the smart window has local/remote access/control capabilities. There are several types of smart windows working as master device or slave device. The operation of smart window automation system has three modes, normal/ open mode, shut/tint mode and smart phone mode. The tube of air circulation system is hidden inside the frame surrounding IGU. Most of the electronic components are integrated to be FPSOC Field Programmable System On Chip that all the electronic component is hidden in the frame surrounding IGU, too. Therefore, the smart window doesn't have any blockage of window view with the Solar panel, Electrochromic panel, Multimedia panel and air circulation system. The smart window has the clean outlook as the conventional dual panel IGU does. The master device of the smart window system is similar to the huge screen working as a smart phone. In normal/open mode, the smart window is similar to the conventional dual panel window having the full-panel clean and clear view. For the different architectures of the smart homes, the smart window must have versatile alignments and system control that the smart window has to be implemented with the Field Programmable System On Chips of Anlinx, Milinx and Zilinx made of the W5RS advanced FPSOC chip technologies.

#### **Related U.S. Application Data**

in-part of application No. 12/291,984, filed on Nov. 14, 2008, now Pat. No. Plant 20,686, Continuationin-part of application No. 12/291,618, filed on Nov. 12, 2008, now Pat. No. 7,876,188, Continuation-inpart of application No. 12/229,412, filed on Aug. 23, 2008, now Pat. No. 8,089,323, Continuation-in-part of application No. 12/082,601, filed on Apr. 12, 2008, now abandoned, Continuation-in-part of application No. 12/079,179, filed on Mar. 25, 2008, now Pat. No. 8,089,353, Continuation-in-part of application No. 11/593,271, filed on Nov. 6, 2006, now Pat. No. 7,511,589, Continuation-in-part of application No. 11/500,125, filed on Aug. 5, 2006, now Pat. No. 7,525,392, Continuation-in-part of application No. 08/892,358, filed on Jul. 14, 1997, now Pat. No. 5,850,093, said application No. 11/500,125 is a continuation-in-part of application No. 08/854,800, filed on May 12, 1997, now abandoned, Continuation-in-part of application No. 08/081,074, filed on Jun. 22, 1993, now Pat. No. 5,793,125, Continuation-in-part of application No. 15/472,262, filed on Mar. 28, 2017, now abandoned, which is a continuation-in-part of application No. 13/918,989, filed on Jun. 16, 2013, now abandoned.

Sep. 23, 2021 Sheet 1 of 82

Sep. 23, 2021 Sheet 2 of 82

FIG.1B

# **Patent Application Publication**

Sep. 23, 2021 Sheet 5 of 82

US 2021/0293083 A1

FIG.4D

FIG.4B

FIG.5B

FIG.5A

ital Cuit

C. D.

Sep. 23, 2021 Sheet 22 of 82

FIG.14A

I(t)

FIG.14C

(

FIG.14E1

. Maria

. Mili

2 \*\*\*\*\* Power and ground noise seen in 2 e S Ş conventional digital circuit . 100 Ground Noise + ÿ Nos ...... Ż Ż à Ż Ŕ Ż Ŵ Ì

FIG.18D

**Patent Application Publication**

FIG.26G

Sep. 23, 2021 Sheet 43 of 82

Sep. 23, 2021 Sheet 45 of 82

Ò₿

$\triangleleft \blacktriangleleft$

$\bigcirc \triangleleft \square$

$V_{CM}$

VCM

$V_{CM}$

$\sim$ +

5

FIG.32B

Ą

FIG.32A

FIG.32F

Sep. 23, 2021 Sheet 60 of 82

Sep. 23, 2021 Sheet 63 of 82

FIG.39B

FIG.39D

FIG.45K

FIG.48B

# SMART WINDOW FOR GREEN ENERGY SMART HOME AND SMART GRID WITH FIELD PROGRAMMABLE SYSTEM ON CHIP FPSOC OF ANLINX, MILINX AND ZILINX

# RELATED APPLICATIONS

**[0001]** This patent application is the Continuation in Part application of application of

- **[0002]** U.S. application Ser. No. 12/752,121 filed Apr. 1, 2010 claiming priorities of

- [0003] U.S. application Ser. No. 12/422,719 filed Apr. 13, 2009;

- [0004] U.S. patent application Ser. No. 15/810,005 filed Nov. 11, 2017, now U.S. Pat. No. 10,328,357 issued in Jun. 25, 2019;

- [0005] U.S. patent application Ser. No. 12/317,973, filed Dec. 31, 2008, now U.S. Pat. No. 8,089,324 issued on Jan. 3, 2012;

- [0006] U.S. patent application Ser. No. 12/291,984, filed Nov. 12, 2008;

- [0007] U.S. patent application Ser. No. 12/291,618, filed Nov. 12, 2008, now U.S. Pat. No. 7,876,188 issued on Jan. 25, 2011;

- [0008] U.S. patent application Ser. No. 12/288,770, filed Oct. 23, 2008, now U.S. Pat. No. 7,663,349 issued on Feb. 16, 2010;

- [0009] U.S. patent application Ser. No. 12/229,412, filed Aug. 23, 2008, now U.S. Pat. No. 8,089,323 issued on Jan. 3, 2012;

- [0010] U.S. patent application Ser. No. 12/082,601, filed Apr. 12, 2008;

- [0011] U.S. patent application Ser. No. 12/079,179, filed Mar. 25, 2008, now U.S. Pat. No. 8,089,353 issued on Jan. 3, 2012;

- [0012] U.S. patent application Ser. No. 11/593,271, filed Nov. 6, 2006, now U.S. Pat. No. 7,511,589 issued on Mar. 31, 2009;

- [0013] U.S. patent application Ser. No. 11/500,125, filed Aug. 5, 2006, now U.S. Pat. No. 7,525,392 issued on Apr. 28, 2009;

- [0014] U.S. patent application Ser. No. 08/892,358, filed Jul. 14, 1997, now U.S. Pat. No. 5,850,093 issued on Dec. 15, 1998;

- [0015] U.S. patent application Ser. No. 08/854,800, filed Mar. 23, 1992, now U.S. Pat. No. 5,280,200 issued on Jan. 18, 1994;

- [0016] U.S. patent application Ser. No. 08/081,074, filed Jun. 22, 1993, now U.S. Pat. No. 5,793,125 issued on Aug. 11, 1998;

- [0017] U.S. patent application Ser. No. 577,792, filed Sep. 5, 1990, now U.S. Pat. No. 5,198,691 issued on Mar. 30, 1993;

- [0018] U.S. patent application Ser. No. 577,791, filed Sep. 5, 1990, now U.S. Pat. No. 5,111,076 issued on May 5, 1992;

- **[0019]** which was the Continue in Part of U.S. application Ser. No. 13/918,989 filed Jun. 16, 2013 claiming priorities of which was the Continue in Part of U.S. application Ser. No. 15/472,262 filed Mar. 28, 2017

- **[0020]** which herein incorporated by references in its entirety.

# BACKGROUND FIELD OF INVENTION

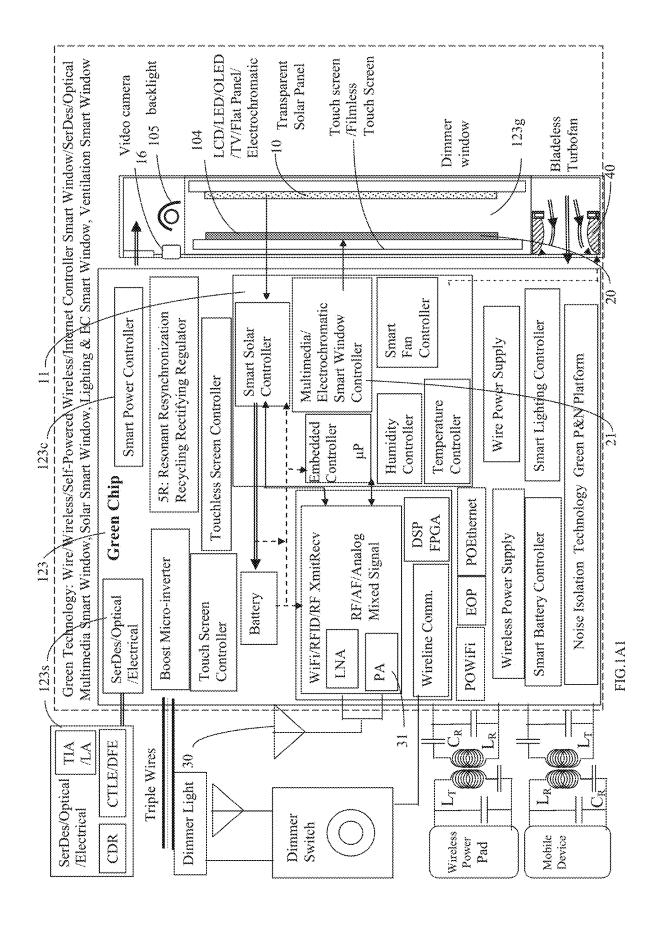

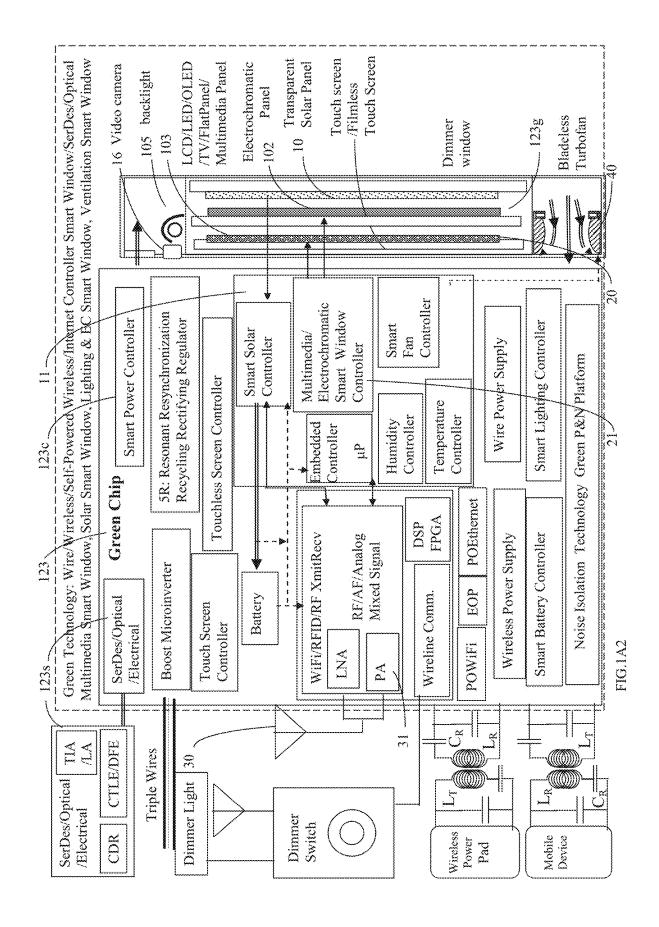

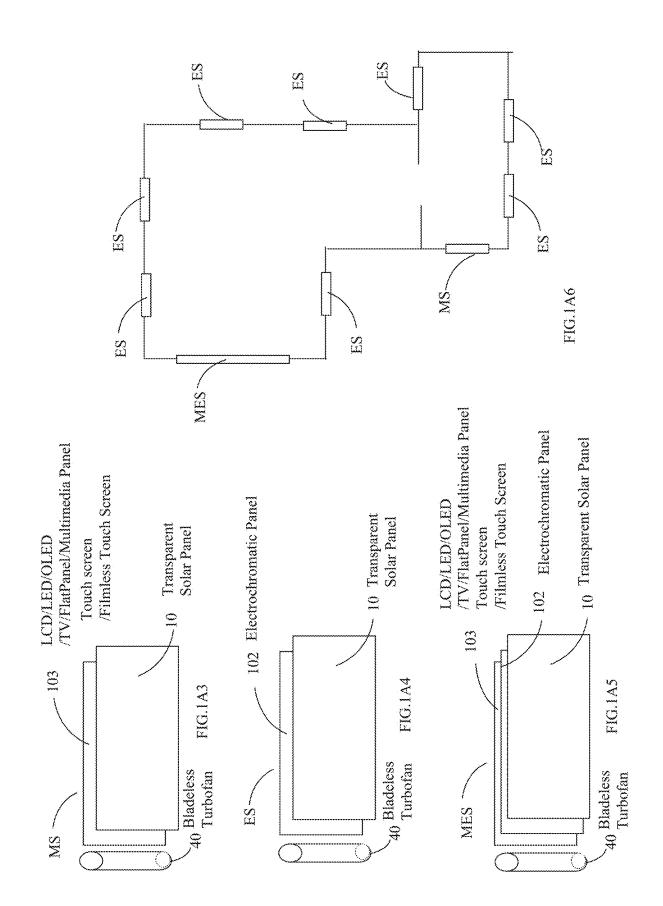

[0021] The smart window is the system design for the future smart home has the entertainment, remote access and control, green power management, lighting management and air condition, etc. The smart home is the home automation system design having the Master and Slave devices. (1) To be feasible, the smart window must be as transparent having window view as the conventional IGU Insulated Glass Unit. (2) To have the same window view as conventional IGU, all the complex electronic components are embedded in the frame of the smart window. (3) To have all the complex electronic components embedded in the frame, all the complex components are integrated to be the FPSOC chip, Field programmable System On Chip. (4) To prove all the electronic components being able to be integrated, the Field Programmable System On Chip FPSOC of Anlinx, Milinx and Zilinx is disclosed in detail. As shown in FIG. 1A3, FIG. 1A4, FIG. 1A5 and FIG. 1A6, the Green Energy Smart Window home automation system is implemented with the master smart window and the slave smart window. As shown in FIG. 1A5, the master smart window has the transparent Multimedia panel, Electrochromic panel and transparent Solar panel. As shown in FIG. 1A3, the master smart window has transparent Multimedia panel and transparent Solar panel. As shown in FIG. 1A4, the slave smart window has the Electrochromic panel and transparent Solar panel. To have the energy harvest for smart grid, the transparent solar panel has the full window area. To have the entertainment, the transparent multimedia panel has the fill window area, too. To have the clean and clear vision, the air circulation of the AC air conditioner cannot pass through the window panel area and must pass through the frame post of the window as shown in FIG. 1N1. The green energy smart window further comprising smart fan. The smart fan comprises the pipe, bladeless turbofan and temperature sensor inside the frame of IGU of the green energy smart window. The bladeless turbofan locates at the opening of the pipe and circulates the air for air conditioning through the pipe. The temperature sensor detects the temperatures of air to activate the smart fans.

[0022] The innovative smart window system design integrates all the different technologies to be the smart window. The smart window for the green energy smart home has the patentable innovations for the following multiple functions: (1) controlling the light and heat injecting into rooms; (2) air conditioning tube design for the clean and clear IGU; (3) both local and remote/internet/wireless access control for smart window automation system of green energy smart home; (4) not only providing energy to smart window itself but also providing energy to smart home and smart grid; (5) in the normal Open mode, the complete view of the smart window is clean and clear without any blockage and dust, etc.; (6) in the Smart Phone mode, the smart window serves as the entertainment, communication, computation, local and remote control access, etc.; (7) in the Shut Mode or Smart Phone Mode, the smart window serves as the screen to block the view of the smart window; (8) with the FPSOC Field Programmable System On Chip of Anlinx, Milinx and Zilinx chips, the smart window can serve the versatile requirements of different architectures of smart home; (9) the electronic components are integrated in the FPSOC chip that all the electronic blocks can be embedded in the frame 2

to have the clean view as the conventional window does. None of the prior inventions has the above nine characteristics.

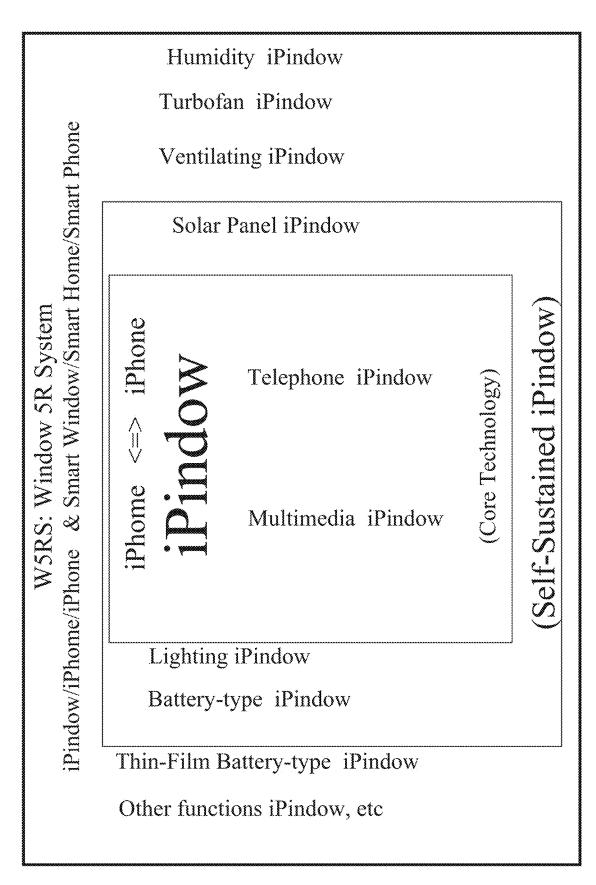

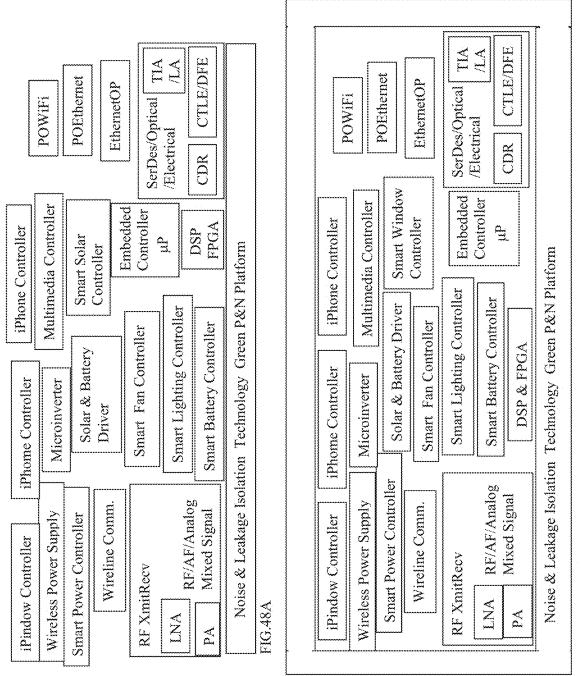

[0023] As shown in the FIG. 1A, the Green Energy Smart Window of W5RS is the new standard which is promoted by the innovative company, Tang System. The transparent multimedia panel, electrochromic panel and transparent solar panel are in the side view. However, the electronic block diagrams are implemented with FPSOC and embedded in the smart window frame. A Green Energy Smart Window of Wireless Window 5R System W5RS is constituted of Transparent Multimedia panel, Electrochromic panel and Transparent Solar panel, etc. The Transparent Solar Cell panel harvests solar energy to be electric energy to provide power to Transparent Multimedia panel and Electrochromic panel. The Green Energy Smart Window is not only self-powered but also provides the electrical energy to the home, smart grid and mobile devices. "W5RS" is the killer product application in Silicon Valley and "5R" is the killer core IP technology in Silicon Valley. "W5" represents the "Wireless and Wireline Weaving Wishful Window". "5R" represents "Recycling Resonant Resynchronizing Rectifying Regulator". "5S" represents the "Smart Solar Supply Silicon System".

[0024] In summary, the energy supplied for the house warming or the house cooling is the largest power consumption. The largest amount energy dissipation is the window of the house. The Electrochromic EC window is adopted to minimize the largest power consumption. However, the Electrochromic EC window has the leaking current that the EC window controller has the stand-by power consumption. So, we need to have the Green Energy Smart Window for the Smart Home. The Green Energy Smart Window of Smart Home has to be energy self-contained. The transparent solar window of the Smart Window for Smart Home can convert the sunlight energy to be the energy of battery, smart grid and electrochromic EC window, etc. To have the clear window view, all the electronic components are embedded inside the frame of the smart window. To have all the electronic component embedded inside the frame, most of the electronic components are integrated to be the FPSOC. Therefore, the FPSOC is the key technology for the implementation of the clear view smart window. The 23Less Green Technologies for the Field Programmable System On Chip FPSOC of the Green Energy Smart Window are as follows.

- **[0025]** (1) Defectless Uniform multi-state dimmer EC Glass;

- [0026] (2) PowerLoss-Less 5R: Recycling Resonant Resynchronous Rectifier Regulator;

- [0027] (3) H-Bridgeless ACIDC converter;

- [0028] (4) RF-Noiseless Window Driver;

- [0029] (5) H-Bridgeless Microinverter;

- [0030] (6) Rippleless Battery Charger;

- [0031] (7) Curtainless Smart Window:

- [0032] (8) Filmless Touch Screen:

- [0033] (9) Touchless Screen:

- [0034] (10) Rippless Fast Lock PLL;

- [0035] (11) Humidity-EMI-Less Xtaless LC Clock with plastic package;

- [0036] (12) bladeless turbofan;

- [0037] (13) PowerLoss-Less PA;

- [0038] (14) Xtaless Clock;

- [0039] (15) Inductorless SNIPS;

- [0040] (16) Ground BounceLess I/O;

- **[0041]** (17) Overshootless LDO;

- [0042] (18) Rippleless LDO;

- [0043] (19) Sawless LNA;

- [0044] (20) Capless LDO;

- [0045] (21) Diodeless Random Generator;

- [0046] (22) Resistorless Current Sensor;

- [0047] (23) Brakeless Motor Vehicle;

[0048] So, the green technology needs to provide the house energy to fill up the energy requirement. It needs to convert the conventional window to be the Green Energy Smart Window. It needs to incorporate all the dimmer light, dimmer window, multimedia panel, electrochromic panel and solar panel, etc. to be wireless network. For the versatile complex home environment, through the wireless network, the master smart window control the slave smart window. The green technology is for the smart window multimedia panel, solar panel and EC panel, etc. To have the efficient wireless charging of Power over WiFi, PoWiFi, the RF power amplifier PA of the window controller needs to be power efficient. The WiFi PA has power efficiency to be less than 15%. For the WiFi standard, our Power-Lossless conjugated PA has the power efficiency more than 75%. To receive the wireless efficiently, the 5R core technology converts the AC sinusoidal power energy to DC energy with high power efficiency being larger than 95%. Even for the wireless power supply standards of the Wireless Power Consortium (WPC) Qi and Alliance For Wireless Power (A4WP), the novel "single stage" 5R can have the AC/DC power efficiency as high as 95% which is the highest record in the world. It is the record of the world.

**[0049]** Furthermore, our Sawless low noise amplifier LNA works in the noiseless integrated chip with our Power-Lossless conjugated PA. Our noise isolation technology is the key technology for the next-generation cutting-edge Field-System-On-Chip FPSOC. The controller costs a lot. The controller has to be the integrated chip to save the cost. To integrate the controller to be an integrated chip, it must have the noise isolation technology. To merge ASIC with FPGA to be the FPSOC, it needs the Noise Isolation Technology of Green Technology. With our 23Less Green Technology, we can generate the noiseless Field Programmable System On Chip FPSOC. With our ultrasonic assisted deposition, platen and hardening process, the Defectless Uniform multi-state dimmer EC Glass can be achieved to make the smart EC Window to be commercial.

[0050] A Green Energy Smart Window of Wireless 5R System W5RS is constituted of transparent Multimedia panel, Electrochromic panel and transparent Solar panel. The transparent Solar Cell panel harvests solar energy to be electric energy to provide power to transparent Multimedia panel and Electrochromic panel. The electrical energy further provides to smart grid and mobile devices. Furthermore, Green Energy Smart Window of W5RS adopts the isolation technology to integrate the FPGA, Analog Front, RF Front, Digital circuits. etc. to be FPSOC. ASIC is Application Specific Integrated Circuit. FPGA is Field Programmable Gate Array and FPSOC is the Field-System-On-Chip. For the Green Technology, FPSOC will merge ASIC and FPGA together to be the Field-System-On-Chip. As the semiconductor device process continues shrinking down, the mask price and process price are much higher. The product revenue of one-generation cannot recover the investment. It needs the revenue of several generations to cover the Nonrecurring engineering (NRE) cost. So, all the chips will be forced to be FPSOC. So far, there are ASIC and FPGA two categories. In the future, it will only have FPSOC, Field-System-On-Chip.

**[0051]** Anlinx is analog programmable chip. Milinx is mixed signal programmable chip. Zilinx is the analog, digital, mixed signal and RF programmable chip. The Field-System-On-Chip FPSOC of Anlinx, Milinx and Zilinx is based on the 23Less green technology to integrate the FPGA with ASIC to be the field programmable FPSOC. Thanks to the cooperative works of Dr. Mei Jech Lin, Eric Yu-Shiao Tarng, Alfred Yu-Chi Tarng. Angela Yu-Shiu Tarng, Shun-Yu Nieh and Huang-Chang Tarng, the revolutionary innovations had developed to be the FPSOC of Anlinx, Milinx and Zilinx.

# BACKGROUND—DESCRIPTION OF PRIOR ART

[0052] The smart window is to implement the innovative green energy smart home and smart grid, etc. However, this smart window concept doesn't exist before. Due to the lack of the FPSOC technologies, the electrochromic window, the solar energy harvest panel, multimedia TV and air circulation, etc. technologies are existed piece by piece and they cannot integrate as the smart window does. The solar energy harvest panel doesn't have the full panel width as the electrochromic window does. The solar energy panel blocks the sunshine that the solar energy harvest panel is only a small portion of the window panel. It cannot generate enough power to the smart grid as well as the smart home does. Furthermore, the air circulation flows between the panels. It violates the working principle of Insulated Glass Unit IGU. Therefore, there is no air circulation in the IGU of electrochromic window.

[0053] Furthermore, the system integration of the multiple smart panels doesn't exist. The smart solar panel doesn't exist. The Electrochromic window consumes a lot of power due to the power leakage of the electrochromic thin-film battery of the electrochromic glass. The Multimedia window is not compatible with Electrochromic window. The Solar Window doesn't provide energy to smart grid and mobile devices, either. Furthermore, the FPGA field programmable gate array cannot integrate the high performance ADC on the same chip. The switch noise generated by the FPGA will destroy all the performance of the high performance ADC analog to digital convener. Therefore, there is no high performance ADC on FPGA. The radio front, analog front RF/AF/analog circuits cannot be integrated on FPGA, either. All these ADC and RF/AF/analog circuits are left to be on the ASIC application specific integrated chip. The chips are the noise generators. All the noise generated by the chips is dumped on the board. There is an implicit assumption that the board is the ground having the infinite capacitance. However, this implicit assumption is no more true as the mobile products becomes thin and small. There is no big board to serve as the ideal ground. Since there is no isolation technology in the conventional chip that the ASIC still has to be used. The noise isolation of the conventional chip adopts the multiple power and ground buses. Furthermore, without the 23Less Green Technology, the electronic components cannot be integrated to be chips that the electronic components cannot be embedded in the frame of window. It makes the window having no clear view.

#### Objects and Advantages

[0054] The next generation smart home has the green energy management, communication multimedia and remote internet control for home. The smart window is the core technology of the smart home and smart grid. The Green Energy Smart Window of W5RS has the communication and multimedia capabilities of phone, internet and TV services. Even for the WPC Qi and A4WP wireless power supply standards, the novel single stage 5R can have the AC/DC power efficiency as high as 95% which is the highest record in the world. "5S" represents "Smart Solar Supply Silicon System". "W5" represents "Wireless Wireline Weave Wishful Window". "5R" represents "Recycling Resonant Resynchronization Rectifying Regulator". "W5RS" is the killer application product of Silicon Valley and "5R" is the killer core IP technology of Silicon Valley. Using the noise isolation technology to build up the platform to integrate all the FPGA and ASIC together to be FPSOC, the Green Energy Smart Window provides the complete set solution for smart home. It saves all the world energy consumption by more than half. Furthermore, the system integration of the transparent multimedia panel, electrochromic panel, transparent solar panel and the FPSOC makes the smart window having the clean outlook and clear view as the conventional IGU Insulated Glass Unit does.

### BRIEF DESCRIPTION OF THE FIGURES

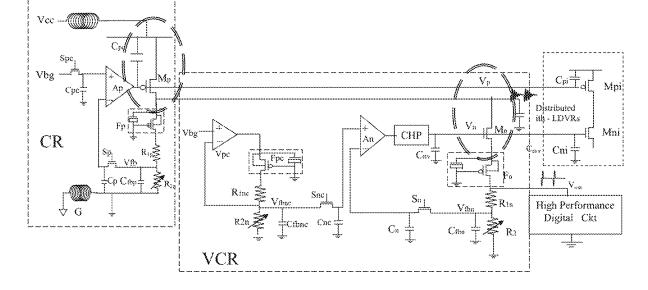

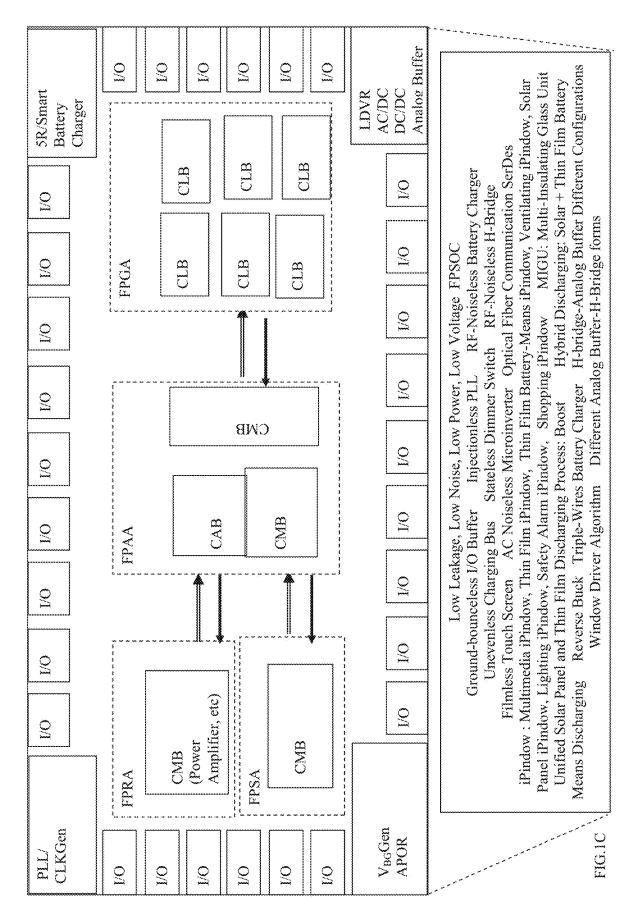

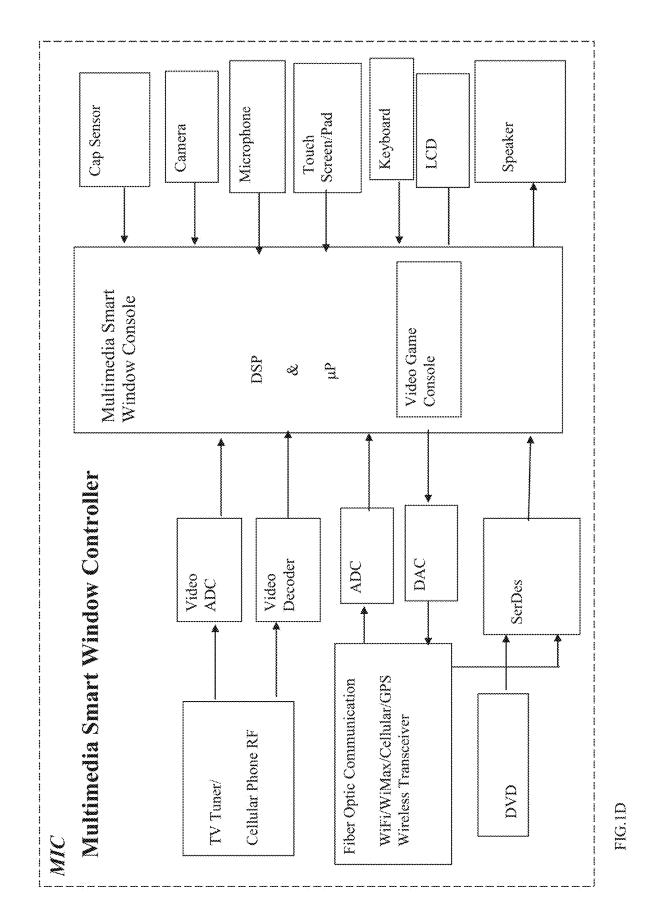

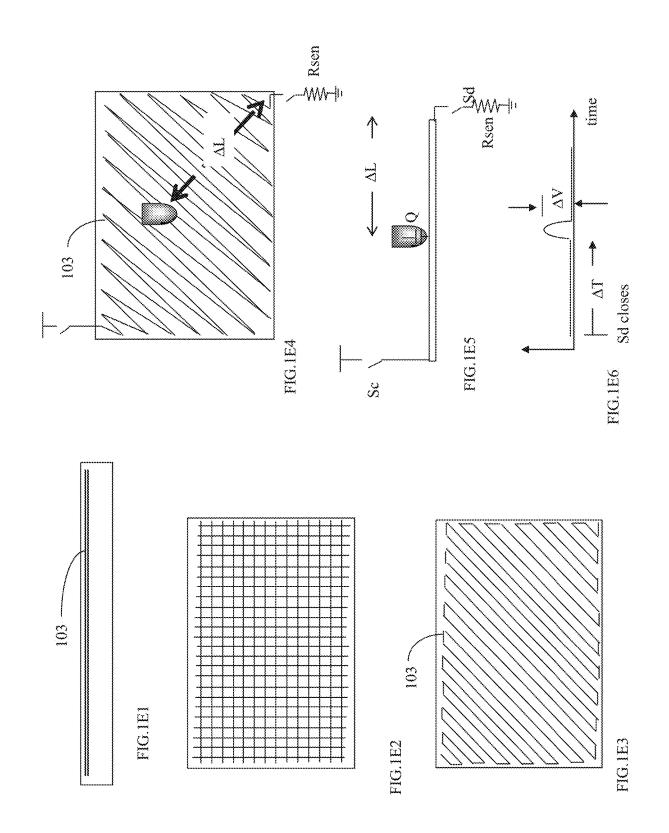

[0055] FIG. 1A1 is the overall system of the Green Energy Smart Window for the Smart Home; it includes the transparent multimedia panel such as LCD/LED/OLED/TV Flat panel and/or electrochromatic panel, the transparent solar cell panel, ventilation, smart fan controller, humidity controller, transparent touch screen, touchless screen, battery, thin-film battery, wireless communication, wireless power supply, SerDes, fiber optic communication, smart fan, EC window and dimmer light, etc.; all the transparent multimedia panel, electrochromic panel and solar panel have the whole window size. FIG. 1A2 is the overall system of the Green Energy Smart Window having multiple glass or plastic support panels for the transparent multimedia panel such as LCD/LED/OLED/TV Flat panel, electrochromatic panel and transparent solar cell panel to be a smart window. FIG. 1A3 the MS type master smart window is constituted of the transparent multimedia panel and transparent solar panel; both the transparent multimedia panel and the solar panel have the full window size; the air circulation is embedded in the frame of window. FIG. 1A4 the ES type slave smart window is constituted of the electrochromic panel and the transparent solar panel; both the electrochromic panel and the transparent solar panel have the full window size; the air circulation is embedded in the frame of window. FIG. 1A5 the MES type master smart window is constituted of the transparent multimedia panel, electrochromic panel and the transparent solar panel; the transparent multimedia panel, electrochromic panel and the transparent solar panel have the full window size; the air circulation is embedded in the frame of window. FIG. 1A6 is one illustrating example of the smart home implemented with the system made of smart windows. FIG. 1B is the architecture of the Smart Window of Smart Home. FIG. 1C is the Field System On Chip FPSOC for the Smart Window of Smart Home; the FPSOC includes sub-modules listed at the bottom. FIG. 1D is the system and architecture of the multi4

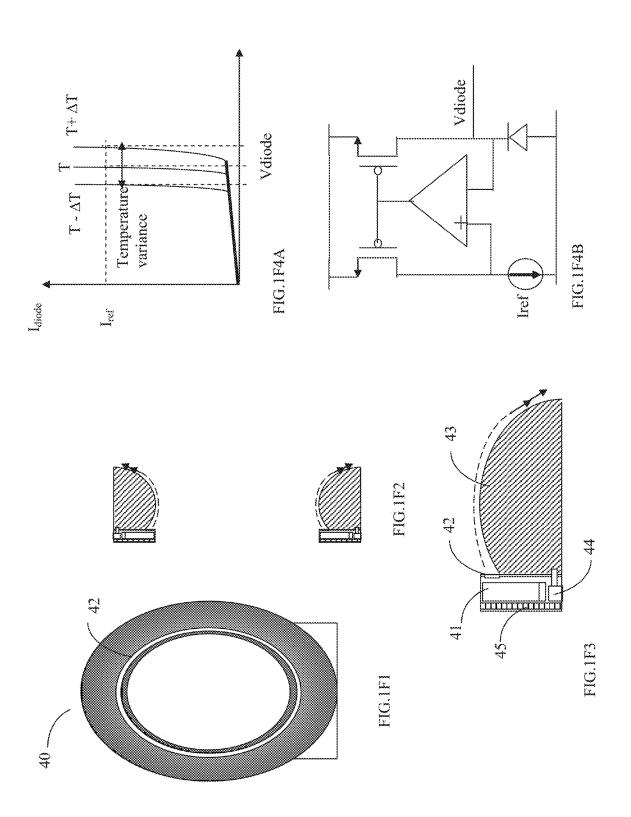

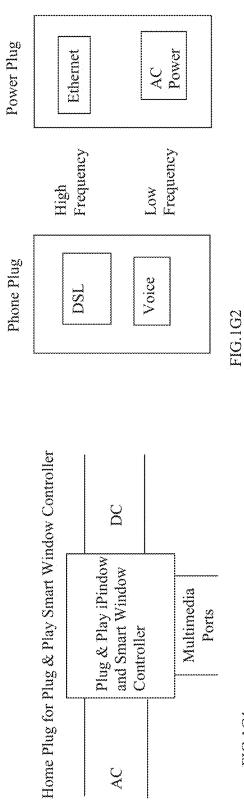

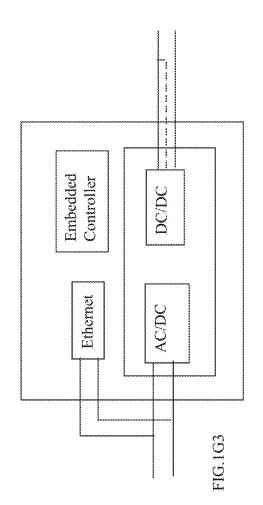

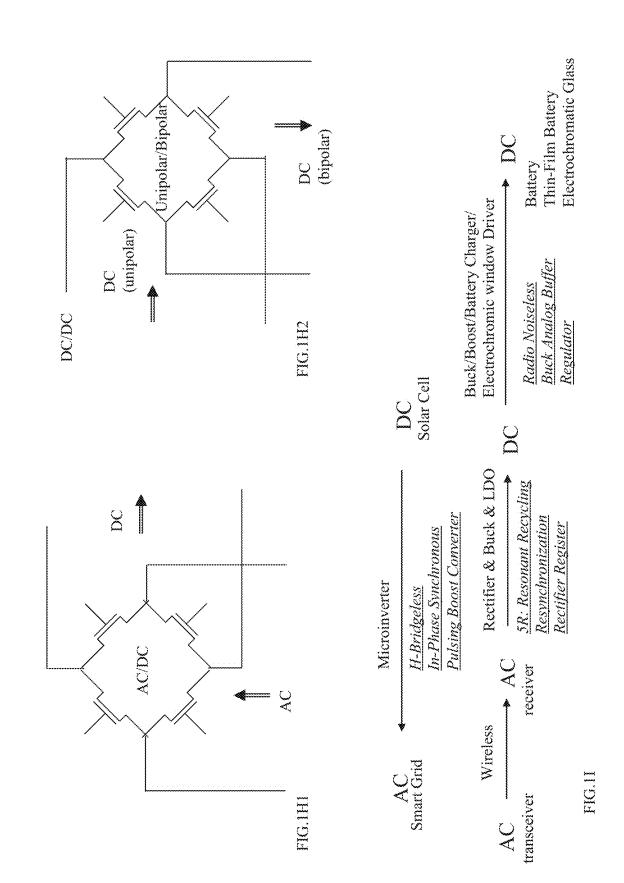

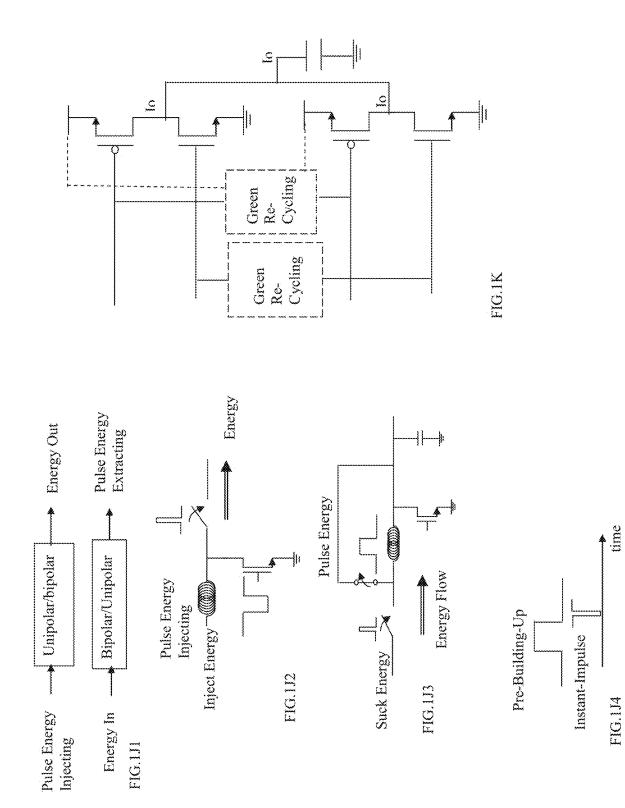

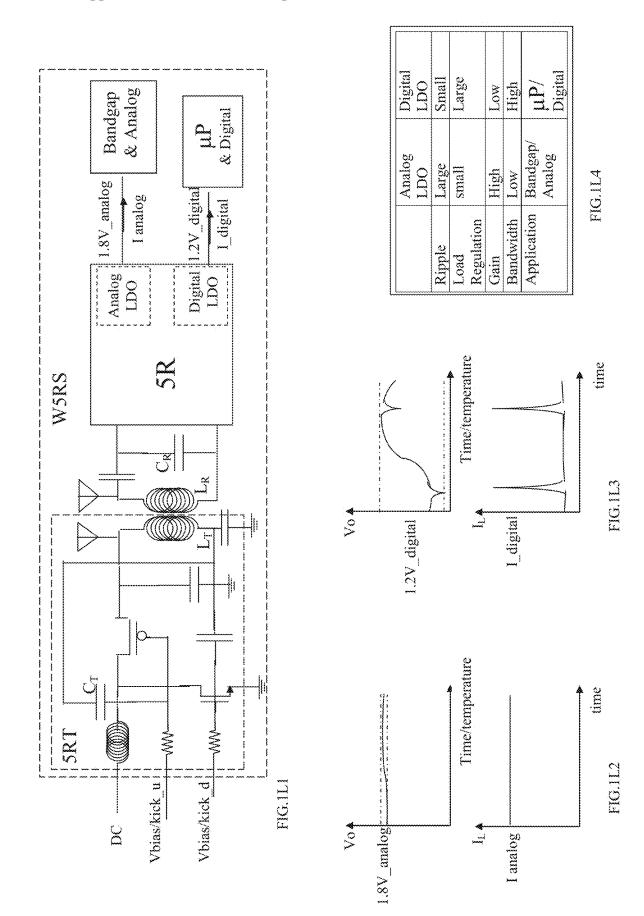

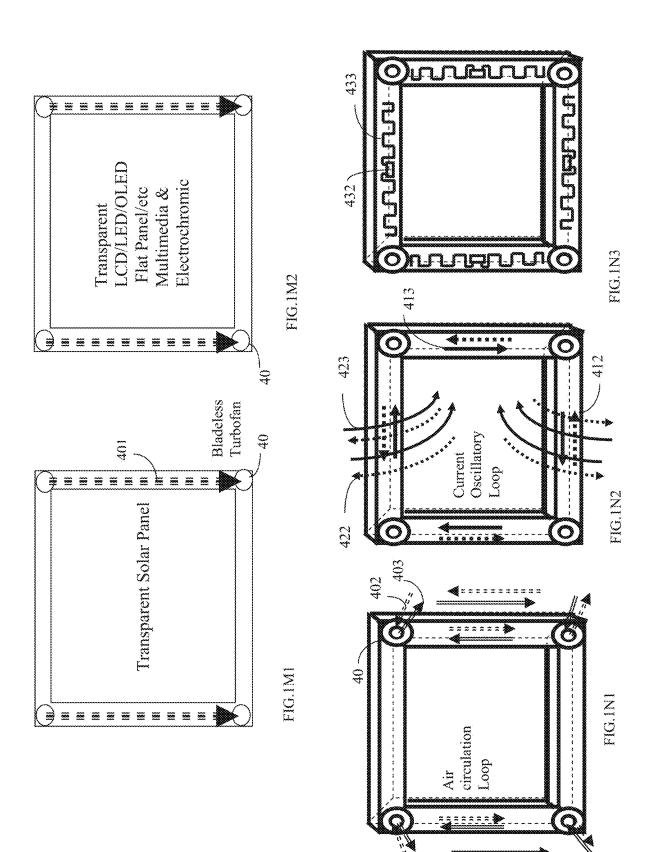

media Smart Window Controller of Smart Home. FIG. 1E1 is the cross-section of the transparent touch-screen; FIG. 1E2 is the top-view of the conventional transparent touchscreen. FIG. 1E3 is the top-view of the filmless touchscreen. FIG. 1E4 is the touch on the top of the filmless touch-screen. FIG. 1E5 is the equivalent circuit of the touch on the top of the filmless touch-screen. FIG. 1E6 is the pulsing wave propagating in the conducting layer of the filmless touch screen. FIG. 1F1 is the smart fan having for the Smart Window of Smart Home. FIG. 1F2 is the section view of the smart fan embedded in the smart window. FIG. 1F3 is the working principle of the bladeless turbofan. FIG. 1F4A is the diode characteristic curves over temperature. FIG. 1F4B is the temperature sensor circuit to measure the on-chip temperature for the smart ventilation window, etc. FIG. 1G1 is the smart plug made of the FPSOC. FIG. 1G2 is the analogy between the phone plug and power plug. FIG. 1G3 is the combinatory Phone Plug and Power Plug made of the FPSOC is the Unipolar-DC/Bipolar-DC conversion of the battery charger and window driver, etc. with H-bridge. FIG. 1H1 is the AC/DC conversion of the rectifier and micro-inverter, etc. with the H-bridge. FIG. 1H2 the bladeless turbofan and humidity/de-humidity/filter air-conditional multi-function. FIG. 1I is the global view of the power conversions among different power resources. FIG. 1J1 is the block diagram of the H-Bridgeless power conversion. FIG. 1J2 is the circuit of H-Bridgeless power conversion injecting the power. FIG. 1J3 is the circuit of H-Bridgeless power conversion extracting the power. FIG. 1J4 is the timing diagram for the triggering action of the H-Bridgeless power conversion. FIG. 1K is an illustrated example to show the fundamental working principal of power re-cycling between the huge SMPS output switches; it is to reduce the power switch loss especially in high-frequency switching operation. FIG. 1L1 is the W5RS Window 5R System using the Wireless 5R Recycling Resonant Resynchronization Rectifier Regulator Supply, programmable LDOs of Analog LDO and Digital LDO. FIG. 1L2 is the waveforms of the Analog LDO for the power supply of bandgap circuit, etc. FIG. 1L3 is the waveform of the Digital LDO for the power supply of microprocessor, etc. FIG. 1L4 is the comparisons between Analog LDO and Digital LDO. FIG. 1M1 is the exterior view of the smart window. FIG. 1M2 is the interior view of the smart window. FIG. 1N1 is the air circulation loop of the smart window. FIG. 1N2 is the low frequency current oscillatory loop for the wireless charging. FIG. 1N3 is the antenna of the wireless charging for high frequency protocols such as POWiFi, Bluetooth BT and RFID, etc.

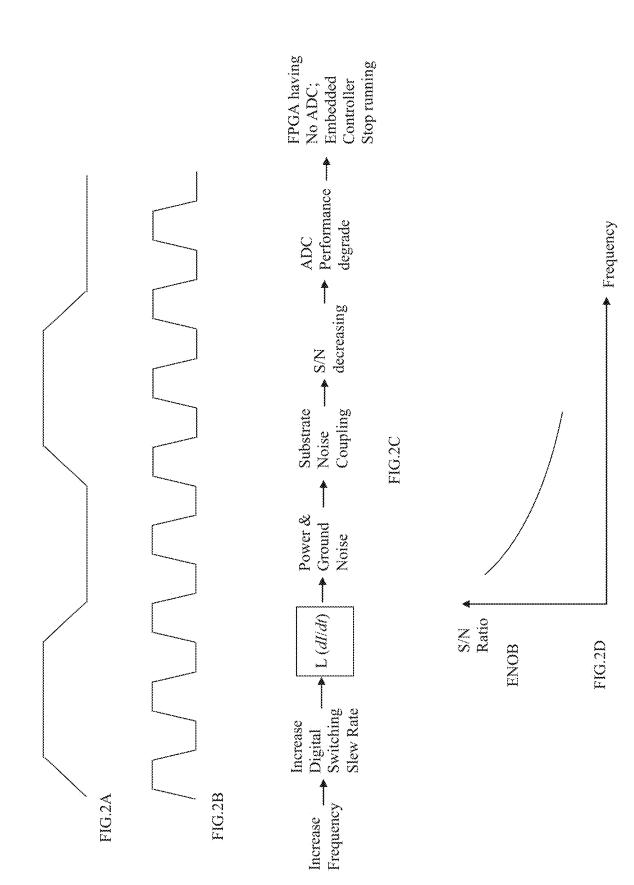

**[0056]** FIG. 2A is the low frequency clock/signal waveform. FIG. 2B is the high frequency clock/signal waveform. FIG. 2C is the chain reaction mechanism of frequency impacting on the system integration. FIG. 2D is the performance degrade as the function of the frequency for the Analog/ADC or RF/LNA circuit. It is the frequency impact on the Green Technology.

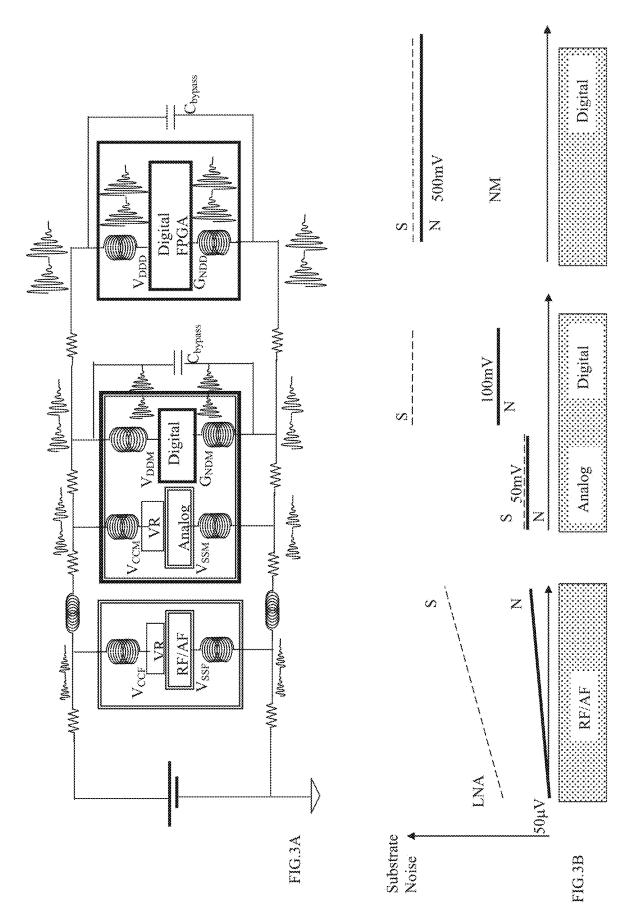

[0057] FIG. 3A is the partition of the system to be chips. FIG. 3B is the signal level and the substrate noise level of the chips. It is the conventional system.

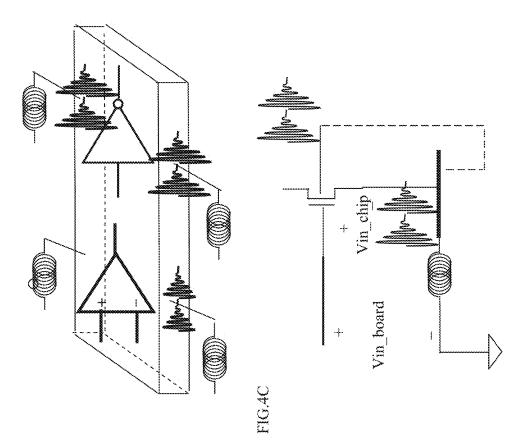

**[0058]** FIG. **4**A is the analog chip. FIG. **4**B is the digital chip having the substrate noise. FIG. **4**C is the substrate noise coupling in the integration of the analog chip and the digital chip. FIG. **4**D is the noise coupling mechanism of the substrate noise. It is the impact of the substrate noise coupling.

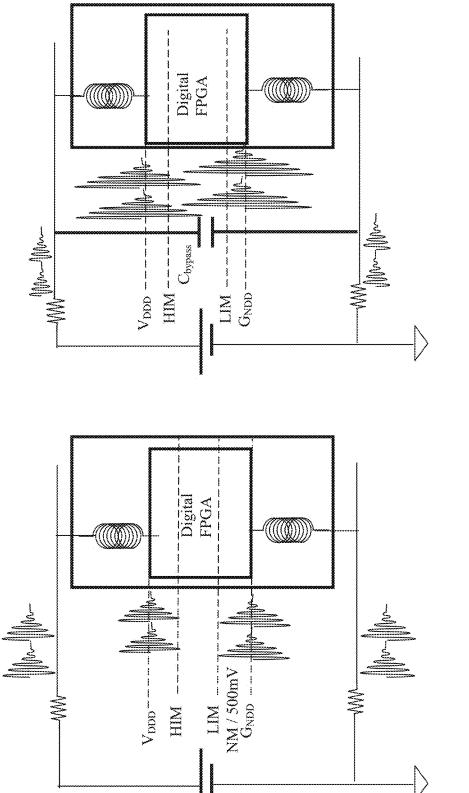

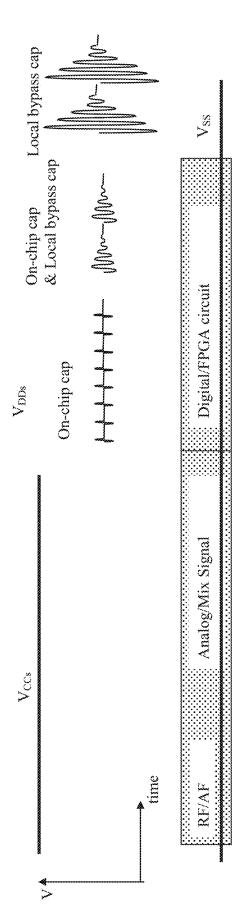

**[0059]** FIG. **5**A is the switching noise generated by the digital and/or FPGA chips. FIG. **5**B is the switch noise augmented by the decoupling capacitor. It is the conventional digital and FPGA switching noise.

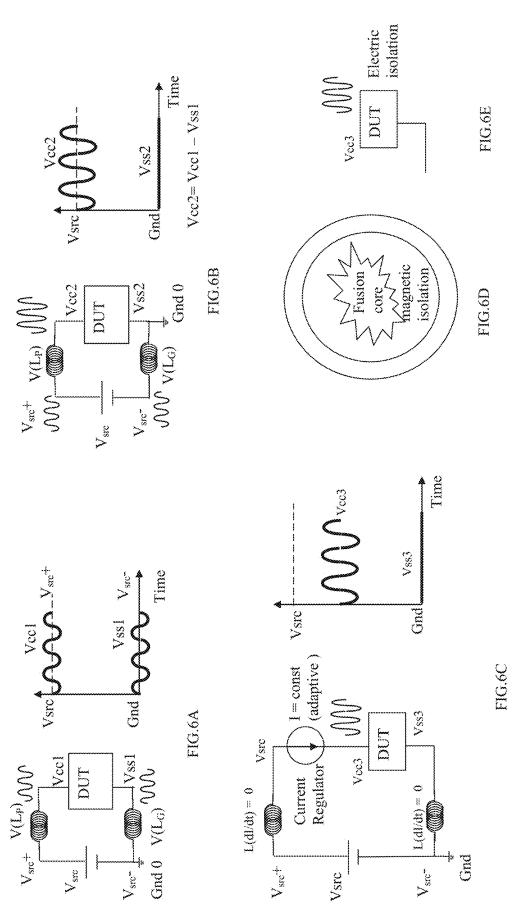

**[0060]** FIG. **6**A is the conventional digital chip having the ground node (0 node) set at the board. FIG. **6**B is the ground nodes (0 node) set at the substrate of the chip in the SPICE simulation. FIG. **6**C is the noise isolation having the ground node (0 node) set at the board.

**[0061]** FIG. **6**D is the analogy of the magnetic shield for the heat isolation in the fusion chamber. FIG. **6**E is the electric shield for the noise isolation in the planar chip. It is the introduction of the noise isolation technique.

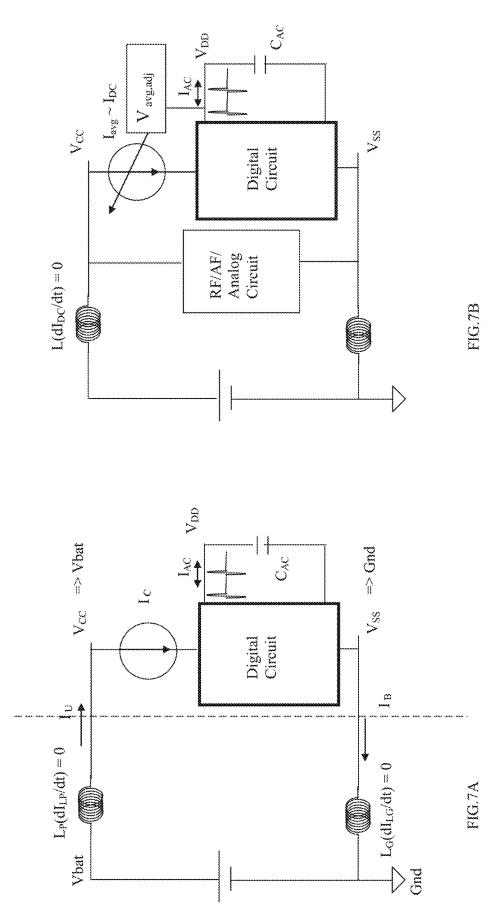

**[0062]** FIG. 7A is the noise isolation for the digital chip having the noiseless substrate; the Kirchhoff's Current Law (KCL) shows  $I_U=I_B$  that only one current regulator is needed. FIG. 7B the analog circuit can co-exist in the same chip having noiseless substrate. It is the fundamental pattern of the noise isolation technique.

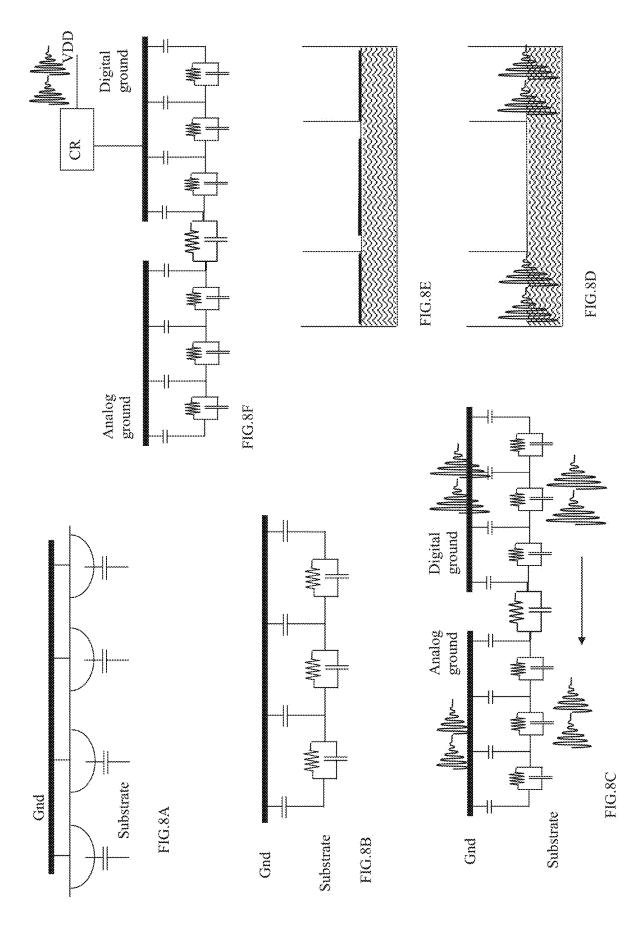

**[0063]** FIG. **8**A is the substrate. FIG. **8**B is the electric model for the substrate. FIG. **8**C is the noise coupling in substrate model with separate ground buses. FIG. **8**D is the hydraulic model for the noise coupling in substrate model with separate ground buses. FIG. **8**E is the hydraulic model for the noise isolation technique. FIG. **8**F is the electric model for the Noise Isolation Technology. It is the substrate model.

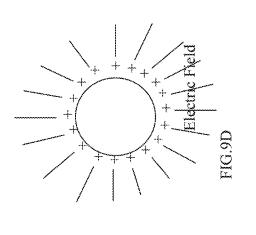

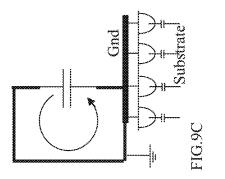

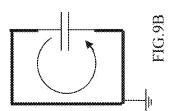

**[0064]** FIG. **9**A is the capacitor with the current loop of charging and discharging. FIG. **9**B is the capacitor with the current loop having the ground node for charging and discharging. FIG. **9**C is the capacitor with the current loop having the ground node and substrate for charging and discharging. FIG. **9**D is the Electric Field analogy of the Noise Isolation Technology. FIG. **9**E is the power and ground voltages in the system integration with the noise isolation technology. It is the analysis of the power and ground voltages in the noise-isolation technique; it proves that there is no substrate noise injected into the substrate.

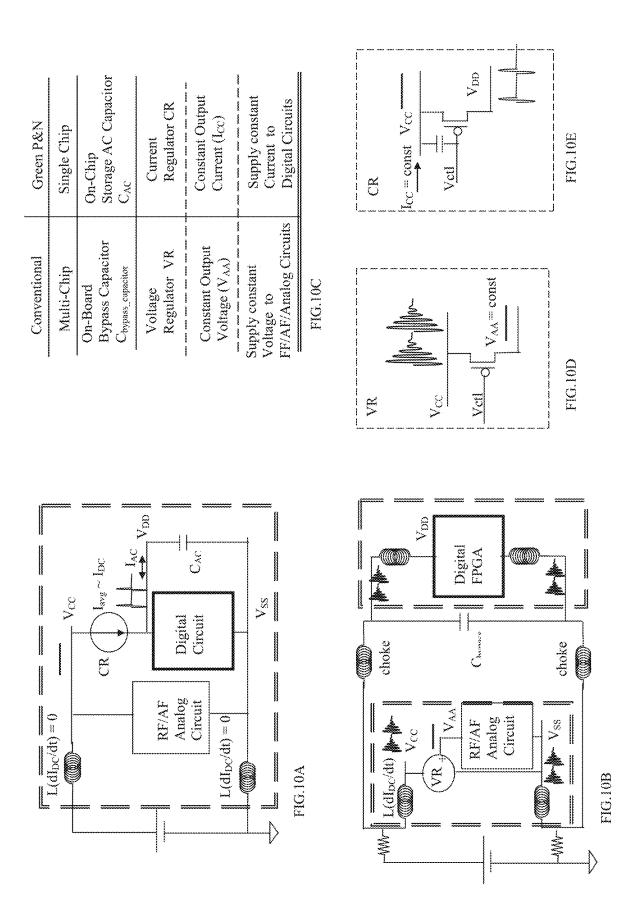

**[0065]** FIG. **10**A is the noise isolation technique with the current regulator. FIG. **10**B is the conventional analog chip using the voltage regulator to get rid of the power supply noise by the factor PSRR power supply rejection ratio. FIG. **10**C is the comparisons between the "current regulator of the noise isolation technique" and the "voltage regulator of the analog chip in the noisy board" environment. FIG. **10**D is the switching operation of the voltage regulator. FIG. **10**E is the switching operation of the current regulator. It is the comparisons between the "current regulator. It is the comparisons between the "current regulator noise isolation platform" and the "voltage regulator analog-digital multipower-bus platform".

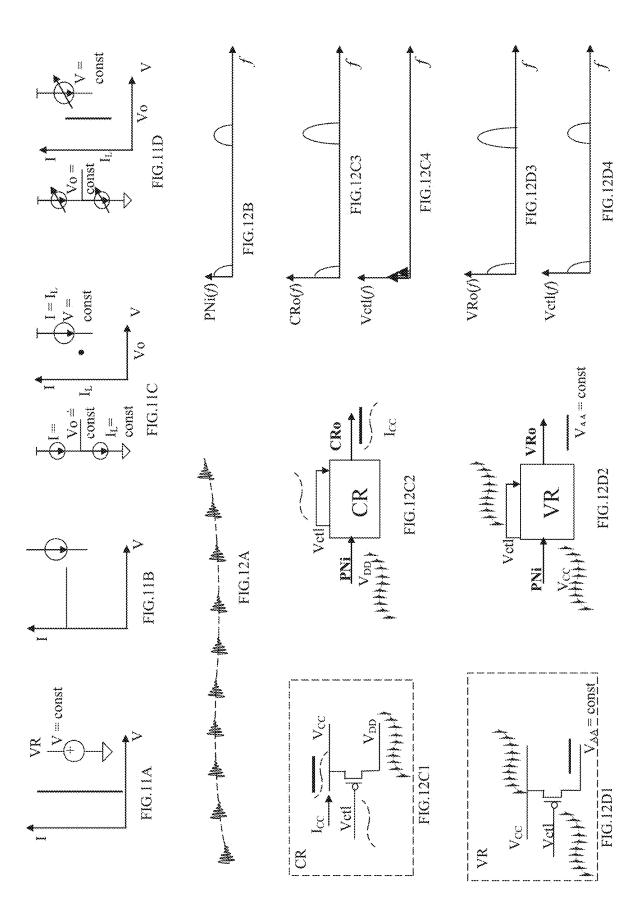

**[0066]** FIG. **11**A is the voltage source. FIG. **11**B is the current source. FIG. **11**C is the current source of the current regulator. FIG. **11**D is the adaptive current source of the current regulator. It is the comparison of voltage source and current source.

[0067] FIG. 12A is the digital switching noises in the power supply. FIG. 12B is the spectrum of the power supply having the digital switching noise. FIG. 12C1 is the waveforms of signals of current regulator. FIG. 12C2 is the block diagram of the current regulator. FIG. 12C3 is the input noise signal spectrum of the current regulator. FIG. 12C4 is the control signal spectrum of the current regulator. FIG. 12C4 is the signal waveform of voltage regulator. FIG. 12D2 is the block diagram of the voltage regulator. FIG. 12D2 is the block diagram of the voltage regulator. FIG. 12D2 is the block diagram of the voltage regulator. FIG. 12D2 is the block diagram of the voltage regulator. FIG. 12D2 is the block diagram of the voltage regulator. FIG. 12D2 is the block diagram of the voltage regulator. FIG. 12D2 is the block diagram of the voltage regulator. FIG. 12D2 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator. FIG. 12D3 is the block diagram of the voltage regulator.

**12D3** is the input noise signal spectrum of the voltage regulator. FIG. **12D4** is the control signal spectrum of the voltage regulator. It is the comparison of the current regulator and voltage regulator.

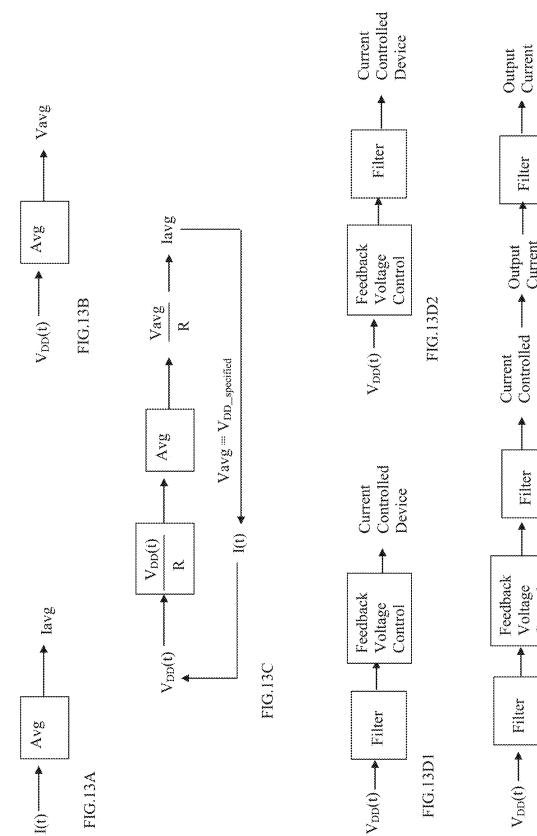

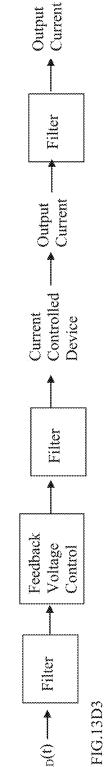

**[0068]** FIG. **13**A is the current average. FIG. **13**B is the voltage average. FIG. **13**C is the current average of the current regulator being implemented with the voltage average. FIG. **13D1** is the preferred implementation of the current regulator of which pre-filter serving as the average function. FIG. **13D2** is the alternative implementation of the current regulator of which post-filter serving as the average function. FIG. **13D3** is the cascading current regulator; it has the pre-filter and post-filter for the feedback signal; the filter is for the feed forward output current. It is the average current generator for the current regulator.

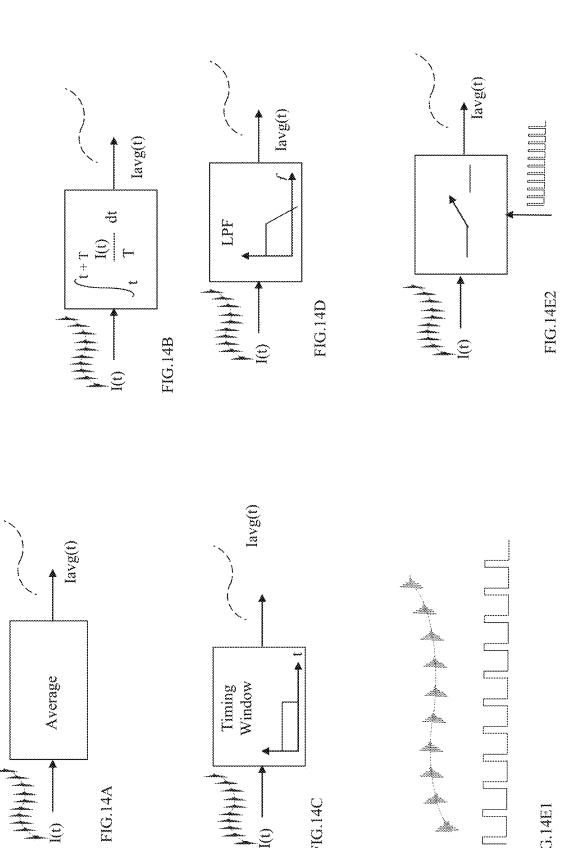

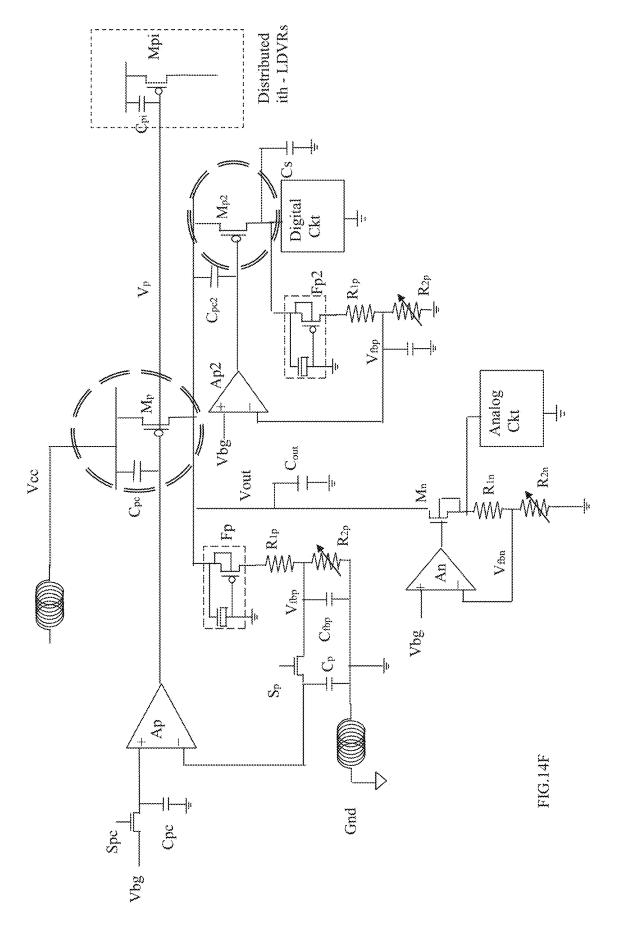

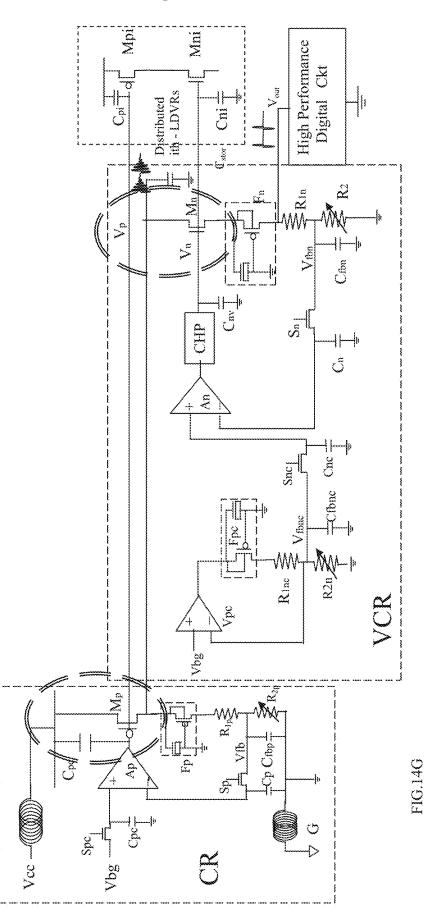

[0069] FIG. 14A is the block diagram of the average. FIG. 14B is the window function in the time domain to implement the average with the integration and divider. FIG. 14C is the timing window function to implement the average function. FIG. 14D is the low pass filter to implement the average function. FIG. 14E1 is the waveform of the digital switching noise. FIG. 14E2 is the sampling to implement the average function. FIG. 14F is the current regulator adopting the filter as shown in the FIG. 14D and the sampling as shown in FIG. 14E2 to get the average current for the P-P type cascading current regulator. FIG. 14G is the alterative implementation of the current regulator; it adopts the filter as shown in the FIG. 14D; the sampling is as shown in FIG. 14E2; it is to get the average current for the P-N type cascading current regulator. It is noted that the current regulator having the filter Fp and Fn; the voltage regulator doesn't have a filter. It is the different ways to implement the average function.

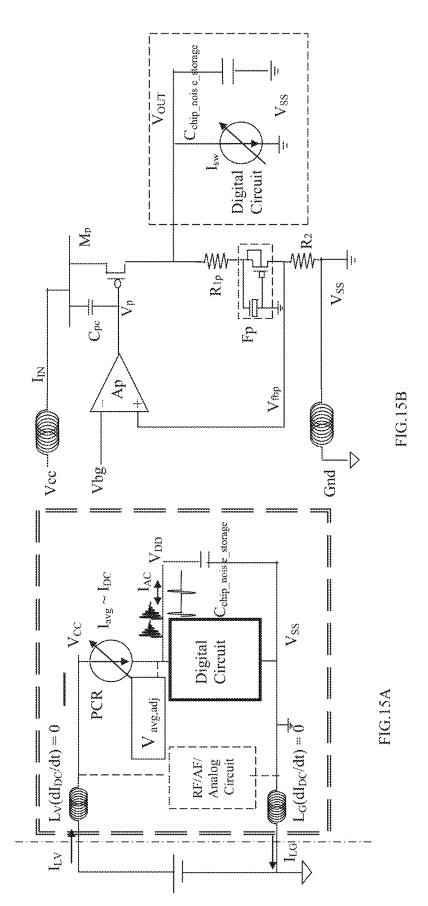

**[0070]** FIG. **15**A is the architecture of the current regulator. FIG. **15**B is the circuit and system of the current regulator. It is the fundamental current regulator.

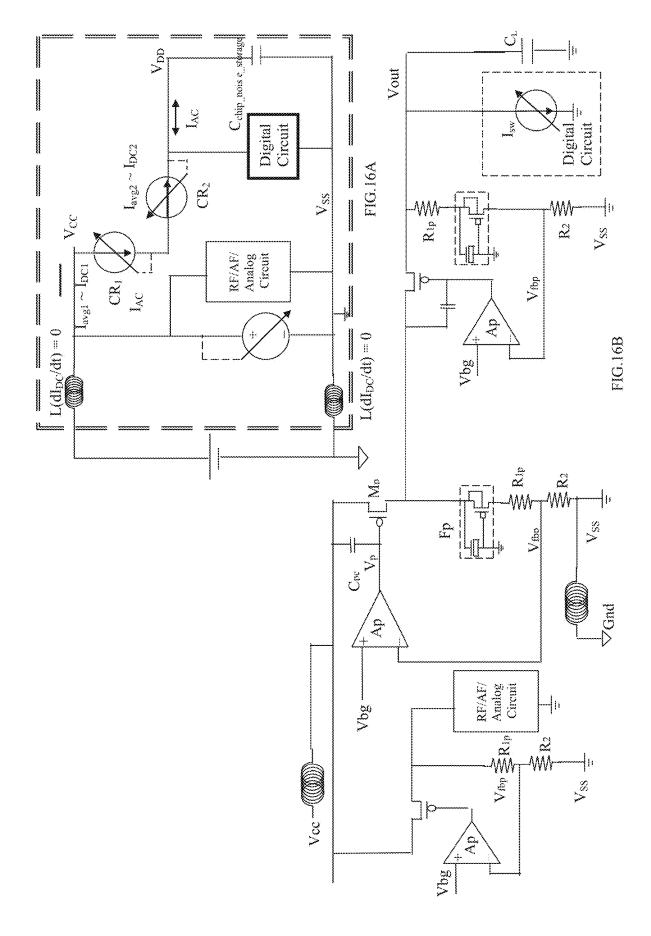

**[0071]** FIG. **16**A is the architecture having the current regulator and voltage regulator. FIG. **16**B is the circuit and system having the current regulator and voltage regulator. The current regulator is for the digital circuit or whole chip; the voltage regulator is for the analog or RF circuit.

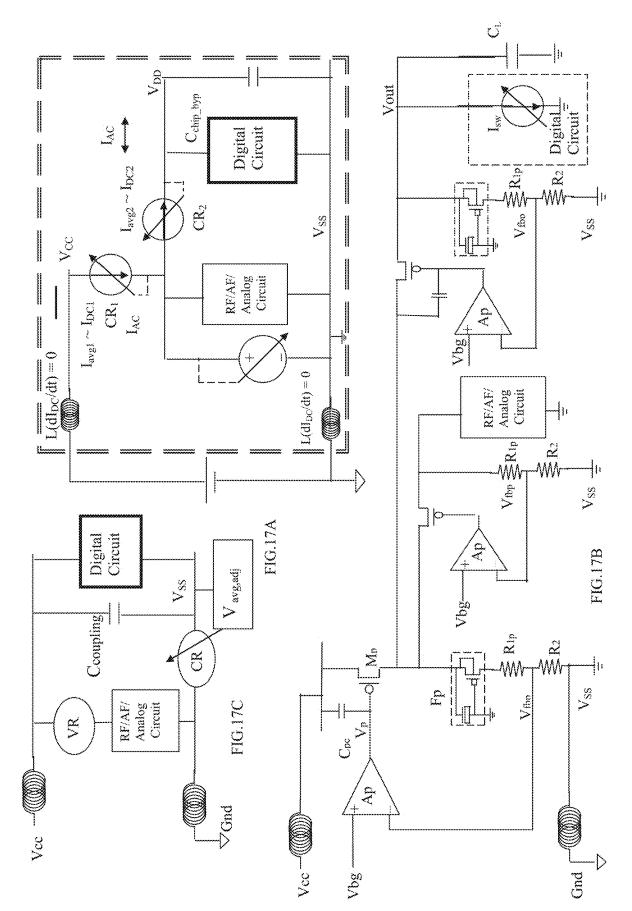

**[0072]** FIG. **17**A is the architecture of the cascade current regulator and voltage regulator. FIG. **17**B is the circuit of the cascade current regulator and voltage regulator. FIG. **17**C is the architecture for the current regulator being at the ground side of the digital circuit, the voltage regulator being for the AF/RF circuit and the big coupling capacitor having the connection between the power line and ground line of the digital circuit or whole chip; the voltage regulator is for the analog or RF circuit.

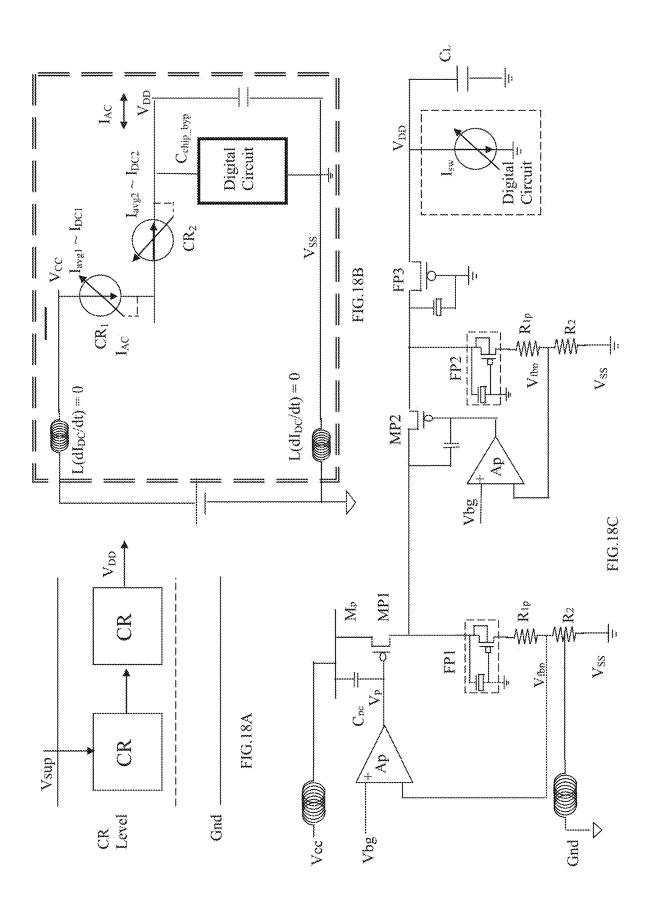

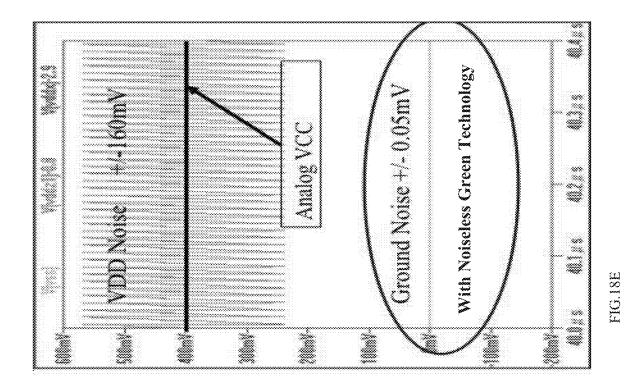

[0073] FIG. 18A is the system block diagram of the cascade current regulator. FIG. 18B is the architecture of the cascade current regulator. FIG. 18C is the circuit of the cascade current regulator. FIG. 18D is the simulation of power and ground curves of the conventional Power and Ground plan. FIG. 18E is the simulation of power and ground curves of the Noise Isolation Technology. It is the cascade current regulator for the digital circuit or whole chip.

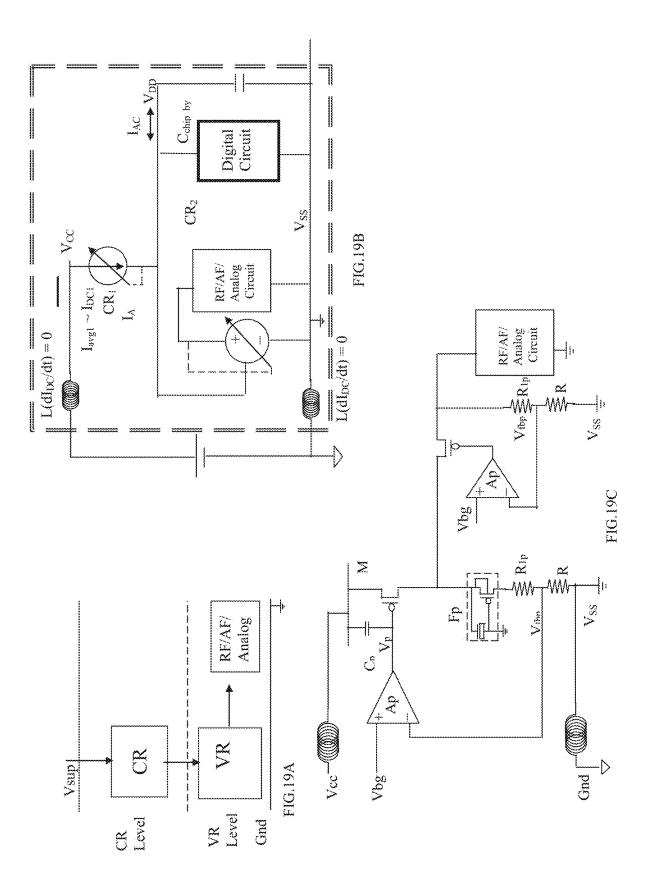

**[0074]** FIG. **19**A is the system of the cascade current regulator and voltage regulator. FIG. **19**B is the architecture of the cascade current regulator and voltage regulator. FIG.

**19**C is the circuit of the cascade current regulator and voltage regulator. It is the cascade of current regulator and voltage regulator.

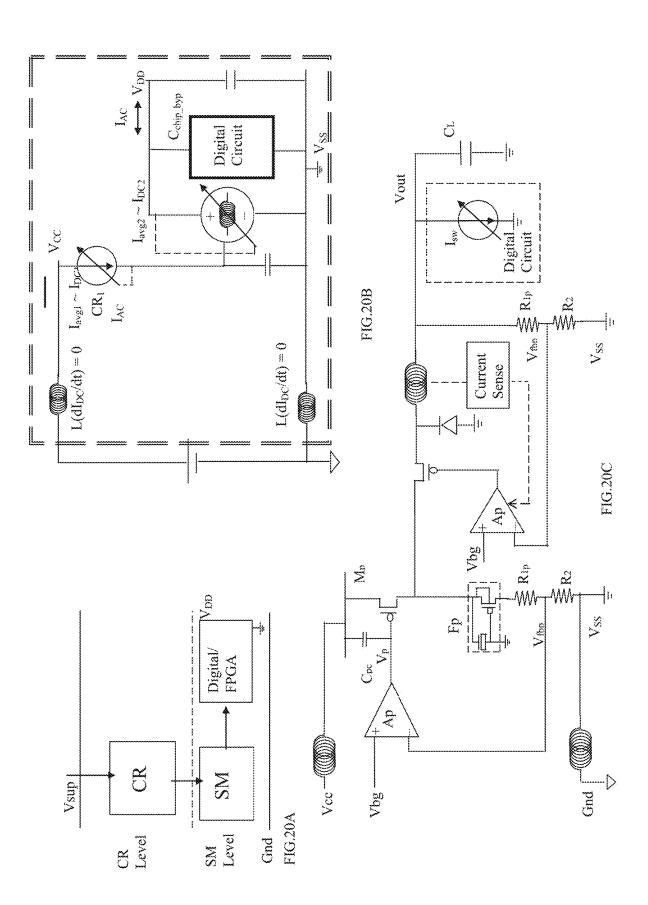

**[0075]** FIG. **20**A is the system of the cascade of the current regulator and switch mode power supply. FIG. **20**B is the architecture of the cascade current regulator and switch mode power supply. FIG. **20**C is the circuit of the cascade current regulator and the switch mode power supply. It is the cascade of the current regulator and switch mode power supply.

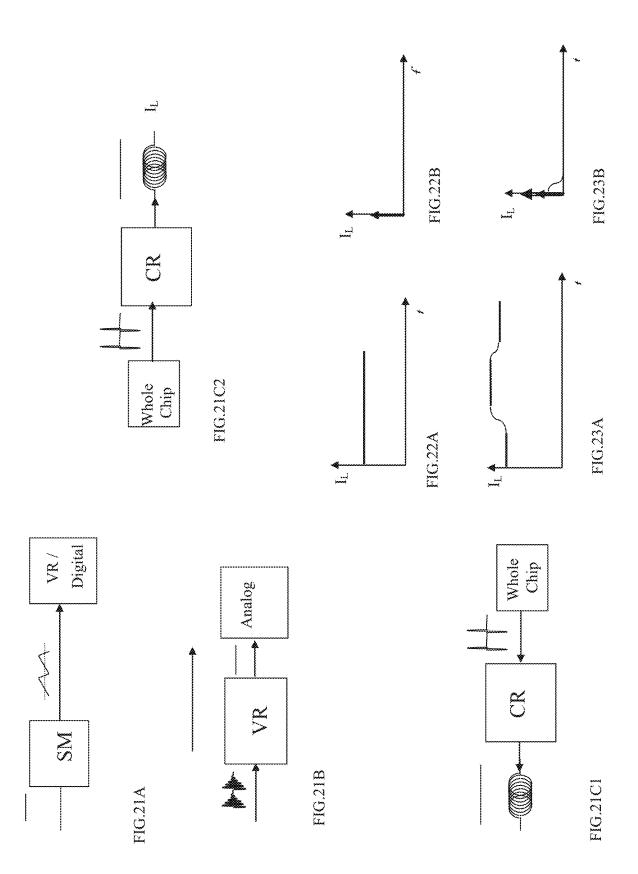

**[0076]** FIG. **21**A is the switch mode power supply for the digital circuit or voltage regulator. FIG. **21**B is the voltage regulator power for the analog circuit or RF circuit. FIG. **21**C1 is the signal flow block diagram of the current regulator; the signal flowing direction is in the reverse direction of the voltage regulator. FIG. **21**C2 is the signal flow block diagram of the current regulator; the signal flow is in the normal left-to-right direction. It is the comparison of the conventional power supply with the current regulator power supply.

[0077] FIG. 22A is the current regulator having the constant current; FIG. 22B is the spectrum of the current regulator having the constant current. It is the current regulator.

**[0078]** FIG. **23**A is the current regulator having the slow varying current. FIG. **23**B is the spectrum of the current regulator having the slow varying current. It is the slow varying current regulator.

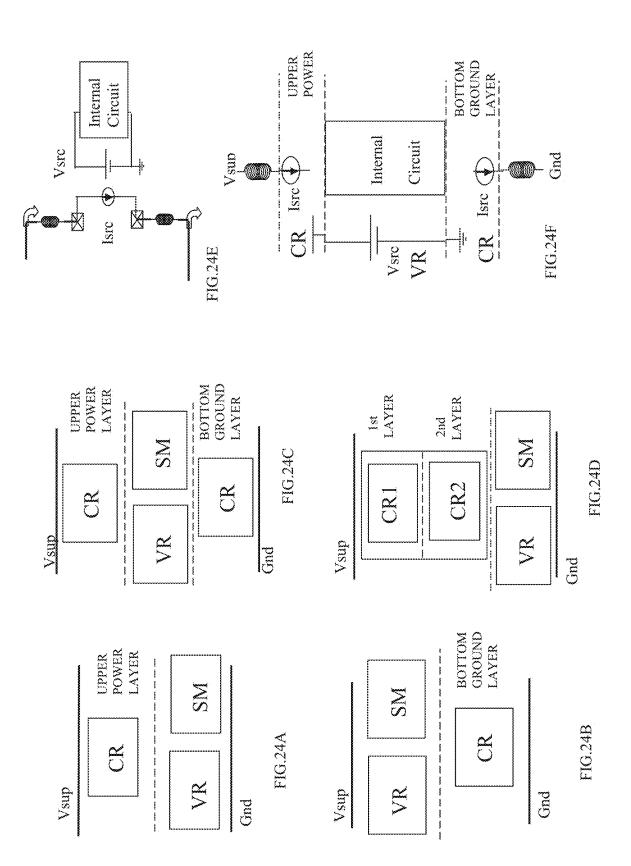

[0079] FIG. 24A is the current regulator located at the upper power layer. FIG. 24B is the current regulator located at the lower power layer. FIG. 24C is the multi-current regulator located at the upper and lower power layer. FIG. 24D is the hierarchical view of the multi-current regulator. FIG. 24E is the circuit model for the current regulator, it generates the voltage source for the digital circuit, etc. FIG. 24F is the general platform of the multiple current sources. It is the the versatile arrangements of the on-chip multipower supplies.

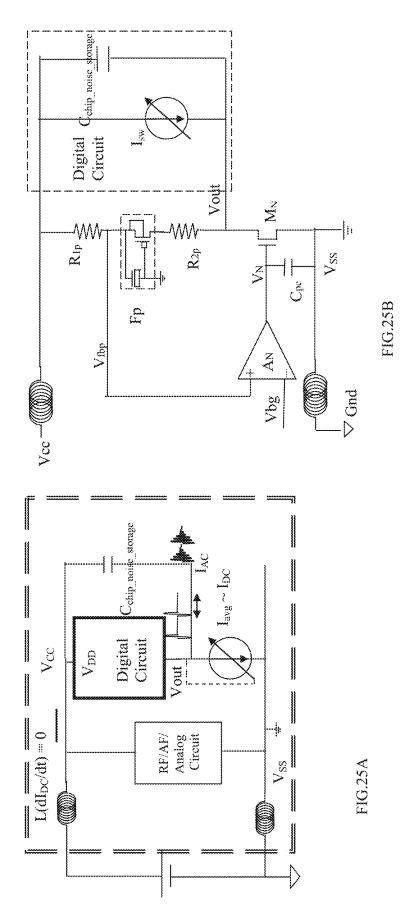

**[0080]** FIG. **25**A is the architecture of the N-type current regulator. FIG. **25**B is the circuit and system of the N-type current regulator. It is the N-type fundamental current regulator; it is shown by the CR in bottom ground layer in FIG. **24**B.

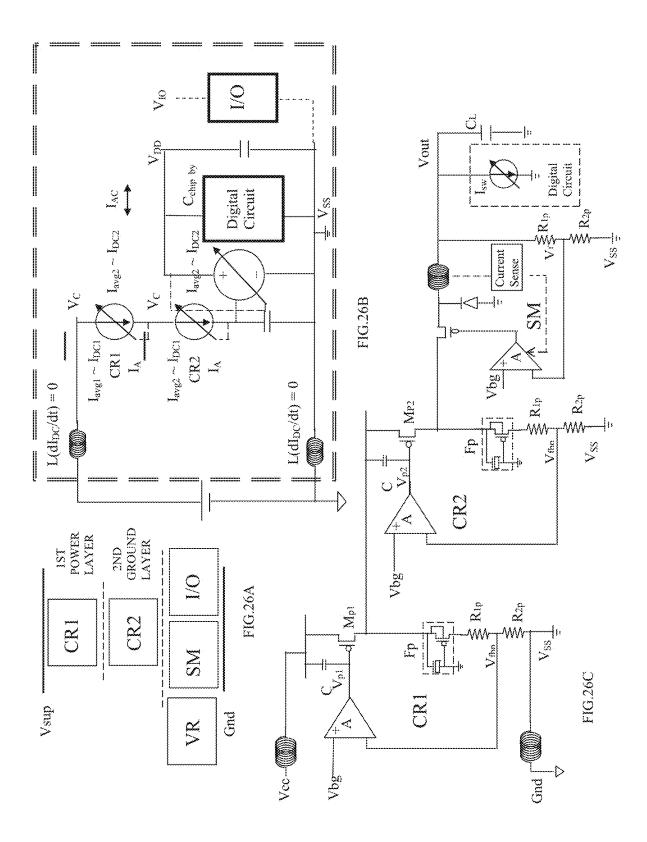

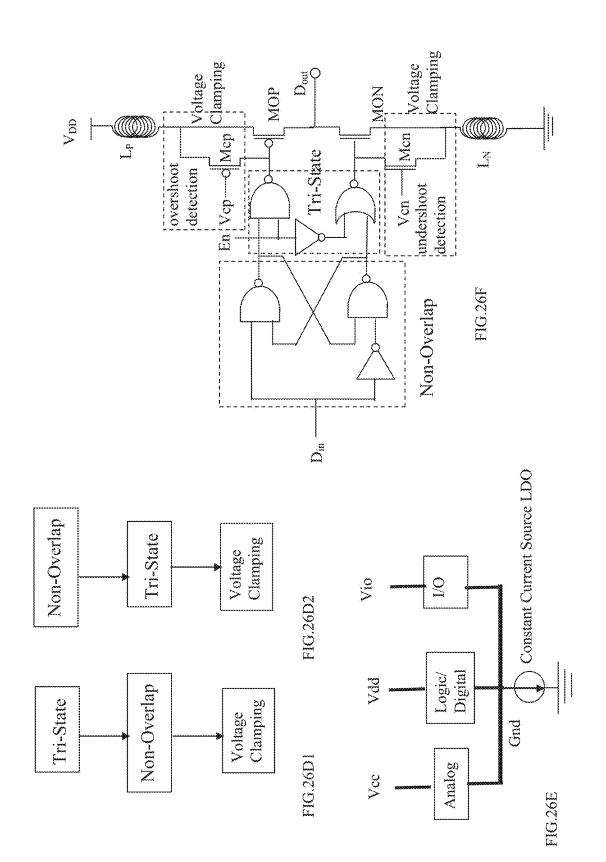

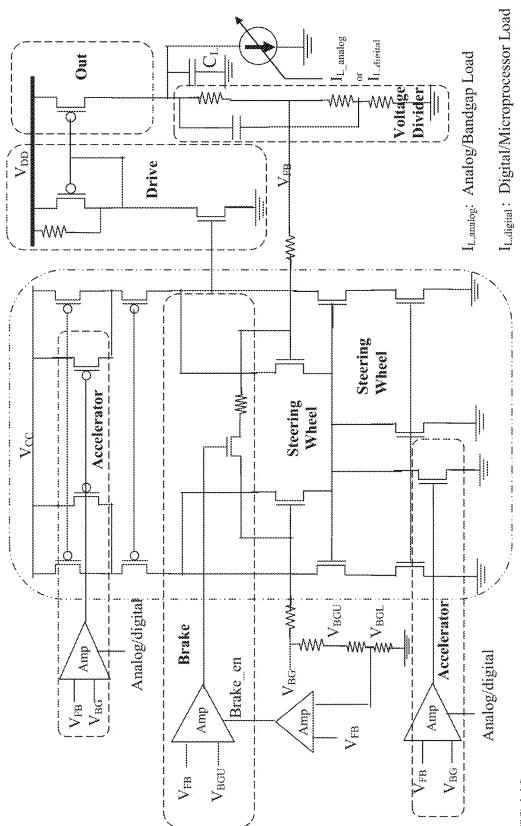

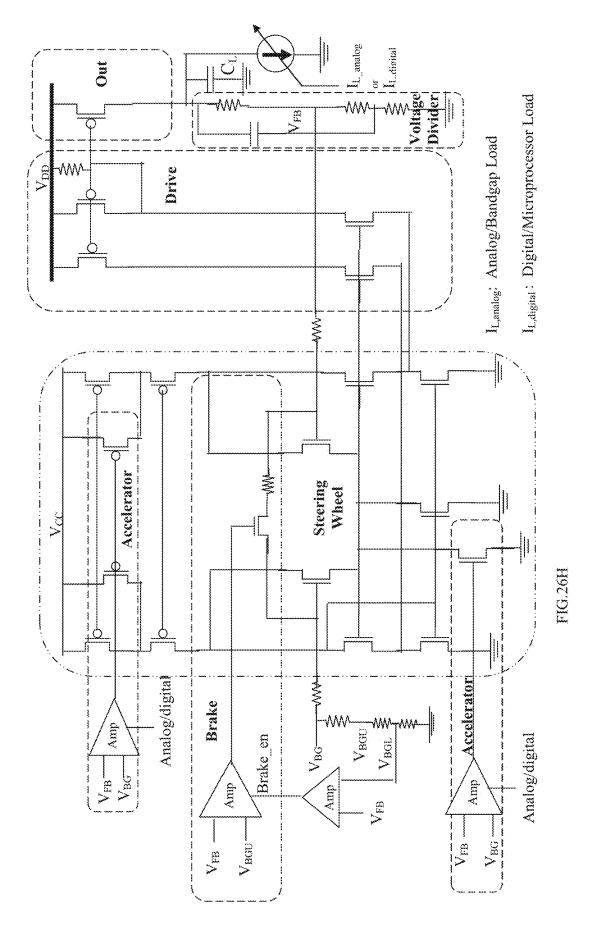

[0081] FIG. 26A is the system block diagram of the cascade current regulator or the hierarchical current regulator. FIG. 26B is the architecture of the cascade current regulator or the hierarchical current regulator. FIG. 26C is the circuit of the cascade current regulator or the hierarchical current regulator. FIG. 26D1 is the design hierarchy as shown in conventional I/O. FIG. 26D2 is the design hierarchy as shown in ground-bounceless I/O. FIG. 26E is the substrate-noiseless Power and Ground P&G-Plane. FIG. **26**F is the ground-bounceless I/O. FIG. **26**G is the analog/ digital Programmable LDO having the Brake. Accelerating and steering wheel functions. FIG. 26H is the alternative design of the analog/digital Programmable LDO with transimpedance cascade Amplifier. It is the cascade current regulator or the hierarchical current regulator shown in FIG. 24D.

**[0082]** FIG. **27**A is the general current regulator noise isolation platform. FIG. **27**B is the conventional mixed signal chip. FIG. **27**C is the CR wrapper of the current regulator noise isolation platform for the conventional mixed signal chip.

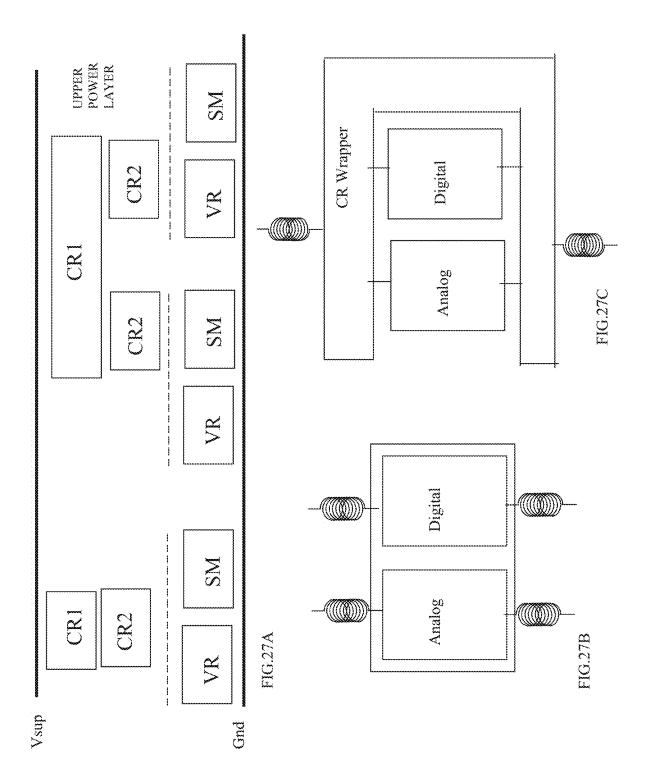

**[0083]** FIG. **28**A is the partition of the chips. FIG. **28**B is the A/D waveform of the A/D ADC or D/A DAC. FIG. **28**C is the SIP waveform of the Series to Parallel S/P or Parallel to Series P/S in SERDES. It is the conventional system integration.

**[0084]** FIG. **29**A is the chip partition with the system integration of the A/D, SIP with FPGA, DSP and Embedded Controller, etc. FIG. **29**B is the platform of the system integration of the AID, SIP with FPGA, DSP and Embedded Controller, etc. It is the system integration of the AID, SIP with FPGA, DSP and Embedded Controller, etc.

**[0085]** FIG. **30**A is the system integration of all the RF, AF, AID with FPGA, DSP and Embedded Controller, etc. FIG. **30**B is the platform of the system integration of all the RF, AF, AID, SIP with FPGA, DSP and Embedded Controller, etc. It is the system integration of all the RF, AF, AID with FPGA. DSP and Embedded Controller, etc.

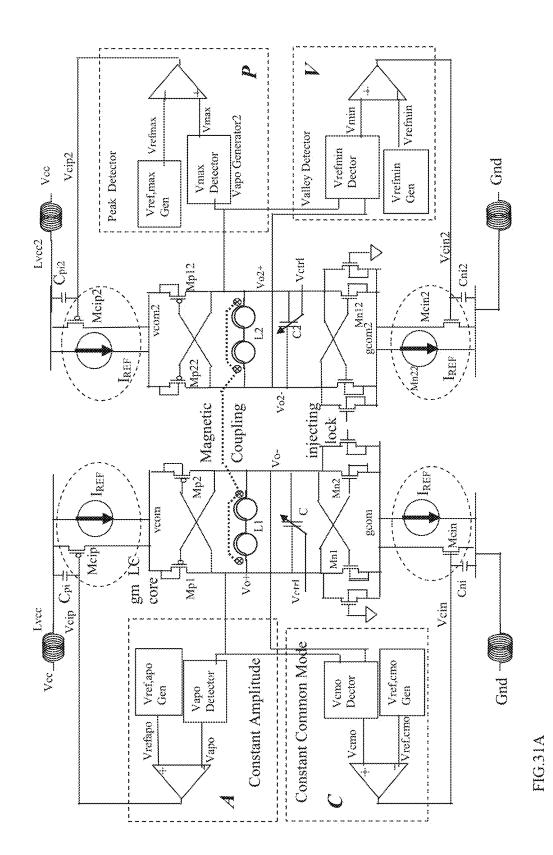

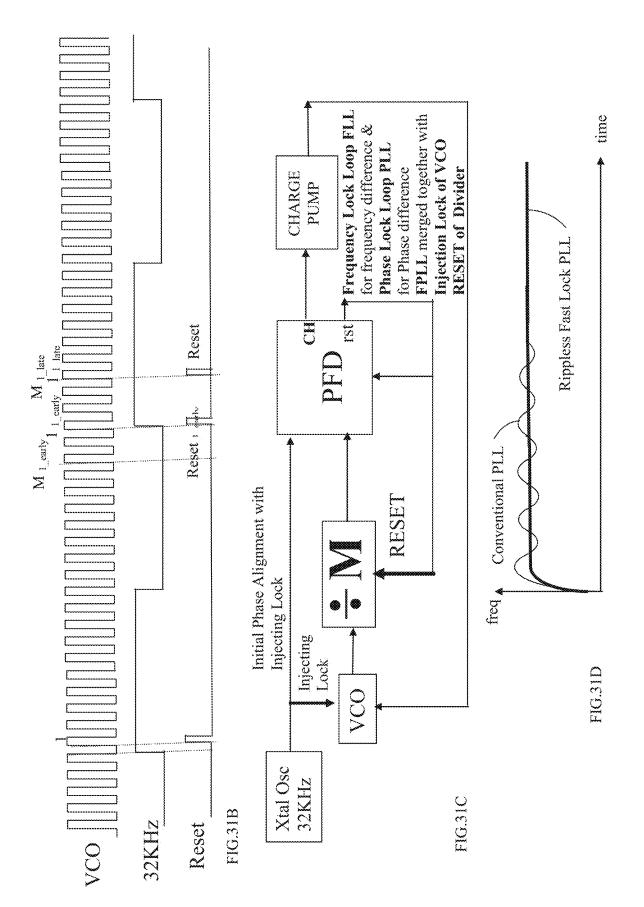

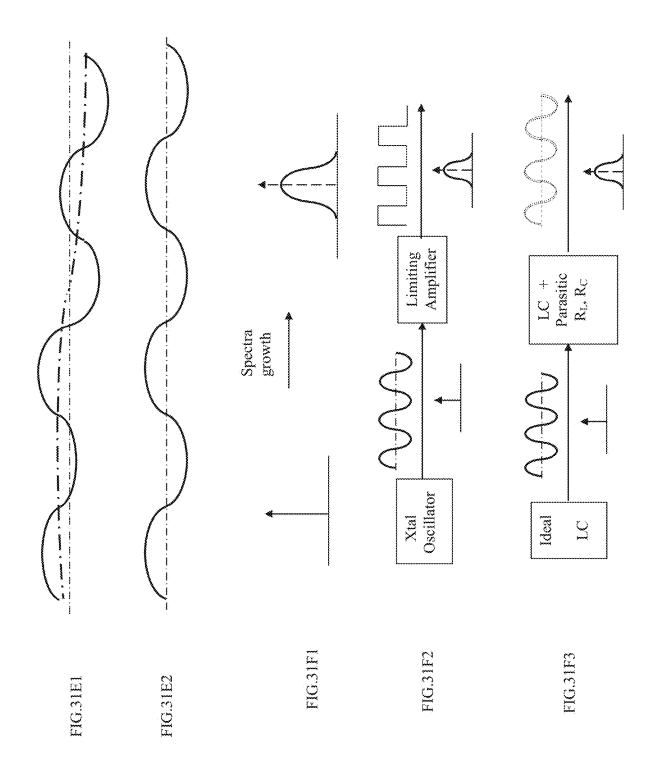

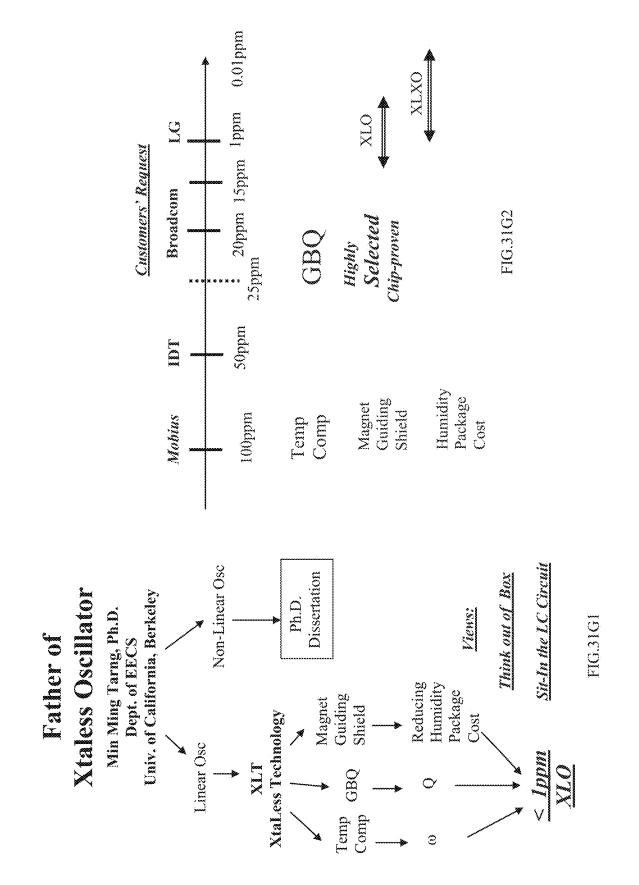

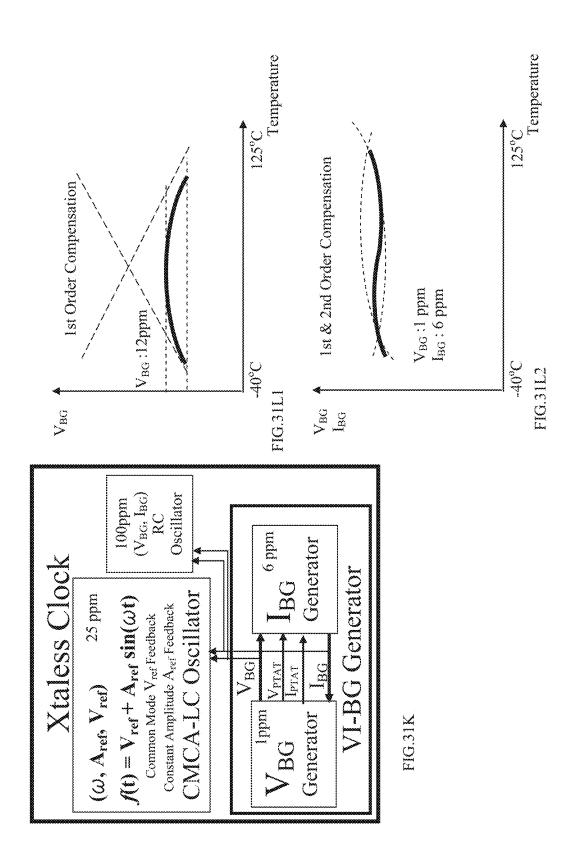

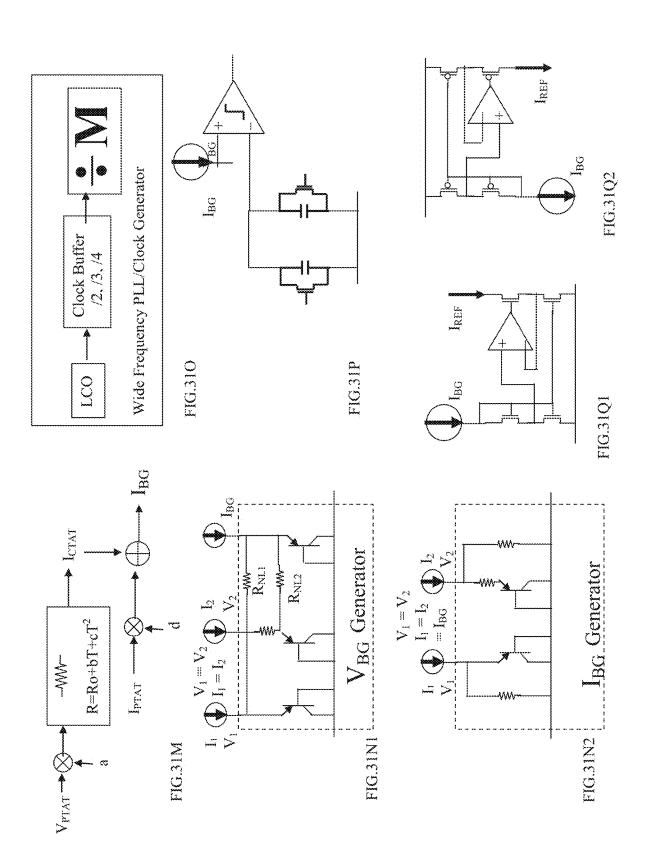

[0086] FIG. 31A is the Xtaless Clock circuit with the embedded Noise Isolation Technology: the embedded Noise Isolation Technology is implemented as shown in FIG. 30A. FIG. 31B the timing diagram of the Rippleless Fast lock FPLL. FIG. 31C is the block diagram of the Rippleless Fast lock FPLL. FIG. 31D is the comparison between the conventional PLL and the Rippleless Fast lock FPLL. FIG. 31E1 is the wandering of oscillatory wave. FIG. 31E2 is the normal oscillatory wave. FIG. 31F1 is the spectra growth of ideal oscillatory wave. FIG. 31F2 is the spectra growth of the square wave. FIG. 31F3 is the spectra growth due to the parametric inductance and capacitance. FIG. 31G1 is the historical review of Xtaless Clock theory. FIG. 31G2 is the route map of the Xtaless Clock development. FIG. 31H is the magnetic enhanced transimpedance amplifier TIA of the optical SerDes as shown in FIG. 1A. FIG. 31I is the schematic symbol of the magnetic enhanced transformer type inductors. FIG. 31J is the 3-dimensional view of the magnetic enhanced transformer type inductors. FIG. 31K is the architecture and system of the Xtaless Clock having Bandgap Generator. FIG. 31L1 is the linear curvature compensation for the conventional bandgap voltage generator. FIG. 31L2 is the bandgap generator for bandgap voltage and bandgap current having  $(V_{BG}, I_{BG})$  coupling: it has both the 1st and the 2nd curvature compensation. FIG. 31M is the system and architect of IBG Bandgap Current generator. FIG. 31N1 is the system and architect of  $V_{BG}$  Bandgap Voltage generator. FIG. 31N2 is the system and architect of Iso Bandgap current generator. FIG. 31O is the system and architect for the wide frequency PLL/Clock generator. FIG. 31P is the system and architect of the RC type Xtaless Clock. FIG. 31Q1 is the schematics of the N-type current buffer made of current mirror. FIG. 31Q2 is the schematics of the P-type current buffer made of current mirror.

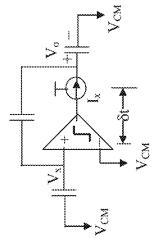

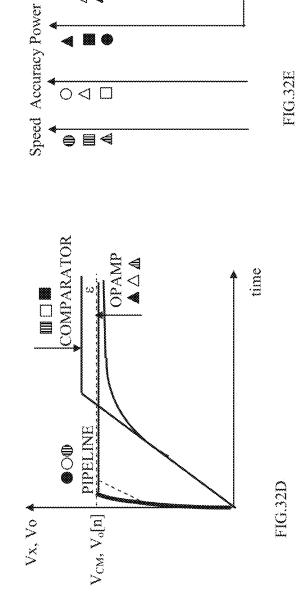

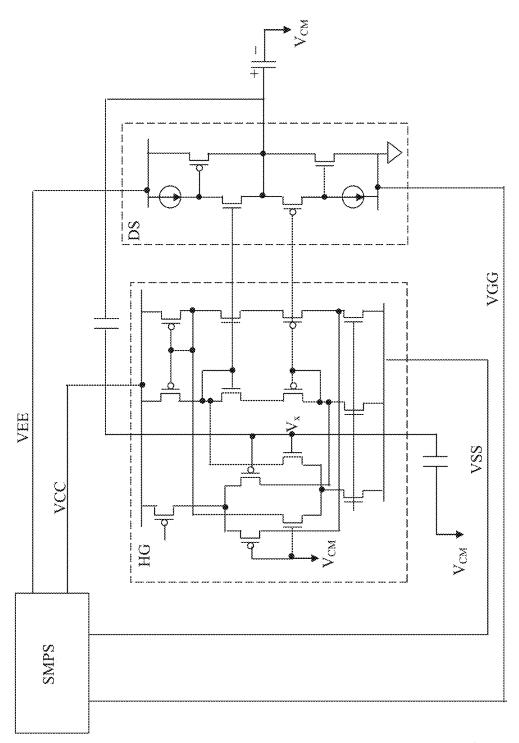

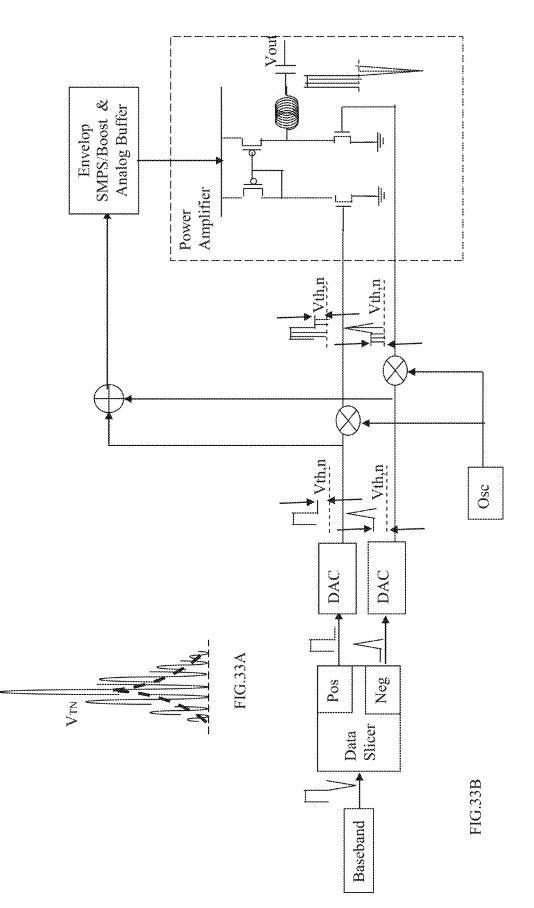

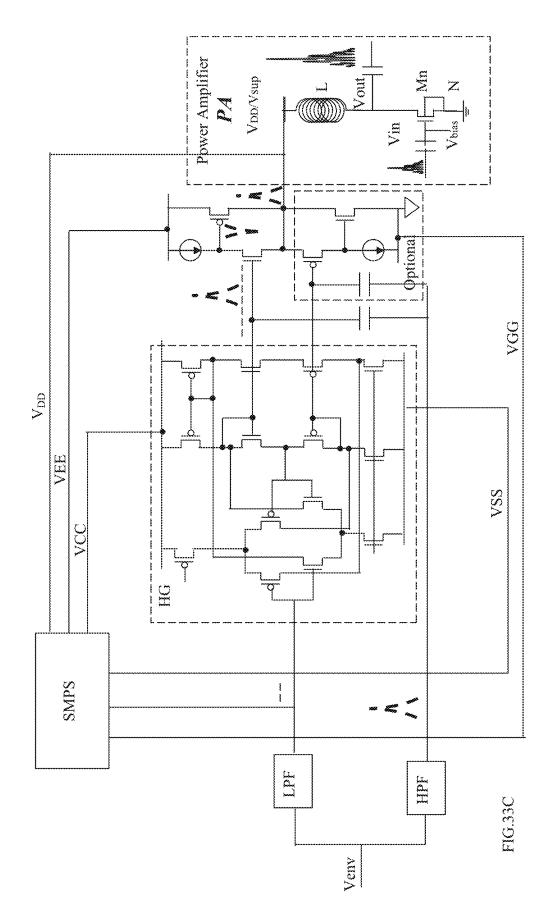

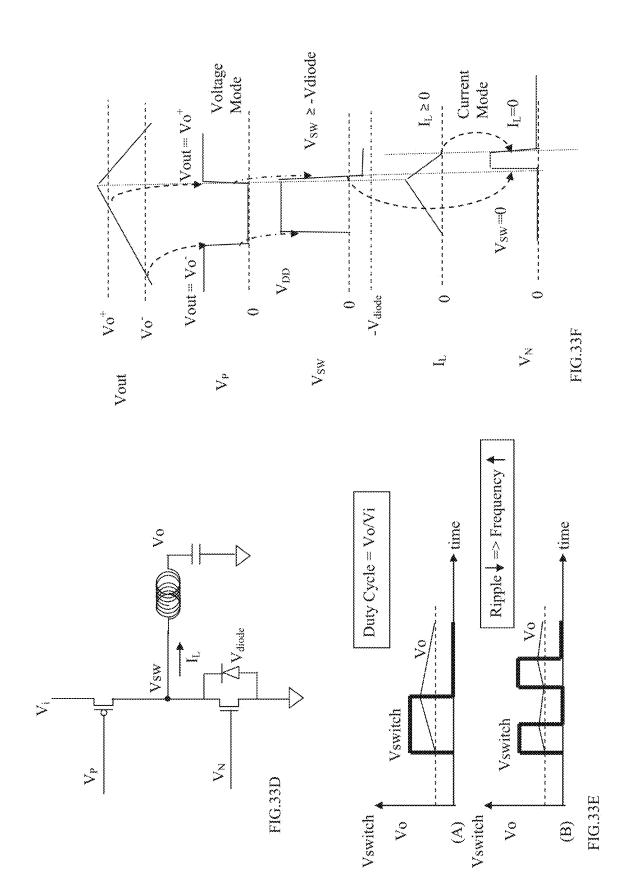

[0087] FIG. 32A is the MDAC of the conventional pipeline ADC. FIG. 32B is the MDAC of the comparator based ADC. FIG. 32C is the MDAC of the super-drive ADC. FIG. 32D is the comparison of speed of the super-drive ADC with the conventional ADC and the comparator based ADC. FIG. 32E is the comparison of speed, accuracy and power of the super-drive ADC with the conventional ADC and the comparator based ADC. FIG. 32F is the schematics of the MDAC of the super-drive ADC where MDAC is multiplying digital-to-analog converter. It is the performance comparison among the super-drive ADC, the conventional ADC and the comparator based ADC. [0088] FIG. 33A is the waveform of the high PAR signals. FIG. 33B is the RF system having the high power efficiency Power Amplifier. FIG. 33C is the circuit of the low power ultra-fast dynamic power supply for the power amplifier having the high power efficiency and low power operation. FIG. 33D is the SMPS output stage of buck converter. FIG. 33E is the illustration of the fundament principle of the SMPS buck converter. FIG. 33F is the illustration of the operation of the Adaptive Optimum Constant On Time AOCOT Buck Converter with the hybrid voltage mode and current mode. It is the ultra-fast dynamic power supply for the high power-efficiency high peak-average-ratio PAR Power Amplifier.

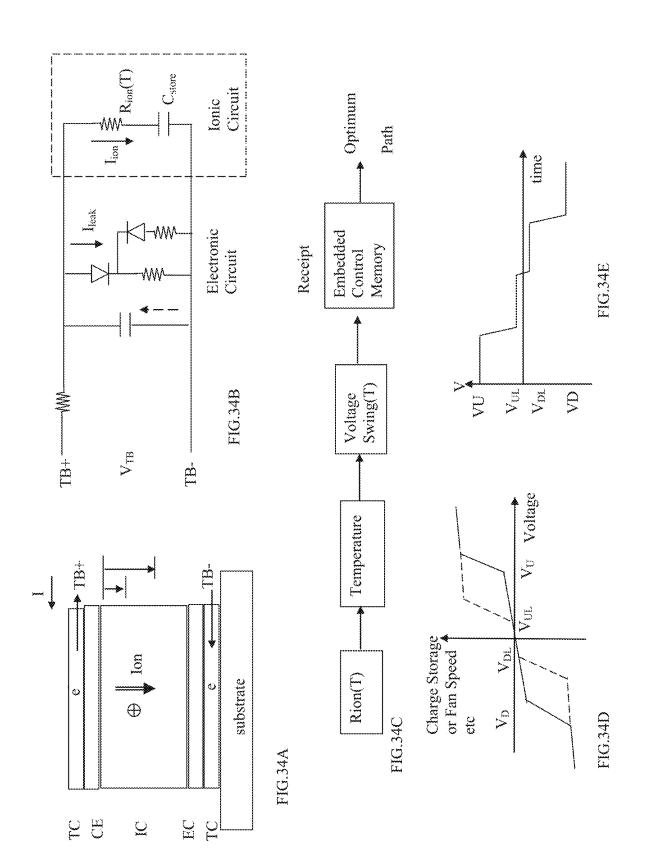

**[0089]** FIG. **34**A is the layered structure of the Thin-Film Battery and/or EC window. FIG. **34**B is the electrical model of the Thin-Film Battery and/or EC window. FIG. **34**C is the signal flow of the temperature compensated Thin-Film Battery and/or EC window. FIG. **34**D is the optical hysteresis curve of Thin-Film Battery and/or EC window. FIG. **34**E is the operation of the Thin-Film Battery and/or EC window. It is the operation characteristics of the Thin-Film Battery and/or Electrochromic EC window.

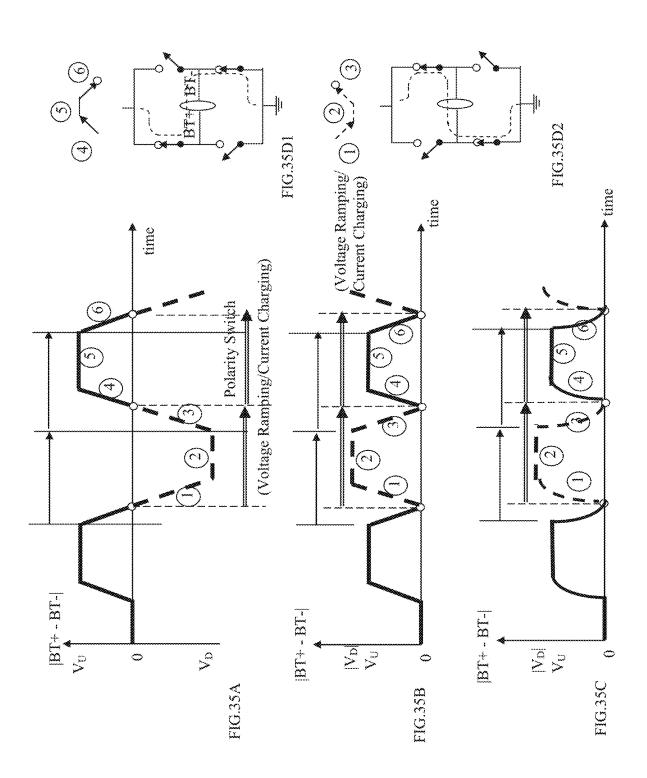

**[0090]** FIG. **35**A is the bipolar operation of the Thin-Film Battery and/or EC window. FIG. **35**B is the unipolar operation of the Thin-Film Battery and/or EC window. FIG. **35**C is the non-linear unipolar operation of the Thin-Film Battery and/or EC window. FIG. **35**D1 is the unipolar operation for the positive voltage. FIG. **35**D2 is the unipolar operation for the negative voltage. It is the switching operation of Thin-Film Battery and/or EC window.

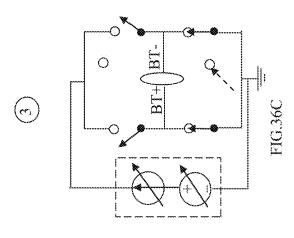

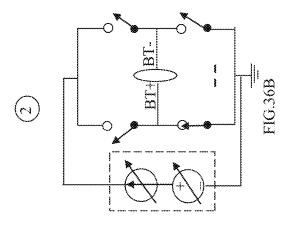

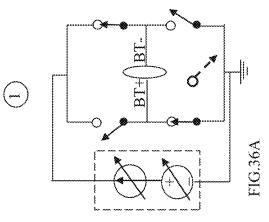

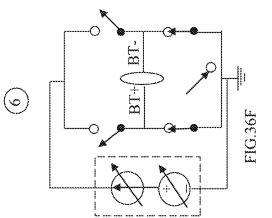

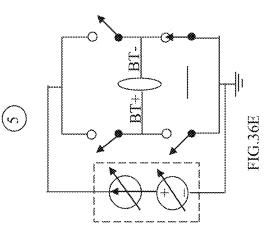

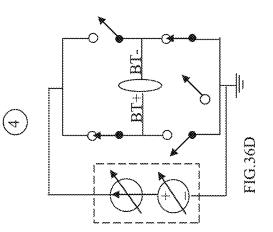

[0091] FIG. 36A is the unipolar operation of the region 1 charging up Battery and/or EC window. FIG. 36B is the unipolar operation of the region 2 hold Battery and/or EC window. FIG. 36C is the unipolar operation of the discharging Battery and/or EC window of region 3. FIG. 36D is the unipolar operation of the charging up Battery and/or EC window of region 4. FIG. 36E is the unipolar operation of the hold Battery and/or EC window of region 5. FIG. 36F is the unipolar operation of the discharging Battery and/or EC window of region 5. FIG. 36F is the unipolar operation of the discharging Battery and/or EC window of region 6. It is the Battery and/or EC window unipolar operation with the H-Bridge as shown in FIG. 35A and FIG. 35B.

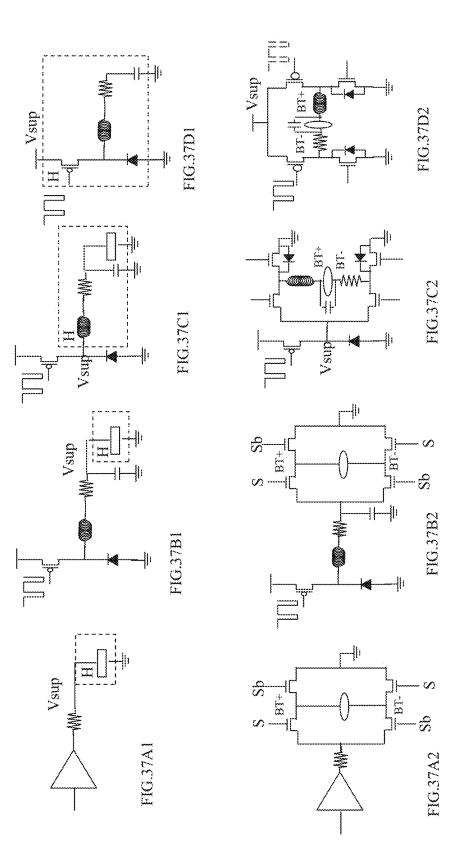

[0092] FIG. 37A1 is the analog buffer circuit with the H-Bridge. FIG. 37A2 is the H-Bridge operating on the analog buffer to generate the voltage ramping circuit. FIG. 37B1 is the buck converter circuit with the H-Bridge. FIG. 37B2 is the H-Bridge operating on the capacitor load of the buck converter to generate the voltage ramping or current charging. FIG. 37C1 is the buck converter circuit with the H-Bridge operating on the inductor and capacitor, etc. FIG. 37C2 is the H-Bridge operating on the inductor and capacitor load of the buck converter to generate the voltage ramping or current charging. FIG. 37D1 is the buck converter circuit with the H-Bridge operating on the whole buck convener. FIG. 37D2 is the H-Bridge operating on the buck converter to generate the voltage ramping or current charging. It is the H-Bridge operating on the power circuit to generate the EC window controller.

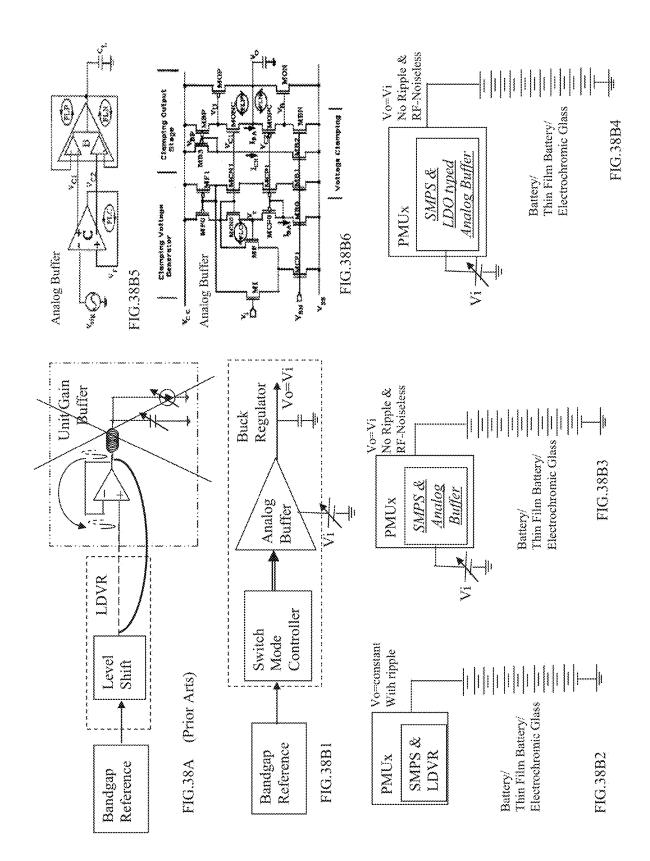

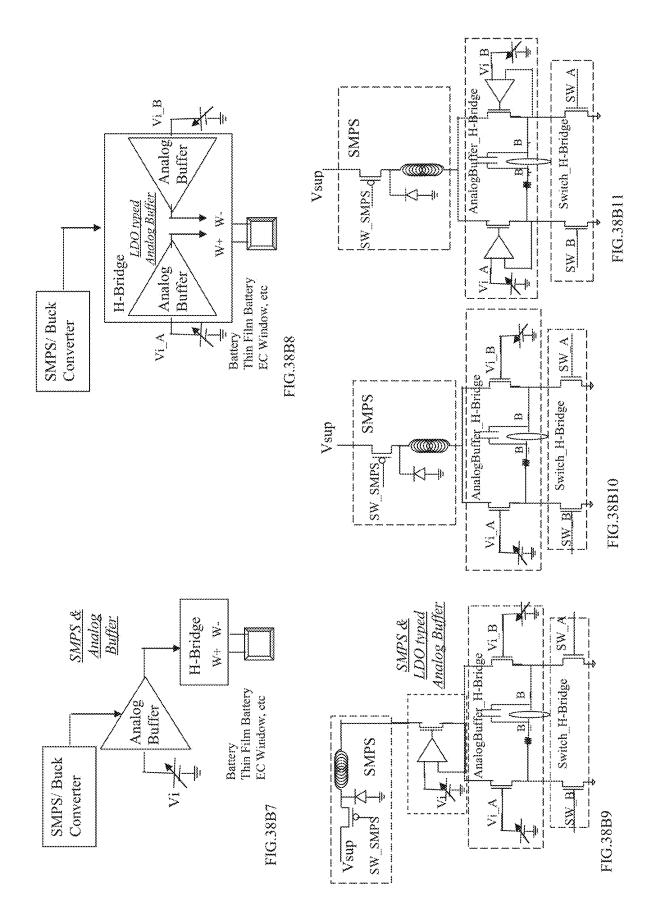

[0093] FIG. 38A is the conventional wrong way to drive a big load with the unit-gain amplifier. FIG. 38B1 is the correct way to drive a big load with analog buffer. FIG. 38B2 is the Power Management Unit PMU having the Switch Mode Power Supply SMPS and Low Drop Voltage Regulator LDVR to supply power to the Battery type device such

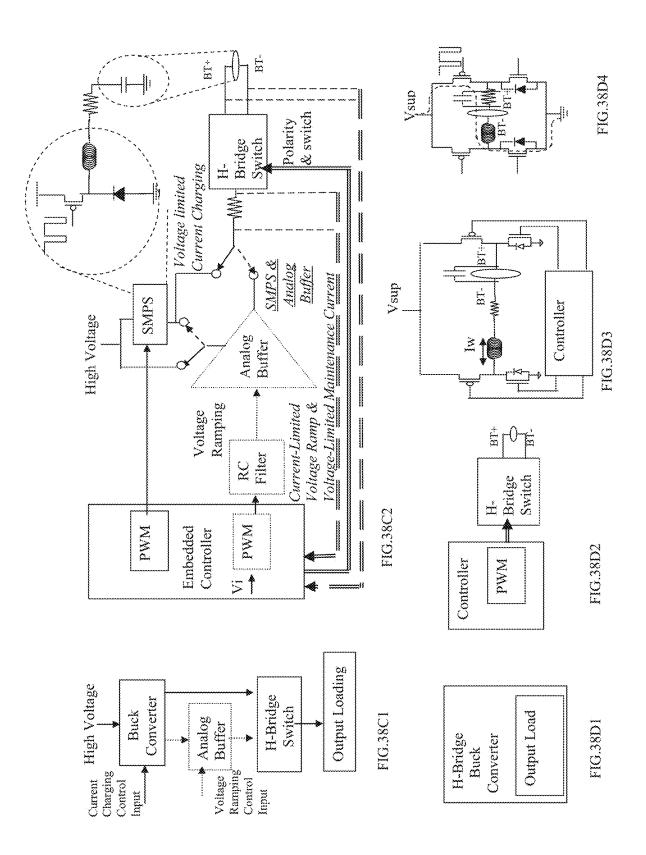

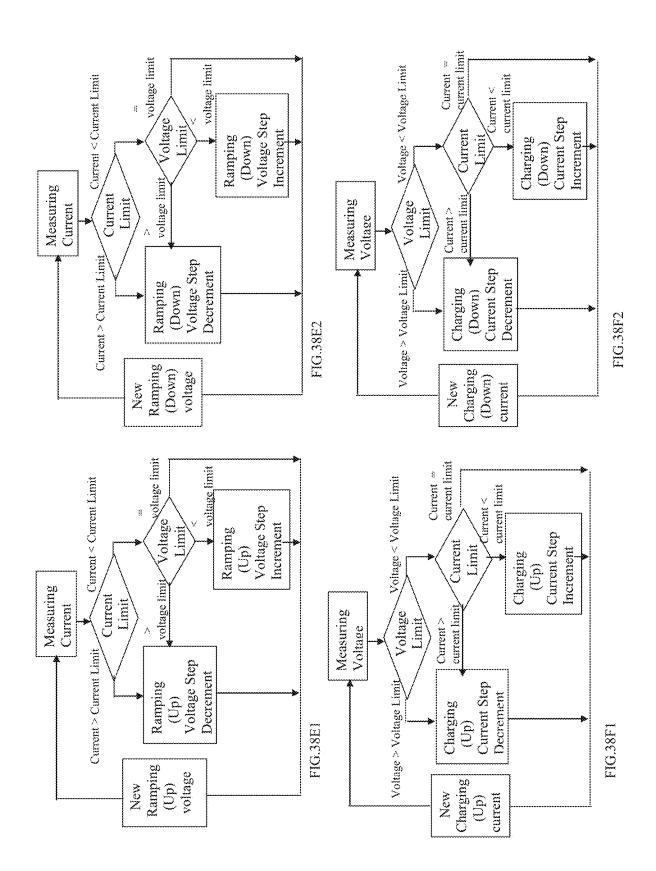

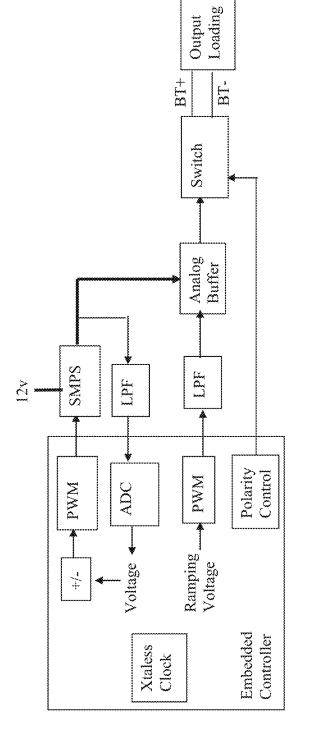

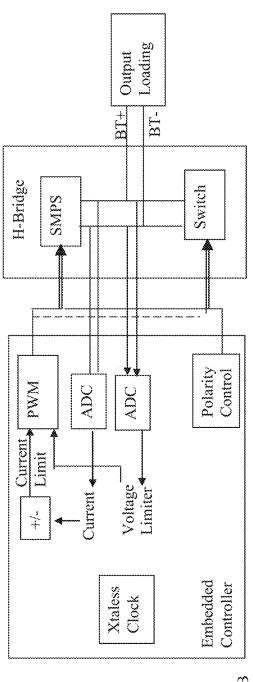

as battery, thin film battery and electrochromic glass devices, etc. FIG. 38B3 is the PMU Power Management Unit having the Switch Mode Power Supply SMPS and Analog Buffer to supply power to the Battery typed device such as battery, thin film battery and electrochromic glass devices, etc. FIG. 38B4 is the PMU Power Management Unit having the Switch Mode Power Supply SMPS and LDO typed Analog Buffer to supply power to the Battery type device such as battery, thin film battery and electrochromic glass devices, etc. FIG. 38B5 is the block diagram of the Analog Buffer; FIG. 38B6 is the detailed schematics of the Analog Buffer. FIG. 38B7 is the SMPS-LDO typed Analog Buffer and H-Bridge. FIG. 38B8 is the SMPS and H-Bridge with LDO typed Analog Buffer embedded in the H-Bridge. FIG. 38B9 is the SMPS-LDO typed Analog Buffer and H-Bridge. FIG. 38B10 is the analog buffer embedded in the H-Bridge. FIG. 38B11 is the LDO type analog buffer embedded in the H-Bridge for voltage control. FIG. 38C1 is the block diagram of the Switch Mode Power Supply combining with Low Drop Voltage Regulator (LDVR) type Analog Buffer to be the Rippleless battery charger and RF-Noiseless EC window controller. FIG. 38C2 is the design platform for the Rippleless battery charger and RF-Noiseless battery charger and/or EC window controller. FIG. 38D1 is the architecture of the H-Bridge buck converter typed battery charger and/or EC window controller. FIG. 38D2 is the block diagram of the H-Bridge buck converter typed EC window controller. FIG. 38D3 is the embedded battery charger and/or window controller. FIG. 38D4 is the operation of the embedded battery charger and/or window controller. FIG. 38E1 is the algorithm of the current-limited voltage ramping in charging up phase. FIG. 38E2 is the algorithm of the current-limited voltage ramping in discharging phase. FIG. 38F1 is the algorithm of the voltage-limited current charging in charging up phase. FIG. 38F2 is the algorithm of the voltage-limited current charging in discharging phase.

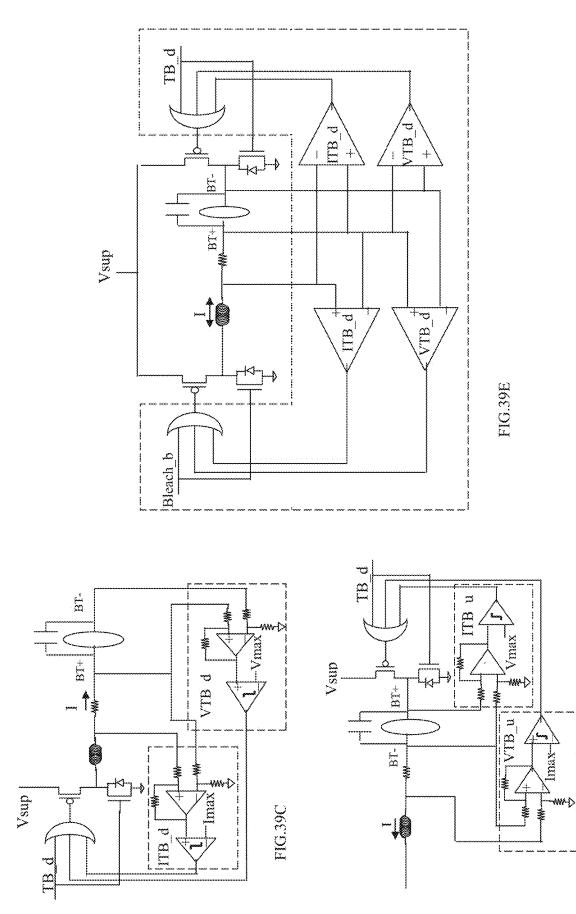

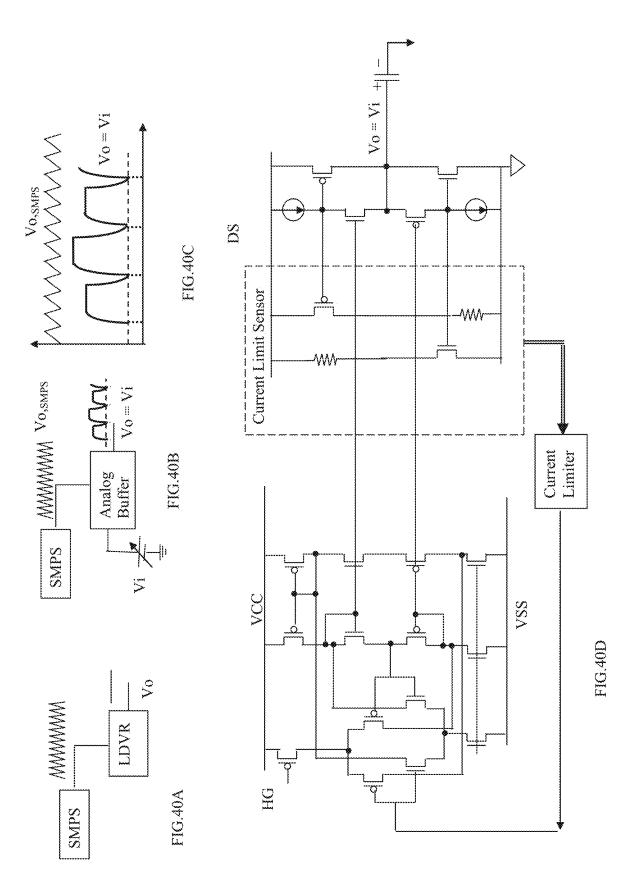

[0094] FIG. 39A is the block diagram for the currentlimited super-performance battery, thin-film battery and/or voltage-ramping EC window controller, etc. FIG. 39B is the block diagram for the current-limited super-performance battery, thin-film battery and/or voltage-limited currentcharging EC window controller, etc. FIG. 39C is the bleaching/discharging process; FIG. 39D is the coloring/charging process; FIG. 39E is the complete super-performance battery, thin-film battery and/or EC window driver, etc. It is the super-performance battery, thin-film battery and EC window driver, etc. which can be developed to be the dedicated chip. [0095] FIG. 40A is the conventional power supply system. FIG. 40B is the power supply made of the analog buffer for voltage ramping operations of the battery charger and/or EC window controller. FIG. 40C is the waveform of the voltage ramping operation of the analog buffer. FIG. 40D is the analog buffer circuit for the voltage ramping battery charger and/or EC window controller. It is the analysis of the analog buffer typed voltage ramping.

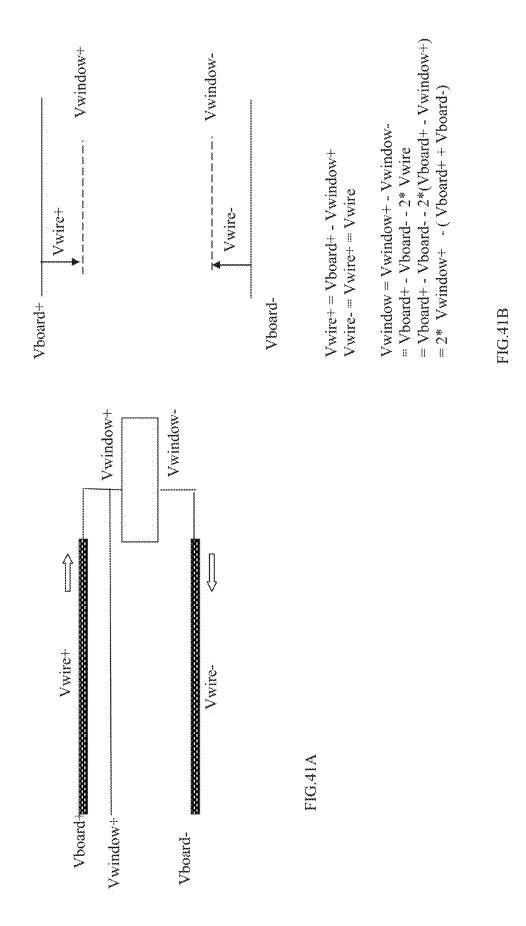

**[0096]** FIG. **41**A is the triple-wire connection for longdistance connection to drive device. FIG. **41**B is the wire architecture of the triple-wire connection for long distance connection to drive device.

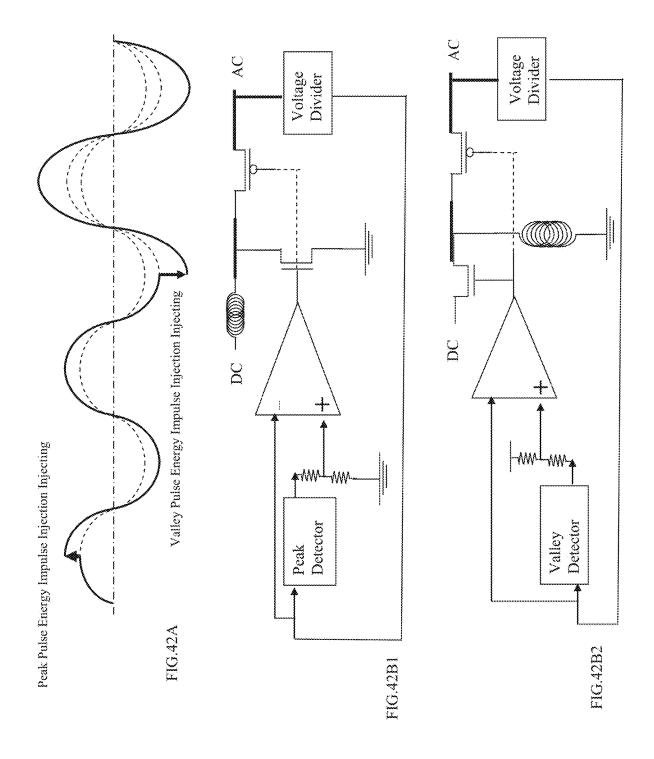

[0097] FIG. 42A is the energy injection into AC line. FIG. 42B1 is the energy injection into AC line at the peak voltage of the AC line. FIG. 42B2 is the energy injection into AC line at the valley voltage of the AC line.

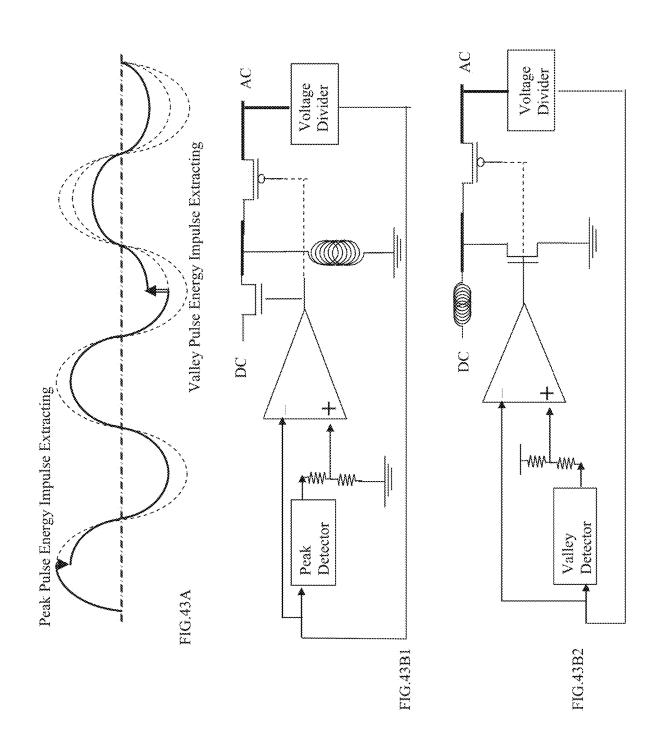

**[0098]** FIG. **43**A is the energy extraction out of AC line. FIG. **43**B1 is the energy extraction out of AC line at the peak voltage of the AC line. FIG. **43**B2 is the energy extraction out of AC line at the valley voltage of the AC line.

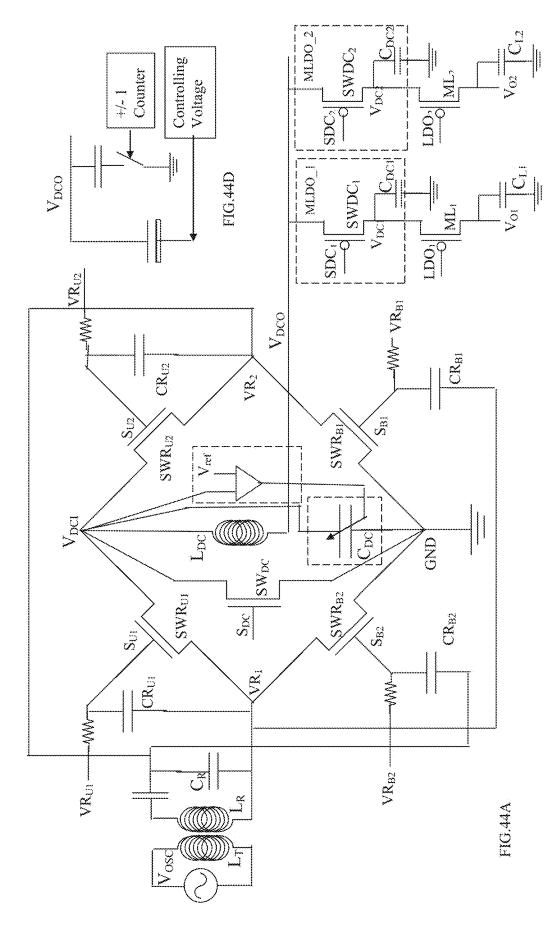

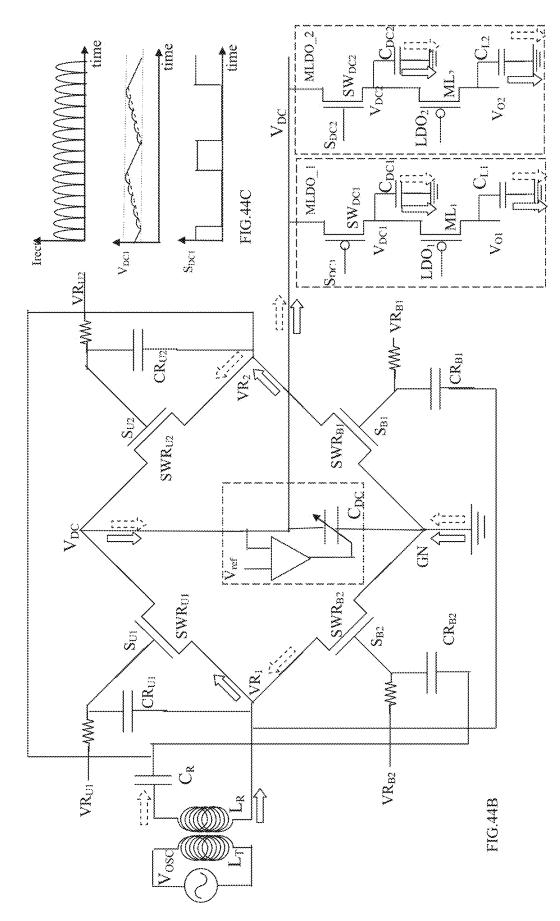

**[0099]** FIG. **44**A is the Rectifier-DC/DC-Regulator. FIG. **44**B is the 5R Recycling Resonant Re-synchronous Rectifier Regulator with the controlled capacitors for frequency tuning. FIG. **44**C is the timing diagram of the 5R: FIG. **44**D is the fine tune circuit for oscillation.

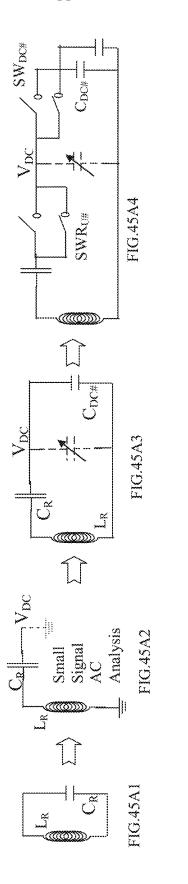

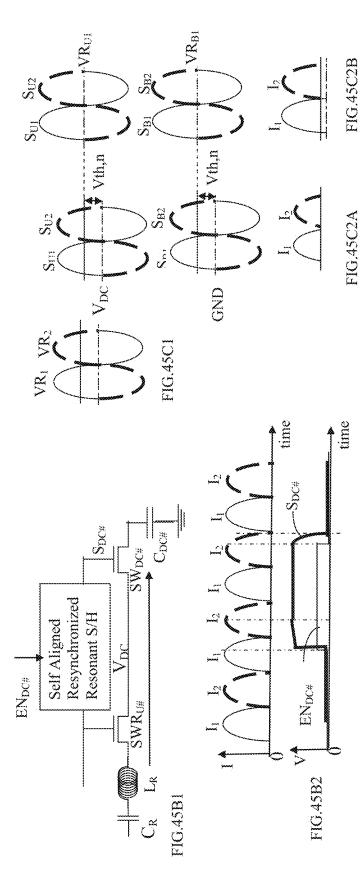

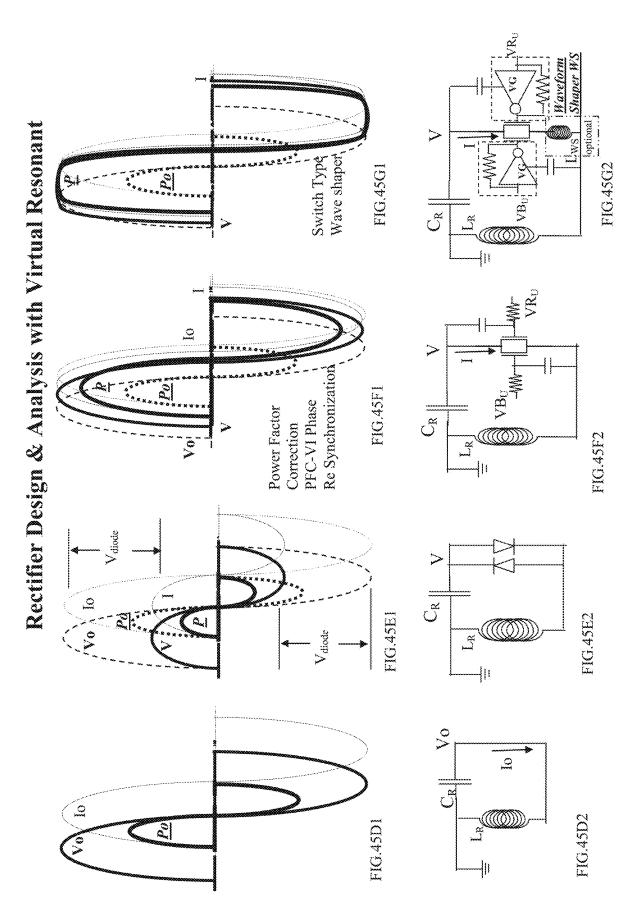

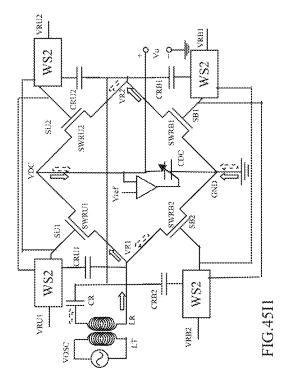

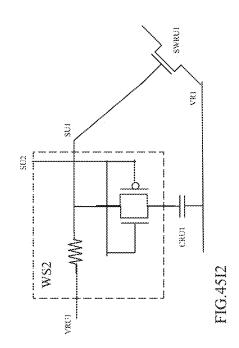

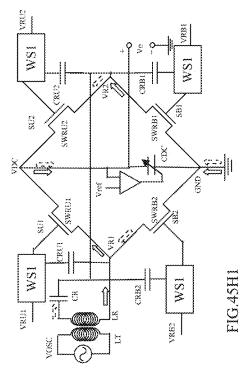

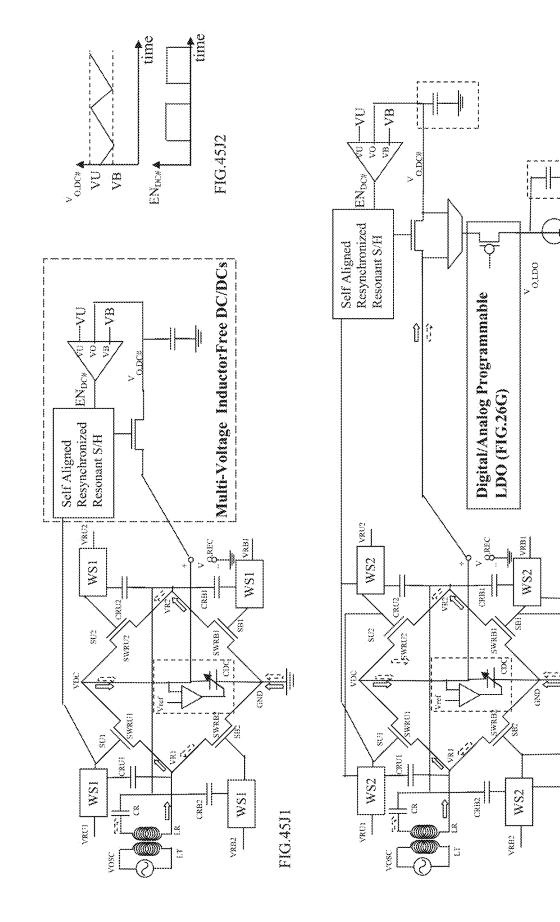

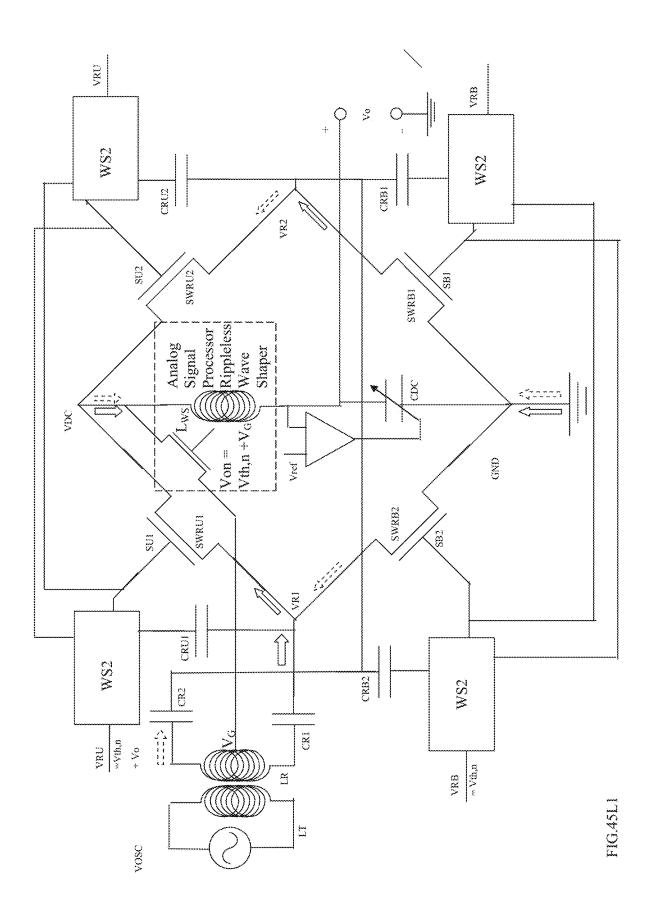

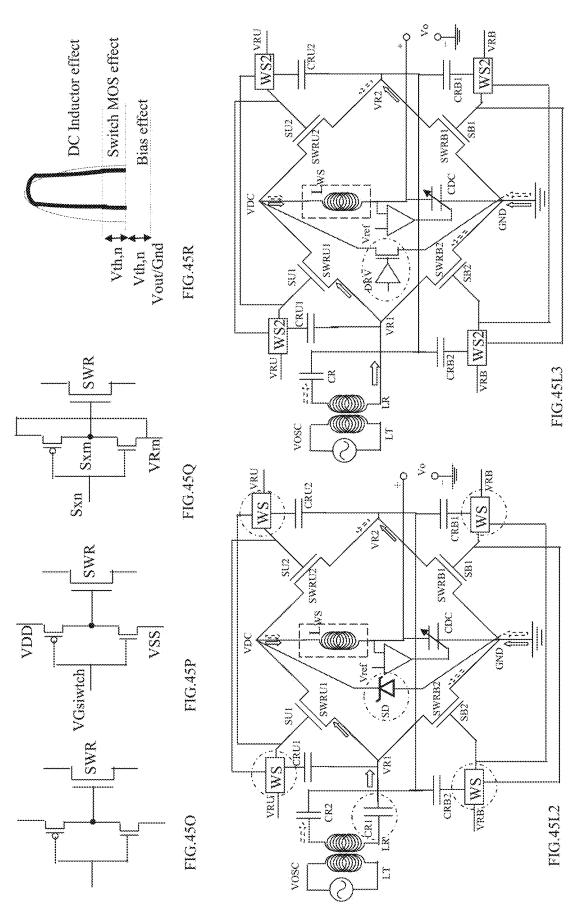

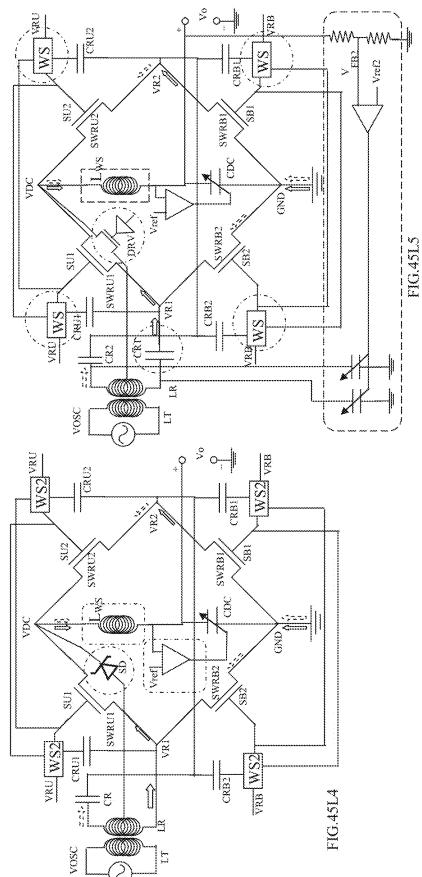

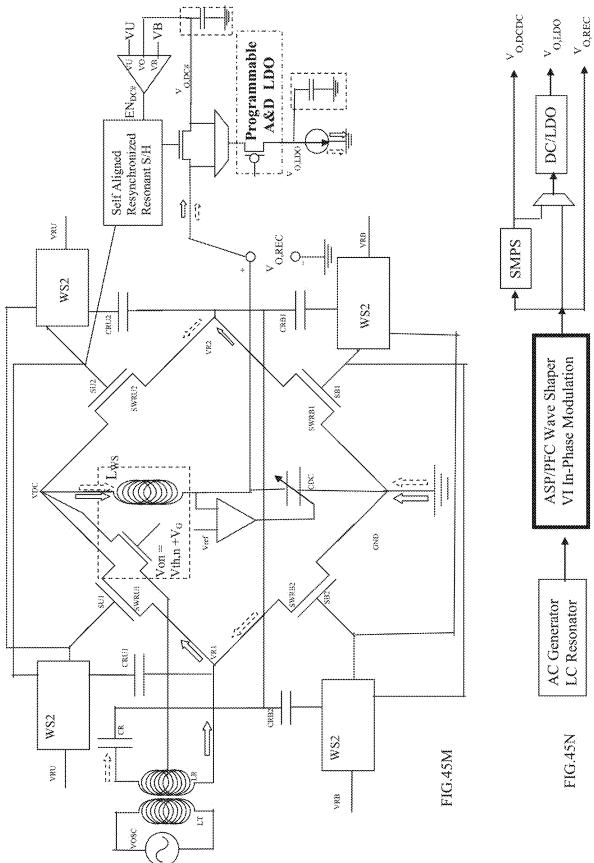

[0100] FIG. 45A1 is the fundamental Oscillatory Resonator. FIG. 45A2 is the equivalent fundamental Oscillatory Resonator having two different ends,  $V_{DC}$  and Ground. FIG. 45A3 is the fundamental 5R Oscillatory Resonator which can be derived from FIG. 45A2. FIG. 45A4 is the basic 5R Recycling Resonant Resynchronization Rectifying Regulator which can be derived from FIG. 45A3. FIG. 45B1 is the Recycling Resonant mechanism for the switch of DC/DC converter. FIG. 45B2 is the timing diagram of the Recycling Resonant mechanism for the switch of DC/DC converter. FIG. 45C1 is the resonant oscillation of the LC resonator of the wireless power receiver. FIG. 45C2A is the rectifier operation without the bias voltage. FIG. 45C2B is the rectifier operation with the bias voltage. FIG. 45D1 is the resonant voltage, current and power of the ideal resonant circuit as shown in FIG. 45D2. FIG. 45D2 is the ideal resonant circuit. FIG. 45E1 is the resonant voltage, current and power of the resonant circuit having the diodes which emulates the rectifier circuit having H-bridge with Schottky diodes. FIG. 45E2 is the resonant circuit having the diodes which emulates the rectifier circuit having H-bridge Schottky diodes. FIG. 45F1 is the resonant voltage, current and power of the resonant circuit having the active MOS which emulates the rectifier circuit having H-bridge with MOS. FIG. 45F2 is the resonant circuit having MOS device which emulates the rectifier circuit having H-bridge with MOS. FIG. 45G1 is the resonant voltage, current and power of the resonant circuit having the active MOS which emulates the rectifier circuit having H-bridge with MOS and wave-shaper switching driver. FIG. 45G2 is the resonant circuit having the MOS which emulates the rectifier circuit having H-bridge with MOS and wave-shaper switching driver. FIG. 45H1 is the rectifier having wave-shaper switching driver as shown in FIG. 45H2. FIG. 45H2 is the fundamental wave-shaper. FIG. 4511 is the rectifier having wave-shaper switching driver as shown in FIG. 4512. FIG. 4512 is the mutual-latching enhanced wave-shaper. FIG. 45J1 is the rectifier with multi-voltage Inductor-Free DC/DC converter. FIG. 45J2 is the waveform of the multi-voltage Inductor-Free DC/DC converter. FIG. 45K is the complete set of Recycling Resonant Resynchronization Rectifying Regulator 5R having the single power-conversion stage. FIG. 45I is the complete schematics of the 5R having the Analog Signal Process/Power Factor Correction ASP/PFC wave shaper. FIG. 45L2 is the alternative design of 5R circuit with Schottky Diodes. FIG. 45L3 is the alternative design of 5R circuit with active MOS. FIG. 45L4 is the alternative design of 5R circuit with Schottky Diodes. FIG. 45L5 is the alternative design of 5R circuit with active MOS. FIG. 45M is the complete schematics of the 5R having the ASP/PFC wave shaper. SMPS and A&D programmable LDO. FIG. 45N is the functional block diagram of the 5R having ASP/PFC wave shaper, SMPS and A&D programmable LDO. FIG. 450 is the generic wave shaper of WS. FIG. 45P is the gate-activated switching buffer driver type wave shaper. FIG. **45**Q is the source-activated switch-energy recycling wave shaper WS**2**. FIG. **45**R is the operational mechanism analysis of wave shaper. It is the fundamental principles of 5R Recycling Resonant Re-synchronous Rectifier Regulator.

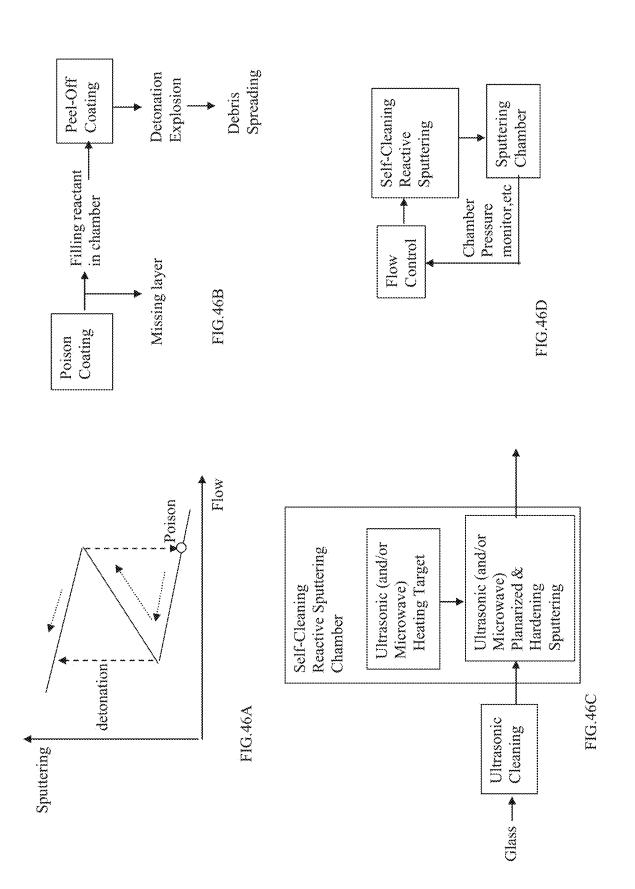

**[0101]** FIG. **46**A is the characteristics of the gas reaction sputtering process. FIG. **46**B is the detonating phenomena in the gas reaction sputtering chamber. FIG. **46**C is the self-cleaning sputtering process. FIG. **46**D is the block diagram of the system for the self-cleaning sputtering chamber. It is the operation of the self-cleaning sputtering chamber.

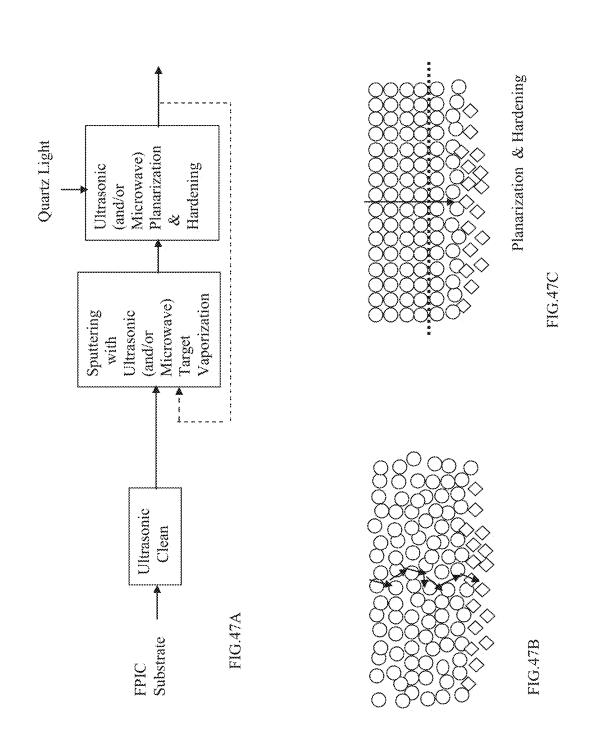

**[0102]** FIG. **47**A is the recursive/pipeline manufacturing process for the high performance EC window manufacturing process. FIG. **47**B is the section view without the plating and hardening process. FIG. **47**C is the section view with the plating and hardening process. It is the high performance EC window manufacturing process.

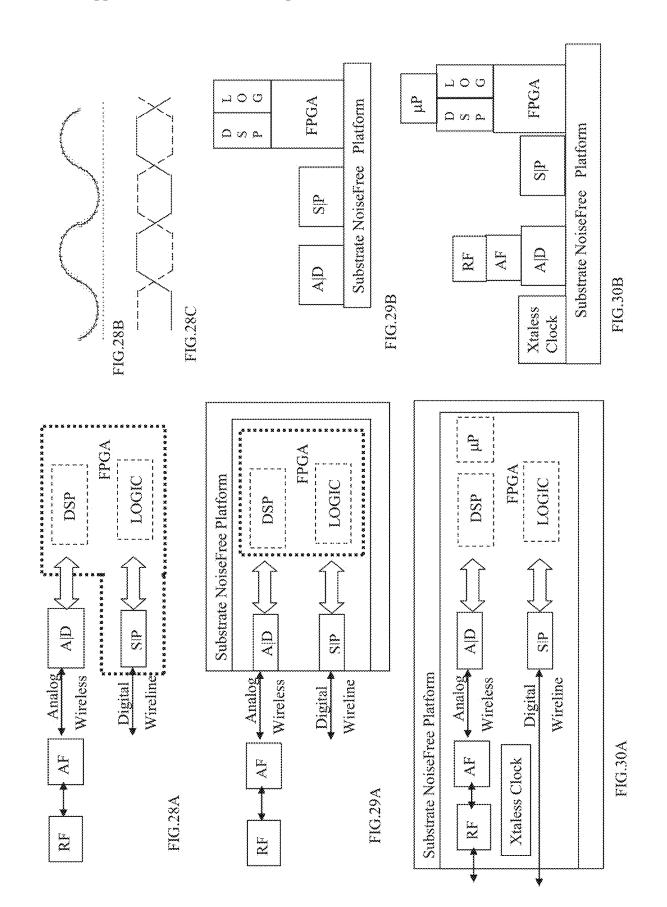

**[0103]** FIG. **48**A is the platform of the Anlinx & Milinx & Zilinx FPSOC having the 23Less Green Technology for Smart Window. FIG. **48**B is the Anlinx & Milinx & Zilinx FPSOC having the IP wrapper of Noise Isolation Technology for 23Less Green Technology for Smart Window. It is the Anlinx & Milinx & Zilinx Field Programmable System On Chip FPSOC with the 23Less Green Technology for Smart Window.

#### DESCRIPTION AND OPERATION

**[0104]** The Green Technology is the reduction of energy consumption, noise generation and resource saving. The green technology integration system comprises an smart Insulated Glass Unit. The smart Insulated Glass unit is referred as the Intelligent Graphic Unit IGU. The Intelligent Graphical Unit IGU further comprises the transparent multimedia panel, electrochromic panel and the transparent solar cell panel, etc. The electrical energy generated by transparent Solar panel can provide to transparent Multimedia panel and Electrochromic panel, etc. Furthermore, the electrical energy generated by the green energy Smart Window can provide to the smart grid with wireline power line and provide to the mobile devices with wireless power supply, etc.

[0105] To be feasible, the smart window must be as transparent having window view as the conventional IGU Insulated Glass Unit. To have the same window view as conventional IGU, all the complex electronic components must be embedded in the frame of the smart window. To have all the complex electronic components embedded in the frame, all the complex components must be integrated to be chip, FPSOC field programmable system on chip. To prove all the electronic components being able to be integrated, the Field Programmable System On Chip FPSOC of Anlinx, Milinx and Zilinx is disclosed in detail. Therefore, the green energy smart window is based on the W5RS Wireless Window 5R System to integrate the electronic components in the FPSOC and embedded all the components in the frame. "5S" represents "Smart Solar Supply Silicon System". "W5" represents "Wireless Wireline Weave Wishful Window". "5R" represents "Recycling Resonant Resynchronization Rectifying Regulator". "W5RS" is the killer product applications of Silicon Valley and "5R" is the killer core IP technologies of Silicon Valley. Even for the Wireless Power Consortium WPC Qi and Alliance for Wireless Power A4WP wireless power supply standards, the novel "single-stage 5R" can have the AC/DC power efficiency as high as 95% which is the highest record in the world. The green energy smart home of iPhome has the green energy smart window/iPindow. The green energy smart window is constituted of the multiple types of smart windows. The multiple smart windows are such as transparent multimedia window, transparent solar window and electrochromic window, etc. These panels are integrated to be one smart window unit.

**[0106]** As shown in FIG. 1A and FIG. 1B, the green energy Wireless Window 5R System W5RS is constituted of transparent Smart Multimedia Panel, Smart Electrochromic Panel and transparent Smart Solar Panel, etc. The transparent Smart Solar Panel harvests solar energy to be electric energy to provide power to the transparent Smart Multimedia Panel and Smart Electrochromic Panel, etc. The electrical energy further provides to smart grid and mobile means. There are versatile arrangements for the transparent multimedia panel and Electrochromatic panel in smart window. For the FIG. 1A, the LCD/LED/OLED TV/FlatPanel/Electrochromatic 140 can be replaced with

**[0107]** (1) transparent LCD/LED/OLED/TV/FlatPanel multimedia panel only as shown in FIG. **1A3** to be the master window; or

**[0108]** (2) Electrochromatic panel only as shown in FIG. **1A4** to be the slave window; or

**[0109]** (3) LCD/LED/OLED % IV/Flat Panel/Electrochromatic multimedia panel and Electrochromatic panel as shown in FIG. **1A5** to be the master window. As shown in the FIG. **1B**, the interior panel is transparent multimedia panel; the middle panel is Electrochromatic; the exterior panel is the transparent solar as shown in FIG. **1A5**.

**[0110]** Furthermore, the smart window can be the transparent LCD/LED/OLED/TV/FlatPanel multimedia panel only serving as the master device.

[0111] The Green Energy System comprising the Master device of MES type smart window or MS type smart window and the Slave device of the ES type smart window. [0112] As shown in FIG. 1A5, the MES type green energy smart window unit for smart home and smart grid comprises the electronic components having control circuitry, power supply and internet devices. The control circuitry comprises a processor, a multimedia window controller, an electrochromic window controller, a solar panel controller, and a power supply controller. The power supply comprises a rechargeable power supply, a wireless charging power supply circuit, an inverter circuit and a backlight circuit. The internet devices comprise a wireless internet remote access and control circuit. The green energy smart window has a transparent multimedia panel, an electrochromic panel and a transparent solar panel enclosed in an isolated glass unit IGU. The transparent multimedia panel, electrochromic panel and transparent solar panel have the whole panel size been the same as said smart window. The smart window has three operation modes, (1) normal open mode, (2) shut mode and (3) smart phone mode. The turbine fan and all the electronic components are embedded in the frame of said green energy smart window unit. In the normal open mode, the whole panel of the smart window view is clean and clear looking being transparent as the conventional dual panel window without any blockage in the open mode. In the shut mode, the whole smart window panel light is blocked by said smart window. In the shut mode, the whole smart window panel light is blocked either by coloring the electrochromic panel or by darkening the transparent multimedia panel. In the smart phone mode, the transparent multimedia panel of the smart window working as smart phone with huge smart phone, interactive TV screen, internet access and control of the smart window. The green energy smart window serves as the master device of the smart home and smart grid. All interactive and remote control for the smart home is through the interface of the transparent multimedia panel in said smart phone mode. The transparent solar panel is transparent and facing outside. The transparent multimedia panel is facing inside room and controlled by a host serving as master device. In the normal open mode, the multimedia panel is transparent and has no blockage of the window view. The isolated glass unit comprises an exterior glass panel located at a first side facing an external light source and an interior glass panel located at a second side, opposite the first side. The transparent solar cell panel is positioned on the exterior glass panel in the isolated glass unit, whereby exterior light transmitting through the transparent solar cell panel and received by the electrochromic panel and the transparent multimedia panel. The transparent solar cell panel is capable of generating power to smart grid and smart window unit including the control circuitry, the rechargeable power supply, the wireless charging power supply circuit, the electrochromic panel, and the transparent multimedia panel. The transparent multimedia panel is capable of displaying video being positioned on said interior glass panel in the isolated glass unit and further comprises a transparent touch screen displaying and detecting touch inputs. The green energy smart window further comprises a microcomputer to control the smart phone type Multimedia Panel. The Multimedia Panel is transparent in the open mode. The Multimedia Panel is the smart phone type huge screen to setup, control and communication, etc. in the smart phone Mode. The micro-computer controlled Multimedia Panel further comprises transparent touching screen to have user interactive with the Multimedia Panel. The transparent touching screen covers on the screen of the Multimedia Panel. Touching on the transparent touching screen, it makes the interaction with Multimedia Panel through the microcomputer. The transparent touching screen laying on the interior glass panel having layer of transparent sensor to detect the touching positions on the transparent touching screen. The electrochromic panel is positioned in the isolated glass unit, and is capable of blocking received light. The backlight provides light for the transparent multimedia panel during night. The transparent solar panel supplies power to the smart grid through the inverter. The transparent multimedia panel has the wireless internet remote access and control circuit controlling as master device. The mobile device charging unit comprises a wireless power pad charger inductively coupled to said wireless charging power supply circuit. The power supply controller is capable of controlling rechargeable power supply to selectively discharge current to an external electrical smart grid coupled to the smart window unit.

**[0113]** As shown in FIG. **1**A**3**, the MS type green energy smart window unit for smart home and smart grid comprises electronic components comprising control circuitry, power supply and internet devices. The control circuitry comprises a processor, a multimedia window controller, a solar panel controller, and a power supply controller. The power supply comprises a rechargeable power supply; a wireless charging power supply circuit, an inverter circuit and a backlight circuit. The internet devices comprises a wireless internet

remote access and control circuit. The green energy smart window has a transparent multimedia panel and a transparent solar panel enclosed in an isolated glass unit. The transparent multimedia panel and transparent solar panel has a whole panel size been the same as the smart window. The smart window has three operation modes, (1) normal open mode, (2) shut mode and (3) smart phone mode. The electronic components are embedded in the frame of the green energy smart window unit. In the normal open mode, the whole panel of the smart window view is clean and clear looking as the conventional dual panel window. The smart window is without any blockage and is transparent in the normal open mode. In the shut mode, the whole smart window panel light is blocked by the smart window. In the shut mode, the whole smart window panel light is blocked by darkening the transparent multimedia panel. In the smart phone mode, the transparent multimedia panel of the smart window works as smart phone with huge smart phone, interactive TV screen, internet access and control of the smart window. The green energy smart window serves as master device of the smart home and smart grid. All interactive and remote control for the smart home is through the interface of the transparent multimedia panel in the smart phone mode. The transparent solar panel is transparent and facing outside. The transparent multimedia panel being facing inside room and controlled by a host serving as master device. In the normal open mode, the multimedia panel is transparent and has no blockage of the window view. The isolated glass unit comprises an exterior glass panel located at the first side facing an external light source and an interior glass panel located at the second side, opposite the first side. The transparent solar cell panel is positioned on the exterior glass panel in the isolated glass unit. The exterior light transmits through the transparent solar cell panel and received by the transparent multimedia panel. The transparent solar cell panel is capable of generating power to smart grid and smart window unit. The smart window unit includes the control circuitry, the rechargeable power supply, the wireless charging power supply circuit and the transparent multimedia panel. The transparent multimedia panel is capable of displaying video being positioned on the interior glass panel in the isolated glass unit. The smart multimedia panel further comprises a transparent touch screen displaying and detecting touch inputs. The backlight provides light for the transparent multimedia panel during night. The transparent solar panel supplies power to the smart grid through the inverter. The wireless internet remote access and control circuit enable the transparent multimedia panel working as master device. The mobile device charging unit comprises a wireless power pad charger inductively coupled to the wireless charging power supply circuit. The power supply controller is capable of controlling rechargeable power supply to selectively discharge current to an external electrical smart grid coupled to the smart window unit.

**[0114]** As shown in FIG. **1A4**, the ES type green energy smart window unit for smart home and smart grid comprises the electronic components comprising control circuitry, power supply and internet devices. The control circuitry comprises a processor, an electrochromic window controller, a solar cell panel controller, and a power supply controller. The power supply comprises a rechargeable power supply: a wireless charging power supply circuit; an inverter circuit and a backlight circuit. The internet devices comprising a

wireless internet remote access and control circuit. The green energy smart window has an electrochromic panel and a transparent solar panel enclosed in an isolated glass unit. The electrochromic panel and transparent solar panel have a whole panel size been the same as said smart window. The smart window has three operation modes. (1) normal open mode, (2) shut mode and (3) smart phone mode. The turbine fan and all the electronic components being embedded in the frame of the green energy smart window unit. In the normal open mode, the whole panel of the smart window view is clean and clear looking as the conventional dual panel does The window view is transparent without any blockage in the open mode. In the shut mode, the whole smart window panel light is blocked by the smart window. In the shut mode, the whole smart window panel light is blocked by the coloring of the electrochromic panel.

**[0115]** In the smart phone mode, the smart window is controlled as slave device. The green energy smart window serves as slave device of the smart home. All interactive and remote control for the smart home is through the interface of said internet device in the smart phone mode. The transparent solar panel is transparent and facing outside. The smart window is controlled by host serving as a slave device in the smart phone mode, said electrochromic panel is transparent and has no blockage of the window view.

The isolated glass unit comprises an exterior glass panel located at a first side facing an external light source. An interior glass panel located at a second side, opposite the first side. The transparent solar cell panel is positioned on the exterior glass panel in the isolated glass unit. The exterior light transmits through the transparent solar cell panel and received by the electrochromic panel and the transparent multimedia panel. The transparent solar cell panel is capable of generating power to smart grid and smart window unit including the control circuitry, the rechargeable power supply, the wireless charging power supply circuit and the electrochromic panel. The electrochromic panel is positioned in the isolated glass unit and is capable of blocking received light. The transparent solar panel supplies the power to the smart grid through the inverter. The wireless internet remote access and control circuit control the smart window as a slave device. A mobile device charging unit comprises a wireless power pad charger inductively coupled to the wireless charging power supply circuit. The power supply controller is capable of controlling the rechargeable power supply to selectively discharge current to an external electrical smart grid coupled to the smart window unit.

**[0116]** The Transparent Solar Cell is transparent that exterior light passes through the Transparent Solar Cell and shines on the Electrochromic Panel and the transparent Multimedia Panel. The transparent multimedia widow is the video display such as LCD/LED/TV/Flat Panel to provide interactive entertainment, local/remote access and control to be the master device. The transparent Solar Cell Panel harvests the solar energy to be electric energy to provide power to the transparent Multimedia Panel and Electrochromic Panel. The electrical energy further provides to smart grid and mobile devices. Furthermore, the electrical energy can provide to mobile devices with wireless power.

**[0117]** The Smart Window of Smart Home is based on the 23Less Green Technology. The 23Less Green Technology for the Noiseless Field Programmable Integrated Circuit FPSOC are Curtainless Window, Bladeless Turbo Fan,

Brakeless Vehicle, Sawless LNA, Resistorless SMPS and Transceiver, Capless LDVR, Inductorless SMPS, Diodeless Random Number Generator, Xtaless Clock Generator, Clockless Switch Mode Power Supply, etc.

[0118] As shown in FIG. 1A and FIG. 1B, the green energy smart window 123 has the window 123g comprising transparent multimedia LCD panel, transparent solar panel 10 and EC panel 20, etc. On the right side of FIG. 1A, it is the sectional view of the green energy smart window. On the left side of the FIG. 1A, there are the functional blocks which are implemented as the electronic system embedded in the IGU frame of the green energy smart window. The Intelligent Graphical Unit IGU 123g has the multimedia LCD panel, transparent solar panel 10 and/or EC panel 20, etc. integrated to be one unit. The transparent solar panel 10 and the Switch Mode Power Supply SMPS 11 provide the solar power energy to the green energy smart window 123 and the smart fan. In the smart window, there are many smart controllers such as Smart Home controller, smart lighting controller, smart solar controller, smart battery controller, smart power controller and smart fan controller, etc. As shown in FIG. 1C, FIG. 48A and FIG. 48B, Anlinx & Zilinx & Zilinx' Field-System-On-Chip FPSOC will integrate all the smart controllers on the same platform to be FPSOC Field Programmable System On Chip.

**[0119]** The transparent Solar panel provides the electricity to the transparent Multimedia panel and Electrochromic panel, etc. to be "self-contained Intelligent Graphical Unit IGU". All the smart controllers will be embedded in the frame of the Intelligent Graphical Unit IGU. As shown in FIG. **1F1**, the Intelligent Graphical Unit IGU further comprises the smart fan and the smart fan controller. In the smart fan, there are the multiple functional modules of the bladeless turbofan, air conditioner, the humidity/de-humidity and air-filter, etc. The bladeless turbine circulates the air for air conditioning and ventilation. In the winter, as shown in FIG. **1N1**, the ceiling warm air will be sucked in to the channel inside the frame of the Intelligent Graphical Unit IGU then be blown out at the floor by the bladeless turbofan.

[0120] The green energy Wireless Window 5R System W5RS is constituted of Transparent Multimedia Panel, Electrochromic Panel and Transparent Solar Cell Panel. The Multimedia Panel. Electrochromic Panel and Transparent Solar Cell Panel are enclosed in the isolated glass unit IGU. The isolated glass unit IGU further comprises exterior glass and interior glass. The exterior glass faces the outside of building. The interior glass faces the inside of room. The Transparent Solar Cell Panel is attached on the exterior glass in the isolated glass unit IGU. The transparent Multimedia Window is attached on the interior glass in the isolated glass unit IGU. As shown in FIG. 1M1, the transparent solar panel is attached to the exterior transparent support such as glass or flexible plastics. As shown in FIG. 1M2, the transparent LCD/LED/OLED Flat Panel/etc and Electrochromic are attached to the exterior transparent support such as glass or flexible plastics. As shown in FIG. 1N1, the air 402, 403 doesn't flow through the channel between two glasses. The bladeless turbofan 40 is located at the corner of IGU. The IGU is completely isolated and filled with the clean inert gas. The IGU is to use the isolation of double window to keep the room temperature to save the energy. It is impossible to clean up the dust inside the IGU. Therefore, the IGU is completely isolated and filled with the inert gas. The air will flow through the tube inside the frame and will not flow

through the channel between the two glasses of the window. As shown in FIG. 1N2, for the low frequency wireless charging system, the wireless charge uses the current loop **412**, **413** embedded in the Frame of IGU. The magnetic field **422** and **423** oscillates to charge the wireless charger. As shown in FIG. 1N3, for the high frequency charging system, the wireless charge uses the Antenna embedded in the Frame of IGU. The chip **432** drives the antenna **433** to emit the EM wave to charge the wireless charger.

**[0121]** FIG. 1B is the architecture of Smart Window for the Smart Home. The Smart Window of Smart Home includes the multimedia iPindow and Telephone iPindow to be the core. The self-sustained iPindow, is constituted of the core of iPindow, Solar Panel iPindow, Battery-type iPindow and Lighting iPindow, etc. The Smart Window of Smart Home further comprises the options of Ventilating iPindow, Turbofan iPindow, Humidity iPindow, Thin-Film Battery iPindow and other functions iPindow, etc. During night, the backlight **105** serves as the backlight for the LCD/LED/ OLED/TV/FlatPanel Multimedia Panel **103**. The antenna **30** and power amplifier **31** etc. of the RF/wireless circuits provide the wireless, internet, remote access and control for the smart windows with the multimedia panel **103**.

**[0122]** The solar panel **10** is transparent and facing outside. The transparent multimedia panel **103** is facing inside room and controlled by host. In the open mode, the multimedia panel **103** is transparent having no blockage of the window view. In the shut mode, the window is blackout. In the open mode, the electrochromic panel has no voltage and the LCD multimedia panel is applied with full voltage. In the shut mode, the electrochromic panel is applied with voltage and the LCD multimedia panel has no voltage.