# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2023/0040543 A1 Campos et al.

# (43) **Pub. Date:**

## Feb. 9, 2023

## (54) SYSTEMS AND METHODS FOR COHERENT OPTICS IN AN ACCESS NETWORK

(71) Applicant: CABLE TELEVISION LABORATORIES, INC., LOUISVILLE, CO (US)

(72) Inventors: Luis Alberto Campos, Superior, CO (US); Zhensheng Jia, Superior, CO (US); Matthew D. Schmitt, Pleasanton,

(21) Appl. No.: 17/937,572

(22) Filed: Oct. 3, 2022

## Related U.S. Application Data

- (63) Continuation of application No. 16/370,873, filed on Mar. 29, 2019, now Pat. No. 11,476,949.

- (60) Provisional application No. 62/650,079, filed on Mar. 29, 2018, provisional application No. 62/805,509, filed on Feb. 14, 2019.

### **Publication Classification**

Int. Cl. (51)H04B 10/63 (2006.01)H04B 10/61 (2006.01)H04J 14/02 (2006.01)H04L 12/28 (2006.01)H04B 10/27 (2006.01)H04B 10/40 (2006.01)H04B 10/516 (2006.01)H04J 14/06 (2006.01)

(52) U.S. Cl.

CPC ...... H04B 10/63 (2013.01); H04B 10/6164 (2013.01); H04B 10/61 (2013.01); H04J 14/02 (2013.01); H04L 12/2885 (2013.01); H04B 10/27 (2013.01); H04B 10/40 (2013.01); H04B 10/516 (2013.01); H04B 10/616 (2013.01); **H04J 14/06** (2013.01)

#### (57)ABSTRACT

A communication network includes a coherent optics transmitter, a coherent optics receiver, an optical transport medium operably coupling the coherent optics transmitter to the coherent optics receiver, and a coherent optics interface. The coherent optics interface includes a lineside interface portion, a clientside interface portion, and a control interface portion.

FIG. 1A

FIG. 1B

FIG. 2

FIG. 3

FIG. 5

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 15

FIG. 16

FIG. 17

FIG. 19

FIG. 20

FIG. 22

FIG. 23

FIG. 24

FIG. 27

FIG. 28

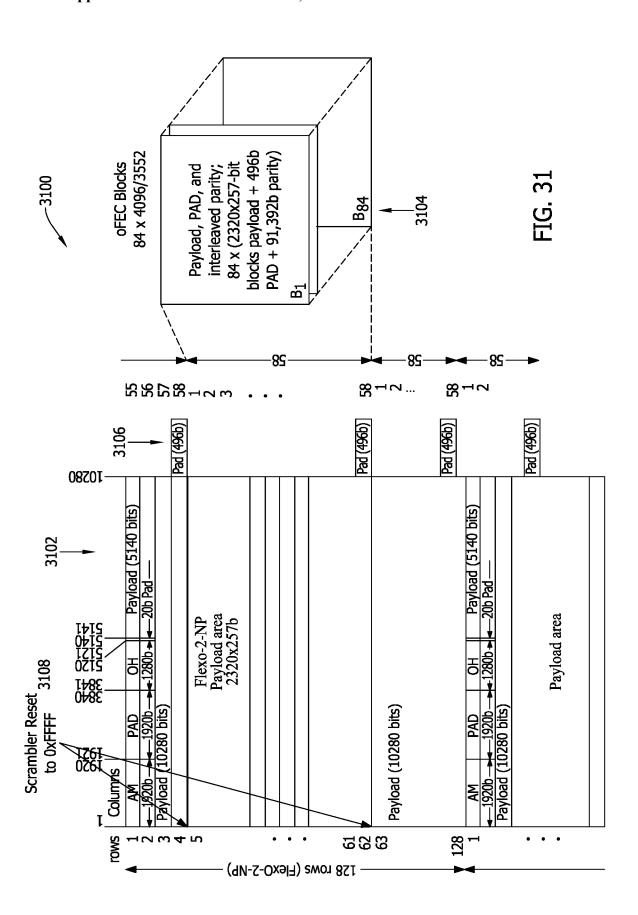

FIG. 29

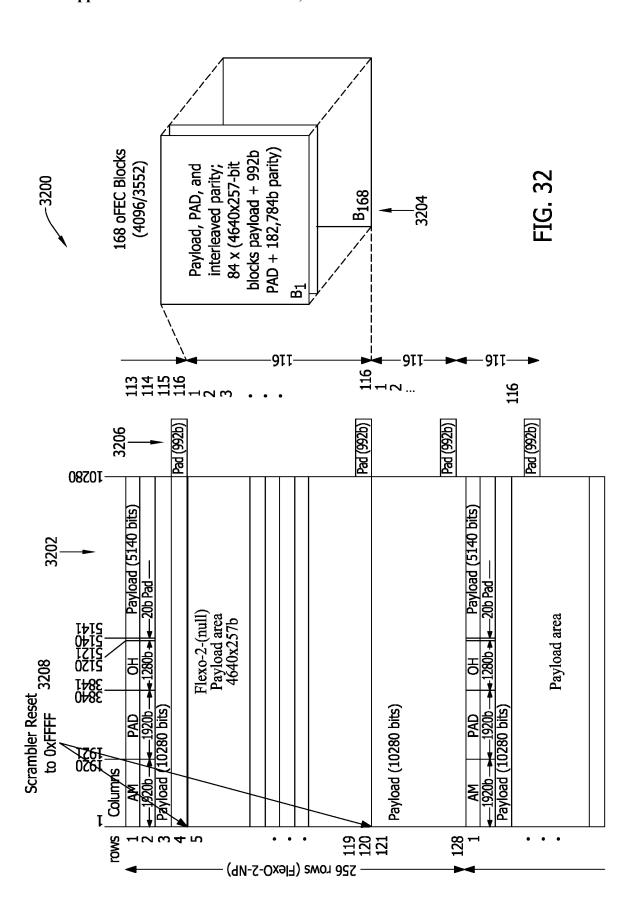

FIG. 30

FIG. 35

FIG. 37

FIG. 38

FIG. 41

FIG. 43

FIG. 47

FIG. 49

FIG. 50

FIG. 51

5200

FIG. 52

FIG. 53

# SYSTEMS AND METHODS FOR COHERENT OPTICS IN AN ACCESS NETWORK

# CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of U.S. patent application Ser. No. 16/370,873, filed Mar. 29, 2019, which application claims the benefit of and priority to U.S. Provisional Patent Application Ser. No. 62/650,079, filed Mar. 29, 2018, and to U.S. Provisional Patent Application Ser. No. 62/805,509, filed Feb. 14, 2019, all of which are incorporated herein by reference in their entireties.

## BACKGROUND

[0002] The field of the disclosure relates generally to communication networks, and more particularly, to access networks capable of transporting signals according to one or more network protocols.

[0003] Most network operators have very limited fiber available between the headend (HE)/hub and the fiber node to use for data and video services, often only just 1-2 fiber strands to serve groups of fiber nodes. With end users demanding more bandwidth to the home, operators need a strategy on how to increase capacity in the access network. One such strategy involves adding more fiber between the HE/hub and the fiber node, but retrenching is costly and time consuming, so return on investment (Rol) considerations make this option unattractive; a solution that more efficiently re-uses the existing infrastructure would be preferred. Accordingly, it has been proposed to use existing infrastructures to meet the bandwidth demand, thereby avoiding retrenching costs, through use of point-to-point (P2P) coherent optics along with wavelength division multiplexing (WDM) in the access network.

[0004] Coherent optics technology is becoming common in the subsea, long-haul, and metro networks, but has not yet been applied to access networks due to the relatively high cost of the technology for such applications. However, it is desirable to develop cost-effective coherent optics technology applications for the cable access network because (i) the distances from the HE/hub to the fiber node are much shorter in the access network in comparison with other types of networks, (ii) the access network is always a P2P architecture, and (iii) fixed-wavelength optical passives may be utilized. It is therefore desirable to provide coherent optics systems and methods for the access network realize a larger margin for adding more compact wavelengths, improved resulting signal-to-noise ratios (SNR).

[0005] By adapting coherent optics technology to the access network, some of the modules used in other networks (e.g., to conduct distortion compensation, nonlinear compensation, and error correction) may be eliminated, simplified, and/or implemented using components with relaxed requirements, thereby resulting in significant cost savings for a P2P coherent optic link implementation. Additionally, the capabilities, performance, and features of access network transceivers in particular may be further relaxed with respect to optical output power level, transmitter wavelength capability, amount of fiber chromatic dispersion compensation, and transmitter optical-signal-to-noise ratio (OSNR), which would still further lower the design costs and enable use of lower cost components in the access networks.

## **SUMMARY**

[0006] In an embodiment, a communication network includes a coherent optics transmitter, a coherent optics receiver, an optical transport medium operably coupling the coherent optics transmitter to the coherent optics receiver, and a coherent optics interface. The coherent optics interface includes a lineside interface portion, a clientside interface portion, and a control interface portion.

## **BRIEF DESCRIPTION**

[0007] These and other features, aspects, and advantages of the present disclosure will become better understood when the following detailed description is read with reference to the accompanying drawings in which like characters represent like parts throughout the drawings, wherein:

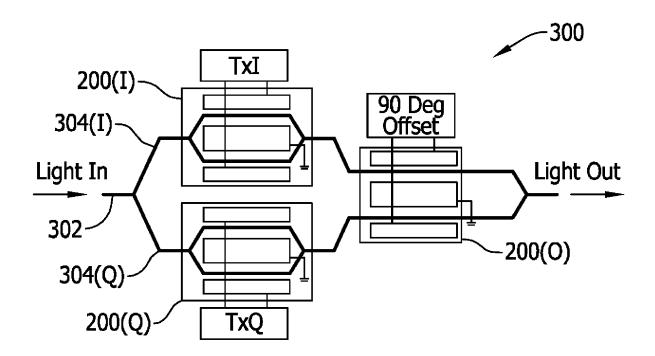

[0008] FIG. 1A depicts an emission spectrum for a distributed feedback laser diode.

[0009] FIG. 1B depicts an emission spectrum for an external cavity laser diode.

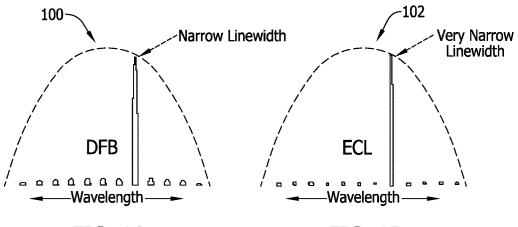

$\ensuremath{[0010]}$  FIG. 2 is a schematic illustration of an electro-optic modulator.

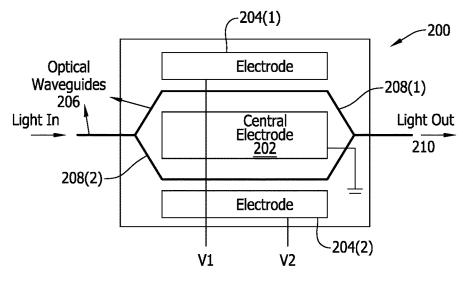

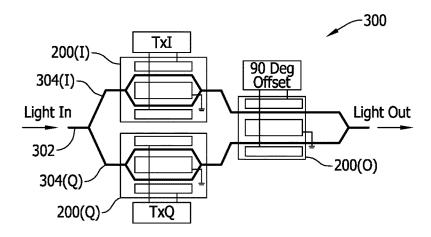

[0011] FIG. 3 is a schematic illustration of an IQ modulator structure utilizing two of the electro-optic modulators depicted in FIG. 2.

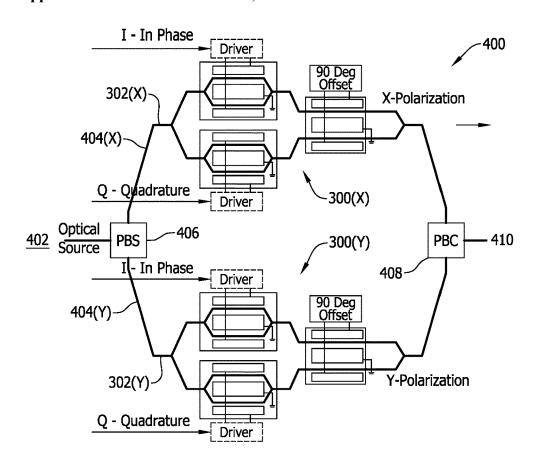

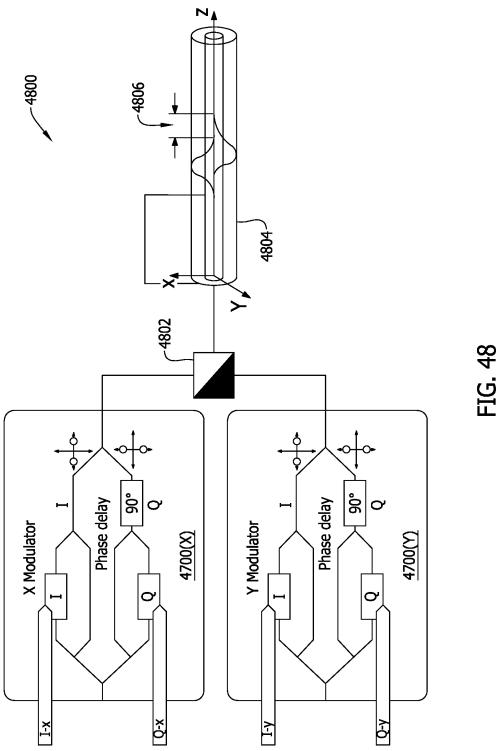

[0012] FIG. 4 is a schematic illustration of a dual polarization coherent IQ modulator.

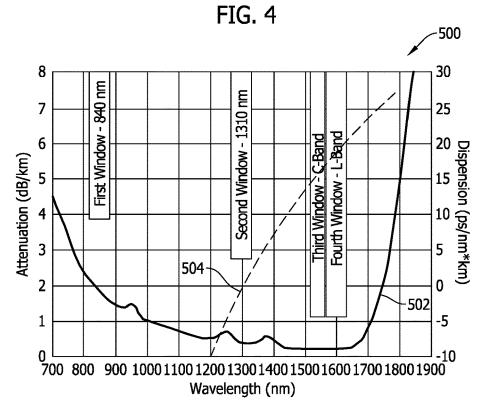

[0013] FIG. 5 is a graphical illustration of a comparative plot of attenuation with dispersion.

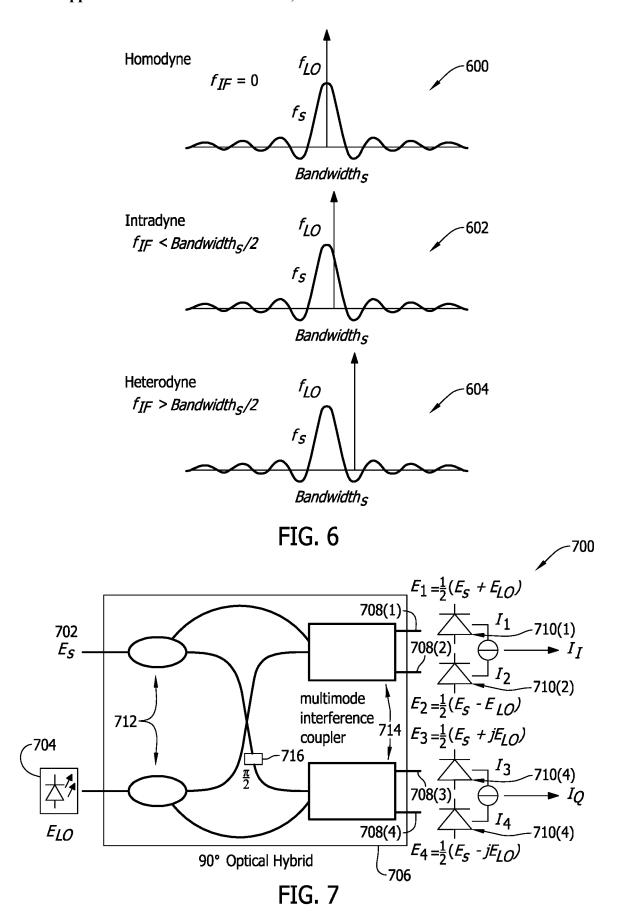

[0014] FIG. 6 is a graphical illustration of comparative plots of respective coherent detection schemes.

[0015] FIG. 7 is a schematic illustration of a phase diversity coherent receiver.

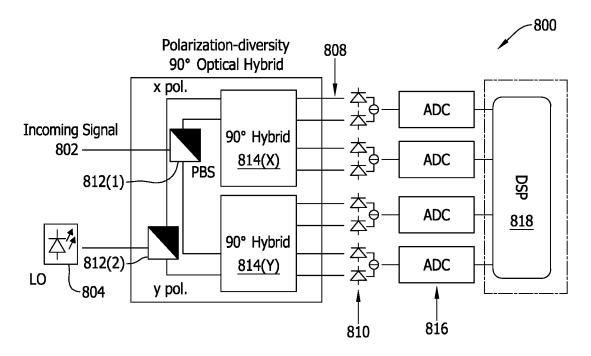

[0016] FIG. 8 is a schematic illustration of a phase and polarization diversity coherent receiver.

[0017] FIG. 9 depicts a digital signal process.

[0018] FIG. 10 is a schematic illustration of a transceiver having a dual optical interface structure.

[0019] FIG. 11 is a schematic illustration of a transceiver having a single optical interface structure.

[0020] FIG. 12 is a functional schematic illustration of a transmitter.

[0021] FIG. 13 is a functional schematic illustration of a receiver.

[0022] FIGS. 14A-B are graphical illustrations depicting comparative encoding plots.

[0023] FIG. 15 is a schematic illustration depicting an exemplary symbol stream architecture.

[0024] FIG. 16 is a schematic illustration depicting an exemplary codeword architecture.

[0025] FIG. 17 is a schematic illustration depicting an exemplary block subdivision.

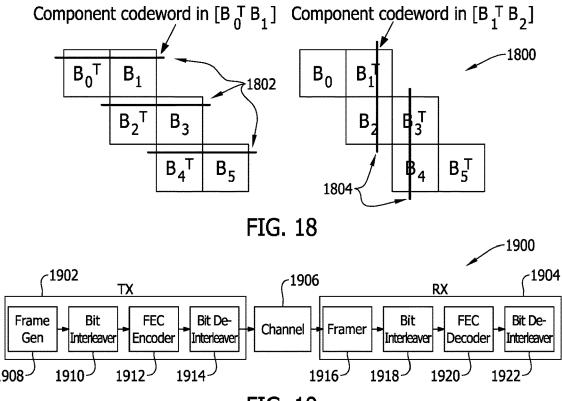

[0026] FIG. 18 is a schematic illustration depicting an exemplary staircase coding scheme.

[0027] FIG. 19 is a schematic illustration of an exemplary error decorrelator.

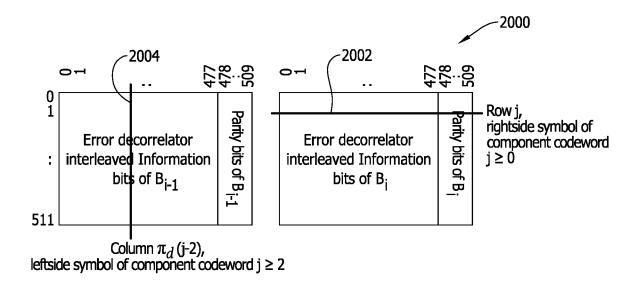

[0028] FIG. 20 is a schematic illustration depicting an exemplary staircase code architecture.

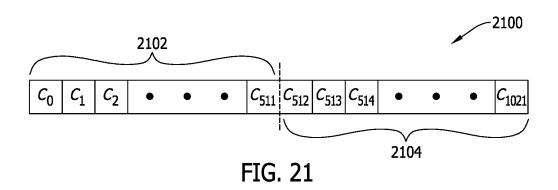

[0029] FIG. 21 is a schematic illustration depicting an exemplary component codeword.

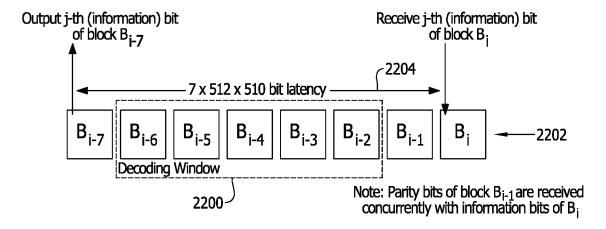

[0030] FIG. 22 is a schematic illustration depicting an exemplary staircase decoding window for a series of blocks.

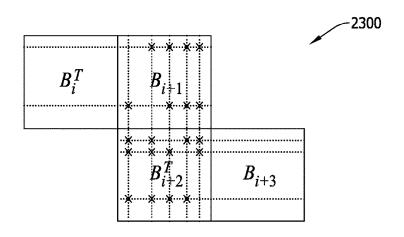

[0031] FIG. 23 is a schematic illustration depicting a non-correctable stall error pattern for a staircase coding scheme.

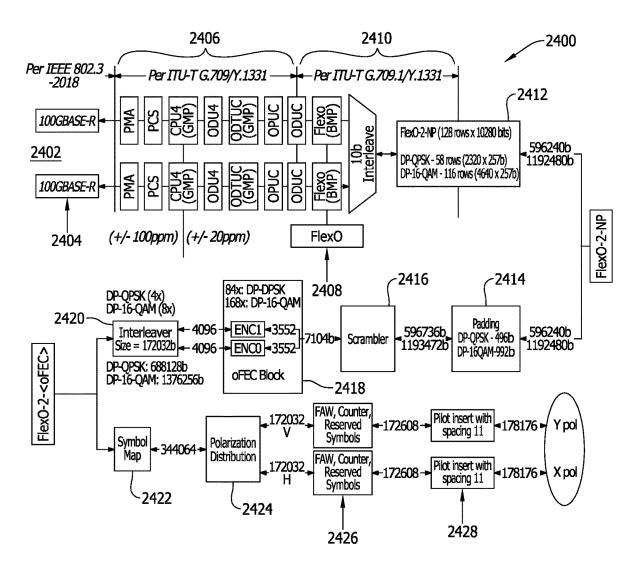

[0032] FIG. 24 is a schematic illustration depicting a client side adaptation process.

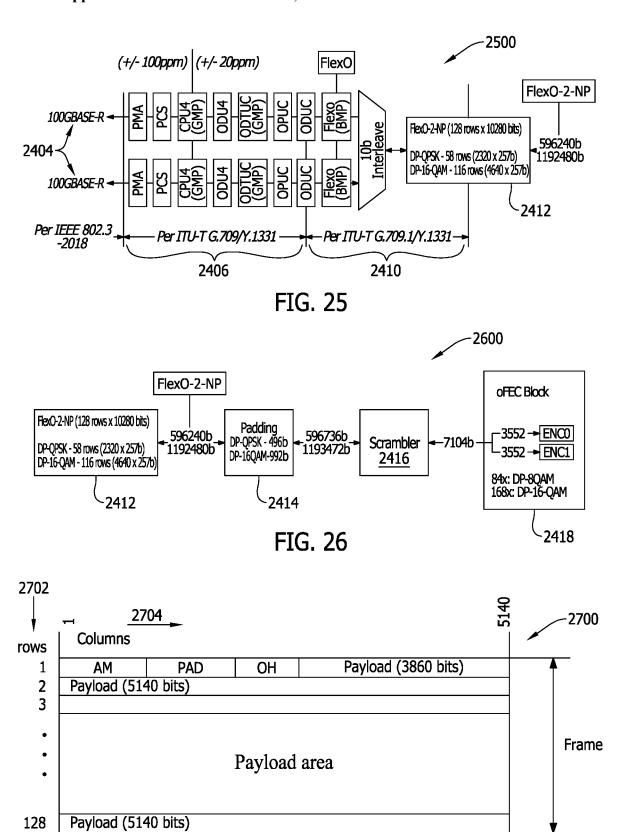

[0033] FIG. 25 is a schematic illustration depicting a framing and mapping subprocess of the process depicted in FIG. 24.

[0034] FIG. 26 is a schematic illustration of an encoding subprocess of the process depicted in FIG. 24.

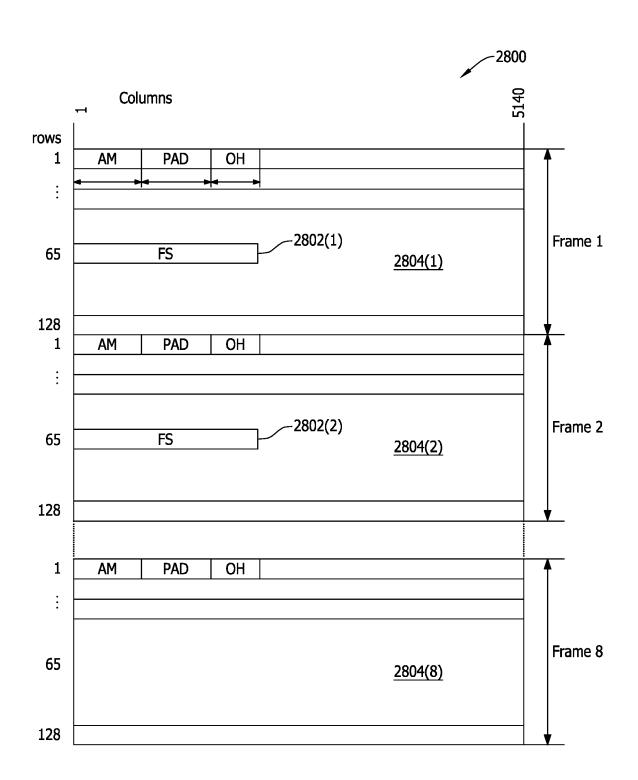

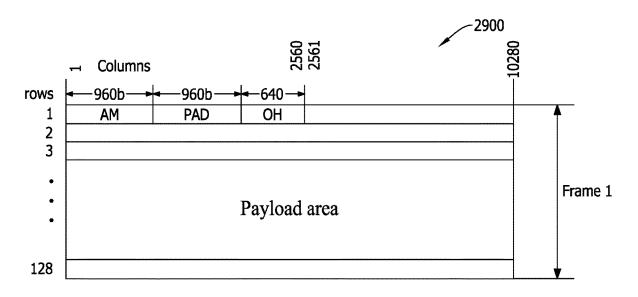

[0035] FIG. 27 is a schematic illustration of an exemplary frame structure.

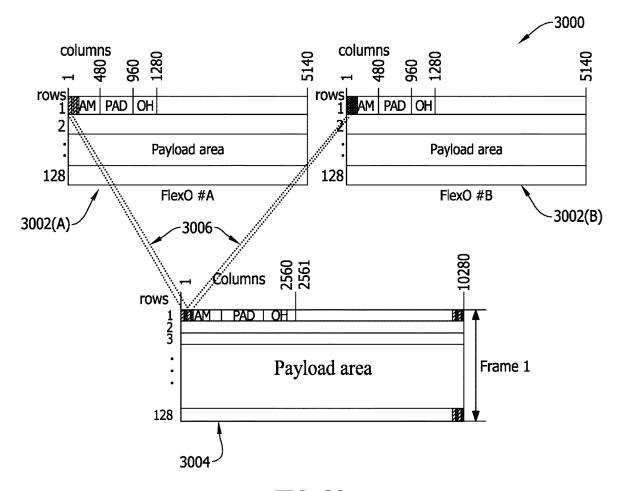

[0036] FIG. 28 is a schematic illustration of an exemplary multi-frame format structure.

[0037] FIG. 29 is a schematic illustration of an exemplary frame structure.

[0038] FIG. 30 is a schematic illustration of an exemplary interleaved frame structure.

[0039] FIG. 31 is a schematic illustration of an exemplary block mapping scheme.

[0040] FIG. 32 is a schematic illustration of an exemplary block mapping scheme.

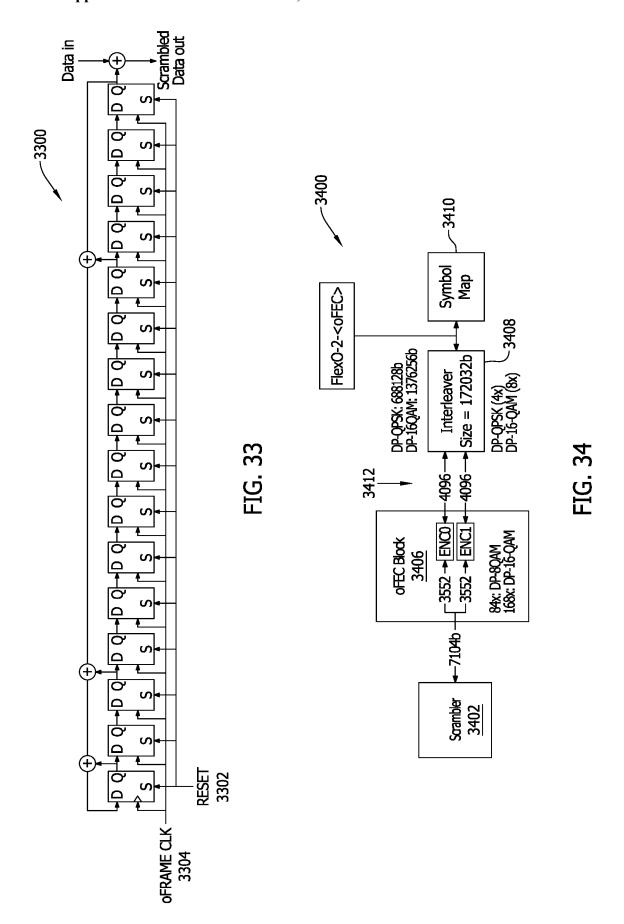

[0041] FIG. 33 is a schematic illustration of an exemplary frame synchronous scrambler.

[0042] FIG. 34 is a schematic illustration of an exemplary encoding and interleaving unit.

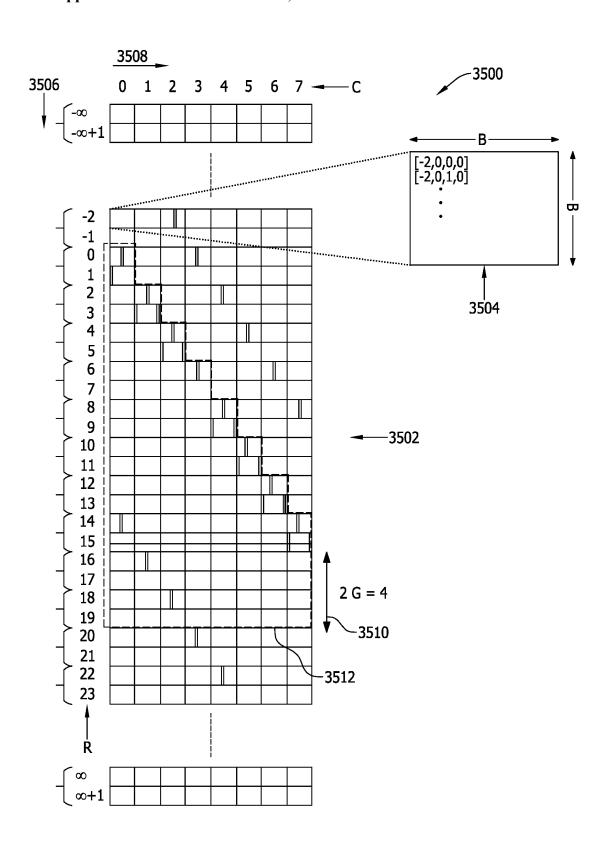

[0043] FIG. 35 depicts an exemplary open forward error correction structure.

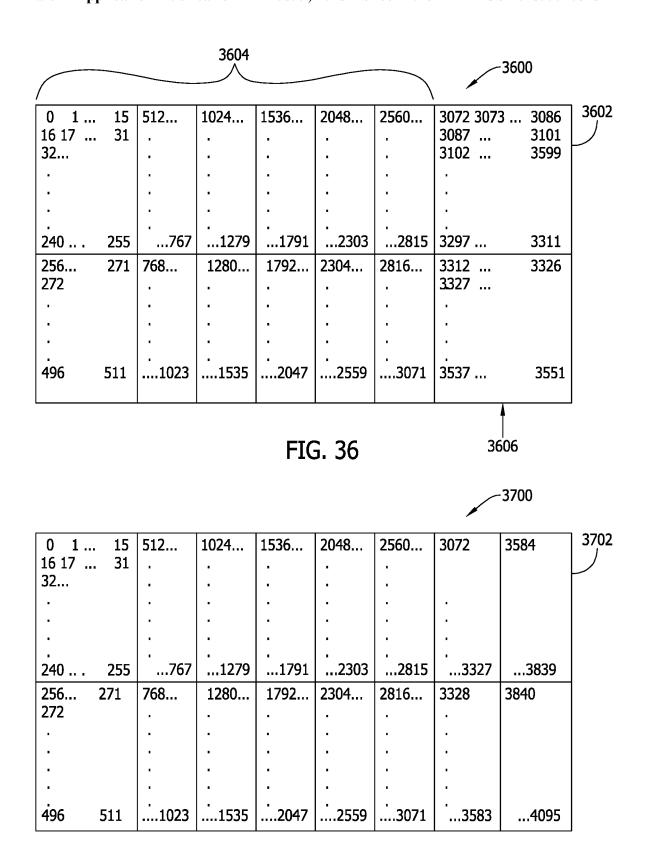

[0044] FIG. 36 depicts an exemplary bit sequencing scheme.

[0045] FIG. 37 depicts an exemplary bit numbering scheme.

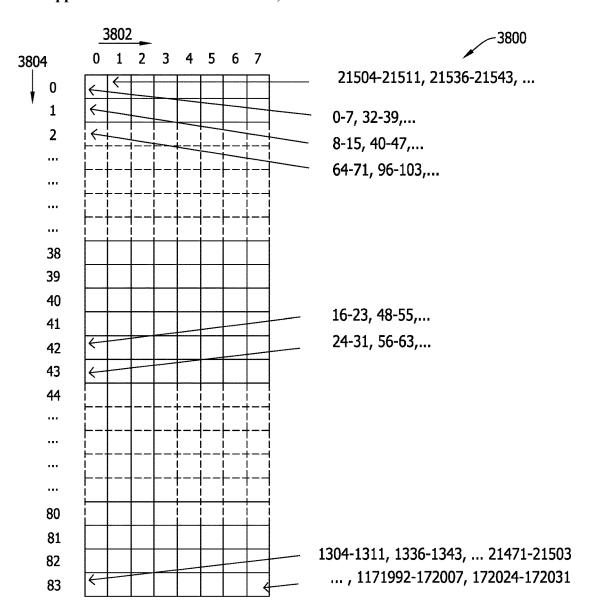

[0046] FIG. 38 depicts an exemplary inter-block interleaving structure.

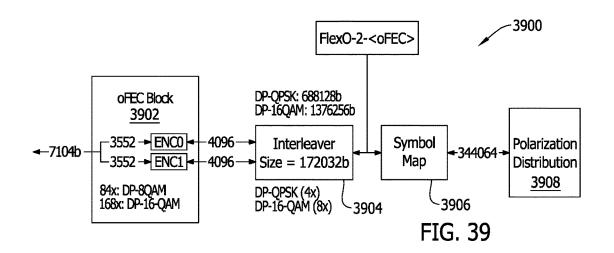

[0047] FIG. 39 is a schematic illustration of an exemplary symbol mapping and polarization distribution process.

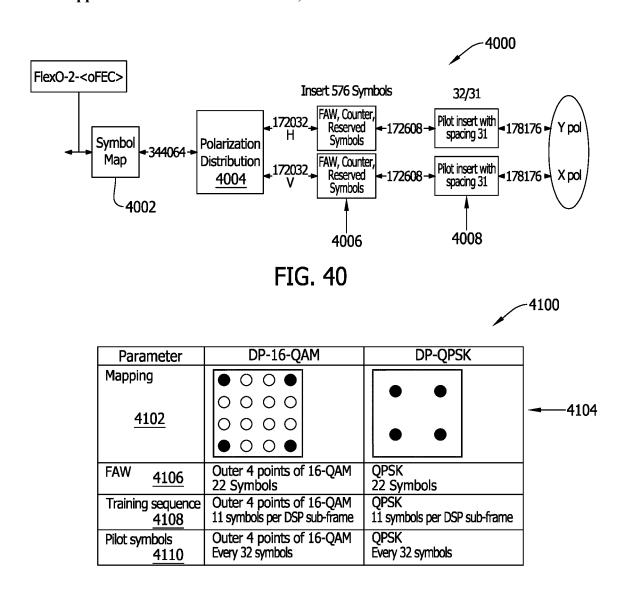

[0048] FIG. 40 is a schematic illustration of an exemplary framing process.

[0049] FIG. 41 is a schematic illustration of an exemplary distribution table for a super-frame/sub-frame structure.

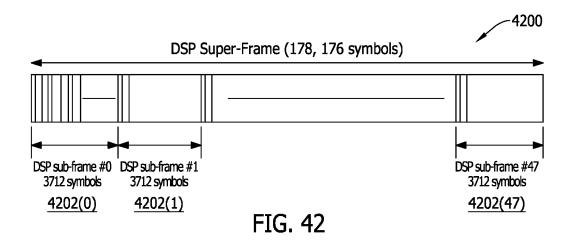

[0050] FIG. 42 depicts an exemplary super-frame structure.

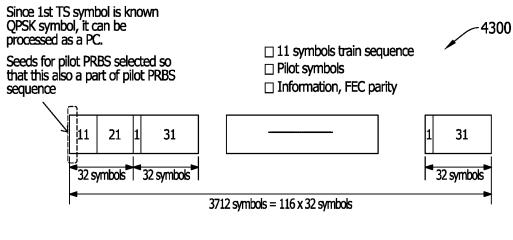

[0051] FIG. 43 depicts exemplary sub-frames of the super-frame structure depicted in FIG. 42.

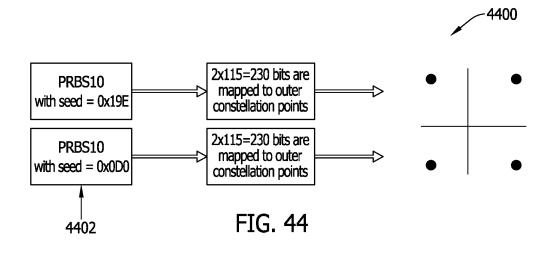

[0052] FIG. 44 depicts an exemplary pilot sequence mapping scheme.

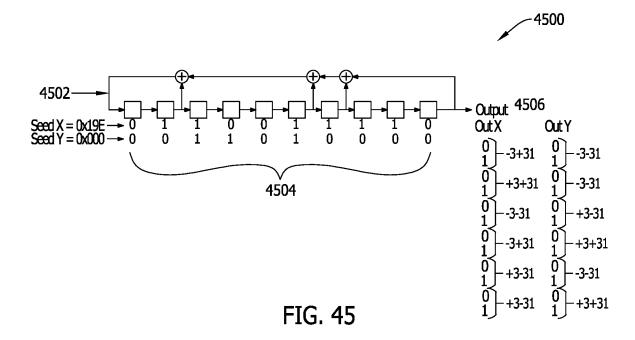

[0053] FIG. 45 is a schematic illustration of an exemplary pilot seed sequencing process.

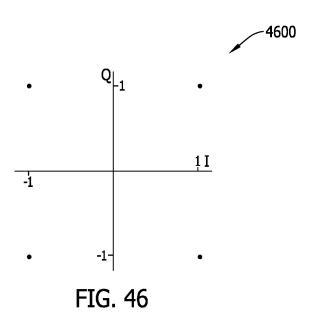

[0054] FIG. 46 is a graphical illustration of an exemplary constellation.

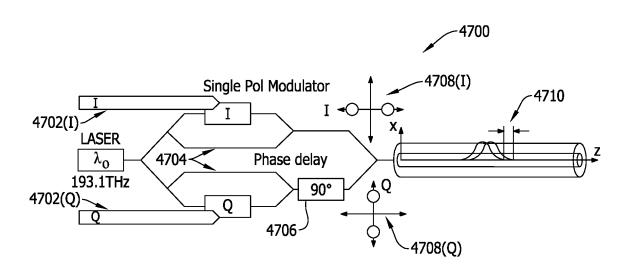

[0055] FIG. 47 is a schematic illustration of an exemplary single polarization modulator.

[0056] FIG. 48 is a schematic illustration of an exemplary dual polarization modulator.

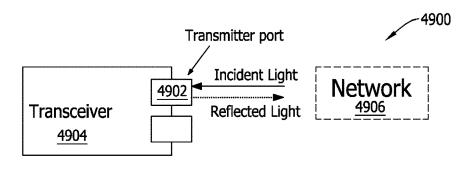

[0057] FIG. 49 is a schematic illustration depicting an exemplary transmitter reflectance effect.

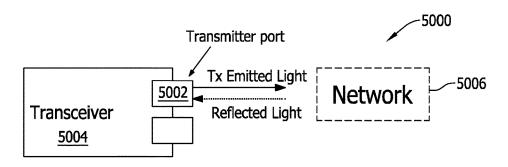

[0058] FIG. 50 is a schematic illustration depicting an exemplary optical return effect.

[0059] FIG. 51 is a graphical illustration depicting a differential group delay plot.

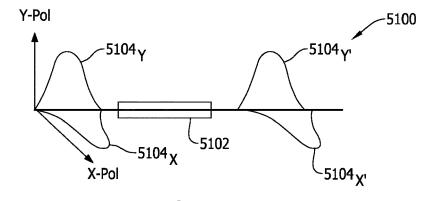

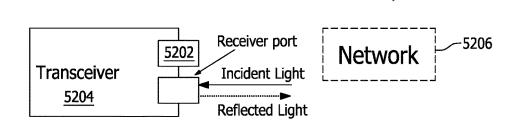

[0060] FIG. 52 is a schematic illustration depicting an exemplary receiver reflectance effect.

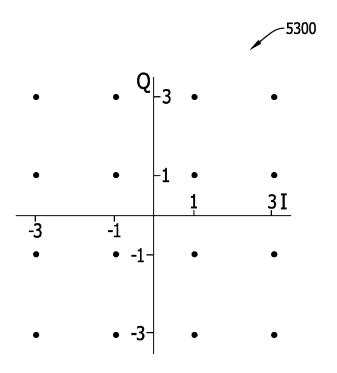

[0061] FIG. 53 is a graphical illustration of an exemplary constellation.

[0062] Unless otherwise indicated, the drawings provided herein are meant to illustrate features of embodiments of this disclosure. These features are believed to be applicable in a wide variety of systems including one or more embodiments of this disclosure. As such, the drawings are not meant to include all conventional features known by those of ordinary skill in the art to be required for the practice of the embodiments disclosed herein.

### DETAILED DESCRIPTION

[0063] In the following specification and claims, reference will be made to a number of terms, which shall be defined to have the following meanings.

[0064] The singular forms "a," "an," and "the" include plural references unless the context clearly dictates otherwise

[0065] "Optional" or "optionally" means that the subsequently described event or circumstance may or may not occur, and that the description includes instances where the event occurs and instances where it does not.

[0066] As used herein, unless specified to the contrary, "modem termination system," or "MTS" may refer to one or more of a cable modem termination system (CMTS), an optical network terminal (ONT), an optical line terminal (OLT), a network termination unit, a satellite termination unit, and/or other termination devices and systems. Similarly, "modem" may refer to one or more of a cable modem (CM), an optical network unit (ONU), a digital subscriber line (DSL) unit/modem, a satellite modem, etc.

[0067] As used herein, the term "database" may refer to either a body of data, a relational database management system (RDBMS), or to both, and may include a collection of data including hierarchical databases, relational databases, flat file databases, object-relational databases, object oriented databases, and/or another structured collection of records or data that is stored in a computer system.

[0068] Furthermore, as used herein, the term "real-time" refers to at least one of the time of occurrence of the associated events, the time of measurement and collection of predetermined data, the time for a computing device (e.g., a processor) to process the data, and the time of a system response to the events and the environment. In the embodiments described herein, these activities and events occur substantially instantaneously.

**[0069]** As used herein, the term "transceiver," unless specified otherwise, refers to a P2P coherent optics transceiver, having a coherent optics transmitting portion and a coherent optics receiving portion. In some instances, the transceiver may refer to a specific device under test (DUT) for several of the embodiments described herein.

[0070] Approximating language, as used herein throughout the specification and claims, may be applied to modify any quantitative representation that could permissibly vary without resulting in a change in the basic function to which it is related. Accordingly, a value modified by a term or terms, such as "about," "approximately," and "substantially," are not to be limited to the precise value specified. In at least some instances, the approximating language may correspond to the precision of an instrument for measuring the value. Here and throughout the specification and claims, range limitations may be combined and/or interchanged; such ranges are identified and include all the sub-ranges contained therein unless context or language indicates otherwise.

[0071] The embodiments described herein provide innovative access network architectures and processes that are particularly useful for the growing access network trends in the field. The present systems and methods leverage coherent optics, and particularly with respect to P2P systems, to significantly improve the cable access network and access networks in general. The embodiments herein enable the development and utilization of interoperable transceivers using coherent optical technology over P2P communication links. The present embodiments include new and improved specifications for the optical physical layer requirements for coherent optical transceivers.

[0072] The following embodiments are described with respect to transceivers operating at 100 and 200 gigabits per second (Gbps), however, the person of ordinary skill in the art will appreciate that these operating parameters are described by way of example, and not in a limiting sense. The principles herein are applicable to coherent optics systems operating at different transmission speeds, and particularly as the demand for increased speed and bandwidth continues to grow. The following examples are also described with respect to exemplary fiber links up to approximately 40, however, the person of ordinary skill in the art will further appreciate that the present techniques will support links of up to 80 km, 120 km, and greater in some circumstances.

[0073] The following embodiments include improvements to the P2P coherent optics specifications, and particularly with respect to the physical (PHY) layer. The present embodiments are described with respect to functional operation and interfaces among various network components, and with particular focus on transceiver operation related to the PHY layer, as well as transceiver operation that is not specific to the PHY layer. The present systems and methods further provide improved processes for framing, forward error correction (FEC), and symbol mapping for compliant hardware operating at various transmission speeds and modulations (e.g., 100G QPSK, 200G QPSK, 200G 16QAM).

[0074] The present systems and methods are applicable to several coherent optics system components, including the coherent transmitter and the coherent receiver. In an embodiment, the transceiver includes both a coherent transmitter and a coherent receiver, that is, hardware capabilities for both coherent transmission and coherent reception. In the exemplary embodiment, the coherent transmitter includes at least two key components: (i) one or more optical sources; and (ii) an external modulator.

[0075] In some embodiments, the optical source may include a laser diode implemented from a semiconductor junction operated in forward bias mode. Electrons in the junction transition from a higher to a lower energy state, and a photon is emitted having energy equal to the difference in electron energy states, which is also referred to as spontaneous light emission. In a laser diode, reflective facets or mirrors may be implemented such that the generated photons bounce back and forth, stimulating the emission of more photons, which is also referred to as stimulated emission, or lasing, and results in light emission at higher intensity levels and with a high degree of coherence. The mirrors or facets on opposite sides of the active region formed by the junction create an optical cavity. The geometry of the cavity, along with the range in energy levels generated by the change of state in the junction, will determine one or more dominant resonant wavelengths transmitted by the laser diode.

[0076] It is important, in optical systems, to be able to maintain operating characteristics. In the WDM environment, the optical system is configured to reliably maintain the transmitted wavelength at a desired value. Some optical systems incorporate thermo-electric-cooling capabilities to obtain better wavelength control, which adds cost to the optical end devices, but facilitates improved wavelength multiplexing, which further enables some avoidance of the cost of fiber retrenching to add additional capacity.

[0077] FIG. 1A depicts an emission spectrum 100 for a distributed feedback (DFB) laser diode. FIG. 1B depicts an emission spectrum 102 for an external cavity laser (ECL) diode. In an exemplary embodiment, emission spectra 100, 102 are representative of coherent laser structures that may be implemented in the access environment. That is, light emitted by lasers in the access environment may not be strictly monochromatic; different linewidths may be realized according to the individual structure and characteristics on the laser. The linewidth of the emitted light wavelength may have a significant impact on the speed, dynamic range, coherence, and coexistence among optical carriers communicated on the same fiber. Generally, optical sources that can be confined to narrow spectra are preferable when the optical source is sharing the fiber spectrum with other optical sources (e.g., WDM). A narrower linewidth limits the energy that will spill into other channels.

[0078] Coexistence in the cable access network is an important consideration. Most cable operators run a centralized network that includes headends (HEs), hubs, and fiber nodes. This type of centralized architecture was originally configured to transmit downstream video to cable subscribers, but and since evolved into a data-over-cable network as defined by the Data over Cable Service Interface Specification (DOCSIS) that introduced the cable modem termination system (CMTS) in the headend and the cable modem (CM) at customer premises. The centralized architecture also originally provided internet access and video delivery on the same coaxial cable. Video EdgeQAM (EQAM) was later introduced at the HE/Hub to enable digital video, video-ondemand (VOD), and switched-digital-video. EQAM evolved to support the modulation of both MPEG video and DOCSIS data onto the wire using a Modular Headend Architecture (MHA-TR). The CMTS and EQAM continued to evolve into the converged cable access platform (CCAP) that provided higher densities of EQAM and CMTS combined together into the same chassis; other technologies like Ethernet optics and Ethernet passive optical network (EPON) theoretically may share the same chassis as well. As a result, the CCAP enabled data, voice, and video to be handled over IP before being converted to RF or optical signals.

[0079] The external modulator component of the transceiver transmitter typically will use one of two types of external modulation approaches: (1) electro-absorption effect; and (2) interferometry. In the first approach, the electro-absorption effect controls the degree of attenuation through an optical transmission path. In the second approach, interferometry which changes the light amplitude by adjusting the relative phase on two split optical branches. An exemplary modulator structure for implementing the interferometric approach is described below with respect to FIG. 2.

[0080] FIG. 2 is a schematic illustration of an electro-optic modulator 200. In an embodiment, modulator 200 represents a Mach-Zehnder intensity modulator structure, also referred to as a Mach-Zehnder interferometer or a Mach-Zehnder Modulator (MZM). Modulator 200 includes a central electrode 202 and two outer electrodes 204. Light entering modulator 200 is split by optical waveguides 206 into two separate optical branches 208 before recombining at an output 210 modulator 200. In exemplary operation, the interferometric approach changes the light amplitude by adjusting the relative phase on the two split optical branches 208(1), 208(2), respectively, such that, after recombination, the separately adjusted optical portions may add destructively (i.e., 180 degrees out of phase) with no light leaving modulator 200, or may add constructively (i.e., in phase) with maximum optical intensity at output 210. In the exemplary embodiment depicted in FIG. 2, optical pathways are shown in bold, in contrast to electrical pathways.

[0081] FIG. 3 is a schematic illustration of an IQ modulator structure 300 utilizing two of electro-optic modulators 200, FIG. 2. Coherent optics enables the implementation of techniques for utilizing both the modulation and phase of light, as well as two different light polarizations, to transmit multiple bits per symbol over fiber transport media using, for example, modulation formats such as phase shift keying (e.g., QPSK) and/or quadrature-amplitude-modulation (QAM). The coherent modulation formats have an in-phase (I) amplitude component and a quadrature phase (Q) amplitude component.

[0082] In an embodiment, structure 300 represents an electro-optic IQ modulator including at least two MZMs, e.g., a first MZM for the I path (e.g., modulator **200**(I)), and a second MZM for the Q path (e.g., modulator 200(Q)). More specifically, an input optical signal is first split, by outer optical waveguides 302, into two separate phaseshifted paths 304 prior to input into modulators 200(I), 200(Q). That is, phase-shifted paths 304(I), 304(Q) are phase-shifted to be at 90 degrees apart, which enables the first and second MZMs (200(I), 200(Q), respectively) to separately operate on orthogonal components of the optical signal. Accordingly, in the coherent system, instead of modulating only the amplitude of light, both amplitude and phase may be modulated by structure 300, which is sometimes also referred to as a nested IO MZM. In some embodiments, structure 300 may further include a third offset modulator 200(O) for recombining the separate phaseshifted paths 304(I), 304(Q).

[0083] FIG. 4 is a schematic illustration of a dual polarization coherent IQ modulator 400. In the exemplary embodiment illustrated in FIG. 4, modulator 400 utilizes two IQ modulator structures 300, FIG. 3, to separately process respective X- and Y-polarizations of a transmitted laser signal from an optical source 402. In this example, the laser signal from optical source 402 is separated into an X-polarization path 404(X) and a Y-polarization path 404(Y) by a polarization beam splitter (PBS) 406 for independent IQ modulation of each polarization by IQ modulator structures 300(X) and 300(Y), respectively. Each IQ modulator structure 300 then operates, from its respective optical waveguide 302, in a substantially similar fashion to that described above with respect to FIG. 3, until reaching a polarization beam combiner (PBC) 408, which from which a combined dual-polarized signal is generated. In this manner, the transport capacity is effectively double that of the single IQ modulator structure 300 shown in FIG. 3.

[0084] Nevertheless, performance of systems residing and coexisting within the fiber strand may be affected by the optical channel limitations of the fiber access environment. For example, several different fiber-related impairments are known to impact the performance. Some such impairments are dependent on the fiber length, whereas others are dependent on the geometry, material, wavelength, bandwidth, and/or optical power level of the fiber.

[0085] Dispersion is a known fiber length-dependent impairment. Dispersion occurs when different portions of the optical signal travel at different speeds within the optical fiber. As a consequence of this effect, an optical signal may experience spreading in time. Different types of dispersion include chromatic dispersion, waveguide dispersion, modal dispersion, and polarization mode dispersion. Chromatic dispersion, or material dispersion, is caused by the changing of the refractive index with the optical frequency. Waveguide dispersion relates to how well the index of refraction represents an ideal waveguide throughout the fiber length, with differences from the ideal waveguide causing dispersion. Modal dispersion occurs when different propagating modes are present in fiber. In the cable access environment, for example, because use of single mode fiber (SMF) is common, fiber modal dispersion is not a present factor, and waveguide dispersion is considered negligible in comparison with chromatic dispersion. Chromatic dispersion, or Dispersion ( $\lambda$ ), may be approximated according to:

Dispersion (

$$\lambda$$

) =  $\frac{S_0}{4} * \left[ \lambda - \frac{\lambda_0^4}{\lambda^3} \right] ps/(nm * km),$

[0086] where  $\lambda_0$  is the zero dispersion wavelength (typically 1313 nm for SMF, or within the range of 1302-1322 nm), and  $S_0$  is the dispersion slope at  $\lambda_0$ , which typically is 0.086 ps/(nm<sup>2</sup>\*km), and considered always less than 0.092 ps/(nm<sup>2</sup>\*km) in this example. SMF dispersion variation with respect to wavelength is described further below with respect to FIG. 5.

[0087] FIG. 5 is a graphical illustration of a comparative plot 500 of attenuation with dispersion. In the exemplary embodiment depicted in FIG. 5, an attenuation curve 502 represents the attenuation of the SMF over wavelength, and a dispersion curve 504 represents the dispersion over wavelength. Attenuation in fiber is dependent on the wavelength or frequency. As can be seen along attenuation curve 502, for this exemplary SMF, the attenuation is 0.22 dB/km at a 1550 nm wavelength transmission, and the attenuation is 0.3 dB/km at a 1310 nm wavelength transmission.

[0088] In this example, transmission window that is highly coveted is the C-Band (i.e., 1530 nm-1565 nm), due to its enabled option for amplification, as well as its low loss characteristics. However, in the access network, due to the shorter distances in many use case scenarios, there is no need for amplification. Accordingly, the present systems and methods are particularly suitable for use of the L-Band (i.e., 1565 nm-1625 nm), for which production of erbium-doped fiber amplifiers (EDFAs) in high volume has not yet occurred. Therefore, the advantageous implementations provided herein for the access network will greatly improve the overall transmission with respect to these characteristics. It may be noted, that in the cable environment, the impact of

optical reflections it is often diminished by the use of angle-faceted connectors. That is, the small angle of an angle-faceted, or APC, connector causes a reflected signal to exit the fiber. Nevertheless, splice imperfections may also generate reflections which impact performance.

[0089] Polarization mode dispersion (PMD) occurs when two orthogonal polarizations travel at different speeds, which causes pulse spreading, resulting from random imperfections such as circular asymmetry. The PMD coefficient (in units of ps/√km) is the parameter that specifies PMD characteristics for a particular length of fiber, and the PMD of the fiber is the average value of the differential group delay (DGD). The PMD in single mode fiber ranges from 0.1 ps/vkm to 1 ps/vkm. SMF generally has a PMD <0.1  $ps/\sqrt{km}$ , although in the case of cable, the specification calls for <0.5 ps/√km after cabling. In other use cases, a PMD requirement for non-coherent 10 Gbps Non-Return-to-Zero (NRZ) of <4 ps may be used. For example, a 40 km link would expect to see, at most, a value of  $0.5*\sqrt{40}=3.16$  ps, which would not require compensation. However, at a transmission speed of 40 Gbps, the PMD coefficient requirement is <1 ps/vkm, and in this case, a 40 km link would require compensation. Coherent detection techniques provide a higher tolerance to PMD in comparison with noncoherent detection techniques, and therefore, the present systems and methods would expect higher symbol rates to be achieved with minimal, or no, PMD compensation for the present link distances of the access network. In analog optical links, PMD is not generally considered to be a significant issue, since the modulation bandwidth is about 1

[0090] Nonlinear effects in fiber may be caused by intensity dependence of the refractive index fiber medium, and also by inelastic-scattering effects that are present at very high optical intensity levels. Other nonlinear effects are related to optical amplification systems, but are not addressed in detail with respect to the present access scenario techniques. For example, in relatively shorter fiber distances (e.g., <60 km), inline amplification systems are not a significant consideration. However, the refractive index dependence on optical power is described herein with respect to the present systems and methods. Refractive index effects include, for example, self-phase modulation (SPM), cross-phase modulation (XPM), and four-wave mixing (FWM).

[0091] For SPM, a time-varying signal intensity generates a varying refractive index in a medium with an intensity-dependent refractive index (e.g., fiber). The higher intensity portions of an optical signal traveling through a fiber thus encounter a higher refractive index in comparison with the relatively lower intensity portions of the signal. SPM therefore includes the chirping and dispersion generated by variation in the index of refraction. The optical power level and the length of interaction may also affect the amount of SPM

[0092] XPM is, in principle, considered to be generally the same as SPM. However, in some cases, XPM represents the effect of the intensity-varying index of refraction on other optical carriers that are propagating at the same time as the original signal. As the number of channels increase, the amount of XPM also increases. In a WDM system, XPM converts power fluctuations in a particular channel to phase fluctuations in the other co-propagating channels. XPM is

higher with relatively higher power levels and greater interaction lengths (i.e., longer fiber links).

[0093] FWM is a third order nonlinear effect of susceptibility. In FWM, if three fields propagate at frequencies  $\omega_1$ ,  $\omega_2$ , and  $\omega_3$ , a fourth frequency  $\omega_4$  is generated such that  $\omega_4 = \omega_1 \pm \omega_2 \pm \omega_3$ . FWM is independent of modulation bandwidth, but is dependent on frequency spacing and fiber dispersion. Since dispersion varies with wavelength, the signal waves and the generated waves will experience different group velocities, which destroys capabilities for phase matching of waves, while also lowering the efficiency of power transfer to newly-generated frequencies. Therefore, dispersion-shifted fibers will experience more severe FWM effects than standard SMF. As the group velocity mismatch increases and the channel spacing widens, the FWM effect decreases.

[0094] FIG. 6 is a graphical illustration of comparative plots 600, 602, 604 of respective coherent detection schemes. More particularly, plot 600 represents a homodyne coherent detection scheme for a signal at a frequency  $f_S$  having a baseband intermediate frequency  $f_{IF}$  equal to zero (i.e.,  $f_{IF}$ =0), plot 602 represents an intradyne coherent detection scheme for the signal at a frequency  $f_S$  having the baseband intermediate frequency  $f_{IF}$  less than half of the optical signal bandwidth Bandwidth $_S$  (i.e.,  $f_{IF}$ <Bandwidth $_S$ 2), and plot 604 represents a heterodyne coherent detection scheme the signal at a frequency  $f_S$  having the baseband intermediate frequency  $f_{IF}$  greater than half of the optical signal bandwidth Bandwidth $_S$  (i.e.,  $f_{IF}$ >Bandwidth $_S$ /2).

**[0095]** In a coherent receiver, a local oscillator (LO, at frequency  $\mathbf{f}_{LO}$ ) is known to be used to down-convert the electrical field of the incoming optical signal to the baseband intermediate frequency  $\mathbf{f}_{IF}$ . Coherent detection is thus able to map an entire optical field into the digital domain, thereby enabling the detection of the amplitude, phase, and state of polarization of the signal. Depending on the intermediate frequency, which is defined as  $\mathbf{f}_{IF} = \mathbf{f}_S - \mathbf{f}_{LO}$ , coherent receivers thus fall into the fall into three classes described herein (i.e., homodyne, intradyne, and heterodyne).

[0096] In the following embodiments, intradyne receivers are described, for purposes of illustration but not in a limiting sense, as the exemplary option for 100G coherent systems. In an intradyne receiver, the intermediate frequency  $f_{IF}$  may be selected to fall within the signal band by approximately aligning the LO frequency  $f_{LO}$  with the signal frequency  $f_{S}$ . Intradyne detection allows the detection of both the I and Q components of the received signal, and thus the intradyne receiver is also referred to as a "phase diversity" receiver. In some embodiments, digital phase locking algorithms are implemented to recover the modulation signal from the sampled I and Q components, typically using high-speed analog-to-digital conversion (ADC) and digital signal processing (DSP).

[0097] FIG. 7 is a schematic illustration of a phase diversity coherent receiver 700. In an exemplary embodiment of receiver 700, a light signal 702 ( $E_S$ ) and a continuous-wave LO 704 ( $E_{LO}$ ) are input to a 90° optical hybrid 706, which processes the two inputs 702, 704 into four separate outputs 708 that are received by a respective photodetector 710. In the coherent detection paradigm, the beating product of electric fields of the modulated signal light 702 and the continuous-wave LO 704 result in a lower frequency representation of the signal information which may then be processed electrically.

[0098] To detect both IQ components of input light signal 702, 90° optical hybrid 706 includes a 2×2 optical coupler 712 having a 90° phase shift property between the direct-pass and cross-coupling outputs by way of a multimode interference (MMI) coupler 714. By combining such optical couplers into the configuration illustrated in FIG. 7, together with an additional 90° phase shift 716 in one arm thereof, a detection of real and imaginary parts may be effectively achieved. In an embodiment, balanced detection is introduced into coherent receiver 700 to suppress the DC component and maximize the signal photocurrent. In this example, the respective output IQ photocurrents from balanced photodetectors 710 may be represented as:

$$I_1(t)=I_1(t)-I_2(t)=R\sqrt{P_{\rm S}P_{\rm LO}}\cos\{\varphi_S(t)-\theta_{LO}(t)\};$$

and

$$I_O(t) = I_3(t) - I_4(t) = R\sqrt{P_S P_{LO}} \sin\{(\varphi_{Ss}(t) - (t))\},\$$

[0099] where R is the responsivity of the photodiode,  $P_S$  and  $P_{LO}$  are the power of the optical fields for incoming and LO signals 702 and 704, respectively. Implementation of receiver 700 thereby enables the recovery of both the relevant sine and cosine components. In this example, the phase noise  $\theta_{LO}$  (t) may be estimated as varying with time, and the phase information  $\phi_S(t)$  may be restored through subsequent DSP on the intradyne-detected signal (not shown in FIG. 7).

[0100] FIG. 8 is a schematic illustration of a phase and polarization diversity coherent receiver 800. Receiver 800 is similar to receiver 700, FIG. 7, in several structural and functional effects, and similar elements thereof are referred to by the same labels. For example, in an embodiment of receiver 800, an incoming signal 802 (e.g., polarization multiplexed) and an LO signal 804 are input to a polarization diversity 90° optical hybrid 806, which processes the two inputs 802, 804 into eight separate outputs 808 that are received by eight respective photodetectors 810. In operation of receiver 800, both of incoming signal 802 and LO signal 804 are split, within polarization diversity 90° optical hybrid 806, into two orthogonal polarizations using respective PBS units 812, after which the co-polarized components of incoming signal 802 and LO signal 804 are mixed within two separate  $90^{\circ}$  optical hybrids 814 (e.g., 814(X), 814(Y)) to produce I and Q components for each X and Y polarization. The resulting four IX, QX, IY, QY signals after balancing by photodetectors 810 may then be digitized by respective analog-to-digital converters (ADCs) 816 (or separate ADCs 816, in this example), after which a DSP 818 may further process the converted signals for signal demodulation.

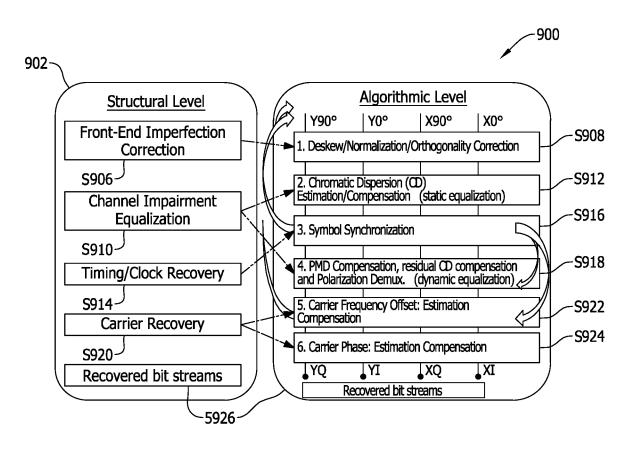

[0101] FIG. 9 depicts a DSP process 900. In an exemplary embodiment, DSP process 900 illustrates DSP functionality in a processor of a digital coherent optical receiver (e.g., DSP 818 of coherent receiver 800, FIG. 8) for a polarization multiplexed QAM signal with respect to a structural level 902 and an algorithmic level 904 of the relevant processor. Respective steps of process 900, unless otherwise described, may be performed in the following order, a different order, or some steps may be performed substantially simultaneously with other steps.

[0102] In the exemplary embodiment, process 900 begins at step S906, in which the four digitized signals input to DSP 818 (i.e., I and Q components for each X and Y polarization), after processing by ADCs 816, are passed through a relevant structural block of DSP 818 to compensate front-end imper-

fections. In an embodiment, the front-end imperfections are compensated, in step S908, by one or more correction algorithms of algorithmic level 904, which may include a deskew algorithm to correct the timing skew between the four channels resulting from the difference in both optical and electrical path lengths within coherent receiver 800. In some embodiments of step S906, other types of front-end imperfections may be corrected, including without limitation, differences between the respective output powers of the four channels (due to different responses of PINs and/or transimpedance amplifiers (TIAs) in receiver 800), and quadrature imbalance resulting from a particular optical hybrid not exactly introducing a 90-degree phase shift. Accordingly, in some embodiments of step S908, algorithmic level 904 may further include normalization and orthogonality correction algorithms.

[0103] In step S910, major channel transmission impairments may be compensated through use of appropriate digital filters of structural level 902, which may, at step S912, further utilize estimation and compensation algorithms to address impairments such as chromatic dispersion and PMD. An embodiment of step S912, and based on different time scales of the dynamics of the respective impairments, the static equalization for chromatic dispersion compensation may be performed first because of its independence of state of polarization (SoP) and modulation format, as well as the impact on subsequent blocks of structural level 902 before the chromatic dispersion estimation may be needed to achieve accurate compensation.

[0104] In step S914, the clock recovery for symbol synchronization may be processed within structural level 902 to track the timing information of incoming samples. In an embodiment of step S910, joint processing between clock recovery blocks and polarization demultiplexing blocks may be performed to achieve, at step S916, symbol synchronization within algorithmic level 904 after all channel impairments are equalized (e.g., as represented by respective arrows indicated in FIG. 9). In an embodiment of step S916, a fast-adaptive equalization may be jointly performed for two polarizations through a butterfly structure and stochastic gradient algorithms, such as a constant modulus algorithm (CMA) and variants thereof. In step S918, algorithmic level 904, additional algorithms may be performed with respect to PMD compensation, residual chromatic dispersion compensation, and polarization demultiplexing/dynamic equaliza-

[0105] In step S920, and carrier recovery is processed at structural level 902, which may be performed in cooperation with step S922, carrier frequency offset estimation or compensation algorithms within algorithmic level 904. In an exemplary embodiment of step S922, the frequency offset between source laser 802 and LO 804 may be estimated and removed to prevent the constellation rotation at the intradyne frequency. In step S924, within algorithmic level 904, the carrier phase noise may be estimated and removed from the modulated signal, which may then be followed by algorithms for symbol estimation and hard or soft-decision forward error correction (FEC) for channel decoding. At step S926, the final bit streams may be recovered at both structural level 902 and algorithmic level 904.

[0106] Again, as described above, it may be noted that, for a particular digital coherent receiver, the ordering of DSP flow may according to the design choices at the receiver, differ from the order described immediately above. For

example, instead of, or in addition to, a feed-forward process, joint processing and feedback among different process blocks may be performed, including without limitation, clock recovery and polarization demultiplexing. In some embodiments, similar functions may be performed through use of training sequences based on data-aided or blinded algorithms. In other embodiments, a coherent receiver may perform fewer steps than those described above, or may include additional steps beyond those specifically described, but nevertheless within the scope of this description.

[0107] Coherent detection and DSP technologies have thus been key factors enabling the development of 100G coherent optical transmission systems. DSP technology has played in even more ubiquitous role, at both the transmitter and receiver, and the development of 200G coherent optical systems, and this trend is expected to continue in the development of further next-generation coherent optical systems. Although specific algorithms may be different for each process block of the DSP (e.g., due to various realizations of the same process block in the implementation level), the general functionality at the structural level (e.g., structural level 902) or functional abstractions (e.g., algorithmic level 904) are expected to be similar for all relevant major commercial products implementing these technologies.

[0108] The typical optical access network includes a few components that are considered to be fundamental thereto. That is, "fundamental" components are those components that have been heretofore most widely used in the access network, and which are expected to play a significant role in the access networks of the future. Such fundamental components may be described as being grouped, into three categories: (1) the optical transmitter; (2) the optical channel; and (3) the optical receiver. Optical transceivers are considered to include both an optical transmitter and an optical receiver. These fundamental components are described further below with respect to the following embodiments.

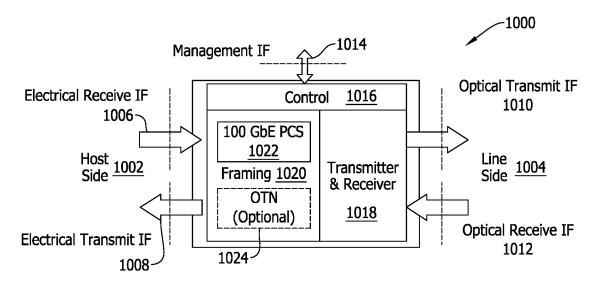

[0109] FIG. 10 is a schematic illustration of a transceiver 1000 having a dual optical interface structure. In the embodiment depicted in FIG. 10, transceiver 1000 is disposed with respect to an electrical client side 1002 (or host side 1002) and an optical line side 1004. In this example, transceiver 1000 includes an electrical receive interface 1006 and an electrical transmit interface 1008 at client side 1002, and optical transmit interface 1010 and an optical receive interface 1012 at line side 1004. That is, client side/host side 1002 corresponds to electrical interfaces 1006, 1008, and line side 1004 corresponds to optical interfaces 1010, 1012. In an exemplary embodiment, transceiver 1000 further includes a management interface 1014 in communication with a control layer 1016 of transceiver 1000.

[0110] Dual optical interface transceiver 1000 thus utilizes separate optical interfaces 1010, 1012 capable of operable communication with respective transmit and receive functions of transmitter and receiver portions 1018 of transceiver 1000. In an embodiment, transceiver 1000 further includes a framing unit 1020 in communication with electrical interfaces 1006, 1008 at host side 1002 (e.g., a 100 Gb Ethernet PCS 1022 and/or an optional optical transport unit 1024).

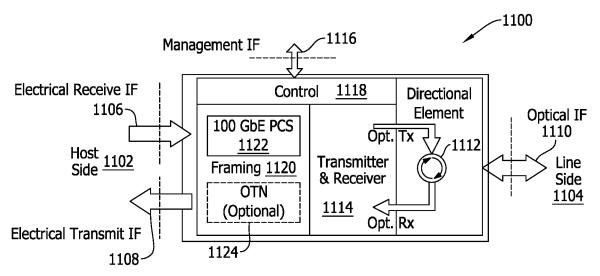

[0111] FIG. 11 is a schematic illustration of a transceiver 1100 having a single optical interface structure. In the embodiment depicted in FIG. 11, transceiver 1100 is similar to transceiver 1000, FIG. 10, is similarly disposed with respect to an electrical client/host side 1102 and an optical

line side 1104, and includes an electrical receive interface 106 and an electrical transmit interface 1108 at client side 1102. Transceiver 1100 differs from transceiver 1000, however, in that transceiver 1100 includes a single optical interface 1110 at line side 1104. Optical interface 1110 is able to communicate with a directional element 1112 of transceiver 1100, capable of functionally directing transmitted and received optical signals between the respective transmitter and receiver portions 1114 of transceiver 1100. [0112] In an exemplary embodiment, transceiver 1100 further includes a management interface 1116 in communication with a control layer 1118 of transceiver 1100. In some embodiments, transceiver 1100 also similarly includes a framing unit 1120 in communication with electrical interfaces 1106, 1108 at host side 1102 (e.g., a 100 Gb Ethernet PCS 1122 and/or an optional optical transport unit 1124). [0113] Implementation of single optical interface structure of transceiver 1100 is particularly useful in the case where only a single fiber it is available from hub to node. In this embodiment, signal direction functionality is incorporated into transceiver 1100 (e.g., by directional element 1112) to enable the transmitter optical signal (i.e., Opt. Tx) to be directed to the single optical interface (i.e., optical interface 1110), while enabling the signal (i.e., Opt. Rx) incoming through the single optical interface to be directed to the respective receiver of portion 1114, with a performance impact that is expected to be negligible, and while also utilizing the same communication frequency in both the

[0114] Architectural considerations with respect to implementations using the single interface transceiver are described functionally below with respect to FIGS. 12 and 13, which are provided for illustration purposes, but not in a limiting sense. Other transmitter and receiver implementations may follow different sequences and different feedback dependencies.

transmit and receive directions.

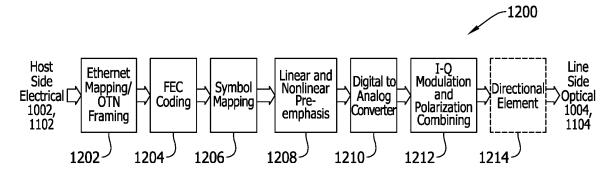

[0115] FIG. 12 is a functional schematic illustration of a transmitter 1200. In an exemplary embodiment, transmitter 1200 is configured to perform relevant transmitter functions occurring, for example, in a coherent optical transceiver (e.g., transceiver 1000, FIG. 10, transceiver 1100, FIG. 11) from the electrical input on the host side (e.g., host side 1002, FIG. 10, host side 1102, FIG. 11) to the optical output on the line side (e.g., line side 1004, FIG. 10, line side 1104, FIG. 11).

[0116] In exemplary operation, transmitter 1200 includes one or more functional units, which may operate in the order listed, or in a different order, and may be individually implemented by hardware elements, software modules, or by combinations of hardware and software. In some embodiments, transmitter 1200 may include fewer functional units, or additional functional units described herein, without departing from the scope of this description. These transmitter functional units may include, without limitation, one or more of an Ethernet mapping and optional OTN framing unit 1202, an FEC coding unit 1204, a symbol mapping unit 1206, a linear and nonlinear pre-emphasis unit 1208, a DAC unit 1210, an IQ modulation and polarization combining unit 1210, and an optional directional element unit 1214. That is, directional element unit 1214 may be implemented in the case of a single optical interface transceiver (e.g., transceiver 1100, FIG. 11), but may not be needed in the case of a dual optical interface transceiver (e.g., transceiver 1000, FIG. 10).

[0117] In an exemplary embodiment, the optical signal transmitted through transmitter 1200 may be described using parameters including, without limitation, one or more of encoding scheme, line rate, polarization imbalance, quadrature and polarization skew, transmitter clock jitter, frequency tolerance, optical output power, laser wavelength, laser linewidth, and transmitter OSNR. The optical distribution medium of the access network (e.g., cable environment, telecommunication environment, etc.) may include various elements over the respective link, including one or more of optical fiber, optical splitters, optical circulators, wavelength multiplexers, wavelength demultiplexers, and other optical passive components. The various impairments that may impact the optical signals traversing the link they include one or more of optical loss or gain, chromatic dispersion, PMD, polarization dependent loss, polarization rotation, optical crosstalk, and optical SNR degradation.

[0118] An optical signal so generated by an "imperfect" embodiment of transmitter 1200, which may be further degraded by one or more impairments from the optical distribution medium, enters the line side of the transceiver (e.g., transceiver 1000, FIG. 10, transceiver 1100, FIG. 11) for detection, compensation and processing by a receiver portion thereof, as described further below with respect to FIG. 13

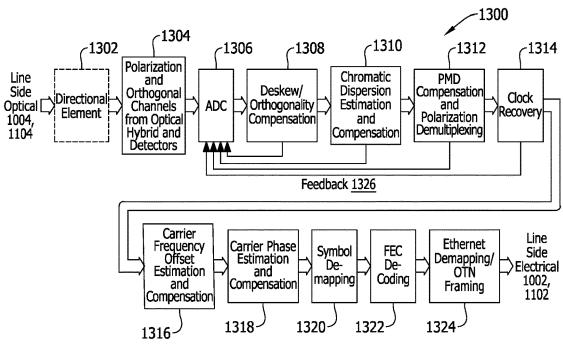

[0119] FIG. 13 is a functional schematic illustration of a receiver 1300. In an exemplary embodiment, receiver 1300 is configured to perform relevant receiver functions occurring, for example, in the coherent optical transceiver (e.g., transceiver 1000, FIG. 10, transceiver 1100, FIG. 11) from the optical input on the host side (e.g., host side 1002, FIG. 10, host side 1102, FIG. 11) to the electrical output on the line side (e.g., line side 1004, FIG. 10, line side 1104, FIG. 11). In exemplary operation, receiver 1300 includes one or more functional units which generally correspond to relevant functional units of transmitter 1200, FIG. 12, and which may similarly operate in the order listed, or in a different order, and may be individually implemented by hardware elements, software modules, or by combinations of hardware and software.

[0120] The receiver functional units may include, without limitation, one or more of an optional directional element unit 1302 (e.g., in the case of a single optical interface transceiver such as transceiver 1100, FIG. 11), a detection unit 1304 for detecting I and Q orthogonal channels for each X and Y polarizations, an ADC unit 1306, a deskew and orthogonality compensation unit 1308, a chromatic dispersion estimation and compensation unit 1310, a PMD compensation and polarization multiplexing unit 1312, a clock recovery unit 1314, a carrier frequency offset estimation and compensation unit 1316, a carrier phase estimation and compensation unit 1318, a symbol demapping unit 1320, an FEC decoding unit 1322, and an Ethernet demapping and optional OTN framing unit 1324. In an embodiment, receiver 1300 may include feedback channels 1326 to ADC unit 1306, from one or more of respective units 1308, 1310, 1312, 1314.

[0121] In an exemplary embodiment, the optical signal processed through receiver 1300 may be described using parameters including, without limitation, one or more of modulation, symbol rate, symbol mapping, FEC, line rate, encoding scheme, frequency tolerance, frame format and mapping, optical input power, laser wavelength, laser linewidth, receiver OSNR, polarization imbalance, quadrature

and polarization skew, transmitter clock jitter, chromatic dispersion, polarization dispersion, and polarization rotation (SoP track).

[0122] With respect to both transmitter 1200 and receiver 1300, some general transceiver characteristics may also be considered, such as the end-to-end link latency, which includes both the transmitter and receiver latencies, as well as the transmission delay of the optical channel. Additionally, the operation of the transceiver may also be impacted by the ambient temperature, which may then require additional compensation therefor. With respect to receiver 1300 in particular, the present systems and methods may further utilize the data reacquisition time as a useful metric to indicate the time the receiver takes to turn back on after loss of signal.

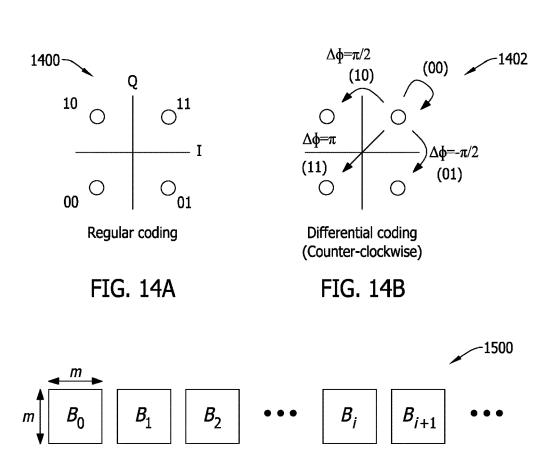

[0123] FIGS. 14A-B are graphical illustrations depicting comparative encoding plots 1400, 1402. More particularly, encoding plot 1400 represents a constellation of a regular QPSK coding scheme, and encoding plot 1402 represents a constellation of a differential QPSK coding scheme (counterclockwise, in this example). A comparison of differential QPSK coding scheme of plot 1402 with the regular QPSK coding scheme of plot 1400 illustrates the advantages realized by implementation of differential coding with respect to the embodiments described further below. Specifically, implementation of differential coding functions to mitigate the transmission performance degradation caused by cycle slip. As depicted in FIG. 14B, in the case of counterclockwise differential coding, the IQ value "10" is a 90 degree shift, the IQ value "11" is a 180 degree shift, the IQ value "01" is a -90 degree shift, and the IQ value "00" represents no shift. In an exemplary embodiment, a transceiver implementing the differential coding scheme of plot 1402 of FIG. 14B is configured to support a  $\Pi/2$  phase rotation with counterclockwise rotation.

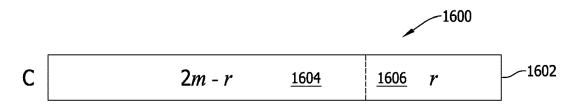

[0124] FIG. 15 is a schematic illustration depicting an exemplary symbol stream architecture 1500. In an exemplary embodiment, architecture 1500 represents a stream of m×m arrays of symbols, and may be implemented with respect 100G implementations utilizing staircase FEC. For example, a transceiver in compliance with the 100G PHY requirements described herein may be configured to support FEC using 512×510 Staircase codes. For purposes of this discussion, "Staircase codes" are referred to as a class of error-correcting codes that combine ideas from recursive convolutional coding and block coding, resulting in a "continuous" product-like code that is characterized by the relationship between successive matrices of symbols. As illustrated in FIG. 15, architecture 1500 includes a sequence  $B_0$ ,  $B_1$ ,  $B_2$ , (i.e., theoretically infinite) of m×m matrices  $B_i$ ,  $i \in \mathbb{Z}_+$ , where the elements of B, are binary.

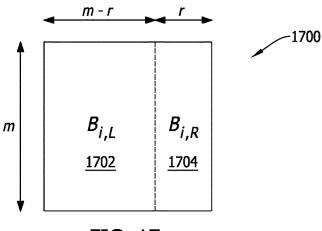

[0125] FIG. 16 is a schematic illustration depicting an exemplary codeword architecture 1600. In the exemplary embodiment depicted in FIG. 16, architecture 1600 is illustrated as a subdivision of a systematic component codeword 1602 having a length 2m, into a leftmost information position 1604 having a length 2m–r, and a rightmost parity position 1606 having a length r. In this example, component codeword 1602 may be a conventional FEC block code (e.g., Hamming, BCH, Reed-Solomon, etc.) in systematic form (also referred to as C), is selected to have block length 2m of symbols, a length r of which constitute parity symbols

**1606**. That is, leftmost 2m-r symbols **1604** constitute information positions of C, and rightmost r symbols constitute parity positions of C.

[0126] FIG. 17 is a schematic illustration depicting an exemplary block subdivision 1700. In the exemplary embodiment depicted in FIG. 17, each block  $B_i$  is divided into its m-r leftmost column 1702 and its r rightmost column 1704. In an embodiment, prior to encoding, a first block  $B_0$  is initialized to a reference state (e.g., block  $B_0$  may be initialized to an all-zero state). Next, m(m-r) information bits are stored in  $B_{(1,L)}$ , and the values of  $B_{(1,R)}$  are calculated by: (i) forming an m×(2m-r) matrix  $\Lambda$ =[ $B_0^T$   $B_{(1,L)}$ ] (i.e.,  $B_0^T$  is the transposed matrix of  $B_0$ ); and (ii) the elements of  $B_{(1,R)}$  are then computed such that each of the rows of the matrix [ $B_0^T$   $B_{(1,L)}$  $B_{(1,R)}$ ] is a valid codeword of C. That is, the elements in the j<sup>th</sup> row of  $B_{(1,R)}$  are exactly the r parity symbols that result from encoding the 2m-r 'information' symbols in the j<sup>th</sup> row of  $\Lambda$ .

**[0127]** Generally, the relationship between successive blocks in a staircase code satisfies the relation: for any  $i \ge 1$ , each of the rows of the matrix  $[B_{i-1}{}^TB_0)]$  is a valid codeword of the component code C (i.e.,  $B_{i-1}{}^T$  is the transposed matrix of  $B_{i-1}$ ). An equivalent "visual" description of a staircase code, from which the name originates, is illustrated below with respect to FIG. **18**.

[0128] FIG. 18 is a schematic illustration depicting an exemplary staircase coding scheme 1800. In the exemplary embodiment depicted in FIG. 18, every row 1802 and every column 1804 in the staircase visualization of scheme 1800 is a valid codeword of C. Most FEC codes are designed to perform under additive white Gaussian noise (AWGN), i.e., the decoder assumes that the noise samples are uncorrelated and Gaussian distributed. The performance of these codes may, however, substantially decrease if the added noise is correlated. Error decorrelators though, may be added to the FEC Encoder/Decoder to reduce the correlation of noise samples, thus approaching the performance under AWGN. [0129] FIG. 19 is a schematic illustration of an exemplary error decorrelator 1900. In an exemplary embodiment, decorrelator 1900 includes a transmitter portion 1902, a receiver portion 1904, communicating over a channel 1906. Transmitter portion 1902 may include one or more software, hardware, or hardware/software hybrid elements such as a frame generator 1908, a bit interleaver 1910, an FEC encoder 1912, and a bit de-interleaver 1914. The receiver portion 1904 may similarly include one or more of a framer 1916, bit interleaver 1918, an FEC decoder 1920, and a bit de-interleaver 1922.

[0130] In exemplary operation of error decorrelator 1900, the position of correlated error symbols may be randomized such that the performance of the staircase code is not impacted by correlated errors. For example, at both the transmitter portion 1902 and receiver portion 1904, the respective error decorrelator interleaver (EDI) and corresponding error decorrelator de-interleaver (EDD) (e.g., bit interleaver 1910/bit de-interleaver 1914, bit interleaver 1918/bit de-interleaver 1922) may operate directly on framed data, in a complementary fashion at the input (and output) of the core encoder (e.g., encoder 1912) and decoder blocks (e.g., decoder 1920). The purpose of performing bit interleaving at the input (EDI) and output (EDD) of the Staircase FEC encoder is to preserve the "systematic" nature of the encoding function (i.e., the position of data bits in the data frame are unaffected). At decoder 1920, the EDI is applied to the input of the Staircase FEC decoder, which effectively randomizes the position of the channel errors. At the decoder output, the EDD is applied to restore the bits to their transmitted ordering.

[0131] FIG. 20 is a schematic illustration depicting an exemplary staircase code architecture 2000. In the embodiment depicted in FIG. 20, architecture 2000 represents a 512×510 block staircase encoder encoding of a 512-bitx 510-bit staircase code, which is accomplished by considering two-dimensional blocks  $B_i$  of binary data, each with 512 rows 2002 and 510 columns 2004. In this example, the block size of 512×510=261120 bits carries exactly two optical transport unit (OTU4, in this example) client payloads. The component code is a 3 error correcting extended BCH(1022, 990) code in this example.

[0132] FIG. 21 is a schematic illustration depicting an exemplary component codeword 2100. Due to the staircase construction, it may be convenient to classify the symbols of each component BCH(1022,990) codeword as occupying a "leftside" 2102 or the "rightside" 2104 of codeword 2100. Accordingly, component codewords in the 512×510 staircase code may each include 512 "leftmost" symbols in relation to leftside 2102 (e.g., contributed from the previous staircase block), and 510 "rightmost" symbols in relation to rightside 2104. That is, the symbols  $(C_0, C_1, \ldots, C_{511})$ constitute leftside 2102, and the symbols ( $C_{512}, C_{513}, \ldots$ , C<sub>1021</sub>) constitute rightside **2104** of the component BCH (1022,990) codeword 2100. In this example, the first two rows of B<sub>i</sub> correspond to shortened codewords (leftmost symbols are assumed to be zeros), which can be exploited in the decoder.

[0133] The binary value stored in position (row,column)'2 (j,k) of B<sub>i</sub> may be denoted d<sub>i</sub>{j,k}. In each block, information bits are stored as d<sub>i</sub>{j,k}, 0≤j≤511, 0≤k≤477, and parity bits are stored as d<sub>i</sub> {j,k}, 0≤j≤511, 478≤k≤509. The parity bits are computed such that: for row j, 0≤j≤1, and [d<sub>i</sub>{j,478},d<sub>i</sub>{j,479},...,d<sub>i</sub>{j,509}] is calculated as [d<sub>i</sub> {j,478},d<sub>i</sub>{j,479},...,d<sub>i</sub> {j,509}]=[0,0,...,0,d<sub>i</sub> {j,0},d<sub>i</sub> {j,1}...,d<sub>i</sub> {j,477}[P, where P is a 990×32 parity-generation matrix; and for row j, 2≤j≤511, [d<sub>i</sub> {j,478},d<sub>i</sub>{j,479},...,d<sub>i</sub> {j,509}] is calculated as [d<sub>i</sub> {j,478},d<sub>i</sub>{j,479},...,d<sub>i</sub> {j,509}]=[d<sub>i-1</sub>{0,1},d<sub>i-1</sub>{1,1},...,d<sub>i-1</sub>{511,1},d<sub>i</sub>{j,0},d<sub>i</sub>{j,1}...d<sub>i</sub>{j,477}]P, where 1= $\Pi_d$ (j-2), and  $\Pi_d$  is a permutation function.

[0134] FIG. 22 is a schematic illustration depicting an exemplary staircase decoding window 2200 for a series of blocks 2202. In the embodiment depicted in FIG. 22, decoding window 2200 is illustrated as a five-block staircase decoding window for a 512×510 Staircase decoder. In exemplary operation of decoding window 2200, staircase codes are decoded by iteratively decoding the BCH component codewords within decoding window 2200, and decoding window 2200 includes an implementation-specific number of consecutive staircase blocks (five blocks, in this example). That is, the 512×510 Staircase decoder deploys, as a minimum, a 5-block decoding window (e.g., decoding window 2200) to perform iterative decoding of its BCH (1022,990) component codewords.

[0135] In this example, a total latency 2204 in this minimum configuration will be seven staircase blocks. Decoding window 2200 then moves forward in time (i.e., to the "right" from the perspective depicted in FIG. 22) once the parity bits corresponding to block  $B_{i-1}$  are received. At every shift in decoding window 2200, iterative decoding may then be

performed over the respective component codewords within decoding window **2200**. Therefore, in this embodiment, implementation of the  $512\times510$  Staircase code achieves a net coding gain of 9.38 dB at an output BER= $1.0e^{-15}$ . The input BER threshold is  $4.5e^{-3}$ . Accordingly, latency **2204** of the minimum  $512\times510$  Staircase decoder is  $7\times512\times510=1$ , 827,840 bits.

[0136] FIG. 23 is a schematic illustration depicting a non-correctable stall error pattern 2300 for a staircase coding scheme. In theory, burst error tolerance can be as high as 1538 bits (e.g., approximately three columns of  $B_i$ ) if there are no additional random or correlated errors (and assuming error decorrelator function is turned off). In practice, it is often necessary to take into account additional random and/or correlated errors when specifying the burst error tolerance. Thus, it is expected that implementation of an error decorrelator function may be necessary to prevent non-correctable stall error patterns, as depicted in FIG. 23. [0137] At the transmitter, information bits of an 8×30592 bit input block B, (in a row-by-row, i.e., a left-to-right, top-to-bottom order) May be passed through an error decorrelator interleaver (EDI) process, after which the interleaved information bits  $B_i^*$  may be written into a 512×478 bit array (in a column-by column, i.e., top-to-bottom, leftto-right order). In parallel, the parity bits in a 512×32 bit array holding the parity computed over the previous  $8\times30592$  bit input block  $B_{i-1}$  may be passed through (also in a column-by-column, i.e. top-to-bottom, left-to-right order) an error decorrelator de-interleaver (EDD) process, after which the de-interleaved parity bits  $B_{i-1}^{\#}$  may be written into an 8×2048 bit array. Staircase FEC parity may then be computed over the information bits of the block (B<sub>i</sub>\*) within the 512×478 bit array, the information bits of the previous block  $(B_{i-1}^*)$  that are located in the other 512×478 bit array, and the parity bits in a 512×32 bit array containing the parity bits of the previous computation  $(B_{i-1})$ . The computed parity bits may be written in a row-by-row basis in the other 512×32 bit parity array (B,). The client information bits of block i  $(B_i)$  and the computed parity bits of block i-1  $(B_{i-1}^*)$ may then be combined and transmitted within the client frame format.

[0138] At the corresponding receiver, the received information bits of block i and parity bits of block i-1 may similarly be passed through an EDI process, after which the interleaved information and parity bits may be written into one of m 512×478 and 512×32 bit arrays (in a column-by column, i.e., top-to-bottom, left-to-right order). In parallel, the corrected information bits in a 512×478 bit array holding the interleaved bits of information of block i-m  $(B_{i-m})$  may be passed through (in a column-by-column, i.e., top-tobottom, left-to-right order) an error decorrelator de-interleaver (EDD) process after which the de-interleaved information bits  $B_{i-m}$  may be mapped in an 8×30592 bit block structure (in a row-by-row, i.e., a left-to-right, top-to-bottom order). Staircase codes may then be decoded by iteratively decoding the component codewords within a decoding window (e.g., decoding window 2200, FIG. 22). The corrected information bits in block B<sub>i-m</sub> may then be written in a row-by-row basis.

[0139] In simulations including random errors at BER=4. 0e<sup>-3</sup>, correlated errors due to differential decoding, and burst errors of N bits occurring every 10 FEC blocks, bursts of up to N=400 bits have been shown to be tolerated with small penalty, i.e., backing off maximum input BER from 4.5e<sup>-3</sup>

to  $4.0e^{-3}$  (e.g., approximately a 0.1 dB penalty). Such simulations have proven particularly informative with respect to the 100G PHY specification described herein.

[0140] Transceivers that are compliant with respect to the present systems and methods, whether for the 100G PHY embodiments, the 200G PHY embodiments, or embodiments not specific to the present, new optical PHY layers will conform to a number of general transceiver requirements. The present description though, is not intended to define specific environmental conditions that compliant transceivers are required to support. In most cases, environmental condition specifications are expected to be defined by the end customer when defining their purchasing requirements. Nevertheless, for transceivers operating in the field, the present embodiments assume that such transceivers are expected to be required to operate at startup temperatures as low as -40 C, and may need to operate in conditions with an internal temperature as high as +85 C. Accordingly, for the expected range of temperatures supported by the transceiver (as defined by the manufacturer), it is assumed that such transceivers are able to meet the requirements of the present systems and methods across the entire supported temperature range.

[0141] With respect to the client side interface, the embodiments herein are described with respect to solutions utilizing the present PHY will support Ethernet transport. That is, for illustrative purposes, the compliant transceivers of the present embodiments are described herein as being capable of supporting Ethernet input and output on the client side interfaces (e.g., element 1022, FIG. 10, element 1122, FIG. 11). Nevertheless, the person of ordinary skill in the art will appreciate that other layer 2 protocols, for example, may be supported within the scope of the present systems and methods.

[0142] The electrical interfaces described herein are assumed to be compliant with the 100G and 200G embodiments of the present description, but may be otherwise generally defined by the respective product definitions. Nevertheless, the compliant transceivers of the present embodiments are described as being capable of supporting 2×100 GbE on the client side, in thereby providing 200G at the optical interface on the line side. However, an electrical interface supporting 2×100 GbE is described by way of example, and not in a limiting sense. The person of ordinary skill in the art will appreciate that other electrical interface configurations, 200 GbE, for example, are within the scope of the present description, and such transceivers are similarly assumed to support the transport of Ethernet traffic and Ethernet frames.

[0143] Referring back to FIGS. 10 and 11, two different line side interface options are described herein, namely, a dual optical interface option (e.g., transceiver 1000), and a single optical interface option (e.g. transceiver 1100). According to the present systems and methods, either interface option is capable of supporting a single frequency for transmitting and receiving, on the one hand, or separate frequencies for transmitting and receiving come on the other hand. That is, the present embodiments are configured to support both line side interface options. In an exemplary embodiment, the complaint transceiver is configured to support use of the same frequency for transmitting and receiving, and may further be optionally configured to be capable of supporting transmitting and receiving using different frequencies.

[0144] Also in an exemplary embodiment, complaint transceivers supporting the 200G mode of operation may be optionally configured to further include backward capability to support the 100G mode of operation, in addition to the 200G functionality described herein. In at least one embodiment, a compliant device supporting the 100G mode of operation it is further configured to include a mechanism for switching between the 100G and 200G modes. That is, when the compliant device is operating in the 100G mode, the transceiver will meet relevant requirements for 100G operation; when the compliant device is operating in the 200G mode, the transceiver will meet all the relevant requirements for 200G operation.

[0145] FIG. 24 is a schematic illustration depicting a client side adaptation process 2400. In an exemplary embodiment, process 2400 is configured to adapt client side data into coherent line side data through a series of framing, FEC, and mapping operations. In the embodiment illustrated in FIG. 24, a client side interface 2402 provides two 100 GbE client signals 2404, which may then be adapted for transport over a 200G coherent DP-QPSK or DP-16QAM optical link.

[0146] In exemplary operation of process 2400, the two 100 GbE clients 2404 are initially mapped, by a mapping unit 2406, into two 100G FlexO frame structures 2408, which are then multiplexed, by a multiplexing unit 2410 (e.g., including a 10b multiplexer), from the two separate 100G FlexO frame/multi-frame aligned structures into a 200G FlexO-2-NP (e.g., 200G FlexO without parity field) frame structure 2412. 200G FlexO-2-NP frame structure 2412 may then be adapted, at a padding unit 2414. scrambled by a scrambler 2416, and open FEC (oFEC) encoded at an oFEC block 2418. After FEC encoding at block 2418, frame structure 2412 may be further interleaved by an interleaver 2420, thereby rendering frame structure 2412 into FlexO-2-<oFEC>. The bitstream of the resultant FlexO-2-<oFEC> frames may then be mapped, by a symbol map 2422 into constellation symbols of each polarization (described above) at a polarization distribution block 2424, after which training symbols may be added, Super-Frame Alignment Word (super-FAW) symbols added at FAW blocks 2426, and pilot symbols added at pilot blocks 2428.

[0147] FIG. 25 is a schematic illustration depicting a framing and mapping subprocess 2500 of process 2400, FIG. 24. In the embodiment depicted in FIG. 25, subprocess 2500 emphasizes the conversion of the two 100GBASE-R Ethernet clients 2404 into the FlexO-2-NP frames of frame structure 2412 that are subsequently adapted and scrambled before being FEC encoded (described further below with respect to FIG. 26). In exemplary operation of subprocess 2500, the two 100 GbE Ethernet Clients (e.g., 100 GBASE-R) may be defined according to IEEE 802.3-2018, and the client FEC, if any, is presumed in this embodiment to have been terminated prior to mapping by mapping unit 2406. Mapping unit 2406 may, for example, be defined according to ITU-T G.709, and then multiplexing unit 2410 may be defined according to ITU-T G.709.1.

[0148] The individual configuration of the elements depicted within mapping unit 2406 are the provided for illustration purposes, and not in a limiting sense. In an exemplary embodiment, the compliant transceiver is configured such that mapping unit 2406 is capable of: (i) mapping 100GBASE-R signals 2404 into an optical transport unit/optical data unit/optical payload unit (e.g., OTU4/ODU4/OPU4) structure, such as that defined in ITU-T

G.709; (ii) mapping the respective 100GBASE-R payloads into an OPU-4 using GMP, such as that defined in ITU-T G.709 subclause 17.7.5; (iii) supporting 100GBASE-R multi-lane processing, such as that defined in ITU-T G.709 subclause 17.7.5.1; (iv) mapping each ODU4 signal into an ODTUC signal, and the ODTUC into the OPUC tributary slots, such as that defined in ITU-T G.709 clause 20; (v) mapping each OTUC signal into a FlexO frame instance, such as that defined in ITU-T G.709.1 Clause 10; and (vi) aligning and deskewing the OTUC instances, such as according to the definition in ITU-T G.709.1 subclause 10.4. [0149] FIG. 26 is a schematic illustration of an encoding subprocess 2600 of process 2400, FIG. 24. In the embodiment depicted in FIG. 25, subprocess 2600 emphasizes adaptation and encoding of FlexO-2-NP frame structure 2412 immediately prior to interleaving into the FlexO-2-<oFEC>. In exemplary operation of subprocess 2600, the complaint transceiver is configured to support adaptation (e.g., at padding unit 2414) according to ITU-T G.709 Annex E specifications for adaptation of 64/66B encoded 100GBASE-R interfaces. In an exemplary embodiment, the complaint receiver is further configured such that: (i) interleaver 2420 is capable of interleaving each FlexO frame instance into a FlexO-2-NP frame structure, such as that described further below with respect to FIGS. 29 and 30; (ii) padding unit 2414 is capable of adapting the FlexO-2-NP frame structure to the oFEC blocks, such as that described further below with respect to FIGS. 30 and 31, including padding insertion; and (iii) scrambler 2416 is capable of

[0150] For process 2400, including subprocesses 2500, 2600, the intermediate frame structure bit rates (i.e., client types and payload bit rates) are illustrated below in Table 1. The respective frame structures thereof, as well as the adaptation to the oFEC blocks, are described further below.

frame synchronous scrambling, such as that described fur-

ther below with respect to FIG. 32.

TABLE 1

| Interface  | Interface Nominal Bit Rate | Tolerance |

|------------|----------------------------|-----------|

| 100GBASE-R | 103.125000000 Gbps         | ±100 ppm  |

| ODU4       | 104.794445815 Gbps         | ±20 ppm   |

| ODUC       | 105.258138053 Gbps         | ±20 ppm   |

| FlexO      | 105.643510782 Gbps         | ±20 ppm   |

| FlexO-2-NP | 211.287021564 Gbps         | ±20 ppm   |