## (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2017/0287930 A1

### Oct. 5, 2017 (43) **Pub. Date:**

#### (54) THREE-DIMENSIONAL SEMICONDUCTOR DEVICE

- (71) Applicant: Samsung Electronics Co., Ltd., Suwon-si (KR)

- Inventors: Changhyun LEE, Suwon-si (KR); Heonkyu LEE, Hwaseong-si (KR); Shinhwan KANG, Seoul (KR); Youngwoo PARK, Seoul (KR)

- (21) Appl. No.: 15/593,494

- (22) Filed: May 12, 2017

#### Related U.S. Application Data

- Continuation of application No. 15/245,218, filed on Aug. 24, 2016, now Pat. No. 9,685,452.

- (30)Foreign Application Priority Data

Sep. 18, 2015 (KR) ...... 10-2015-0132515

#### **Publication Classification**

- (51) Int. Cl. H01L 27/11582 (2006.01)H01L 23/528 (2006.01)H01L 27/11565 (2006.01)

- U.S. Cl. CPC .. H01L 27/11582 (2013.01); H01L 27/11565 (2013.01); H01L 23/5283 (2013.01)

#### (57)**ABSTRACT**

A three-dimensional (3D) semiconductor device includes a stack structure including electrodes vertically stacked on a substrate, a channel structure coupled to the electrodes to constitute a plurality of memory cells three-dimensionally arranged on the substrate, the channel structure including first vertical channels and second vertical channels penetrating the stack structure and a first horizontal channel disposed under the stack structure to laterally connect the first vertical channels and the second vertical channels to each other, a second horizontal channel having a first conductivity type and connected to a sidewall of the first horizontal channel of the channel structure, and conductive plugs having a second conductivity type and disposed on top ends of the second vertical channels.

FIG. 1

FIG. 2

FIG. 4B

**Patent Application Publication**

FIG. 8A

FIG. 8B

FIG. 10

FIG. 17

FIG. 18

FIG. 25

FIG. 27

FIG. 30

FIG. 31

FIG. 33

FIG. 34

FIG. 35

### THREE-DIMENSIONAL SEMICONDUCTOR DEVICE

# CROSS-REFERENCE TO RELATED APPLICATION

[0001] This application is a continuation of U.S. patent application Ser. No. 15/245,218, filed on Aug. 24, 2016, which claims priority under 35 U.S.C. §119 to Korean Patent Application No. 10-2015-0132515, filed on Sep. 18, 2015, in the Korean Intellectual Property Office, the disclosure of which is hereby incorporated by reference in its entirety.

#### **BACKGROUND**

[0002] The inventive concepts relate to three-dimensional (3D) semiconductor devices and, more particularly, to 3D semiconductor devices capable of improving reliability and integration density.

[0003] Semiconductor devices have been highly integrated to provide high performance and low costs. The integration density of semiconductor devices may affect the costs of the semiconductor devices, thereby resulting in a demand of a highly integrated semiconductor device. An integration density of a conventional two-dimensional (2D) or planar semiconductor device may be mainly determined by an area where a unit memory cell occupies. Therefore, the integration density of the conventional 2D semiconductor device may be greatly affected by a technique of forming fine patterns. However, since extremely high-priced apparatuses are needed to form fine patterns, the integration density of 2D semiconductor devices continues to increase but is still limited. Thus, three-dimensional (3D) semiconductor devices including three-dimensionally arranged memory cells have been developed.

#### **SUMMARY**

[0004] Embodiments of the inventive concepts may provide three-dimensional (3D) semiconductor devices capable of improving reliability and integration density.

[0005] According to some example embodiments of the inventive concepts, a 3D semiconductor device may include a stack structure including electrodes vertically stacked on a substrate, a channel structure coupled to the electrodes to constitute a plurality of memory cells three-dimensionally arranged on the substrate, the channel structure including first vertical channels and second vertical channels penetrating the stack structure and a first horizontal channel disposed under the stack structure to laterally connect the first vertical channels and the second vertical channels to each other, a second horizontal channel having a first conductivity type and connected to a sidewall of the first horizontal channel of the channel structure, and conductive plugs having a second conductivity type and disposed on top ends of the second vertical channels.

[0006] According to some example embodiments of the inventive concepts, a 3D semiconductor device may include a plurality of stack structures extending in a first direction and spaced apart from each other in a second direction, each of the stack structures including electrodes vertically stacked on a substrate, first vertical channels and second vertical channels penetrating each of the stack structures, a first horizontal channel extending in the first direction under each of the stack structures and connecting the first vertical

channels and the second vertical channels to each other, second horizontal channels being in contact with both sidewalls of the first horizontal channel, a conductive line extending in the first direction on each of the stack structures and connected to the second vertical channels, and a bit line extending in the second direction on the conductive line and connected to the vertical channels. Each of the second horizontal channels may extend in the first direction between the stack structures adjacent one another when viewed from a plan view.

[0007] According to some example embodiments of the inventive concepts, a 3D semiconductor device may include a first horizontal channel extending in a first direction on a substrate, second horizontal channels extending in the first direction at both sides of the first horizontal channel and being in contact with both sidewalls of the first horizontal channel, a stack structure extending in the first direction and including a plurality of electrodes vertically stacked on the first horizontal channel, first vertical channels and second vertical channels penetrating the stack structure so as to be connected to the first horizontal channel, and conductive plugs disposed on top ends of the second vertical channels. The second horizontal channels may have a first conductivity type, and the conductive plugs may have a second conductivity type.

[0008] According to some embodiments of the present inventive concepts, a three-dimensional (3D) semiconductor device is provided. In some embodiments, the device includes a stack structure that extends in a first direction and that includes a plurality of electrodes that are vertically stacked on a substrate, first vertical channels and second vertical channels that penetrate the stack structure, a first horizontal channel that extends in the first direction under the stack structure and that connects the first vertical channels and the second vertical channels to each other, a second horizontal channel that extends in the first direction and that contacts both sidewalls of the first horizontal channel and conductive plugs that are on top ends of the second vertical channels, the conductive plugs having a second conductivity type that different from the first conductivity type.

[0009] In some embodiments, the first vertical channels are arranged along the first direction and along the second direction that is perpendicular to the first direction and the first horizontal channel is connected to the first vertical channels that are arranged along the first direction and the first vertical channels that are arranged along the second direction.

[0010] Some embodiments provide that the vertical channels, the second vertical channels, and the first horizontal channel constitute one semiconductor layer that continuously extends without an interface therein. In some embodiments, an interface exists between the first horizontal channel and the second horizontal channel.

[0011] Some embodiments include source plugs that are on top ends of the second vertical channels. In some embodiments, the source plugs have a conductivity type opposite to a conductivity type of the second horizontal channel and bottom surfaces of the source plugs are lower than a bottom surface of an uppermost one of the electrodes.

[0012] Some embodiments include a data storage layer

[0012] Some embodiments include a data storage layer that is between the stack structure and the first vertical channels and that is between the stack structure and the second vertical channels, and a residual data storage pattern that is between the first horizontal channel and the substrate.

Some embodiments provide that the stack structure includes insulating layers that are between the electrodes. In some embodiments, the data storage layer extends between a bottom surface of a lowermost insulating layer of the stack structure and the first horizontal channel and the second horizontal channel is in contact with a portion of the data storage layer and a portion of the residual data storage pattern.

[0013] Some embodiments further include a conductive pad that is on a top end of each of the vertical channels. In some embodiments, the conductive pad has the second conductivity type and a bottom surface of the conductive pad is higher than a top surface of an uppermost one of the electrodes.

[0014] It is noted that aspects of the inventive concept described with respect to one embodiment, may be incorporated in a different embodiment although not specifically described relative thereto. That is, all embodiments and/or features of any embodiment can be combined in any way and/or combination. These and other objects and/or aspects of the present inventive concept are explained in detail in the specification set forth below.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0015] The inventive concepts will become more apparent in view of the attached drawings and accompanying detailed description.

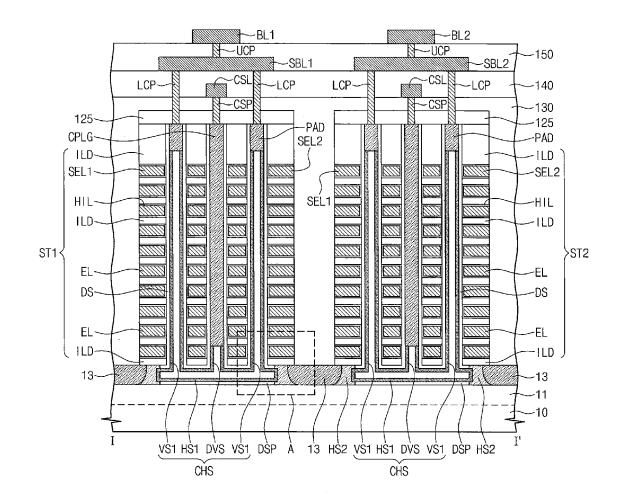

[0016] FIG. 1 is a schematic block diagram illustrating a three-dimensional (3D) semiconductor device according to some embodiments of the inventive concepts.

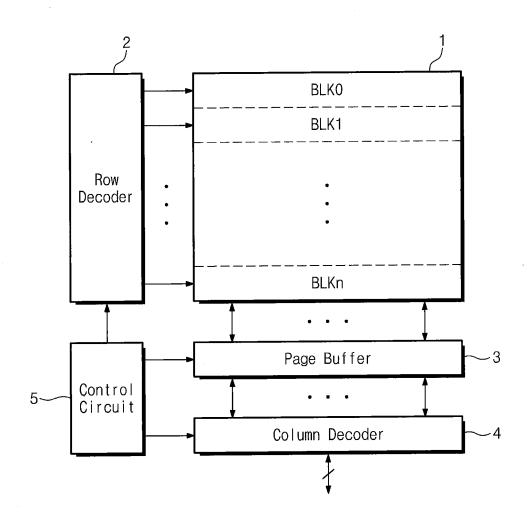

[0017] FIG. 2 is a circuit diagram illustrating a cell array of a 3D semiconductor device according to some embodiments of the inventive concepts.

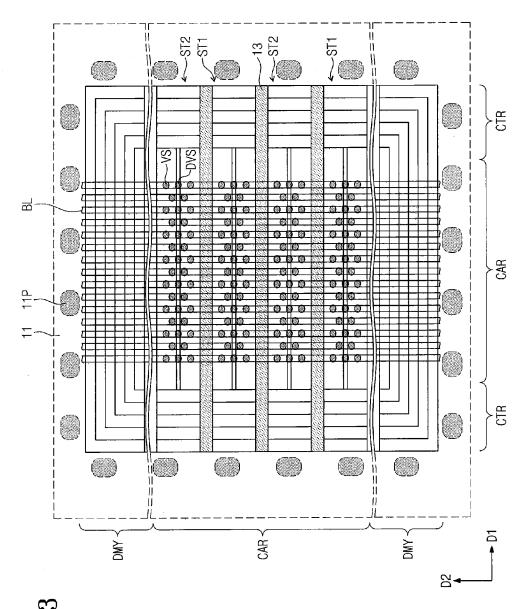

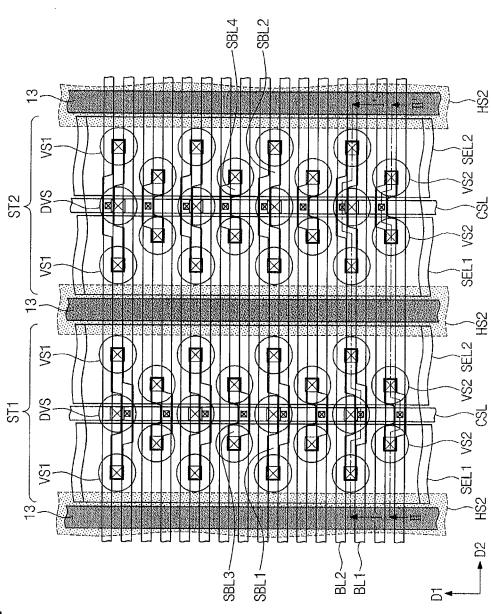

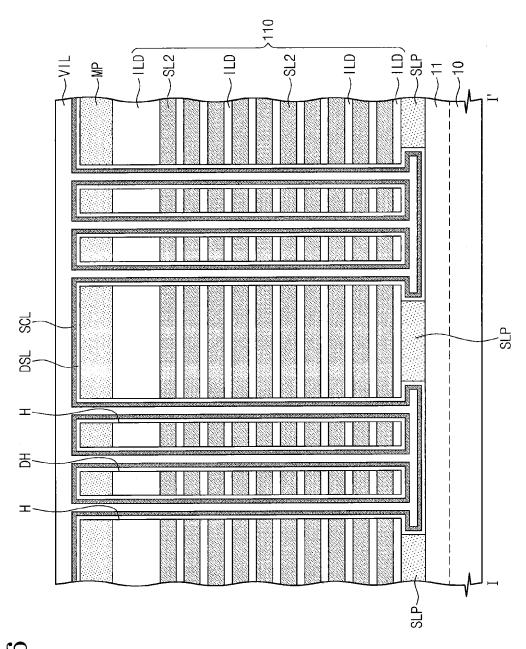

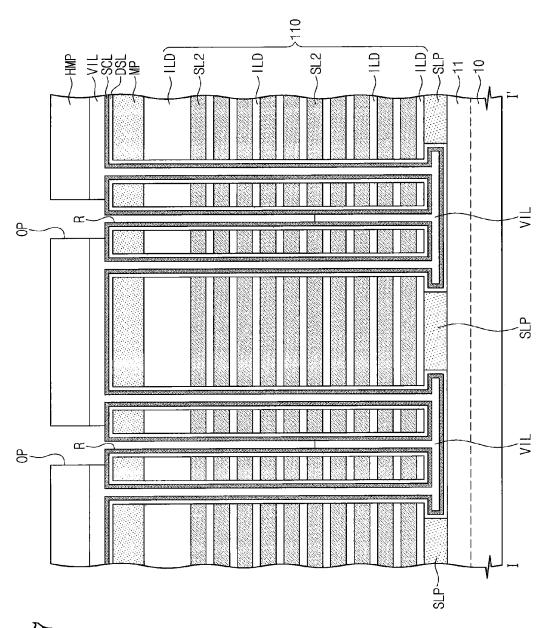

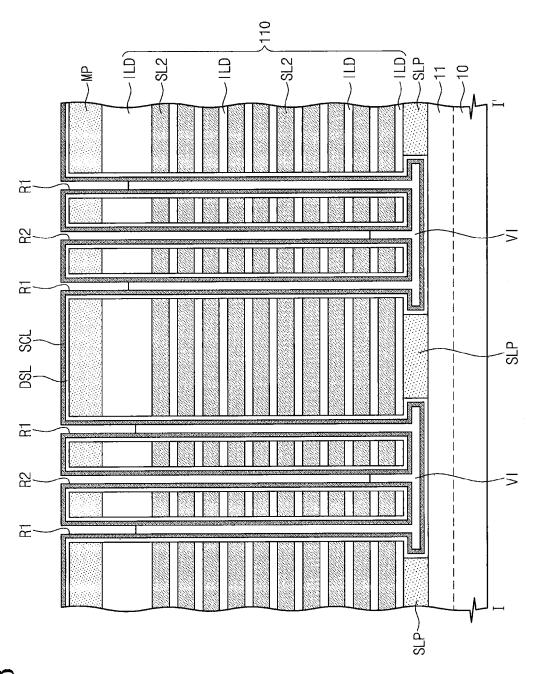

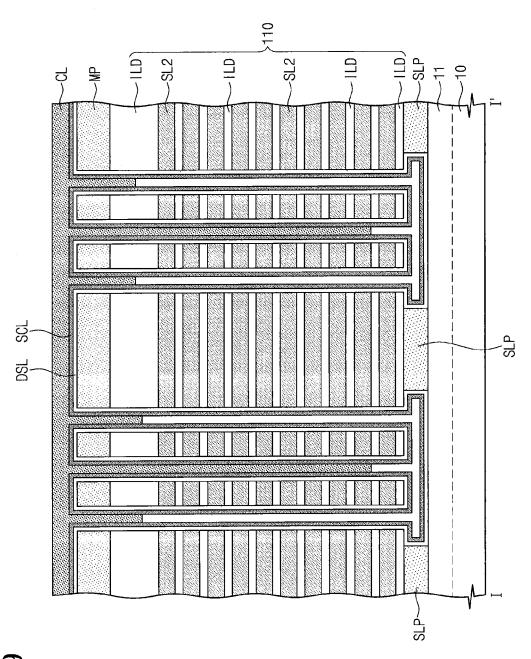

[0018] FIG. 3 is a plan view illustrating a 3D semiconductor device according to some embodiments of the inventive concepts.

[0019] FIG. 4A is a plan view illustrating a cell array region of a 3D semiconductor device according to some embodiments of the inventive concepts.

[0020] FIG. 4B is a plan view illustrating a channel structure of a 3D semiconductor device according to some embodiments of the inventive concepts.

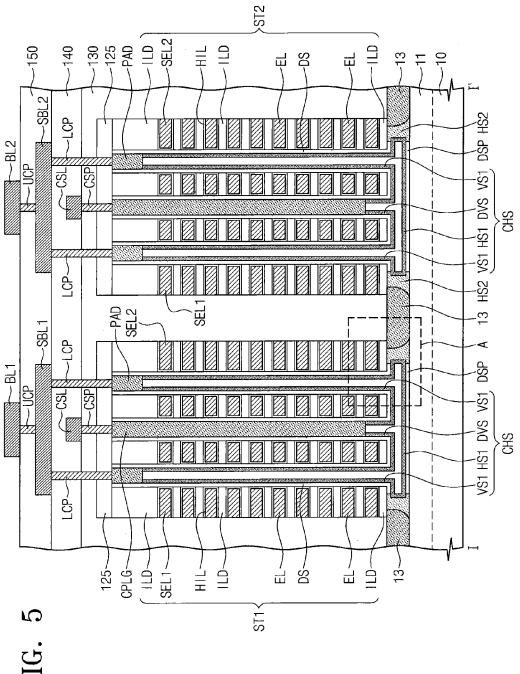

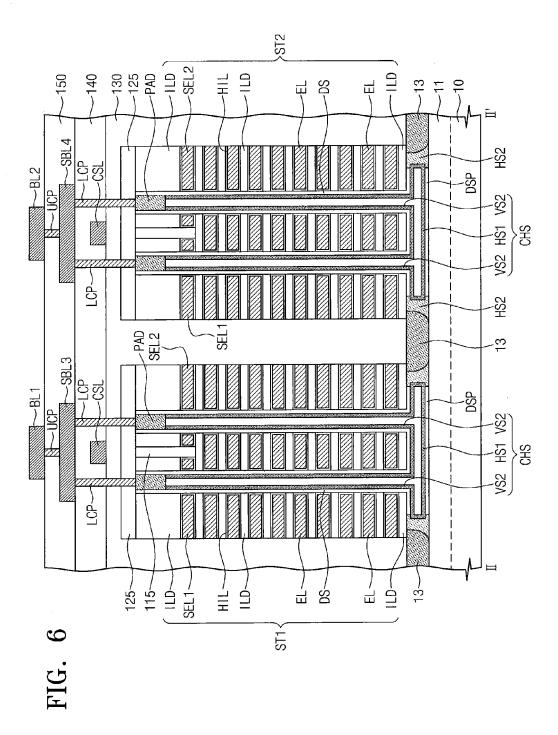

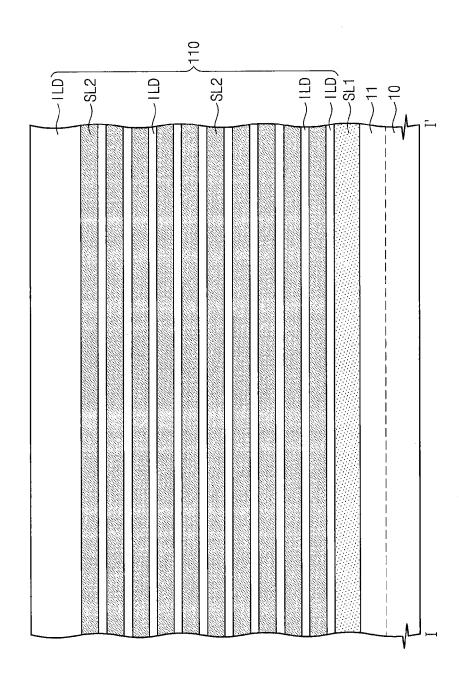

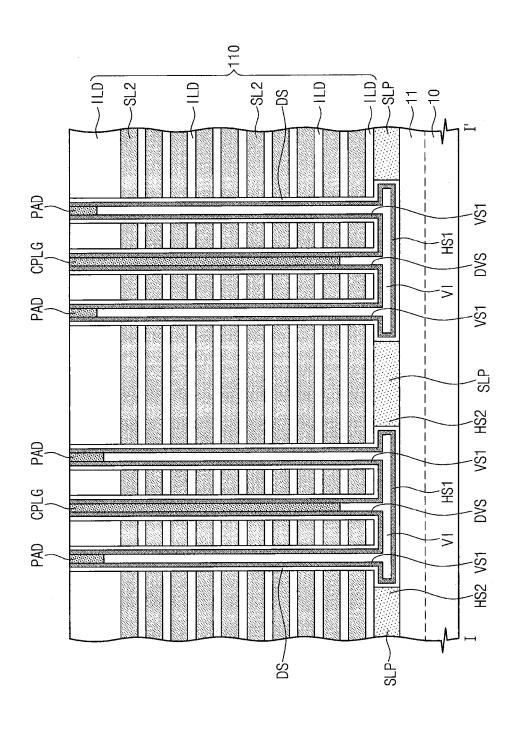

[0021] FIGS. 5 and 6 are cross-sectional views taken along lines I-I' and II-II' of FIG. 4A, respectively, to illustrate a 3D semiconductor device according to some embodiments of the inventive concepts.

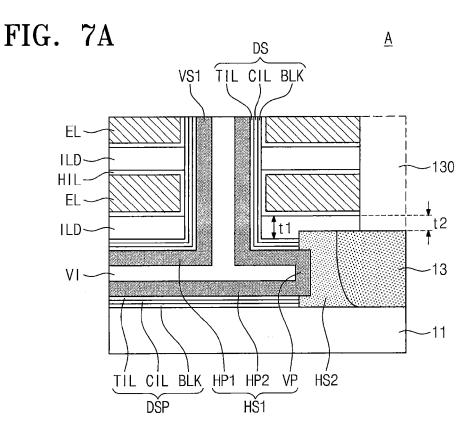

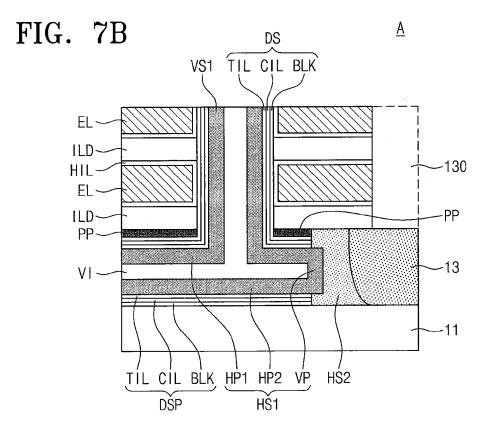

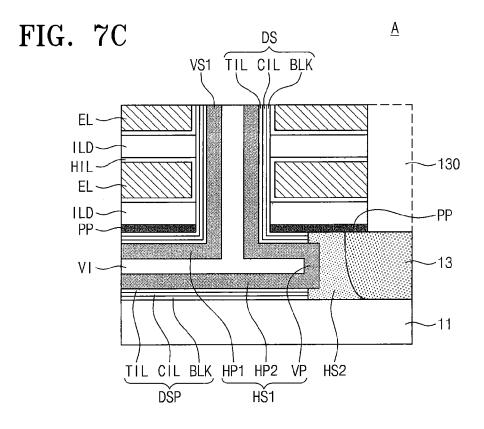

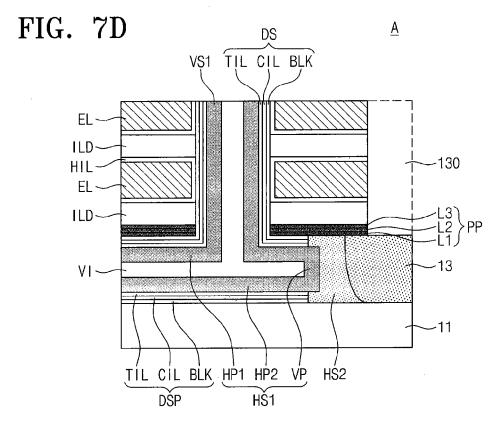

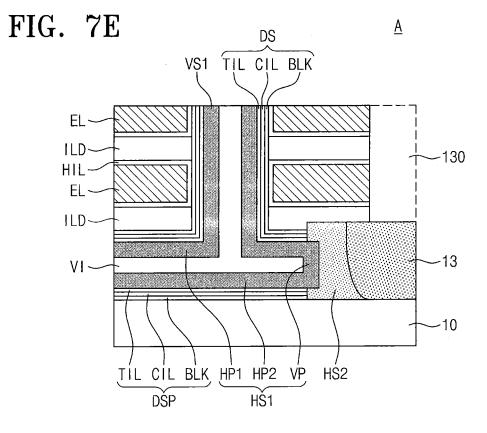

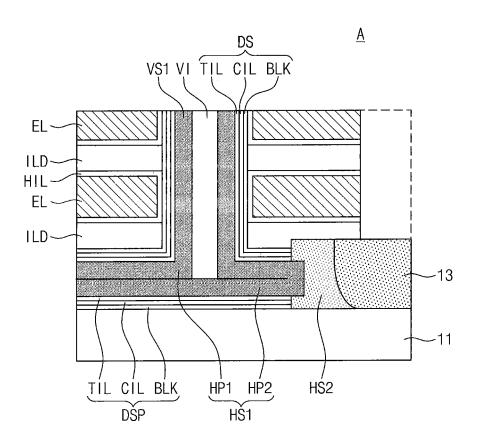

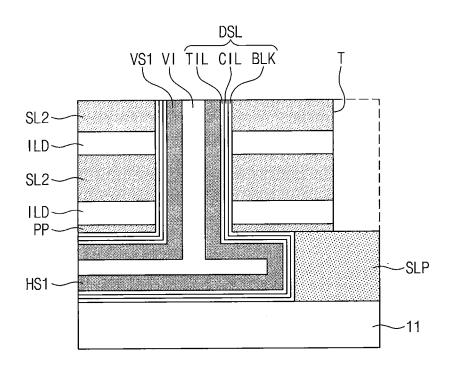

[0022] FIGS. 7A to 7E are enlarged views of a portion 'A' of FIG. 5.

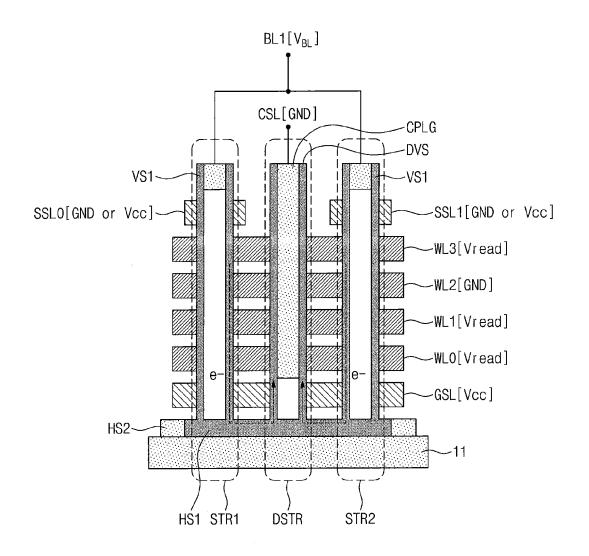

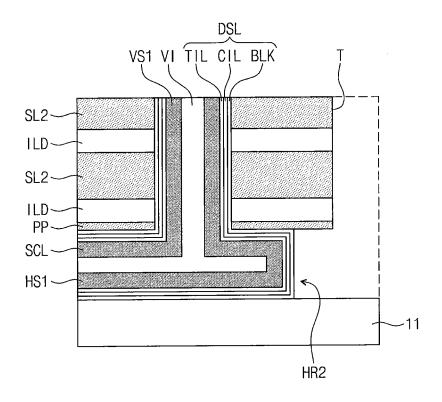

[0023] FIGS. 8A and 8B are views illustrating methods for operating a 3D semiconductor device according to some embodiments of the inventive concepts.

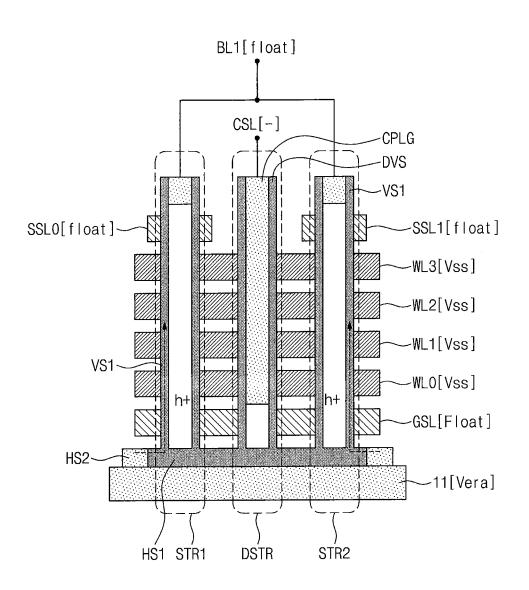

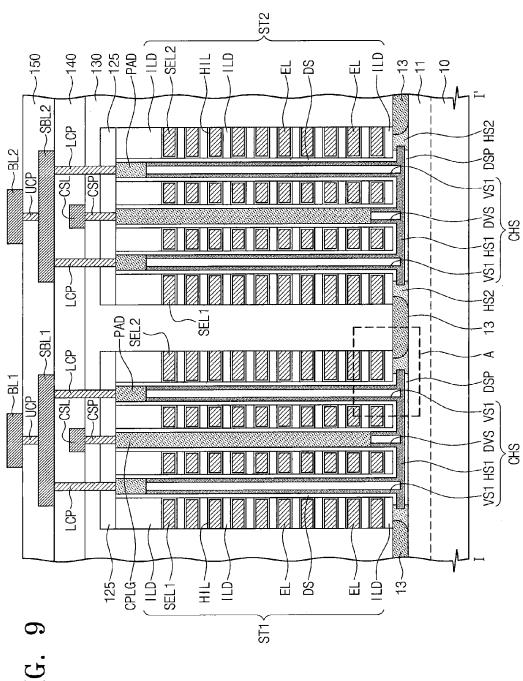

[0024] FIG. 9 is a cross-sectional view illustrating a 3D semiconductor device according to some embodiments of the inventive concepts.

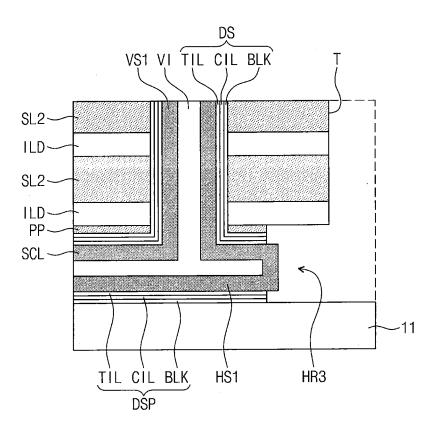

[0025] FIG. 10 is an enlarged view of a portion 'A' of FIG.

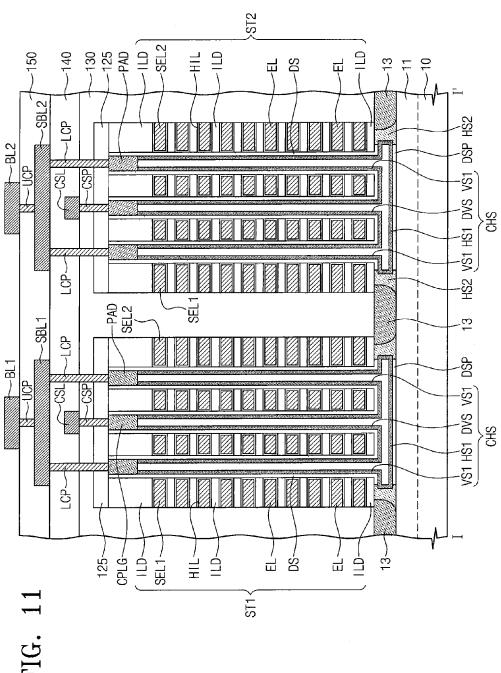

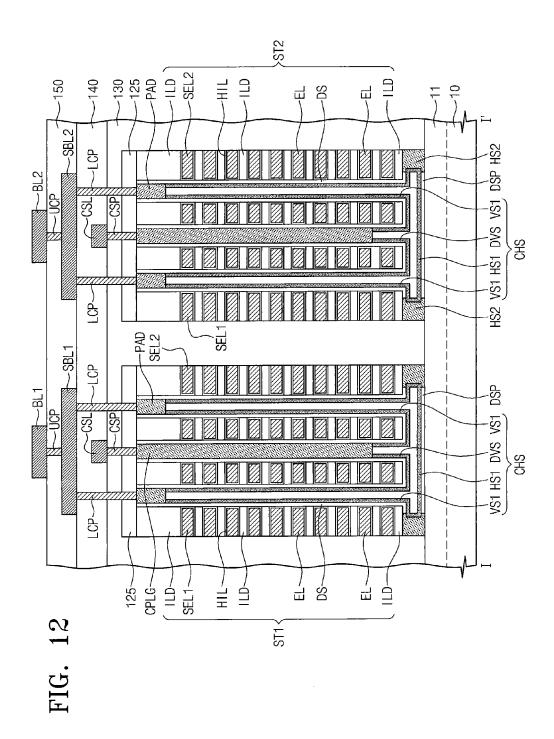

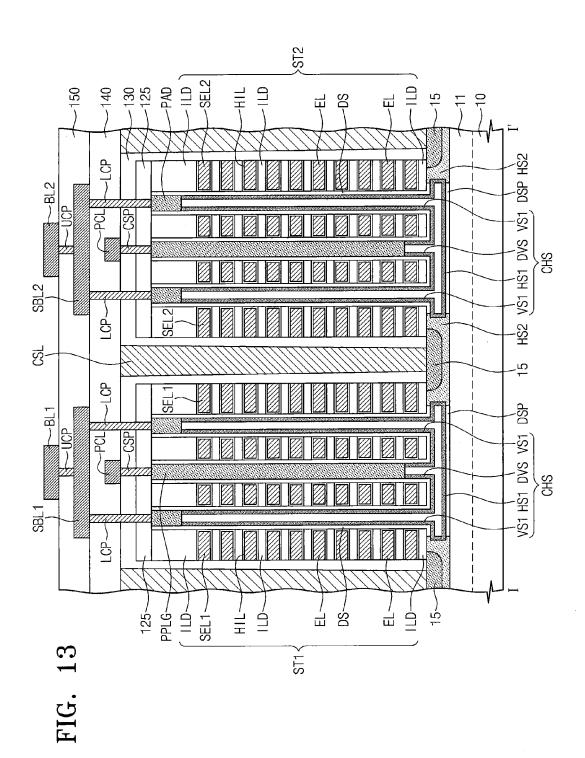

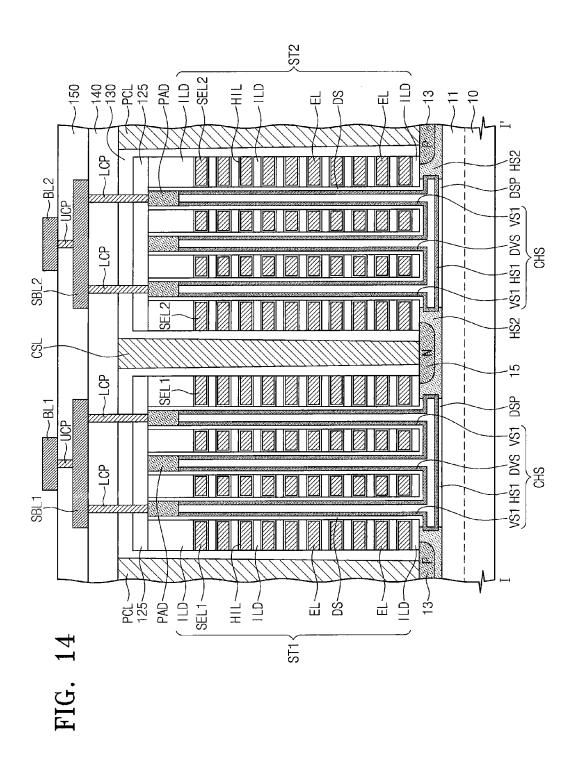

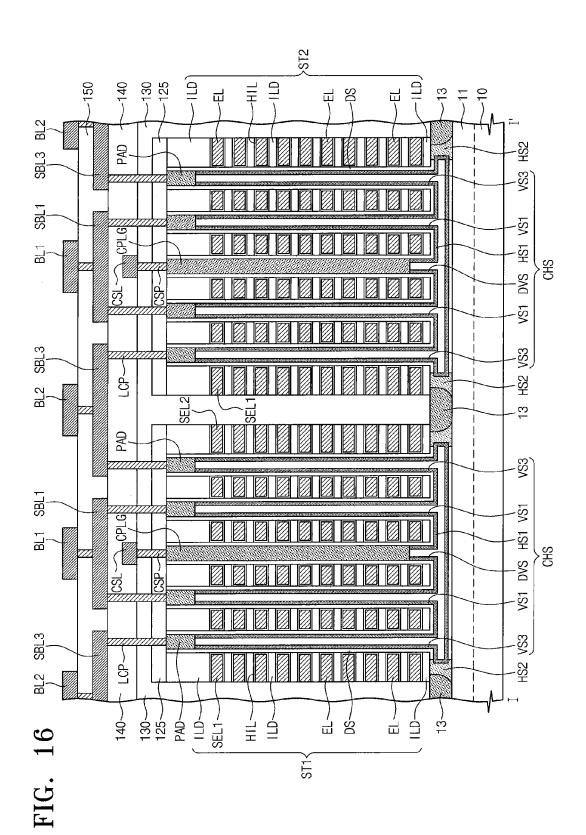

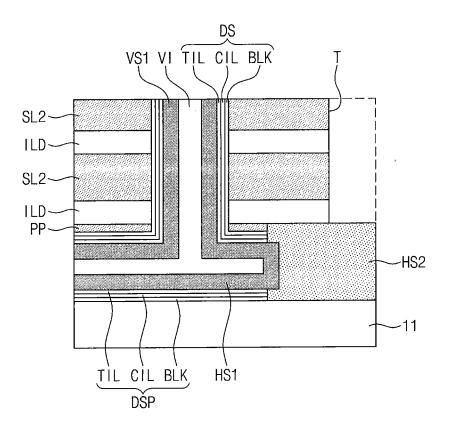

[0026] FIGS. 11, 12, 13, and 14 are cross-sectional views illustrating 3D semiconductor devices according to some embodiments of the inventive concepts.

[0027] FIG. 15 is a plan view illustrating a 3D semiconductor device according to some embodiments of the inventive concepts.

[0028] FIG. 16 is a cross-sectional view taken along a line I-I' of FIG. 15 to illustrate a 3D semiconductor device according to some embodiments of the inventive concepts. [0029] FIG. 17 is a schematic block diagram illustrating a 3D semiconductor device according to some embodiments of the inventive concepts.

[0030] FIG. 18 is a cross-sectional view illustrating a 3D semiconductor device according to some embodiments of the inventive concepts.

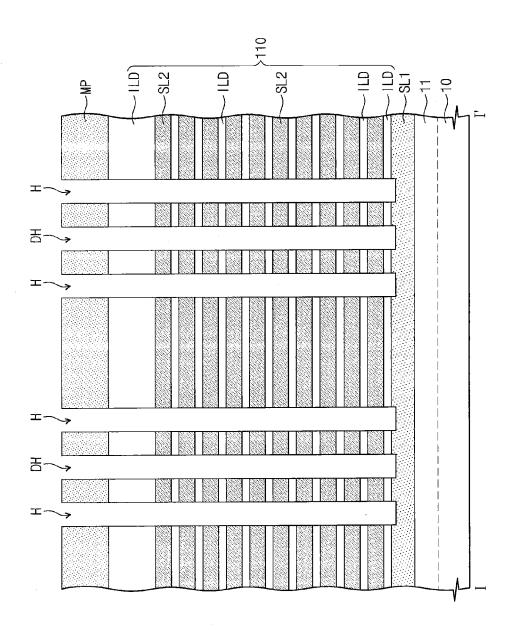

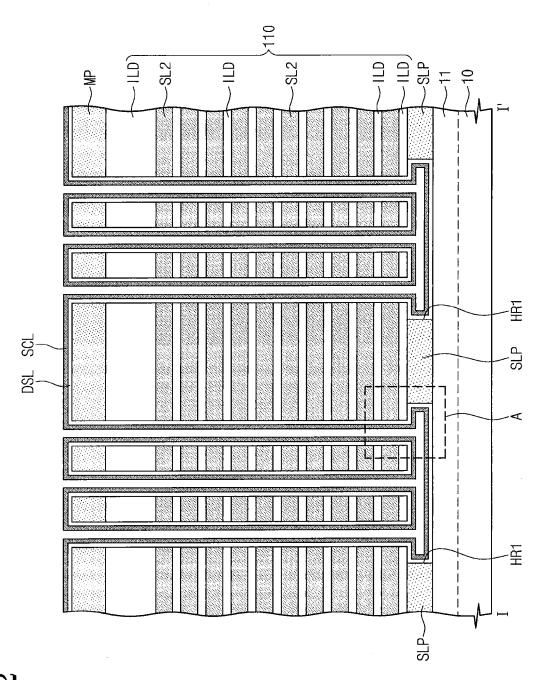

[0031] FIGS. 19 to 29 are cross-sectional views taken along the line I-I' of FIG. 4A to illustrate methods of manufacturing a 3D semiconductor device according to some embodiments of the inventive concepts.

[0032] FIGS. 30 to 35 are enlarged views of portions 'A' of FIGS. 21 to 26, respectively, to illustrate methods of manufacturing a 3D semiconductor device according to some embodiments of the inventive concepts.

[0033] FIGS. 36 to 40 are cross-sectional views illustrating methods of forming a conductive pad and a source plug of a 3D semiconductor device according to some embodiments of the inventive concepts.

## DETAILED DESCRIPTION OF THE EMBODIMENTS

[0034] The inventive concepts will now be described more fully hereinafter with reference to the accompanying drawings, in which exemplary embodiments of the inventive concepts are shown. The inventive concepts and methods of achieving them will be apparent from the following exemplary embodiments that will be described in more detail with reference to the accompanying drawings. The embodiments of the inventive concept may, however, be embodied in different forms and should not be constructed as limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the scope of the inventive concept to those skilled in the art.

[0035] The terminology used herein is for the purpose of describing particular embodiments only and is not intended to limit the invention. As used herein, the singular terms "a," "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. As used herein, the term "and/or" includes any and all combinations of one or more of the associated listed items. It will be understood that when an element is referred to as being "connected" or "coupled" to another element, it may be directly connected or coupled to the other element or intervening elements may be present.

[0036] Similarly, it will be understood that when an element such as a layer, region or substrate is referred to as being "on" another element, it can be directly on the other element or intervening elements may be present. In contrast, the term "directly" means that there are no intervening elements. It will be further understood that the terms "comprises", "comprising,", "includes" and/or "including", when used herein, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof. Additionally, exemplary embodiments are described herein with reference to cross-sectional views and/or plan views that are idealized exemplary views. Accordingly, shapes of exemplary views may be modified according to manufacturing techniques and/or allowable errors. Therefore, the embodiments of the inventive concepts are not limited to the specific shape illustrated in the exemplary views, but may include other shapes that may be created according to manufacturing processes.

[0037] Exemplary embodiments of aspects of the present inventive concepts explained and illustrated herein include their complementary counterparts. The same reference numerals or the same reference designators denote the same elements throughout the specification.

[0038] FIG. 1 is a schematic block diagram illustrating a three-dimensional (3D) semiconductor device according to some embodiments of the inventive concepts.

[0039] Referring to FIG. 1, a 3D semiconductor device may include a memory cell array 1, a row decoder 2, a page buffer 3, a column decoder 4, and a control circuit 5. The 3D semiconductor device may be a 3D semiconductor memory device.

[0040] The memory cell array 1 may include a plurality of memory blocks BLK0 to BLKn. Each of the memory blocks BLK0 to BLKn may include a plurality of memory cells, a plurality of word lines, and a plurality of bit lines. The word lines and the bit lines may be electrically connected to the memory cells.

[0041] The row decoder 2 may decode an address signal inputted from an external system to select one of the word lines. The address signal decoded in the row decoder 2 may be provided to a row driver (not shown). The row driver may provide a selected word line voltage and unselected word line voltages generated from a voltage generation circuit (not shown) to the selected word line and unselected word lines in response to a control signal of the control circuit 5. The row decoder 2 may be connected in common to the plurality of memory blocks BLK0 to BLKn and may provide driving signals to the word lines of one memory block selected by a block selection signal.

[0042] The page buffer 3 may be connected to the memory cell array 1 through the bit lines to sense data stored in the memory cells. The page buffer 3 may be connected to a bit line selected by an address signal decoded in the column decoder 4. According to an operation mode, the page buffer 3 may temporarily store data to be stored in the memory cells or may sense data stored in the memory cells. For example, the page buffer 3 may be operated as a write driver during a program operation mode and may be operated as a sense amplifier during a sensing operation mode. The page buffer 3 may receive power (e.g., a voltage or a current) from the control circuit 5 and may provide the received power to the selected bit line.

[0043] The column decoder 4 may provide a data-transmitting path between the page buffer 3 and an external device (e.g., a memory controller). The column decoder 4 may decode an address signal inputted from the external device to select one of the bit lines. The column decoder 4 may be connected in common to the plurality of memory blocks BLK0 to BLKn and may provide data to the bit lines of the memory block selected by the block selection signal. [0044] The control circuit 5 may control overall operations of the 3D semiconductor device. The control circuit 5 may receive control signals and an external voltage and may be operated in response to the received control signals. The control circuit 5 may include a voltage generator that generates voltages (e.g., a program voltage, a sensing voltage, and an erase voltage) necessary to inner operations by means of the external voltage. The control circuit 5 may control a sensing operation, a write operation, and/or an erase operation in response to the control signals.

[0045] FIG. 2 is a circuit diagram illustrating a cell array of a 3D semiconductor device according to some embodiments of the inventive concepts.

[0046] Referring to FIG. 2, a cell array of a 3D semiconductor device according to some embodiments of the inventive concepts may include a common source line CSL, a plurality of bit lines BL, and a plurality of cell strings CSTR connected between the common source line CSL and the bit lines BL.

[0047] The bit lines BL may be two-dimensionally arranged. A plurality of the cell strings CSTR may be connected in parallel to each of the bit lines BL. The cell strings CSTR may be connected in common to the common source line CSL. In other words, a plurality of the cell strings CSTR may be disposed between one common source line CSL and the plurality of bit lines BL. In some embodiments, the common source line CSL may include a plurality of common source lines CSL two-dimensionally arranged. The same voltage may be applied to the plurality of the common source lines CSL, or the common source lines CSL may be electrically controlled independently of each other.

[0048] Each of the cell strings CSTR may include a ground selection transistor GST connected to the common source line CSL, a string selection transistor SST connected to the bit line BL, and a plurality of memory cell transistors MCT interposed between the ground and string selection transistors GST and SST. The ground selection transistor GST, the memory cell transistors MCT, and the string selection transistor SST may be connected in series to each other in the order named.

[0049] The common source line CSL may be connected in common to sources of the ground selection transistors GST. A ground selection line GSL, a plurality of word lines WL0 to WL3 and a string selection line SSL which are disposed between the common source line CSL and the bit lines BL may be used as a gate electrode of the ground selection transistor GST, gate electrodes of the memory cell transistors MCT and a gate electrode of the string selection transistor SST, respectively. Each of the memory cell transistors MCT may include a data storage element. In addition, channel regions of the transistors constituting the cell strings CSTR may be electrically connected in common to a P-type well (P-well).

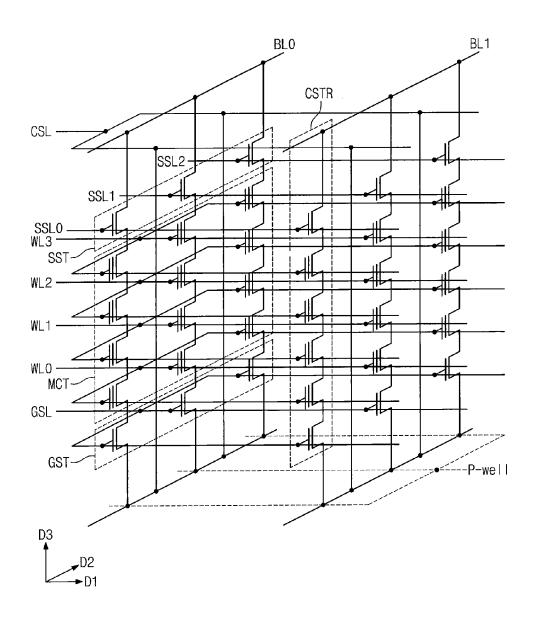

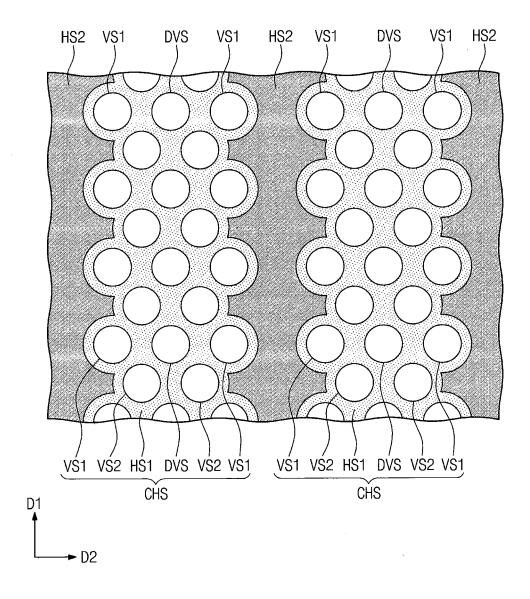

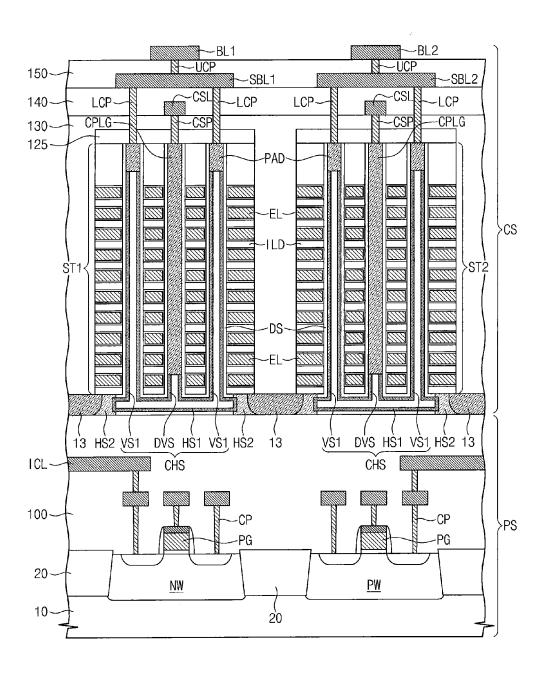

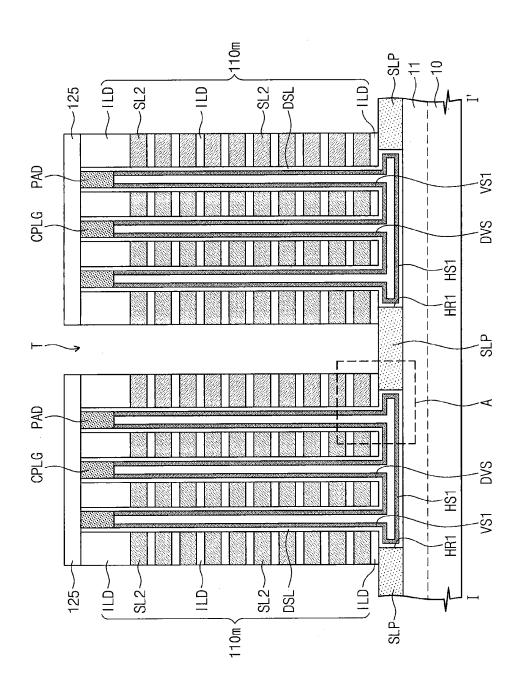

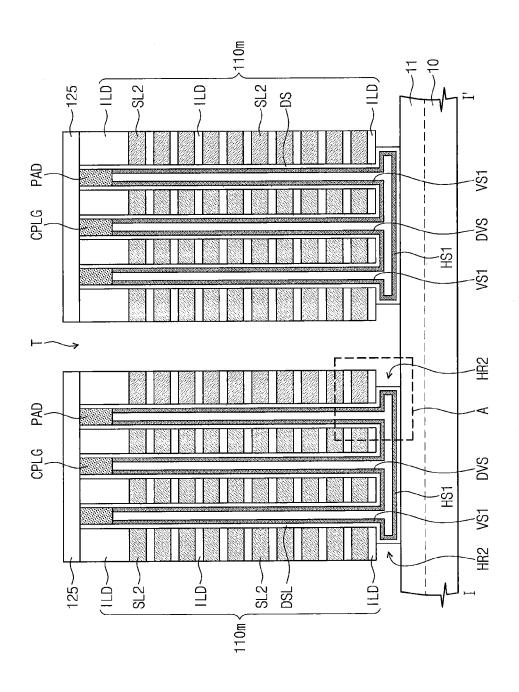

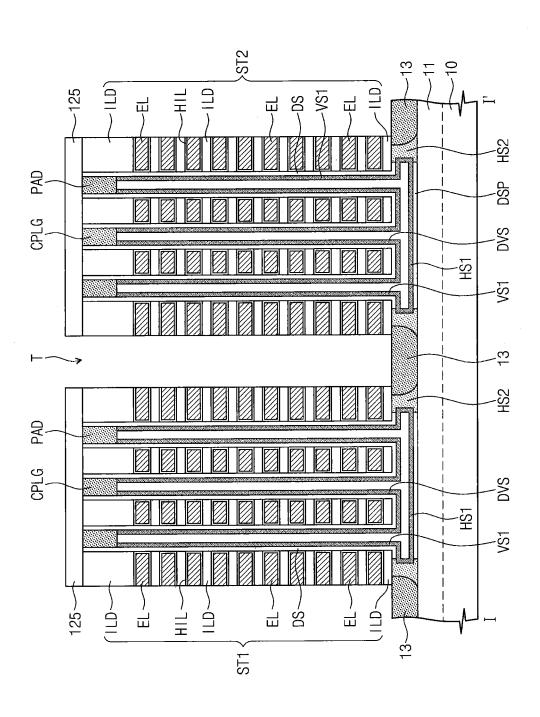

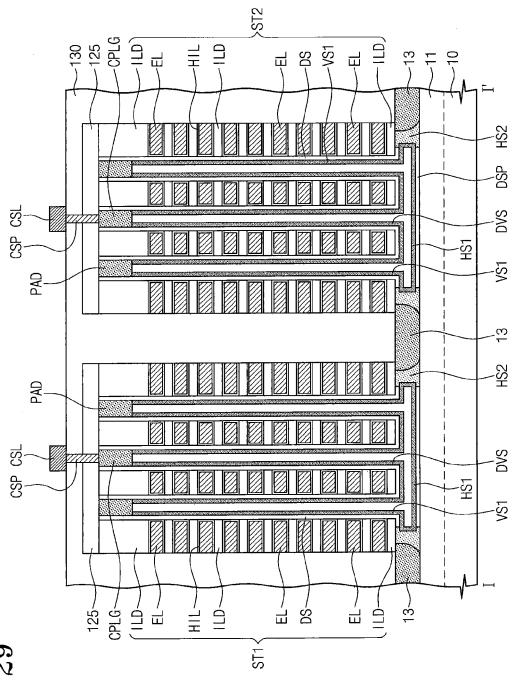

[0050] FIG. 3 is a plan view illustrating a 3D semiconductor device according to some embodiments of the inventive concepts. FIG. 4A is a plan view illustrating a cell array region of a 3D semiconductor device according to some embodiments of the inventive concepts. FIG. 4B is a plan view illustrating a channel structure of a 3D semiconductor device according to some embodiments of the inventive concepts. FIGS. 5 and 6 are cross-sectional views taken along lines I-I' and II-II' of FIG. 4A, respectively, to illustrate a 3D semiconductor device according to some embodiments of the inventive concepts. FIGS. 7A to 7E are enlarged views of a portion 'A' of FIG. 5.

[0051] Referring to FIGS. 3, 4A, 4B, 5, and 6, a substrate 10 may include cell array region CAR, contact regions CTR, and dummy regions DMY. The contact regions CTR may be disposed at both sides of the cell array region CAR in a first direction D1. The dummy regions DMY may be disposed at both sides of the cell array region CAR in a second direction D2 perpendicular to the first direction D1. A plurality of first

stack structures ST1 and a plurality of second stack structures ST2 may extend in the first direction D1 in parallel to each other on the substrate 10 and may be spaced apart from each other in the second direction D2. As illustrated in FIG. 3, the first stack structures ST1 and the second stack structures ST2 may be alternately arranged along the second direction D2 when viewed from a plan view. In some embodiments, the first and second directions D1 and D2 may be parallel to a top surface of the substrate 10.

[0052] In some embodiments, the substrate 10 may be formed of a semiconductor material and may include a well dopant layer 11 doped with dopants of a first conductivity type. For example, the substrate 10 may include at least one of silicon (Si), germanium (Ge), silicon-germanium (SiGe), gallium-arsenic (GaAs), indium-gallium-arsenic (InGaAs), aluminum-gallium-arsenic (AlGaAs), or any combination thereof. For example, the substrate 10 may be a bulk silicon substrate, a silicon-on-insulator (SOI) substrate, a germanium substrate, a germanium-on-insulator (GOI) substrate, a silicon-germanium substrate, and/or a substrate including an epitaxial layer obtained by performing a selective epitaxial growth (SEG) process.

[0053] In certain embodiments, the substrate 10 may include an insulating material and may include a single layer or a plurality of thin layers. For example, the substrate 10 may include at least one of a silicon oxide layer, a silicon nitride layer, or a low-k dielectric layer.

[0054] Each of the first and second stack structures ST1 and ST2 may include electrodes EL vertically stacked on the substrate 10 and insulating layers ILD disposed between the electrodes EL. In other words, the electrodes EL may be stacked along a third direction D3 perpendicular to the first and second directions D1 and D2. In some embodiments, the third direction D3 may be perpendicular to the top surface of the substrate 10. The electrodes EL of the first and second stack structures ST1 and ST2 may include a conductive material. For example, the electrodes EL may include at least one of a doped semiconductor (e.g., doped silicon), a metal (e.g., tungsten, copper, or aluminum), a conductive metal nitride (e.g., titanium nitride or tantalum nitride), or a transition metal (e.g., titanium or tantalum).

[0055] In some embodiments, the uppermost electrode of each of the first and second stack structures ST1 and ST2 may be divided into segments laterally spaced apart from each other. In other words, the uppermost electrode of each of the first and second stack structures ST1 and ST2 may include a first string selection electrode SEL1 and a second string selection electrode SEL2 which extend in the first direction D1 and are spaced apart from each other in the second direction D2, and a separation insulating pattern 115 may be disposed between the first and second string selection electrodes SEL1 and SEL2.

[0056] In each of the first and second stack structures ST1 and ST2, thicknesses of the insulating layers ILD may be varied according to characteristics of the 3D semiconductor device. In some embodiments, the thicknesses of the insulating layers ILD may be substantially equal to each other. In some embodiments, one or some of the insulating layers ILD may be thicker than another or others of the insulating layers ILD. In some embodiments, each of the insulating layers ILD may include at least one of a silicon oxide layer or a low-k dielectric layer. In some embodiments, the insulating layers ILD may include pores and/or air gaps.

[0057] In some embodiments, the 3D semiconductor device may be a vertical NAND flash memory device. In this case, some of the electrodes EL of each of the first and second stack structures ST1 and ST2 may be used as control gate electrodes of the memory cell transistors MCT of FIG. 2.

[0058] In some embodiments, the electrodes EL of each of the first and second stack structures ST1 and ST2 may be coupled to one channel structure CHS to constitute the memory cell transistors MCT of FIG. 2, the string selection transistors SST of FIG. 2, and the ground selection transistors GST of FIG. 2. In each of the first and second stack structures ST1 and ST2, the first and second string selection electrode SEL1 and SEL2 corresponding to the uppermost electrode may be used as the gate electrodes of the string selection transistors SST of FIG. 2 controlling electrical connection between a bit line BL and the channel structure CHS, the lowermost electrode EL may be used as the gate electrodes of the ground selection transistors GST of FIG. 2 controlling electrical connection between the channel structure CHS and the common source line CSL. The electrodes EL between the uppermost electrode and the lowermost electrode may be used as the control gate electrodes of the memory cell transistors MCT of FIG. 2 and word lines connecting the control gate electrodes.

[0059] In some embodiments, one channel structure CHS may include first vertical channels VS1, second vertical channels VS2, dummy vertical channels DVS, and a first horizontal channel HS1. The first and second vertical channels VS1 and VS2 and the dummy vertical channels DVS may penetrate each of the first and second stack structures ST1 and ST2. The first horizontal channel HS1 may be disposed under each of the first and second stack structures ST1 and ST2 and may laterally or horizontally connect the first and second vertical channels VS1 and VS2 and the dummy vertical channels DVS to each other.

[0060] The first vertical channels VS1 may be spaced apart from each other and may be arranged in the first direction D1 and the second direction D2. The second vertical channels VS2 may be spaced apart from each other and may be arranged in the first direction D1 and the second direction D2. At this time, each of the second vertical channels VS2 may be disposed at a position shifted from a corresponding one of the first vertical channels VS1 in a direction diagonal to the second direction D2. In other words, the first and second vertical channels VS1 and VS2 adjacent one another may be arranged in a zigzag form along the first direction D1. The dummy vertical channels DVS of each of the first and second stack structures ST1 and ST2 may be arranged in the first direction D1 and may be disposed between the first and second string selection electrodes SEL1 and SEL2. Each of the dummy vertical channels DVS may be disposed between the first vertical channels VS1 arranged in the second direction D2 and may be aligned with each of the second vertical channels VS2 adjacent thereto in a direction diagonal to the second direction D2. In some embodiments, each of the vertical channels VS1, VS2, and DVS may have a hollow pipe or macaroni shape. In certain embodiments, each of the vertical channels VS1, VS2, and DVS may have a cylindrical shape.

[0061] In some embodiments, the first horizontal channel HS1 may extend from bottom ends of the vertical channels VS1, VS2, and DVS so as to be disposed under each of the first and second stack structures ST1 and ST2. The first

horizontal channel HS1 may extend along the first direction D1. In other words, the first horizontal channel HS1 may be connected in common to the first and second vertical channels VS1 and VS2 arranged in the first and second directions D1 and D2 and the dummy vertical channels DVS arranged in the first direction D1. In some embodiments, the first and second vertical channels VS1 and VS2, the dummy vertical channels DVS, and the first horizontal channel HS1 may constitute a single semiconductor layer that continuously extends without an interface.

[0062] In some embodiments, the first horizontal channel HS1 may have a hollow pipe or macaroni shape connected to the vertical channels VS1, VS2, and DVS. For example, the first and second vertical channels VS1 and VS2, the dummy vertical channels DVS, and the first horizontal channel HS1 may constitute a pipe shape which is in one body.

[0063] As illustrated in FIG. 4B, the first horizontal channel HS1 may overlap with the first or second stack structure ST1 or ST2 when viewed from a plan view. In addition, the first horizontal channel HS1 may have rounded sidewalls, and each rounded sidewall of the first horizontal channel HS1 may be in contact with a second horizontal channel HS2. A width of the first horizontal channel HS1 may be smaller than that of each of the first and second stack structures ST1 and ST2.

[0064] In some embodiments, the first and second vertical channels VS1 and VS2, the dummy vertical channels DVS, and the first horizontal channel HS1 may be formed of a semiconductor material and may be undoped or doped with dopants of the same conductivity type (i.e., the first conductivity type) as the well dopant layer 11. The vertical channels VS1, VS2, and DVS and the first horizontal channel HS1 may have a crystal structure including at least one of a single-crystalline structure, an amorphous structure, or a poly-crystalline structure.

[0065] In some embodiments, first and second vertical channels VS1 and VS2, the dummy vertical channels DVS, and the first horizontal channel HS1 may constitute the single semiconductor layer not having an interface, as described above. The semiconductor layer may have a substantially uniform thickness and may extend from inner sidewalls of the first or second stack structure ST1 or ST2 onto a bottom surface of the first or second stack structure ST1 or ST2. In other words, thicknesses of the first and second vertical channels VS1 and VS2 may be substantially equal to a thickness of the first horizontal channel HS1.

[0066] A filling insulation pattern VI may fill inner spaces of the vertical channels VS1, VS2, and DVS and the first horizontal channel HS1. For example, the filling insulation pattern VI may extend from the inner spaces of the vertical channels VS1, VS2, and DVS into the inner space of the first horizontal channel HS1.

[0067] The second horizontal channels HS2 may be disposed at both sides of the first horizontal channel HS1 of the channel structure CHS to connect the first horizontal channel HS1 to the well dopant layer 11. In some embodiments, the second horizontal channel HS2 may be formed of a semiconductor material and may be undoped or doped with dopants of the same conductivity type (i.e., the first conductivity type) as the well dopant layer 11. The second horizontal channel HS2 may have a crystal structure including at least one of a single-crystalline structure, an amorphous structure, or a poly-crystalline structure.

[0068] In more detail, the second horizontal channel HS2 may be disposed between the first and second stack structures ST1 and ST2 in a plan view and may extend in parallel to the first horizontal channel HS1 along the first direction D1. The second horizontal channels HS2 may be in contact with both sidewalls of the first horizontal channel HS1 below the first and second stack structures ST1 and ST2. An interface may exist between the first horizontal channel HS1 and the second horizontal channel HS2 which are formed of semiconductor materials. The second horizontal channel HS2 may be electrically connected to the vertical channels VS1, VS2, and DVS through the first horizontal channel HS1.

[0069] The second horizontal channel HS2 may include a dopant region 13 that is disposed between the first and second stack structures ST1 and ST2 when viewed from a plan view. Here, the dopant region 13 may be doped with dopants of the first conductivity type. A dopant concentration of the dopant region 13 may be higher than that of the second horizontal channel HS2.

[0070] In some embodiments, conductive pads PAD may be disposed on top ends of the first and second vertical channels VS1 and VS2, and source plugs CPLG may be disposed on top ends of the dummy vertical channels DVS. In some embodiments, the top ends of the vertical channels VS1, VS2, and DVS may be lower than the top surface of each of the first and second stack structures ST1 and ST2, and top surfaces of the conductive pad PAD and the source plug CPLG may be substantially coplanar with the top surface of each of the first and second stack structures ST1 and ST2. A vertical length of each of the source plugs CPLG may be greater than those of the conductive pads PAD. In other words, bottom surfaces of the conductive pads PAD may be higher than the top surface of the uppermost electrode SEL1 and SEL2, and bottom surfaces of the source plugs CPLG may be lower than the bottom surface of the uppermost electrode SEL1 and SEL2. For example, the source plug CPLG may vertically extend toward the substrate 10 such that the bottom surface of the source plug CPLG is adjacent the first horizontal channel HS1.

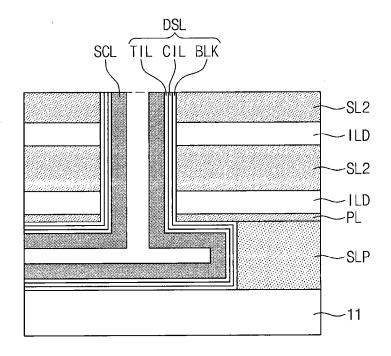

[0071] The conductive pads PAD and the source plugs CPLG may be dopant regions doped with dopants or may be formed of a conductive material. In some embodiments, the conductive pads PAD and the source plugs CPLG may have a second conductivity type opposite to the first conductivity type of the dopant region 13 and the well dopant layer 11. [0072] In some embodiments, a data storage layer DS may be disposed between each of the vertical channels VS1, VS2, and DVS and each of the first and second stack structures ST1 and ST2 and may extend between the first horizontal channel HS1 and a bottom surface of each of the first and second stack structures ST1 and ST2. In addition, a residual data storage pattern DSP may be disposed between the first horizontal channel HS1 and the well dopant layer 11 and may be spaced apart from the data storage layer DS.

[0073] In some embodiments, when the 3D semiconductor device is the vertical NAND flash memory device, each of the data storage layer DS and the residual data storage pattern DSP may include a tunnel insulating layer TIL, a charge storage layer CIL, and a blocking insulating layer BLK, as illustrated in FIGS. 7A to 7E. Data stored in the data storage layer DS may be changed using Flower-Nordheim tunneling caused by a voltage difference between the electrode EL and each of the first and second vertical channels

VS1 and VS2 including the semiconductor material. In some embodiments, the data storage layer DS may be a thin layer that is capable of storing data based on other operation principles. For example, the data storage layer DS may be a thin layer for a phase-change memory cell and/or a thin layer for a variable resistance memory cell.

[0074] A horizontal insulating pattern HIL may extend from between the data storage layer DS and each of the electrodes EL onto top and bottom surfaces of each of the electrodes EL. The horizontal insulating pattern HIL on top and bottom surfaces of the first and second string selection electrodes SEL1 and SEL2 may further extend between the separation insulating pattern 115 and the first and second string selection electrodes SEL1 and SEL2. In some embodiments, when the 3D semiconductor device is the vertical NAND flash memory device, the horizontal insulating pattern HIL may be used as a blocking layer.

[0075] A capping insulating pattern 125 may be disposed on each of the first and second stack structures ST1 and ST2 to cover top surfaces of the conductive pads PAD and top surfaces of the source plugs CPLG.

[0076] A filling insulation layer 130 may be disposed on an entire top surface of the substrate 10 to cover the first and second stack structures ST1 and ST2 and to completely fill a space between the first and second stack structures ST1 and ST2. In some embodiments, the filling insulation layer 130 may be in contact with a top surface of the second horizontal channel HS2, i.e., a top surface of the dopant region 13.

[0077] A common source line CSL extending in the first direction D1 may be disposed on the filling insulation layer 130. The common source line CSL may be connected to the source plugs CPLG through contact plugs CSP. The common source line CSL may be disposed on each of the first and second stack structures ST1 and ST2 and may be electrically connected in common to the dummy vertical channels DVS arranged along the first direction D1.

[0078] A first insulating layer 140 may be disposed on the filling insulating layer 130 to cover the common source lines CSL. First, second, third, and fourth assistant interconnections SBL1, SBL2, SBL3, and SBL4 may be disposed on the first insulating layer 140. The first and third assistant interconnections SBL1 and SBL3 may be disposed on the first stack structure ST1, and the second and fourth assistant interconnections SBL2 and SBL4 may be disposed on the second stack structure ST2. The first and third assistant interconnections SBL1 and SBL3 may intersect the common source line CSL disposed on the first stack structure ST1, and the second and fourth assistant interconnections SBL2 and SBL4 may intersect the common source line CSL disposed on the second stack structure ST2.

[0079] The first assistant interconnections SBL1 may be electrically connected to the first vertical channels VS1 penetrating the first stack structure ST1 through lower contact plugs LCP. The third assistant interconnections SBL3 may be electrically connected to the second vertical channels VS2 penetrating the first stack structure ST1 through lower contact plugs LCP.

[0080] The second assistant interconnections SBL2 may be electrically connected to the first vertical channels VS1 penetrating the second stack structure ST2 through lower contact plugs LCP. The fourth assistant interconnections SBL4 may be electrically connected to the second vertical

channels VS2 penetrating the second stack structure ST2 through lower contact plugs LCP.

[0081] A second insulating layer 150 may be disposed on the first insulating layer 140 to cover the first to fourth assistant interconnections SBL1 to SBL4, and first and second bit lines BL1 and BL2 may be disposed on the second insulating layer 150. The first and second bit lines BL1 and BL2 may extend in the second direction D2 and may be alternately arranged along the first direction D1.

[0082] The first bit lines BL1 may be connected to the first assistant interconnections SBL1 and the third assistant interconnections SBL3 through upper contact plugs UCP, and the second bit lines BL2 may be connected to the second assistant interconnections SBL2 and the fourth assistant interconnections SBL4 through upper contact plugs UCP.

[0083] The channel structures according to various embodiments of the inventive concepts will be described in detail with reference to FIGS. 7A to 7E.

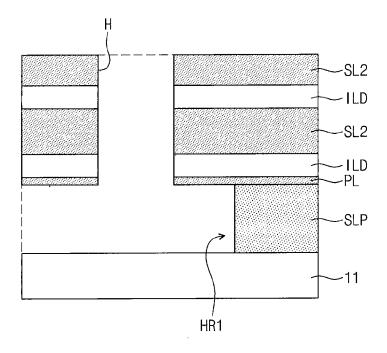

[0084] Referring to FIGS. 7A to 7E, the first and second vertical channels VS1 and VS2 may be continuously connected to the first horizontal channel HS1 without an interface therebetween. In some embodiments, the first horizontal channel HS1 may include an upper horizontal portion HP1, a lower horizontal portion HP2, and wall portions VP. The upper and lower horizontal portions HP1 and HP2 may be spaced apart from each other by the filling insulation pattern VI. One of the wall portions VP may be connected between one end of the upper horizontal portion HP1 and one end of the lower horizontal portion HP2, and the other of the wall portions VP may be connected to between another end of the upper horizontal portion HP1 and another end of the lower horizontal portion HP2. The upper and lower horizontal portions HP1 and HP2 and the wall portions VP may have a substantially uniform thickness. The second horizontal channels HS2 may be disposed at both sides of the first horizontal channel HS1 so as to be in direct contact with the wall portions VP of the first horizontal channel HS1.

[0085] Referring to FIGS. 7A to 7D, the second horizontal channel HS2 may be in direct contact with the well dopant layer 11. The second horizontal channel HS2 may be doped with dopants of the first conductivity type, and the dopant concentration of the second horizontal channel HS2 may be lower than or substantially equal to that of the well dopant layer 11. In the case in which the dopant concentration of the second horizontal channel HS2 is lower than that of the well dopant layer 11, the dopant region 13 of the first conductivity type may be disposed in the second horizontal channel HS2. Here, the dopant region 13 of the first conductivity type may extend in the first direction D1 and may be in contact with the well dopant layer 11. The dopant concentration of the dopant region 13 may be substantially equal to that of the well dopant layer 11. In other words, during an erase operation of the vertical NAND flash memory device, an erase voltage applied to the well dopant layer 11 may be provided to the dopant region 13 of the first conductivity type.

[0086] Referring to FIG. 7E, the first and second stack structures ST1 and ST2, the first and second vertical channels VS1 and VS2, the dummy vertical channels DVS, and the first and second horizontal channels HS1 and HS2 may be disposed on the substrate 10 formed of an insulating material. Here, the second horizontal channel HS2 may be in contact with the substrate 10 formed of the insulating

material and may include the dopant region 13 of the first conductivity type. In this case, the erase voltage may be applied to the dopant region 13 of the first conductivity type during the erase operation of the vertical NAND flash memory device.

[0087] The data storage layer DS may extend from between the stack structure ST1 or ST2 and each of the first and second vertical channels VS1 and VS2 into between the first horizontal channel HS1 and the lowermost insulating layer ILD. The residual data storage pattern DSP may be disposed between the well dopant layer 11 and the lower horizontal portion HP2 of the first horizontal channel HS1. The data storage layer DS may have the same thin layer(s) as the residual data storage pattern DSP. In some embodiments, each of the data storage layer DS and the residual data storage pattern DSP may include the tunnel insulating layer TIL, the charge storage layer CIL, and the blocking insulating layer BLK.

[0088] In the data storage layer DS and the residual data storage pattern DSP, the charge storage layer CIL may include at least one of a trap site-rich insulating layer, a floating gate electrode, or an insulating layer including conductive nano dots (or nano particles). The charge storage layer CIL may be formed using a chemical vapor deposition (CVD) technique and/or an atomic layer deposition (ALD) technique. For example, the charge storage layer CIL may include at least one of, but not limited to, a silicon nitride layer, a silicon oxynitride layer, a silicon-rich nitride layer, a nano-crystalline silicon layer, and/or a laminated trap layer. The tunnel insulating layer TIL may include at least one of materials having energy band gaps greater than that of the charge storage layer CIL and may be formed by a CVD process and/or an ALD process. For example, the tunnel insulating layer TIL may include a silicon oxide layer formed using the CVD process or the ALD process. In some embodiments, the tunnel insulating layer TIL may include one of high-k dielectric layers such as an aluminum oxide layer and a hafnium oxide layer. The blocking insulating layer BLK may include at least one of materials having of which energy band gaps are smaller than that of the tunnel insulating layer TIL and greater than that of the charge storage layer CIL. For example, the blocking insulating layer BLK may include at least one of high-k dielectric layers such as an aluminum oxide layer and a hafnium oxide layer. The blocking insulating layer BLK may be formed using at least one of a CVD process or an ALD process. At least one of the layers TIL, CIL, and BLK may be formed using a wet oxidation process. In some embodiments, the blocking insulating layer BLK may include first and second blocking insulating layers. In this case, the first blocking insulating layer may include at least one of the high-k dielectric layers such as an aluminum oxide layer and a hafnium oxide layer, and the second blocking insulating layer may include a material having a lower dielectric constant than the first blocking insulating layer. Some embodiments provide that the second blocking insulating layer may include at least one of the high-k dielectric layers, and the first blocking insulating layer may include a material having a lower dielectric constant than the second blocking insulating layer.

[0089] According to some embodiments illustrated in FIG. 7A, the second horizontal channel HS2 may be in contact with the sidewall of the first horizontal channel HS1 and a portion of the data storage layer DS. In each of the first and

second stack structures ST1 and ST2, the lowermost insulating layer ILD may have a first thickness t1 on the first horizontal channel HS1 and may have a second thickness t2 on the second horizontal channel HS2. Here, the second thickness t2 may be smaller than the first thickness t1.

[0090] According to some embodiments illustrated in FIG. 7B, a protection insulating pattern PP may be disposed between a bottom surface of the lowermost insulating layer ILD and the data storage layer DS. The second horizontal channel HS2 may be in contact with the sidewall of the first horizontal channel HS1, a portion of the data storage layer DS, and the protection insulating pattern PP. The protection insulating pattern PP may be formed of a different material from the lowermost insulating layer ILD. Here, the lowermost insulating layer ILD may be in contact with a portion of the second horizontal channel HS2 and may have a substantially uniform thickness.

[0091] According to some embodiments illustrated in FIG. 7C, a protection insulating pattern PP may be disposed between the bottom surface of the lowermost insulating layer ILD and the data storage layer DS and between the second horizontal channel HS2 and the lowermost insulating layer ILD. In other words, the second horizontal channel HS2 may be in contact with the sidewall of the first horizontal channel HS1 and a portion of the data storage layer DS and may be spaced apart from the lowermost insulating layer ILD.

[0092] According to some embodiments illustrated in FIG. 7D, a protection insulating pattern PP may be disposed between the bottom surface of the lowermost insulating layer ILD and the data storage layer DS and may include a plurality of thin layers. For example, the protection insulating pattern PP may have the same stacked structure as the data storage layer DS. For example, the protection insulating pattern PP may include a silicon oxide layer L1, a silicon nitride layer L2, and a silicon oxide layer L3 which are sequentially stacked. The protection insulating pattern PP may extend between the lowermost insulating layer ILD and the second horizontal channel HS2.

[0093] FIGS. 8A and 8B are views illustrating methods for operating a 3D semiconductor device according to some embodiments of the inventive concepts. FIG. 8A is a view illustrating a read operation of a 3D semiconductor device, and FIG. 8B is a view illustrating an erase operation of a 3D semiconductor device.

[0094] Referring to FIGS. 8A and 8B, a first string selection line SSL0, word lines WL0 to WL3, and a ground selection line GSL may be coupled to one of the first vertical channels VS1 to constitute a first string STR1. A second string selection line SSL1, the word lines WL0 to WL3, and the ground selection line GSL may be coupled to another of the first vertical channels VS1 to constitute a second string STR2. The word lines WL0 to WL3 and the ground selection line GSL may be coupled to the dummy vertical channel DVS to constitute a dummy string DSTR. The top ends of the dummy vertical channel DVS may be electrically connected to the source plug CPLG. The top ends of the first and second vertical channels VS1 and VS2 may be electrically connected to the first bit line BL1. The first and second strings STR1 and STR2 may be connected in common to the common source line CSL through the first horizontal channel HS1 and the dummy vertical channel DVS. In addition, the first and second strings STR1 and STR2 may be connected to the second horizontal channel HS2 and the well dopant layer (11) through the first horizontal channel HS1. [0095] According to some embodiments of the inventive concepts, a path through which electrons move during the read operation may be different from a path through which holes move during the erase operation.

[0096] Referring to FIG. 8A, in the read operation of the 3D semiconductor device, a ground voltage GND may be applied to a selected word line WL2 and a read voltage Vread may be applied to unselected word lines WL0, WL1, and WL3. Here, the read voltage Vread may be higher than threshold voltages of the transistors to generate inversion layers in the first vertical channels VS1. A predetermined bit line voltage  $V_{BL}$  may be applied to a selected bit line BL1, and the ground voltage GND may be applied to unselected bit lines. The power supply voltage Vcc for turning on the string and ground selection transistors may be applied to a selected string selection line SSL0 or SSL1 and a ground selection line GSL. The ground voltage GND may be applied to an unselected string selection line SSL0 or SSL1, the common source line CSL, and the well dopant layer (11). [0097] Under the above voltage conditions, a read current path may be generated between the selected bit line BL1 and the common source line CSL during the read operation. When the first string selection line SSL0 is selected, a flow of electrons may occur through the first vertical channel VS1 of the first string STR1, the first horizontal channel HS1, and the dummy vertical channel DVS between the selected bit line BL1 and the common source line CSL. When the second string selection line SSL1 is selected, a flow of electrons may occur through the first vertical channel VS1 of the second string STR2, the first horizontal channel HS1, and the dummy vertical channel DVS between the selected bit line BL1 and the common source line CSL.

[0098] Referring to FIG. 8B, in the erase operation of the 3D semiconductor device, a ground voltage Vss may be applied to the word lines WL0 to WL3. In addition, the bit line BL1, the string selection lines SSL0 and SSL1, and the common source line CSL may be floated. Moreover, an erase voltage Vera may be applied to the well dopant layer (11) through a well pickup region 11p of FIG. 3. The erase voltage Vera may be transmitted to the second horizontal channel HS2.

[0099] Under these voltage conditions, holes may be provided into the first and second vertical channels VS1 and VS2 through the first and second horizontal channels HS1 and HS2 during the erase operation. In other words, the path through the holes are provided may be generated in the first and second horizontal channels HS1 and HS2 and the first and second vertical channels VS1 and VS2 during the erase operation.

[0100] FIG. 9 is a cross-sectional view illustrating a 3D semiconductor device according to some embodiments of the inventive concepts. FIG. 10 is an enlarged view of a portion 'A' of FIG. 9. In the present embodiment, the descriptions to the same technical features as in the embodiment of FIGS. 3, 4A, 4B, 5, and 6 will be omitted or mentioned briefly for the purpose of ease and convenience in explanation.

[0101] Referring to FIGS. 9 and 10, the first and second stack structures ST1 and ST2 extending in the first direction D1 may be disposed on the substrate 10 so as to be spaced apart from each other in the second direction D2. The channel structure CHS may be provided to each of the first

and second stack structures ST1 and ST2. The channel structure CHS may include the first and second vertical channels VS1 and VS2, the dummy vertical channels DVS, and the first horizontal channel HS1.

[0102] The first and second vertical channels VS1 and VS2 and the dummy vertical channels DVS may penetrate each of the first and second stack structures ST1 and ST2. and the first horizontal channel HS1 may be disposed under each of the first and second stack structures ST1 and ST2. The first horizontal channel HS1 may continuously extend from the vertical channels VS1, VS2, and DVS and may extend in parallel to each of the first and second stack structures ST1 and ST2 along the first direction D1, as described with reference to FIGS. 4A and 4B. The second horizontal channels HS2 may be disposed at both sides of the first horizontal channel HS1. The second horizontal channels HS2 may extend in the first direction D1 and may be in contact with both sidewalls of the first horizontal channel HS1, respectively. The first horizontal channel HS1 may be connected to the first and second vertical channels VS1 and VS2 without an interface therebetween, but an interface may be formed between the first horizontal channel HS1 and the second horizontal channel HS2 by semiconductor crystals.

[0103] In some embodiments, the first horizontal channel HS1 may completely fill a space between the substrate 10 and each of the first and second stack structures ST1 and ST2 without the filling insulation pattern VI. In more detail, the first horizontal channel HS1 may have upper and lower horizontal portions HP1 and HP2 that are in contact with each other. At this time, an interface may be formed between the upper and lower horizontal portions HP1 and HP2 by semiconductor crystals. The upper horizontal portion HP1 may cover the data storage layer DS covering the bottom surface of each of the first and second stack structures ST1 and ST2, and the lower horizontal portion HP2 may cover the residual data storage pattern DSP disposed on the substrate 10.

[0104] The filling insulation pattern VI may fill the inner space of each of the vertical channels VS1, VS2, and DVS having the hollow pipe shapes. The filling insulation patterns VI of the vertical channels VS1, VS2, and DVS may be in contact with the first horizontal channel HS1 and may be separated from each other.

[0105] The data storage layer DS may be disposed between each of the first and second stack structures ST1 and ST2 and the vertical channels VS1, VS2, and DVS. The data storage layer DS may extend onto the bottom surface of the lowermost insulating layer ILD of each of the first and second stack structures ST1 and ST2.

[0106] The conductive pads PAD may be respectively disposed on the first and second vertical channels VS1 and VS2, and the source plugs CPLG may be respectively disposed on the dummy vertical channels DVS. In some embodiments, the conductive pads PAD and the source plugs CPLG may be dopant regions. In this case, the conductive pads PAD and the source plugs CPLG may have the second conductivity type opposite to the first conductivity type of the dopant region 13 formed in the second horizontal channel HS2.

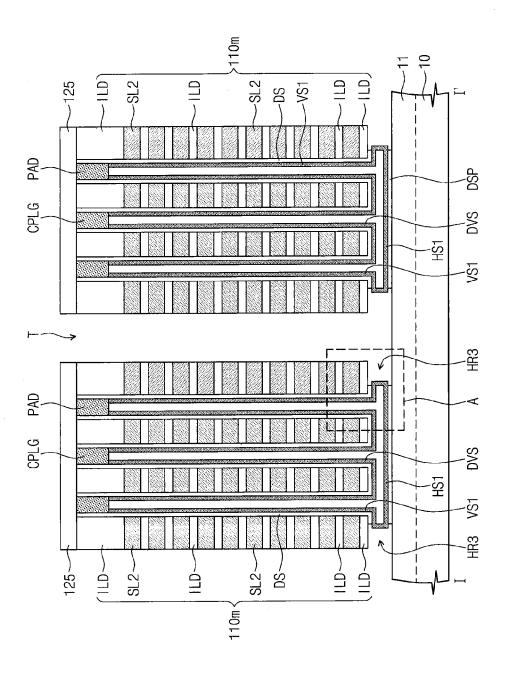

[0107] FIGS. 11, 12, 13, and 14 are cross-sectional views illustrating 3D semiconductor devices according to some embodiments of the inventive concepts. Hereinafter, the descriptions to the same technical features as in the embodi-

ment of FIGS. 3, 4A, 4B, 5, and 6 will be omitted or mentioned briefly for the purpose of ease and convenience in explanation.

[0108] Referring to FIG. 11, the first and second vertical channels VS1 and VS2 and the dummy vertical channels DVS may penetrate each of the first and second stack structures ST1 and ST2, and the first horizontal channel HS1 may be disposed under each of the first and second stack structures ST1 and ST2. The first horizontal channel HS1 may continuously extend from the vertical channels VS1, VS2, and DVS and may extend in parallel to each of the first and second stack structures ST1 and ST2 along the first direction D1. The second horizontal channels HS2 may be disposed at both sides of the first horizontal channel HS1. The second horizontal channels HS2 may extend in the first direction D1 and may be in contact with both sidewalls of the first horizontal channel HS1, respectively.

[0109] The conductive pads PAD may be respectively disposed on the first and second vertical channels VS1 and VS2, and the source plugs CPLG may be respectively disposed on the dummy vertical channels DVS. In some embodiments, the conductive pads PAD and the source plugs CPLG may have the second conductivity type opposite to the first conductivity type of the dopant region 13 of the second horizontal channel HS2.

[0110] In some embodiments, bottom surfaces of the source plugs CPLG connected to the dummy vertical channels DVS may be higher than the top surface of the uppermost electrode. For example, the bottom surfaces of the source plugs CPLG may be disposed at the same level as the bottom surfaces of the conductive pads PAD disposed on the top ends of the first and second vertical channels VS1 and VS2

[0111] The source plugs CPLG may be electrically connected to the common source line CSL through the contact plugs CSP, and the conductive pads PAD may be electrically connected to the bit lines BL1 and BL2 through the lower and upper contact plugs LCP and UCP and the assistant interconnections SBL1 and SBL2.

[0112] Referring to FIG. 12, the first and second stack structures ST1 and ST2 extending in the first direction D1 may be spaced apart from each other in the second direction D2 on the substrate 10. The first and second vertical channels VS1 and VS2 and the dummy vertical channels DVS may penetrate each of the first and second stack structures ST1 and ST2, and the first horizontal channel HS1 may be disposed under each of the first and second stack structures ST1 and ST2. The first horizontal channel HS1 may continuously extend from the vertical channels VS1, VS2, and DVS and may extend in parallel to each of the first and second stack structures ST1 and ST2 along the first direction D1.

[0113] Second horizontal channels HS2 may be disposed at both sides of the first horizontal channel HS1. The second horizontal channels HS2 may extend in the first direction D1 and may be in contact with both sidewalls of the first horizontal channel HS1, respectively. In some embodiments, the second horizontal channel HS2 disposed under an edge of the first stack structure ST1 adjacent the second stack structure ST2 may be separated from the second horizontal channel HS2 disposed under an edge of the second stack structure ST2 adjacent the first stack structure ST1. In other words, the filling insulation layer 130 disposed between the first and second stack structures ST1 and ST2 may penetrate

the second horizontal channel HS2 so as to be in contact with the substrate 10, and the second horizontal channels HS2 may have sidewalls aligned with sidewalls of the first and second stack structures ST1 and ST2.

[0114] In some embodiments, the second horizontal channels HS2 may be doped with dopants of the first conductivity type, and the dopant concentration of the second horizontal channel HS2 may be higher than that of the first horizontal channel HS1. The dopant concentration of the first horizontal channel HS1 may be substantially equal to that of the well dopant layer 11.

[0115] Referring to FIG. 13, the first and second stack structures ST1 and ST2 extending in the first direction D1 may be spaced apart from each other in the second direction D2 on the substrate 10. The first and second vertical channels VS1 and VS2 and the dummy vertical channels DVS may penetrate each of the first and second stack structures ST1 and ST2, and the first horizontal channel HS1 may be disposed under each of the first and second stack structures ST1 and ST2. The first horizontal channel HS1 may continuously extend from the vertical channels VS1, VS2, and DVS and may extend in parallel to each of the first and second stack structures ST1 and ST2 along the first direction D1. The second horizontal channels HS2 may be disposed at both sides of the first horizontal channel HS1. The second horizontal channels HS2 may extend in the first direction D1 and may be in contact with both sidewalls of the first horizontal channel HS1, respectively. The first and second vertical channels VS1 and VS2 may be continuously connected to the first horizontal channel HS1 without an interface therebetween, but an interface may be formed between the first horizontal channel HS1 and the second horizontal channel HS2 by semiconductor crystals.

[0116] In some embodiments, a common source region 15 may be disposed in each of the second horizontal channels HS2. The common source region 15 may have the second conductivity type opposite to the first conductivity type of the well dopant layer 11. The common source region 15 may extend in the first direction D1 between the first and second stack structures ST1 and ST2 when viewed from a plan view. The common source region 15 may be spaced apart from the well dopant layer 11.

[0117] In some embodiments, the conductive pads PAD may be disposed on the top ends of the first and second vertical channels VS1 and VS2, and pickup plugs PPLG may be disposed on the top ends of the dummy vertical channels DVS. The conductive pads PAD and the pickup plugs PPLG may be dopant regions doped with dopants or may be formed of a conductive material. In some embodiments, the pickup plugs PPLG may have the same conductivity type (i.e., the first conductivity type) as the well dopant layer 11, but the conductive pads PAD may have the second conductivity type opposite to the first conductivity type.

[0118] In some embodiments, a vertical length of the pickup plug PPLG may be longer than that of the conductive pad PAD. In other words, the bottom surface of the conductive pad PAD may be higher than the top surface of the uppermost electrode, and a bottom surface of the pickup plug PPLG may be lower than the bottom surface of the uppermost electrode. In certain embodiments, the bottom surfaces of the pickup plug PPLG and the conductive pad PAD may be higher than the top surface of the uppermost electrode.

[0119] In some embodiments, a well conductive line PCL may be disposed on the filling insulation layer 130 disposed on the each of the first and second stack structures ST1 and ST2 and may extend in the first direction D1. The well conductive line PCL may be connected to the pickup plugs PPLG arranged along the first direction D1 through contact plugs CSP. In the erase operation of the 3D semiconductor device, the erase voltage may be applied to the well conductive line PCL and the pickup plugs PPLG. The conductive pads PAD may be connected to the bit lines BL1 and BL2 through the upper and lower contact plugs LCP and UCP and the assistant interconnections SBL1 and SBL2.

[0120] In some embodiments, a common source line CSL may penetrate the filling insulation layer 130 between the first and second stack structures ST1 and ST2 so as to be connected to the common source region 15. In other words, a common source voltage may be applied to the common source line CSL and the common source region 15 in a program operation or the read operation of the 3D semiconductor device.

[0121] Referring to FIG. 14, the first and second stack structures ST1 and ST2 may extend in the first direction D1 on the substrate 10 and may be spaced apart from each other in the second direction D2. As described above, the one channel structure CHS may penetrate each of the first and second stack structures ST1 and ST2, and the second horizontal channels HS2 may be disposed at both sides of the first horizontal channel HS1.

[0122] In some embodiments, the conductive pads PAD may be disposed on the top ends of the first and second vertical channels VS1 and VS2 and the top ends of the dummy vertical channels DVS. The conductive pads PAD may be dopant regions doped with dopants and/or may be formed of a conductive material. In some embodiments, the conductive pads PAD may have the second conductivity type opposite to the first conductivity type.

[0123] In some embodiments, the common source region 15 may be disposed in the second horizontal channel HS2 disposed at one side of the first horizontal channel HS1, and a pickup dopant region 13 may be disposed in the second horizontal channel HS2 disposed at another side of the first horizontal channel HS1. The common source region 15 may be doped with dopants. Here, the common source region 15 may have the second conductivity type opposite to the first conductivity type of the well dopant layer 11, but the pickup dopant region 13 may have the same conductivity type (i.e., the first conductivity type) as the well dopant layer 11.

[0124] In some embodiments, the common source region 15 and the pickup dopant region 13 may extend in the first direction D1 and may be spaced apart from the well dopant layer 11. The first stack structure ST1 may have a first sidewall and a second sidewall opposite to each other. The common source region 15 may be disposed between the first stack structure ST1 and the second stack structure ST1 adjacent the first sidewall of the first stack structure ST1 in a plan view, and the pickup dopant region 13 may be disposed between the first stack structure ST1 and the second stack structure ST1 adjacent to the second sidewall of the first stack structure ST2 in a plan view.

[0125] In some embodiments, the common source line CSL may penetrate the filling insulation layer 130 between the first stack structure ST1 and the second stack structure ST2 adjacent the first sidewall of the first stack structure ST1 so as to be connected to the common source region 15. In the

program or read operation of the 3D semiconductor device, the common source voltage may be applied to the common source line CSL and the common source region 15.

[0126] A well conductive line PCL may penetrate the filling insulation layer 130 between the first stack structure ST1 and the second stack structure ST2 adjacent the second sidewall of the first stack structure ST1 so as to be connected to the pickup dopant region 13. Thus, the erase voltage may be provided to the first and second horizontal channels HS1 and HS2 and the first and second vertical channels VS1 and VS2 through the well conductive line PCL and the pickup dopant region 13 in the erase operation of the 3D semiconductor device.

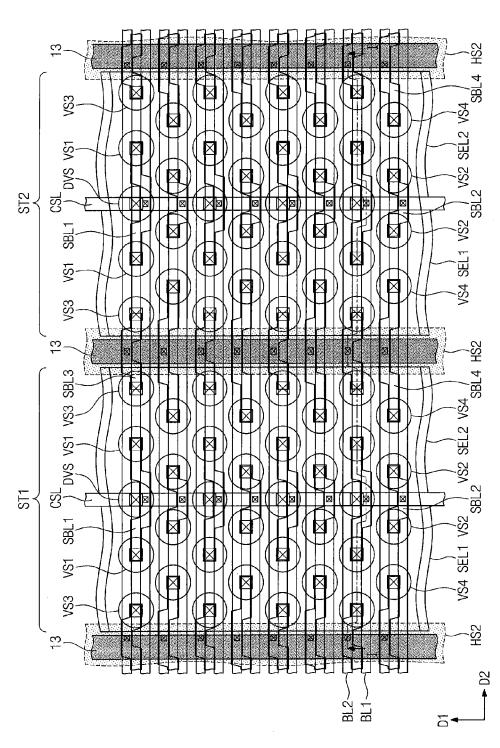

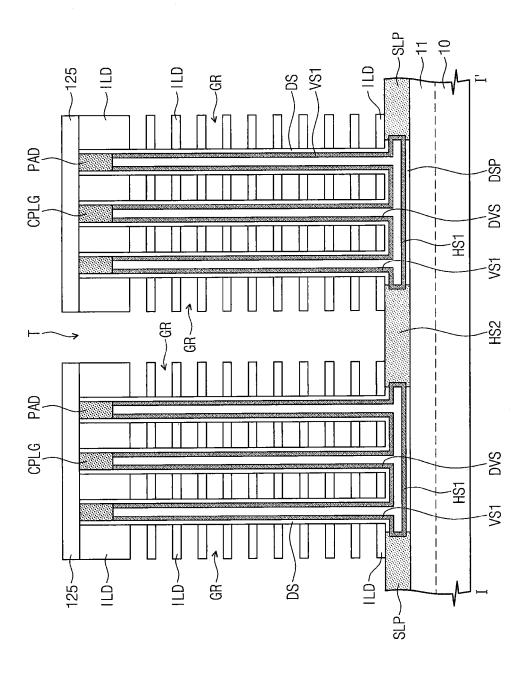

[0127] FIG. 15 is a plan view illustrating a 3D semiconductor device according to some embodiments of the inventive concepts. FIG. 16 is a cross-sectional view taken along a line I-I' of FIG. 15 to illustrate a 3D semiconductor device according to some embodiments of the inventive concepts. [0128] Referring to FIGS. 15 and 16, the first and second stack structures ST1 and ST2 may extend in the first direction D1 on the substrate 10 and may be spaced apart from each other in the second direction D2. Each of the first and second stack structures ST1 and ST2 may include electrodes EL vertically stacked on the substrate 10, and the uppermost electrode of each of the first and second stack structures ST1 and ST2 may be divided into the first string selection electrode SEL1 and the second string selection electrode SEL2 spaced apart from each other by the separation insulating pattern 115. The first and second string selection electrodes SEL1 and SEL2 may extend in the first direction D1.

[0129] One channel structure CHS may be provided in each of the first and second stack structures ST1 and ST2. The channel structure CHS may include a plurality of first to fourth vertical channels VS1, VS2, VS3, and VS4, dummy vertical channels DVS, and a first horizontal channel HS1. [0130] The plurality of first to fourth vertical channels VS1, VS2, VS3, and VS4 and the dummy vertical channels DVS may penetrate each of the first and second stack structures ST1 and ST2. The dummy vertical channels DVS may be arranged along the first direction D1 between the first and second string selection electrodes SEL1 and SEL2. The first vertical channels VS1 may be arranged along the first direction D1 to constitute a first column, and the second vertical channels VS2 may be arranged along the first direction D2 to constitute a second column. The third vertical channels VS3 may be arranged along the first direction D1 to constitute a third column, and the fourth vertical channels VS4 may be arranged along the first direction D2 to constitute a fourth column.

[0131] The first to fourth vertical channels VS1 to VS4 penetrating the first string selection electrode SEL1 and the fourth to fourth vertical channels VS1 to VS4 penetrating the second string selection electrode SEL2 may be arranged in mirror symmetry with respect to the dummy vertical channels DVS. The first and third vertical channels VS1 and VS3 may be aligned with the second and fourth vertical channels VS2 and VS4 in a direction diagonal to the second direction D2, respectively.

[0132] The first to fourth vertical channels VS1 to VS4 and the dummy vertical channels DVS may have hollow pipe, tube and/or macaroni shapes. In some embodiments, the first to fourth vertical channels VS1 to VS4 and the dummy vertical channels DVS may have cylindrical shapes.

[0133] The first horizontal channel HS1 may be disposed under each of the first and second stack structures ST1 and ST2 and may continuously extend from the first to fourth vertical channels VS1, VS2, VS3, and VS4 and the dummy vertical channels DVS. In other words, the first to fourth vertical channels VS1, VS2, VS3, and VS4, the dummy vertical channels DVS, and the first horizontal channel HS1 may constitute one semiconductor layer that continuously extends to have a pipe shape in one body.

[0134] The first horizontal channel HS1 may extend in parallel to the first and second stack structures ST1 and ST2 and may have rounded sidewalls, as described with reference to FIG. 4B. In addition, a width of the first horizontal channel HS1 may be smaller than that of each of the first and second stack structures ST1 and ST2. The second horizontal channels HS2 may be disposed at both sides of the first horizontal channel HS1. The second horizontal channels HS2 may extend in the first direction D1 and may be in contact with the sidewalls of the first horizontal channel HS1. The first to fourth vertical channels VS1, VS2, VS3, and VS4 may be continuously connected to the first horizontal channel HS1 without an interface therebetween. An interface may be formed between the first horizontal channel HS1 and the second horizontal channel HS2 by semiconductor crystals.

[0135] The second horizontal channel HS2 may have the same conductivity type (i.e., the first conductivity type) as the well dopant layer 11. The second horizontal channel HS2 may have the dopant region 13, which is disposed between the first and second stack structures ST1 and ST2 when viewed from a plan view. The dopant region 13 may have the first conductivity type, and the dopant concentration of the dopant region 13 may be higher than that of the second horizontal channel HS2.

[0136] The conductive pads PAD may be disposed on top ends of the first to fourth vertical channels VS1, VS2, VS3, and VS4, respectively, and the source plugs CPLG may be disposed on the top ends of the dummy vertical channels DVS, respectively. The vertical length of the source plug CPLG may be longer than that of the conductive pad PAD. In other words, the bottom surfaces of the conductive pads PAD may be higher than the top surface of the uppermost electrode, and the bottom surfaces of the source plugs CPLG may be lower than the bottom surface of the uppermost electrode. For example, the source plug CPLG may vertically extend toward the substrate 10 such that the bottom surface of the source plug CPLG is adjacent the first horizontal channel HS1.

[0137] The conductive pads PAD and the source plugs CPLG may be dopant regions doped with dopants or may be formed of a conductive material. In some embodiments, the conductive pads PAD and the source plugs CPLG may have the second conductivity type opposite to the first conductivity type of the dopant region 13 and the well dopant layer 11. In some embodiments, as described with reference to FIG. 13, the pickup plug PPL1 having the first conductivity type may be disposed on the top end of the dummy vertical channel DVS, and the common source region 15 having the second conductivity type may be disposed in the second horizontal channel HS2.

[0138] The common source line CSL may be disposed on the filling insulation layer 130 covering the first and second stack structures ST1 and ST2. The common source line CSL may be connected to the source plugs CPLG through the

contact plugs CSP. The common source line CSL may be disposed on each of the first and second stack structures ST1 and ST2 and may be electrically connected in common to the dummy vertical channels arranged along the first direction D1.

[0139] The first insulating layer 140 may be disposed on the filling insulating layer 130 to cover the common source lines CSL, and the first to fourth assistant interconnections SBL1, SBL2, SBL3, and SBL4 may be disposed on the first insulating layer 140.

[0140] In some embodiments, each of the first assistant interconnections SBL1 may be connected to the first vertical channels VS1 adjacent one another in the second direction D2 through lower contact plugs LCP. Each of the second assistant interconnections SBL2 may be connected to the second vertical channels VS2 adjacent one another in the second direction D2 through lower contact plugs LCP. In some embodiments, lengths of the second assistant interconnections SBL2 may be shorter than those of the first assistant interconnections SBL1.

[0141] Each of the third assistant interconnections SBL3 may be connected to the third vertical channels VS3 adjacent one another in the second direction D2 through lower contact plugs LCP. Each of the fourth assistant interconnections SBL4 may be connected to the fourth vertical channels VS4 adjacent one another in the second direction D2 through lower contact plugs LCP. In some embodiments, lengths of the fourth assistant interconnections SBL4 may be shorter than those of the third assistant interconnections SBL3.

[0142] The first and second assistant interconnections SBL1 and SBL2 may intersect the common source line CSL on each of the first and second stack structures ST1 and ST2, and the third and fourth assistant interconnections SBL3 and SBL4 may intersect the dopant region 13.

[0143] The second insulating layer 150 may be disposed on the first insulating layer and the first to fourth assistant interconnections SBL1 to SBL4, and the first and second bit lines BL1 and BL2 may be disposed on the second insulating layer 150. The first and second bit lines BL1 and BL2 may extend in the second direction D2 and may be alternately arranged in the first direction D1.

[0144] Each of the first bit lines BL1 may be connected to the first assistant interconnections SBL1 or the second assistant interconnections SBL2 through upper contact plugs UCP. Each of the second bit lines BL2 may be connected to the third assistant interconnections SBL3 or the fourth assistant interconnections SBL4 through upper contact plugs UCP.

[0145] In the embodiment of FIGS. 15 and 16, the first to fourth vertical channels VS1 to VS4 may be connected in common to the common source line CSL through the first horizontal channel HS1 and the dummy vertical channels DVS during the read operation. In the erase operation, the first to fourth vertical channels VS1 to VS4 may be connected to the second horizontal channel HS2, supplied with the erase voltage, through the first horizontal channel HS1.

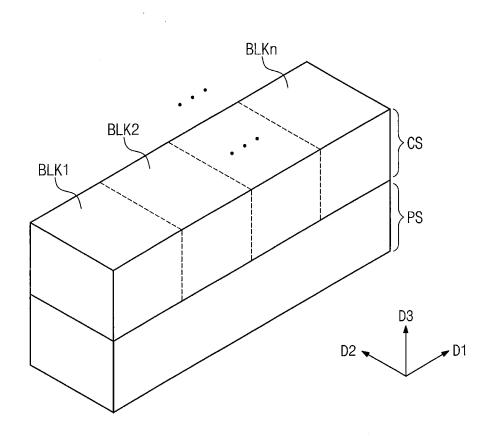

[0146] FIG. 17 is a schematic block diagram illustrating a 3D semiconductor device according to some embodiments of the inventive concepts.

[0147] Referring to FIG. 17, a 3D semiconductor device according to some embodiments may include a peripheral logic structure PS and a cell array structure CS stacked on the peripheral logic structure PS. In other words, the periph-

eral logic structure PS and the cell array structure CS may overlap with each other when viewed from a plan view.