# UK Patent Application (19)GB (11)2615773

23.08.2023

2202126.5 (21) Application No:

(22) Date of Filing: 17.02.2022

(71) Applicant(s):

**Imagination Technologies Limited** (Incorporated in the United Kingdom) Imagination House, Home Park Estate, KINGS LANGLEY, Hertfordshire, WD4 8LZ, **United Kingdom**

(72) Inventor(s):

**Thomas Ferrere**

(74) Agent and/or Address for Service:

**Imagination Technologies Limited** Patents Dept., Imagination House, Home Park Estate, KINGS LANGLEY, Hertfordshire, WD4 8LZ, **United Kingdom**

(51) INT CL:

G06F 7/483 (2006.01) G06F 7/499 (2006.01) G06F 7/544 (2006.01)

(56) Documents Cited:

EP 3719639 A2 US 20180300105 A1

(58) Field of Search: INT CL G06F

- (54) Title of the Invention: Method and system for calculating dot products Abstract Title: Calculating dot product

- (57) A method of performing dot product of an array of '2k' floating point numbers comprising two sets of k floating-point numbers ai and bi is disclosed. The method includes receiving both sets of 'k' floating point numbers and multiplying each floating point number ai with a floating point number bi to generate k product numbers (zi), each product number (zi) having a mantissa bit length of 'r' bits. The method further comprises creating a set of 'k' numbers (yi) based on the k product numbers (zi), the numbers (yi) having a bit-length of 'n' bits. Further the method includes identifying a maximum exponent sum (emax) among k exponent sums (eabi) of each pair of floating point numbers ai and bi, aligning the magnitude bits of the numbers (yi) based on the maximum exponent sum (emax) and adding the set of 'k' numbers concurrently to obtain the dot product.

FIG. 1

FIG. 2

FIG. 3

FIG. 4a

FIG. 4b

FIG. 5

FIG. 6a

FIG. 6b

FIG. 6c

FIG. 6d

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

# METHOD AND SYSTEM FOR CALCULATING DOT PRODUCTS

### BACKGROUND

10

15

20

25

[0001] Most computing systems use number formats, typically in binary notation or base 2, for performing various computations. These number formats include fixed-point or floating-point number formats. Fixed point number formats can provide additional precision but is used to represent only a limited range of values. Therefore, floating point number formats are used in most of the modern computing systems to provide a trade-off between range and precision.

**[0002]** A floating-point number comprises a mantissa (m) having a bit length of 'b' bits, an exponent (e) having a bit length of 'a' bits and optionally a sign bit (s) to represent a binary number. In some widely used formats the exponent is biased (i.e. offset) by a value (c) so as to represent numbers smaller than 1 and is used to encode exceptional values at its end points. For non-extremal values of e, the floating-point number x is said to be normalized and the number x is represented as  $(-1)^s 2^{e-c} (1+2^{-b}m)$ . Thus, floating point numbers can be used to represent very small or very large numbers precisely using scientific notation, in binary or in some other base. The use of floating-point numbers in arithmetic computations provides varying degrees of precision depending on the bit length or type of floating-point format used.

**[0003]** Computations involving convolution/dot products of large arrays of real valued numbers occur commonly in the solution of various numerical problems. The dot product of large arrays or two sets of numbers  $(a_0, a_1, a_2... a_{k-1})$  and  $(b_0, b_1, b_2... b_{k-1})$  is defined as

a.b =

$$\sum_{i=0}^{k-1} a_i b_i$$

[0004] It is therefore advantageous to have hardware dedicated to performing dot products in high performance computing systems, graphic processing systems, neural network accelerators and the like. Conventionally, there are different ways to achieve this, with different benefits and drawbacks.

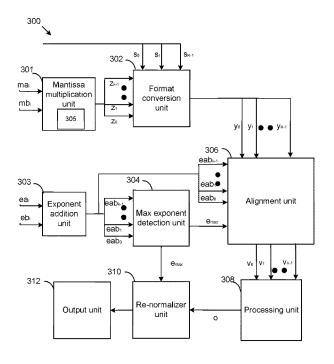

[0005] A known method in computing systems, to do dot product of two arrays/ sets of floating-point numbers, is by using separate floating point multiplication and floating point addition. A dot product unit 100 using this principle is shown in FIG.1. The dot product unit 100 comprises a set of floating point multiplication units 102a, 102b, 102c and 102d, and a set of floating point adder units 104a, 104b and 104c. The dot product unit 100 is implemented as a tree of floating point multiplication units and addition units. The dot

product unit 100 receives a first set of floating point numbers (a<sub>1</sub>, a<sub>2</sub>, a<sub>3</sub>, and a<sub>4</sub>) and a second set of floating point numbers (b<sub>1</sub>, b<sub>2</sub>, b<sub>3</sub>, and b<sub>4</sub>) as inputs. Consider that each number in the first set of floating point numbers ai comprises a mantissa mai and an exponent eai. Similarly, each number in the second set of floating point numbers bi comprises a mantissa mb<sub>i</sub> and an exponent eb<sub>i</sub>. Each floating point number a<sub>i</sub> in the first set of floating-point numbers is provided as a first input to a respective one of floating point multiplication units 102a, 102b, 102c and 102d. Each floating point number bi in a second set of floating-point numbers is provided as a second input to a respective one of floating point multiplication units 102a, 102b, 102c and 102d. Each floating point multiplication unit 102a, 102b, 102c and 102d performs the multiplication of floating point numbers a<sub>i</sub> and b<sub>i</sub>, to obtain a product c<sub>i</sub>. Once the product c<sub>i</sub> from each multiplication unit 102a, 102b, 102c and 102d is obtained, the results (floating point numbers) are accumulated by a series of adders in any dynamically or statically chosen order to obtain the output. Thus, the adders can be arranged in any order. In one example, as depicted in the FIG.1 the product c<sub>1</sub> and c<sub>2</sub> from two consecutive floating point multiplication units 102a and 102b are provided to a first floating point adder unit 104a to add the products (c₁ and c₂). Similarly, the products c₃ and c<sub>4</sub> from the next two consecutive floating point multiplication units 102c and 102d are provided to a second floating point adder unit 104b to add the product (c<sub>3</sub> and c<sub>4</sub>). Further, the accumulated values are further provided as an input to a third floating point adder 104c to be accumulated to obtain the output y. The output from the multiplier or adder in each step is rounded, which causes a rounding error in the output generated by each step. The rounding error is a characteristic feature of floating-point calculations.

10

35

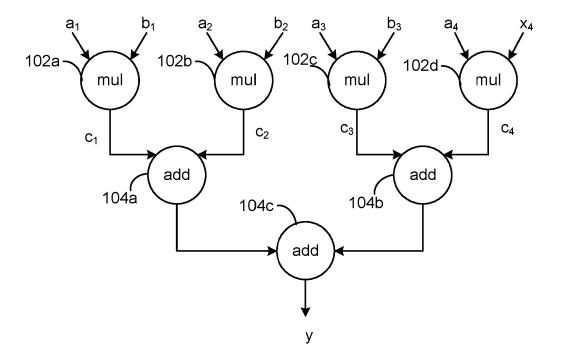

[0006] Another known method in computing systems, to do dot product of two arrays/ sets of floating-point numbers, is by using fused multiplication and addition operations. A dot product unit 200 using this principle is shown in FIG. 2. The dot product unit 200 comprises a set of Fused Multiply and Add (FMA) units 202a, 202b, 202c and 202d. An FMA unit performs the floating point multiplication and addition in a single step with a single rounding. Thus, FMA improves the speed and accuracy of computation of dot product involving accumulation of products. In FIG. 2, the results of one fused multiply add unit is provided as an input to another fused multiply add unit such that the product of two numbers is added to the product of the next two numbers. The dot product unit 200 receives both sets of floating point numbers  $a_i$  and  $b_i$  as inputs. Each floating point number  $a_i$  in the first set of floating-point numbers is provided as a first input to a respective one of FMA units 202a, 202b, 202c and 202d. Each floating point number  $b_i$  in the second set of floating-point numbers is provided as a second input to a respective one of FMA units 202a, 202b, 202c and 202d. Each FMA 202a, 202b and 202c computes multiplication of numbers  $a_i$  and  $b_i$

and adds it with the results of a previous FMA with a single rounding (N.B. in the case of FMA 202d there is no 'previous' FMA, as FMA 202d is at the top of tree, and so the addition operation simply adds the result of the multiplication operation to zero). For example, as depicted in FIG.2 the FMA 202d receives the numbers a<sub>4</sub> and b<sub>4</sub> as the multiplicand inputs.

Further a 0 input is provided as a third input. The FMA 202d multiplies a<sub>4</sub> and b<sub>4</sub> and adds the result with 0 to obtain the output d<sub>4</sub>. Further, the FMA 202c receives the numbers a<sub>3</sub> and b<sub>3</sub> as the multiplicand inputs and d<sub>4</sub> as a third input. The FMA 202c multiplies a<sub>3</sub> and b<sub>3</sub> and adds the result with d<sub>4</sub> to obtain the output d<sub>3</sub>. Similarly, FMA 202b obtains the output d<sub>3</sub> by multiplying a<sub>2</sub> and b<sub>2</sub> and adding the result with d<sub>3</sub>. Further the FMA 202a obtains the final output y=d<sub>1</sub> by multiplying a<sub>1</sub> and b<sub>1</sub> and adding the result with d<sub>2</sub>.

**[0007]** Thus, pairs of floating-point number  $a_i$  and  $b_i$  from both sets of floating point numbers are multiplied together and added to a previously calculated output to generate a new or cumulative output. In other words, the overall sum is performed as a sequence of multiplication and addition of numbers. A final output (y) generated after multiplying and adding all the floating-point numbers in the array is provided as the output.

**[0008]** Either of the above described methods can be implemented iteratively looping through the same unit(s) or concurrently by using a parallel or sequential composition of units. Whether using the first dot product unit 100 or 200, the precision of the output cannot be guaranteed as different ordering of inputs may yield different results, due to the intermediate rounding operations. Further, there is a high delay introduced due to the number of logic gates in the critical path.

**[0009]** Hence, existing methods and architectures for processing floating-point numbers have drawbacks.

#### SUMMARY

25

1.5

20

**[0010]** This Summary is provided to introduce a selection of concepts in a simplified form that are further described below in the Detailed Description. This Summary is not intended to identify key features or essential features of the claimed subject matter, nor is it intended to be used to limit the scope of the claimed subject matter.

**[0011]** A method of performing dot product of an array of '2k' floating point numbers comprising two sets of k floating-point numbers  $a_i$  and  $b_i$  is disclosed. The method includes receiving both sets of 'k' floating point numbers and multiplying each floating point number  $a_i$  with a floating point number  $b_i$  to generate k product numbers  $(z_i)$ , each product number  $(z_i)$  having a mantissa bit length of 'r' bits. The method further comprises creating a set of

'k' numbers  $(y_i)$  based on the k product numbers  $(z_i)$ , the numbers  $(y_i)$  having a bit-length of 'n' bits. Further the method includes identifying a maximum exponent sum  $(e_{max})$  among k exponent sums  $(eab_i)$  of each pair of floating point numbers  $a_i$  and  $b_i$ , aligning the magnitude bits of the numbers  $(y_i)$  based on the maximum exponent sum  $(e_{max})$  and adding the set of 'k' numbers concurrently to obtain the dot product.

**[0012]** According to a first aspect there is provided a method of performing dot product of an array of '2k' floating point numbers,  $k \ge 3$ , using a hardware implementation, the array comprising a first set of k floating-point numbers  $a_0$ ,  $a_1$ ...,  $a_{k-1}$ , and a second set of k floating-point numbers  $b_0$ ,  $b_1$ ..., $b_{k-1}$ , wherein the method comprises: receiving both sets of 'k' floating point numbers; multiplying each floating point number  $a_i$  with a floating point number  $b_i$  to generate k product numbers  $(z_i)$ , each product number  $(z_i)$  having a mantissa bit length of 'r' bits; creating a set of 'k' numbers  $(y_i)$  based on the k product numbers  $(z_i)$ , the numbers  $(y_i)$  having a bit-length of 'n' bits obtained by adding both extra most-significant bits and extra least-significant bits to the bit length 'r' of the product numbers  $(z_i)$ , wherein the 'n' bits comprises a number of magnitude bits, wherein 'n' is  $r + \lceil \log_2(k) \rceil + \lceil \log_2(k-1) \rceil + x$  bits, where x is an integer, and  $x \ge 1$ ; identifying a maximum exponent sum  $(e_{max})$  among k exponent sums  $(eab_i)$ , each exponent sum is the sum of exponents of the floating point number  $a_i$  and the floating point number  $a_i$  aligning the magnitude bits of the numbers  $(y_i)$  based on the maximum exponent sum  $(e_{max})$ ; and adding the set of 'k' numbers concurrently.

10

20

25

30

**[0013]** Optionally, each number in the first set of k floating-point numbers  $a_0$ ,  $a_1$ ...,  $a_{k-1}$  comprises a mantissa (ma<sub>i</sub>) and an exponent (ea<sub>i</sub>) and each number in the second set of k floating-point numbers  $b_0$ ,  $b_1$ ...,  $b_{k-1}$  comprises a mantissa (mb<sub>i</sub>) and an exponent (eb<sub>i</sub>), where each mantissa (ma<sub>i</sub>) is having a bit length of 'p' bits and each mantissa (mb<sub>i</sub>) is having a bit length of 'q' bits.

**[0014]** Optionally, multiplying each floating point number ai with the corresponding floating point number bi comprises multiplying mantissa (ma<sub>i</sub>) and mantissa (mbi) to obtain an intermediate mantissa product (mab<sub>i</sub>).

**[0015]** Optionally, the method of performing a dot product emulates the precision obtained using separate multiplication and addition units, for performing dot product having an output mantissa bit length of P bits, by setting the mantissa bit length of 'r' bits as 'r=P+2' bits.

**[0016]** Optionally, the method emulates the precision obtained using fused multiplication and addition units, for performing dot product having an output mantissa bit length of Q bits, by setting the mantissa bit length of 'r' bits as 'r= max (Q+2, p+q+3)' bits.

**[0017]** Optionally, generating k product numbers  $(z_i)$  having the mantissa bit length of 'r' bits comprises: rounding, the bits of the intermediate mantissa product  $(mab_i)$  to r bits, if p+q+2>r bits; or padding, extra least-significant bits to the bit length of the intermediate mantissa product  $(mab_i)$  to generate r bits, if p+q+2 < r bits.

[0018] Optionally, identifying a maximum exponent sum (e<sub>max</sub>) includes identifying the maximum value among k exponent sums (eab<sub>i</sub>) where k exponent sums (eab<sub>i</sub>) is obtained by summing exponent (ea<sub>i</sub>) and exponent (eb<sub>i</sub>).

**[0019]** Optionally, adding extra most-significant bits to the bit length 'r' of the product numbers  $(z_i)$  comprises adding at least  $\lceil \log_2(k) \rceil$  number of the most-significant bits.

[0020] Optionally, adding extra least-significant bits to the bit length 'r' of the product numbers ( $z_i$ ) comprises adding at least  $\lceil \log_2(k-1) \rceil + 1$  number of the least-significant bits.

**[0021]** Optionally, the method further comprises: calculating an output value by adding 'k' numbers (y<sub>i</sub>); renormalizing the output value; and rounding the output value to represent the output value as a floating-point number.

[0022] Optionally, aligning the magnitude bits of the numbers  $(y_i)$  to be based on the maximum exponent  $(e_{max})$  comprises the steps of, for each pair floating-point number (i): calculating the difference (ed) between the maximum exponent sum  $(e_{max})$  and each exponent sum  $(eab_i)$ ; and shifting the magnitude bits of the corresponding number  $(y_i)$ , to the LSB side, based on the calculated difference  $(e_d)$ .

[0023] Optionally, further to shifting the magnitude bits of the numbers, the method further comprises performing rounding or truncating the bits of the numbers that are shifted outside the bit-length of the number.

**[0024]** Optionally, the method further comprises determining a two's complement of the magnitude bits of the numbers, based on a sign bit (s<sub>i</sub>) of each corresponding number, if the set of 'k' floating point numbers comprises signed floating-point numbers.

25

30

[0025] Optionally, the set of 'k' floating point numbers in a first format comprises: unsigned floating point numbers which explicitly includes a leading bit; or unsigned floating point numbers which implicitly includes a leading bit or signed floating point numbers which explicitly includes a leading bit; or signed floating point numbers which implicitly includes a leading bit.

[0026] According to a second aspect there is provided a hardware implementation for performing dot product of an array of '2k' floating point numbers, k≥ 3, the array comprising a first set of k floating-point numbers  $a_0$ ,  $a_1$ ...,  $a_{k-1}$ , and a second set of k floating-point numbers  $b_0$ ,  $b_1$ ...,  $b_{k-1}$ , wherein the hardware implementation comprises a multiplication unit, a format conversion unit, a maximum exponent detection unit, an alignment unit, and a processing unit. The multiplication unit comprising a plurality of multiplier configured to: receive both sets of 'k' floating point numbers; and multiply each floating point number ai with a corresponding floating point number b<sub>i</sub> to generate k product numbers (z<sub>i</sub>), each product number (z<sub>i</sub>) having a mantissa bit length of 'r' bits. The format conversion unit configured to create a set of 'k' numbers (yi) based on the k product numbers (zi), the numbers (y<sub>i</sub>) having a bit-length of 'n' bits obtained by adding both extra most-significant bits and extra least-significant bits to the bit length 'r' of the product numbers (z<sub>i</sub>), wherein the 'n' bits comprises a number of magnitude bits, wherein 'n' is  $r + \lceil \log_2(k) \rceil +$  $[\log_2(k-1)] + x$  bits, where x is an integer, and  $x \ge 2$ . The maximum exponent detection unit configured to identify a maximum exponent sum (e<sub>max</sub>) among k exponent sums (eab<sub>i</sub>), each exponent sum is the sum of exponents of the floating point number ai and the floating point number bi. The alignment unit configured to align the magnitude bits of the numbers based on the maximum exponent sum ( $e_{max}$ ). The processing unit configured to add the set of 'k' numbers concurrently to generate an output value.

10

15

30

20 **[0027]** Optionally, the hardware implementation further comprises a renormalizing unit configured to: renormalize the output value; and round the output value to represent the output value as a floating-point number.

**[0028]** Optionally, each number in the first set of k floating-point numbers  $a_0$ ,  $a_1$ ...,  $a_{k-1}$  comprises a mantissa (ma<sub>i</sub>) and an exponent (ea<sub>i</sub>) and each number in the second set of k floating-point numbers  $b_0$ ,  $b_1$ ...,  $b_{k-1}$  comprises a mantissa (mb<sub>i</sub>) and an exponent (eb<sub>i</sub>), where each mantissa (ma<sub>i</sub>) is having a bit length of 'p' bits and each mantissa (mb<sub>i</sub>) is having a bit length of 'q' bits.

**[0029]** Optionally, the multiplication unit comprises a plurality of multiplier units configured to multiply concurrently each mantissa (ma<sub>i</sub>) with corresponding mantissa (mb<sub>i</sub>) to obtain an mantissa product (mab<sub>i</sub>).

**[0030]** Optionally, the hardware implementation for performing a dot product operation emulates the precision obtained using separate multiplication and addition units, for performing dot product having an output mantissa bit length of P bits, by setting the mantissa bit length of 'r' bits as 'r= P+2' bits.

**[0031]** Optionally, the hardware implementation for performing a dot product operation emulates the precision obtained using fused multiplication and addition units for performing dot product having an output mantissa bit length of Q bits, by setting the mantissa bit length of 'r' bits as 'r= max (Q+2, p+q+3)' bits.

**[0032]** Optionally, the multiplication unit is configured to generate k product number  $(z_i)$  having the mantissa bit length of 'r' bits by: rounding, the bits of the intermediate mantissa product  $(mab_i)$  to r bits, if p+q+2>r bits; or padding, extra least-significant bits to the bit length of the intermediate mantissa product  $(mab_i)$  to generate r bits, if p+q+2 < r bits.

**[0033]** Optionally, the maximum exponent detection unit is configured to identify a maximum exponent sum  $(e_{max})$  among k exponent sums  $(eab_i)$ , where k exponent sums  $(eab_i)$  is obtained by summing exponent  $(ea_i)$  and exponent  $(eb_i)$ .

10

25

30

**[0034]** Optionally, the alignment unit is configured to align the magnitude bits of the numbers to be based on the maximum exponent  $(e_{max})$ , wherein the alignment unit comprises a plurality of subtraction units and a plurality of shifter units. Each subtraction unit is configured to calculate the difference  $(e_d)$  between the maximum exponent sum  $(e_{max})$  and exponent sum  $(eab_i)$ . Each shifter unit configured to shift the magnitude bits of the corresponding number, to the LSB side, based on the calculated difference  $(e_d)$ .

[0035] Optionally, the alignment unit is configured to further truncate the bits of the numbers that are shifted outside of the bit length of the numbers.

[0036] Optionally, the alignment unit further comprises a plurality of complementing units configured to determine two's complement of the magnitude bits of each number, based on a sign bit (s<sub>i</sub>) of the corresponding number, if the set of 'k' floating point numbers comprises signed floating point numbers.

**[0037]** According to a third aspect there is provided a method of performing dot product of an array of '2k' floating point numbers,  $k \ge 3$ , using a hardware implementation, the array comprising a first set of k floating-point numbers  $a_0$ ,  $a_1$ ...,  $a_{k-1}$ , and a second set of k floating-point numbers  $b_0$ ,  $b_1$ ..., $b_{k-1}$ , wherein the method comprises: receiving both sets of 'k' floating point numbers; multiplying each floating point number  $a_i$  with a floating point number  $b_i$ , each multiplication generating a first intermediate product number  $(z_i)$  and a second intermediate product numbers  $(z_i)$ , thereby generating 2k product numbers comprising k first intermediate product numbers  $(z_i)$  and k second intermediate product numbers  $(z_i)$ , each having a bit length of 'r+1' bits; creating a set of '2k' numbers comprising k first numbers  $(y_i)$  and k second numbers  $(y_i)$ , based on the 2k product numbers, each having

a bit-length of 'n' bits obtained by adding both extra most-significant bits and extra least-significant bits to the bit length of the product numbers  $(z_i \text{ and } z_i)$ , wherein the 'n' bits comprises a number of magnitude bits, wherein 'n' is  $r+1+\lceil\log_2(k)\rceil+\lceil\log_2(k-1)\rceil+x$  bits, where x is an integer, and  $x\geq 1$ ; identifying a maximum exponent sum  $(e_{max})$  among k exponent sums  $(eab_i)$ , each exponent sum is the sum of exponents of the floating point number ai and the floating point number bi; aligning the magnitude bits of the numbers  $(y_i)$  and  $(e_{max})$  based on the maximum exponent sum  $(e_{max})$ ; and adding the set of '2k' numbers concurrently.

10

15

20

30

35

[0038] According to a fourth aspect there is provided a hardware implementation for performing dot product of an array of '2k' floating point numbers, k≥ 3, the array comprising a first set of k floating-point numbers  $a_0$ ,  $a_1$ ...,  $a_{k-1}$ , and a second set of k floating-point numbers  $b_0$ ,  $b_1...,b_{k-1}$ , wherein the hardware implementation comprises a multiplication unit, a format conversion unit, a maximum exponent detection unit, an alignment unit and a processing unit. The multiplication unit comprising a plurality of multiplier configured to: receive both sets of 'k' floating point numbers; and multiply each floating point number ai with a corresponding floating point number bi to generate a first intermediate product number (z<sub>i</sub>') and a second intermediate product numbers (z<sub>i</sub>''), thereby generating 2k product numbers comprising k first intermediate product numbers (zi') and k second intermediate product numbers (zi'), each having a bit length of 'r+1' bits. The format conversion unit configured to create a set of '2k' numbers comprising k first numbers (y<sub>i</sub>') and k second numbers (y<sub>i</sub>"), based on the 2k product numbers, each having a bit-length of 'n' bits obtained by adding both extra most-significant bits and extra least-significant bits to the bit length of the product numbers (z<sub>i</sub> and z<sub>i</sub>"), wherein the 'n' bits comprises a number of magnitude bits, wherein 'n' is  $r + 1 + \lceil \log_2(k) \rceil + \lceil \log_2(k-1) \rceil + x$  bits, where x is an integer, and  $x \ge 1$ . The maximum exponent detection unit configured to identify a maximum exponent sum (e<sub>max</sub>) among k exponent sums (eab<sub>i</sub>), each exponent sum is the sum of exponents of the floating point number ai and the floating point number bi. The alignment unit configured to align the magnitude bits of the numbers (yi' and yi'') based on the maximum exponent sum (e<sub>max</sub>). The processing unit configured to add the set of '2k' numbers concurrently to generate an output value.

**[0039]** The hardware implementation hardware implementation for performing dot product according to the first aspect discussed above may be embodied in hardware on an integrated circuit. There may be provided a method of manufacturing, at an integrated circuit manufacturing system, a hardware implementation for performing dot product. There may be provided an integrated circuit definition dataset that, when processed in an integrated circuit manufacturing system, configures the system to manufacture a hardware

implementation for performing dot product. There may be provided a non-transitory computer readable storage medium having stored thereon a computer readable description of a hardware implementation for performing dot product that, when processed in an integrated circuit manufacturing system, causes the integrated circuit manufacturing system to manufacture an integrated circuit embodying a hardware implementation for performing dot product.

[0040] There may be provided an integrated circuit manufacturing system comprising: a non-transitory computer readable storage medium having stored thereon a computer readable description of the a hardware implementation for performing dot product according to the first aspect discussed above.; a layout processing system configured to process the computer readable description so as to generate a circuit layout description of an integrated circuit embodying the hardware implementation for performing dot product; and an integrated circuit generation system configured to manufacture the hardware implementation for performing dot product according to the circuit layout description.

- 15 **[0041]** There may be provided computer program code for performing any of the methods described herein. There may be provided non-transitory computer readable storage medium having stored thereon computer readable instructions that, when executed at a computer system, cause the computer system to perform any of the methods described herein.

- 20 **[0042]** The above features may be combined as appropriate, as would be apparent to a skilled person, and may be combined with any of the aspects of the examples described herein.

## BRIEF DESCRIPTION OF THE DRAWINGS

10

- 25 **[0043]** Examples will now be described in detail with reference to the accompanying drawings in which:

- **[0044]** FIG. 1 is a block diagram illustrating a conventional floating point dot product calculator having separate multiplication and addition units;

- [0045] FIG. 2 is a schematic block diagram illustrating another conventional floating point dot product calculator having fused multiplication and addition units;

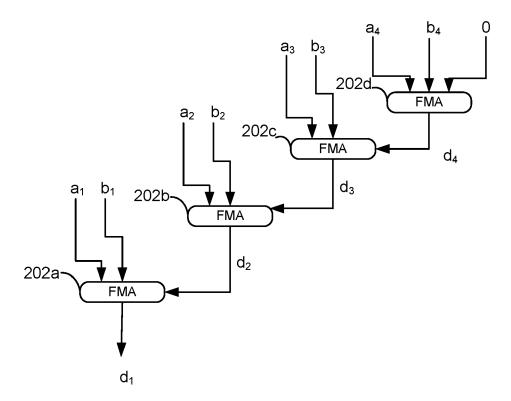

- **[0046]** FIG. 3 is a block diagram illustrating an example of a hardware implementation for performing dot product operation;

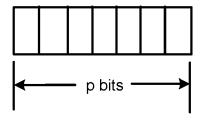

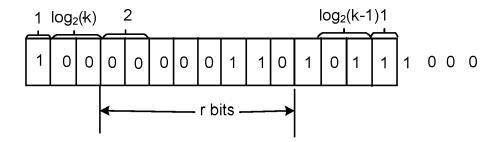

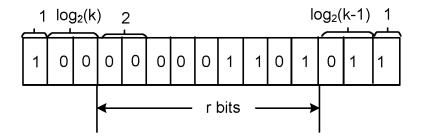

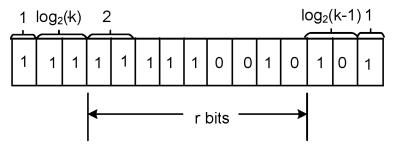

**[0047]** FIG. 4a is a block diagram illustrating a mantissa for a floating-point number in an incoming format representation;

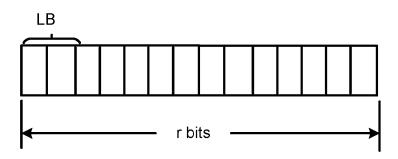

**[0048]** FIG. 4b is a block diagram illustrating a product number in a first intermediate format representation;

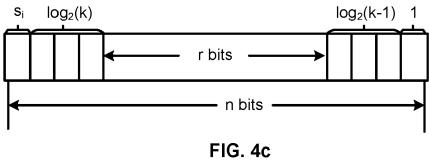

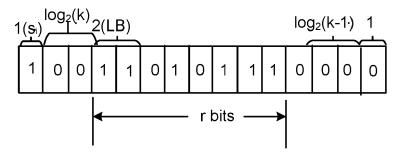

[0049] FIG. 4c is a block diagram illustrating a second intermediate format representation of a signed number;

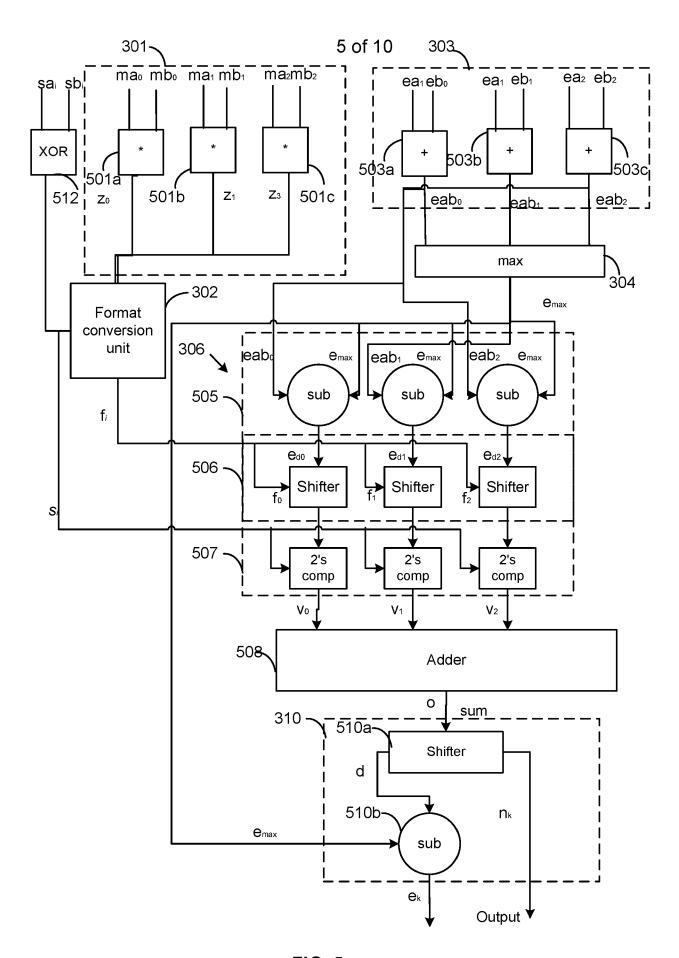

**[0050]** FIG. 5 is a block diagram illustrating the different units in the hardware implementation for performing dot product explained in FIG. 3;

[0051] FIG. 6a to FIG. 6d illustrate an example of a floating-point number converted from a first format representation to a second format representation;

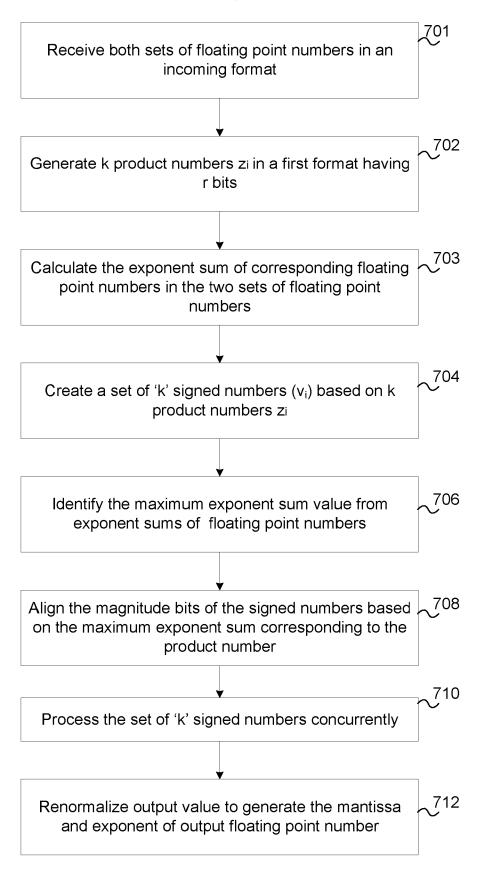

**[0052]** FIG. 7 is a flowchart illustrating a method of performing dot product of two sets of k floating-point numbers;

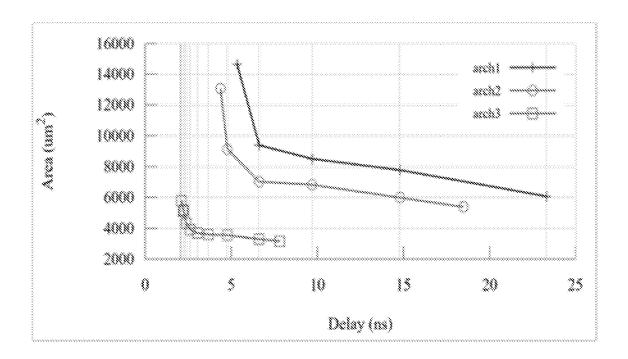

[0053] FIG 8 is a graph illustrating a comparison of the implementation of the architecture 300 with other standard architectures for processing a set of floating-point numbers;

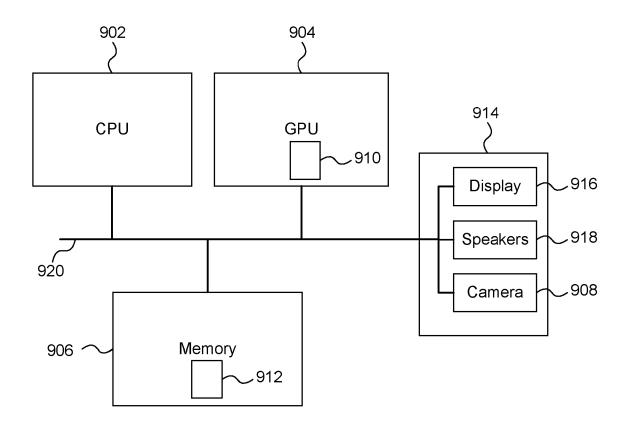

.5 **[0054]** FIG. 9 shows a computer system in which a dot product calculator is implemented;

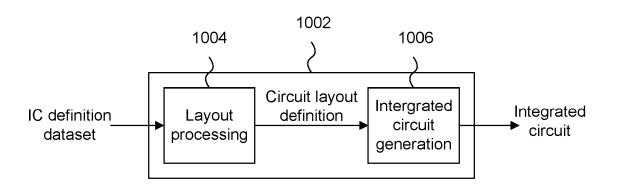

**[0055]** FIG. 10 shows an integrated circuit manufacturing system for generating an integrated circuit embodying a dot product calculator; and

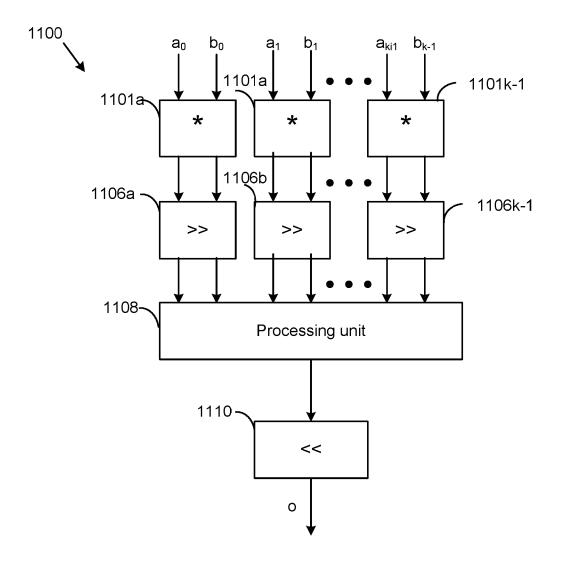

[0056] FIG. 11 illustrates the architecture 300 implementing a carry-save multiplication.

[0057] The accompanying drawings illustrate various examples. The skilled person will appreciate that the illustrated element boundaries (e.g., boxes, groups of boxes, or other shapes) in the drawings represent one example of the boundaries. It may be that in some examples, one element may be designed as multiple elements or that multiple elements may be designed as one element. Common reference numerals are used throughout the figures, where appropriate, to indicate similar features.

# 25 **DETAILED DESCRIPTION**

30

**[0058]** The following description is presented by way of example to enable a person skilled in the art to make and use the invention. The present invention is not limited to the embodiments described herein and various modifications to the disclosed embodiments will be apparent to those skilled in the art.

[0059] Embodiments will now be described by way of example only.

10

15

20

30

**[0060]** As explained above, the conventional hardware for performing a dot product of two sets of numbers includes hardware implementing separate multiplication and addition units or one implementing fused multiplication and addition units. The multiplicands  $a_i$  and  $b_i$  from both sets of floating point numbers may be represented in an incoming format F comprising a mantissa and an exponent. The mantissa  $ma_i$  and  $mb_i$  each comprise a bit length of p bits when represented in the incoming format F. The output of the multiplication unit may have a floating point number format F'. The format F' need not be the same as format F, and may have a mantissa width large enough to hold the exact multiplication output - for example the mantissa product  $(c_i)$  may be twice as large as the mantissa bit length of the multiplicands  $a_i$  and  $b_i$ . In some cases, the multiplicands  $a_i$  and  $b_i$  may be represented in different formats such that the mantissas of  $a_i$  and  $b_i$  may have different bit lengths. In such cases, the multiplication output may have a floating point format F' where the mantissa product is the sum of the mantissa bitlength of  $a_i$  and the mantissa bit length of  $b_i$ .

[0061] Irrespective of whether the input sets have the same mantissa lengths, when the mantissa of the product c<sub>i</sub> has a bit length at least as long as the sum of the bit lengths of the mantissas of the multiplicands a<sub>i</sub> and b<sub>i</sub>, the dot product unit 100 using separate multiplication and addition described in FIG.1 has the same precision as the dot product unit 200 using fused multiplication and addition units, assuming no overflow or underflow, because there is no rounding required. However, if the second format F' is not wide enough to hold the exact multiplication output then performing dot product using the dot product unit 200 implementing fused multiplication and addition unit is more precise.

**[0062]** Whether using fused multiplication and addition or separately performing multiplication and addition, different orderings of the input pairs as multiplicands may yield different results. This is because of the effect of certain phenomenon such as catastrophic cancellation occurring when accumulating values in floating-point numbers.

**[0063]** Some arrangements of floating point adders providing faster computation include arrangements for performing parallel summation. These can also be used to reduce the latency of the network. For example, Fig. 1 shows a particular implementation of a network of floating point adders taking the outputs of the multiplication units 102a, 102b, 102c and 102d. The illustrated network of floating point adders in Fig. 1 is a balanced tree (or a balanced tree adder), for performing parallel summation and aimed at reducing latency.

With such a configuration, addition of 'n' floating-point numbers (i.e. in Fig 1, the multiplication outputs  $c_i$ ) can be realized using  $\lceil \log_2(n) \rceil$  stages.

**[0064]** Further, in generalized examples the tree adder need not be a balanced structure. The tree adder can instead add the floating-point numbers using a single adder at every different stage. For example, any two floating point numbers are added in a first stage to generate a first sum value. Further, the first sum value is added to another floating-point number in a second stage using a second adder to generate a second sum value and so on. The latency of the arrangement increases in this example compared to a balanced tree adder.

[0065] Consider the mantissa products L, -L, M and N are provided as an input to the adder unit either as the outputs of the multiplication units when using the dot product unit 100 using separate multiplication and addition units described in FIG.1 or as intermediate multiplication values when using the dot product unit 200 implementing fused multiplication and addition units. When performing the addition, in all these examples, in each stage the output values of the accumulation are rounded or truncated in order to fit the output value into its finite representation. Multiple rounding may result in catastrophic cancellations. For different orders in which each input is provided to a tree adder, different outputs are generated. A catastrophic cancellation can occur when very small numbers are added to very large ones, and may cause significant bits of the result to be lost due to rounding. E.g., when summing a large positive number, L, the corresponding negative number, -L, and two small positive numbers M and N, the precise value of the sum is (M+N). An arrangement of floating point additions summing L and -L in a first primary adder and M and N in a second primary adder ought to give the final result (M+N). However, if the inputs are ordered differently and the primary adders perform the sums (L+M) and (-L+N), and L is much larger than M and N, then the outputs of the primary adders could be rounded to L and -L, giving an overall output of 0. Similar effects can be observed when using a network of fused multiplication and addition units.

20

30

**[0066]** As discussed above, the existing methods of processing floating point numbers, such as performing dot product using separate multiplication and addition units as described in FIG.1 or using fused multiplication and addition units as described in FIG.2 generate output values of varying precision based on the order in which the numbers are provided as the input. That is, a certain order of providing the inputs generates the best result which is the closest approximation to the actual dot product of the numbers. Other orders of providing the inputs may generate results which are not so close to the actual dot product

of the numbers. Thus, based on the order in which the inputs are provided, there could be a range of results obtained, around the actual dot product of the floating-point numbers.

**[0067]** The varying precision of the results obtained is due to reasons such as truncation errors or rounding errors, and catastrophic cancellation as discussed earlier. Also, the delay in obtaining the dot product for a large array of numbers is drastic, as the multiplications and additions happen over several sequential steps. Even though the method of performing multiplication and addition using separate multiplication and addition enables the multiplications to occur in parallel, and then some of the additions to be performed in parallel, the overall addition still needs to be performed in various stages to generate a final output value. Further, re-normalizing and rounding is performed in each stage, which increases the delay in generating the output value. Therefore, there is a need for a method of processing a set of floating-point numbers more precisely and with less delay.

**[0068]** Described herein is a hardware implementation and method of processing a set of k floating-point numbers concurrently. The method includes receiving the inputs in their incoming format, generating the output of the multiplication unit in a first (intermediate) format, and then converting the first format to a number in a second (intermediate) format for performing addition (the output of which may be in a further format that may or may not be the same as any of the previously mentioned formats). More precisely the method includes receiving a floating-point number from each set in an incoming format, generating a product number having a first format by performing mantissa multiplication and exponent summation concurrently while emulating the precision of a chosen conventional multiplier. Further, the method includes processing the numbers in the second format concurrently (e.g. obtaining a sum by performing a single sum over all the numbers in the set, in contrast to performing multiple sums across the set) to generate an output value.

**[0069]** FIG. 3 is a block diagram illustrating an example of an implementation of an architecture for processing a set of k floating-point numbers. The architecture 300 is a dot product unit for performing multiplication and addition of a large array of 2k floating point numbers to generate an output value. The large array of 2k floating point numbers comprise a first set of k floating-point numbers  $(a_0, a_1, a_2... a_{k-1})$  and a second set of k floating-point numbers  $(b_0, b_1, b_2... b_{k-1})$ . The architecture is particularly suitable for calculating the dot product of large arrays of numbers but can be used to calculate the dot product of two, or more than two, numbers as required. The architecture 300 comprises a mantissa multiplication unit 301, a format conversion unit 302, an exponent addition unit 303, a maximum exponent detection unit 304, an alignment unit 306, a processing unit 308, and a re-normalizing unit 310. Each number in the first set of 'k' floating-point numbers comprises

a mantissa ma<sub>i</sub> and an exponent ea<sub>i</sub>. Each number in the second set of 'k' floating-point numbers comprises a mantissa mb<sub>i</sub> and an exponent eb<sub>i</sub>. Each number in the first set of 'k' floating-point numbers is having a mantissa bit length of 'p' bits and each number in the second set of 'k' floating-point numbers is having a mantissa bit length of 'q' bits. Both sets of 'k' floating-point numbers may be signed numbers or unsigned numbers. In the case of signed numbers, the numbers would also each comprise a sign bit (sa<sub>i</sub> or sb<sub>i</sub>) as well as the mantissa and exponent. However, some floating-point formats (e.g. unsigned formats) may not include a sign bit.

**[0070]** The first set of k floating-point numbers  $(a_0, a_1, a_2... a_{k-1})$  and the second set of k floating-point numbers  $(b_0, b_1, b_2... b_{k-1})$  can be received in an input unit (not shown in the figure). The input unit can be a storage or a memory unit that can store the received inputs. Both sets of 'k' floating-point numbers are stored in an incoming format. Both sets of 'k' floating-point numbers may be of the same format or of different incoming formats for example if  $p \neq q$ .

10

15

20

[0071] The bit-length of the mantissa and exponent of the numbers in the incoming format is identified based on the type of the floating-point number format. The incoming format may be a predefined format that the architecture 300 is designed to receive, or may be identified on a task-by-task basis (e.g. by a controller, not shown). Examples of various types of the floating-point number formats include but are not limited to IEEE formats including half precision floating-point numbers (16 bit float), single precision floating-point numbers (float) and double precision floating-point numbers (double), or other formats such as a brain floating-point numbers (bfloat16). In one example, for the explanation of the method, we consider both the number a<sub>i</sub> in the first set and number b<sub>i</sub> in the second set to have the same incoming format as IEEE single precision floating-point format having a mantissa (mai or mbi) with a bit length of 23 bits and an exponent (eai or ebi) with a bit length of 8 bits. In another example the informing formats of both the number ain the first set and number b<sub>i</sub> in the second set may be different. For example, we consider IEEE single precision floating-point format as the incoming format of the number a in the first set having a mantissa mai with a bit length of 23 bits and an exponent eai with a bit length of 8 bits, and we consider brain floating-point format as the incoming format of the number bi in the first set having a mantissa mbi with a bit length of 7 bits and an exponent ebi with a bit length of 8 bits. However, it is understood that the invention is not limited to these (combinations of) formats and a person skilled in the art would understand that the architecture 300 could be implemented to use numbers in any type of the floating-point number format to perform the method described herein. The mantissa mai of each number in the first set of 'k' floatingpoint numbers and the mantissa mbi of each number in the second set of 'k' floating-point numbers stored in an incoming format is provided to a mantissa multiplication unit 301. Prior to providing the input the fractional part of the mantissa ma<sub>i</sub> having the bit length of 'p' bits may be extended by the implicit leading bit to obtain a normalised mantissa of p+1 bits. Similarly, the fractional part of the mantissa mb<sub>i</sub> having the bit length of 'q' bits may be extended by the implicit leading bit to obtain a normalised mantissa of q+1 bits.

**[0072]** The mantissa multiplication unit 301 comprises a plurality of multiplier units configured to generate 'k' product numbers  $(z_0, z_1, z_2... z_{k-1})$  in a different, first, format, having a bit length of 'r' bits as described in more detail below. Each multiplier unit is configured to perform a mantissa multiplication of corresponding mantissas from the first set and second set of k floating point numbers to obtain an intermediate mantissa product:

$mab_i = ma_i \times mb_i$

10

15

20

2.5

30

35

**[0073]** The bit length of the full precision result obtained when performing the mantissa multiplication may be larger/smaller compared to r bits. Thus, mantissa multiplication unit 301 fits the output of the plurality of multipliers into a bit length of 'r' bits thereby generating product number  $z_i$  in the first format. Thus, the output of each multiplier unit, mantissa product mab<sub>i</sub> is either rounded to r bits or padded with extra (zero) bits to fit the mantissa product into r bits. The value of bitlength 'r' is set based on the required precision of the dot product unit 300. In particular, 'r' can be (broadly) considered as accounting for the number of bits required to emulate the precision of the multiplication aspect of a conventional dot product unit. It will consist of a number of explicit leading bits and a number of fractional bits. As the input floating point numbers  $a_i$  and  $b_i$  are normalized before multiplication, the product number having bit length of r bits in the first format comprises two explicit leading bits (as the multiplication of two numbers between 1.0 inclusive and 2.0 exclusive may generate a number between 1.0 inclusive and 4.0 exclusive). Hence there is a need to increase the bitlength by one to account for the explicit leading '1' bit position during summation.

[0074] In a first case scenario, the hardware implementation of a dot product unit 300 may emulate the precision of P bits obtained with the dot product unit 100 using separate multiplication and addition units. In this context, a precision of P bit means that the dot product unit 300 achieves a precision not less than the worst-case precision achieved by the (emulated) dot product unit 100 generating a final output having a mantissa of P bits. In other words, P is the bit length of the mantissa output when performing multiplication and mantissa input when performing addition when implementing separate multiplication and addition units to perform dot product. However, for any given bit length P, the actual precision of the dot product unit 100 (as already discussed, due to the accumulation aspect)

will depend on the order in which the inputs are processed. As such, in the present context, the dot product unit 300 is configured to be at least as precise as the worst-case precision that the emulated dot product unit 100 might achieve. To achieve this, when the hardware implementation of a dot product unit 300 emulates the precision of P bits obtained with the dot product unit 100, the bit length of 'r' bits is set as 'r=P+2' bits.

[0075] In a second case scenario, the hardware implementation of dot product unit 300 may emulate the precision of Q bits obtained with the dot product unit 200 using fused multiplication and addition units. Again, in this context, a precision of Q bits means that the dot product unit 300 achieves a precision not less than the worst-case precision achieved by the (emulated) dot product 200 generating a final output having a mantissa of Q bits. In other words, Q is the bit length of the mantissa output and accumulation mantissa input when performing multiplication and addition when implementing fused multiply and add units to perform dot product. However, for any given bit length Q, the actual precision of the dot product unit 200 (as already discussed, due to the accumulation aspect) will depend on the order in which the inputs are processed. As such, in the present context, the dot product unit 300 is configured to be at least as precise as the worst-case precision that the emulated dot product unit 200 might achieve. To achieve this, when the hardware implementation of dot product unit 300 emulates the precision of Q bits obtained with the dot product unit 100, the bit length of 'r' bits is set as 'r= max (Q+2, p+q+3)' bits.

10

15

25

[0076] As already mentioned, if the value of 'r' is less than the full precision bit length of mantissa multiplication i.e. p+q+2, then the mantissa product is faithfully rounded to obtain the desired bit length. Further, if the value of 'r' is greater than the full precision bit length of mantissa multiplication i.e. p+q+2, then the mantissa product is padded with zeros to obtain the desired bit length.

**[0077]** That is, if p+q+2>r bits, the mantissa product (mab<sub>i</sub>) is faithfully rounded to r bits to obtain product number  $z_i$ . Rounding the mantissa product can be achieved in many ways. In one example, the plurality of multiplier units can be implemented using a truncated multiplier. When using the truncated multiplier to perform mantissa multiplication, the truncated multiplier directly computes r bits of the mantissa product mab<sub>i</sub> by truncating the extra bits over 'r' bits thereby directly producing the product number  $z_i$  in the first format. In another example, the plurality of multiplier units can be implemented using a full multiplier. When using the full multiplier to perform mantissa multiplication, the multiplier computes an intermediate mantissa product mab<sub>i</sub>, having a bit length of larger than 'r' bits which is further rounded to 'r' bits thereby generating the product number  $z_i$  in the first format.

**[0078]** Further if p+q+2 < r bits, the mantissa product (mab<sub>i</sub>) is padded with extra least-significant bits to generate product numbers  $z_i$  having r bits. Thus, the product number  $z_i$  can be represented as a fixed point value mab<sub>i</sub>2<sup>-r+2</sup>.

**[0079]** Similarly, in order to emulate the precision of dot product unit 200, the value of 'r' is greater than the full precision bit length of mantissa multiplication, i.e. p+q+2, by at least one position (if  $Q+2 \le p+q+3$ ) or more (if  $Q+2 \ge p+q+3$ ). Hence the mantissa product is padded with zeros to obtain the desired bit length.

**[0080]** Concurrently, the exponent ea<sub>i</sub> of each number in the first set of 'k' floating-point numbers and the exponent eb<sub>i</sub> of each number in the second set of 'k' floating-point numbers stored in an incoming format is provided to an exponent addition unit 303. The exponent addition unit comprises a plurality of adder units, each adder unit configured to generate an exponent sum,

**[0081]** The format conversion unit 302 receives 'k' product number numbers  $(z_0, z_1, z_2... z_{k-1})$  from the mantissa multiplication unit 301. The format conversion unit 302 converts 'k' product numbers  $(z_0, z_1, z_2... z_{k-1})$  in a first format to 'k' numbers in a different, second format  $(y_0, y_1, y_2... y_{k-1})$ , as described in more detail below.

[0082] The format conversion unit 302 converts the 'k' product numbers ( $z_0$ ,  $z_1$ ,  $z_2$ ...  $z_{k-1}$ ) in the first format to numbers in the second format. This comprises converting each product number  $z_i$  in the set of 'k' product numbers to a number 'y<sub>i</sub>'. The format conversion unit 302 converts the product numbers  $z_i$  having a bit length of 'r' bits (in first format) to create the number 'y<sub>i</sub>' with a bit length of 'n' bits (to represent a second format). The bit length of 'n' bits is obtained by adding both one or more extra most-significant bits (MSBs) and one or more extra least-significant bits (LSB) to the product number  $z_i$  (of bit length 'r' bits in the first format. Thus, the bit length 'n' is always greater than the bit length 'r' of the product numbers generated and hence greater than the original mantissa of the input floating point numbers  $a_i$  and  $b_i$ .

[0083] If the sets of 'k' floating-point numbers received are unsigned floating point numbers, then the representation of unsigned numbers created, with a bit length of 'n' bits includes n magnitude bits. If the sets of 'k' floating-point numbers received are signed floating point numbers, then the extra MSBs added to the mantissa of the first format can comprise a bit representing a sign bit. Thus, the representation of signed numbers created, with a bit length of 'n' bits includes a sign bit and (n-1) magnitude bits. The sign bits of the

floating point numbers  $a_i$  and  $b_i$  are XORed to generate the sign bit of the corresponding number  $y_i$

[0084] The product numbers in the first format are converted to numbers in the second format based on the number of floating-point numbers (k) in the set. That is, the number of extra MSBs and LSBs added to the product numbers (z<sub>i</sub>) of the first format is determined based on the number 'k'. The bit length of the product numbers (z<sub>i</sub>) is extended to the MSB side by at least a logarithmic amount of the number 'k' ( $\lceil \log_2(k) \rceil$ ) bits and to the LSB side by at least a logarithmic amount of the number 'k-1' ( $[\log_2(k-1)]$ ) bits to obtain the number 'y<sub>i</sub>'. An extra bit is added to the MSB to represent a sign bit if the input floating point numbers are signed floating point numbers. Therefore  $[\log_2(k)] + 1$  extra MSBs and  $[\log_2(k-1)] +$ 1 LSBs are added on either side of the bit length 'r' of bit length of the product numbers (z<sub>i</sub>). That is, one additional bit (other than the  $\lceil \log_2(k) \rceil$ ) bits) in the extra MSBs added is assigned for the sign bit si. The sign bit is obtained by XORing the sign bits of the corresponding input floating point numbers ai and bi. The additional bit (other than the  $\lceil \log_2(k-1) \rceil$ ) bits) in the extra LSBs added is a precision bit, for obtaining extra precision. The extra MSBs and LSBs added prevent overflow or underflow of bits, while processing the set of 'k' numbers which is explained in detail later. The numbers of extra MSBs and LSBs added to each side could be the same or different in different examples. In general, the bit length 'n' of the number 'yi' in the second format can be obtained as

20

$$n = r + [\log_2(k)] + [\log_2(k-1)] + x$$

bits

15

25

30

where x is an integer and preferably  $x \ge 1$ , and where the value of x depends on the number of extra bits added to represent leading bit, sign bit and precision bits, if any. For example, x may be as small as 1 when there are no sign bits in the original received numbers, or may be as small as 2 when the original received numbers do have a sign bit. In both cases, x may be larger to provide greater precision.

**[0085]** In a second different implementation, the product number  $z_i$  in the first format may comprise r + log(k-1) + 1 bits, instead of 'r' bits described in the above paragraphs, so that when performing the multiplication stage rounding (if p+q+2>r bits) as many bits as possible of the mantissa product are retained for addition. In such a case, in order to emulate the precision of P bits obtained with the dot product unit 100 using separate multiplication and addition units by the hardware implementation of a dot product unit 300, the bit length of 'r' bits is set as 'r=P+1-log(k-1)'.

**[0086]** In such a case, the format conversion unit 302 converts the product numbers  $z_i$  having a bit length of 'r+ log (k-1) +1' bits (in first format) to create the number 'y<sub>i</sub>' with a bit

length of 'n' bits (to represent a second format). The bit length of 'n' bits is obtained by adding one or more extra most-significant bits (MSBs) to the product number  $z_i$  of bit length 'r' bits in the first format. The bit length of the product numbers  $(z_i)$  is extended to the MSB side by at least a logarithmic amount of the number 'k'  $(\lceil \log_2(k) \rceil)$  bits. Also a number of additional bits can be added to the LSBs as precision bits, for obtaining extra precision. Thus, the bit length 'n' of the number 'y<sub>i</sub>' in the second format can be obtained as

$$n = r + \lceil \log_2(k) \rceil + \lceil \log_2(k-1) \rceil + x$$

bits

15

25

**[0087]** FIG. 4a illustrates the representation of a mantissa (either mantissa  $ma_i$  or  $mb_i$ ) in an incoming format in an example in which both sets of incoming numbers share a common format and FIG. 4b illustrates the representation of product numbers  $(z_i)$  in a first (intermediate) format. FIG. 4c illustrates the representation of signed numbers  $(y_i)$  in a second (intermediate) format. In FIG. 4a, the incoming format is shown as a brain floating point number with a mantissa bit length (p) of 7 bits.

**[0088]** FIG.4b shows the product numbers ( $z_i$ ) represented in a first format having a bit length of 'r' bits. As discussed above, the bit length of 'r' bits is set as 'r=P+2' bits or as 'r= max (Q+2, p+q+3)' bits based on the required precision. The output obtained by multiplying the mantissas (ma<sub>i</sub>) having bit length of p bits and (mb<sub>i</sub>), having bit length of q bits is truncated/ rounded to fit to r bits, if p+q+2>r. However, if p+q+2 < r bits, the output obtained by multiplying the mantissas (ma<sub>i</sub>) and (mb<sub>i</sub>) is padded with extra least-significant bits to generate product numbers  $z_i$  having r bits. Suppose the value of r bits is 16 bits. The representation of the product number in the first format comprises two explicit leading bits (LB) as a part of the r bits.

**[0089]** FIG. 4c illustrates the representation of signed numbers  $(y_i)$  in a third format. The representation in the FIG. 4c illustrates signed number ' $y_i$ ' with a bit length of  $n = r + \lceil \log_2(k) \rceil + \lceil \log_2(k-1) \rceil + 2$  bits. This is obtained by adding  $\log_2(k) + 1$  extra MSBs and  $\log_2(k-1) + 1$  extra LSBs to the bit-length 'r' of the mantissa. Thus, in an example when a set of 8 floating point numbers, for which the bit length r is set to 17 bits (e.g. extended from an initial bit length of 7 as shown in FIG 4a), are added, i.e. k=8, then the signed number in the second format will have a bit length of n=25 bits.

[0090] It is clear from the example in FIG. 4c, that the number 'y<sub>i</sub>' represented in a second format, as defined herein, comprises r bits which includes two bits assigned for representing the leading bits (LBs), a bit assigned for representing a sign bit (s<sub>i</sub>), and a further  $\lceil \log_2(k) \rceil$  bits as extra MSBs, and  $\lceil \log_2(k-1) \rceil + 1$  extra LSBs. As such, the number 'y<sub>i</sub>' of the second format is a signed number and comprises both a sign bit and magnitude bits (i.e. the bits

indicating the absolute magnitude of the represented value). The sign bit is assigned as a '0' or '1' bit based on whether the number is a positive or negative number.

**[0091]** In the example shown in FIG. 4c, the number 'y<sub>i</sub>' comprises  $\lceil \log_2(k-1) \rceil + 1$  extra LSBs added to the product numbers (z<sub>i</sub>). The number 'y<sub>i</sub>' could comprise  $\lceil \log_2(k-1) \rceil + u$  extra LSBs added to the mantissa (m<sub>i</sub>), where u is any integer, u≥1. Preferably, the number 'y<sub>i</sub>' comprises  $\lceil \log_2(k-1) \rceil + 1$  extra LSBs added to the product numbers (z<sub>i</sub>). The extra LSBs added to the product numbers (z<sub>i</sub>) increase the precision of the result obtained and reduce underflow of bits of the product number while aligning the number 'y<sub>i</sub>' which is explained in detail below.

[0092] Thus, in the example described in the above paragraphs where the incoming format is a signed floating point number and the first format is a number that has two explicit leading bits, at least  $\lceil \log_2(k) \rceil + 1$  extra MSBs and  $\lceil \log_2(k-1) \rceil + 1$  LSBs are added on either side of the bit length 'r' of product numbers  $z_i$  to create the number ' $y_i$ ', thus making the number of additional bits  $x \ge 2$ .

[0093] Similarly, in another example case, assuming the incoming format is an unsigned floating point number and the first format is a number that has two explicit leading bits,  $\lceil \log_2(k) \rceil$  extra MSBs and at least  $\lceil \log_2(k-1) \rceil + 1$  extra LSBs are added on either side of the bit length 'r' of product numbers ( $z_i$ ) to create the number ' $y_i$ ', thus making the number of the additional bits  $x \ge 1$ .

[0094] Thus, in a generalized example,  $x \ge 1$  and  $x \le 'r'$  bits, making the maximum bit length of number 'y<sub>i</sub>',

$$n = 2r + \lceil \log_2(k) \rceil + \lceil \log_2(k-1) \rceil$$

**[0095]** The extra MSBs and LSBs added to the product numbers (z<sub>i</sub>) other than the sign bit are initially assigned '0' bits in the second format. The sign bit is assigned as a '0' or '1' bit based on whether the number is a positive or negative number.

25

**[0096]** Further, the exponent sum 'eab<sub>i</sub>' (eab<sub>0</sub>, eab<sub>1</sub>, eab<sub>2</sub>, eab<sub>3</sub>...eab<sub>k-1</sub>) of each pair of floating point numbers ea<sub>i</sub> and eb<sub>i</sub> in the first incoming format is provided as an input to the maximum exponent detection unit 304. The input 'eab<sub>i</sub>' to the maximum detection unit is provided from the exponent addition unit 303 as shown in FIG. 3. In some other arrangements, the exponent sums may be passed through the format conversion unit 302 to the maximum exponent detection unit 304.

**[0097]** The maximum exponent detection unit 304 identifies the maximum exponent sum  $(e_{max})$  from the k exponent sums  $(eab_0, eab_1, eab_2, eab_3...eab_{k-1})$ . The maximum exponent detection unit 304 detects the maximum exponent sum using various methods or functions. An example of a method of identifying the maximum exponent sum is using a binary tree structure. A method of identifying the maximum exponent sum  $(e_{max})$  is described in detail, below, with reference to FIG. 5. However, which option is preferable may depend on the available resources (e.g. parallel processing may be faster overall, but more computationally intensive).

10

15

20

2.5

30

35

[0098] In addition to being provided to the maximum exponent detection unit 304, the exponent sum values eab; are provided, from the exponent addition unit 303, as input to the alignment unit 306. The alignment unit 306 receives the exponent sums 'eabi' of each pair of floating point numbers a<sub>i</sub> and b<sub>i</sub> as a first input. The alignment unit 306 further receives the maximum exponent sum (e<sub>max</sub>) from the maximum exponent detection unit 304 as a second input and the number 'yi' from the format conversion unit 302 as the third input. In one implementation, the alignment unit 306 may comprise the format conversion unit implemented as a part of the alignment unit rather than a separate unit. In such case the alignment unit 306 receives the product number 'z<sub>i</sub>' as an input and converts the product number 'z<sub>i</sub>' into the number 'y<sub>i</sub>' before shifting. The alignment unit 306 aligns the magnitude bits of each number 'yi', thereby converting the number 'yi' to a different number (or integer v<sub>i</sub>) with a bit-length of n bits based on the maximum exponent. The method of aligning the number 'y<sub>i</sub>' is explained in detail with reference to FIG.5, but in summary the numbers in the second format are adjusted to be based on the maximum exponent, and the adjusted numbers  $(v_0, v_1, v_2...v_{k-1})$  are treated for convenience as integers for the subsequent processing in the processing unit 308.

**[0099]** Thereafter, the k integers ( $v_0$ ,  $v_1$ ,  $v_2...v_{k-1}$ ) thus generated are provided to the processing unit 308. The processing unit 308 is an adder unit. The processing unit 308 processes the k integers (i.e. the k aligned numbers) concurrently. That is the processing unit performs a process on all the integers in the set at the same time rather than, for example, processing elements of the set sequentially. The processing unit 308 performs addition of the k integers to generate an output value o. It is noted that addition of a negative number to a positive number is equivalent to performing a subtraction, and so the term processing is used herein to cover the acts of both addition and subtraction, alone or in combination.

**[00100]** The output value o from the processing unit 308 and the maximum exponent sum from the maximum exponent detection unit 304 is further provided into the re-normalizing

unit 310. The renormalizing unit 310 converts the output value from the processing unit to a floating-point number with a mantissa mi and exponent 'ei'. The format of the output value can be selected depending on the desired precision (e.g. depending on whether the aim is to emulate the precision of an arrangement such as that of Fig. 1 or Fig. 2). The output unit 312 stores the converted output value (i.e. the output floating point number).

**[00101]** FIG. 5 is a block diagram illustrating the different units in the implementation of the architecture 300 in FIG. 3. Consider a scenario where the set of k floating point numbers in the first format comprises three numbers, i.e. k=3. The input unit (not shown in the figure) may receive a first set of three floating point numbers ai (a0, a1, a2) and a second set of three floating point numbers bi (b0, b1, b2) as input.

**[00102]** The mantissa multiplication unit 301 receives the mantissas ( $ma_0$ ,  $ma_1$ ,  $ma_2$ ) of the first set of three floating point numbers ( $a_0$ ,  $a_1$ ,  $a_2$ ) and the ( $mb_0$ ,  $mb_1$ ,  $mb_2$ ) of the second set of three floating point numbers  $b_i$  ( $b_0$ ,  $b_1$ ,  $b_2$ ) as input from the input unit. The mantissa multiplication unit 301 comprises a plurality of multiplier units 501a, 501b, and 501c. Each multiplier unit is configured to generate a product number  $z_i$  having a bit length of 'r' bits. Each multiplier unit is configured to perform a mantissa multiplication of corresponding mantissas from the first set and second set of k floating point numbers to obtain a mantissa product:

$mab_i = ma_i \times mb_i$

20

30

15

10

**[00103]** The multiplier unit 501a multiplies the mantissas ma<sub>0</sub> and mb<sub>0</sub> of the floating point numbers a<sub>0</sub> and b<sub>0</sub> respectively to generate a product number  $z_0$ . Similarly, the multiplier unit 501b and 501c generate the product numbers  $z_1$  and  $z_2$  respectively.

**[00104]** As discussed earlier, the value of bitlength 'r' is set based on the required precision of the dot product unit 300. In a first case scenario, where the hardware implementation of dot product unit 300 emulates the precision of P bits obtained when performing dot product using separate multiplication and addition, the bit length of 'r' bits is set as 'r=P+2' bits. In a second case scenario, where the hardware implementation of dot product unit 300 emulates the precision of Q bits obtained when performing dot product using fused multiplication and addition, the bit length of 'r' bits is set as 'r= max (Q+2, 2p+3)' bits when both sets of floating point number have same incoming format (p=q) or 'r= max (P+2, p+q+3)' bits when both sets of floating point number have different incoming format (i.e.  $p\neq q$ ).

**[00105]** The plurality of multiplier units 501a, 501b and 501c may, in one example, be implemented using a truncated multiplier. When using the truncated multiplier to perform multiplication of the mantissas, the truncated multiplier directly computes r bits of the output

by truncating the extra bits over 'r' bits thereby directly producing the product number zi in a first format. In another example, the plurality of multiplier units 501a, 501b and 501c may be implemented using a full multiplier. When using the full multiplier to perform mantissa multiplication, the multiplier computes an intermediate mantissa product mabi, having a bit length of larger than 'r' bits which is further rounded to 'r' bits thereby generating the product number zi in the first format.

**[00106]** If p+q+2>r bits, the mantissa product (mabi) is faithfully rounded to r bits. Further if p+q+2 < r bits, the mantissa product (mabi) is padded with extra least-significant bits to generate product numbers zi having r bits.

**[00107]** Concurrently, the exponent addition unit 303 receives the exponents (ea<sub>0</sub>, ea<sub>1</sub>, ea<sub>2</sub>) of the first set of three floating point numbers (a<sub>0</sub>, a<sub>1</sub>, a<sub>2</sub>) and the (eb<sub>0</sub>, eb<sub>1</sub>, eb<sub>2</sub>) of the second set of three floating point numbers (b<sub>0</sub>, b<sub>1</sub>, b<sub>2</sub>) as input from the input unit. The exponent addition unit 303 comprises a plurality of adder units 503a, 503b and 503c. Each adder unit is configured to calculate the sum of the exponent ea<sub>i</sub> and the exponent eb<sub>i</sub> of floating point numbers in each set to generate an exponent sum eab<sub>i</sub> corresponding to each product number  $z_i$

15

**[00108]** The adder unit 503a is configured to add the exponent  $ea_0$  of the floating point number  $a_0$  and the exponent  $eb_0$  of the floating point number  $b_0$  to generate an exponent sum  $eab_0$ . Similarly, the adder units 503b and 503c generates exponent sums  $eab_1$  and  $eab_2$  respectively.

**[00109]** In examples where the first set of three floating point numbers  $a_i$  ( $a_0$ ,  $a_1$ ,  $a_2$ ) and a second set of three floating point numbers  $b_i$  ( $b_0$ ,  $b_1$ ,  $b_2$ ) are signed floating point numbers, the sign bits of the corresponding floating point numbers ai and bi are XORed to obtain the value of a sign bit  $s_i$  ( $s_0$ ,  $s_1$ ,  $s_2$ ) corresponding to the product numbers  $z_i$  ( $z_0$ ,  $z_1$ ,  $z_2$ ).

**[00110]** The output of the mantissa multiplication unit 301 is further provided to the format conversion unit 302. In other words the plurality of multiplier units 501a, 501b and 501c in the mantissa multiplication unit 301 provides the product numbers  $z_0$ ,  $z_1$  and  $z_2$  in the first format having a bit length of r bits to the format conversion unit 302. Further, the sign bits  $s_i$  ( $s_0$ ,  $s_1$ ,  $s_2$ ) if any are also provided to the format conversion unit 302. The format conversion unit 302 converts the set of three numbers in the first format to three numbers  $y_i$  in the second format as described with reference to FIG. 3. In this example, consider both sets of 3 floating point numbers in the incoming format are signed numbers and the set of k product

numbers in the first format comprises two explicit leading bits, holding the integer part of the mantissa. Therefore, the set of three floating point numbers are converted to three signed numbers having a bit-length of n bits including a sign bit  $s_i$  and (n-1) magnitude bits  $f_i$  including two explicit leading bits. In other example cases, the both sets of three floating point numbers in the incoming format could be unsigned numbers.

**[00111]** Further, the exponent sums 'eab<sub>i</sub>' (eab<sub>0</sub>, eab<sub>1</sub>, eab<sub>2</sub>, and eab<sub>3</sub>) from the exponent addition unit 303 are provided to the maximum exponent detection unit 304.

**[00112]** The maximum exponent detection unit 304 in FIG. 5 may comprise two maximum function logics to identify the maximum exponent sum. This is by way of example only, and other implementations may have a different structure for finding the maximum exponent, or similar structures but with a different number of logics to account for a different number of inputs.

**[00113]** In the example of using two maximum function logics, the first maximum function logic may receive the exponent sums  $eab_0$  and  $eab_1$ . The first maximum function logic identifies the maximum exponent value among  $eab_0$  and  $eab_1$ . Further, the output of the first maximum function logic and the exponent  $eab_2$  are provided to the second maximum function logic. The second maximum function logic identifies the maximum exponent value among the output of the first maximum function logic and t exponent  $eab_2$  to detect the  $e_{max}$  i.e. the maximum exponent sum among the input exponent sums  $eab_0$ ,  $eab_1$ , and  $eab_2$ .

**[00114]** As mentioned above, the maximum detection unit 304 can be implemented in different other ways. For example, maximum detection unit 304 can be implemented using a binary search tree.

**[00115]** Returning to the depicted example, the maximum exponent sum identified by the maximum detection unit 304 is provided as input to the alignment unit 306. Further, the exponent sums eab<sub>0</sub>, eab<sub>1</sub>, and eab<sub>2</sub> are provided as input to the alignment unit 306. Further the three signed numbers 'y<sub>i</sub>' in the second format are provided as input to the alignment unit 306. The alignment unit 306 aligns the magnitude bits f<sub>i</sub> of each signed number 'y<sub>i</sub>', based on the maximum exponent sum and the respective exponent sum of the exponents of the numbers generating the product number in the first format corresponding to the signed number. In other words, the magnitude bits of the signed numbers for which the corresponding product number did not already have the sum of exponents as the maximum exponent are shifted to account for the difference in exponent sum for the pair of numbers in both sets compared to the maximum exponent sum (effectively adding zeros before the first (or, at least, the first non-zero) magnitude bit, and removing trailing bits as required, to

25

re-align the magnitude bits as appropriate). The alignment unit 306 thus converts each signed number (' $y_i$ ') to another integer ( $v_i$ ) that is output by the alignment unit 306. The integer  $v_i$  is considered as a fixed point number format. Similarly, in case of unsigned numbers the alignment unit shifts the magnitude bits of the unsigned numbers based on the maximum exponent sum and the respective exponent sum of the numbers generating the product number in the first format corresponding to the unsigned number.

**[00116]** The conversion of the signed number ' $y_i$ ' to an integer  $v_i$  is illustrated with examples shown in FIG.6a- 6d. It will be appreciated, in describing this series of figures, that the starting point is the signed number ' $y_i$ ' in a second format number, as output by the format conversion unit 302, and the end point is the converted signed number  $v_i$  (integer  $v_i$ ) mentioned above. However, for ease of reference, the intermediary stages may also be referred to as signed numbers in the description below.

10

15

25

30

**[00117]** Consider an example of two sets of three floating point numbers, each floating-point number in an incoming format with an implicit leading bit and a sign bit separate to the mantissa. Each number has a mantissa  $m_i$  having a bit length of 7-bits in the first format (such as bfloat 16). Suppose the bit length product number  $z_i$  generated by multiplying the mantissa of two floating point numbers one from each set is set as r=17 bits. Thus, in this example, each number in a set of three numbers, when converted to the second format comprises a signed number  $y_i$  having a bit length 'n' (including a sign bit  $s_i$ ), where

20

$$n = r + \lceil \log_2(k) \rceil + \lceil \log_2(k-1) \rceil + 2 = 17 + \lceil \log_2(3) \rceil + \lceil \log_2(3-1) \rceil + 2$$

$$= 17 + 2 + 1 + 2 = 22$$

**[00118]** FIG. 6a illustrates the signed number 'y<sub>i</sub>' in the second format with a bit length of n bits. In an example, consider that the number shown FIG. 6a represents a signed number y<sub>0</sub> provided as input to the alignment unit 306. The alignment unit 306 comprises a plurality of subtraction modules 505. The alignment unit 306 further comprises a plurality of shifter units 506 and a plurality of complementing units 507.

**[00119]** The alignment unit 306 receives an exponent sum eab<sub>i</sub> as a first input from exponent addition unit 303, the maximum exponent sum e<sub>max</sub> as a second input from the maximum exponent detection unit 304 and a signed number 'y<sub>i</sub>' from the format conversion unit 302 as a third input. As explained in FIG.3, the format conversion unit 302 can, in one example, be implemented as a part of the alignment unit 306. The exponent addition unit 303 provides the exponent sum 'eab<sub>i</sub>' of the three numbers to each subtraction module.

Each of the subtraction modules receives an exponent sum eab<sub>i</sub> as a first input from exponent addition unit 303, the maximum exponent sum  $e_{max}$  as a second input from the maximum exponent detection unit 304. Each subtraction module calculates a difference ' $e_{di}$ ' between the maximum exponent sum ' $e_{max}$ ' and the exponent sum 'eab<sub>i</sub>' of two numbers number. In FIG. 5, a first subtraction module receives an exponent eab<sub>0</sub> of two first numbers from exponent addition unit 303 and the maximum exponent sum  $e_{max}$  from the maximum exponent detection unit 304. The first subtraction module calculates a first difference referred to as  $e_{do}$  in FIG.5. Similarly, the remaining subtracting modules calculate the differences  $e_{d1}$  and  $e_{d2}$ , as shown in FIG.5. As shown, the plurality of subtraction modules calculates the differences  $e_{di}$  for each number in parallel, but other arrangements are possible – e.g. a single subtraction module performing each subtraction in series. Returning to the example as depicted, each calculated difference  $e_{d0}$ ,  $e_{d1}$ , and  $e_{d2}$  from the plurality of subtraction modules 505 is further provided to a corresponding shifter unit among the plurality of the shifter units 506.