US 20190295209A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2019/0295209 A1

# Kodama et al.

# (10) Pub. No.: US 2019/0295209 A1 (43) Pub. Date: Sep. 26, 2019

#### (54) IMAGE PROCESSING APPARATUS, DATA PROCESSING APPARATUS, AND IMAGE PROCESSING METHOD

- (71) Applicant: CANON KABUSHIKI KAISHA, Tokyo (JP)

- (72) Inventors: Shigeo Kodama, Tokyo (JP); Kohei Kishi, Kawasaki-shi (JP)

- (21) Appl. No.: 16/296,735

- (22) Filed: Mar. 8, 2019

#### (30) Foreign Application Priority Data

| Mar. 23, 2018 | (JP) | 2018-056750 |

|---------------|------|-------------|

| Jan. 23, 2019 | (JP) | 2019-009773 |

#### **Publication Classification**

| (51) | Int. Cl.  |          |

|------|-----------|----------|

|      | G06T 1/20 | (2006.01 |

|      | G06N 3/04 | (2006.01 |

(52) U.S. Cl. CPC *G06T 1/20* (2013.01); *G06N 3/04* (2013.01)

# (57) **ABSTRACT**

There is provided with an image processing apparatus for performing image processing for an input image. Each of N processing modules refers to a processing result for a reference pixel different from a processing target pixel and generates a processing result for the processing target pixel. Each of the N processing modules generates a processing result for a first pixel included in the first pixel line and next generates a processing result for a second pixel. The second pixel is included in a second pixel line different from the first pixel line in the processing target region and becomes processable in accordance with the generation of the processing result for the first pixel.

FIG. 2

| <u>301</u> | <u>302</u> | <u>303</u> |                       |

|------------|------------|------------|-----------------------|

| 1/16       | 5/16       | 3/16       | * : PIXEL OF INTEREST |

| 7/16       | *          |            |                       |

| 304        | 305        | 8          |                       |

FIG. 4

# FIG. 6C FIG. 6D FIG. 6E

| * |  |

|---|--|

|   |  |

| -1 | 2 | -1 |

|----|---|----|

| -2 | 4 | -2 |

| -1 | 2 | -1 |

| -1 | -2 | -1 |

|----|----|----|

| -2 | 4  | -2 |

| -1 | -2 | -1 |

FIG. 6H

Patent Application Publication Sep. 26, 2019 Sheet 13 of 25

PIXEL TO BE PROCESSED BY IMAGE PROCESSING UNIT 110 PIXEL TO BE PROCESSED BY IMAGE PROCESSING UNIT 111 PIXEL TO BE PROCESSED BY IMAGE PROCESSING UNIT 112 PIXEL TO BE PROCESSED BY IMAGE PROCESSING UNIT 113 PROCESSING TARGET PIXEL IS ABSENT

N N L

FIG. 25A EXECUTION TIME OF **CALCULATION UNIT 2405 EXECUTION TIME OF CALCULATION UNIT 2404 EXECUTION TIME OF** CALCULATION UNIT 2403 **EXECUTION TIME OF** CALCULATION UNIT 2402 VOICE DATA a VOICE DATA b( VOICE DATA c VOICE DATA d(

#### IMAGE PROCESSING APPARATUS, DATA PROCESSING APPARATUS, AND IMAGE PROCESSING METHOD

## BACKGROUND OF THE INVENTION

#### Field of the Invention

**[0001]** The present invention relates to an image processing apparatus, a data processing apparatus, and an image processing method, and in particular to a data processing apparatus capable of parallelly executing data processing including a feedback loop.

#### Description of the Related Art

**[0002]** There is a demand for faster data processing in conjunction with an increase in the digital data amount of image data or the like. One of method for such speeding up data processing is parallel processing. Meanwhile, in some data processing, the result of processing data is used in the processing of subsequent data; that is, the processing has a feedback loop. In such processing, it is necessary to wait for propagation of information needed to process certain data. In addition, information of another propagation source is reflected in the information of the propagation source. Accordingly, there is a dependence between data. It is therefore difficult speed up processing by parallelization.

**[0003]** Japanese Patent Laid-Open No. 2000-125122 discloses a method of parallelizing error diffusion processing that is a kind of feedback processing. In the method of Japanese Patent Laid-Open No. 2000-125122, different calculation units are assigned to pixel lines, and one calculation unit sequentially processes pixels arranged in the X direction. The processing timing is shifted such that each calculation unit processes a pixel for which a diffused density error from another pixel is determined, thereby implementing parallelization.

# SUMMARY OF THE INVENTION

[0004] According to an embodiment of the present invention, an image processing apparatus for performing image processing for an input image comprises: N processing modules each configured to refer to a processing result for a reference pixel different from a processing target pixel and generate a processing result for the processing target pixel, wherein the N processing modules parallelly generate processing results for processing target pixels different from each other, the N processing modules are connected to transfer the processing results, processing results for each of N continuous pixels included in a first pixel line of a processing target region in the input image are sequentially generated in a predetermined order by the different processing module, and each of the N processing modules is further configured to generate a processing result for a first pixel included in the first pixel line and next generate a processing result for a second pixel, wherein the second pixel is included in a second pixel line different from the first pixel line in the processing target region and becomes processable in accordance with the generation of the processing result for the first pixel.

**[0005]** According to another embodiment of the present invention, an image processing apparatus for performing image processing for an input image comprises: N processing modules each configured to refer to a processing result

for a reference pixel different from a processing target pixel and generate a processing result for the processing target pixel, wherein the N processing modules parallelly generate processing results for processing target pixels different from each other, the N processing modules are connected to transfer the processing results, and each of the N processing modules acquires the processing result for the reference pixel from the same processing module regardless of the processing target pixel.

**[0006]** According to still another embodiment of the present invention, an image processing apparatus for performing image processing for an input image comprises: N processing modules each configured to refer to a processing result for a reference pixel different from a processing target pixel and generate a processing result for the processing target pixel, wherein the N processing modules parallelly generate processing results for processing target pixels different from each other, and the N processing modules are connected in a ring shape to transfer the processing results.

[0007] According to yet another embodiment of the present invention, an image processing method for performing image processing for an input image comprises: parallelly generating processing results for processing target pixels different from each other by N processing modules, wherein each of the N processing modules is configured to refer to a processing result for a reference pixel different from the processing target pixel and generate the processing result for the processing target pixel, and wherein the N processing modules are connected to transfer the processing results, wherein processing results for each of N continuous pixels included in a first pixel line of a processing target region in the input image are sequentially generated in a predetermined order by the different processing module, and each of the N processing modules generates a processing result for a first pixel included in the first pixel line and next generates a processing result for a second pixel, wherein the second pixel is included in a second pixel line different from the first pixel line in the processing target region and becomes processable in accordance with the generation of the processing result for the first pixel.

[0008] According to still yet another embodiment of the present invention, a data processing apparatus for performing processing for a sequentially input data group using a recurrent neural network comprises: a plurality of calculation units each configured to perform an operation corresponding to a hidden layer that forms the recurrent neural network, thereby repetitively generating an output result of the hidden layer and intermediate data to be recursively referred to, wherein one calculation unit of the plurality of calculation units is configured to perform the operation corresponding to the hidden layer while recursively referring to the intermediate data for the same hidden layer and transfer the output result of the hidden layer generated by the operation to a different calculation unit, so that the plurality of calculation units perform the processing for the data group using the recurrent neural network.

**[0009]** Further features of the present invention will become apparent from the following description of exemplary embodiments (with reference to the attached drawings).

## BRIEF DESCRIPTION OF THE DRAWINGS

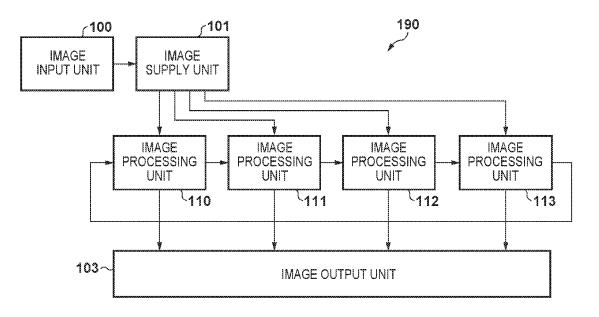

**[0010]** FIG. **1** is a block diagram showing an example of the arrangement of an image processing apparatus according to the first and third embodiments;

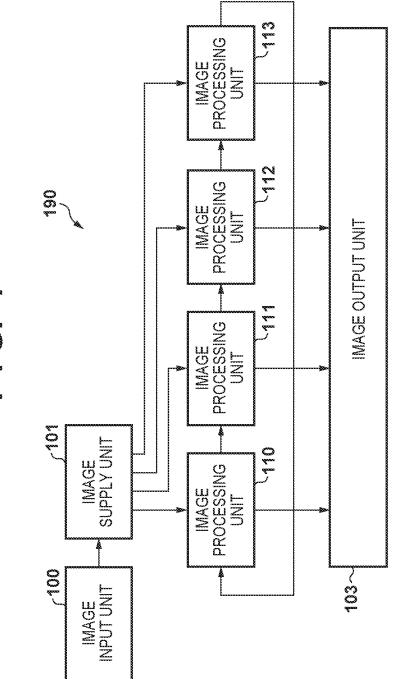

**[0011]** FIG. **2** is a view showing a band area with four lines and a band area with five lines according to the first embodiment;

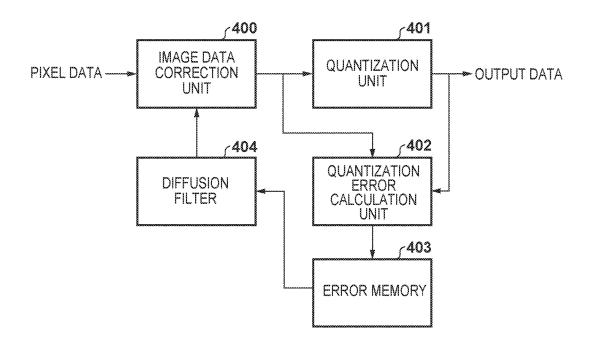

**[0012]** FIG. **3** is a view showing examples of reference pixels and diffusion coefficients in error diffusion processing;

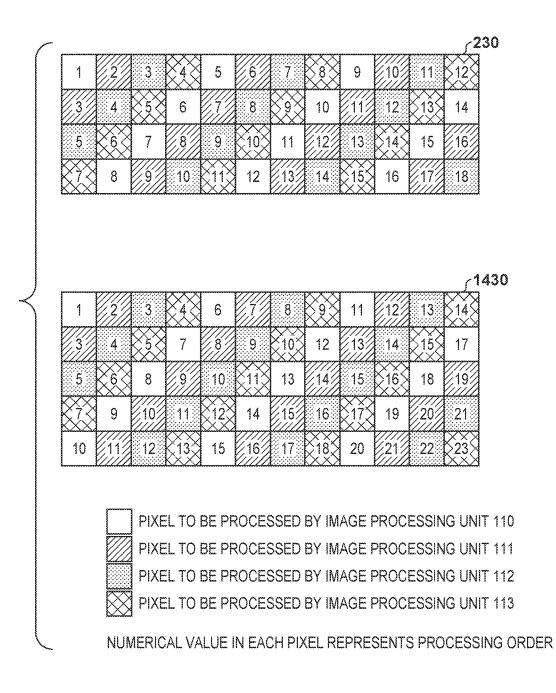

**[0013]** FIG. **4** is a block diagram showing an example of the arrangement of an image processing unit according to the first embodiment;

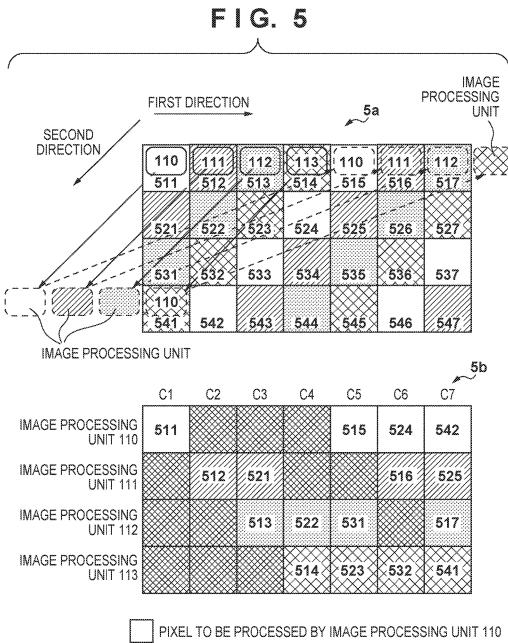

**[0014]** FIG. **5** is a view for explaining processing of a band area with four lines according to the first embodiment;

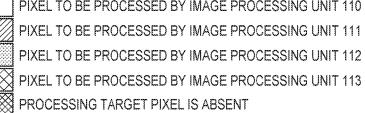

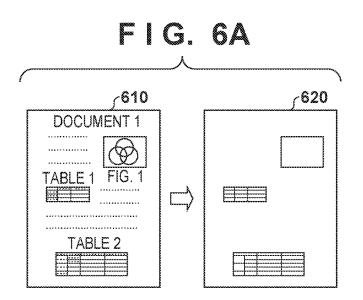

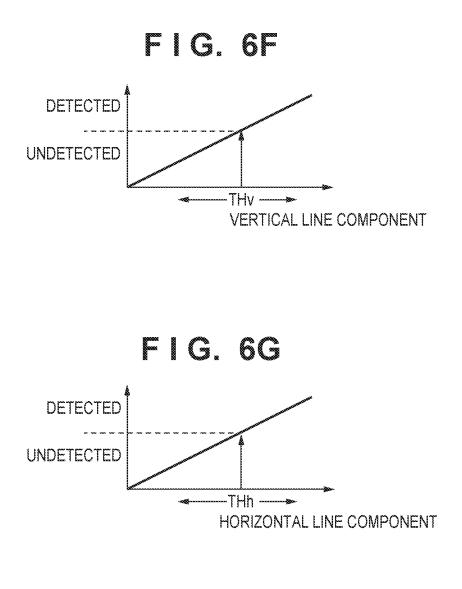

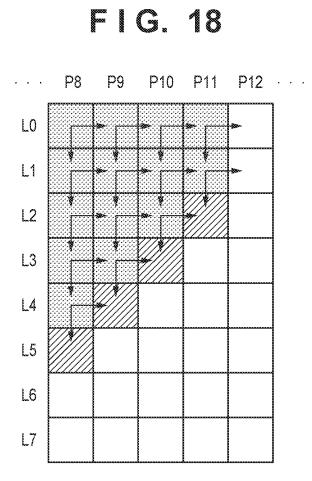

**[0015]** FIGS. **6**A to **6**H are views for explaining image processing according to the third embodiment;

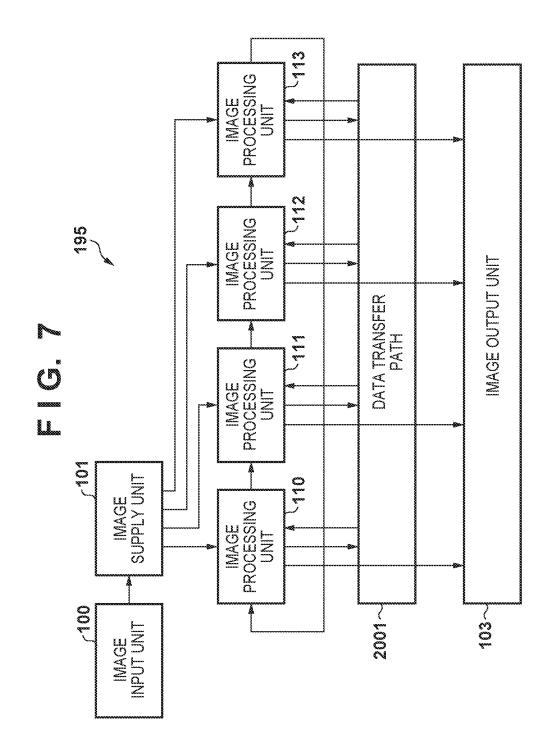

**[0016]** FIG. **7** is a block diagram showing an example of the arrangement of an image processing apparatus according to the second embodiment;

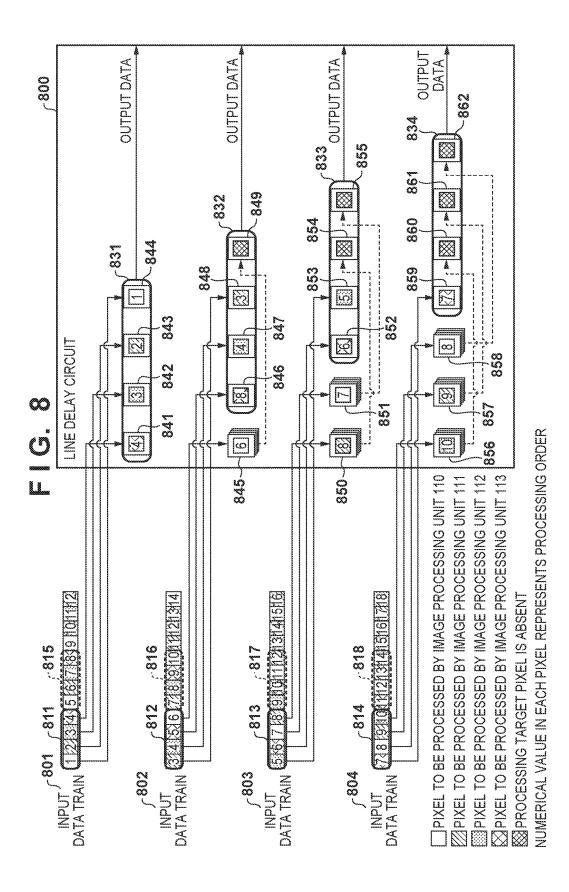

**[0017]** FIG. **8** is a view for explaining the arrangement of a line delay circuit according to the first embodiment;

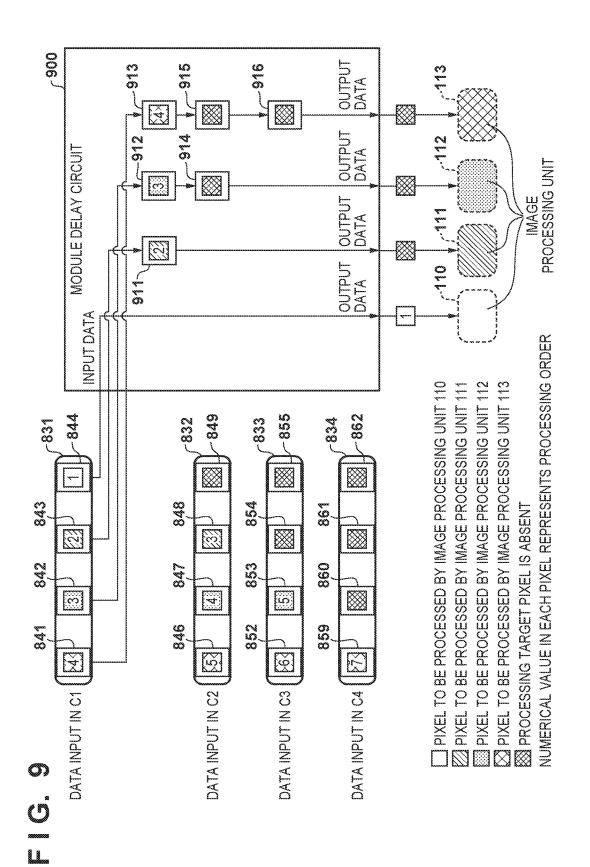

**[0018]** FIG. **9** is a view for explaining the arrangement of a module delay circuit according to the first and second embodiments;

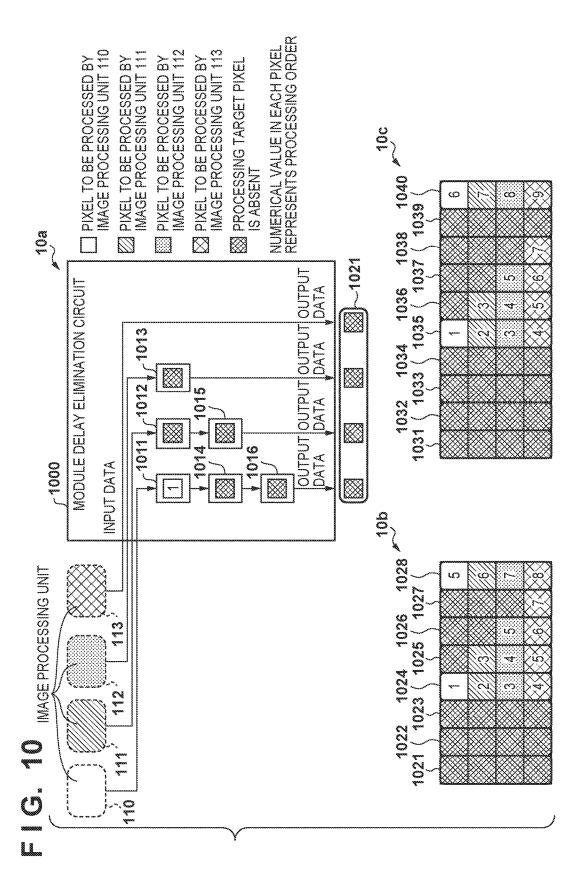

**[0019]** FIG. **10** is a view for explaining the arrangement of a module delay elimination circuit according to the first and second embodiments;

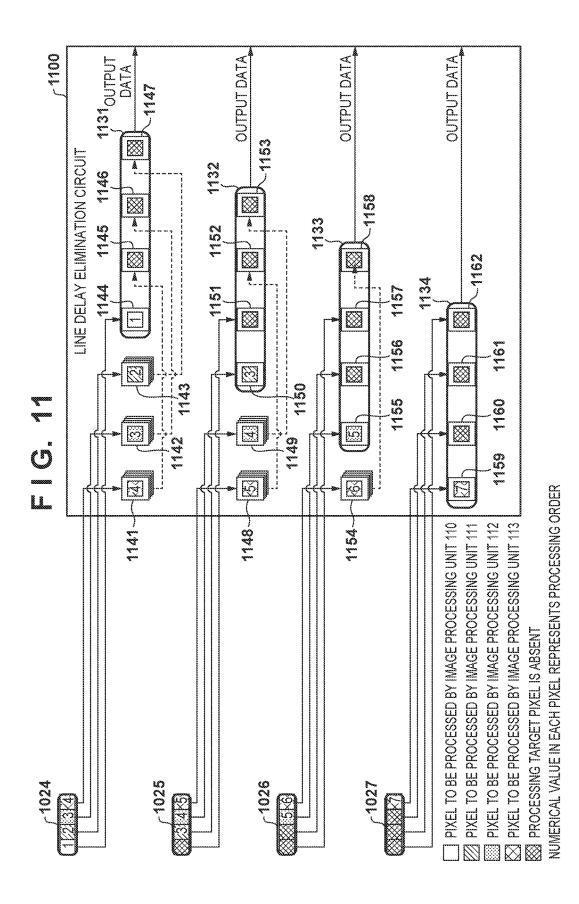

**[0020]** FIG. **11** is a view for explaining the arrangement of a line delay elimination circuit according to the first embodiment;

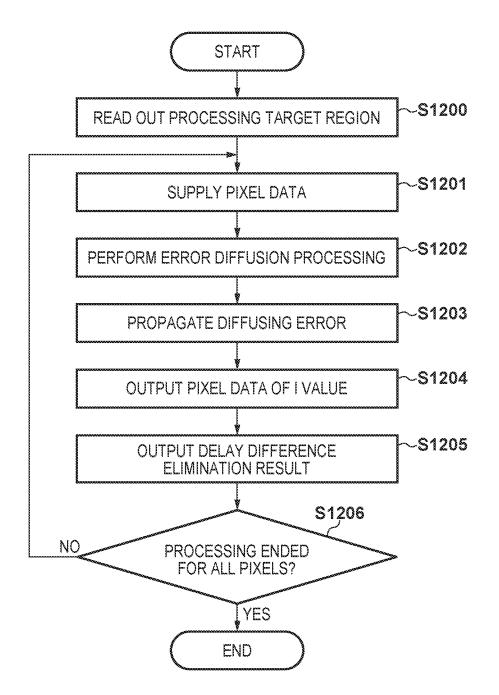

**[0021]** FIG. **12** is a flowchart showing an example of an image processing procedure according to the first embodiment;

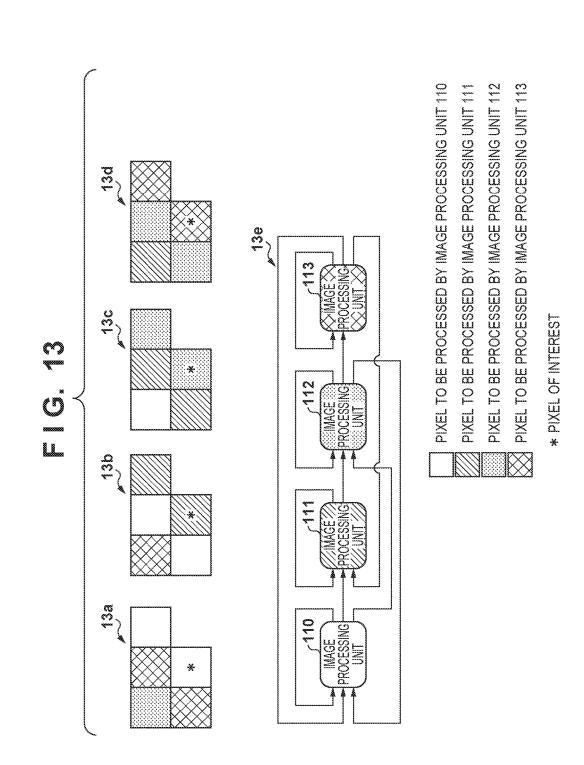

**[0022]** FIG. **13** is a view showing an example of the connection relationship of image processing units according to the first and second embodiments;

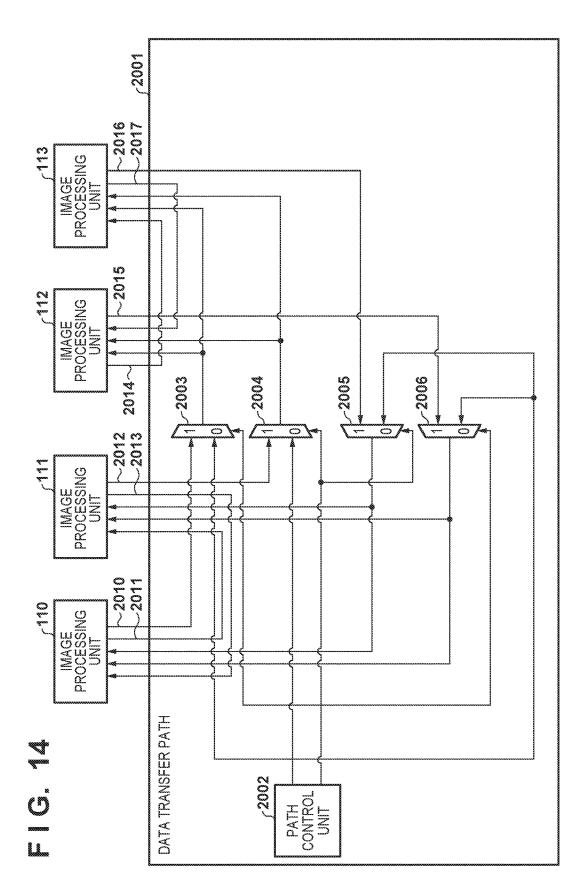

**[0023]** FIG. **14** is a view for explaining a data transfer path according to the second embodiment;

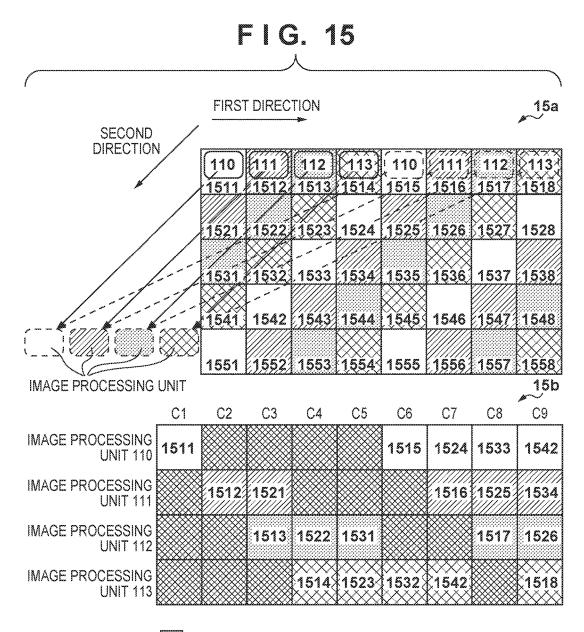

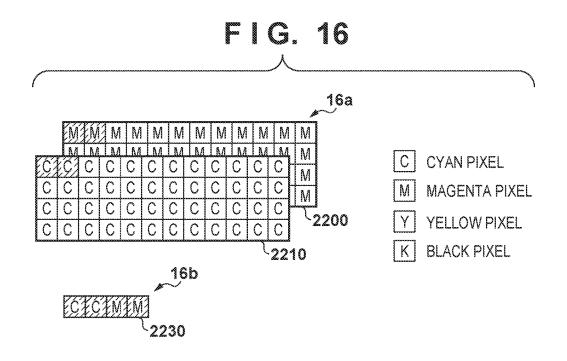

**[0024]** FIG. **15** is a view for explaining processing of a band area with five lines according to the first embodiment; **[0025]** FIG. **16** is a view for explaining processing of a band area according to the second embodiment;

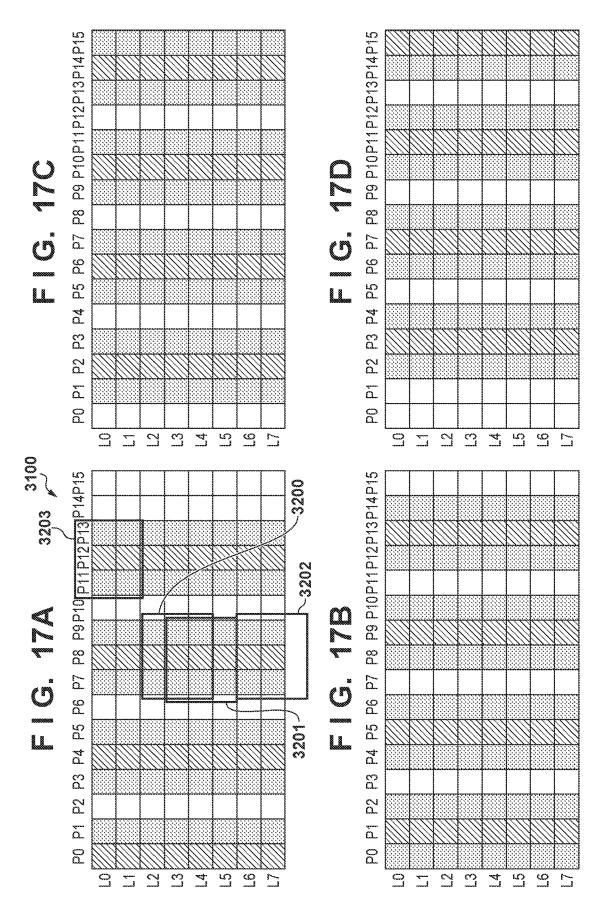

**[0026]** FIGS. **17**A to **17**D are views for explaining image processing according to the third embodiment;

**[0027]** FIG. **18** is a view for explaining image processing according to the third embodiment;

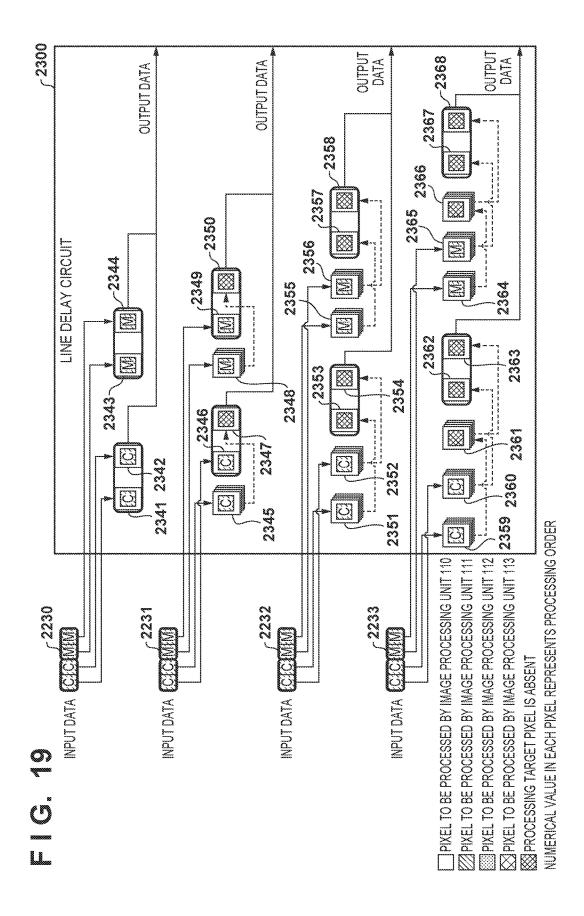

**[0028]** FIG. **19** is a view for explaining the arrangement of a line delay circuit according to the second embodiment;

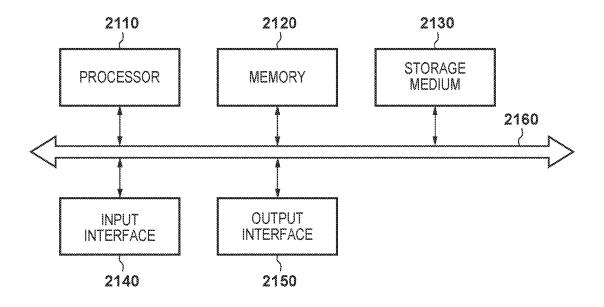

**[0029]** FIG. **20** is a view showing the basic arrangement of a computer usable in each embodiment;

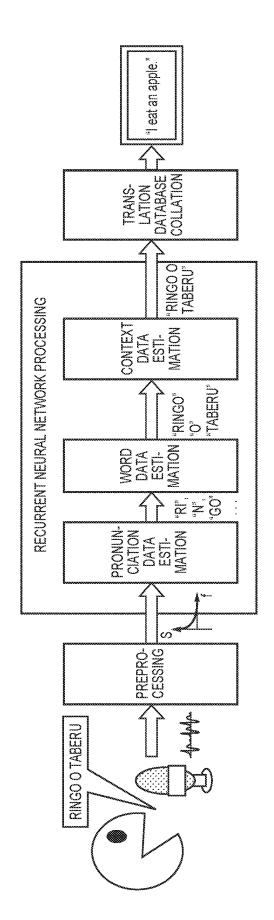

**[0030]** FIG. **21** is a conceptual view of a real-time machine translation system according to the fourth embodiment;

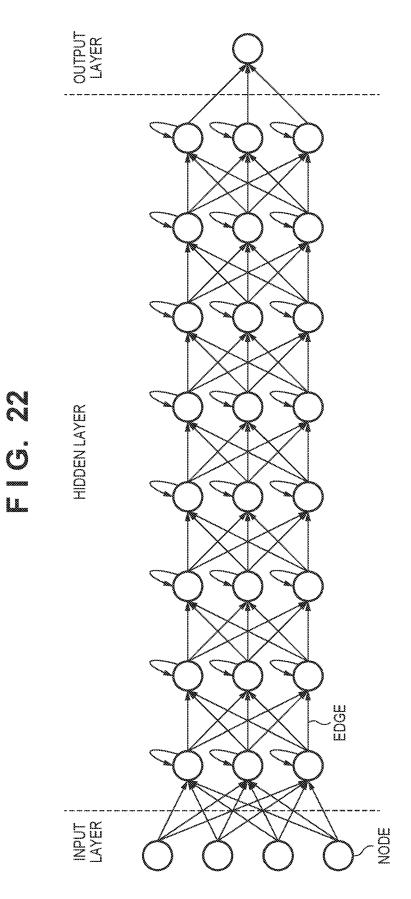

[0031] FIG. 22 is a view showing an example of the arrangement of a recurrent neural network;

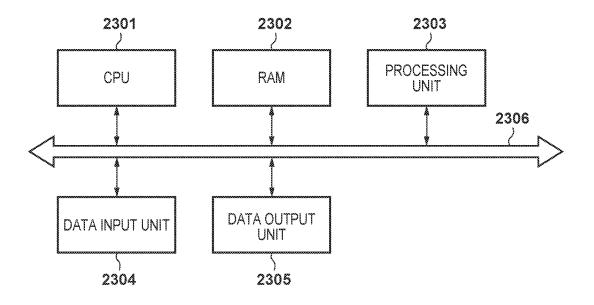

**[0032]** FIG. **23** is a block diagram showing an example of the arrangement of a data processing apparatus according to the fourth embodiment;

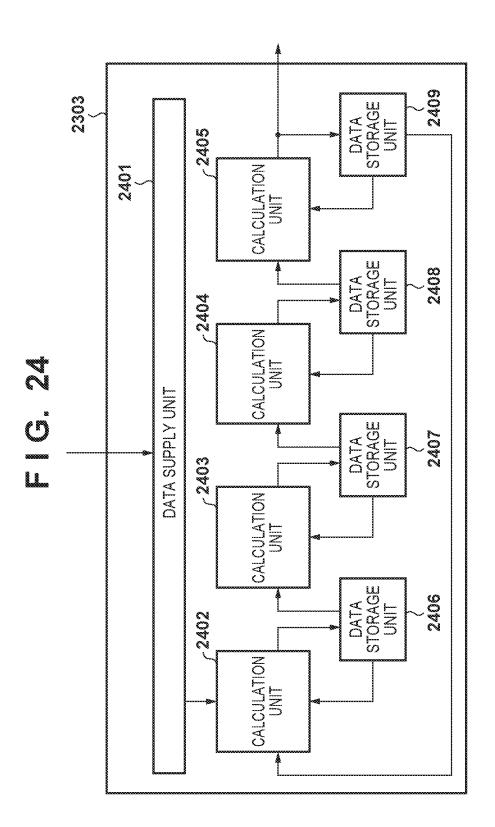

**[0033]** FIG. **24** is a block diagram showing an example of the arrangement of a processing unit according to the fourth embodiment; and

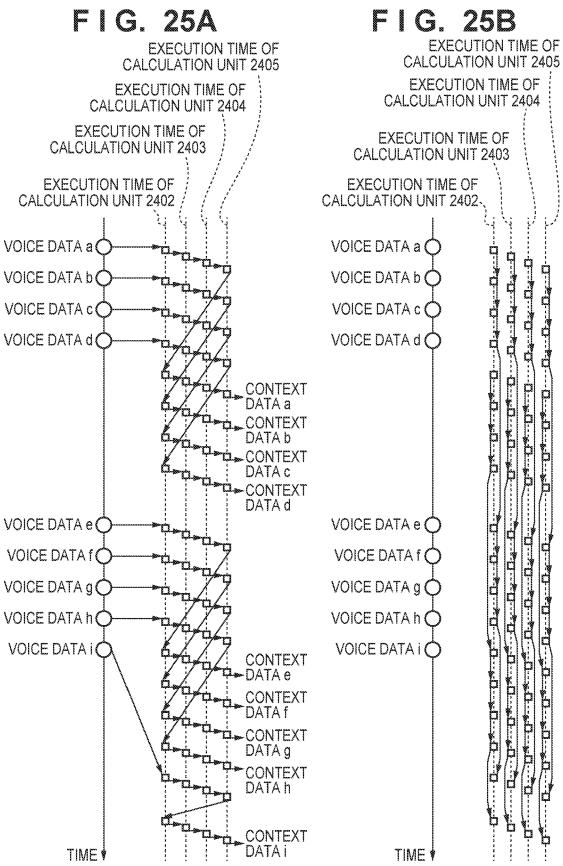

**[0034]** FIGS. **25**A and **25**B are views for explaining a data processing operation according to the fourth embodiment.

**[0035]** In image processing, a method of dividing an image into a plurality of divided data groups (band areas) and processing each band area sequentially from the left side is often used. On the other hand, the method of Japanese Patent Laid-Open No. 2000-125122 can process a band area whose height equals the number of calculation units. However, it is difficult to process a band area whose height is different from the number of calculation units. For example, in a case in which the number of pixel lines is larger than the number of calculation units, it is necessary to perform parallel processing while propagating errors for a pixel line to which no calculation unit is assigned. However, this is difficult.

**[0036]** According to an embodiment of the present invention, it is possible to parallelly perform data processing using the same processing module group for an arbitrary divided data group.

**[0037]** The embodiments of the present invention will now be described with reference to the accompanying drawings. However, the scope of the present invention is not limited to the following embodiments.

#### First Embodiment

[0038] An image processing apparatus according to the first embodiment performs image processing for an input image. The image processing apparatus according to this embodiment includes a plurality of image processing units (processing modules). In this embodiment, the image processing apparatus includes N image processing units. The N image processing units execute the same image processing for pixels of processing targets (to be referred to as processing target pixels hereinafter). Each image processing unit generates a processing result for a processing target pixel by referring to a processing result for a reference pixel different from the processing target pixel. A case in which the image processing apparatus performs error diffusion processing of converting a J-value image (i.e., an image where a pixel has one of J values) into an I-value image (I<J) will be described below. Error diffusion processing is one of processes using a feedback loop. That is, to obtain a processing result (quantization result) for a processing target pixel, it is necessary to refer to a processing result (a quantization error or a diffusing error) for a reference pixel. Additionally, the image processing apparatus according to this embodiment parallelly performs processing for a plurality of processing target pixels. That is, the plurality of image processing units parallelly generate processing results for processing target pixels different from each other. A pixel line or a line indicates a pixel train arranged in the main scanning direction and is also called a data train hereinafter.

**[0039]** FIG. **1** is a block diagram showing an example of the functional arrangement of an image processing apparatus **190** according to the first embodiment. The image processing apparatus **190** includes an image input unit **100**, an image supply unit **101**, an image output unit **103**, and image processing units **110** to **113**.

**[0040]** The image input unit **100** acquires the data of an input image. In this embodiment, the data of an input image is the data of a J-value image. The image input unit **100** acquires the data of the input image from, for example, an image acquisition device such as a scanner or a digital camera or a recording medium such as a hard disk drive.

Then, the image input unit **100** reads out the data of a processing target region in the input image and provides it to the image supply unit **101**. In this embodiment, the input image is divided into a plurality of processing target regions, and processing is performed for each processing target region. Each processing target region will be referred to as a band area hereinafter.

**[0041]** The size of a band area is not particularly limited. In one embodiment, the input image is divided into rectangular regions each having a predetermined number of mainscanning-direction pixels and a predetermined number of sub-scanning-direction pixels. Here, the number of mainscanning-direction pixels of the band area can equal the number of main-scanning-direction pixels of the input image. Additionally, in one embodiment, the number of main-scanning-direction pixels of the band area is larger than the number of sub-scanning-direction pixels. In this embodiment, the main scanning direction is the horizontal direction, and the sub-scanning direction is the vertical direction.

**[0042]** The image supply unit **101** supplies pixel data necessary for processing of processing target pixels to the plurality of image processing units at timings to perform the processing. For example, the image supply unit **101** can supply the image data of a band area acquired from the image input unit **100** to the image processing units **110** to **113**. At this time, the image supply unit **101** can supply the pixel data of J value of the band area to the image processing units **110** to **113** such that the image processing units **110** to **113** can perform parallel processing.

[0043] Each of the image processing units 110 to 113 performs the error diffusion processing for the pixel data of J value acquired from the image supply unit 101, thereby generating pixel data of I value. The plurality of image processing units are connected so as to transfer the processing result, as will be described later. The connection method between the plurality of image processing units is not particularly limited, and, for example, one image processing units. On the other hand, as will be described later with reference to 13e in FIG. 13, connection may be absent between the image processing units that do not need transfer of processing results.

[0044] In this embodiment, the plurality of image processing units are connected in a ring shape. That is, in addition to connection between the image processing unit 110 and the image processing unit 111, connection between the image processing unit 111 and the image processing unit 112, and connection between the image processing unit 112 and the image processing unit 113, connection between the image processing unit 113 and the image processing unit 110 exists. In other words, there exists a connection path that starts from an image processing unit, passes through all the remaining image processing units once, and returns to the first image processing unit. In one embodiment, processing results for N continuous pixels included in the first pixel line of the processing target region in the input image are sequentially generated in a predetermined order by the image processing units that are different from each other, as will be described later. Here, when the image processing units connected in a ring shape in a predetermined order are used, propagation of a diffusing error in the first direction (main scanning direction) can easily be performed.

[0045] The image output unit 103 generates image data of I value using the pixel data acquired from the image processing units 110 to 113. The image output unit 103 records the pixel data processed by the image processing units 110 to 113 in a memory (for example, a DRAM) while eliminating processing delays between the lines, thereby outputting image data of I value to the memory.

**[0046]** Processing performed by the image processing apparatus **190** will be described below in detail. First, error diffusion processing will be described. Error diffusion processing is image processing of sequentially performing processing of diffusing the difference (quantization error) between the input tone value of a processing target pixel and a quantization representative value that is the quantization error of the processing target pixel to an unprocessed pixel in the neighborhood of the processing target pixel. FIG. **3** shows the relationship between a processing target pixel, reference pixels, and diffusion coefficients in one example of error diffusion processing.

**[0047]** In the error diffusion processing, a diffusing error calculated by multiplying a quantization error in a reference pixel by a diffusion coefficient is propagated to a processing target pixel. The diffusion coefficient is a weight according to the relative positions of the processing target pixel and the reference pixel. To perform the error diffusion processing, it is necessary to wait for propagation of the diffusing error of a processed pixel to a reference pixel. When processing is performed by referring to a processing result for another pixel, as in the error diffusion processing, the order of processing needs to be determined in consideration of the dependence between the pixels.

[0048] For example, when performing error diffusion processing shown in FIG. 3, to process a processing target pixel 305 and determine the pixel value, all the processes of pixels 301 to 304 that are reference pixels need to be completed. When the processing of the processing target pixel 305 is completed, the diffusing error is propagated to the next pixel to be processed using the processing target pixel 305 as a reference pixel. A pixel for which the diffusing errors from all the reference pixels are determined is processed next.

[0049] FIG. 4 is a block diagram showing the detailed arrangement of the image processing unit 110. The image processing units 111 to 113 can also have the same arrangement as the image processing unit **110**. That is, the plurality of image processing units may have the same arrangement. The image processing unit 110 includes a correction unit 400, a quantization unit 401, an error calculation unit 402, an error memory 403, and a diffusion filter 404. As described above, each of the plurality of image processing units is formed as a processing module, and includes processing units (the correction unit 400, the quantization unit 401, the error calculation unit 402, and the diffusion filter 404) and a memory (the error memory 403). The physical arrangement of the image processing units 110 to 113 is not particularly limited. For example, the image processing unit 110 may include a circuit or a processing unit such as a processor configured to implement the functions of the correction unit 400, the quantization unit 401, the error calculation unit 402, and the diffusion filter 404 and a memory functioning as the error memory 403.

**[0050]** The correction unit **400** adds a cumulative value (correction value) of a diffusing error from a reference pixel to be described later to input pixel data of J value. The pixel

data of J value may be pixel data represented by, for example, 8 bits (256 tones) per pixel.

[0051] The quantization unit 401 quantizes the pixel data of J value corrected by the correction unit 400 into pixel data of I value. For example, the quantization unit 401 quantizes the pixel data of J value into a binary tone value corresponding to a density value of 0 or a density value of 255. The error calculation unit 402 calculates the error between the pixel data of J value corrected by the correction unit 400 and the pixel data of I value quantized by the quantization unit 401.

[0052] The error memory 403 holds the quantization error calculated by the error calculation unit 402. The error memory 403 can also hold the quantization errors of the reference pixels transferred from the remaining image processing units 111 to 113. The quantization error calculated by the error calculation unit 402 can also be transferred from the error memory 403 to the remaining image processing units 111 to 113. The diffusion filter 404 calculates a diffusing error by multiplying the quantization error of the reference pixel sent from the error calculation unit 402 or the error memory 403 by a diffusion coefficient. In addition, the diffusion filter 404 calculates the cumulative value of the diffusing errors for the processing target pixel and outputs the cumulative value to the correction unit 400.

**[0053]** As described above, the image processing unit **110** can quantize the input pixel data of J value using the pixel data of J value and the diffusing errors of the reference pixels, calculate the diffusing error from the quantization error, and propagates the diffusing error. Not that the error memory **403** may hold the diffusing error of each reference pixel in place of the quantization error of each reference pixel.

**[0054]** The arrangement of the image processing units **110** to **113** is not limited to the above-described arrangement. It is possible to use a processing unit having an arbitrary arrangement capable of receiving the quantization error or diffusing error from each reference pixel, quantizing the pixel value of the processing target pixel to calculate the quantization error, and transferring the quantization error or the diffusing error.

**[0055]** (Example of Processing for Band Area with Four Lines)

[0056] Error diffusion processing for a band area with four lines read from an input image by the image input unit 100 will be described below as a detailed example of processing. In this processing example, parallel processing with four parallel processes is performed using the four image processing units 110 to 113. In addition, for pixels that continue in the first direction as many as the number of parallel processes, different image processing units 110 to 113 perform processing (quantization processing). On the other hand, for a processable pixel that appears in the second direction as a result of processing performed for the processing target pixel by an image processing unit, the same image processing unit performs processing. One image processing unit repeats processing of a pixel located in the second direction. When processing of a pixel in the final data train (in this example, the fourth data train included in the band area) is performed, this image processing unit performs processing of a processable pixel existing in the first data train (in this example, the first data train included in the band area). The first direction is the main scanning direction in the following description. Additionally, the second direction can be defined in accordance with the positions of reference pixels.

[0057] The processing order will be described with reference to 5a in FIG. 5. In the following processing example, pixels adjacent to the processing target pixel on the upper left, upper, upper right, and left sides are used as the reference pixels, as shown in FIG. 3. Hence, a processable pixel is a pixel for which the pixels adjacent on the upper left, upper, upper right, and left sides have undergone the processing (that is, the quantization values and the quantization errors are calculated). As described above, in one embodiment, a reference pixel is located on the pixel line on the upper side of the processing target pixel or located on the left side of the processing target pixel on the same pixel line as the processing target pixel.

[0058] In a cycle C1, the processable pixel is only a pixel 511 at the processing start position. Hence, the image processing unit 110 processes the pixel 511 at the processing start position. Then, a pixel 512 for which processing of all the reference pixels is completed becomes a processable pixel. Here, the pixel 512 is located in the first direction (main scanning direction) from the processed pixel 511. Since the pixels 511 and 512 continue in the first direction, an image processing unit different from the image processing unit 110 that has processed the pixel 511, for example, the image processing unit 111 next to the image processing unit 110 processes the pixel 512 in a cycle C2. Note that the error reference range of the pixel 512 includes a region where no pixel exists. Here, this region is handled assuming that a processed pixel exists in this region, and a diffusing error from this pixel is absent. However, for example, if a diffusing error from another band is propagated, processing may be performed in consideration of this diffusing error.

[0059] In the cycle C2, the pixel 512 is processed by the image processing unit 111, and as a result, pixels 513 and 521 change to processable pixels. The pixel 513 is located in the first direction from the processed pixel 512. Since the pixels 511 to 513 continue in the first direction, an image processing unit different from the image processing units 110 and 111 that have processed these pixels, for example, the image processing unit 112 next to the image processing unit 111 processes the pixel 513 in a cycle C3.

[0060] On the other hand, the pixel 521 is located in the second direction different from the first direction from the processed pixel 512. For this reason, the pixel 521 is processed in the cycle C3 by the image processing unit 111 that has completed the processing of the reference pixel for the pixel 521 in the cycle C2. In this way, in this processing example, the second direction is determined to be the direction from the pixel 512 to the pixel 521, that is, the direction advancing downward by one line and leftward by one pixel. In the subsequent processing cycles, the image processing unit 111 sequentially processes pixels in four data trains in the second direction. That is, the image processing unit 111 processes a pixel located at a predetermined relative position (in this example, a position advancing downward by one line and leftward by one pixel) from the pixel processed in the preceding cycle. Since there are no pixels at a position one pixel away leftward from a pixel 531 and at a position two pixels away leftward from a pixel 541, the image processing unit 111 waits at the processing timings of these pixels.

**[0061]** The image processing unit that has processed the pixels in the four data trains processes a processable pixel in the first data train next, and further repeats sequentially processing pixels in the four data trains in the second direction. In FIG. 5, 5b shows pixels to be processed by the image processing units **110** to **113** in the cycles C1 to C7 in this arrangement. In the cycles C1 to C6, each image processing unit sometimes does not perform processing because a processing target pixel as the target of the processing does not exist. In this case, the image processing unit may not propagate an error. From the cycle C7, each image processing unit has a processing target pixel as the target of the processing, and four pixels simultaneously become the processing target pixels.

[0062] According to the arrangement of this embodiment, the pixels as the targets of simultaneous parallel processing by the plurality of image processing units do not exist on the same line. In addition, a plurality of pixels that appear as the result of simultaneously processing a plurality of pixels do not exist on the same line because they are located at predetermined relative positions in the second direction from the plurality of pixels. The processable pixels that simultaneously appear exist in different height directions because of the dependence shown in the reference range. Additionally, when the reference range shown in FIG. 3 is used, the processable pixels that simultaneously appear are located at different positions in the horizontal direction and also located at different positions in the oblique direction (the direction advancing downward by one line and leftward by one pixel). This is because each image processing unit performs periodical scanning in the second direction to process a plurality of pixels whose positions in the vertical direction, in the horizontal direction, and in the oblique direction are different from each other and then process a processable pixel that appears at a predetermined relative position in the second direction. Because of this arrangement, the plurality of image processing units 110 to 113 can simultaneously process one pixel each.

[0063] In addition, after the (for example, M) pixels existing in the (for example, M) data trains are processed in the second direction, the processing unit processes the processable pixel existing in the first data train next. By such scanning, the plurality of different image processing units 110 to 113 that are sequentially arranged correspond to the plurality of pixels that continue in the first direction, respectively, and perform processing of corresponding pixels. Hence, loop processing is performed in which a pixel continuing in the first direction from the pixel processed by the final image processing unit 113 is processed by the first image processing unit 110. With this arrangement, even if the length of one data train changes, or even if the number of data trains included in the band area changes, the dependence of the image processing units that perform the processing does not change. That is, when one image processing unit performs processing of one pixel, the image processing unit that has processed the reference pixel for this pixel is already determined. For this reason, this pixel can be processed by acquiring a quantization error or a diffusing error from the connected specific image processing unit. As described above, since the connection relationship between the image processing units is not switched during the processing, parallel processing can be performed using the same arrangement.

[0064] A method of supplying pixel data to the image processing units 110 to 113 by the image supply unit 101 will be described next. FIG. 2 shows band areas 230 and 1430 that are the targets of processing. In the band areas 230 and 1430, the processing cycles to process processing target pixels are indicated by numerical values. In addition, the image processing units that are the pixel data supply destinations are shown as background patterns.

[0065] The image supply unit 101 includes a line delay circuit 800 and a module delay circuit 900. The line delay circuit 800 will be described first with reference to FIG. 8. In this processing example, the line delay circuit 800 includes buffers 841 to 862. Input data trains 801 to 804 are included in the band area 230. The line delay circuit 800 sequentially acquires pixel data of a predetermined number of pixels from the input data trains 801 to 804. In this processing example, the line delay circuit 800 acquires pixel data of four pixels in one cycle. Here, the number of pixels corresponding to the pixel data acquired in one cycle is the same as the number of parallel processes and is four. That is, the line delay circuit 800 repeats processing of sequentially acquiring pixel data of four pixels from each of the input data trains 801 to 804 and further sequentially acquiring unacquired pixel data of four pixels from each of the input data trains 801 to 804.

[0066] The image supply unit 101 then transfers the acquired pixel data to the module delay circuit 900. Here, the line delay circuit 800 adds a line delay such that a delay corresponding to one pixel is added to the data train adjacent on the lower side as compared to the upper data train, and then transfers the pixel data to the module delay circuit 900. That is, in a given cycle, pixel data of a predetermined number of pixels continuing rightward from the first horizontal position of the upper line are output from the line delay circuit 800. In the next cycle, pixel data of a predetermined number of pixels which continue rightward from the second horizontal position of the adjacent lower line, which is located on the left side of the first horizontal position, are output from the line delay circuit 800. Thus transferring pixel data of an adjacent line such that the second horizontal position is located on the left side of the first horizontal position will be referred to as adding a line delay here.

[0067] A detailed example of the processing will be described below. No line delay is inserted into the first input data train 801. In a cycle CO, the line delay circuit 800 acquires pixel data 811 of four pixels from the input data train 801 and stores the pixel data in the buffers 841 to 844. Here, the pixel data of the pixels included in the acquired pixel data 811 are stored in descending order such that the pixel data of a pixel on the left side is stored in a front buffer. For example, of the pixel data 811, the pixel data of the leftmost pixel is stored in the buffer 844, and the pixel data of the rightmost pixel is stored in the buffer 841. A shift operation is performed for the data included in the buffers in the line delay circuit 800, as will be described later. A buffer located in the shift direction will be referred to as a front buffer here. In the cycle C1, the pixel data of the four pixels stored in the buffers 841 to 844 are output as pixel data 831 to the module delay circuit 900.

**[0068]** Processing of the input data train **802** will be described next. A line delay corresponding to one pixel with respect to the input data train **801** is inserted into the input data train **802**. In the cycle C1, the line delay circuit **800**

acquires pixel data **812** of four pixels from the input data train **802** and stores the pixel data in the buffers **845** to **848** in descending order. In the cycle C2, the pixel data of the four pixels stored in the buffers **846** to **849** are output as pixel data **832** to the module delay circuit **900**. The buffer **845** is formed by buffers of four stages. The buffer **845** holds the stored pixel data until before the cycle C5 in which next pixel data **816** are acquired. Then, when the pixel data **816** of the next four pixels are stored in the buffers **845** to **848** in the cycle C5, the pixel data in the buffer **845** is stored in the buffer **849**. In other words, the pixel data in the buffer **845** is shifted to the buffer **849**. In the next cycle C6, the pixel data of the four pixels stored in the buffers **846** to **849** are output as the pixel data **832** to the module delay circuit **900**.

[0069] Processing of the input data train 803 is the same as the processing of the input data train 802 except that a line delay corresponding to one pixel with respect to the input data train 802 is inserted into the input data train 803. That is, in the cycle C2, the line delay circuit 800 acquires pixel data 813 from the input data train 803 and stores the pixel data in the buffers 850 to 853. In the cycle C3, pixel data 833 stored in the buffers 852 to 855 are output to the module delay circuit 900. Additionally, when pixel data 817 are stored in the buffers 850 to 853 in the cycle C6, the pixel data in the buffers 850 and 851 are shifted to the buffers 854 and 855 and stored. In the cycle C7, the pixel data 833 are similarly output to the module delay circuit 900.

[0070] Processing of the input data train 804 is the same as the processing of the input data train 803 except that a line delay corresponding to one pixel with respect to the input data train 803 is inserted into the input data train 804. That is, in the cycle C3, pixel data 814 from the input data train 804 are stored in the buffers 856 to 859. In the cycle C4, pixel data 834 stored in the buffers 859 to 862 are output to the module delay circuit 900. When pixel data 818 are stored in the buffers 856 to 859 in the cycle C7, the pixel data in the buffers 856 to 858 are shifted to the buffers 860 and 862 and stored. In the cycle C8, the pixel data 834 are output to the module delay circuit 900.

[0071] In this processing example, the line delay is one pixel per line. This reflects the relative positions of the first pixel and the second pixel in the second direction. That is, one image processing unit sequentially processes the first pixel of the first pixel line and the second pixel of the second pixel line located on the lower side of the first pixel line. Here, since the column position of the second pixel is located one pixel away leftward from the first pixel, a line delay corresponding to one pixel is inserted into the input data train from the second pixel line such that the second pixel data is processed in the cycle next to the cycle in which the first pixel data is processed. On the other hand, depending on the contents of the image processing to be performed, the line delay may be increased to relax the timing restriction. On the other hand, when the line delay is increased, the period (number of cycles) to hold the processing result (for example, a quantization error or a diffusing error) of a reference pixel becomes long. This may lead to an increase in the number of error buffers necessary in the circuit.

**[0072]** The module delay circuit **900** will be described next with reference to FIG. **9**. As is apparent from the above explanation, the pixel data of four pixels continuing in the first direction are input to the module delay circuit **900** in one cycle. The module delay circuit **900** transfers the pixel

data of the four pixels to the image processing units **110** to **113**, respectively. At this time, as the image processing units **110** to **113** sequentially perform the processing, the module delay circuit **900** performs the transfer while adding a module delay. In this processing example, the module delay is one cycle. That is, when the pixel data of four pixels are input, the module delay circuit **900** transfers the first pixel data to the image processing unit **110** in the same cycle, and transfers the second pixel data to the image processing unit **111** in the next cycle. In addition, the module delay circuit **900** transfers the third pixel data to the image processing unit **112** in the following cycle, and transfers the fourth pixel data to the image processing unit **113** in the next cycle. To add the module delay in this way, the module delay circuit **900** includes buffers **911** to **916**.

[0073] Processing of the module delay circuit 900 will be described in more detail. In the cycle C1, the pixel data 831 of the four pixels are input from the line delay circuit 800. The pixel data stored in the buffers 841 to 843 are stored in the buffers 913 to 911, respectively. The buffers 911 to 913 store the pixel data to be transferred to the image processing units 111 to 113, respectively. The pixel data of a pixel on the left side is thus transferred to an image processing unit on the rear side. In addition, the pixel data stored in the buffer 844 is not stored in a buffer in the module delay circuit 900 but output to the image processing unit 110 in the cycle C1.

[0074] In the cycle C2, similarly, the pixel data 832 of the four pixels are input from the line delay circuit 800. The pixel data stored in the buffers 846 to 848 are stored in the buffers 913 to 911, respectively. The pixel data stored in the buffer 849 is not stored in a buffer in the module delay circuit 900 but output to the image processing unit 110 in the cycle C2. The pixel data stored in the buffer 911 is output to the image processing unit 111. In addition, the pixel data stored in the buffers 912 and 913 are stored in the buffers 914 and 915, respectively.

[0075] In the cycle C3 as well, the pixel data 833 are input from the line delay circuit 800. The pixel data stored in the buffer 855 is output to the image processing unit 110, and the pixel data stored in the buffers 852 to 854 are stored in the buffers 913 to 911. The pixel data stored in the buffers 911 and 914 are output to the image processing units 111 and 112, respectively. The pixel data stored in the buffers 912, 913, and 915 are transferred to the buffers 914, 915, and 916, respectively.

[0076] In the cycle C4 as well, the pixel data 834 are input from the line delay circuit 800. The pixel data stored in the buffer 862 is output to the image processing unit 110, and the pixel data stored in the buffers 859 to 861 are stored in the buffers 913 to 911. The pixel data stored in the buffers 911, 914, and 916 are output to the image processing units 111, 112, and 113, respectively. The pixel data stored in the buffers 912, 913, and 915 are transferred to the buffers 914, 915, and 916, respectively.

**[0077]** The same operation as described above is performed from the cycle C5 as well. In this way, the image supply unit **101** supplies the pixel data of pixels that continue in the first direction as many as the number of parallel processes to the image processing units **110** to **113** in every other cycle. With this operation, the image supply unit **101** can supply the pixel data in the band area **230** to the image processing units **110** to **113** as shown in FIG. **2** in a predetermined order.

**[0078]** The image output unit **103** eliminates the line delay and the module delay of the pixel data obtained by the processing of the image processing units **110** to **113** and outputs the pixel data to a memory (a DRAM or the like). The image output unit **103** gives a delay to the output timing of the pixel data so as to eliminate the line delay and the module delay given by the image supply unit **101**. The following arrangement is merely an example, and any arrangement can be used to eliminate the delay.

[0079] The image output unit 103 includes a module delay elimination circuit 1000 and a line delay elimination circuit 1100. The module delay elimination circuit 1000 will be described with reference to 10a in FIG. 10. The module delay elimination circuit 1000 adds a delay to each of the pixel data of the pixels continuing in the first direction as many as the number of parallel processes. The delay difference added when the module delay circuit 900 supplies the pixel data to the image processing units 110 to 113 is thus eliminated. As a result, the pixel data of the pixels continuing in the first direction as many as the number of parallel processes are transferred from the module delay elimination circuit 1000 to the line delay elimination circuit 1100 at the same timing. For this operation, the module delay elimination circuit 1000 includes buffers 1011 to 1016, as shown in 10a. Of the pixel data of the pixels continuing in the first direction as many as the number of parallel processes, pixel data processed in a preceding cycle is held for a period longer by one cycle than that for pixel data processed in the following cycle and then output.

**[0080]** The pixel data of four pixels are input to the module delay elimination circuit **1000** in one cycle. That is, the pixel data of one pixel is input from each of the image processing units **110** to **113**. The pixel data input from the image processing unit **110** to the buffer **1011** is output to the line delay elimination circuit **1100** after three cycles via the buffers **1014** and **1016**. Similarly, the pixel data input from the image processing unit **111** to the buffer **1012** is output to the line delay elimination circuit **1100** after two cycles via the buffer **1015**. The pixel data input from the image processing unit **112** to the buffer **1013** is output to the line delay elimination circuit **1100** after one cycle. The pixel data input from the image processing unit **113** to the module delay elimination circuit **1000** is output to the line delay elimination circuit **1100** after one cycle. The pixel data input from the image processing unit **113** to the module delay elimination circuit **1100** is output to the line delay elimination circuit **1100** after one cycle. The pixel data input from the image processing unit **113** to the module delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line delay elimination circuit **1100** is output to the line dela

[0081] In FIG. 10, 10b shows pixel data 1021 to 1028 output from the module delay elimination circuit 1000 to the line delay elimination circuit 1100 in the cycles C1 to C8. After the pixel data 831 of the four pixels transferred to the module delay circuit 900 in the cycle C1 are processed, the delay difference is thus eliminated in the cycle C4, and the pixel data are output as the pixel data 1024 from the module delay elimination circuit 1000. Each of the pixel data 1021 to 1023 represents a delay circuit 900 and the module delay elimination circuit 1000. Processing by the line delay elimination circuit 1100 for these is unnecessary.

**[0082]** The line delay elimination circuit **1100** will be described with reference to FIG. **11**. The line delay elimination circuit **1100** eliminates the line delay difference between the pixel data input from the module delay elimination circuit **1000**. That is, the line delay elimination circuit **1100** adds a line delay such that a delay corresponding to one pixel is added to the data train adjacent on the upper side as

compared to the lower data train, and then outputs the pixel data. A detailed arrangement for this can be the same as that of the line delay circuit **800**.

[0083] That is, the line delay elimination circuit 1100 includes buffers 1141 to 1162. The pixel data of four pixels are input from the module delay elimination circuit 1000 to the line delay elimination circuit 1100 in one cycle, as shown in 10b. The pixel data 1024 are input to the buffers 1144 to 1141 in descending order. For example, of the pixel data 1024, the pixel data of the leftmost pixel is stored in the buffer 1141. After a line delay corresponding to three pixels is added to the input pixel data, the pixel data are output to a memory (a DRAM or the like). That is, the pixel data input to the buffer 1144 is output in the next cycle. In addition, the pixel data input to the buffer 1145 four cycles after the input and output five cycles after the input.

[0084] Similarly, the pixel data 1025 are input to the buffers 1151 to 1148 in descending order. After a line delay corresponding to two pixels is added, the pixel data are output to the memory. The pixel data 1026 are input to the buffers 1157 to 1154 in descending order. After a line delay corresponding to one pixel is added, the pixel data are output to the memory. The pixel data 1027 are input to the buffers 1159 to 1162 in descending order and output to the memory without adding any line delay.

**[0085]** Processing up to the pixel data **1027** has been described above. From then on, delays corresponding to three pixels, two pixels, one pixel, and zero pixels are sequentially added to the pixel data input to the line delay elimination circuit **1100**, and the pixel data are output from the line delay elimination circuit **1100**. Since the pixel data arranged in descending order are output from the line delay elimination circuit **1100** to the memory, the pixel data are converted to the ascending order and then stored in the memory. With the above-described processing, in the cycles C5 to C8, pixel data that is the processing result of the first pixel in each of the input data trains **801** to **804** is output. In the cycles C9 to C12, pixel data that are the processing results of the second to fifth pixels in each of the input data trains **801** to **804** are output.

[0086] In this way, the pixel data that are the processing results for the pixels in the band area 230 are accumulated in the image output unit 103, and as a result, the error diffusion result of the band area 230 is obtained. As described above, the image output unit 103 includes the module delay elimination circuit 1000 and the line delay elimination circuit 1100. The image output unit 103 adds a delay such that the line delay and the module delay added by the image supply unit 101 are eliminated, and then outputs the pixel data.

**[0087]** (Example of Processing for Band Area with Five Lines)

**[0088]** Error diffusion processing for a band area with five lines read from an input image by the image input unit **100** will be described below as another detailed example of processing. Reference pixels and diffusion coefficients in the error diffusion processing are the same as those shown in FIG. **3**.

**[0089]** The method of determining, for pixel data of each pixel, the image processing units **110** to **113** is the same as in the case of processing for the band area with four lines. In this processing example, an image processing unit pro-

cesses a pixel in the fifth data train, and then processes a processable pixel in the first data train. In FIG. 15, 15a shows the schematic view of this processing order.

**[0090]** The processing order in this example will be described with reference to **15***a*. In the cycle C1, the processable pixel is only a pixel **1511** at the processing start position, and the image processing unit **110** processes the pixel **1511**. Then, a pixel **1512** for which processing of all the reference pixels is completed becomes a processable pixel. The pixel **1512** is located in the main scanning direction from the processed pixel **1511**, and is therefore processed in the cycle C2 by the next image processing unit **111**.

[0091] In the cycle C2, the pixel 1512 is processed by the image processing unit 111, and as a result, pixels 1513 and 1521 change to processable pixels. The pixel 1513 located in the main scanning direction is processed in the cycle C3 by the next image processing unit 112. On the other hand, the pixel 1521 located in the second direction different from the first direction is processed in the cycle C3 by the image processing unit 111 that has completed the processing of the reference pixel in the cycle C2. In this way, the second direction is determined to be the direction from the pixel 1512 to the pixel 1521, that is, the direction advancing downward by one data train and leftward by one pixel.

[0092] The pixel 1521 may be processed by the image processing unit 110 or 113. In this case, however, the image processing unit 110 processes the pixel 1511 in the cycle C1, waits in the cycle C2, and processes the pixel 1521 in the cycle C3. When the image processing unit 111 processes the pixel 1521, the effect of speeding up the processing by parallelization improves. Additionally, when the image processing unit 113 processes the pixel 1521, the diffusing error of the pixel 1511 in the cycle C1 needs to be held up to the cycle C3. Since the error needs to be held in longer cycles, the number of buffers configured to hold the diffusing error in the circuit increases. When the image processing unit 111 processes the pixel 1521, the number of buffers configured to hold the diffusing error in the diffusing error can be decreased.

[0093] From the cycle C4 as well, the image processing units 110 to 113 perform the same processing as described above. 15b shows pixels to be processed by the image processing units 110 to 113 in the cycles C1 to C9 in this arrangement. As in the case in which the number of lines is four, image processing units that do not perform processing exist in the cycles C1 to C8. From the cycle C9, the pixel data of four pixels are simultaneously processed by the image processing units 110 to 113.

**[0094]** In this processing example as well, after the (for example, M) pixels existing in the (for example, M) data trains are processed in the second direction, the image processing unit processes the processable pixel existing in the first data train next. In this processing example as well, since the connection relationship between the image processing units is the same as in the processing for the band area with four lines, the image processing units **110** to **113** having the same circuit arrangement as in the processing for the band area with four lines can be used.

[0095] A method of supplying pixel data to the image processing units 110 to 113 by the image supply unit 101 will be described next. Processing performed when the image input unit 100 reads the band area 1430 with five lines shown in FIG. 2 will be described here. FIG. 2 shows processing target pixels (processing cycles to process pro-

cessing target pixels are indicated by numerical values) in the processing cycles and the image processing units as the pixel data supply destinations.

**[0096]** The image supply unit **101** includes a line delay circuit and a module delay circuit. In this processing example, since the number of lines of the band area is five, the line delay circuit can add a line delay corresponding to four pixels at maximum. The arrangement of the line delay circuit is the same as that of the line delay circuit **800** except this point, and a detailed description thereof will be omitted. That is, the line delay circuit directly outputs pixel data from the first data train, and outputs pixel data from the second to fifth data trains after adding a line delay corresponding to one to four pixels.

[0097] The arrangement of the module delay circuit is the same as that in a case in which the number of lines of the band area is four, and a detailed description thereof will be omitted. That is, of the pixel data of four pixels input from the line delay circuit, the first pixel data is immediately input to the image processing unit 110. In addition, the second to fourth pixel data are input to the image processing units 111 to 113 after one or three cycles.

[0098] As described above, the image supply unit 101 can supply pixel data to the image processing units 110 to 113 in the order shown in FIG. 2 by using the line delay circuit and the module delay circuit.

[0099] The image output unit 103 eliminates the line delay and the module delay of the pixel data obtained by the processing of the image processing units 110 to 113 and outputs the pixel data to the memory (for example, a DRAM), as in a case in which the number of lines of the band area is four. The image output unit 103 includes a module delay elimination circuit and a line delay elimination circuit. The arrangement of the module delay elimination circuit is the same as in the case in which the number of lines is four, and a detailed description thereof will be omitted. That is, the module delay elimination circuit outputs the pixel data input from the image processing units 110 to 112 in the same cycle to the line delay elimination circuit after three to one cycle, and also outputs the pixel data input from the image processing unit 113 directly to the line delay elimination circuit. In FIG. 10, 10c shows pixel data 1023 to 1040 output from the module delay elimination circuit to the line delay elimination circuit in the cycles C1 to C10. As in the case in which the number of lines of the band area is four, the delay difference added by the module delay circuit is eliminated, as can be seen.

**[0100]** The arrangement of the line delay elimination circuit is the same as that of the line delay elimination circuit **1100** except that a line delay corresponding to four pixels can be added at maximum because the number of lines of the band area is five, and a detailed description thereof will be omitted. That is, the line delay elimination circuit adds a line delay corresponding to four to zero pixels to each of pixel data **1035** to **1039** (corresponding to the first to fifth data trains, respectively), and outputs the pixel data to the memory (for example, a DRAM). From then on, the processing of inputting the pixel data of four pixels for each data to the line delay circuit and outputting the pixel data to the memory after adding a delay corresponding to four to zero pixels is repeated.

[0101] (Operation in First Embodiment)

**[0102]** An operation in the first embodiment will be described with reference to the flowchart of FIG. **12**. In step

S1200, the image input unit 100 reads out the data of a band area. In step S1201, the image supply unit 101 acquires pixel data of J value from the image input unit 100 by four pixels. The image supply unit 101 then adds line delays and module delays to the acquired pixel data, as described above, and outputs them to the image processing units 110 to 113.

[0103] As already described above, the order of pixel processing by the image processing units 110 to 113 is determined in advance. That is, processing results for N continuous pixels included in the first pixel line of a processing target region are sequentially generated in a predetermined order by the image processing units different from each other. For example, for pixels that continue in the first direction (main scanning direction) as many as the number of parallel processes, the different image processing units 110 to 113 perform processing (quantization processing). In addition, processing results for N continuous pixels included in the first pixel line are generated in continuous processing cycles in a predetermined order by the image processing units different from each other. Note that in the abovedescribed processing example, one image processing unit not only processes only pixels included in one pixel line but processes at least one of pixels included in each of the first to Mth pixel lines.

[0104] Additionally, each of the plurality of image processing units generates a processing result for the first pixel included in the first pixel line and then generates a processing result for the second pixel. The second pixel is a pixel that is included in the second pixel line different from the first pixel line in the processing target region and changes to a processable pixel in accordance with the generation of the processing result for the first pixel. For example, for a processable pixel that appears in the second direction from the processing target pixel as a result of processing performed for the processing target pixel by an image processing unit, the same image processing unit performs processing. One image processing unit repeats processing of a pixel located in the second direction. When processing of a pixel in the Mth pixel line is performed, the image processing unit then performs processing of a processable pixel existing in the first pixel line. Here, the processing target region includes M pixel lines.

**[0105]** In addition, the second pixel can be a pixel located at a predetermined relative position in the second direction from the first pixel. That is, the relative positions of the first pixel and the second pixel depend on the positions of reference pixels and can be the same independently of the position of the first pixel. For example, if the position of the first pixel is on the ith row and jth column, the position of the second pixel can be on the (i+1)th row and (j-a)th column. Here, a is an arbitrary integer (a positive integer, a negative integer, or zero) determined by the positions of the reference pixels. For example, a=1 in a case in which the reference pixels shown in FIG. **3** are used.

[0106] On the other hand, when the processing target region includes M (M>N) pixel lines, the N image processing units start processing of the Mth pixel line before the processing of the first pixel line is completed. That is, in this embodiment, processing of the band area is completed from left to right.

**[0107]** The image supply unit **101** supplies the pixel data to the plurality of image processing units such that the processing as described above can be implemented. For example, the image supply unit **101** can sequentially supply

the pixel data of N continuous processing target pixels included in the first pixel line to the N image processing units in a predetermined order. In addition, the image supply unit **101** can supply the pixel data of the second pixel to the image processing unit that has completed processing of the first pixel. Furthermore, to one image processing unit, the image supply unit **101** can sequentially supply the pixel data of a processing target pixel in the first pixel line to the pixel data of a processing target pixel in the Mth pixel line and then supply the pixel data of a processing target pixel in the first pixel line.

[0108] In step S1202, the image processing units 110 to 113 perform error diffusion processing. Additionally, in step S1203, the image processing units 110 to 113 perform propagation of diffusing errors. In this embodiment, when the image processing unit 110 processes the processing target pixel, the image processing units that have processed the reference pixels are fixed. That is, as indicated by 13a in FIG. 13, the pixel on the upper left side of the processing target pixel is processed by the image processing unit 112, the pixels on the upper and left sides of the processing target pixel are processed by the image processing unit 113, and the pixel on the upper right side of the processing target pixel is processed by the image processing unit 110. This is because the processing order of the pixels continuing in the first direction and the processing order of the pixels continuing in the second direction by the image processing units 110 to 113 are determined in advance. That is, this is because four pixels continuing in the first direction (main scanning direction) are processed by the image processing units 110 to 113, respectively, and pixels continuing in the second direction (left downward direction) are processed by the same image processing unit. This also applies to a case in which the image processing units 111 to 113 process the processing target pixels, as indicated by 13b to 13d in FIG. 13. Additionally, this relationship is constant independently of the number of lines (for example, irrespective of whether the number of lines is four or five).

**[0109]** As described above, in this embodiment, the relative positions of the image processing unit that processes the processing target pixel and the image processing units that have processed the reference pixels (that is, propagate errors) are fixed. Hence, when the processing units are connected so as to propagate the diffusing errors from the image processing units that have processed the reference pixels to the image processing unit that processes the processing target pixel, error propagation processing can be performed. This connection relationship need not be changed in the course of processing, and also need not be changed even when the size (for example, height or length) of the processing target region is changed. In FIG. **13**, **13***e* shows an example of the connection relationship of the image processing units **110** to **113**.

**[0110]** Note that the processing results (for example, the quantization errors or diffusing errors) to be referred to may be held by the image processing unit that processes the processing target pixel or the image processing units that have processed the reference pixels. In any case, the processing results to be referred to can be transferred at predetermined timings from the image processing units that have processed the reference pixels to the image processing units that processes the processing target pixel. In one embodiment, the first image processing unit acquires the processing result for one of the plurality of reference pixels

from the memory (for example, the error memory **403**) of the first image processing unit, which stores the processing result of the first image processing unit. For example, when the first image processing unit processes the second pixel next to the first pixel, as described above, the processing result of the first pixel that is the reference pixel is stored in the memory of the first image processing unit. Additionally, the first image processing unit can acquire the processing result for another one of the plurality of reference pixels from the second image processing unit different from the first image processing unit. As described above, the image processing unit that is the acquisition source of the processing result is determined in advance.

**[0111]** Note that the image processing unit that processes the processing target pixel and the image processing units that have processed the reference pixels need not be directly connected. For example, in the example shown in 13*e*, the image processing unit 111 may receive the processing result (for example, the quantization error or the diffusing error) of the image processing unit 113 via the image processing unit 110. That is, in one embodiment, the plurality of image processing units may be connected in series in a ring shape, and each image processing units.

[0112] In step S1204, the image processing units 110 to 113 output pixel data of I value. In step S1205, the image output unit 103 eliminates the delay difference between the output pixel data of I value and records the pixel data in the memory. In step S1206, the image supply unit 101 determines whether the processing is completed for all the pixels. If the processing is not performed for all the pixels, the processing is completed for all the pixels, the processing is completed for all the pixels. If the processing is completed for all the pixels. If the processing is completed for all the pixels. If the processing is completed for all the pixels. If the processing is completed for all the pixels. If the processing is performed for all the pixels, the processing is performed for all the pixels, the processing shown in FIG. 12 ends.

**[0113]** In the above description, if the number of lines of the band area changes, the line delay circuit and the line delay elimination circuit of different arrangements are used. However, the line delay circuit and the line delay elimination circuit having the same arrangements may be used independently of the number of lines. For example, processing for a case in which the number of lines is four can be performed using the line delay circuit and the line delay elimination circuit for the above-described case in which the number of lines is five. In this case, the portions configured to add a line delay corresponding to four pixels in the line delay circuit and the line delay circuit are not used.

[0114] In addition, the image input unit 100, the image supply unit 101, the image output unit 103, and a path control unit 2002 (to be described later) may be hardware circuit but may be implemented by software. That is, at least some of these processing units may be implemented by a computer. FIG. 20 is a view showing the basic arrangement of a computer capable of implementing these processing units. Referring to FIG. 20, a processor 2110 is, for example, a CPU and controls the operation of the entire computer. A memory 2120 is, for example, a RAM and temporarily stores programs and data. A computer-readable storage medium 2130 is, for example, a hard disk or a CD-ROM and stores programs and data for a long time. In this embodiment, a program that is stored in the storage medium 2130 and implements the functions of the units is loaded into the memory 2120. Then, the processor 2110 operates in accordance with the program on the memory 2120, thereby implementing the functions of the units. Referring to FIG. **20**, an input interface **2140** is an interface configured to acquire information from an external device. In addition, an output interface **2150** is an interface configured to output information to an external device. A bus **2160** connects the above-described units to enable data exchange.

[0115] As described above, according to this embodiment, even in a case in which the number of lines or the length of the band area changes, the pixels to be processed by the image processing units need not be switched. Additionally, even in the case in which the number of lines or the length of the band area changes, the image processing units need only perform the same processing. Hence, the image processing units having the same arrangement can be used. For this reason, irrespective of the number of lines or the length of the band area, parallel processing can be performed using the image processing units of the same arrangement. In particular, in this embodiment, each of the plurality of image processing units can acquire a processing result for a reference pixel from the same image processing unit independently of the processing target pixel and independently of the number of lines of the band area. It is therefore possible to perform parallel image processing without changing the processing of each image processing unit and the connection between the image processing units even if the number of lines of the band area changes.

#### Second Embodiment

**[0116]** In the second embodiment, an arrangement for switching the number of parallel processes in accordance with the number of colors of an input image will be described. In the second embodiment as well, a case in which an image processing apparatus performs error diffusion processing of converting a J-value image into an I-value image (i < J) will be described. In the following description as well, reference pixels and diffusion coefficients shown in FIG. **3** are used.

[0117] The image processing apparatus according to this embodiment includes four image processing units 110 to 113, as in the first embodiment. In this embodiment, the operation mode is switched in accordance with the number of colors of an input image. For example, the image processing apparatus can operate in a first operation mode in which N image processing units parallelly perform image processing for one color of an input image. As one example, if the number of colors of an input image is one, the four image processing units can parallelly perform processing. In addition, the image processing apparatus can operate in a second operation mode. In the second operation mode, a first group of the N image processing unit parallelly performs image processing for the first color of an input image, and a second group of the N image processing units parallelly performs image processing for the second color of the input image. As one example, if the number of colors of an input image is two, two image processing units can parallelly process the pixel data of each color. In addition, if the number of colors of an input image is one, one image processing unit can process the pixel data of each color.

**[0118]** In one embodiment, the N image processing units are classified into L groups in accordance with the number L of colors of an input image. Here, the groups may include the same number of image processing units, and the number may be N/L. The image processing units included in each group can be connected such that the image processing units

included in each group can transfer processing results. Each image processing unit can transfer a processing result via this connection. The data transfer path may be controlled by the path control unit **2002** such that such a connection is possible, as will be described later.

[0119] FIG. 7 is a block diagram showing an example of the arrangement of an image processing apparatus 195 according to this embodiment. The arrangements of an image input unit 100, an image supply unit 101, the image processing units 110 to 113, and an image output unit 103 are the same as in the first embodiment, and different points will be described below. The image processing apparatus 195 further includes a data transfer path 2001. The image processing units 110 to 113 can propagate diffusing errors via the data transfer path 2001.

**[0120]** (When Number of Colors of Input Image is Two) **[0121]** An arrangement in which the number of colors of an input image is two, and two image processing units parallelly process the pixel data of each color will be described first. A case in which each pixel of the input image has cyan pixel data and magenta pixel data will be described below. Each of the cyan pixel data and the magenta pixel data is data of J value.

**[0122]** The image input unit **100** reads out a band area for each color of the input image. For example, as indicated by **16***a* in FIG. **16**, the image input unit **100** can read out a band area **2210** of cyan and a band area **2200** of magenta.

[0123] The image supply unit 101 includes a line delay circuit 2300 and a module delay circuit 900. FIG. 19 shows an example of the arrangement of the line delay circuit 2300 in a case in which the number of colors of the input image is two. The line delay circuit 2300 includes buffers 2341 to 2368.

[0124] As indicated by 16b in FIG. 16, the line delay circuit 2300 acquires the pixel data of two cyan pixels and two magenta pixels. In the first cycle, the line delay circuit 2300 can acquire the pixel data of two pixels at the left end of the first data train, represented by hatching in 16a. In the next cycle, the line delay circuit 2300 can acquire the pixel data of the second data train. When the pixel data in the final data train are acquired, the line delay circuit 2300 can repeat the operation of acquiring unacquired pixel data in the first data train again. This acquisition processing is the same as that or the line delay circuit 800 except that the pixel data of not four but two continuous pixels are acquired.