# (10) **DE 10 2023 107 574 A1** 2023.11.16

(12)

# Offenlegungsschrift

(21) Aktenzeichen: **10 2023 107 574.8** (22) Anmeldetag: **27.03.2023**

(43) Offenlegungstag: **16.11.2023**

(51) Int Cl.: **H10B 61/00** (2023.01)

H10N 50/80 (2023.01)

(30) Unionspriorität:

63/341,840 13.05.2022 US 17/880,186 03.08.2022 US

(71) Anmelder:

Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu, TW

(74) Vertreter:

BOEHMERT & BOEHMERT Anwaltspartnerschaft mbB - Patentanwälte Rechtsanwälte, 28209 Bremen, DE

(72) Erfinder:

Wang, Yu-Jen, Hsinchu, TW; Huang, Sheng-Huang, Hsinchu, TW; Chuang, Harry-Hak-Lay, Hsinchu, TW; Wang, Hung Cho, Hsinchu, TW; Wang, Ching-Huang, Hsinchu, TW; Huang, Kuo-Feng, Hsinchu, TW

Prüfungsantrag gemäß § 44 PatG ist gestellt.

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen.

(54) Bezeichnung: VERFAHREN ZUM BILDEN VERSCHIEDENER ARTEN VON SPEICHERVORRICHTUNGEN

(57) Zusammenfassung: Eine Halbleitervorrichtung gemäß der vorliegenden Offenbarung weist ein erstes leitfähiges Strukturelement und ein zweites leitfähiges Strukturelement in einer ersten dielektrischen Schicht, eine Pufferschicht über der ersten dielektrischen Schicht, eine zweite dielektrische Schicht über der Pufferschicht, eine erste Bodendurchkontaktierung, die sich durch die Pufferschicht und die zweite dielektrische Schicht erstreckt, eine zweite Bodendurchkontaktierung, die sich durch die Pufferschicht und die zweite dielektrische Schicht erstreckt, eine erste Bodenelektrode, die auf der ersten Bodendurchkontaktierung angeordnet ist, eine zweite Bodenelektrode, die auf der zweiten Bodendurchkontaktierung angeordnet ist, einen ersten magnetischen Tunnelübergangsstapel (MTJ-Stapel) über der ersten Bodenelektrode und einen zweiten MTJ-Stapel über der zweiten Bodenelektrode auf. Der erste MTJ-Stapel und der zweite MTJ-Stapel weisen eine selbe Dicke auf. Der erste MTJ-Stapel weist eine erste Breite auf und der zweite MTJ-Stapel weist eine zweite Breite auf, die größer als die erste Breite ist.

### Beschreibung

#### **PRIORITÄTSDATEN**

**[0001]** Diese Anmeldung beansprucht die Priorität der vorläufigen US-Patentanmeldung Nr. 63/341,840, eingereicht am 13.Mai 2022, die durch Bezugnahme in die vorliegende Anmeldung aufgenommen wird.

#### HINTERGRUND

[0002] Die Industrie integrierter IC (Integrated Circuit)-Halbleiterschaltungen hat ein exponentielles Wachstum erfahren. Technologische Fortschritte IC-Materialien und -Design haben Generationen von ICs hervorgebracht, wobei jede Generation kleinere und komplexere Schaltungen als die vorhergehende Generation aufweist. Im Laufe der IC-Entwicklung hat die Funktionsdichte (d.h. die Anzahl miteinander verbundener Vorrichtungen pro Chipfläche) im Allgemeinen zugenommen, während die Geometriegröße (d.h. die kleinste Komponente (oder Leitung), die unter Verwendung eines Fertigungsprozesses erzeugt werden kann) abgenommen hat. Dieser Abwärtsskalierungsprozess stellt im Allgemeinen Vorteile durch Erhöhen der Produktionseffizienz und Senken damit verbundener Kosten bereit. Ein solches Abwärtsskalieren hat auch die Komplexität einer Bearbeitung und Herstellung von ICs erhöht.

[0003] Heutige elektronische Vorrichtungen beinhalten flüchtige oder nicht flüchtige elektronische Speicher zum Speichern von Daten. Ein flüchtiger Speicher speichert Daten, wenn er eingeschaltet ist, während ein nicht flüchtiger Speicher gespeicherte Daten beibehalten kann, wenn Strom entfernt wird. Ein magnetoresistiver Direktzugriffspeicher (MRAM, Magneto-resistive Random Access Memory) ist ein vielversprechender Kandidat für eine nächste Generation nicht flüchtiger Speichertechnologie. MRAM-Vorrichtungen können unterschiedlich konfiguriert sein, um unterschiedliche Designanforderungen zu erfüllen. Die unterschiedlichen Konfigurationen können Herausforderungen darstellen, wenn verschiedene MRAM-Vorrichtungen in einem einzelnen Chip integriert und gefertigt werden. Während bestehende MRAM-Integrationsschemata daher im Allgemeinen für ihren beabsichtigten Zweck angemessen sind, sind sie nicht in allen Aspekten zufriedenstellend.

### KURZE BESCHREIBUNG DER ZEICHNUNGEN

[0004] Aspekte der vorliegenden Offenbarung lassen sich am besten anhand der folgenden detaillierten Beschreibung in Verbindung mit den beiliegenden Zeichnungen verstehen. Es ist zu beachten, dass gemäß der branchenüblichen Praxis verschiedene Merkmale nicht maßstabsgetreu dargestellt sind und nur der Veranschaulichung dienen. Tat-

sächlich können die Abmessungen der verschiedenen Merkmale zugunsten einer klaren Erläuterung willkürlich vergrößert oder verkleinert sein.

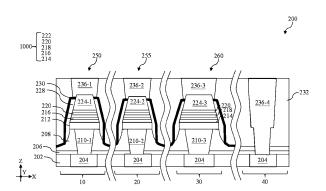

- **Fig.** 1 veranschaulicht ein Ablaufdiagramm eines Verfahrens zum Bilden einer Halbleiterstruktur mit verschiedenen Speicherstrukturen nach einem oder mehreren Aspekten der vorliegenden Offenbarung.

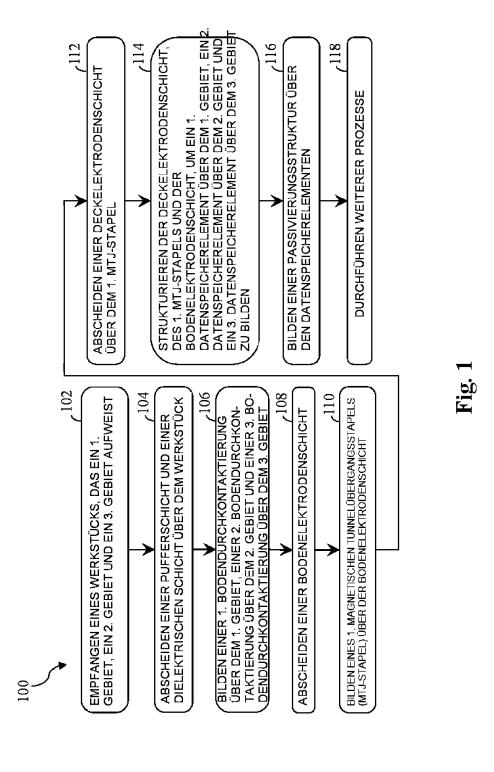

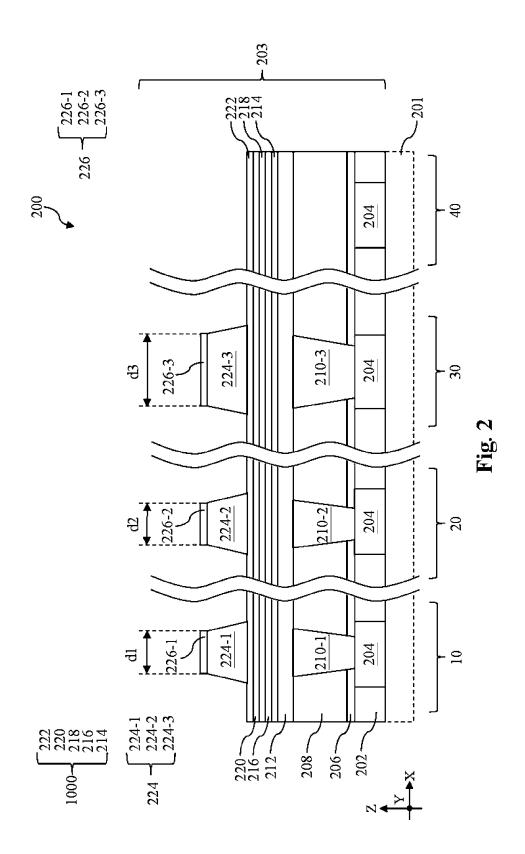

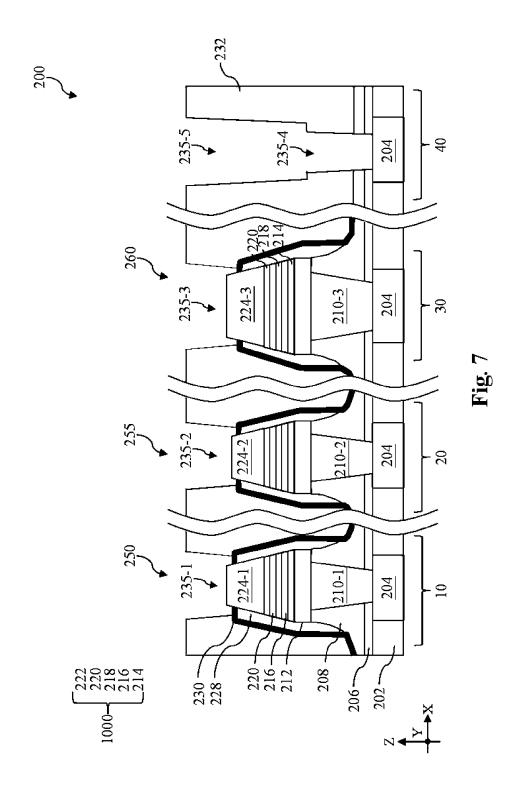

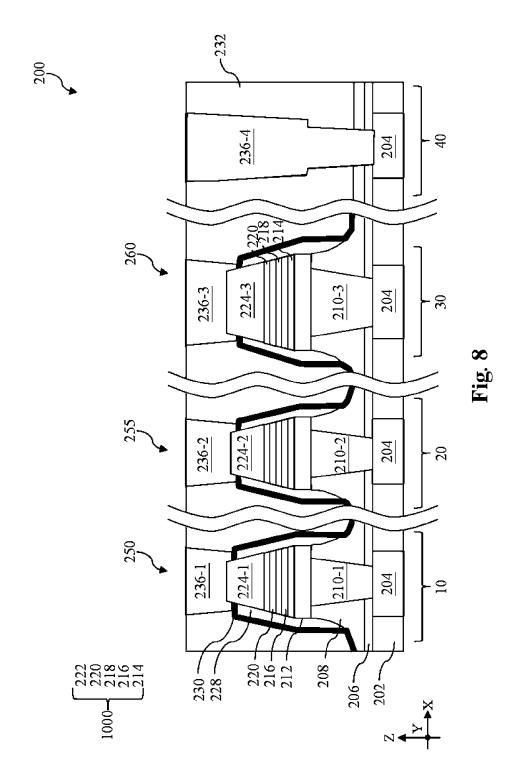

- **Fig.** 2-8 veranschaulichen fragmentarische Querschnittsansichten eines Werkstücks während eines Fertigungsprozesses gemäß dem Verfahren von **Fig.** 1 nach einem oder mehreren Aspekten der vorliegenden Offenbarung.

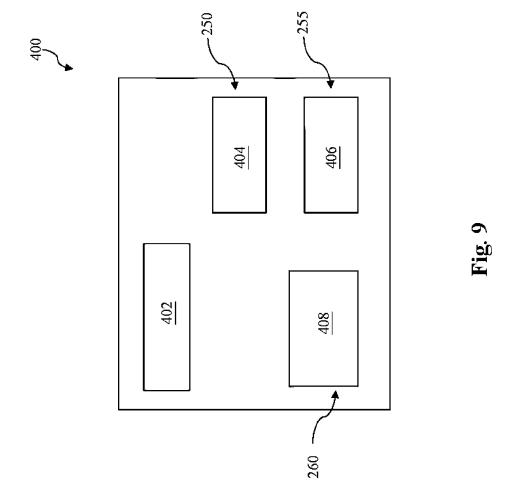

- **Fig.** 9 ist eine schematische Darstellung verschiedener Speicherstrukturen, die in verschiedenen Gebieten einer einzelnen IC-Vorrichtung nach einem oder mehreren Aspekten der vorliegenden Offenbarung implementiert sind.

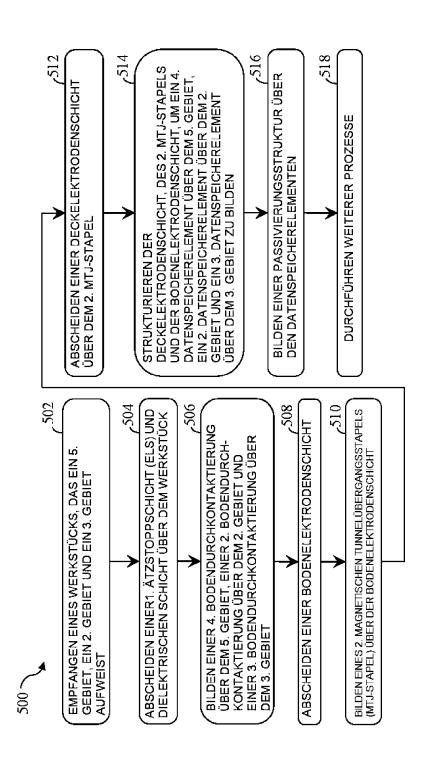

- **Fig.** 10 veranschaulicht ein Ablaufdiagramm eines Verfahrens zum Bilden einer Halbleiterstruktur mit verschiedenen Speicherstrukturen nach einem oder mehreren Aspekten der vorliegenden Offenbarung.

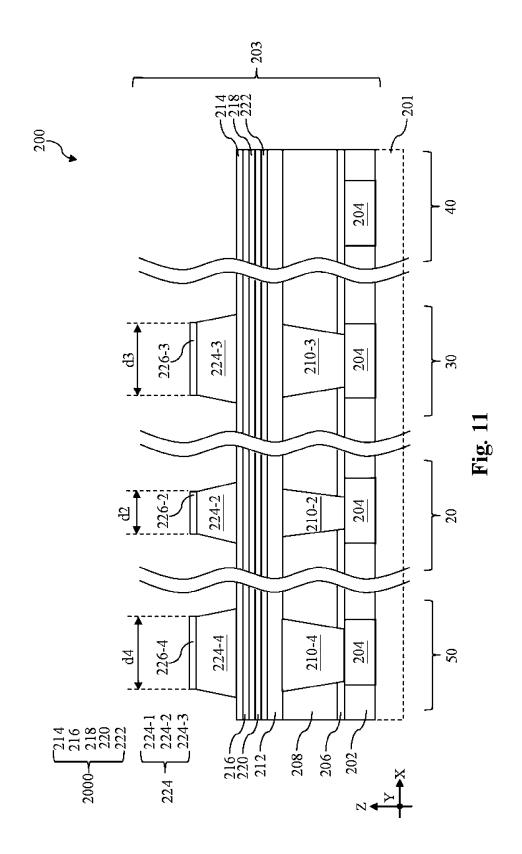

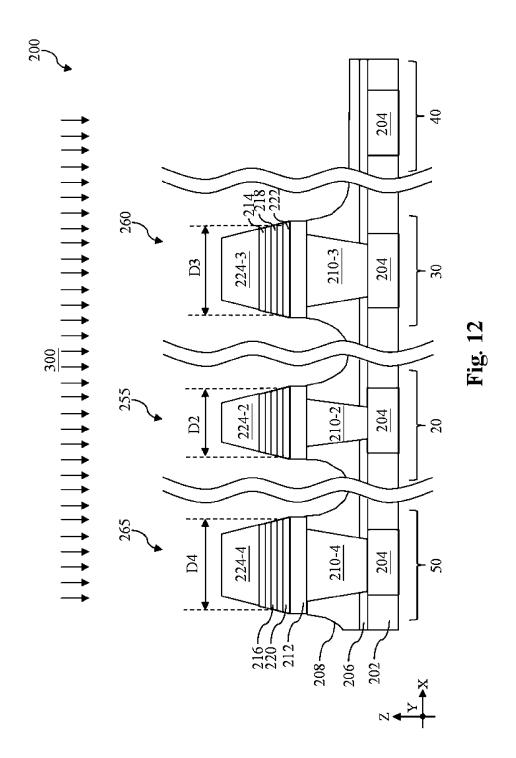

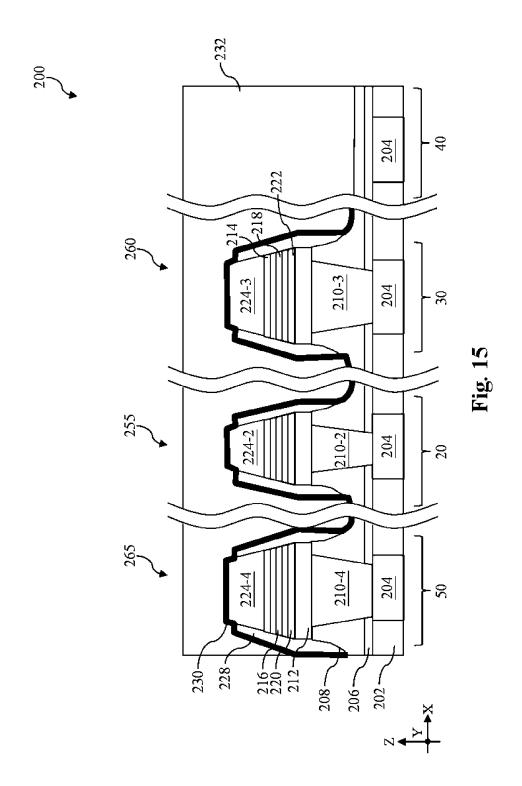

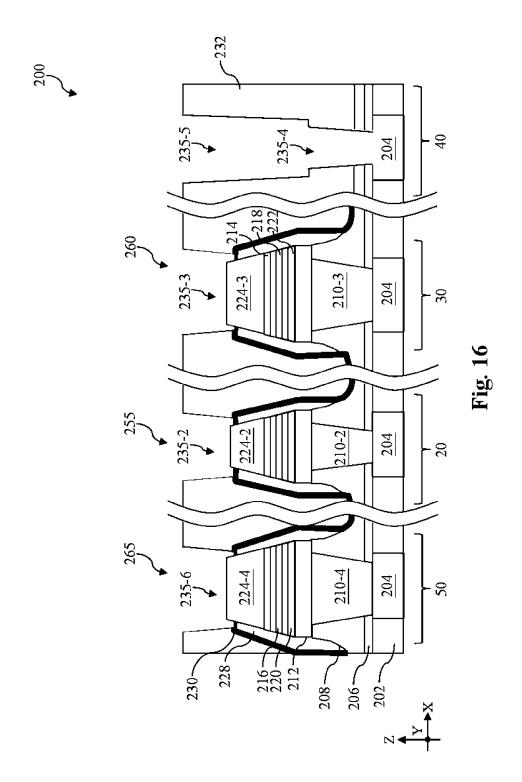

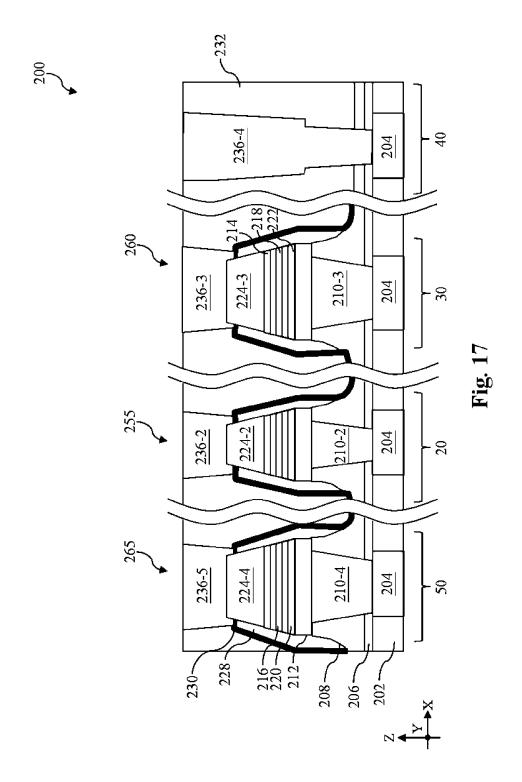

- **Fig.** 11-17 veranschaulichen fragmentarische Querschnittsansichten eines Werkstücks während eines Fertigungsprozesses gemäß dem Verfahren von **Fig.** 1 nach einem oder mehreren Aspekten der vorliegenden Offenbarung.

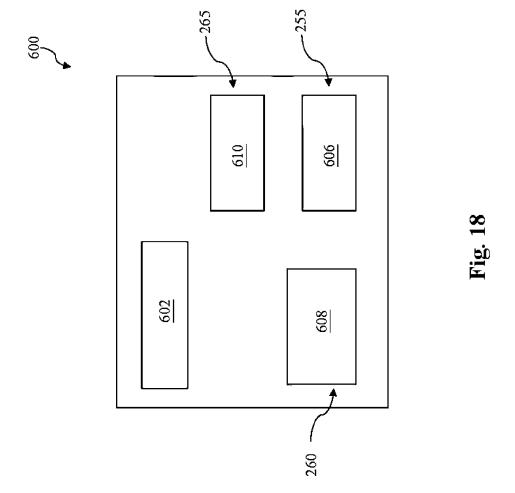

- **Fig.** 18 ist eine schematische Darstellung verschiedener Speicherstrukturen, die in verschiedenen Gebieten einer einzelnen IC-Vorrichtung nach einem oder mehreren Aspekten der vorliegenden Offenbarung implementiert sind.

### AUSFÜHRLICHE BESCHREIBUNG

[0005] Die folgende Offenbarung stellt viele verschiedene Ausführungsformen, oder Beispiele, zum Implementieren verschiedener Merkmale des bereitgestellten Gegenstands bereit. Spezifische Beispiele von Komponenten und Anordnungen werden unten beschrieben, um die vorliegende Offenbarung zu vereinfachen. Diese sind selbstverständlich bloß Beispiele und nicht beabsichtigt begrenzend zu sein. Zum Beispiel kann die Bildung eines ersten Strukturelements über oder auf einem zweiten Strukturelement in der folgenden Beschreibung Ausführungsformen umfassen, in denen das erste und das zweite Strukturelement in direktem Kontakt gebildet sind und kann auch Ausführungsformen umfassen, in denen zusätzliche Strukturelemente zwischen dem ersten und dem zweiten Strukturelement gebildet sein können, sodass das erste und das zweite Strukturelement nicht in direktem Kontakt sein könnten. Zusätzlich kann die vorliegende Offenbarung Referenznummern und/oder -buchstaben in den verschiedenen Beispielen wiederholen. Diese Wiederholung dient dem Zweck der Vereinfachung und Klarheit und gibt selbst keine Beziehung zwischen den unterschiedlichen besprochenen Ausführungsformen und/oder Konfigurationen vor.

[0006] Räumlich relative Ausdrücke wie "unterliegend", "unterhalb", "unter", "überliegend", "ober" und dergleichen können hierin zur Erleichterung der Beschreibung verwendet werden, um die Beziehung eines Elements oder Strukturelements zu (einem) anderen Element(en) oder Strukturelement(en) wie in den Figuren veranschaulicht zu beschreiben. Die räumlich relativen Ausdrücke sollen verschiedene Ausrichtungen der Vorrichtung in Verwendung oder Betrieb zusätzlich zu der in den Figuren abgebildeten Ausrichtung umschließen. Die Vorrichtung kann anders ausgerichtet sein (um 90 Grad gedreht oder bei anderen Ausrichtungen) und die hierin verwendeten räumlich relativen Beschreibungsausdrücke können ebenso entsprechend ausgelegt werden.

[0007] Darüber hinaus, wenn eine Zahl oder ein Bereich von Zahlen mit "etwa", "annähernd" und dergleichen beschrieben ist, soll der Begriff Zahlen umfassen, die innerhalb eines angemessenen Bereichs liegen, unter Berücksichtigung von Variationen, die an sich während Herstellung entstehen, wie einem Durchschnittsfachmann bekannt ist. Zum Beispiel umfasst die Zahl oder der Bereich von Zahlen einen angemessenen Bereich, der die beschriebene Zahl enthält, wie innerhalb von +/-10% der beschriebenen Zahl, basierend auf bekannten Herstellungstoleranzen, die mit der Herstellung eines Strukturelements mit einer Eigenschaft verbunden sind, die mit der Zahl verbunden ist. Zum Beispiel kann eine Materialschicht mit einer Dicke von "etwa 5 nm" einen Abmessungsbereich von 4,25 nm bis 5,75 nm aufweisen, wobei dem Durchschnittsfachmann bekannt ist, dass Herstellungstoleranzen, die mit Abscheiden der Materialschicht verbunden sind, +/-15% betragen. Weiter kann die vorliegende Offenbarung Referenznummern und/oder - buchstaben in den unterschiedlichen Beispielen wiederholen. Diese Wiederholung dient dem Zweck der Vereinfachung und Klarheit und gibt selbst keine Beziehung zwischen den unterschiedlichen besprochenen Ausführungsformen und/oder Einrichtungen vor

[0008] Eine Bitzelle einer magneto-resistiven Direktzugriffspeichervorrichtung (MRAM-Vorrichtung) weist einen magnetischen Tunnelübergangsstapel (MTJ-Stapel, Magnetischer Tunnel Junction) auf, der vertikal zwischen zwei Elektroden, üblicherweise einer Bodenelektrode und einer Deckelektrode, angeordnet ist. Der MTJ-Stapel weist eine gepinnte Schicht durch eine Tunnelsperrschicht getrennt von einer freien Schicht auf. Die magnetische Ausrichtung der gepinnten Schicht ist statisch (d.h. festgesetzt), während die magnetische Ausrichtung der freien Schicht zwischen einer parallelen Konfigura-

tion und einer anti-parallelen Konfiguration in Bezug auf jene der gepinnten magnetischen Schicht wechseln kann. Die parallele Konfiguration stellt einen Zustand geringen Widerstands bereit, der Daten als einen ersten Bitwert (z.B. eine logische "o") speichert. Die anti-parallele Konfiguration stellt einen Zustand hohen Widerstands bereit, der Daten als einen zweiten Bitwert (z.B. eine logische "1") speichert. Der Wechsel zwischen den zwei Konfigurationen stellt zwei magnetische Zustände des MTJ-Stapels bereit. Der magnetische Zustand des MTJ-Stapels wird durch Anwenden eines Schreibstroms angemessener Amplitude und Polarität eingestellt oder durch Anwenden eines Lesestroms, um eine Spannung an eine Erfassungsschaltung anzulegen, ausgelesen. Abhängig von den Widerstandszuständen der Bitzelle kann die Spannung höher oder niedriger sein.

[0009] In manchen Implementierungen wird die Bitzelle eines MRAM durch einen Ansteuerungstransistor gesteuert, der auf der Ebene des Front-End-of-Line (FEOL) angeordnet ist. Der Ansteuerungstransistor weist ein Source-Strukturelement, ein Drain-Strukturelement, ein aktives Gebiet zwischen dem Source-Strukturelement und dem Drain-Strukturelement und ein Gate-Struktur über dem aktiven Gebiet auf. Wenn die Bitzelle in einer vorderseitigen Interconnect-Struktur über dem Ansteuerungstransistor angeordnet ist, ist die Deckelektrode an eine Bitleitung (BL) gekoppelt und die Bodenelektrode ist an eines der Drain-Strukturelemente des Ansteuerungstransistors durch eine Reihe von inselartigen Metallstrukturelementen und Kontaktdurchkontaktierungen gekoppelt. Eine Source-Leitung (SL) ist elektrisch an das Source-Strukturelement des Ansteuerungstransistors gekoppelt. Die Gate-Struktur des Ansteuerungstransistors ist an eine Wortleitung (WL) gekoppelt. Wenn die Wortleitung (WL) durch Anlegen einer Freigabespannung ausgewählt wird, wird der Ansteuerungstransistor eingeschaltet. Die Bitzelle ist zwischen der Bitleitung (BL) und der Source-Leitung (SL) gekoppelt.

[0010] MRAM-Vorrichtungen gibt es in verschiedenen Formen, um verschiedenen Designanforderungen gerecht zu werden. Zum Beispiel hat ein Flashartiger (Reflow) MRAM gute Wärmestabilität und Daten, die darin gespeichert sind, gehen mit geringerer Wahrscheinlichkeit nach einem Aufschmelzprozess (Erhitzungsprozess) verloren. Ein Reflow-MRAM kann eine Ansprechzeit von weniger als 100 Nanosekunden (ns) aufweisen. Ein RAM-artiger MRAM hat kurzfristige, nicht flüchtige Eigenschaft und kann bei einer höheren Geschwindigkeit unter Verwendung eines relativ geringen Stroms gelesen oder beschrieben werden. Ein RAM-artiger MRAM hat eine schnellere Ansprechzeit, wie weniger als 20 ns. Eine nicht flüchtige MRAM-Vorrichtung (NvMRAM-Vorrichtung) weist Eigenschaften auf, die zwischen jenen eines Reflow-MRAM und RAM-artigen-MRAM liegen. Sie hat gute Speicherleistung, muss aber nicht bei einer relativ hohen Temperatur arbeiten. Ein NvMRAM kann eine Ansprechzeit von weniger als 50 ns aufweisen. Eine einmalig programmierbare (OTP, One-Time Programmable) MRAM-Vorrichtung ist eingerichtet, nur einmal durch eine Schreibspannung beschrieben zu werden. Die Schreibspannung ist ausreichend hoch, um die dielektrischen Schichten in dem MTJ-Stapel des OTP MRAM irreversibel durchzubrechen. Infolgedessen können Daten, die in einem OTP MRAM gespeichert sind, nicht verändert werden. Diese verschiedenen MRAM-Vorrichtungen haben unterschiedliche Konfigurationen. Zum Beispiel kann in manchen bestehenden Implementierungen ein Reflow-MRAM eine dickere freie Schicht aufweisen, um Wärmestabilität zu verbessern. Ein RAM-artiger MRAM kann eine dünnere freie Schicht aufweisen, um ein schnelleres Ansprechen zu erzielen. Bilden freier Schichten in verschiedenen Dicken auf demselben Substrat kann jedoch zusätzliche Fotolithografieschritte erfordern und zusätzliche Kosten verursachen. Es besteht ein Bedarf an der Bildung verschiedener MRAM-Vorrichtungen auf einer einzigen IC mit angemessenen Kosten und angemessener Ausbeute.

[0011] Die vorliegende Offenbarung stellt Einzel-IC MRAM-Integrationsschemata bereit, die ermöglichen, dass verschiedene Arten von MRAM-Vorrichtungen gleichzeitig auf derselben IC gefertigt werden können, ohne wesentliche Leistungskompromisse, um eine gleichzeitige Fertigung bei angemessenen Kosten zu ermöglichen, weist die freie Schicht in den MRAM-Vorrichtungen in jedem der Einzel-IC MRAM-Integrationsschemata eine gleichförmige Dicke auf. Die verschiedenen Wärmestabilitäts- und Ansprechzeitanforderungen werden durch Implementierung verschiedener kritischer Dimensionen (CDs, Critical Dimensions) des MTJ erfüllt. Da der Wechsel von MRAM-Vorrichtungen von Stromdichte abhängig ist, kann Implementieren von MTJ-Stapeln verschiedener kritischer Dimensionen Stromdichte und somit Ansprechzeit variieren. In manchen Ausführungsformen ist die MTJ CD für einen Reflow-MRAM größer als jene für einen NvMRAM und die MTJ CD für einen OTP MRAM ist größer als jene eines RAM-artigen MRAM oder eines NvMRAM. In einem Einzel-IC MRAM-Integrationsschema sind Reflow-MRAMs, NvMRAMs und OTP MRAMs auf einer IC integriert. In einem anderen Einzel-IC MRAM-Integrationsschema sind RAM-artige MRAMs. OTP MRAMs und NvMRAMs auf einer IC integriert.

**[0012]** Die verschiedenen Aspekte der vorliegenden Offenbarung werden nun ausführlicher unter Bezugnahme auf die Figuren beschrieben. In dieser Hinsicht ist **Fig.** 1 ein Ablaufdiagramm, das Verfahren

100 zum Bilden einer IC-Vorrichtungsstruktur gemäß Ausführungsformen der vorliegenden Offenbarung veranschaulicht. Verfahren 100 ist unten in Verbindung mit Fig. 2-8 beschrieben, die fragmentarische Querschnittsansichten eines Werkstücks 200 in verschiedenen Fertigungsstufen gemäß Ausführungsformen von Verfahren 100 sind. Fig. 10 ist ein Ablaufdiagramm, das Verfahren 500 zum Bilden einer IC-Vorrichtungsstruktur gemäß Ausführungsformen der vorliegenden Offenbarung zeigt. Verfahren 500 ist unten in Verbindung mit Fig. 11-17 beschrieben, die fragmentarische Querschnittsansichten eines Werkstücks 200 in verschiedenen Fertigungsstufen gemäß Ausführungsformen von Verfahren 500 sind. Verfahren 100 und 500 sind nur Beispiele und sind nicht als Einschränkung der vorliegenden Offenbarung auf das, was ausdrücklich in Verfahren 100 oder 500 veranschaulicht ist, auszulegen. Zusätzliche Schritte können vor, während und nach dem Verfahren 100 oder Verfahren 500 bereitgestellt sein und manche beschriebene Schritte können für zusätzliche Ausführungsformen des Verfahrens ersetzt, eliminiert oder verschoben werden. Zugunsten der Einfachheit sind hier nicht alle Schritte ausführlich beschrieben. Da das Werkstück 200 zu einer Halbleiterstruktur 200 oder einer Halbleitervorrichtung 200 nach Beendigung der Fertigungsprozesse gefertigt wird, kann das Werkstück 200, wie es der Kontext verlangt, als die Halbleiterstruktur 200 oder die Halbleitervorrichtung 200 bezeichnet werden.

[0013] Unter Bezugnahme auf Fig. 1 und Fig. 2 umfasst Verfahren 100 einen Block 102, wo ein Werkstück 200 empfangen wird. Das Werkstück 200 weist ein Substrat 201 und eine Interconnect-Struktur 203 über dem Substrat 201 auf. Verfahren 100 kann implementiert werden, um Speichervorrichtungen oder Datenspeicherstrukturen in einer von etwa fünf (5) bis etwa neunzehn (19) Metallschichten (oder Metallisierungsschichten) in der Interconnect-Struktur 203 zu bilden. Die Interconnect-Struktur 203 kann eine rückseitige Interconnect-Struktur oder eine vorderseitige Interconnect-Struktur sein. Wie unten näher beschrieben wird, wird das Substrat 201 aus einem Halbleitermaterial gebildet und wurde Front-End-of-Line-Prozessen (FEOL-Prozessen) unterzogen. Solche FEOL-Prozesse können verschiedene Transistoren bilden, die verschiedenen Funktionen dienen. Zum Beispiel können diese verschiedenen Transistoren eine zentrale Verarbeitungseinheit (CPU, Central Processing Unit), eine Grafikverarbeitungseinheit (GPU, Graphics Process Unit), Zugangstransistoren für Speichervorrichtungen bilden. Die Transistoren können planar Transistoren oder Multi-Gate-Transistoren sein. Eine Multi-Gate-Vorrichtung bezieht sich im Allgemeinen auf eine Vorrichtung mit einer Gate-Struktur oder einen Abschnitt davon, die über mehr als einer Seite eines Kanalgebiets angeordnet ist. Finnen-artige Feldeffekttransistoren (FinFETs) und Mehrfachbrücken-(MBC-Transistoren, Kanal-Transistoren Multi-Bridge-Channel) sind Beispiele für Multi-Gate-Vorrichtungen, die beliebte und vielversprechende Kandidaten für Hochleistungs- und verlustarme Anwendungen geworden sind. Ein FinFET weist einen erhöhten Kanal auf, der von einem Gate an mehr als einer Seite umgeben ist (zum Beispiel umgibt das Gate eine Oberseite und Seitenwände einer "Finne" aus Halbleitermaterial, die sich von einem Substrat erstreckt). Ein MBC-Transistor weist eine Gate-Struktur auf, die sich teilweise oder vollständig um ein Kanalgebiet erstrecken kann, um Zugang zu dem Kanalgebiet an zwei oder mehr Seiten bereitzustellen. Da seine Gate-Struktur die Kanalgebiete umgibt, kann ein MBC-Transistor auch als ein umgebender Gate-Transistor (SGT, Surrounding Gate Transistor) oder ein Gate-all-Around-Transistor (GAA-Transistor) bezeichnet werden. Das Kanalgebiet eines MBC-Transistors kann aus Nanodrähten, Nanoblättern oder anderen Nanostrukturen gebildet sein und aus diesem Grund kann ein MBC-Transistor auch als ein Nanodrahttransistor oder ein Nanoblatttransistor bezeichnet werden.

[0014] In manchen Ausführungsformen enthält das Substrat 201 Silizium (Si). Alternativ oder zusätzlich enthält Substrat 201 einen anderen elementaren Halbleiter, wie Germanium (Ge); einen Verbindungshalbleiter, wie Siliziumcarbid, Galliumarsenid, Galliumphosphid, Indiumphosphid, Indiumarsenid und/oder Indiumantimonid; einen Legierungshalbleiter, wie Siliziumgermanium (SiGe), GaAsP, AllnAs, AlGaAs, GalnAs, GalnP und/oder GalnAsP; oder Kombinationen davon. In manchen Implementierungen enthält das Substrat 201 ein oder mehrere Materialien der Gruppe III-V, ein oder mehrere Materialien der Gruppe II-IV oder Kombinationen davon. In manchen Implementierungen ist das Substrat 201 ein Halbleiter-auf-Isolator Substrat, wie ein Silizium-auf-Isolator-Substrat (SOI-Substrat), ein Siliziumgermanium-auf-Isolator-Substrat (SGOI-Substrat) oder ein Germanium-auf-Isolator-Substrat (GeOI-Substrat). Halbleiter-auf-Isolator-Substrate können unter Verwendung von Trennung durch Implantation von Sauerstoff (SIMOX, Separation by Implantation of Oxygen), Waferbonding und/oder andere geeignete Verfahren gefertigt werden. Da Verfahren 100 an einem Werkstück 200 durchgeführt wird, bei dem FEOL-Prozesse an dem Substrat 201 durchgeführt wurden, ist das Substrat 201 in Fig. 2 nur in strichlierten Linien dargestellt und fehlt in Fig. 3-8.

[0015] Während die Interconnect-Struktur 203 mehrere Metallschichten aufweist, können die Speichervorrichtungen/Datenspeicherstrukturen in einer der Metallschichten gebildet werden, wie einer vierten Metallschicht (M4), einer fünften Metallschicht (M5) oder einer sechsten Metallschicht (M6). Da die Interconnect-Struktur 203 eine vorderseitige Intercon-

nect-Struktur oder eine rückseitige Interconnect-Struktur sein kann, können die Speichervorrichtungen/Datenspeicherstrukturen der vorliegenden Offenbarung in einer vierten vorderseitigen Metallschicht, einer fünften vorderseitigen Metallschicht, einer sechsten vorderseitigen Metallschicht, einer vierten rückseitigen Metallschicht, einer fünften rückseitigen Metallschicht, einer sechsten rückseitigen Metallschicht gebildet sein. Unter Bezugnahme auf Fig. 2 stellen leitfähige Strukturelemente 204 in einer ersten dielektrischen Schicht 202 eine Metallschicht unter den Speichervorrichtungen dar. Die erste dielektrische Schicht 202 kann Materialien wie Tetraethylorthosilicatoxid (TEOS-Oxid) undotiertes Silicatglas oder dotiertes Siliziumoxid wie Borphosphosilicatglas (BPSG), geschmolzenes Quarzglas (FSG, Fused Silica Glass), Phosphosilicatglas (PSG), bordotiertes Siliziumglas (BSG) und/oder andere geeignete dielektrische Materialien enthalten. Die leitfähigen Strukturelemente 204 können Metallleitungen sein und können Ruthenium (Ru), Kupfer (Cu), Nickel (Ni), Kobalt (Co) oder Wolfram (W) enthalten. In einer Ausführungsform enthalten die leitfähigen Strukturelemente 204 Kupfer (Cu). Die leitfähigen Strukturelemente 204 können Metallleitungen oder Kontaktdurchkontaktierungen aufwei-

[0016] Weiter unter Bezugnahme auf Fig. 2 weist das Werkstück 200 ein erstes Gebiet 10, ein zweites Gebiet 20, ein drittes Gebiet 30 und ein viertes Gebiet 40 auf. Diese Gebiete können aneinander angrenzen oder können voneinander beabstandet sein. Diese verschiedenen Gebiete können verschiedene Anordnungen in Bezug auf Speichervorrichtungen haben. In manchen Ausführungsformen kann das erste Gebiet 10 ein Gebiet zum Bilden von RAM-artigen MRAMs sein, kann das zweite Gebiet 20 ein Gebiet zum Bilden von NvMRAMs sein, kann das dritte Gebiet 30 ein Gebiet zum Bilden von OTP MRAMs sein und kann das vierte Gebiet 40 ein Gebiet sein, das frei von jeder MRAM-Struktur ist.

[0017] Unter Bezugnahme auf Fig. 1 und Fig. 2 umfasst Verfahren 100 einen Block 104, wo eine Pufferschicht 206 und eine zweite dielektrische Schicht 208 über dem Werkstück 200 abgeschieden sind. Die Pufferschicht 206 kann Siliziumcarbid (SiC) oder Siliziumoxycarbid (SiOC) enthalten, was dazu beiträgt, Elektromigration der leitfähigen Strukturelemente 204 zu unterbinden. Die zweite dielektrische Schicht 208 kann Siliziumoxid enthalten. In einer Ausführungsform kann die zweite dielektrische Schicht 208 siliziumreiches Oxid (SRO) enthalten und unterscheidet sich von der ersten dielektrischen Schicht 202. Wie hier verwendet, ist ein Siliziumgehalt in Siliziumreichem Oxid geringer als das Silizium-stöchiometrische Verhältnis in Siliziumdioxid. In dieser Ausführungsform ist der Siliziumgehalt in der ersten dielektrischen Schicht 202 größer als der Siliziumgehalt in der zweiten dielektrischen Schicht 208. Die Pufferschicht 206 kann unter Verwendung von chemischer Dampfphasenabscheidung (CVD, Chemical Vapor Deposition) abgeschieden werden. Die zweite dielektrische Schicht 208 kann unter Verwendung von Niederdruck-CVD (Low Pressure CVD, LPCVD) oder CVD abgeschieden werden.

[0018] Unter Bezugnahme auf Fig. 1 und Fig. 2 umfasst Verfahren 100 einen Block 106, wo eine erste Bodendurchkontaktierung 210-1, eine zweite Bodendurchkontaktierung 210-2 und eine dritte Bodendurchkontaktierung 210-3 über dem ersten Gebiet 10, dem zweiten Gebiet 20 beziehungsweise dem dritten Gebiet 30 gebildet werden. Obwohl nicht ausdrücklich in Fig. 2 gezeigt, können Operationen in Block 106 Bildung von Durchkontaktierungsöffnungen, um die leitfähigen Strukturelemente 204 freizulegen, und Bildung der ersten Bodendurchkontaktierung 210-1, der zweiten Bodendurchkontaktierung 210-2 und der dritten Bodendurchkontaktierung 210-3 in den Durchkontaktierungsöffnungen umfassen. Bildung der Durchkontaktierungsöffnungen umfasst eine Kombination von Fotolithografieprozessen und Ätzprozessen. In einem beispielhaften Prozess wird eine Hartmaskenschicht über der zweiten dielektrischen Schicht 208 abgeschieden. Eine Fotolackschicht wird über der Hartmaskenschicht abgeschieden. Die Fotolackschicht wird dann mit einer strukturierten Strahlung belichtet, die durch eine Fotomaske geht oder von dieser reflektiert wird, in einem Nachbelichtungsbackprozess gebacken, in einer Entwicklerlösung entwickelt und dann gespült, wodurch eine strukturierte Fotolackschicht gebildet wird. Die strukturierte Fotolackschicht wird dann als eine Ätzmaske aufgetragen, um die Hartmaskenschicht zu ätzen, um eine strukturierte Hartmaskenschicht zu bilden. Die strukturierte Hartmaskenschicht wird dann als eine Ätzmaske aufgetragen, um die zweite dielektrische Schicht 208 und die Pufferschicht 206 zu ätzen. Das Ätzen der zweiten dielektrischen Schicht 208 und der Pufferschicht 206 kann ein Trockenätzprozess sein, der Verwendung von Argon (Ar), einem fluorhaltigen Ätzmittel (zum Beispiel SF<sub>6</sub>, NF<sub>3</sub>, CH<sub>2</sub>F<sub>2</sub>, CHF<sub>3</sub>, C<sub>4</sub>F<sub>8</sub> und/oder C<sub>2</sub>F<sub>6</sub>), einem sauerstoffhaltigen Ätzmittel, einem chlorhaltigen Ätzmittel (zum Beispiel Cl2, CHCl3, CCI<sub>4</sub> und/oder BCI<sub>3</sub>), einem bromhaltigen Ätzmittel (zum Beispiel HBr und/oder CHBr<sub>3</sub>), einem iodhaltigen Ätzmittel oder Kombinationen davon umfasst.

[0019] Nachdem die Durchkontaktierungsöffnungen gebildet wurden, wird eine Metallfüllschicht über dem Werkstück 200 abgeschieden, um die Durchkontaktierungsöffnungen zu füllen. Die Metallfüllschicht kann Titannitrid (TiN), Ruthenium (Ru), Kupfer (Cu), Nickel (Ni), Kobalt (Co) oder Wolfram (W) enthalten. In einer Ausführungsform kann die Metallfüllschicht Titannitrid (TiN) enthalten. Die Metallfüllschicht kann unter Verwendung von physikalischer Dampfphase-

nabscheidung (PVD, Physical Vapor Deposition), CVD, elektrolosem Plattieren, Elektroplattieren oder einem geeigneten Verfahren abgeschieden werden. Nach dem Abscheiden der Metallfüllschicht wird das Werkstück 200 unter Verwendung eines chemischmechanischen Polierprozesses (CMP-Prozess, Chemical Mechanical Polishing) zum Entfernen der überschüssigen Metallfüllschicht planarisiert, um die zweite dielektrische Schicht 208 freizulegen. An diesem Punkt wird die erste Bodendurchkontaktierung 210-1 in dem ersten Gebiet 10 gebildet, um elektrisch und physisch an das leitfähige Strukturelement 204 in dem ersten Gebiet 10 gekoppelt zu werden; die zweite Bodendurchkontaktierung 210-2 wird in dem zweiten Gebiet 20 gebildet, um elektrisch und physisch an das leitfähige Strukturelement 204 in dem zweiten Gebiet 20 gekoppelt zu werden; und die dritte Bodendurchkontaktierung 210-3 wird in dem dritten Gebiet 30 gebildet, um elektrisch und physisch an das leitfähige Strukturelement 204 in dem dritten Gebiet 30 gekoppelt zu werden. Es wird festgehalten, dass über dem vierten Gebiet 40 keine Bodendurchkontaktierung gebildet wird.

[0020] Unter Bezugnahme auf Fig. 1 und Fig. 2 umfasst Verfahren 100 einen Block 108, wo eine Bodenelektrodenschicht 212 über dem Werkstück 200 abgeschieden wird, umfassend über der zweiten dielektrischen Schicht 208, der ersten Bodendurchkontaktierung 210-1, der zweiten Bodendurchkontaktierung 210-2 und der dritten Bodendurchkontaktierung 210-3. Die Bodenelektrodenschicht 212 kann eine einzelne Schicht oder eine Mehrfachschicht sein. Wenn die Bodenelektrodenschicht 212 eine einzelne Schicht ist, kann sie Titannitrid (TiN) oder Tantalnitrid (TaN) enthalten. Wenn die Bodenelektrodenschicht 212 eine Mehrfachschicht ist, kann sie eine Tantalnitridschicht (TaN-Schicht) und eine Titannitridschicht (TiN-Schicht) enthalten. Die Bodenelektrodenschicht 212 kann unter Verwendung von PVD oder CVD abgeschieden werden. Die Bodenelektrodenschicht 212 wird global über dem Werkstück 200 abgeschieden, umfassend über Deckflächen der ersten Bodendurchkontaktierung 210-1, der zweiten Bodendurchkontaktierung 210-2, der dritten Bodendurchkontaktierung 210-3 und der zweiten dielektrischen Schicht 208.

[0021] Unter Bezugnahme auf Fig. 1 und Fig. 2 umfasst Verfahren 100 einen Block 110, wo ein erster magnetischer Tunnelübergangsstapel (MTJ-Stapel) 1000 über der Bodenelektrodenschicht 212 abgeschieden wird. Der erste MTJ-Stapel 1000 weist eine gepinnte Schicht 214 über der Bodenelektrodenschicht 212, eine Tunnelsperrschicht 216 über der gepinnten Schicht 214, eine freie Schicht 218 über der Tunnelsperrschicht 216, eine Wartungsschicht 220 über der freien Schicht 218 und eine Abdeckschicht 222, die über der Wartungsschicht 220 angeordnet ist, auf. Die gepinnte Schicht 214

kann ein ferromagnetisches Material wie Kobalteisen (CoFe), Kobalteisenbor (CoFeB), oder eine Kobalt-Platin-Legierung (Co-Pt-Legierung) enthalten. In manchen alternativen Ausführungsformen kann die gepinnte Schicht 214 CoFeTa, NiFe, Co, CoFe, CoPt, eine Legierung von Ni, Co und Fe, Platinmangan (PtMn), Iridiummangan (IrMn), Rhodiummangan (RhMn), Eisenmangan (FeMn) oder OsMn enthalten. Die Tunnelsperrschicht 216 kann aus einem Metalloxid gebildet sein, das ausgewählt ist aus einer Gruppe bestehend aus Magnesiumoxid (MgO), Titanoxid (TiO), Aluminiumtitanoxid (AlTiO), Magnesiumzinkoxid (MgZnO), Aluminiumoxid (AlO), Zinkoxid (ZnO), Zirconiumoxid (ZrO), Hafniumoxid (HfO) oder Magnesiumtantaloxid (MgTaO). In einer Ausführungsform ist die Tunnelsperrschicht 216 aus Magnesiumoxid gebildet. Die freie Schicht 218 ist aus einem ferromagnetischen Material gebildet und kann Kobalteisenbor (CoFeB) enthalten. Die Wartungsschicht 220 kann aus einem Metalloxid gebildet sein, das ausgewählt ist aus einer Gruppe bestehend aus Magnesiumoxid (MgO), Titanoxid (TiO), Aluminiumtitanoxid Magnesiumzinkoxid (AITiO), (MgZnO), Aluminiumoxid (AlO), Zinkoxid (ZnO), Zirconiumoxid (ZrO), Hafniumoxid (HfO) oder Magnesiumtantaloxid (MgTaO). In einer Ausführungsform kann die Wartungsschicht 220 Magnesiumoxid enthalten. Die Abdeckschicht 222 kann optional sein und kann Molybdän (Mo) oder Ruthenium (Ru) enthalten. Die gepinnte Schicht 214, die Tunnelsperrschicht 216, die freie Schicht 218, die Wartungsschicht 220 und die Abdeckschicht 222 können jeweils unter Verwendung von PVD, CVD, Elektroplattieren, elektrolosem Plattieren oder einem geeigneten Verfahren abgeschieden werden. In manchen Ausführungsformen, die in den Figuren nicht ausdrücklich dargestellt sind, kann die Abdeckschicht 222 fehlen und der erste MTJ-Stapel 1000 kann nur die gepinnte Schicht 214, die Tunnelsperrschicht 216, die Wartungsschicht 220 und die freie Schicht 218 aufweisen. Ein zweiter MTJ-Stapel 2000 wird unten gemeinsam mit einem alternativen Verfahren 500 beschrieben. Der zweite MTJ-Stapel 2000 weist eine Stapelreihenfolge auf, die umgekehrt zu jener des ersten MTJ-Stapels 1000 ist. Es sollte klar sein, dass Verfahren 100 auch zum Implementieren des zweiten MTJ-Stapels 2000 anstelle des ersten MTJ-Stapels 1000 verwendet werden kann.

[0022] Unter Bezugnahme auf Fig. 1 und Fig. 2 umfasst Verfahren 100 einen Block 112, wo eine Deckelektrodenschicht 224 über dem ersten MTJ-Stapel 1000 abgeschieden wird. Die Deckelektrodenschicht 224 kann eine einzelne Schicht oder eine Mehrfachschicht sein. Wenn die Deckelektrodenschicht 224 eine einzelne Schicht ist, kann sie Titannitrid (TiN) oder Tantalnitrid (TaN) enthalten. Wenn die Deckelektrodenschicht 224 eine Mehrfachschicht ist, kann sie eine Tantalnitridschicht und eine Titannitridschicht enthalten. Die Deckelektroden-

schicht 224 kann unter Verwendung von PVD oder CVD abgeschieden werden. Die Deckelektrodenschicht 224 wird global über dem Werkstück 200 abgeschieden, umfassend über dem ersten MTJ-Stapel 1000.

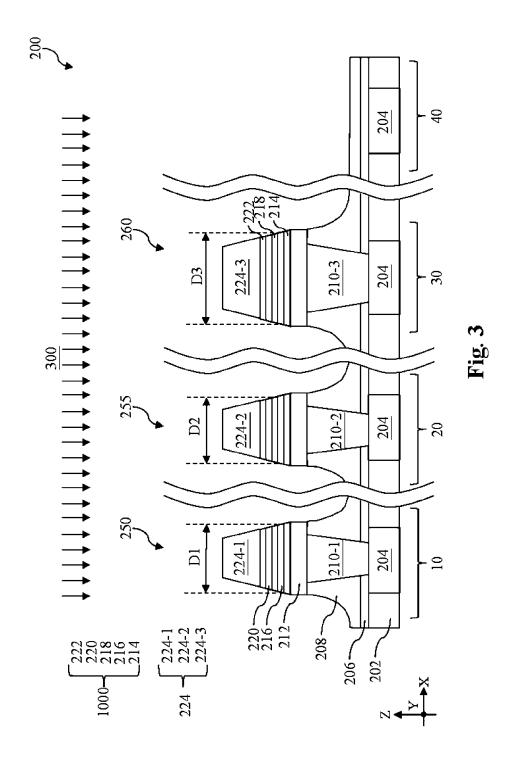

[0023] Unter Bezugnahme auf Fig. 1, Fig. 2 und Fig. 3 umfasst Verfahren 100 einen Block 114, wo die Deckelektrodenschicht 224, der erste MTJ-Stapel 1000 und die Bodenelektrodenschicht 212 strukturiert werden, um ein erstes Datenspeicherelement 250 über dem ersten Gebiet 10, ein zweites Datenspeicherelement 255 über dem zweiten Gebiet 20 und ein drittes Datenspeicherelement 260 über dem dritten Gebiet 30 zu bilden. In Block 114 werden Fotolithografieprozesse und Ätzprozesse durchgeführt, um das erste Datenspeicherelement 250, das zweite Datenspeicherelement 255 und das dritte Datenspeicherelement 260 zu bilden. In einem beispielhaften Prozess wird eine Hartmaskenschicht 226 über dem Werkstück 200 abgeschieden, umfassend über der Deckelektrodenschicht 224. In manchen Ausführungsformen kann die Hartmaskenschicht 226 Siliziumoxid, Siliziumnitrid oder eine Kombination davon enthalten. In einer Ausführungsform wird die Hartmaskenschicht 226 aus Siliziumoxid (z.B. Tetraethylorthosilicatoxid (TEOS-Oxid)) gebildet und kann unter Verwendung von Schleuderbeschichtung oder fließfähiger CVD (FCVD) abgeschieden werden. Dann wird eine Fotolackschicht über der Hartmaskenschicht 226 abgeschieden. Die abgeschiedene Fotolackschicht wird dann mit einer strukturierten Strahlung belichtet, die durch eine Fotomaske geht oder von dieser reflektiert wird, in einem Nachbelichtungsbackprozess gebacken, in einer Entwicklerlösung entwickelt und dann gespült, wodurch eine strukturierte Fotolackschicht gebildet wird. Wie in Fig. 2 gezeigt, wird die strukturierte Fotolackschicht dann als eine Ätzmaske aufgetragen, um die Hartmaskenschicht 226 zu ätzen, um eine erste Hartmaskenstruktur 226-1 über dem ersten Gebiet 10, eine zweite Hartmaskenstruktur 226-2 über dem zweiten Gebiet 20 und eine dritte Hartmaskenstruktur 226-3 über dem dritten Gebiet 30 zu bilden. Diese strukturierten Hartmaskenstrukturen werden dann als eine Ätzmaske aufgebracht, um die Deckelektrodenschicht 224, den ersten MTJ-Stapel 1000, die Bodenelektrodenschicht 212 und die zweite dielektrische Schicht 208 zu ätzen. Das Ätzen in Block 114 kann ein Ionenstrahlätzen (IBE, Ion Beam Etching) 300 umfassen. Beim Strukturieren von MTJ-Stapeln kann IBE wünschenswerter sein als reaktives Ionenätzen (RIE, Reactive Ion Etching), da IBE mit geringerer Wahrscheinlichkeit chemische Unreinheiten in den MTJ-Stapel einführt. Unreinheiten können Leistung des Datenspeicherelements verschlechtern. Das IBE 300 kann ein oder mehrere Edelgasionen wie Ar, Kr, Xe und Ne verwenden, die mit RF-Leistung oder Gleichstrom erzeugt werden. Es sollte klar sein, dass IBE typischerweise Drehen des Werkstücks 200 umfasst.

[0024] Zur Bildung der Speichervorrichtungen mit verschiedenen Vorrichtungseigenschaften weisen die Datenspeicherelemente verschiedene Abmessungen auf. Es wird beobachtet, dass bei einem identischen MTJ-Stapel ein Datenspeicherelement mit einer größeren freien Schicht eine bessere Wärmestabilität aufweist als ein Datenspeicherelement mit einer kleineren freien Schicht. Zusätzlich stellt ein Datenspeicherelement mit einer kleineren freien Schicht eine schnellere Ansprechzeit als ein Datenspeicherelement mit einer größeren freien Schicht bereit. In manchen Ausführungsformen, wo ein Datenspeicherelement eine kreisförmige Form bei Betrachtung entlang einer vertikalen Richtung aufweist, kann sich eine kritische Abmessung (CD) des Datenspeicherelements auf einen Durchmesser der freien Schicht beziehen. In manchen Ausführungsformen, dargestellt in Fig. 2, werden Hartmaskenstrukturen unterschiedlicher Abmessungen impleverschiedene mentiert. um Datenspeicherelementdurchmesser (oder Abmessungen) zu erzielen. Wie in Fig. 2 gezeigt, weist die erste Hartmaskenstruktur 226-1 eine erste Abmessung d1 auf, weist die zweite Hartmaskenstruktur 226-2 eine zweite Abmessung d2 auf und weist die dritte Hartmaskenstruktur 226-3 eine dritte Abmessung d3 auf. Die erste Abmessung d1 kann ähnlich der zweiten Abmessung d2 sein. Die dritte Abmessung d3 ist größer als entweder die erste Abmessung d1 oder die zweite Abmessung d2.

[0025] Wie in Fig. 3 gezeigt, kann das IBE 300 zu verjüngten Seitenwänden führen, sodass jedes des ersten Datenspeicherelements 250, des zweiten Datenspeicherelements 255 und des dritten Datenspeicherelements 260 eine kleinere Deckelektrodenabmessung und eine größere Bodenelementabmessung aufweist. Das erste Datenspeicherelement 250 weist die erste Deckelektrode 224-1 auf, die aus der Deckelektrodenschicht 224 gebildet ist. Das zweite Datenspeicherelement 255 weist die zweite Deckelektrode 224-2 auf, die aus der Deckelektrodenschicht 224 gebildet ist. Das dritte Datenspeicherelement 260 weist die dritte Deckelektrode 224-3 auf, die aus der Deckelektrodenschicht 224 gebildet ist. In manchen Ausführungsformen kann das erste Datenspeicherelement 250 durch eine erste MTJ-Abmessung D1 gekennzeichnet sein, die im Wesentlichen der Abmessung (oder dem Durchmesser) der freien Schicht 218 in dem ersten Datenspeicherelement 250 ähnlich sein kann. Das zweite Datenspeicherelement 255 kann durch eine zweite MTJ-Abmessung D2 gekennzeichnet sein, die im Wesentlichen ähnlich der Abmessung (oder dem Durchmesser) der freien Schicht 218 in dem zweiten Datenspeicherelement 255 sein kann. Das dritte Datenspeicherelement 260 kann durch eine dritte

MTJ-Abmessung D3 gekennzeichnet sein, die im Wesentlichen ähnlich der Abmessung (oder dem Durchmesser) der freien Schicht 218 in dem dritten Datenspeicherelement 260 sein kann. In manchen Implementierungen kann die erste MTJ-Abmessung D1 ähnlich der zweiten MTJ-Abmessung D2 sein. Die dritte MTJ-Abmessung D3 kann größer als entweder die erste MTJ-Abmessung D1 oder die zweite MTJ-Abmessung D2 sein. In manchen Fällen kann die erste MTJ-Abmessung D1 zwischen etwa 20 nm und etwa 50 nm sein, kann die zweite MTJ-Abmessung D2 zwischen etwa 20 nm und etwa 55 nm sein und kann die dritte MTJ-Abmessung D3 zwischen etwa 60 nm und etwa 85 nm sein.

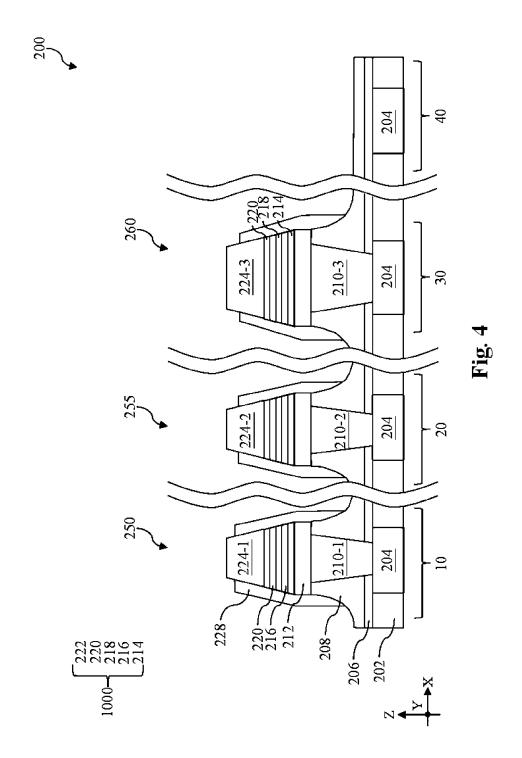

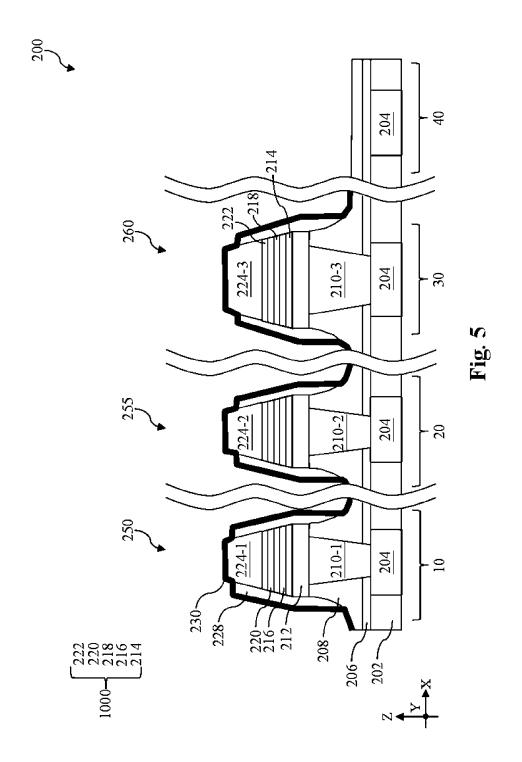

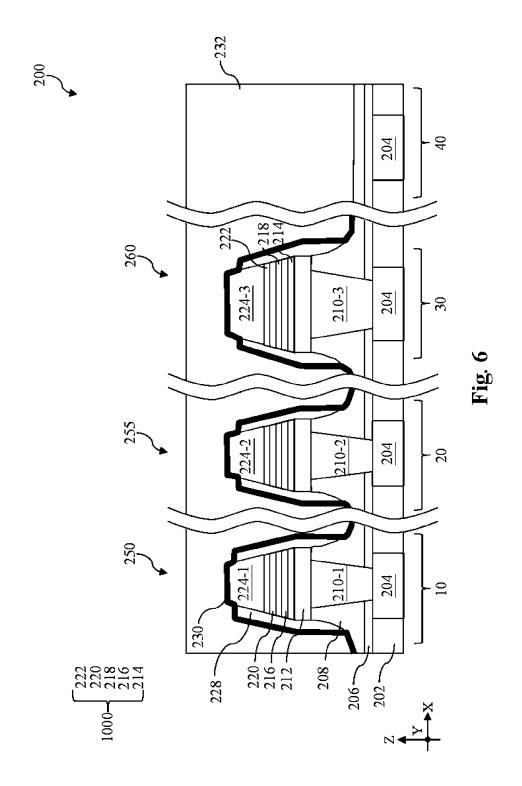

[0026] Unter Bezugnahme auf Fig. 1, Fig. 4, Fig. 5 und Fig. 6 umfasst Verfahren 100 einen Block 116, wobei eine Passivierungsstruktur über dem ersten Datenspeicherelement 250, dem zweiten Datenspeicherelement 255 und dem dritten Datenspeicherelement 260 gebildet wird. Die Passivierungsstruktur kann eine Abstandhalterschicht 228, die entlang Seitenwänden der Datenspeicherelemente angeordnet ist, eine Ätzstoppschicht (ESL, Etch Stop Layer) 230 über der Abstandhalterschicht 228 und eine dritte dielektrische Schicht 232 über der ESL 230 aufweisen. Obwohl nicht ausdrücklich in den Figuren gezeigt, können Operationen in Block 116 ein Vorhangabscheiden der Abstandhalterschicht 228, Rückätzen der Abstandhalterschicht 228, um die Abstandhalterschicht 228 auf nach oben weisenden Oberflächen (gezeigt in Fig. 4) zu entfernen, Abscheiden der ESL 230 über der Abstandhalterschicht 228 und Abscheiden der dritten dielektrischen Schicht 232 umfassen. In manchen Ausführungsformen kann die Abstandhalterschicht 228 Siliziumnitrid, Siliziumoxid oder ein geeignetes Material enthalten und kann unter Verwendung von CVD oder ALD abgeschieden werden. In einer Ausführungsform kann die Abstandhalterschicht 228 Siliziumnitrid enthalten. Die ESL 230 kann Aluminiumoxid oder ein Metalloxid, das ätzbeständiger als die Abstandhalterschicht 228 ist, enthalten. Die ESL 230 kann unter Verwendung von CVD oder ALD abgeschieden werden. Die dritte dielektrische Schicht 232 kann Materialien wie Tetraethylorthosilicatoxid (TEOS-Oxid), undotiertes Silicatglas oder dotiertes Siliziumoxid wie Borphosphosilicatglas (BPSG), geschmolzenes Quarzglas (FSG), Phosphosilicatglas (PSG), bordotiertes Siliziumglas (BSG) und/oder andere geeignete dielektrische Materialien enthalten. In manchen Fällen kann die dritte dielektrische Schicht 232 unter Verwendung von Schleuderbeschichtung oder FCVD abgeschieden werden. Wie in Fig. 6 gezeigt, ist die Abstandhalterschicht 228 in physischem Kontakt mit der zweiten dielektrischen Schicht 208, Seitenwänden der Bodenelektroden 212, den gepinnten Schichten 214, der Tunnelsperrschicht 216, der freien Schicht 218, der Wartungsschicht 220 und der Abdeckschicht 222 der Datenspeicherelemente über dem ersten Gebiet 10, dem zweiten Gebiet 20 und dem dritten Gebiet 30. Die ESL 230 ist in physischem Kontakt mit der zweiten dielektrischen Schicht 208, der Abstandhalterschicht 228 und den Deckelektroden. In manchen Ausführungsformen, die in **Fig.** 5 veranschaulicht sind, wird die ESL 230 nicht über dem vierten Gebiet 40 gebildet, da Vorhandensein der ESL 230 über dem vierten Gebiet 40 eine gute elektrische Verbindung mit dem leitfähigen Strukturelement 204 in dem vierten Gebiet 40 behindern kann.

[0027] Unter Bezugnahme auf Fig. 1, Fig. 7 und Fig. 8 umfasst Verfahren 100 einen Block 118, wobei weitere Prozesse durchgeführt werden. Solche weiteren Prozesse können Bildung einer ersten Kontaktöffnung 235-1, einer zweiten Kontaktöffnung 235-2, einer dritten Kontaktöffnung 235-3, einer vierten Kontaktöffnung 235-4 und einer fünften Kontaktöffnung 235-5 (gezeigt in Fig. 7) und Abscheiden einer Metallfüllschicht in den Kontaktöffnungen umfassen, um weitere Kontaktstrukturelemente zu bilden (wie in Fig. 8 gezeigt). Fotolithografieprozesse und Ätzprozesse können verwendet werden, um die Kontaktöffnung zu bilden. In einem beispielhaften Prozess wird die fünfte Kontaktöffnung 235-5 über dem vierten Gebiet 40 gebildet, während das erste Gebiet 10, das zweite Gebiet 20 und das dritte Gebiet 30 durch einen Strukturierungsfilm, wie eine Foto-Antireflexionsbodenschicht lackschicht, eine (BARC-Schicht, Bottom Antireflective Coating) geschützt sind. Nach der Entfernung des Strukturierungsfilms werden die erste Kontaktöffnung 235-1, die zweite Kontaktöffnung 235-2 und die dritte Kontaktöffnung 235-3 und die fünfte Kontaktöffnung 235-5 durch die dritte dielektrische Schicht 232, die ESL 230, die zweite dielektrische Schicht 208 und die Pufferschicht 206 unter Verwendung von Fotolithografieprozessen und Ätzprozessen gebildet, wie in Fig. 7 dargestellt. Das leitfähige Strukturelement 204 in dem vierten Gebiet 40 wird in der vierten Kontaktöffnung 235-4 freigelegt. Die erste Kontaktöffnung 235-1 legt die erste Deckelektrode 224-1 frei. Die zweite Kontaktöffnung 235-2 legt die zweite Deckelektrode 224-2 frei. Die dritte Kontaktöffnung 235-3 legt die dritte Deckelektrode 224-3 frei. Die vierte Kontaktöffnung 235-4 und die fünfte Kontaktöffnung 235-5 bilden gemeinsam eine Durchgangsöffnung in dem vierten Gebiet 40, da in dem vierten Gebiet 40 kein Datenspeicherelement vorhanden ist. Das Ätzen in Block 118 kann einen Trockenätzprozess umfassen, der Argon (Ar), ein fluorhaltiges Ätzmittel (zum Beispiel SF<sub>6</sub>, NF<sub>3</sub>, CH<sub>2</sub>F<sub>2</sub>, CHF<sub>3</sub>, C<sub>4</sub>F<sub>8</sub> und/oder C<sub>2</sub>F<sub>6</sub>), ein sauerstoffhaltiges Ätzmittel, ein chlorhaltiges Ätzmittel (zum Beispiel Cl2, CHCl3, CCl<sub>4</sub> und/oder BCl<sub>3</sub>), ein bromhaltiges Ätzmittel (zum Beispiel HBr und/oder CHBr<sub>3</sub>), ein iodhaltiges Ätzmittel oder Kombinationen davon verwendet.

[0028] Es wird dann auf Fig. 8 Bezug genommen. Dann wird eine Metallfüllschicht über den Kontaktöffnungen unter Verwendung von PVD, CVD, Elektroplattieren oder elektrolosem Plattieren abgeschieden. Die Metallfüllschicht kann Ruthenium (Ru), Kupfer (Cu), Nickel (Ni), Kobalt (Co) oder Wolfram (W) enthalten. In einer Ausführungsform enthält die Metallfüllschicht Kupfer (Cu). Nach Abscheiden der Metallfüllschicht wird ein Planarisierungsprozess, wie ein CMP-Prozess, durchgeführt, um überschüssige Metallfüllschicht über der dritten dielektrischen Schicht 232 zu entfernen. Nach dem CMP-Prozess wird eine erste obere Kontaktdurchkontaktierung 236-1 über dem ersten Datenspeicherelement 250 gebildet, um an die erste Deckelektrode 224-1 elektrisch zu koppeln; eine zweite obere Kontaktdurchkontaktierung 236-2 wird über dem zweiten Datenspeicherelement 255 gebildet, um an die zweite Deckelektrode 224-2 elektrisch zu koppeln; eine dritte obere Kontaktdurchkontaktierung 236-3 wird über dem dritten Datenspeicherelement 260 durchgeführt, um an die dritte Deckelektrode 224-3 elektrisch zu koppeln, und eine vierte obere Kontaktdurchkontaktierung 236-4 wird gebildet, um sich durch die dritte dielektrische Schicht 232, die zweite dielektrische Schicht 208 und die Pufferschicht 206 zu erstrecken, um an das leitfähige Strukturelement 204 in dem vierten Gebiet 40 elektrisch zu koppeln. Obwohl nicht ausdrücklich gezeigt, kann eine Sperrschicht über den Kontaktöffnungen vor dem Abscheiden der Metallfüllschicht abgeschieden werden. Die Sperrschicht kann Titannitrid (TiN) oder Tantalnitrid (TaN) enthalten. Zusätzlich kann Verfahren 100 fortgesetzt werden, um weitere Metallschichten über dem Werkstück 200 zu bilden, wie in Fig. 8 gezeigt.

[0029] Fig. 9 ist eine schematische Draufsicht eines ersten IC-Chips 400, der ein Prozessorgebiet 402, ein RAM-artiges MRAM-Gebiet 404, ein NvMRAM-Gebiet 406 und ein OTP MRAM-Gebiet 408 aufweist. Das Prozessorgebiet 402 kann Kerntransistoren auf FEOL-Ebene aufweisen, um eine zentrale Verarbeitungseinheit (CPU) zu bilden. Das RAM-artige MRAM-Gebiet 404 kann dem ersten Gebiet 10 entsprechen und kann die ersten Datenspeicherelemente 250 auf der BEOL-Ebene aufweisen. Das NvMRAM-Gebiet 406 kann dem zweiten Gebiet entsprechen und kann die zweiten Datenspeicherelemente 255 auf der BEOL-Ebene aufweisen. Das OTP MRAM-Gebiet 408 kann dem dritten Gebiet 30 entsprechen und kann das dritte Datenspeicherelement 260 auf der BEOL-Ebene aufweisen. Wie zuvor beschrieben können die Datenspeicherelemente in dem RAM-artigen MRAM-Gebiet 404, dem NvMRAM-Gebiet 406 und dem OTP MRAM-Gebiet 408 denselben ersten MTJ-Stapel 1000 aufweisen und können gleichzeitig gebildet werden. Der erste IC-Chip 400 ist für Künstliche-Intelligenz-Anwendungen (KI-Anwendungen) geeignet, da er eingerichtet ist, eine kurze Ansprechzeit zu haben. Wärmestabilität von MRAMs ist für die KI-Anwendungen von geringer Bedeutung. Da in dem ersten IC-Chip 400 eine kurze Ansprechzeit gesucht wird, kann die freie Schicht 218 in dem ersten MTJ-Stapel 1000 an der dünneren Seite des Spektrums sein. In manchen Fällen kann die freie Schicht 218 in dem ersten MTJ-Stapel 1000 zwischen etwa 1,5 nm und etwa 3,0 nm sein.

[0030] Wie zuvor beschrieben, kann Verfahren 100 durchgeführt werden, um das erste Datenspeicherelement 250, das zweite Datenspeicherelement 255 und das dritte Datenspeicherelement 260 über dem ersten Gebiet 10, dem zweitem Gebiet 20 und dem dritten Gebiet 30 des Werkstücks 200 zu bilden. Jedes des ersten Datenspeicherelements 250, des zweiten Datenspeicherelements 255 und des dritten Datenspeicherelements 260 wird aus demselben ersten MTJ-Stapel 1000 gebildet. Die vorliegende Offenbarung stellt auch ein Verfahren 500 bereit, das ein viertes Datenspeicherelement 265, das zweite Datenspeicherelement 255 und das dritte Datenspeicherelement 260 über dem fünften Gebiet 50, dem zweiten Gebiet 20 und dem dritten Gebiet 30 des Werkstücks 200 bildet. Jedes des vierten Datenspeicherelements 265, des zweiten Datenspeicherelements 255 und des dritten Datenspeicherelements 260 ist aus demselben zweiten MTJ-Stapel 2000 gebildet, der sich von dem ersten MTJ-Stapel 1000 unterscheidet. Verfahren 500 ist unten in Verbindung mit fragmentarischen Querschnittsansichten des Werkstücks 200 in Fig. 11-17 beschrieben. Verfahren 500 und Verfahren 100 können ähnliche Operationen teilen und eine wiederholte Beschreibung kann absichtlich fehlen oder der Knappheit wegen gekürzt sein.

**[0031]** Unter Bezugnahme auf **Fig.** 10 und **Fig.** 11 umfasst Verfahren 500 einen Block 502, wo ein Werkstück 200 empfangen wird. Operationen in Block 502 sind ähnlich jenen in Block 102. Daher wird auf eine ausführliche Beschreibung der Operationen in Block 502 verzichtet.

[0032] Unter Bezugnahme auf Fig. 10 und Fig. 11 umfasst Verfahren 500 einen Block 504, wo eine Pufferschicht 206 und eine zweite dielektrische Schicht 208 über dem Werkstück 200 sind. Operationen in Block 504 sind ähnlich jenen in Block 104. Daher wird auf eine ausführliche Beschreibung der Operationen in Block 504 verzichtet.

[0033] Unter Bezugnahme auf Fig. 10 und Fig. 11 umfasst Verfahren 500 einen Block 506, wo eine vierte Bodendurchkontaktierung 210-4, eine zweite Bodendurchkontaktierung 210-2 und eine dritte Bodendurchkontaktierung 210-3 über dem fünften Gebiet 50, dem zweiten Gebiet 20 beziehungsweise dem dritten Gebiet 30 gebildet sind. Operationen in Block 506 sind ähnlich jenen in Block 106. Daher wird

auf eine ausführliche Beschreibung der Operationen in Block 506 verzichtet. Es wird festgehalten, dass das Werkstück 200, das mit Verfahren 500 verbunden ist, ein fünftes Gebiet 50 anstelle des ersten Gebiets 10 aufweist. Diese Nomenklatur wird angewendet, um anzugeben, dass ein anderes Datenspeicherelement - ein viertes Datenspeicherelement 265 - über dem fünften Gebiet 50 gebildet ist. Ähnlich wird die vierte Bodendurchkontaktierung 210-4 verwendet, um eine Verknüpfung mit dem vierten Datenspeicherelement 265 anzugeben, auch wenn sie ähnli-Abmessungen wie die erste Bodendurchkontaktierung 210-1, die zweite Bodendurchkontaktierung 210-2 oder die dritte Bodendurchkontaktierung 210-3 aufweisen kann.

[0034] Unter Bezugnahme auf Fig. 10 und Fig. 11 umfasst Verfahren 500 einen Block 508, wo eine Bodenelektrodenschicht 212 über dem Werkstück 200 abgeschieden wird, enthaltend über der zweiten dielektrischen Schicht 208, der vierten Bodendurchkontaktierung 210-4, der zweiten Bodendurchkontaktierung 210-2 und der dritten Bodendurchkontaktierung 210-3. Operationen in Block 508 sind ähnlich jenen in Block 108. Daher wird auf eine ausführliche Beschreibung der Operationen in Block 508 verzichtet.

[0035] Unter Bezugnahme auf Fig. 10 und Fig. 11 umfasst Verfahren 500 einen Block 510, wo ein zweiter magnetischer Tunnelübergangsstapel (MTJ-Stapel) 2000 über der Bodenelektrodenschicht 212 abgeschieden ist. Der zweite MTJ-Stapel 2000 hat eine Stapelreihenfolge, die umgekehrt zu jener des ersten MTJ-Stapels 1000 ist. Wie in Fig. 11 gezeigt, weist der zweite MTJ-Stapel 2000 eine Abdeckschicht 222 über der Bodenelektrodenschicht 212, eine Wartungsschicht 220 über der Abdeckschicht 222, eine freie Schicht 218 über der Wartungsschicht 220, eine Tunnelsperrschicht 216 über der freien Schicht 218 und eine gepinnte Schicht 214 über der Tunnelsperrschicht 216 auf. Die gepinnte Schicht 214 kann ein ferromagnetisches Material wie Kobalteisen (CoFe), Kobalteisenbor (CoFeB) oder eine Kobalt-Platin-Legierung (Co-Pt-Legierung) enthalten. In manchen alternativen Ausführungsformen kann die gepinnte Schicht 214 CoFeTa, NiFe, Co, CoFe, CoPt, eine Legierung von Ni, Co und Fe, Platinmangan (PtMn), Iridiummangan (IrMn), Rhodiummangan (RhMn), Eisenmangan (FeMn) oder OsMn enthalten. Die Tunnelsperrschicht 216 kann aus einem Metalloxid gebildet sein, das ausgewählt ist aus einer Gruppe bestehend aus Magnesiumoxid (MgO), Titanoxid (TiO), Aluminiumtitanoxid (AlTiO), Magnesiumzinkoxid (MgZnO), Aluminiumoxid (AlO), Zinkoxid (ZnO), Zirconiumoxid (ZrO), Hafniumoxid (HfO) oder Magnesiumtantaloxid (MgTaO). In einer Ausführungsform ist die Tunnelsperrschicht 216 aus Magnesiumoxid gebildet. Die freie Schicht 218 ist aus einem ferromagnetischen Material gebildet und

kann Kobalteisenbor (CoFeB) enthalten. Die Wartungsschicht 220 kann aus einem Metalloxid gebildet sein, das ausgewählt ist aus einer Gruppe bestehend aus Magnesiumoxid (MgO), Titanoxid (TiO), Aluminiumtitanoxid (AITiO), Magnesiumzinkoxid (MgZnO), Aluminiumoxid (AlO), Zinkoxid (ZnO), Zirconiumoxid (ZrO), Hafniumoxid (HfO) oder Magnesiumtantaloxid (MgTaO). In einer Ausführungsform kann die Wartungsschicht 220 Magnesiumoxid enthalten. Die Abdeckschicht 222 kann optional sein und kann Molybdän (Mo) oder Ruthenium (Ru) enthalten. Die gepinnte Schicht 214, die Tunnelsperrschicht 216, die freie Schicht 218, die Wartungsschicht 220 und die Abdeckschicht 222 können jeweils unter Verwendung von PVD, CVD, Elektroplattieren, elektrolosem Plattieren oder einem geeigneten Verfahren abgeschieden werden. In manchen Ausführungsformen, die in den Figuren nicht ausdrücklich gezeigt sind, kann die Abdeckschicht 222 fehlen und der zweite MTJ-Stapel 2000 kann nur die gepinnte Schicht 214, die Tunnelsperrschicht 216, die Wartungsschicht 220 und die freie Schicht 218 enthalten.

[0036] Unter Bezugnahme auf Fig. 10 und Fig. 11 umfasst Verfahren 500 einen Block 512, wo eine Deckelektrodenschicht 224 über dem zweiten MTJ-Stapel 2000 abgeschieden ist. Operationen in Block 512 sind ähnlich jenen in Block 112. Daher wird auf eine ausführliche Beschreibung der Operationen in Block 512 verzichtet.

[0037] Unter Bezugnahme auf Fig. 10, Fig. 11 und Fig. 12 umfasst Verfahren 500 einen Block 514, wo die Deckelektrodenschicht 224, der zweite MTJ-Stapel 2000 und die Bodenelektrodenschicht 212 strukturiert sind, um ein viertes Datenspeicherelement 265 über dem fünften Gebiet 50, ein zweites Datenspeicherelement 255 über dem zweiten Gebiet 20 und ein drittes Datenspeicherelement 260 über dem dritten Gebiet 30 zu bilden. In Block 514 werden Fotolithografieprozesse und Ätzprozesse durchgeführt, um das vierte Datenspeicherelement 265, das zweite Datenspeicherelement 255 und das dritte Datenspeicherelement 260 zu bilden. In einem beispielhaften Prozess wird eine Hartmaskenschicht 226 über dem Werkstück 200 abgeschieden, enthaltend über der Deckelektrodenschicht 224. In manchen Ausführungsformen kann die Hartmaskenschicht 226 Siliziumoxid, Siliziumnitrid oder eine Kombination davon enthalten. In einer Ausführungsform wird die Hartmaskenschicht 226 aus Siliziumoxid (z.B. Tetraethylorthosilicatoxid (TEOS-Oxid)) gebildet und kann unter Verwendung von Schleuderbeschichtung oder fließfähiger CVD (FCVD) abgeschieden werden. Dann wird eine Fotolackschicht über der Hartmaskenschicht 226 abgeschieden. Die abgeschiedene Fotolackschicht wird dann mit einer strukturierten Strahlung belichtet, die durch eine Fotomaske geht oder von dieser reflektiert wird, in

einem Nachbelichtungsbackprozess gebacken, in einer Entwicklerlösung entwickelt und dann gespült, wodurch eine strukturierte Fotolackschicht gebildet wird. Wie in Fig. 11 gezeigt, wird die strukturierte Fotolackschicht dann als eine Ätzmaske aufgetragen, um die Hartmaskenschicht 226 zu ätzen, um eine vierte Hartmaskenstruktur 226-4 über dem ersten Gebiet 10, eine zweite Hartmaskenstruktur 226-2 über dem zweiten Gebiet 20 und eine dritte Hartmaskenstruktur 226-3 über dem dritten Gebiet 30 zu bilden. Diese strukturierten Hartmaskenstrukturen werden dann als eine Ätzmaske aufgebracht, um die Deckelektrodenschicht 224, den zweiten MTJ-Stapel 2000, die Bodenelektrodenschicht 212 und die zweite dielektrische Schicht 208 zu ätzen. Das Ätzen in Block 514 kann ein Ionenstrahlätzen (IBE) 300 umfassen. Was das Strukturieren von MTJ-Stapeln betrifft, kann IBE wünschenswerter sein als reaktives Ionenätzen (RIE), da IBE mit geringerer Wahrscheinlichkeit chemische Unreinheiten in den MTJ-Stapel einführt. Unreinheiten können Leistung des Datenspeicherelements verschlechtern. Das IBE 300 kann ein oder mehrere Edelgasionen wie Ar, Kr, Xe und Ne verwenden, die mit RF-Leistung oder Gleichstrom erzeugt werden. Es sollte klar sein, dass IBE typischerweise Drehen des Werkstücks 200 umfasst.

[0038] Zur Bildung von Speichervorrichtungen mit verschiedenen Vorrichtungseigenschaften weisen die Datenspeicherelemente verschiedene Abmessungen auf. Es wird beobachtet, dass bei einem identischen MTJ-Stapel ein Datenspeicherelement mit einer größeren freien Schicht bessere Wärmestabilität aufweist als ein Datenspeicherelement mit einer kleineren freien Schicht. Zusätzlich stellt ein Datenspeicherelement mit einer kleineren freien Schicht eine schnellere Ansprechzeit bereit als ein Datenspeicherelement mit einer größeren freien Schicht. In manchen Ausführungsformen, wo ein Datenspeicherelement eine kreisförmige Form bei Betrachtung entlang einer vertikalen Richtung aufweist, kann sich eine kritische Abmessung (CD) des Datenspeicherelements auf einen Durchmesser der freien Schicht beziehen. In manchen Ausführungsformen, dargestellt in Fig. 11, werden Hartmaskenstrukturen unterschiedlicher Abmessungen impleverschiedene mentiert. um Datenspeicherelementdurchmesser (oder Abmessungen) zu erreichen. Wie in Fig. 11 gezeigt, weist die vierte Hartmaskenstruktur 226-4 eine vierte Abmessung d4 auf, die zweite Hartmaskenstruktur 226-2 weist eine zweite Abmessung d2 auf und die dritte Hartmaskenstruktur 226-3 weist eine dritte Abmessung d3 auf. Die vierte Abmessung d4 ist größer als die zweite Abmessung d2 oder die dritte Abmessung d3. Die dritte Abmessung d3 ist größer als die zweite Abmessung d2.

[0039] Wie in Fig. 12 gezeigt, kann das IBE 300 zu verjüngten Seitenwänden führen, sodass jedes des vierten Datenspeicherelements 265, des zweiten Datenspeicherelements 255 und des dritten Datenspeicherelements 260 eine kleinere Deckelektrodenabmessung und eine größere Bodenelementabmessung hat. Das vierte Datenspeicherelement 265 weist die vierte Deckelektrode 224-4 auf, die aus der Deckelektrodenschicht 224 gebildet ist. Das zweite Datenspeicherelement 255 weist die zweite Deckelektrode 224-2 auf, die aus der Deckelektrodenschicht 224 gebildet ist. Das dritte Datenspeicherelement 260 weist die dritte Deckelektrode 224-3 auf, die aus der Deckelektrodenschicht 224 gebildet ist. In manchen Ausführungsformen kann das vierte Datenspeicherelement 265 durch eine vierte MTJ-Abmessung Dd gekennzeichnet sein, die im Wesentlichen ähnlich der Abmessung (oder dem Durchmesser) der freien Schicht 218 in dem vierten Datenspeicherelement 265 ist. Das zweite Datenspeicherelement 255 kann durch eine zweite MTJ-Abmessung D2 gekennzeichnet sein, die im Wesentlichen ähnlich der Abmessung (oder dem Durchmesser) der freien Schicht 218 in dem zweiten Datenspeicherelement 255 ist. Das dritte Datenspeicherelement 260 kann durch eine dritte MTJ-Abmessung D3 gekennzeichnet sein, die im Wesentlichen ähnlich der Abmessung (oder dem Durchmesser) der freien Schicht 218 in dem dritten Datenspeicherelement 260 ist. In manchen Implementierungen ist die vierte MTJ-Abmessung D4 größer als die zweite MTJ-Abmessung D2 oder die dritte MTJ-Abmessung D3. Die dritte MTJ-Abmessung D3 kann größer als die zweite MTJ-Abmessung D2 sein. In manchen Fällen kann die vierte MTJ-Abmessung D4 zwischen etwa 75 nm und etwa 100 nm sein, kann die zweite MTJ-Abmessung D2 zwischen etwa 20 nm und etwa 55 nm sein und kann die dritte MTJ-Abmessung D3 zwischen etwa 60 nm und etwa 85 nm sein.

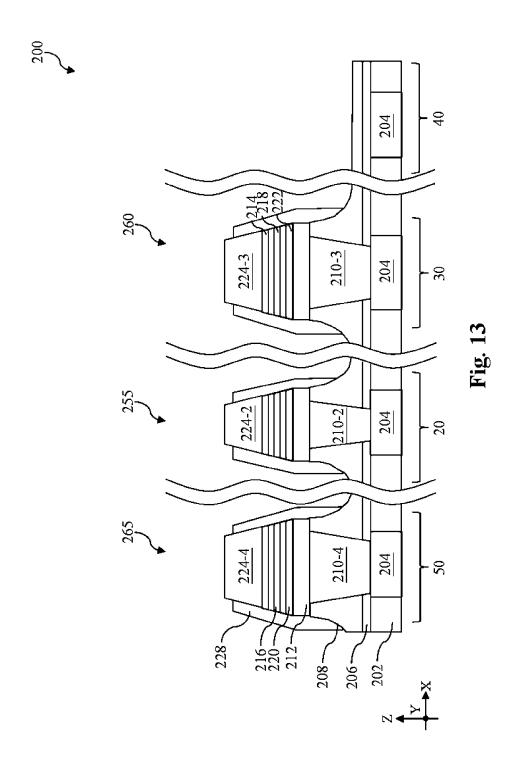

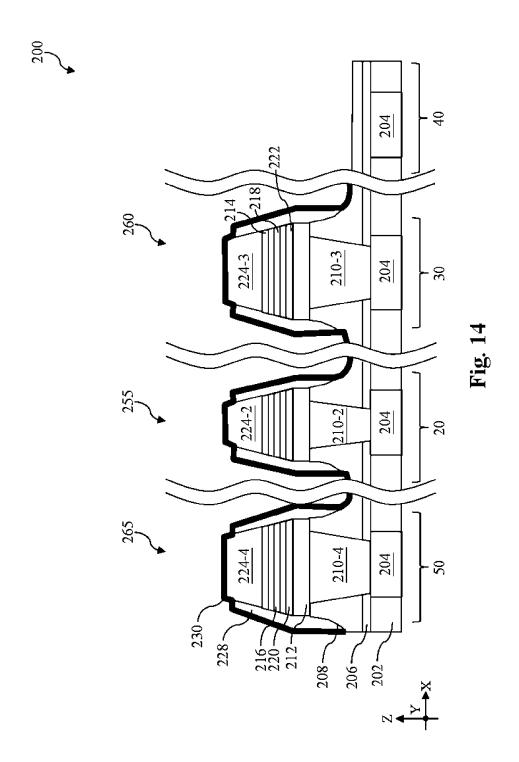

[0040] Unter Bezugnahme auf Fig. 10, Fig. 13, Fig. 14 und Fig. 15 umfasst Verfahren 500 einen Block 516, wobei eine Passivierungsstruktur über dem vierten Datenspeicherelement 265, dem zweiten Datenspeicherelement 255 und dem dritten Datenspeicherelement 260 gebildet wird. Die Passivierungsstruktur kann eine Abstandhalterschicht 228, die entlang Seitenwänden der Datenspeicherelemente angeordnet ists, eine Ätzstoppschicht (ESL) 230 über der Abstandhalterschicht 228 und eine dritte dielektrische Schicht 232 über der ESL 230 aufweisen. Obwohl nicht ausdrücklich in den Figuren gezeigt, können Operationen in Block 516 ein Vorhangabscheiden der Abstandhalterschicht 228, Rückätzen der Abstandhalterschicht 228, um die Abstandhalterschicht 228 auf nach oben weisenden Oberflächen (gezeigt in Fig. 13) zu entfernen, Abscheiden der ESL 230 über der Abstandhalterschicht 228 (gezeigt in Fig. 14) und Abscheiden der dritten dielektrischen Schicht 232 (gezeigt in Fig. 15) umfassen. In manchen Ausführungsformen kann die Abstandhalterschicht 228 Siliziumnitrid, Siliziumoxid oder ein geeignetes Material enthalten und kann unter Verwendung von CVD oder ALD abgeschieden werden. In einer Ausführungsform kann die Abstandhalterschicht 228 Siliziumnitrid enthalten. Die ESL 230 kann Aluminiumoxid oder ein Metalloxid enthalten, das ätzbeständiger als die Abstandhalterschicht 228 ist. Die ESL 230 kann unter Verwendung von CVD oder ALD abgeschieden werden. Die dritte dielektrische Schicht 232 kann Materialien wie Tetraethylorthosilicatoxid (TEOS-Oxid), undotiertes Silicatglas oder dotiertes Siliziumoxid wie Borphosphosilicatglas (BPSG), geschmolzenes (FSG), Phosphosilicatglas (PSG), bordotiertes Siliziumglas (BSG) und/oder andere geeignete dielektrische Materialien enthalten. In manchen Fällen kann die dritte dielektrische Schicht 232 unter Verwendung von Schleuderbeschichtung oder FCVD abgeschieden werden. Wie in Fig. 15 gezeigt, steht die Abstandhalterschicht 228 in physischem Kontakt mit der zweiten dielektrischen Schicht 208, Seitenwänden der Bodenelektroden 212, den gepinnten Schichten 214, der Tunnelsperrschicht 216, der freien Schicht 218, der Wartungsschicht 220 und der Abdeckschicht 222 der Datenspeicherelemente über dem vierten Gebiet 40, dem zweiten Gebiet 20 und dem dritten Gebiet 30. Die ESL 230 ist in physischem Kontakt mit der zweiten dielektrischen Schicht 208, der Abstandhalterschicht 228 und den Deckelektroden. In manchen Ausführungsformen, in Fig. 14 veranschaulicht, wird die ESL 230 nicht über dem vierten Gebiet 40 gebildet, da Vorhandensein der ESL 230 über dem vierten Gebiet 40 eine gute elektrische Verbindung mit dem leitfähigen Strukturelement 204 in dem vierten Gebiet 40 behindern kann.

[0041] Unter Bezugnahme auf Fig. 10, Fig. 16 und Fig. 17 umfasst Verfahren 500 einen Block 518, wobei weitere Prozesse durchgeführt werden. Solche weiteren Prozesse können Bilden einer sechsten Kontaktöffnung 235-6, einer zweiten Kontaktöffnung 235-2, einer dritten Kontaktöffnung 235-3, einer vierten Kontaktöffnung 235-4 und einer fünften Kontaktöffnung 235-5 (gezeigt in Fig. 16) und Abscheiden einer Metallfüllschicht in den Kontaktöffnungen umfassen, um weitere Kontaktstrukturelemente zu bilden (wie in Fig. 17 gezeigt). Fotolithografieprozesse und Ätzprozesse können verwendet werden, um die Kontaktöffnung zu bilden. In einem beispielhaften Prozess wird die fünfte Kontaktöffnung 235-5 über dem vierten Gebiet 40 gebildet, während das fünfte Gebiet 50, das zweite Gebiet 20 und das dritte Gebiet 30 durch einen Strukturierungsfilm, wie eine Fotolackschicht, eine Antireflexionsbodenschicht (BARC-Schicht) geschützt sind. Nach der Entfernung des Strukturierungsfilms werden die sechste Kontaktöffnung 235-6, die zweite Kontaktöffnung 235-2, die dritte Kontaktöffnung 235-3 und die fünfte Kontaktöffnung 235-5 durch die dritte dielektrische

Schicht 232, die ESL 230, die zweite dielektrische Schicht 208 und die Pufferschicht 206 unter Verwendung von Fotolithografieprozessen und Ätzprozessen gebildet, wie in Fig. 16 gezeigt. Das leitfähige Strukturelement 204 in dem vierten Gebiet 40 liegt in der vierten Kontaktöffnung 235-4 frei. Die sechste Kontaktöffnung 235-6 legt die vierte Deckelektrode 224-4 frei. Die zweite Kontaktöffnung 235-2 legt die zweite Deckelektrode 224-2 frei. Die dritte Kontaktöffnung 235-3 legt die dritte Deckelektrode 224-3 frei. Die vierte Kontaktöffnung 235-4 und die fünfte Kontaktöffnung 235-5 bilden gemeinsam eine Durchgangsöffnung in dem vierten Gebiet 40, da in dem vierten Gebiet 40 kein Datenspeicherelement vorhanden ist. Das Ätzen in Block 518 kann einen Trockenätzprozess umfassen, der Argon (Ar), ein fluorhaltiges Ätzmittel (zum Beispiel SF<sub>6</sub>, NF<sub>3</sub>, CH<sub>2</sub>F<sub>2</sub>, CHF<sub>3</sub>, C<sub>4</sub>F<sub>8</sub> und/oder C<sub>2</sub>F<sub>6</sub>), ein sauerstoffhaltiges Ätzmittel, ein chlorhaltiges Ätzmittel (zum Beispiel Cl<sub>2</sub>, CHCl<sub>3</sub>, CCl<sub>4</sub> und/oder BCl<sub>3</sub>), ein bromhaltiges Ätzmittel (zum Beispiel HBr und/oder CHBr<sub>3</sub>), ein iodhaltiges Ätzmittel oder Kombinationen davon verwendet.

[0042] Es wird dann auf Fig. 17 Bezug genommen. Eine Metallfüllschicht wird dann über den Kontaktöffnungen unter Verwendung von PVD, CVD, Elektroplattieren, oder elektrolosem Plattieren abgeschieden. Die Metallfüllschicht kann Ruthenium (Ru), Kupfer (Cu), Nickel (Ni), Kobalt (Co) oder Wolfram (W) enthalten. In einer Ausführungsform enthält die Metallfüllschicht Kupfer (Cu). Nach Abscheiden der Metallfüllschicht wird ein Planarisierungsprozess. wie ein CMP-Prozess, durchgeführt, um überschüssige Metallfüllschicht über der dritten dielektrischen Schicht 232 zu entfernen. Nach dem CMP-Prozess wird eine fünfte obere Kontaktdurchkontaktierung 236-5 über dem vierten Datenspeicherelement 265 gebildet, um an die vierte Deckelektrode 224-4 elektrisch zu koppeln; eine zweite obere Kontaktdurchkontaktierung 236-2 wird über dem zweiten Datenspeicherelement 255 gebildet, um an die zweite Deckelektrode 224-2 elektrisch zu koppeln; eine dritte obere Kontaktdurchkontaktierung 236-3 wird über dem dritten Datenspeicherelement 260 gebildet, um an die dritte Deckelektrode 224-3 elektrisch zu koppeln, und eine vierte obere Kontaktdurchkontaktierung 236-4 wird gebildet, um sich durch die dritte dielektrische Schicht 232, die zweite dielektrische Schicht 208 und die Pufferschicht 206 zu erstrecken, um an das leitfähige Strukturelement 204 in dem vierten Gebiet 40 zu koppeln. Obwohl nicht ausdrücklich gezeigt, kann eine Sperrschicht über den Kontaktöffnungen vor Abscheiden der Metallfüllschicht abgeschieden werden. Die Sperrschicht kann Titannitrid (TiN) oder Tantalnitrid (TaN) enthalten. Zusätzlich kann Verfahren 500 fortgesetzt werden, um weitere Metallschichten über dem Werkstück 200 zu bilden, wie in Fig. 17 gezeigt.

[0043] Fig. 18 ist eine schematische Draufsicht eines zweiten IC-Chips 600, der ein Prozessorgebiet 602, ein Reflow-MRAM-Gebiet 610, ein NvMRAM-Gebiet 606 und ein OTP MRAM-Gebiet 608 aufweist. Das Prozessorgebiet 602 kann Kerntransistoren auf der FEOL-Ebene aufweisen, um eine zentrale Verarbeitungseinheit (CPU) zu bilden. Das Reflow-MRAM-Gebiet 610 kann dem fünften Gebiet 50 entsprechen und kann die vierten Datenspeicherelemente 265 auf der BEOL-Ebene aufweisen. Das NvMRAM-Gebiet 606 kann dem zweiten Gebiet 20 entsprechen und kann die zweiten Datenspeicherelemente 255 auf der BEOL-Ebene aufweisen. Das OTP MRAM-Gebiet 608 kann dem dritten Gebiet 30 entsprechen und kann das dritte Datenspeicherelement 260 auf der BEOL-Ebene aufweisen. Wie zuvor beschrieben können die Datenspeicherelemente in dem Reflow MRAM-Gebiet 610, dem NvMRAM-Gebiet 606 und dem OTP MRAM-Gebiet 608 denselben zweiten MTJ-Stapel 2000 aufweisen und können gleichzeitig gebildet werden. Der zweite IC-Chip 600 ist für Mikrosteuereinheitsanwendungen (MCU-Anwendungen, Micro-Controller Unit) geeignet, da er eingerichtet ist, gute Wärmestabilität aufzuweisen und einen Speicher für lange Zeit beizubehalten. Kurze Ansprechzeit ist für die MCU-Anwendungen von geringerer Bedeutung. Da Wärmestabilität in dem zweiten IC-Chip 600 gesucht wird, kann die freie Schicht 218 in dem zweiten MTJ-Stapel 2000 an der dickeren Seite des Spektrums sein. In manchen Fällen kann die freie Schicht 218 in dem zweiten MTJ-Stapel 2000 zwischen etwa 2,0 nm und etwa 3,5 nm sein.

[0044] In einem beispielhaften Aspekt betrifft die vorliegende Offenbarung eine Halbleitervorrichtung. Die Halbleitervorrichtung weist ein erstes leitfähiges Strukturelement und ein zweites leitfähiges Strukturelement auf, die in einer ersten dielektrischen Schicht angeordnet sind, eine Pufferschicht, die über der ersten dielektrischen Schicht angeordnet ist, eine zweite dielektrische Schicht, die über der Pufferschicht angeordnet ist, eine erste Bodendurchkontaktierung, die sich durch die Pufferschicht und die zweite dielektrische Schicht entlang einer ersten Richtung erstreckt, um an das erste leitfähige Strukturelement zu koppeln, eine zweite Bodendurchkontaktierung, die sich durch die Pufferschicht und die zweite dielektrische Schicht entlang der ersten Richtung erstreckt, um an das zweite leitfähige Strukturelement zu koppeln, eine erste Bodenelektrode, die auf der ersten Bodendurchkontaktierung angeordnet ist, eine zweite Bodenelektrode, die auf der zweiten Bodendurchkontaktierung angeordnet ist, einen ersten magnetischen Tunnelübergangsstapel (MTJ-Stapel) über der ersten Bodenelektrode und einen zweiten MTJ-Stapel über der zweiten Bodenelektrode. Der erste MTJ-Stapel und der zweite MTJ-Stapel weisen eine selbe Dicke entlang der ersten Richtung auf. Der erste MTJ-Stapel weist eine erste Breite entlang einer zweiten Richtung senkrecht zu der ersten Richtung auf und der zweite MTJ-Stapel weist eine zweite Breite entlang der zweiten Richtung auf. Die zweite Breite ist größer als die erste Breite.

[0045] In manchen Ausführungsformen weist der erste MTJ-Stapel eine gepinnte Schicht über der ersten Bodenelektrode, eine Tunnelsperrschicht über der gepinnten Schicht und eine freie Schicht über der Tunnelsperrschicht auf. In manchen Ausführungsformen enthält die gepinnte Schicht Kobalt, Eisen, Bor oder Platin, enthält die Tunnelsperrschicht Magnesiumoxid und enthält die freie Schicht Kobalt, Eisen oder Bor. In manchen Fällen weist der erste MTJ-Stapel weiter eine Wartungsschicht über der freien Schicht und eine Abdeckschicht über der Wartungsschicht auf. In manchen Implementierungen enthält die Wartungsschicht Magnesiumoxid und die Abdeckschicht enthält Molybdän oder Ruthenium. In manchen Ausführungsformen ist die erste Breite zwischen etwa 20 nm und etwa 55 nm und die zweite Breite ist zwischen etwa 75 nm und etwa 100 nm. In manchen Ausführungsformen enthält die Pufferschicht Siliziumcarbid. In manchen Ausführungsformen enthält die erste dielektrische Schicht siliziumreiches Siliziumoxid.

[0046] In einem anderen beispielhaften Aspekt betrifft die vorliegende Offenbarung eine Halbleitervorrichtung. Die Halbleitervorrichtung weist eine erste Speicherstruktur und eine zweite Speicherstruktur auf. Die erste Speicherstruktur weist eine erste Bodenelektrode, eine erste Deckelektrode über der ersten Bodenelektrode und einen ersten magnetischen Tunnelübergangsstapel (MTJ-Stapel), der zwischen der ersten Bodenelektrode und der ersten Deckelektrode liegt, entlang einer ersten Richtung auf. Die zweite Speicherstruktur weist eine zweite Bodenelektrode, eine zweite Deckelektrode über der zweiten Bodenelektrode und einen zweiten MTJ-Stapel, der zwischen der ersten Bodenelektrode und der ersten Deckelektrode liegt, entlang der ersten Richtung auf. Der erste MTJ-Stapel weist eine erste Breite entlang einer zweiten Richtung senkrecht zu der ersten Richtung auf und der zweite MTJ-Stapel weist eine zweite Breite entlang der zweiten Richtung auf. Die zweite Breite ist größer als die erste Breite.

[0047] In manchen Ausführungsformen weisen der erste MTJ-Stapel und der zweite MTJ-Stapel eine selbe Dicke entlang der ersten Richtung auf. In manchen Implementierungen enthalten die erste Bodenelektrode, die erste Deckelektrode, die zweite Bodenelektrode und die zweite Deckelektrode Titannitrid, Tantalnitrid, oder eine Kombination davon. In manchen Ausführungsformen enthält der erste MTJ-Stapel eine Abdeckschicht über der ersten Bodenelektrode, eine Wartungsschicht über der Abdeckschicht, eine freie Schicht über der Wartungs-

schicht, eine Tunnelsperrschicht über der freien Schicht und eine gepinnte Schicht über der Tunnelsperrschicht. In manchen Ausführungsformen enthält die Abdeckschicht Molybdän oder Ruthenium, die Wartungsschicht enthält Magnesiumoxid, die freie Schicht enthält Kobalt, Eisen oder Bor, die Tunnelsperrschicht enthält Magnesiumoxid und die gepinnte Schicht enthält Kobalt, Eisen, Bor oder Platin. In manchen Fällen weist die Halbleitervorrichtung weiter eine dritte Speicherstruktur auf, die eine dritte Bodenelektrode und eine dritte Deckelektrode über der dritten Bodenelektrode aufweist. Die Halbleitervorrichtung weist auch einen eine dritten (MTJ-) Stapel, der zwischen der dritten Bodenelektrode und der dritten Deckelektrode liegt, entlang der ersten Richtung auf. Der dritte MTJ-Stapel weist eine dritte Breite entlang der zweiten Richtung auf. Die dritte Breite ist größer als die erste Breite. In manchen Ausführungsformen ist die erste Breite zwischen etwa 20 nm und etwa 55 nm, ist die zweite Breite zwischen etwa 80 nm und etwa 100 nm und ist die dritte Breite zwischen etwa 75 nm und etwa 100 nm.

[0048] In einem weiteren beispielhaften Aspekt betrifft die vorliegende Offenbarung ein Verfahren. Das Verfahren umfasst Empfangen eines Werkstücks, das ein erstes leitfähiges Strukturelement und ein zweites leitfähiges Strukturelement, die in einer ersten dielektrischen Schicht angeordnet sind, eine zweite dielektrische Schicht über der ersten dielektrischen Schicht, eine erste Bodendurchkontaktierung, die sich durch die zweite dielektrische Schicht entlang einer ersten Richtung erstreckt, um an das erste leitfähige Strukturelement zu koppeln, und eine zweite Bodendurchkontaktierung, die sich durch die zweite dielektrische Schicht entlang der ersten Richtung erstreckt, um an das zweite leitfähige Strukturelement zu koppeln, auf. Das Verfahren umfasst weiter Abscheiden einer Bodenelektrodenschicht über der ersten Bodendurchkontaktierung, der zweiten Bodendurchkontaktierung und der zweiten dielektrischen Schicht, Abscheiden eines magnetischen Tunnelübergangsstapels (MTJ-Stapel) über der Bodenelektrodenschicht. Abscheiden einer Deckelektrodenschicht über dem MTJ-Stapel. Abscheiden einer Hartmaskenschicht über der Deckelektrodenschicht. Strukturieren der Hartmaskenschicht, um eine erste Hartmaskenstruktur direkt über der ersten Bodendurchkontaktierung und eine zweite Hartmaskenstruktur direkt über der zweiten Bodendurchkontaktierung zu bilden, und Ätzen der Deckelektrodenschicht, des MTJ-Stapels und der Bodenelektrodenschicht unter Verwendung der ersten Hartmaskenstruktur und der zweiten Hartmaskenstruktur als eine Ätzmaske, um eine erste Speicherstruktur direkt über der ersten Bodendurchkontaktierung und eine zweite Speicherstruktur direkt über der zweiten Bodendurchkontaktierung zu bilden. Die erste Hartmaskenstruktur weist eine erste Breite entlang einer zweiten Richtung senkrecht zu der ersten Richtung auf und die zweite Hartmaskenstruktur weist eine zweite Breite entlang der zweiten Richtung auf. Die zweite Breite ist größer als die erste Breite.

[0049] In manchen Ausführungsformen umfasst das Ätzen Verwendung von Ionenstrahlätzen (IBE). In manchen Fällen weist die erste Speicherstruktur eine erste Bodenelektrode, die aus der Bodenelektrodenschicht gebildet ist, auf, die zweite Speicherstruktur weist eine zweite Bodenelektrode, die aus der Bodenelektrodenschicht gebildet ist, auf, die erste Bodenelektrode weist eine dritte Breite entlang der zweiten Richtung auf und die zweite Bodenelektrode weist eine vierte Breite entlang der zweiten Richtung auf. Die vierte Breite ist größer als die dritte Breite. In manchen Ausführungsformen kann das Verfahren weiter nach dem Ätzen Abscheiden einer Abstandhalterschicht über der ersten Speicherstruktur und der zweiten Speicherstruktur, Rückätzen der Abstandhalterschicht, nach dem Rückätzen Abscheiden einer Ätzstoppschicht über der Abstandhalterschicht, der ersten Speicherstruktur und der zweiten Speicherstruktur und Abscheiden einer dritten dielektrischen Schicht über der Ätzstoppschicht umfassen. In manchen Ausführungsformen enthält die Ätzstoppschicht Aluminiumoxid.

[0050] Zuvor wurden Merkmale mehrerer Ausführungsformen dargelegt, sodass ein Durchschnittsfachmann die Aspekte der vorliegenden Offenbarung besser verstehen kann. Durchschnittsfachleute sollten begrüßen, dass sie die vorliegende Offenbarung leicht als Grundlage zum Entwerfen oder Modifizieren anderer Prozesse und Strukturen verwenden können, um dieselben Zwecke auszuführen und/oder dieselben Vorteile der hier vorgestellten Ausführungsformen zu erreichen. Durchschnittsfachleute sollten auch gleichwertige Konstruktionen erkennen, die nicht vom Wesen und Umfang der vorliegenden Offenbarung abweichen, und dass sie verschiedene Änderungen, Ersetzungen und Abänderungen hier vornehmen können, ohne vom Wesen und Umfang der vorliegenden Offenbarung abzuweichen.

# DE 10 2023 107 574 A1 2023.11.16

# ZITATE ENTHALTEN IN DER BESCHREIBUNG

Diese Liste der vom Anmelder aufgeführten Dokumente wurde automatisiert erzeugt und ist ausschließlich zur besseren Information des Lesers aufgenommen. Die Liste ist nicht Bestandteil der deutschen Patent- bzw. Gebrauchsmusteranmeldung. Das DPMA übernimmt keinerlei Haftung für etwaige Fehler oder Auslassungen.

## **Zitierte Patentliteratur**

- US 63/341840 [0001]

### Patentansprüche

1. Halbleitervorrichtung, aufweisend:

ein erstes leitfähiges Strukturelement und ein zweites leitfähiges Strukturelement, die in einer ersten dielektrischen Schicht angeordnet sind;

eine Pufferschicht, die über der ersten dielektrischen Schicht angeordnet ist;

eine zweite dielektrische Schicht, die über der Pufferschicht angeordnet ist;

eine erste Bodendurchkontaktierung, die sich durch die Pufferschicht und die zweite dielektrische Schicht entlang einer ersten Richtung erstreckt, um an das erste leitfähige Strukturelement zu koppeln; eine zweite Bodendurchkontaktierung, die sich durch die Pufferschicht und die zweite dielektrische Schicht entlang der ersten Richtung erstreckt, um an das zweite leitfähige Strukturelement zu koppeln; eine erste Bodenelektrode, die auf der ersten Bodendurchkontaktierung angeordnet ist;

eine zweite Bodenelektrode, die auf der zweiten Bodendurchkontaktierung angeordnet ist;

einen ersten magnetischen Tunnelübergangsstapel (MTJ-Stapel) über der ersten Bodenelektrode; und einen zweiten MTJ-Stapel über der zweiten Bodenelektrode,

wobei der erste MTJ-Stapel und der zweite MTJ-Stapel eine selbe Dicke entlang der ersten Richtung aufweisen.

wobei der erste MTJ-Stapel eine erste Breite entlang einer zweiten Richtung senkrecht zu der ersten Richtung aufweist und der zweite MTJ-Stapel eine zweite Breite entlang der zweiten Richtung aufweist, wobei die zweite Breite größer als die erste Breite ist.

2. Halbleitervorrichtung nach Anspruch 1, wobei der erste MTJ-Stapel aufweist:

eine gepinnte Schicht über der ersten Bodenelektrode;

eine Tunnelsperrschicht über der gepinnten Schicht; und

eine freie Schicht über der Tunnelsperrschicht.

3. Halbleitervorrichtung nach Anspruch 2, wobei die gepinnte Schicht Kobalt, Eisen, Bor oder Platin enthält,

wobei die Tunnelsperrschicht Magnesiumoxid enthält,

wobei die freie Schicht Kobalt, Eisen oder Bor enthält.

- 4. Halbleitervorrichtung nach Anspruch 2, wobei der erste MTJ-Stapel weiter aufweist: eine Wartungsschicht über der freien Schicht; und eine Abdeckschicht über der Wartungsschicht.

- 5. Halbleitervorrichtung nach Anspruch 4, wobei die Wartungsschicht Magnesiumoxid enthält,

wobei die Abdeckschicht Molybdän oder Ruthenium enthält.

6. Halbleitervorrichtung nach einem der vorstehenden Ansprüche,