#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2013/119846 A2

(43) International Publication Date 15 August 2013 (15.08.2013)

(51) International Patent Classification: *G11C 11/16* (2006.01)

(21) International Application Number:

PCT/US2013/025191

(22) International Filing Date:

7 February 2013 (07.02.2013)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/595,815 7 February 2012 (07.02.2012) US 13/586,934 16 August 2012 (16.08.2012) US

- (71) Applicant: QUALCOMM INCORPORATED [US/US]; Attn: International Ip Administration, 5775 Morehouse Drive, San Diego, California 92121 (US).

- (72) Inventors: LI, Xia; 5775 Morehouse Drive, San Diego, California 92121 (US). WU, Wenqing; 5775 Morehouse Drive, San Diego, California 92121 (US). KIM, Jung Pill; 5775 Morehouse Drive, San Diego, California 92121 (US). ZHU, Xiaochun; 5775 Morehouse Drive, San Diego, Cali-

fornia 92121 (US). **KANG, Seung H.**; 5775 Morehouse Drive, San Diego, California 92121 (US). **MADALA, Raghu Sagar**; 5775 Morehouse Drive, San Diego, California 92121 (US). **YUEN, Kendrick H.**; 5775 Morehouse Drive, San Diego, California 92121 (US).

- (74) Agent: TALPALATSKY, Sam; 5775 Morehouse Drive, San Diego, California 92121 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH,

[Continued on next page]

(54) Title: MULTI-FREE LAYER MTJ AND MULTI-TERMINAL READ CIRCUIT WITH CONCURRENT AND DIFFERENTIAL SENSING

(57) Abstract: A multi-free layer magnetic tunnel junction (MTJ) cell includes a bottom electrode layer, an antiferromagnetic layer on the bottom electrode layer, a fixed magnetization layer on the antiferromagnetic layer and a barrier layer on the fixed magnetization layer. A first free magnetization layer is on a first area of the barrier layer, and a capping layer is on the first free magnetization layer. A free magnetization layer is on a second area of the barrier layer, laterally displaced from the first area, and a capping layer is on the second free magnetization layer. Optionally current switches establish a read current path including the first free magnetization layer concurrent with not establishing a read current path including the second free magnetization layer. Optionally current switches establishing a read current path including the first and second free magnetization layer.

#

GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

## Published:

without international search report and to be republished upon receipt of that report (Rule 48.2(g))

#### **Declarations under Rule 4.17:**

as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

1

# MULTI-FREE LAYER MTJ AND MULTI-TERMINAL READ CIRCUIT WITH CONCURRENT AND DIFFERENTIAL SENSING

# Claim of Priority under 35 U.S.C. §119

[0001] The present Application for Patent claims priority to Provisional Application No. 61/595,815 entitled "Novel Multi-Free Layer MTJ Structures for Multi-Bits/Levels and for Differential Sensing," filed February 7, 2012, and assigned to the assignee hereof and hereby expressly incorporated by reference herein.

#### Field of Disclosure

[0002] The technical field of the disclosure relates to bi-stable resistive element non-volatile memory and, more specifically, to spin torque transfer (STT) magnetic tunnel junction (MTJ) memory cells.

## **Background**

- [0003] STT-MTJ is considered a promising technology for next generation non-volatile memory, as potential features include fast switching, high switching cycle endurance, low power consumption, and extended unpowered archival storage.

- [0004] A conventional STT-MTJ element includes a "fixed" magnetization layer having, as its name indicates, a fixed magnetization and a "free" magnetization layer that is switchable between two mutually opposite, stable magnetization states one being "parallel" (P) to the magnetization of the fixed layer, and the other being opposite, or anti-parallel" (AP), to the fixed magnetic layer. The electrical resistance of a given STT-MTJ element is lower when in its P state than when its AP state. The magnetization state of an STT-MTJ element can therefore be read by detecting its resistance. By assigning one of the P and AP states to represent a first binary value, e.g., a "0", and the other to represent a second binary value, e.g., a "1" the STT-MTJ element can be a binary, i.e., one-bit storage.

- [0005] The conventional STT-MTJ element, more particularly the free magnetization layer of the STT-MTJ element, can be selectively switched between the P and AP states, and visa versa, by

2

passing an electric "write" current through its free and fixed magnetization layers. Provided the write current is above a given critical point (CPT), the STT-MTJ will switch into the P or AP state, with the selection of which states dependent on the direction of the write current. The STT-MTJ element is read by passing a "read" or "sense" current through the device, having a controlled, repeatable amplitude and, since V = IR, a sense or read voltage that is developed indicates whether the STT-MTJ element is in the P or AP state, i.e., whether the STT-MTJ element is storing a "1" or a "0."

[0006] Needs in STT-MTJ memory include lower bit error rate, lower power, and increased storage density, e.g., bits per unit area or volume.

## **SUMMARY**

- [0007] MTJ memory cells according to various exemplary embodiments can provide, among other features and benefits, multiple free layers arranged in a three-terminal configuration, forming multiple tunnel barriers that, in an aspect, can be individually programmed to selected magnetization states and, according to various aspects, concurrently or individually read.

- [0008] Example multi-free layer MTJ memory cells according to one or more exemplary embodiments can have a bottom electrode layer, an anti-ferromagnetic (AFM) layer on the bottom electrode layer, a fixed magnetization layer on the anti-ferromagnetic layer, a barrier layer on the fixed magnetization layer, a first free magnetization layer on a first area of the barrier layer, a second free magnetization layer on a second area of the barrier layer, laterally displaced from the first area, a first top electrode coupled to the first free magnetization layer and a second top electrode coupled to the second free magnetization layer, a first current switch for switchably coupling the first top electrode to a first MTJ read/write terminal, a second current switch for switchably coupling the second top electrode to a second MTJ read/write terminal; and a third MTJ read/write terminal coupled to the bottom electrode layer.

- [0009] In an aspect, example multi-free layer MTJ cells according to one or more exemplary embodiments can further include a read current switch control coupled to the first current switch, the second current switch, configured to switch the first current switch and the second current switch to a read mode, wherein the read mode couples the first top electrode to the first MTJ

3

read/write terminal and, concurrently, couples the second top electrode to the second MTJ read/write terminal.

- [0010] Example multi-free layer MTJ cells, in an aspect according to one more exemplary embodiments, can be configured to establish in the read mode a read current path between the first MTJ read/write terminal and the second MTJ read/write terminal. In a related aspect, the read current path can include the first free magnetization layer in series with the second free magnetization layer.

- [0011] Example multi-free layer MTJ cell according to another aspect of one or more exemplary embodiments can be configured to provide a read current path that further includes the fixed magnetization layer between an interface of the fixed magnetization layer with the barrier layer under the first area and an interface of the fixed magnetization layer with the barrier layer under the second area.

- [0012] Multi-free layer MTJ cells according to one or more embodiments can include a bottom electrode layer, an AFM layer on the bottom electrode layer, a fixed magnetization layer on the AFM layer, a first pillar supported on a first area of the fixed magnetization layer, the first pillar having a first barrier layer forming a base on the first area of the fixed magnetization layer, a first free magnetization layer on the first barrier layer, and a first MTJ terminal coupled to the first free magnetization layer, a second pillar supported on a second area of the barrier layer, laterally displaced from the first area, having a second barrier layer forming a base supported on the second area of the fixed magnetization layer, a second free magnetization layer on the second barrier layer, a second capping layer on the second free magnetization layer, and a second MTJ terminal coupled to the second capping layer; and a third MTJ terminal coupled to the bottom electrode layer.

- [0013] Example methods according to one or more exemplary embodiments can include injecting a first write current from one of a first MTJ terminal and a base MTJ terminal to the other of the first MTJ terminal and the base MTJ terminal, the first write current passing through a first free magnetization layer, and injecting a second write current from one of a second MTJ terminal and the base MTJ terminal to the other of the second MTJ terminal and the base MTJ terminal, the second write current passing through a second free magnetization layer, detecting an electrical resistance of the first free magnetization layer, and detecting an electrical series electrical

4

resistance of the first free magnetization layer in series with the second free magnetization layer. In an aspect, methods according to one or more exemplary embodiments can include detecting an electrical resistance of the second free magnetization layer based on a result of the detecting the electrical resistance of the first free magnetization layer and a result of the detecting the series electrical resistance of the first free magnetization layer in series with the second free magnetization layer.

- [0014] Methods according to one or more exemplary embodiments can, in one or more aspects, include detecting the electrical resistance of the first free magnetization layer by injecting a first read current from one of the first MTJ terminal and the base MTJ terminal to a current sink coupling to the other of the first MTJ terminal and the base MTJ terminal, the first read current passing through the first free magnetization layer, and can perform detecting the series electrical resistance of the first free magnetization layer in series with the second free magnetization layer by injecting a second read current from one of the first MTJ terminal and the second MTJ terminal to a current sink coupled to the other of the first MTJ terminal and the second MTJ terminal, the second read current passing through the first free magnetization layer and passing through the second free magnetization layer.

- [0015] Methods according to one or more exemplary embodiments can provide an MTJ memory storage of a multi-bit data, and can include storing a first bit by injecting a first write current, based on the first bit, from one of a first MTJ terminal and a base MTJ terminal to the other of the first MTJ terminal and the base MTJ terminal, the first write current passing through a first free magnetization layer to place the first free magnetization layer in a state indicating the first bit, and storing a second bit by injecting a second write current, based on the second bit, from one of a second MTJ terminal and the base MTJ terminal to the other of the second MTJ terminal and the base MTJ terminal, the second write current passing through a second free magnetization layer to place the second free magnetization layer in a state indicating the second bit.

- [0016] Methods according to one or more exemplary embodiments include reading the first bit by injecting a first read current from one of the first MTJ terminal and the base MTJ terminal to a current sink coupled to the other of the first MTJ terminal and the base MTJ terminal, the first read current passing through the first free magnetization layer to form a first bit sense voltage, and detecting the first bit by comparing the first bit sense voltage to a first bit threshold, and

reading the second bit by forming a second bit sense voltage indicative of a combination of the magnetization state of the first free magnetization layer and the magnetization state of the second free magnetization layer, by injecting second read current from one of the first MTJ terminal and the second MTJ terminal to a current sink coupled to the other of the first MTJ terminal and the second MTJ terminal, the second read current passing through the first free magnetization layer and passing through the second free magnetization layer, and detecting the second bit by comparing a result of the of forming the second bit sense voltage to a second bit threshold.

- [0017] Example MTJ memory apparatus according to one embodiment can include means for injecting a first write current from one of a first MTJ terminal and a base MTJ terminal to the other of the first MTJ terminal and the base MTJ terminal, the first write current passing through a first free magnetization layer, and means for injecting a second write current from one of a second MTJ terminal and the base MTJ terminal to the other of the second MTJ terminal and the base MTJ terminal, the second write current passing through a second free magnetization layer.

- [0018] Example methods for MTJ memory according to one exemplary embodiment can include step of injecting a first write current from one of a first MTJ terminal and a base MTJ terminal to the other of the first MTJ terminal and the base MTJ terminal, the first write current passing through a first free magnetization layer; step of injecting a second write current from one of a second MTJ terminal and the base MTJ terminal to the other of the second MTJ terminal and the base MTJ terminal, the second write current passing through a second free magnetization layer, step of detecting an electrical resistance of the first free magnetization layer, and step of detecting an electrical series electrical resistance of the first free magnetization layer in series with the second free magnetization layer.

## BRIEF DESCRIPTION OF THE DRAWINGS

- [0019] The accompanying drawings found in the attachments are presented to aid in the description of embodiments of the invention and are provided solely for illustration of the embodiments and not limitation thereof.

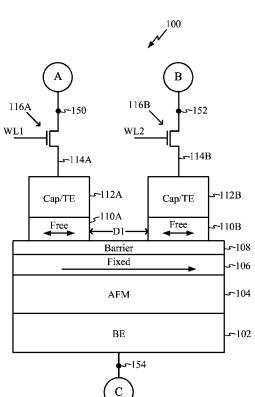

- [0020] FIG. 1 shows one multi-terminal, multi-free layer MTJ structure according to one exemplary embodiment.

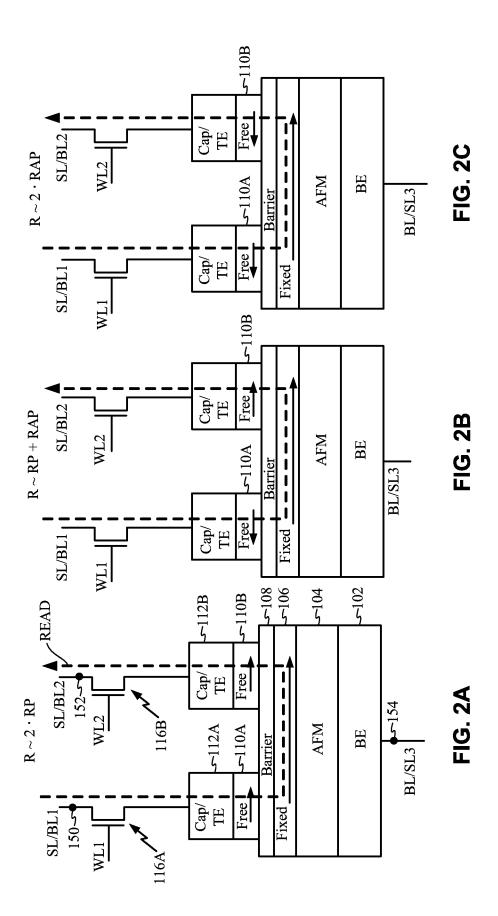

- [0021] FIGS. 2A, 2B, and 2C show a two terminal resistance aspect of the FIG. 1 multi-terminal, multi-free layer MTJ structure according to one exemplary embodiment at, respectively, each of a first, second, and third set of magnetization states for storage processes according to various exemplary embodiments.

- [0022] FIGS. 3A and 3B show example write current flows for writing, respectively, a first free magnetization layer and a second free magnetization layer of the FIG. 1 multiple terminal, multifree layer MTJ structure, in a method according to one exemplary embodiment.

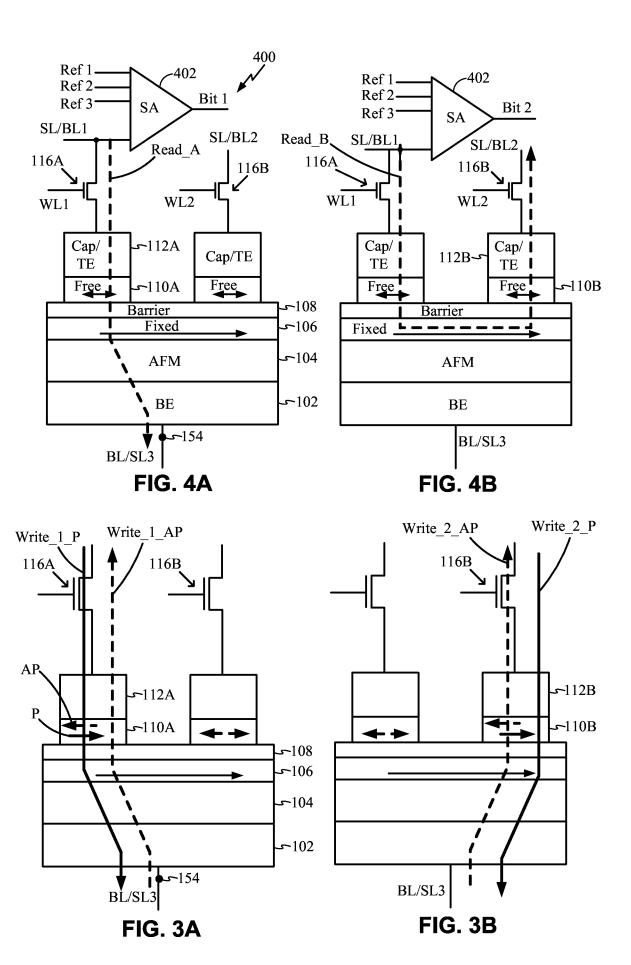

- [0023] FIGS. 4A and 4B show, respectively, one individual free magnetization layer read phase and one multi-free layer read phase of a two-phase, three-terminal multi-level read circuit in accordance with one exemplary embodiment.

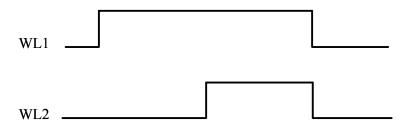

- [0024] FIG. 5 shows one example read enable control signal waveform for controlling two-phase, three terminal multi-level read circuits in accordance with various exemplary embodiments.

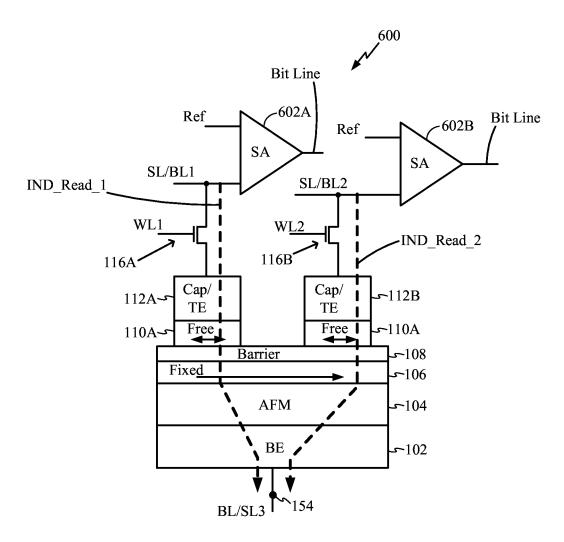

- [0025] FIG. 6 shows one shows one example multi-free layer, individually readable free magnetization layer MTJ cell according to one three-terminal read aspect.

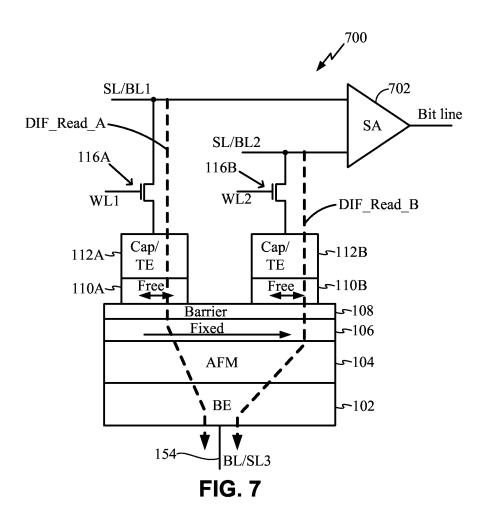

- [0026] FIG. 7 shows one example multi-free layer, three-terminal differential read MTJ cell according to one exemplary embodiment.

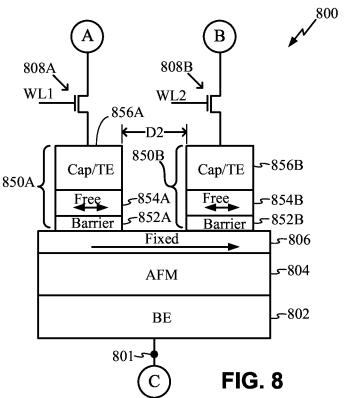

- [0027] FIG. 8 shows one multi-free layer, separate barrier layer MTJ structure according to another exemplary embodiment.

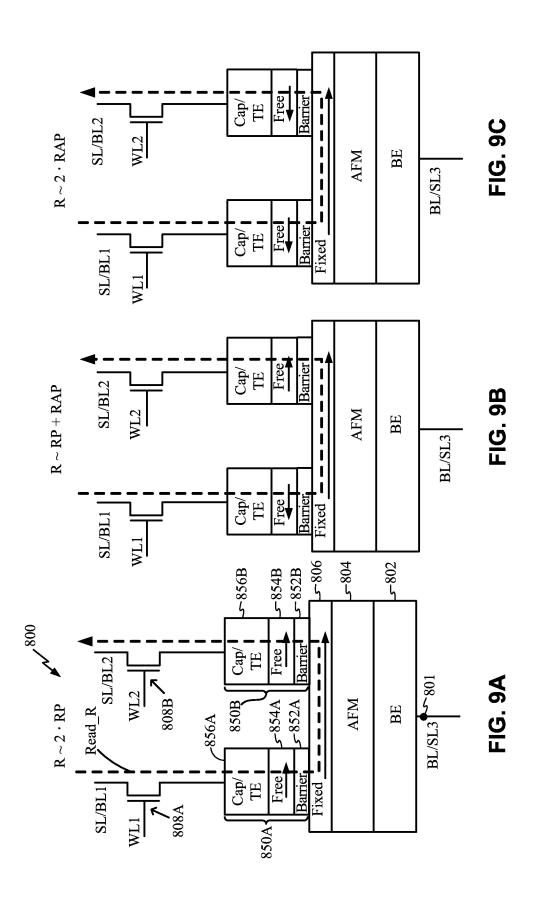

- [0028] FIGS. 9A, 9B, and 9C a two terminal resistance aspect of the FIG. 8 MTJ structure according to one exemplary embodiment at, respectively, each of a first, second, and third set of magnetization states for storage processes according to various exemplary embodiments.

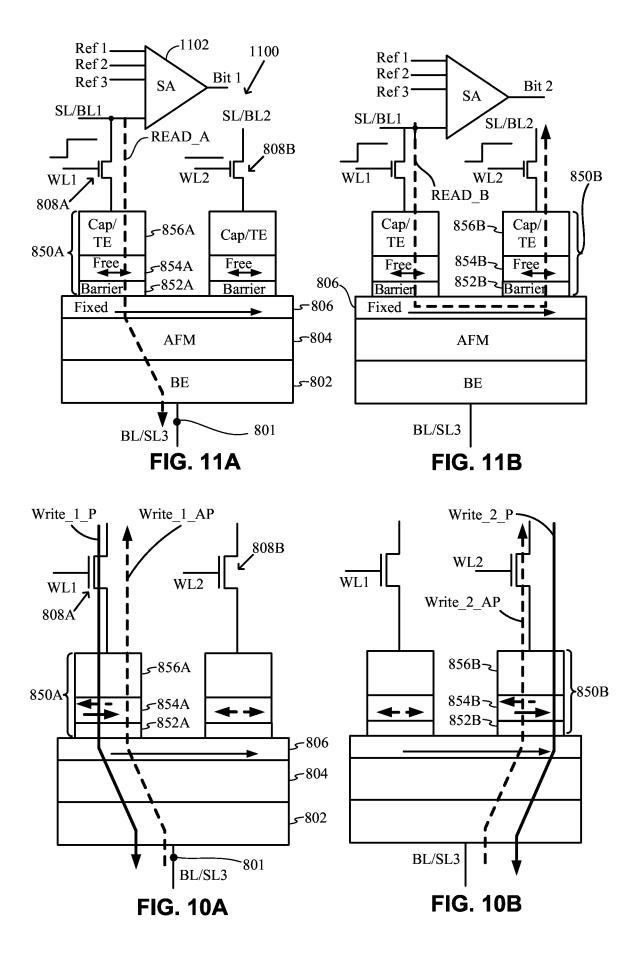

- [0029] FIGS. 10A and 10B show example write current flows for writing, respectively, a first free magnetization layer and a second free magnetization layer according to a three-terminal aspect of the FIG. 8 MTJ structure according to one exemplary embodiment.

- [0030] FIGS. 11A and 11B show, respectively, one individual free magnetization layer read phase and one multi-free layer read phase in one multi-step, three terminal read aspect in relation to the FIG. 8 multi-free layer MTJ structure according to one exemplary embodiment.

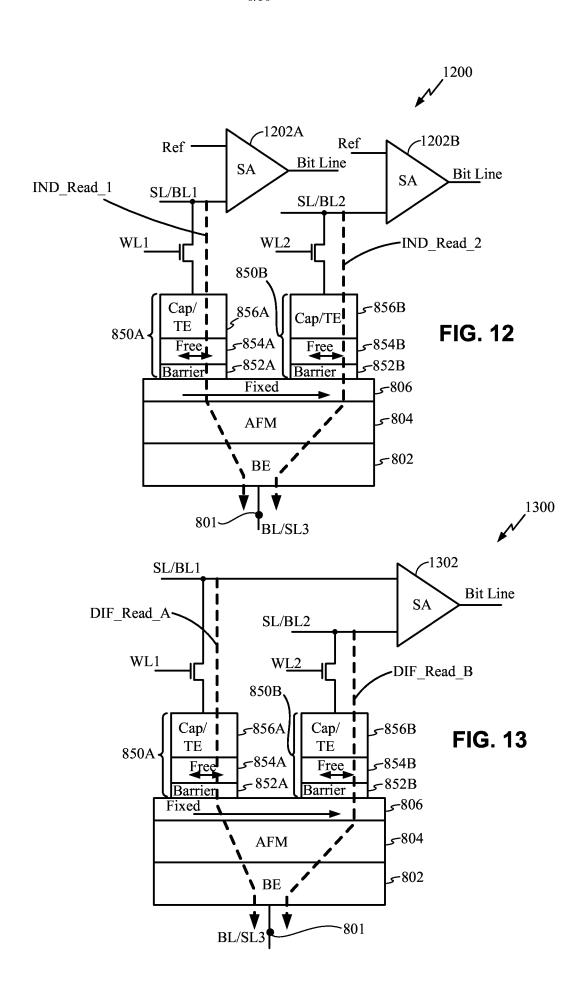

- [0031] FIG. 12 shows one example multiple individual free magnetization layer read MTJ cell in relation to the FIG. 8 multi-free layer MTJ structure, according to one exemplary embodiment.

- [0032] FIG. 13 shows one example multi-free layer differential read MTJ cell according to another three terminal read aspect, employing the FIG. 8 multi-free layer MTJ structure according to one exemplary embodiment.

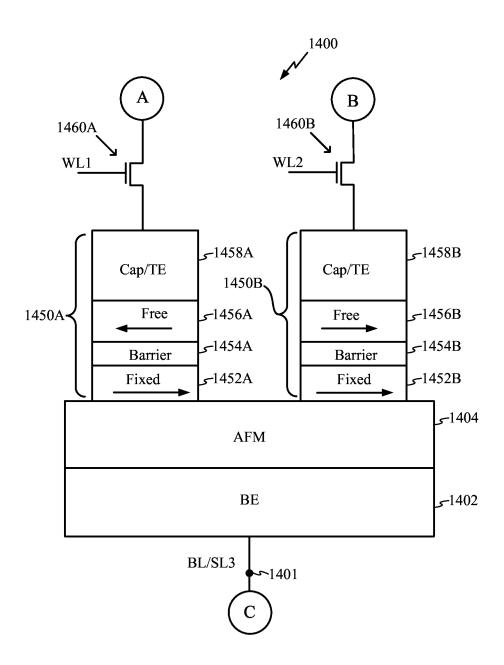

- [0033] FIG. 14 shows one example multiple pillar, common antiferromagnetic (AFM) layer, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment.

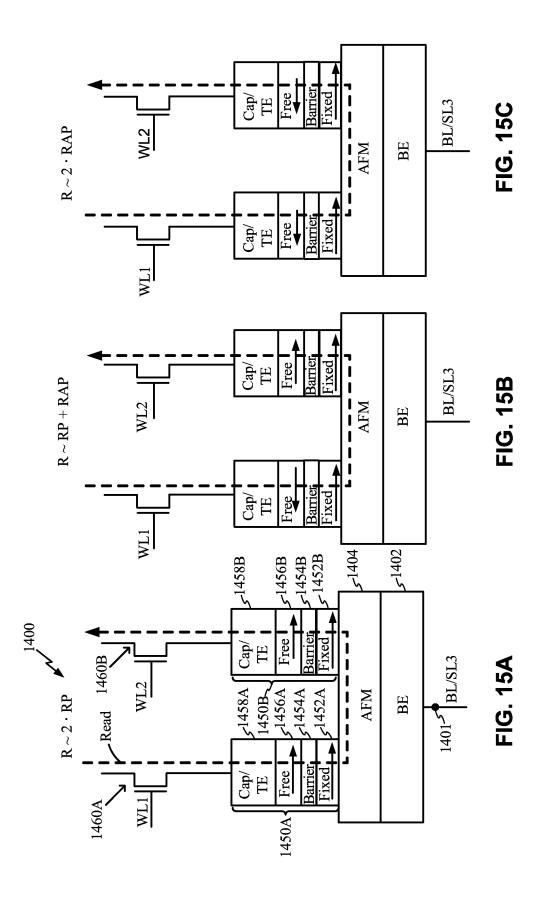

- [0034] FIGS. 15A, 15B, and 15C show a two terminal resistance aspect of the FIG. 14 example multifree layer MTJ structure according to one exemplary embodiment at, respectively, each of a first, second, and third set of magnetization states

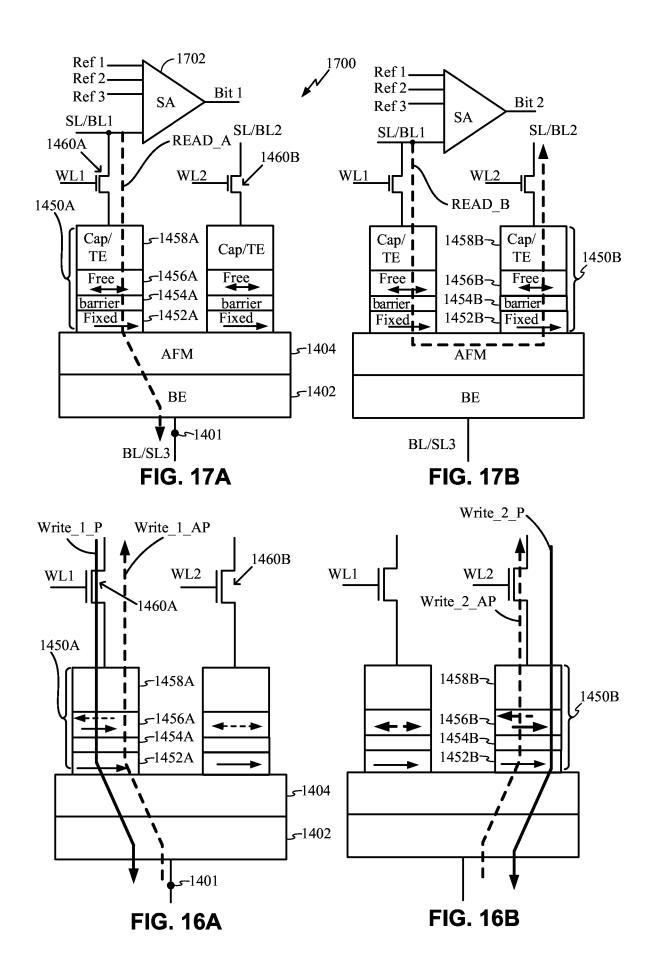

- [0035] FIGS. 16A and 16B show example write current flows for writing, respectively, a first free magnetization layer and a second free magnetization layer of the FIG. 14 example multi-free layer MTJ structure, in a method according to one exemplary embodiment.

- [0036] FIGS. 17A and 17B show, respectively, one individual free magnetization layer read phase and one multi-free layer read phase, in a multi-step, three terminal read aspect in relation to the FIG. 14 multi-free layer MTJ structure, according to one exemplary embodiment.

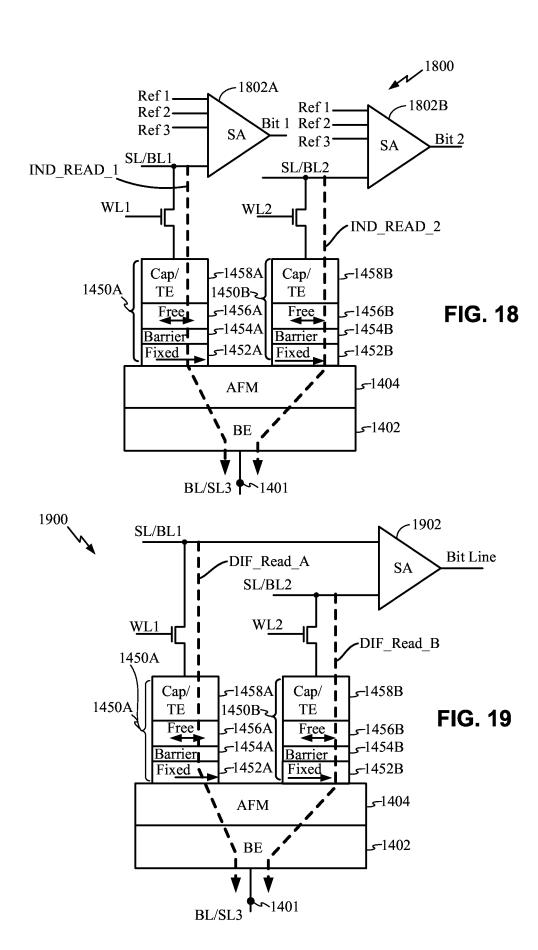

- [0037] FIG. 18 shows one example multiple individual free magnetization layer read MTJ cell according to one read aspect in relation to the FIG. 14 multi-free layer MTJ structure in a method according to one exemplary embodiment.

- [0038] FIG. 19 shows one example multi-free layer differential read MTJ cell according to one three terminal read aspect, in relation to the FIG. 14 multi-free layer MTJ structure according to one exemplary embodiment.

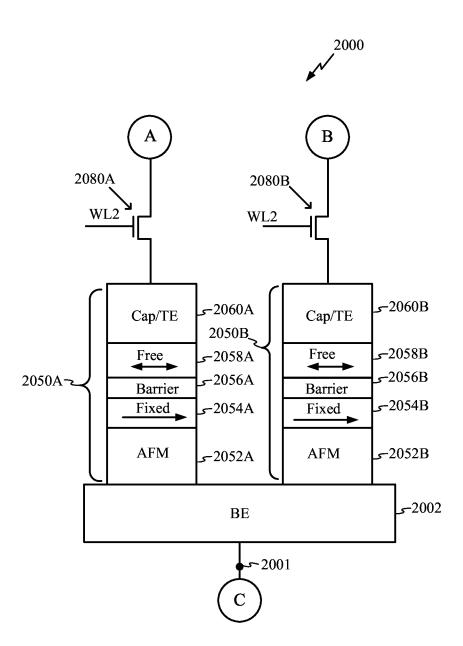

- [0039] FIG. 20 shows one example multiple pillar, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment, in an aspect including pillars having a capping layer, free-layer, barrier layer, and AFM layer.

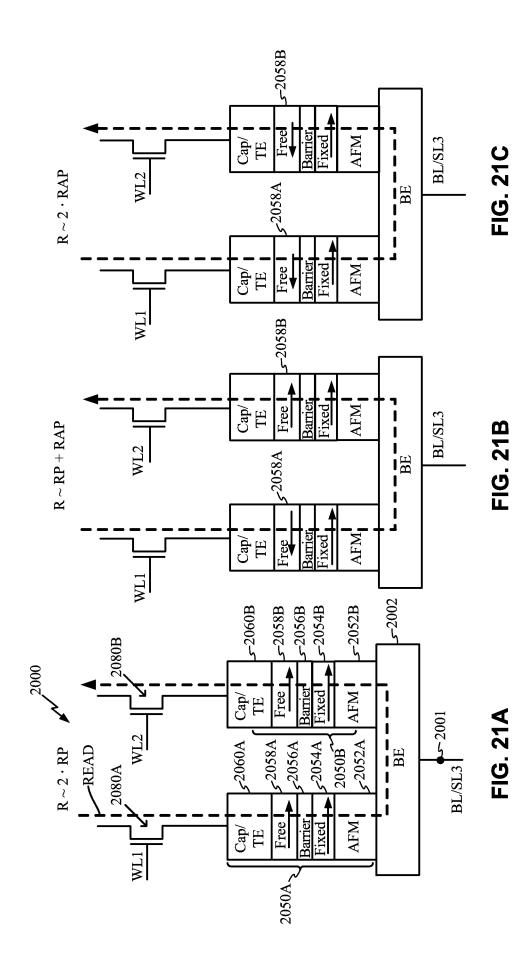

- [0040] FIGS. 21A, 21B, and 21C show a two terminal resistance aspect of the FIG. 20 multiple pillar, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment, at, respectively, each of a first, second, and third set of magnetization states.

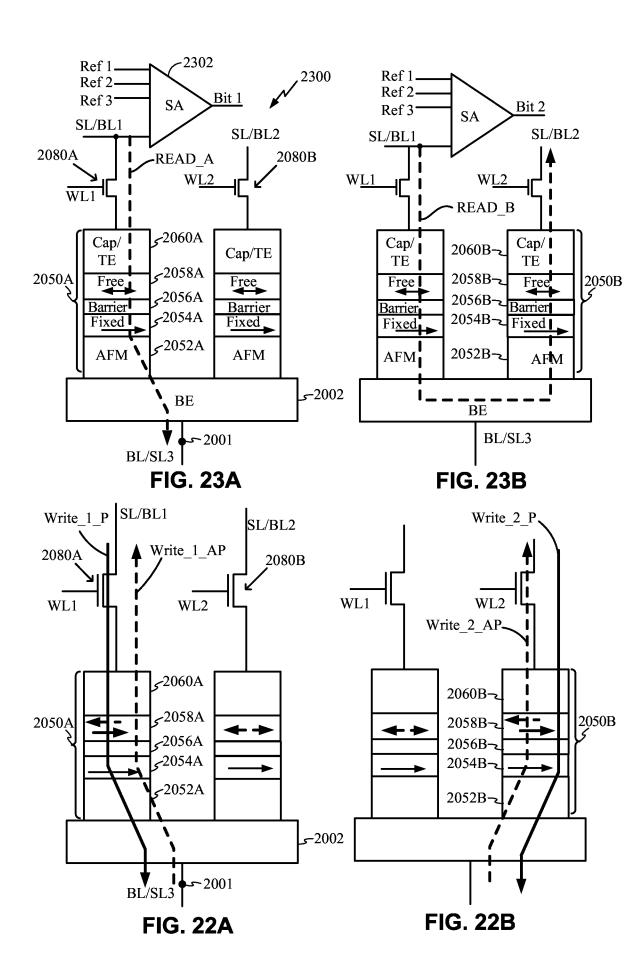

- [0041] FIGS. 22A and 22B show example write current flows for writing, respectively, a first free magnetization layer and a second free magnetization layer of the FIG. 20 example multiple pillar, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment, in a writing method according to one exemplary embodiment.

- [0042] FIGS. 23A and 123B show, respectively, one individual free magnetization layer read phase and one multi-free layer read phase in a multi-step, three terminal read aspect in relation to the FIG. 20 multiple pillar, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment.

- [0043] FIG. 24 shows one example multiple individual free magnetization layer read cell according to one three terminal read aspect, in relation to the FIG. 20 multiple pillar, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment, in a method according to one exemplary embodiment.

- [0044] FIG. 25 shows one example multi-free layer differential read MTJ cell according to a another three terminal read aspect, in relation to the FIG. 20 multiple pillar, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment.

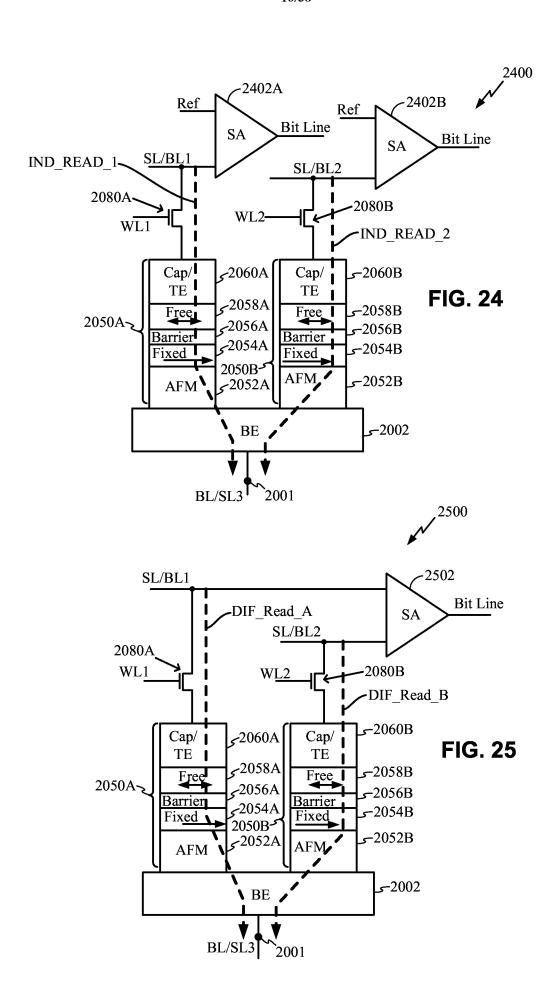

- [0045] FIG. 26 shows one example multiple pillar, multi-free layer MTJ structure according to one exemplary embodiment, in an aspect including pillars having a capping layer, a free-layer, a barrier layer, an AFM layer and a bottom electrode layer.

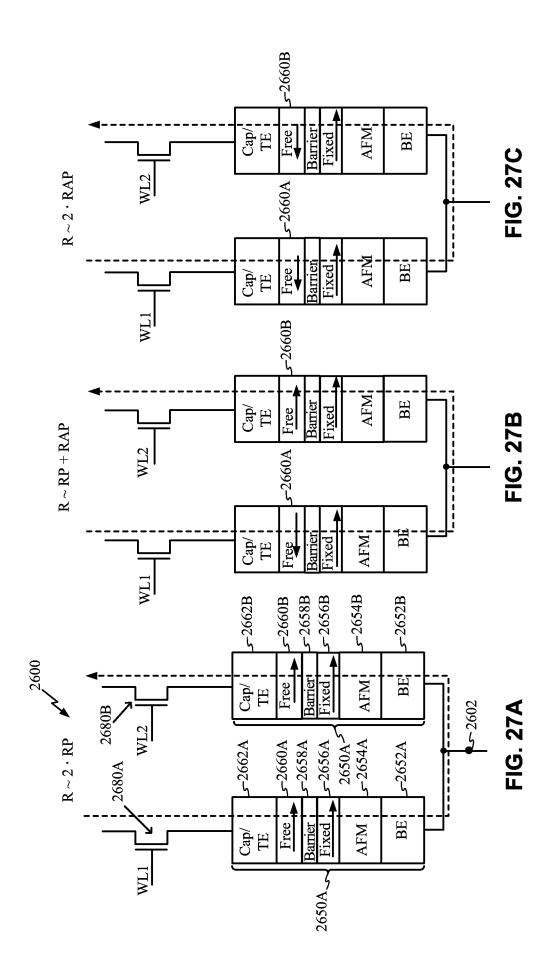

- [0046] FIGS. 27A, 27B, and 27C show a two terminal resistance aspect of the FIG. 26 example multiple pillar, multi-free layer MTJ structure according to one exemplary embodiment at, respectively, each of a first, second, and third set of magnetization states, for storage according to various exemplary embodiments.

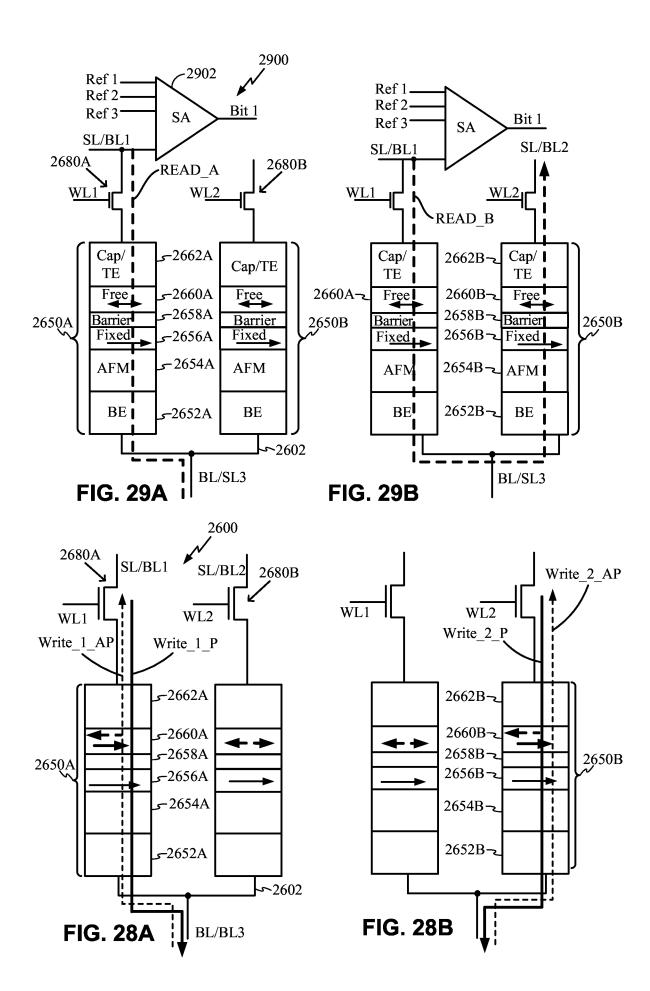

- [0047] FIGS. 28A and 28B show example write current flows for writing, respectively, a first free magnetization layer in first pillar and a second free magnetization layer in a second pillar of the FIG. 26 example multiple pillar, multi-free layer MTJ structure, in a method according to one exemplary embodiment.

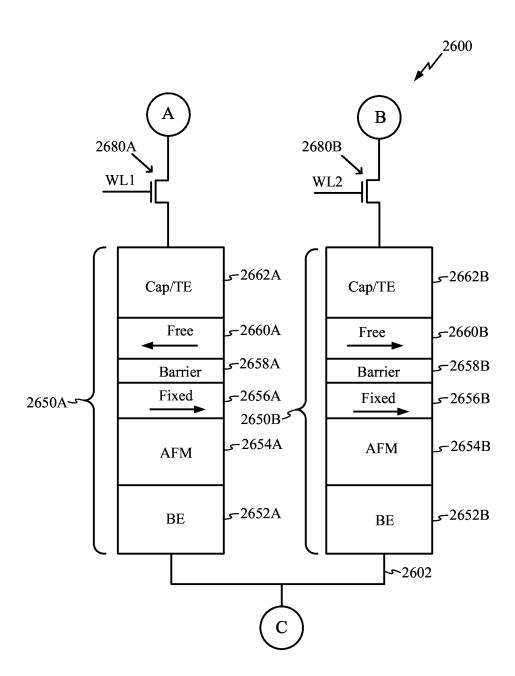

- [0048] FIGS. 29A and 29B show, respectively, one individual free magnetization layer read phase and one multi-free layer read phase, illustrating one multi-step, three terminal read aspect in relation to FIG. 26 example multiple pillar, multi-free layer MTJ structure.

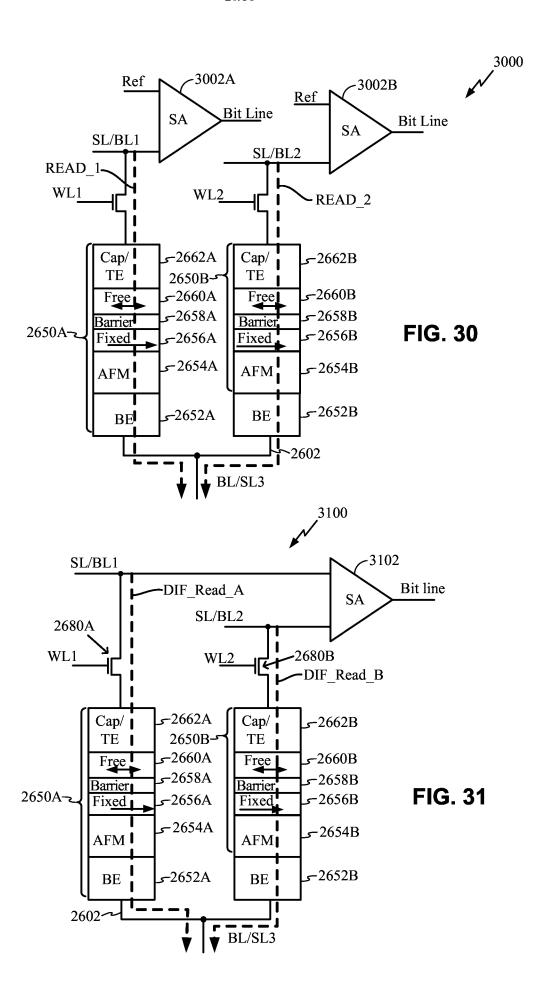

- [0049] FIG. 30 shows one example individual free magnetization layer read MTJ storage cell, according to one three terminal read aspect, in relation to the FIG. 26 multiple pillar, multi-free layer MTJ structure according to one exemplary embodiment.

- [0050] FIG. 31 shows one example multi-free layer differential read MTJ storage cell, according to a further three terminal read aspect, in relation to the FIG. 26 multiple pillar, multi-free layer MTJ structure according to one exemplary embodiment.

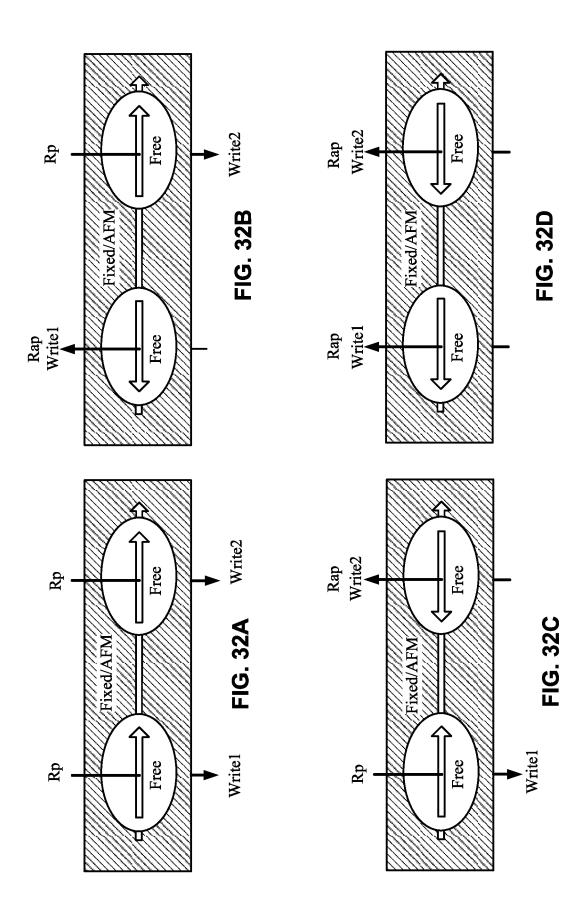

- [0051] FIGS. 32A, 32B, 32C and 32D show four possible sets of free-layer magnetization states for one two layer example of one multi-free layer, in-plane MTJ structure according to one exemplary embodiment, with corresponding write current directions and resulting resistances.

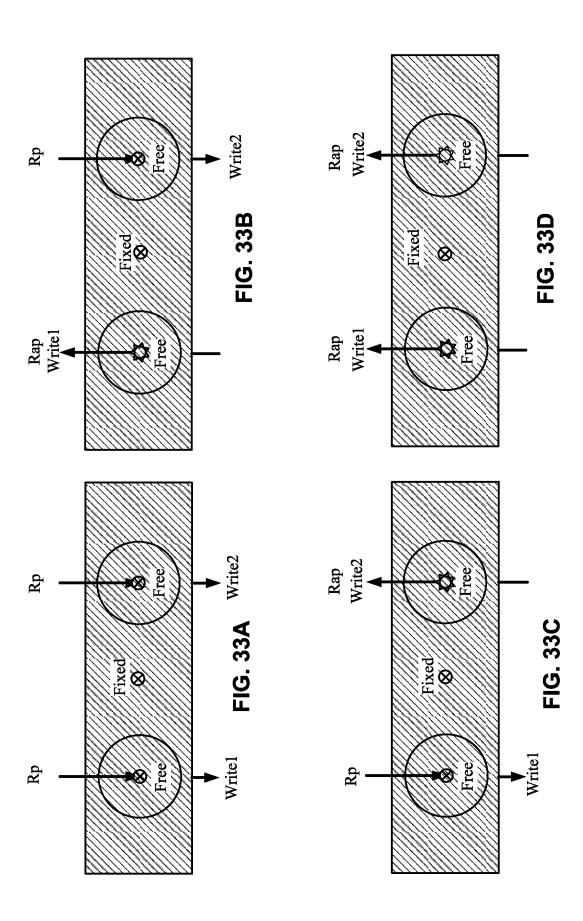

- [0052] FIGS. 33A, 33B, 33C and 33D show four possible sets of free-layer magnetization states for one two layer example of one multi-free layer, perpendicular MTJ structure according to one exemplary embodiment, with corresponding write current directions and resulting resistances.

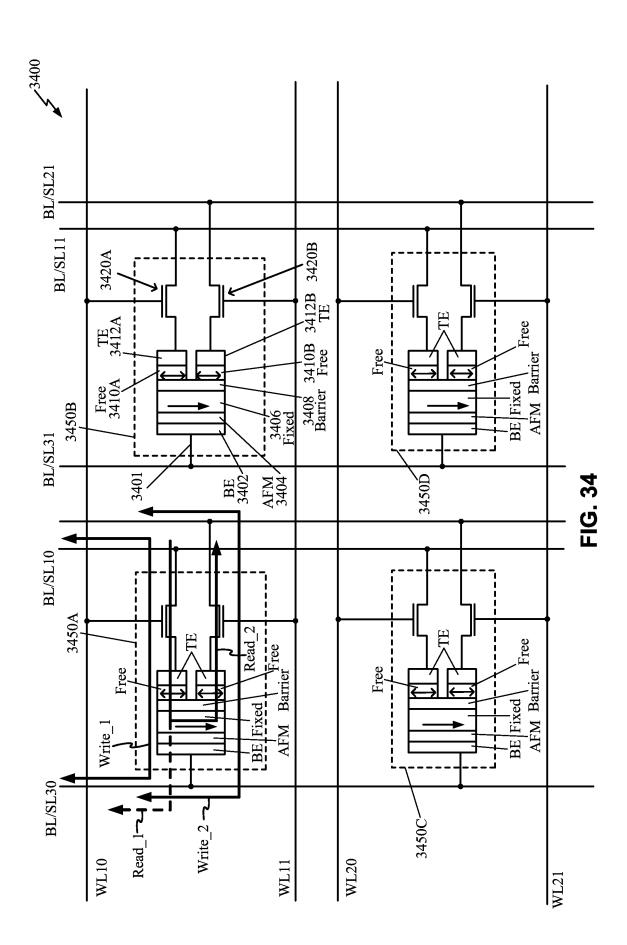

- [0053] FIG. 34 shows one MTJ memory circuit having one example array of multi-terminal, multi-free layer MTJ memory cells in accordance with one or more exemplary embodiments.

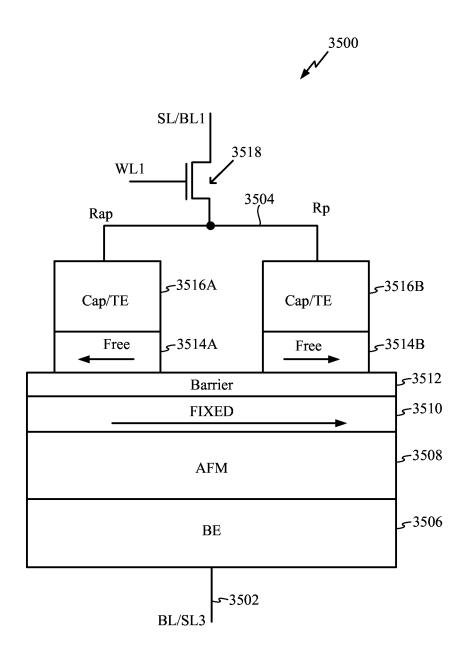

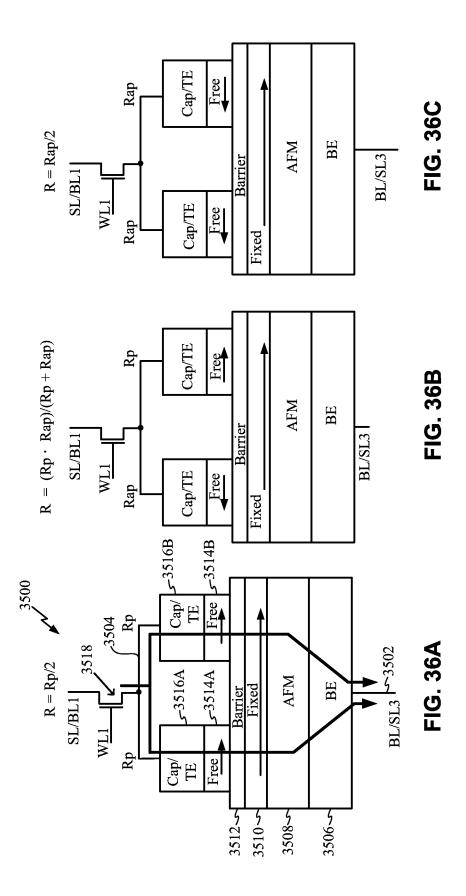

- [0054] FIG. 35 shows one example of a two-terminal, multi-free layer, multi-level MTJ structure in accordance with various exemplary embodiments.

- [0055] FIGS. 36A, 36B, and 36C show the FIG. 35 example two-terminal, multi-free layer, multi-level MTJ structure according to one exemplary embodiment, at an example first, second, and third set of magnetization states, respectively, during a statistical, feedback converging writing process according to one exemplary embodiment. .

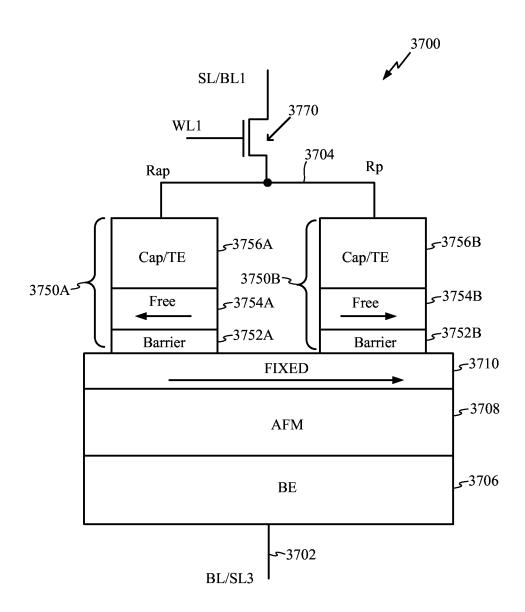

- [0056] FIG. 37 shows one example of a two terminal, multi-free layer, corresponding separate barrier layer, common fixed layer, common AFM layer, common bottom electrode layer, multi-level MTJ structure in accordance with one exemplary embodiment.

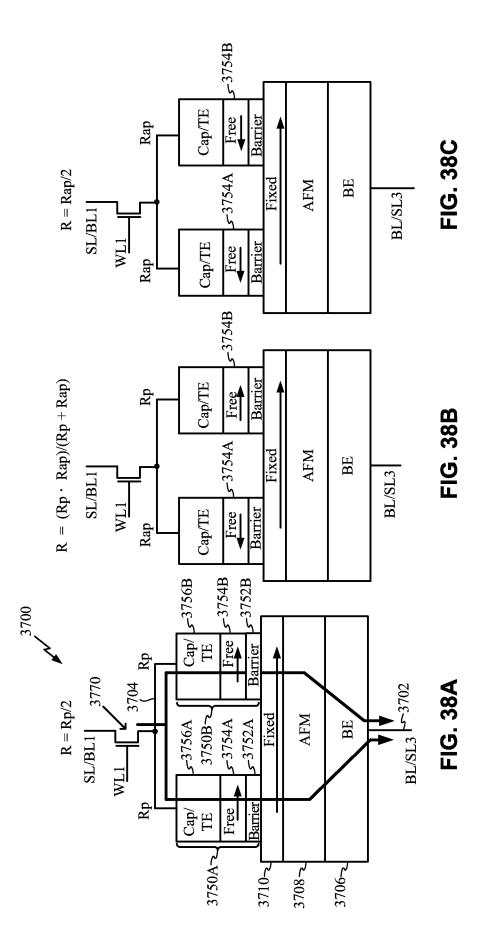

- [0057] FIGS. 38A, 38B, and 38C show the FIG. 37 example two-terminal, multi-free layer, multi-level MTJ structure at an example first, second, and third set of magnetization states, respectively, formed during a statistical, feedback converging writing process according to one exemplary embodiment.

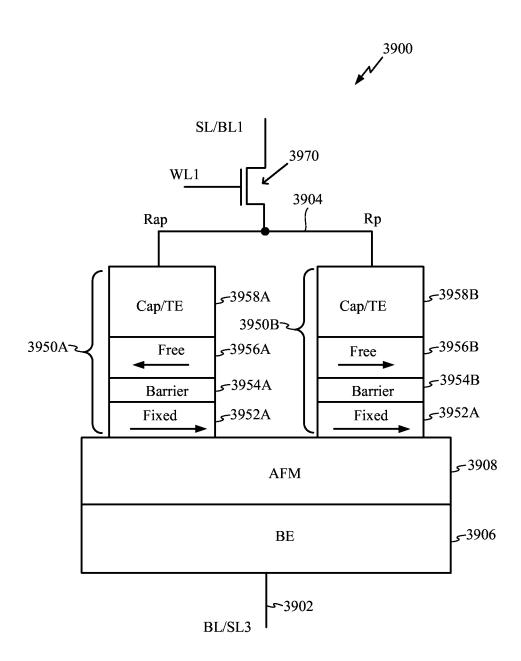

- [0058] FIG. 39 shows one example multiple pillar, common AFM layer, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment, in an aspect providing pillars having a capping layer, free-layer, barrier layer, and fixed layer, in accordance with one exemplary embodiment.

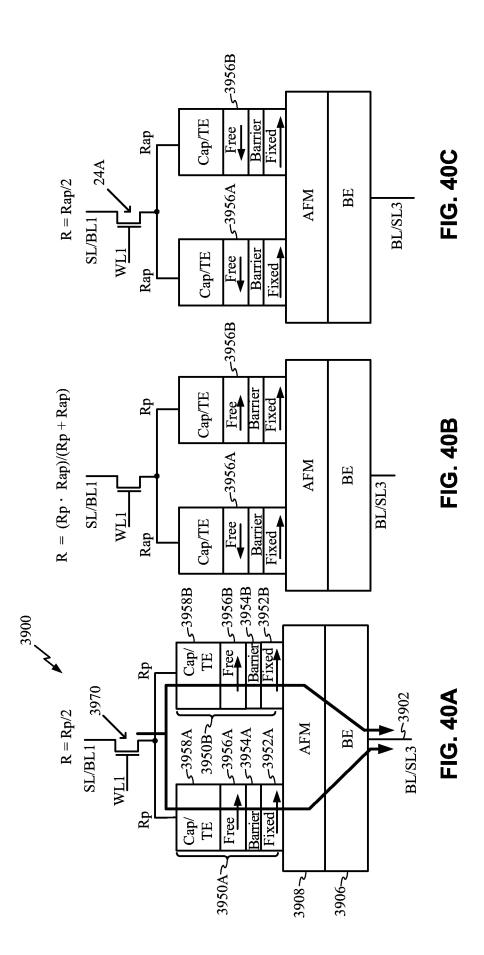

- [0059] FIGS. 40A, 40B, and 40C show the FIG. 34 example two-terminal, multiple pillar, common AFM layer, common bottom electrode layer, multi-free layer MTJ structure at an example first,

- second, and third set of magnetization states, respectively, formed during a statistical, feedback converging writing process according to various exemplary embodiments.

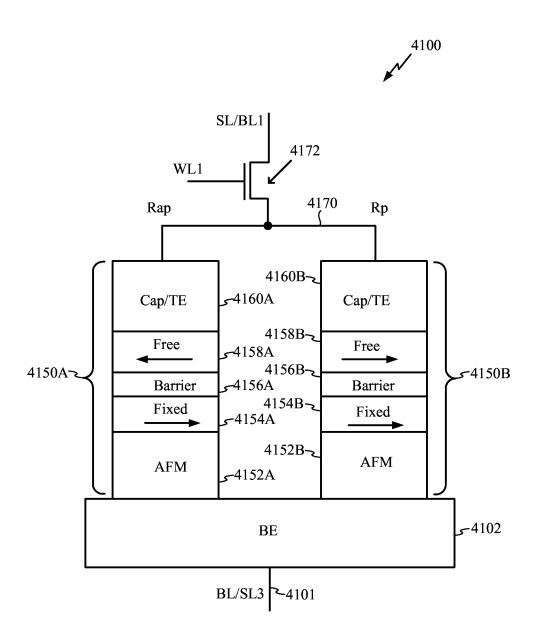

- [0060] FIG. 41 shows one example multiple pillar, common bottom electrode layer, multi-free layer MTJ structure according to one exemplary embodiment, in an aspect including pillars having a capping layer, free-layer, barrier layer, fixed layer and AFM layer, in accordance with various exemplary embodiments.

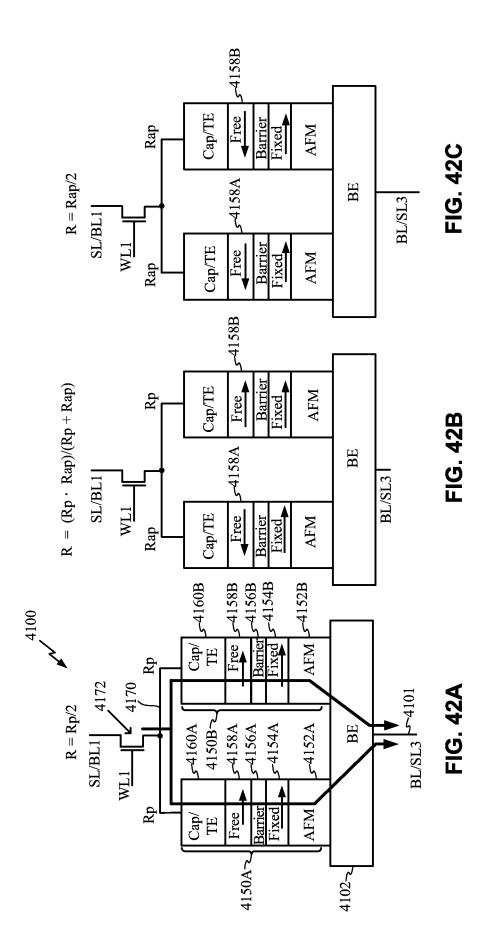

- [0061] FIGS. 42A, 42B, and 42C show the FIG. 41 example two-terminal, multiple pillar, common bottom electrode layer, multi-free layer, multi-level MTJ structure according to one exemplary embodiment, at an example first, second, and third set of magnetization states, respectively, formed during a statistical, feedback converging writing process according to various exemplary embodiments.

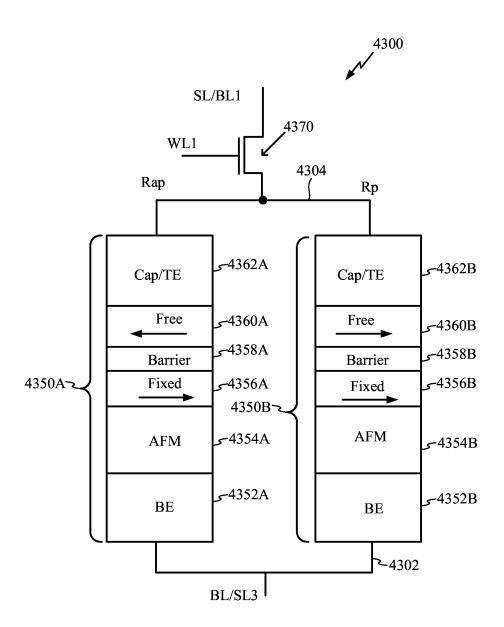

- [0062] FIG. 43 shows one example two-terminal, multiple pillar, multi-free layer, multi-level MTJ structure according to one exemplary embodiment, in an aspect including pillars having a capping layer, free-layer, barrier layer, fixed layer, AFM layer and bottom electrode layer, in accordance with various exemplary embodiments.

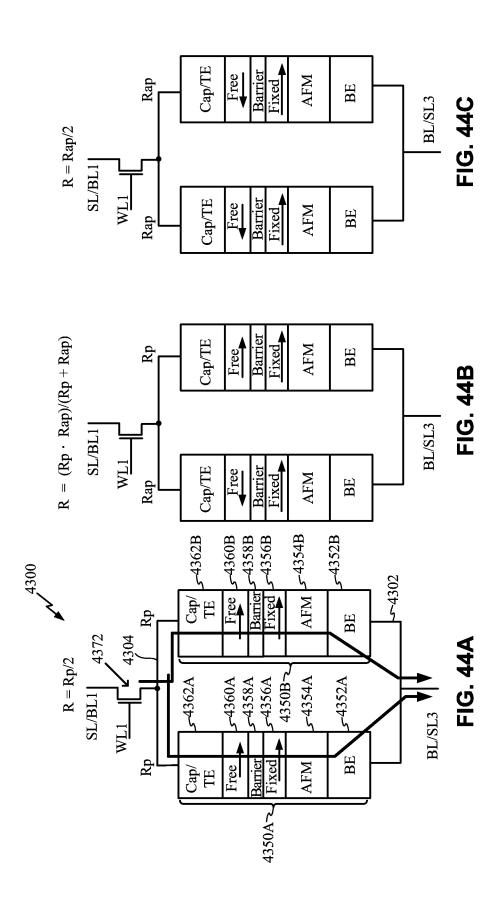

- [0063] FIGS. 44A, 44B, and 44C show the FIG. 43 example two-terminal, multiple pillar, at an example first, second, and third set of magnetization states, respectively, that can be formed during a statistical, feedback converging writing process according to one exemplary embodiment.

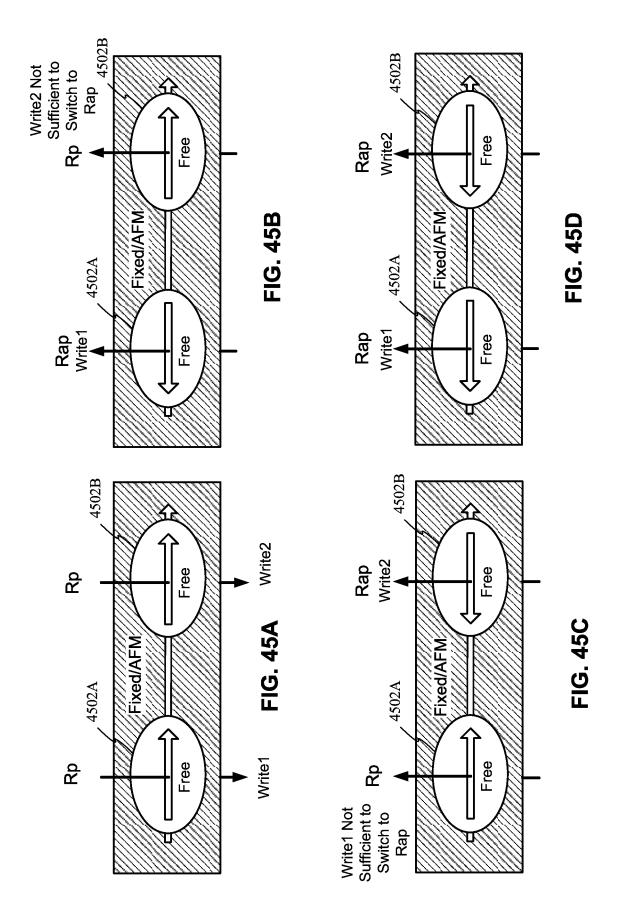

- [0064] FIGS. 45A, 45B, 45C and 45D show four possible sets of free-layer magnetization states for one example of one two-terminal, multi-level, multi-free layer, in-plane MTJ structure according to one exemplary embodiment, with corresponding write current directions and resulting resistances.

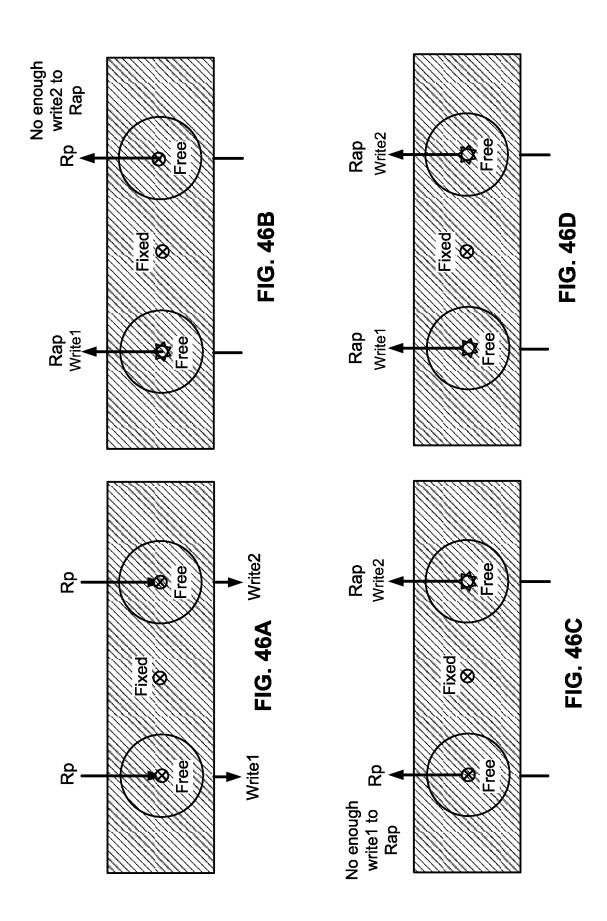

- [0065] FIGS. 46A, 46B, 46C and 46D show four possible sets of free-layer magnetization states for one example of one two-terminal, multi-level, multi-free layer, perpendicular MTJ structure according to one exemplary embodiment, with corresponding write current directions and resulting resistances.

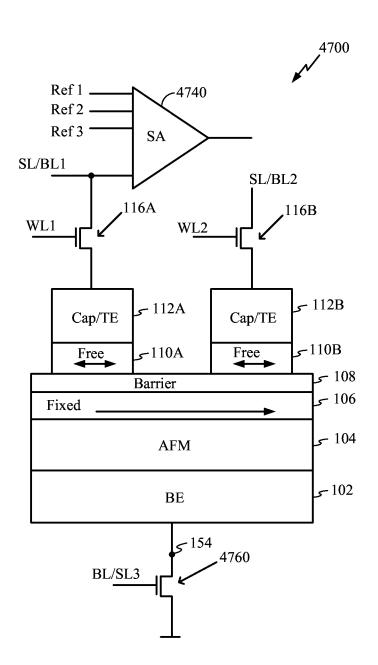

- [0066] FIG. 47 shows one multi-level MTJ storage cell, employing the read FIG. 8 multiple terminal, multi-free layer, corresponding separate barrier layer MTJ structure, according to one exemplary embodiment.

11

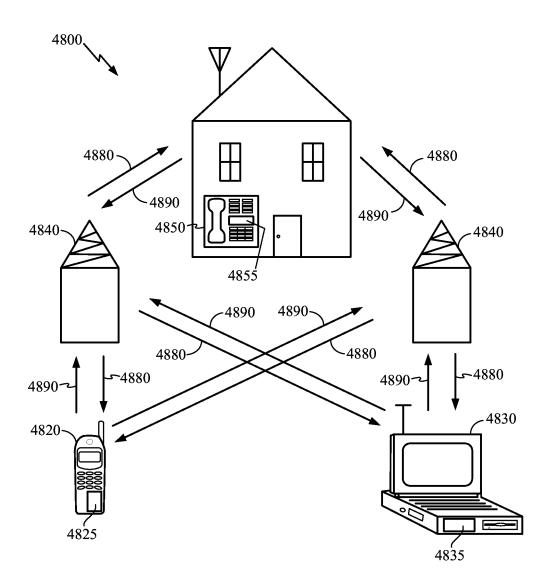

[0067] FIG. 48 illustrates an exemplary wireless communication system in which one or more embodiments of the disclosure may be advantageously employed.

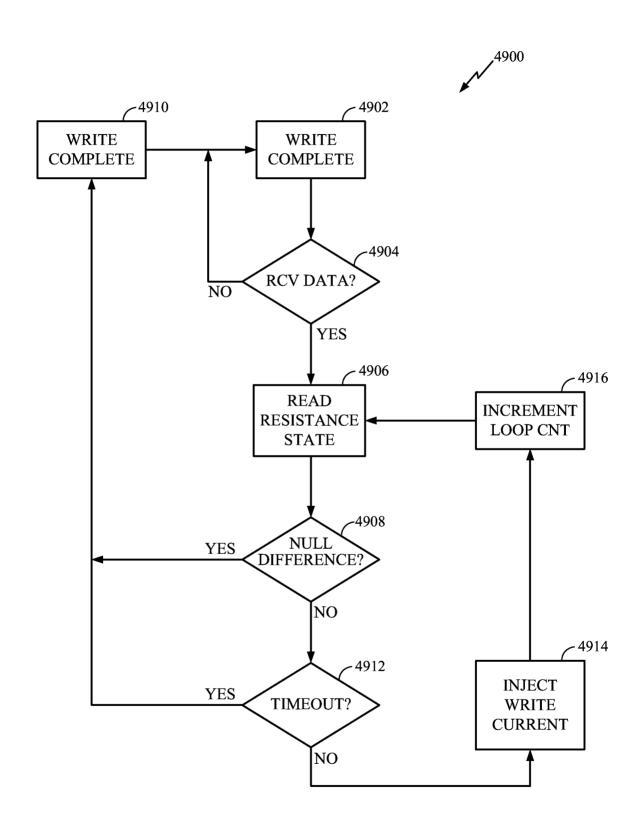

[0068] FIG. 49 shows a flow diagram of one example statistical, feedback converging writing for a two-terminal, multi-free layer, multi-level MTJ device according to various exemplary embodiments.

#### DETAILED DESCRIPTION

- [0069] Aspects of the invention are disclosed in the following description and related drawings directed to specific embodiments of the invention. Alternate embodiments may be devised without departing from the scope of the invention. Additionally, well-known elements of the invention will not be described in detail or will be omitted so as not to obscure the relevant details of the invention.

- [0070] The word "exemplary" is used herein to mean "serving as an example, instance, or illustration." Any embodiment described herein as "exemplary" is not necessarily to be construed as preferred or advantageous over other embodiments. Likewise, the term "embodiments of the invention" does not require that all embodiments of the invention include the discussed feature, advantage or mode of operation.

- [0071] The terminology used herein is for the purpose of describing particular embodiments only and is not intended to be limiting of embodiments of the invention. As used herein, the singular forms "a", "an" and "the" are intended to include the plural forms as well, unless the context clearly indicates otherwise. It will be further understood that the terms "comprises", "comprising,", "includes" and/or "including", when used herein, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof.

- [0072] Further, many embodiments are described in terms of sequences of actions to be performed by, for example, elements of a computing device. It will be recognized that various actions described herein can be performed by specific circuits (e.g., application specific integrated circuits (ASICs)), by program instructions being executed by one or more processors, or by a combination of both. Additionally, these sequence of actions described herein can be considered to be embodied entirely within any form of computer readable storage medium having stored

12

therein a corresponding set of computer instructions that upon execution would cause an associated processor to perform the functionality described herein. Thus, the various aspects of the invention may be embodied in a number of different forms, all of which have been contemplated to be within the scope of the claimed subject matter. In addition, for each of the embodiments described herein, the corresponding form of any such embodiments may be described herein as, for example, "logic configured to" perform the described action.

- [0073] Those of skill in the art will appreciate that information and signals may be represented using any of a variety of different technologies and techniques. For example, data, instructions, commands, information, signals, bits, symbols, and chips that may be referenced throughout the above description may be represented by voltages, currents, electromagnetic waves, magnetic fields or particles, optical fields, electron spins particles, electrospins, or any combination thereof.

- [0074] Further, those of skill in the art will appreciate that the various illustrative logical blocks, modules, circuits, and algorithm steps described in connection with the embodiments disclosed herein may be implemented as electronic hardware, computer software, or combinations of both. To clearly illustrate this interchangeability of hardware and software, various illustrative components, blocks, modules, circuits, and steps have been described above generally in terms of their functionality. Whether such functionality is implemented as hardware or software depends upon the particular application and design constraints imposed on the overall system. Skilled artisans may implement the described functionality in varying ways for each particular application, but such implementation decisions should not be interpreted as causing a departure from the scope of the present invention.

- [0075] FIG. 1 shows one multi-terminal, multi-free layer MTJ structure 100 according to one exemplary embodiment. Referring to FIG. 1, the multi-terminal, multi-free layer MTJ structure 100 can include a bottom electrode layer 102 supporting an antiferromagnetic (AFM) layer 104 which in turn can support a fixed layer 106 with a barrier layer 108 formed on the fixer layer 106. In an aspect the barrier layer 108 supports a first free magnetization layer 110A and a second free magnetization layer 110B, laterally displaced from the first free magnetization layer 110A by a spacing D1. D1 can be close to minimal conventional MTJ size, and it will be understood by persons of ordinary skill in the MTJ art having view of the present disclosure that minimal

conventional MTJ size can depend on the application and on particular MTJ technology selected for the implementation. For purposes of illustration, and without limitation on the numerical value of D1 or of any other parameter that can be used in practices according to the exemplary embodiments, example values of D1 can be 40nm for 40 nm MTJ technology or 28nm for 28 nm MTJ technology, it can be 40nm or 28nm for 40nm or 28nm technology.

- [0076] Referring still to FIG. 1, a first capping/top electrode layer 112A can be disposed on or above the first free magnetization layer 110A and, similarly, a second capping/top electrode layer 112B can be disposed on or above the second free magnetization layer 110B. The first capping/top electrode layer 112A can couple to a first terminal 114A that can, in an aspect, switchably couple through a first word line switch 116A to a first MTJ cell read/write terminal 150, in turn coupled to an external coupling "A." The external coupling A may, for example, be a bit line/ select line capable of being driven by a read current source (not shown) and a write current source (not shown). The first capping/top electrode layer 112B can couple to a second terminal 114B that can, in an aspect, switchably couple through a second word line switch 116B to a second MTJ cell read/write terminal 152 coupled, in turn to an external coupling "B." The coupling B may, for example, be another bit line/ select line capable of being driven by the read current source and the write current source. The bottom electrode layer 102 can couple to a third MTJ cell read/write terminal 154. A bit select line (shown as point "C") can couple to the third MTJ cell read/write terminal 154. In one embodiment, described in greater detail at later sections, another switch (not shown in FIG. 1) can be arranged to switchably establish a current path from the bottom electrode layer 102, through the third MTJ cell read/write terminal 154 to a ground reference or other current sink (not shown in FIG. 1), i.e., to connect "C" to ground.

- [0077] Continuing to refer to FIG. 1, the first word line switch 116A and the second word line switch 116B can be implemented by, for example, an NMOS FET. In an aspect, a first word line WL1 can control the word line switch 116A and a second word line WL2 can control the second word line switch 116B. In one aspect, described in greater detail at later sections, the WL1 and WL1 signals can control establishment of read current paths to sequence of current paths write current source (not shown) to the capping/top electrode layer 112A or 112B.

- [0078] Referring still to FIG. 1, as previously described the first free magnetization layer 110A is spaced from the second free magnetization layer 110B by lateral distance D1 and, because of D1

14

being short (, for example, without limitation, from approximately a one or more tens of nanometers to one or more hundreds of nanometers), polarization is maintained in the fixed layer 106. Also, the double MTJ increases tunneling magnetoresistance (TMR) and the difference between Rp and Rap (alternatively referenced as "delta R"). Therefore, as will be appreciated by persons of ordinary skill in the art from reading this disclosure, the FIG. 1 structure can provide for low-error read sensing.

[0079] FIG. 2A, 2B, and 2C shows a two terminal resistance aspect of the FIG. 1 multi-terminal, multifree layer MTJ structure 100 according to one exemplary embodiment at each of a first, second, and third set, respectively, of magnetization states. It will be understood that "magnetization state" means the alignment (parallel (P) or anti-parallel (AP)) of the first and second free magnetization layers 110A and 110B with respect to the alignment of the fixed layer 106. The "two-terminal" resistance aspect refers to the resistance along the READ path between the FIG. 1 first and second MTJ cell read/write terminals 150 and 152 when the third MTJ cell read/write terminal 154 is floating. As will be described in greater detail at later sections, the FIG. 1 multiterminal, multi-free layer MTJ structure 100 is, in one aspect, capable of a three-terminal mode. The FIG. 2A state is both of the first and second free magnetization layers 110A and 110B being in a parallel (P) alignment with respect to the fixed layer 106. As shown, the resulting resistance through the READ path is approximately two times Rp. The FIG. 2B state is the first free magnetization layer 110A being in an AP alignment and the second free magnetization layer 110B being in a P alignment. Assuming Rap is approximately twice Rp, the resistance of the READ path is approximately three times Rp. Method for selectively writing the first and second free magnetization layers 110A and 110B into any of the FIGS. 2A, 2B or 2C magnetization states will be described in greater detail in reference to FIGS. 3A and 3B.

[0080] FIGS. 3A and 3B show example write current flows for writing a first free magnetization layer and a second free magnetization layer, respectively, of the FIG. 1 multiple terminal, multi-free layer MTJ structure, in a method according to one exemplary embodiment. Referring to FIG. 3A, the writing is performed by switching the first word line switch 116A ON to couple the first MTJ cell read/write terminal 150 (or the first capping/top electrode layer 112A to a write current source and, concurrently, coupling the third MTJ cell read/write terminal 154 to a ground reference or equivalent current sink. If the write current is the depicted direction of the

15

Write\_1\_P current, the first free magnetization layer 110A switches to a P state, as shown by the solid magnetization arrow in the first free magnetization layer 110A. If, on the other hand, the write current is in the depicted Write\_1\_AP direction, the first free magnetization layer 110A switches to the AP state, as shown by the dashed line the first free magnetization layer 110A. Referring to FIG. 3B, writing the second free magnetization layer 110B can be performed by switching the second word line switch 116B ON to couple terminal "B" to the write current source, while coupling the third MTJ cell read/write terminal 154 to a ground reference or equivalent current sink. If the write current is the depicted direction of the Write\_2\_P current, the second free magnetization layer 110B switches to a P state, as shown by the solid magnetization arrow in the second free magnetization layer 110B. However, of the write current is in the depicted Write\_2\_AP direction, the second free magnetization layer 110B switches to the AP state, as shown by the dashed line in the second free magnetization layer 110B.

- [0081] FIGS. 4A and 4B show one individual free magnetization layer read phase and one multi-free layer read phase, respectively, of a two-phase, three-terminal multi-level read circuit 400 aspect in accordance with one exemplary embodiment. To focus on novel concepts without introducing complexity not integral to the concepts, the two-phase, three-terminal multi-level read circuit 400, and example operations further to various embodiments, are described in arrangement utilizing the FIG. 1 example multi-terminal, multi-free layer MTJ structure 100.

- [0082] Referring to FIG. 4A, the first phase couples the bit line "SL/BL1" to a read current source (not shown), with word line signal WL1 switching the word line switch 116A ON, and word line signal WL2 switching the word line switch 116B OFF. In an aspect bit line/select line BL/SL3 is coupled by, for example an address logic (not shown), and to a ground reference or equivalent current sink (not shown). The result is the read current READ\_A passing, according to one example read current polarity, through the MTJ established by the first free magnetization layer 110A separated by the common barrier layer 108 from the common fixed layer 106, then passing through the common AFM layer 104, through the common BE layer 102, and through the bottom terminal 154 to BL/SL3 that, as described above, can be coupled to a ground reference. It will be understood that the direction of the above-described path for the read current READ\_A assumed a read polarity of applying the read voltage at SL/BL1 and the ground/current sink at

16

BL/SL3. The direction of the read current READ\_A can, of course, be reversed by using a read polarity that applies the read voltage at BL/SL3 and the ground/current sink at SL/BL1.

[0083] Referring now to FIG. 4B, further to one aspect the second phase maintains the bit line "SL/BL1" coupled to a read current source (not shown), and word line signal WL1 maintains the word line switch 116A ON, while word line signal WL2 switches the word line switch 116B ON. In an aspect, SL/BL2 is coupled by, for example, a bit line logic (not shown) to ground or an equivalent current sink, and BL/SL3 is uncoupled from the ground reference or equivalent current sink to which it was coupled during the FIG. 4A first phase. The result is the read current READ\_B passing from the bit line BL, through the first MTJ cell read/write terminal 150, through the first capping layer/top electrode layer 112A, through the previously described MTJ established by the first free magnetization layer 110A separated by the common barrier layer 108 from the common fixed layer 106, then laterally across the short distance (shown as "D1" in FIG. 1) through common barrier layer 108 to the region under the common barrier layer 108 under the second free magnetization layer 110B, then up though the MTJ established by the second free magnetization layer 110B separated by the common barrier layer 108 from the common fixed layer 106, up through the second capping/top electrode layer 112B, through the second word line switch 116B to the second MTJ cell read/write terminal 152 ground. The READ\_B current forms an SL/BL1 sense voltage that is based on the series resistance of the above-described MTJs, namely the MTJ established by the first free magnetization layer 110A separated by the common barrier layer 108 from the common fixed layer 106, and the MTJ established by the second free magnetization layer 110B laterally displaced from the first free magnetization layer 110A and separated by the common barrier layer 108 from the common fixed layer 106. As was described for the read current READ\_A in reference to FIG. 4A, the path for the read current READ\_B described assumes the read voltage is applied at SL/BL1 and the ground/current sink at SL/BL2. A reverse direction of the read current READ\_B can obtained by applying the read voltage at SL/BL2 and the ground/current sink at SL/BL1.

[0084] Supply of the reference voltages Ref 1, Ref 2, and Ref 3, and operations of the sense amplifier (SA) 402 according to various exemplary embodiment in detecting the magnetization states of the first and second free magnetization layers 110A and 110B will now be described. In one aspect, the sense amplifier 402 is configured to compare the SL/BL1 sense voltage to Ref 1

17

during the FIG. 4A first phase and, based on the comparison, to detect the state of the first free magnetization layer 110A. In an aspect, this detection can be provided by setting Ref 1 at the midpoint between the nominal sense voltage at "SL/BL1" resulting from the read current READ\_A when the first free magnetization layer 110A is at the P state, as opposed to the nominal sense voltage at "SL/BL1" when in the AP state. Further to this aspect, the SA 402 can be configured to generate, as Bit 1 of the two-bit state, a "1" if the SL/BL1 sense voltage is greater than Ref 1, and a "0" if the SL/BL1 sense voltage is less than Ref 1.

[0085] Referring to FIG. 4B it can be seen that the SL/BL2 sense voltage from the READ\_B will have one of four possible values. Assuming the magnitude of READ\_B is the same as READ\_A, all four of the possible values will be higher than the FIG. 4A SL/BL1 sense voltage. A first pair of these four possible READ\_B SL/BL2 sense voltages will be formed in response to the second free magnetization layer 110B being in a P or AP state when the first free magnetization layer 110A is in the P state. The second pair of these four possible READ\_B SL/BL2 sense voltages will be formed in response to the second free magnetization layer 110B being in a P or AP state when the first free magnetization layer 110A is in the AP state. In one aspect, detecting between the first pair of possible READ\_B SL/BL2 sense voltages can be provided by setting Ref 2 at the midpoint between the first pair, and detecting between the second pair of possible READ\_B SL/BL2 sense voltages can be provided by setting Ref 3 at the midpoint between that second pair of the four possible voltages. In a further aspect, the SA 402 can be configured to select Ref 2 as the comparison voltage for the FIG. 4B second phase, in response to the FIG. 4A first phase detecting the first free magnetization layer 110A being at the state. In other words, if the FIG. 4A first phase resulted in SA 402 generating a "0" as Bit 1, as the least significant bit of the twobit state, then Ref 2 is used to determine Bit 2, the most significant bit. On the other hand, if the FIG. 4A first phase resulted in SA 402 generating a Bit 1 of "1" then Ref 3 is used to determine Bit 2. Accordingly, with Ref 1, Ref 2 and Ref 3 as described, the two-phase, three terminal read shown by FIGS. 4A and 4B can resolve the following four storage Bit 2, Bit 1 states, represented by the P or AP magnetizations of the first free magnetization layer 110A and 110B: "00," "01," "10," and "11." It will be understood that the directions of the read currents READ\_A and READ\_B are described assuming a particular read voltage polarity, which is not intended to limit the scope of any of the exemplary embodiments. On the contrary, as readily understood by persons of ordinary skill in the MTJ arts having view of the present disclosure, the direction of the read currents READ\_A and READ\_B can be in part a design choice, and can be readily selected and set-up by such persons applying general MTJ design techniques to the current disclosure.

- [0086] Referring to FIGS. 3A, 3B, 4A, and 4B, it can be seen that the read path has high R and the write path has a low R. It will be appreciated that the example write and read aspect can apply to, for example, multiple bits or large sensing delta R.

- [0087] FIG. 5 shows one example word line signal waveform for WL1 and WL2 to control the above-described FIG. 4A and 4B read processes.

- [0088] FIG. 6 shows one example multi-free layer, individually readable free magnetization layer MTJ cell 600 according to one three-terminal read aspect. The FIG. 6 multi-free layer, individually readable free magnetization layer MTJ cell 600 can employ the FIG. 1 multi-terminal, multi-free layer MTJ structure 100. Therefore, to better focus on novel aspects without introduction of details not integral to the inventive concepts, the two-phase, three-terminal multi-level read circuit 400, and example operations further to various embodiments, are described in an arrangement utilizing the FIG. 1 example multi-terminal, multi-free layer MTJ structure 100. It will be understood that this is not intended as a limitation on the scope of any embodiments.

- [0089] Referring to FIG. 6, the multi-free layer, individually readable free magnetization layer MTJ cell 600 can include a first sense amplifier (SA) 602A to detect the state of the first free magnetization layer 110A and a second SA 602B to detect the state of the second free magnetization layer 110B. In one aspect, both first and second SA 602A and 602B can receive a Ref that is the above-described Ref 1 voltage, the midpoint between the nominal sense voltage resulting from the first and second free magnetization layers 110A and 110B being at a P state and the nominal sense voltage resulting from the first and second free magnetization layers 110A and 110B being at an AP state.

- [0090] Referring still to FIG. 6, in an example operation WL1 switches the word line switch 116A ON and, according to one aspect, WL2 concurrently switches the word line switch 116B ON. It is assumed that SL/BL1, coupled through the first MTJ cell read/write terminal 150 and the first word line switch 116A to the first capping/top electrode layer 112A, and SL/BL2, coupled through the second MTJ cell read/write terminal 152 by the second word line switch 116B to the

19

second capping/top electrode layer 112B, are each coupled to a read current source (not shown). Read current IND\_Read\_1 then passes through the MTJ established by the first free magnetization layer 110A spaced by the common barrier layer 108 above the common fixed layer 106, through the common AFM layer 104, through the common BE layer 102 and third MTJ cell read/write terminal 154 to ground, developing an SL/BL1 sense voltage indicative of the state of the first free magnetization layer 110A. Likewise, IND\_Read\_2 passes through the MTJ established by the second free magnetization layer 110B spaced, at a location laterally displaced from the first free magnetization layer 110A, by the same common barrier layer 108 above the common fixed layer 106, and though the same common AFM layer 104 and common BE layer 102, through the same third MTJ cell read/write terminal 154 to ground, which develops an SL/BL2 sense voltage indicative of the state of the second free magnetization layer 110B.

[0091] The above-described example read operation showed the WL1 switching the first word line switch 116A ON concurrent with WL2 concurrently switching ON the second word line switch 116B. In one alternative aspect, WL1 and WL2 can be sequenced in a sequential or two-phase read operation, where a first phase switches, for example, first word line switch 116A ON while keeping the second word line switch 116B OFF, thereby establishing SL/BL1 sense voltage for reading first free magnetization layer 110A, and a second phase switches the first word line switch 116A OFF and switching the second word line switch 116B ON, to establish the SL/BL2 sense voltage for reading second free magnetization layer 110B. It will be understood that in this alternative sequential read aspect the order as to which of the first and second word line switches 116A and 116B is switched ON (or OFF) in the first phase and then OFF (or ON) in the second phase and visa a versa is arbitrary. As persons of ordinary skill in the MTJ art will understand from this disclosure, the total read duration may be longer for this sequential read aspect than for the previously described concurrent read aspect. In certain applications, though, the sequential read aspect may, for a given structure and technology, enable or exhibit a higher read accuracy than enabled or exhibited by the concurrent read aspect. For example, it is contemplated that some implementations according to the concurrent read aspect may exhibit, or be analyzed as presenting a potential to exhibit, a possible disturbance of the read voltage from a possible

20

increase in the potential voltage at, or between, one or more of the common fixed layer 106, the common AFM layer 104 and the common BE layer 102.

- [0092] FIG. 7 shows one example multi-free layer differential read MTJ cell 700 according to a further three terminal read aspect. The FIG. 7 multi-free layer differential read MTJ cell 700 can employ the FIG. 1 multiple terminal, multi-free layer MTJ device 100 and is described in such an arrangement to better focus on novel aspects without introduction of details not integral to practicing the inventive concepts. It will be understood that the FIG. 1 multi-terminal, multi-free layer MTJ structure 100 FIG. 1 implementation of the FIG. 7 multi-free layer differential read MTJ cell 700 is only one example, not intended to limit the scope of any embodiments.

- [0093] In an aspect, a single bit can be written to the FIG. 7 multi-free layer differential read MTJ cell 700 by a write process generally according to the write process described in reference to FIG. 3A and 3B, with the further feature that the writing injects either Write\_1\_P or Write\_1\_AP through first free magnetization layer 110A, and a complementary direction Write\_2\_AP or Write\_2\_P through second free magnetization layer 110B, to place the first and second free magnetization layers 110A and 110B in complementary P/AP states. Referring to FIG. 7, as shown by the single SA 702, it will be appreciated that the differential storage and retrieving removes the requirement for a reference cell and, further, may obtain substantially lower bit error rates than readily obtainable using a fixed reference signal.

- [0094] FIG. 8 shows one multi-free layer, separate barrier layer MTJ device 800 according to one multiple pillar embodiment that can provide multiple parallel MTJs and can have a three-terminal aspect, as one alternative to the FIG. 1 one multi-terminal, multi-free layer MTJ structure 100. Referring to FIG. 8, the multi-free layer MTJ device 800 can include, in bottom-to-top order, a common base electrode layer 802, a common AFM layer 804, and a common fixed layer 806. A bottom electrode or third MTJ cell read/write terminal 801 can couple to a bit line generically represented as "C." A first pillar 850A can be arranged at a first location or first area on the upper surface of the common fixed layer 806 and, at a second location or second area laterally displaced by the distance D2 from the first pillar 850A, a second pillar 850B can be arranged. The distance D2 can be in accordance with D1 described in reference to FIG. 1. First pillar 850A can include a barrier layer 852A as a base, a free magnetization layer 854A on the barrier layer 852A, and a capping/top electrode layer 856A on the free magnetization layer

854A. Second pillar 850B can be identically structured having, in bottom-to-top order starting with a barrier layer 852B that can be its base, a free magnetization layer 854B and a capping/top electrode later 856B. The first pillar 850A's free magnetization layer 854A spaced by the pillar 850A's barrier layer 852A above the common fixed layer 806 form a first MTJ and, similarly, the second pillar 850B's free magnetization layer 854B spaced by the second pillar 850B's barrier layer 852B above the common fixed layer 806 form a second MTJ. In one aspect, the spacing (shown but not separately labeled) between the inner, facing walls of the first and second pillars 850A and 850B can be the same as the "D1" dimension described in reference to the FIG. 1 embodiment.

- [0095] FIGS. 9A, 9B, and 9C show a two terminal resistance aspect of the FIG. 8 multi-free layer, separate barrier layer MTJ structure 800 according to one exemplary embodiment at each of the first, second, and third set of magnetization states, respectively. The example states represented by FIGS. 9A, 9B and 9C are shown as corresponding to the example states of the FIG. 1 embodiment represented by FIGS. 2A, 2B and 2C and, when WL1 and WL2 switch the word line switches 808A, 808B ON, exhibit substantially the same resistance over the Read\_R path, i.e., two-terminal resistance, as previously described. The resistances are marked above FIGS. 9A, 9B and 9C. It will be understood that the direction shown on FIGS. 9A- 9B for the Read\_R path assumes, arbitrarily, a read polarity applying the read voltage at SL/BL1 and the ground/current sink at SL/BL2. The illustrated direction is only an example, as a reverse direction can be obtained, and used, by applying the read voltage at SL/BL2 and the ground/current sink at SL/BL1.

- [0096] FIGS. 10A and 10B show example write current flows Write\_1\_P and Write\_1\_AP for writing, in the FIG. 10A mode, the free magnetization layer 854A of the first pillar 850A and, in the FIG. 10B mode, write current flows Write\_2\_P and Write\_2\_AP for writing the free magnetization layer 854B of the second pillar 850B. The Write\_1\_P, Write\_1\_AP, Write\_2\_P, and Write\_2\_AP can be as described in reference to the FIGS. 3A and 3B, except for the free magnetization layers 854A and 854B being written to selected ones of the P or AP states, as opposed to FIG. 1 first and second free magnetization layers 110A and 110B.

- [0097] FIGS. 11A and 11B show, respectively, one individual free magnetization layer read phase and one multi-free layer read phase of a two-phase, three-terminal multi-level read circuit 1100

22

aspect in accordance with one exemplary embodiment. The two-phase, three-terminal multi-level read circuit 400 can utilize the FIG. 8 example multi-free layer MTJ device 800. In an aspect, the two-phase, three-terminal multi-level read circuit 1100 can include a sense amplifier (SA)1102 that can receive Ref 1, Ref 2 and Ref 3, these being at respective voltages as described for the Ref 1, Ref 2 and Ref 3 received by the SA 402 of the FIG. 4A and 4B two-phase, three-terminal multi-level read circuit 400.

[0098] Referring to FIG. 11A, according to one aspect, in the first phase SL/BL1 is coupled to a read current source (not shown), word line signal WL1 switches the word line switch 808A ON, and word line signal WL2 switches the word line switch 808B OFF. In a further aspect, BL/SL3 is coupled by, for example an address logic (not shown) to a ground reference or equivalent current sink (not shown). The read current READ\_A then passes through the MTJ established by the first pillar 850A's free magnetization layer 854A separated, by the first pillar 850A's barrier layer 852A from the common fixed layer 806, and establishes an SL/BL1 sense voltage that, as previously described, the SA 1102 compares to Ref 1. The Bit 1 output of SA 1102 can, in one aspect, be a "0" if the first pillar 850A free magnetization layer 854A is in the P state, and a "1" if it is in the AP state. As previously described, Bit 1 output by SA 1102 can be the least significant, or rightmost bit of a two-bit state Bit 2, Bit 1. The direction shown on FIG. 11A for the read current READ\_A assumes, arbitrarily, a read polarity of the read voltage at SL/BL1 and the ground/current sink at SL/BL2. This is only an example, and a reverse direction for READ\_A can be obtained, and used, by applying the read voltage at SL/BL2 and the ground/current sink at SL/BL1.

[0099] Referring to FIG. 11B, in one aspect the second phase includes WL1 maintaining the word line switch 808A ON, and word line signal WL2 switching the word line switch 808B ON, and BL/SL3 being uncoupled from the ground reference or equivalent current sink to which it was coupled during the FIG. 11A first phase. This establishes a current path for read current READ\_B, the path being from SL/BL1, through the first pillar 850A, into the common fixed layer 806, across the distance of approximately D1 through the common fixed layer, and up through the second pillar 850B, through the word line switch 808B, and then to SL/BL2 which, as described above, is grounded. The resistance of the READ\_B path is the series resistance of the above-described MTJs, namely the MTJ established by the first pillar 850A's free

23

magnetization layer 854A separated, by the first pillar 850A's barrier layer 852A from the common fixed layer 806, and the MTJ established by the second pillar 850B's free magnetization layer 854B separated, by the second pillar 850B's barrier layer 852A from the common fixed layer 806. This READ\_B current forms an SL/BL1 sense voltage indicative of the above-described resistance, and SA 1102 compares this voltage to one of Ref 2 and Ref 3. The comparison generates Bit 2, depending on the FIG. 11A first phase detected state of the free magnetization layer, in other words depending on whether the FIG. 11A first phase Bit 1 output was a "0" or a "1." In an aspect, by the same general concepts as described for the embodiments show at FIGS. 4A and 4B, the sequence of the FIG. 11A first phase and FIG. 11B second phase can resolve the following four storage states, represented by the P or AP magnetizations of the free magnetization layer 854A and 854B: "00," "01," "10," and "11." It will be understood that the direction shown on FIG. 11B for the read current READ\_B assumes, arbitrarily, a read polarity of the read voltage at SL/BL1 and the ground/current sink at SL/BL2. This direction is only an example, and a reverse direction for READ\_B can be obtained, and used, by applying the read voltage at SL/BL2 and the ground/current sink at SL/BL1.

- [00100] FIG. 12 shows one example multi-free layer, individually readable free magnetization layer MTJ cell 1200 according to one three-terminal read aspect that, in the depicted example configuration, can utilize the FIG. 8 multiple terminal, multi-free layer MTJ device 800.

- [00101]Referring to FIG. 12, the multi-free layer, individually readable free magnetization layer 1200 can include a first sense amplifier (SA) 1202A to detect the state of the first pillar 850A free magnetization layer 854A, and a second SA 1202B to detect the state of the second pillar 850B free magnetization layer 854B. In one aspect, both SA 1202A and 1202B can receive a Ref that is the above-described Ref 1 voltage, the midpoint between the nominal sense voltage resulting from the free magnetization layers 854A and 854B being at a P state and the nominal sense voltage resulting from the free magnetization layers 854A and 854B being at an AP state. Assuming read current sources are coupled to SL/BL1 and SL/BL2 as previously described, in an aspect a read current IND\_Read\_1 passes through the MTJ established by the first pillar 850A having the free magnetization layer 854A spaced by the first pillar 850A's barrier layer 852A above the common fixed layer 806, which develops an SL/BL1 sense voltage indicative of the state of free magnetization layer 845A. Similarly, IND\_Read\_2 passes through the MTJ

24

established by the second pillar 850B having the free magnetization layer 854B spaced by the pillar 850B's barrier layer 852B above the common fixed layer 806, which develops an SL/BL2 sense voltage indicative of the state of free magnetization layer 845B. It will be understood that the directions described for the read current IND\_Read\_1 and IND\_Read\_2 shown on FIG. 12 assume, arbitrarily, a read polarity applying the read voltage at SL/BL1 and SL/BL2 and the ground/current sink at BL/SL3, and that a reverse direction for either or both of IND\_Read\_1 and IND\_Read\_2 can be obtained, and used, by applying an opposite assignment of read voltage and ground/current sink to one or both of SL/BL1 and SL/BL2 with respect to BL/SL3.

[00102] FIG. 13 shows one example multi-free layer differential read MTJ cell 1300 according to another three terminal read aspect, employing the FIG. 8 multi-free layer MTJ device 800 according to one exemplary embodiment, in a combination with a differential sense amplifier 1302. In an aspect, a general operation of the FIG. 13 multi-free layer differential read MTJ cell 1300 can be according to the general operation described for the FIG. 7 multi-free layer differential read MTJ cell 700.

[00103]FIG. 14 shows one example multiple pillar, multi-free layer MTJ device 1400 according to one exemplary embodiment that can provide multiple parallel MTJs and can have a three-terminal aspect, as another alternative to the FIG. 1 one multi-terminal, multi-free layer MTJ structure 100, and an alternative to the FIG. 8 multiple pillar, multi-free layer MTJ device 800. In an aspect, the multiple pillar, multi-free layer MTJ device 1400 can include, in bottom-to-top order, a common base electrode layer 1402 and a common AFM layer 1404. A bottom electrode or third MTJ cell read/write terminal 1401 can couple to a bit line generically represented as "C." A first pillar 1450A can be arranged at a first location on the upper surface of the common AFM layer 1404 and, laterally displaced by, for example, the previously described distance D1 from the first pillar 1450A, a second pillar 1450B can be arranged. The first pillar 1450A can include a fixed layer 1452A as a base and, in a bottom-to-top order beginning with a top surface of the fixed layer 1452A, barrier layer 1454A, a free magnetization layer 1456A, and a capping/top electrode layer 1458A. The second pillar 1450B can be identically structured to the first pillar 1450A having, in bottom-to-top order starting with a fixed layer 1452B that can be the base, a barrier layer 1454B, a free magnetization layer 1456B and a capping/top electrode later 1458B. In one aspect, a word line switch 1460A, controlled by word line WL1 couples the capping/top

25

electrode layer 1458A to a generic terminal A, and a word line switch 1460B, controlled by word line WL2, couples the capping/top electrode layer 1458B to a generic terminal B.

- [00104] Referring FIGS. 1 and 14 together, persons of ordinary skill in the MTJ art having view of the present disclosure may appreciate that in various fabrication processes contemplated by this disclosure that include adapting conventional MTJ fabrication techniques, for example etching, to form devices in accordance with these figures that etching for the FIG. 14 structure may be made simpler because the thickness (shown but not separately labeled) of the AFM layer 1404 can enable its use as an etch stop in an etching of, for example, a fixed layer (not shown) from which fixed layers 1452A and 1452B remain, a barrier layer (not shown) from which barrier layers 1454A and 1454B remain, a free magnetization layer (not shown) from which free magnetization layers 1456A and 1456B remain and, depending on the fabrication process selected, a capping/top electrode layer (not shown) from which capping/top electrode layers 1458A and 1458B remain.

- [00105] FIGS. 15A, 15B, and 15C show a two terminal resistance aspect of the FIG. 14 multiple pillar, multi-free layer MTJ device 1400 according to one exemplary embodiment at, respectively, each of the first, second, and third set of magnetization states. The example states represented by FIGS. 15A, 15B and 15C are shown as corresponding to the example states of the FIG. 1 embodiment represented by FIGS. 2A, 2B and 2C and, when WL1 and WL2 switch the word line switches 1460A, 1460B ON, exhibit substantially the same resistance over the Read\_R path, i.e., the two-terminal resistance, as previously described. The resistances are marked above FIGS. 15A, 15B and 15C. It will be understood that the direction of Read\_R path assumes, arbitrarily, a read polarity applying the read voltage at SL/BL1and the ground/current sink at SL/BL2, and that the reverse direction can be obtained, and used, by applying the read voltage at SL/BL2and the ground/current sink at SL/BL1.

- [00106] FIGS. 16A and 16B show example write current flows Write\_1\_P and Write\_1\_AP for writing, in the FIG. 16A mode, the free magnetization layer 1456A of the first pillar 1450A and, in the FIG. 16B mode, write current flows Write\_2\_P and Write\_2\_AP for writing the free magnetization layer 1456B of the second pillar 1456B. The Write\_1\_P, Write\_1\_AP, Write\_2\_P, and Write\_2\_AP can be as described in reference to the FIGS. 3A and 3B, except for

26

the free magnetization layers 1456A and 1456B being written to selected ones of the P or AP states, as opposed to FIG. 1 first and second free magnetization layers 110A and 110B.

- [00107] FIGS. 17A and 17B show, respectively, one individual free magnetization layer read phase and one multi-free layer read phase of a two-phase, three-terminal multi-level read circuit 1700 aspect in accordance with one exemplary embodiment that, in an aspect, can utilize the FIG. 14 example multiple pillar, multi-free layer MTJ device 1400. In an aspect, the two-phase, three-terminal multi-level read circuit can include a sense amplifier (SA) 1702 that can receive Ref 1, Ref 2 and Ref 3, these being at respective voltages as described for the Ref 1, Ref 2 and Ref 3 received by the SA 402 of the FIG. 4A and 4B two-phase, three-terminal multi-level read circuit 400.

- [00108] Referring to FIG. 17A, the first phase assumes SL/BL1 is coupled to a read current source (not shown) and, in an aspect, word line signal WL1 switches the word line switch 1460A ON and word line signal WL2 switches the word line switch 1460B OFF. In a further aspect, BL/SL3 is coupled by, for example, an address logic (not shown) to a ground reference or equivalent current sink (not shown). The path for Read current READ\_A is therefore established, and READ\_A passes through the MTJ established by the first pillar 1450A's free magnetization layer 1456A separated, by the first pillar 1450A's barrier layer 1454A, from the first pillar 1450A's fixed layer 1452, establishes a BL sense voltage. This develops an SL/BL1 sense voltage that, in an aspect, SA 1702 compares to Ref 1. The Bit 1 output of SA 1702 can, in one aspect, be a "0" if the first pillar 1450A free magnetization layer 1456A is in the P state, and a "1" if it is in the AP state. The direction shown on FIG. 17A for the read current READ\_A assumes, arbitrarily, a read polarity of the read voltage at SL/BL1 and the ground/current sink at SL/BL2. This is only an example, and a reverse direction for READ\_A can be obtained, and used, by applying the read voltage at SL/BL2 and the ground/current sink at SL/BL2.

- [00109] Referring to FIG. 17B, in one aspect the second phase includes WL1 maintaining the word line switch 1460A ON, word line signal WL2 switching the word line switch 1460B ON, and BL/SL3 being uncoupled from the ground reference or equivalent current sink to which it was coupled during the FIG. 17A first phase. The path for the read current READ\_B is then established, the path passing from SL/BL1, through the first pillar 1450A, into the common AFM layer 1404, across the distance of approximately D1 through the common AFM layer 1404,

and up through the second pillar 1450B, through the word line switch 1460B to SL/BL2 to ground. The resistance of the READ\_B path is the series resistance of the above-described MTJs, namely the MTJ established by the first pillar 1450A's free magnetization layer 1456A separated, by the first pillar 1450A's barrier layer 1454A, from the first pillar 1450A's fixed layer 1452A, and the MTJ established by the second pillar 1450B's free magnetization layer 1456B separated, by the second pillar 1450B's barrier layer 1454B, from the second pillar 1450B's fixed layer 1452B. This READ\_B current forms an SL/BL1 sense voltage indicative of the above-described series resistance. The FIG. 17B example direction for the read current READ\_A assumes, arbitrarily, a read polarity of the read voltage at SL/BL1 and the ground/current sink at SL/BL2. A reverse direction for READ\_A can be obtained, and used, by applying the read voltage at SL/BL2 and the ground/current sink at SL/BL1.

- [00110] Referring still to FIG. 17B, in an aspect SA 1702 compares the above-described SL/BL1 sense voltage resulting from the READ\_B current to one of Ref 2 and Ref 3, depending on the FIG. 17A first phase detected state of the free magnetization layer, in other words depending on whether the FIG. 17A first phase output Bit 1 was a "0" or a "1." In an aspect, by the same general concepts as described for the embodiments shown at FIGS. 4A and 4B, and shown at FIGS. 11A and 11B, the sequence of the FIG. 17A first phase and FIG. 17B second phase can resolve and output as Bit 2, Bit 1, the following four storage states represented by the P or AP magnetizations of the free magnetization layers 1456A and 1456B: "00," "01," "10," and "11."

- [00111]FIG. 18 shows one example multi-free layer, individually readable free layer MTJ cell 1800 according to one three-terminal read aspect that, in the depicted example configuration, can utilize the FIG. 14 multiple pillar, multi-free layer MTJ device 1400. The multi-free layer, individually readable free layer MTJ cell 1800 can include a first sense amplifier (SA) 1802A to detect the state of the first pillar 1450A free magnetization layer 1456A, and a second SA 1802B to detect the state of the second pillar 1450B free magnetization layer 1456B. In one aspect, both SA 1802A and 1802B can receive a Ref that is the above-described Ref 1 voltage, the midpoint between the nominal sense voltage resulting from the free magnetization layers 1456A and 1456B being at a P state and the nominal sense voltage resulting from the free magnetization layers 1456A and 1456B being at an AP state. Assuming read current sources are coupled to SL/BL1 and SL/BL2 as previously described, in an aspect a current IND\_Read\_1 passes through

the MTJ established by the first pillar 1450A having the free magnetization layer 1456A spaced by the pillar 1450A's barrier layer 1454A above its fixed layer 1452A, which develops an SL/BL1 sense voltage indicative of the state of free magnetization layer 1456A. Similarly, IND\_Read\_2 passes through the MTJ established by the second pillar 1450B having its free magnetization layer 1456B spaced by the first pillar 1450B's barrier layer 1452B above its fixed layer 1452B, which develops an SL/BL2 sense voltage indicative of the state of free magnetization layer 1456B. It will be understood that the directions described for the read current IND\_Read\_1 and IND\_Read\_2 shown on FIG. 12 assume, arbitrarily, a read polarity applying the read voltage at SL/BL1 and SL/BL2 and the ground/current sink at BL/SL3, and that a reverse direction for either or both of IND\_Read\_1 and IND\_Read\_2 can be obtained, and used, by applying an opposite assignment of read voltage and ground/current sink to one or both of SL/BL1 and SL/BL2 with respect to BL/SL3.

- [00112] FIG. 19 shows one example multi-free layer differential read MTJ cell 1900 according to another three terminal read aspect, employing the FIG. 14 multiple pillar, multi-free layer MTJ device 1400 according to one exemplary embodiment, in a combination with a differential sense amplifier 1902. In an aspect, a general operation of the FIG. 19 multi-free layer differential read MTJ cell 1900 can be according to the general operation described for the FIG. 7 multi-free layer differential read MTJ cell 700.

- [00113]FIG. 20 shows one example multiple pillar, multi-free layer MTJ device 2000 according to one exemplary embodiment that can provide multiple parallel MTJs and can have a three-terminal aspect, as another alternative to the FIG. 1 one multi-terminal, multi-free layer MTJ device 100. The exemplary embodiments shown by the FIG. 20 multiple pillar, multi-free layer MTJ device 2000 can be another alternative to the FIG. 8 multiple pillar, multi-free layer MTJ device 800, and/or to the FIG. 14 multiple pillar, multi-free layer MTJ device 1400.

- [00114] Referring to FIG. 20, in an aspect the multiple pillar, multi-free layer MTJ device 2000 can include, in bottom-to-top order, a common base electrode (BE) layer 2002 that can couple, for example through a bottom or third MTJ cell read/write terminal 2001, to a bit line generically represent as "C." A first pillar 2050A can be arranged at a first location on the upper surface of the common BE layer 2002 and, laterally displaced by, for example, the previously described distance D1 from the first pillar 2050A, a second pillar 2050B can be arranged. The first pillar

2050A can include an AFM layer 2052A as a base and, in a bottom-to-top order beginning with a top surface of the AFM layer 2052A, a fixer layer 2054A, a barrier layer 2056A, a free magnetization layer 2058A, and a capping/top electrode layer 2060A. The second pillar 2050B can be identically structured to the first pillar 2050A having, in bottom-to-top order starting with an AFM layer 2052B that can be the base, a fixed layer 2054B, a barrier layer 2056B, a free magnetization layer 2058B and a capping/top electrode later 2060B. In one aspect, a word line switch 2080A, controlled by word line WL1 switchably couples the capping/top electrode layer 2060A to a generic terminal A, and a word line switch 2080B, controlled by word line WL2, switchably couples the capping/top electrode layer 2060B to a generic terminal B.

- [00115]FIGS. 21A, 21B, and 21C show a two terminal resistance aspect of the FIG. 20 multiple pillar, multi-free layer MTJ device 2000 according to one exemplary embodiment at, respectively, each of the first, second, and third set of magnetization states. The example states represented by FIGS. 21A, 21B and 21C are shown as corresponding to the example states of the FIG. 1 embodiment represented by FIGS. 2A, 2B and 2C and, when WL1 and WL2 switch the word line switches 2080A, 2080B ON, exhibit substantially the same resistance over the Read\_R path, i.e., a two-terminal resistance, as previously described. The resistances are marked above in FIGS. 21A, 21B and 21C. It will be understood that the direction of Read\_R path assumes, arbitrarily, a read polarity applying the read voltage at SL/BL1 and the ground/current sink at SL/BL2, and that the reverse direction can be obtained, and used, by applying the read voltage at SL/BL2 and the ground/current sink at SL/BL1.