# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2016/0323524 A1 Smith et al.

Nov. 3, 2016 (43) **Pub. Date:**

#### (54) HIGH DYNAMIC-RANGE IMAGE SENSOR

(71) Applicant: RAMBUS INC., Sunnyvale, CA (US)

Inventors: Craig M. Smith, Spencerport, NY (US); Frank Armstrong, Rochester, NY (US); Jay Endsley, San Jose, CA (US); Thomas Vogelsang, Mountain View, CA (US); James E. Harris, Tyler, TX (US); John Ladd, Santa Clara, CA (US); Michael Guidash,

Rochester, NY (US)

15/100,976 (21) Appl. No.:

(22)PCT Filed: Dec. 3, 2014

PCT/US14/68421 (86)PCT No.:

§ 371 (c)(1),

(2) Date: Jun. 1, 2016

### Related U.S. Application Data

(60) Provisional application No. 61/911,575, filed on Dec. 4, 2013, provisional application No. 61/911,579, filed on Dec. 4, 2013, provisional application No. 61/914, 394, filed on Dec. 11, 2013, provisional application No. 61/918,382, filed on Dec. 19, 2013.

## **Publication Classification**

(51) Int. Cl. (2006.01) H04N 5/355 H04N 5/232 (2006.01)H04N 5/3745 (2006.01)H04N 5/347 (2006.01)H04N 5/361 (2006.01)H04N 9/04 (2006.01)H04N 5/235 (2006.01)

U.S. Cl. CPC ...... H04N 5/355 (2013.01); H04N 9/045 (2013.01); H04N 5/23245 (2013.01); H04N 5/2355 (2013.01); H04N 5/347 (2013.01); H04N 5/361 (2013.01); H04N 5/37457 (2013.01)

#### (57)ABSTRACT

A pixel array within an integrated-circuit image sensor is exposed to light representative of a scene during a first frame interval and then oversampled a first number of times within the first frame interval to generate a corresponding first number of frames of image data from which a first output image may be constructed. One or more of the first number of frames of image data are evaluated to determine whether a range of luminances in the scene warrants adjustment of an oversampling factor from the first number to a second number, if so, the oversampling factor is adjusted such that the pixel array is oversampled the second number of times within a second frame interval to generate a corresponding second number of frames of image data from which a second output image may be constructed.

220~ \_216 Only Columns that  $\geq$  Vth 218~ Version 5 – 4x1 Shared Pixel Q-Binning Analog Read Time 210~[ 204 206~ Integration time 200 202 Readout(DN) Compare SHSadc Convert SHRadc SHSsa  $TGr_{1,3}$ SHRsa RG<sub>1,3</sub> TGc

FIG. 7

293 303 ISP operates as a DMA, receiving subframe data from image sensor and transferring the (emulating ISP reception of full image frame 301 Application Processor reads subframe data Application Processor outputs image frame from memory and sums subframe data to Application Processor configures ISP for Application Processor configues ISP for completed image to DRAM, non-volatile data to image-sensor interface of ISP produce a consolidated image frame ISP processes image frame, writing 295 subframe data to memory IC processing-mode operation Final subframe received? memory, and/or display DMA-mode operation from image sensor) no (get next subframe)

Frame 2— Cond Read Cond Read | Uncond Read \*\*\* ۵ o. Scan Period Cond Read I Cond Read scan period: 7 usf row period/usf: 2 pipeline depth (timeslot/row period): 2 empty row periods/frame: 0 fractionally loaded row periods/frame: 4 Subframe Sequence: 6-1-6-1 row period ★ actual usf -Frame 1-756 concurrency ø 755 group nominal usf 🛧 usf/frame: 14 ▣ • • • • Initial Reset • timeslot (ts) 6-ts • • • • • •

**○** 📟 📟 🗔 Second Conditional Read Third Conditional Read Unconditional Reset First Conditional Read Unconditional Read **Subframe Sequence: 12/1/1/1** usf/frame: 15 scan duration: 15 usf row period/usf: 1 pipeline depth (timeslot/row period): 4 empty row periods/frame: 0 fractionally loaded row periods/frame: 3 FIG. 28A

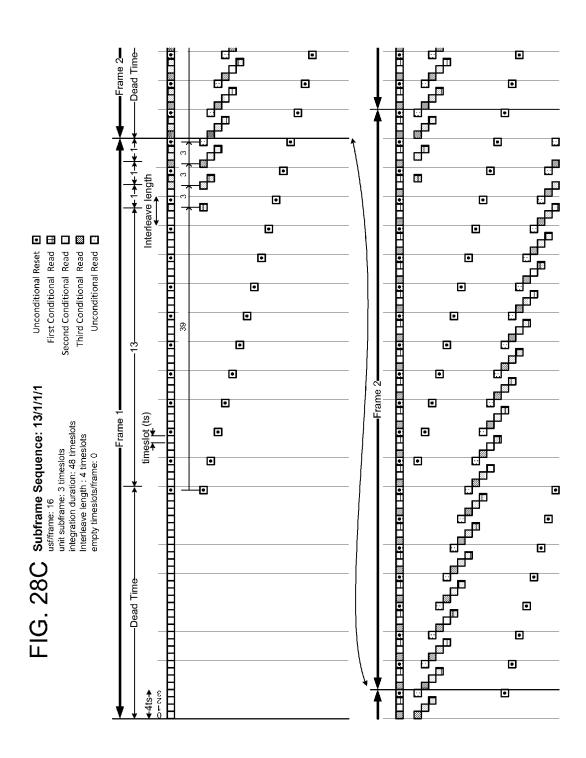

Subframe Sequence: 1/4/4/4

usf/frame: 16 scan period: 4 usf

row period/usf: 3

pipeline depth (timeslot/row period): 1

empty row periods/frame: 9

fractionally loaded row periods/frame: 0

Subframe Sequence: 3/1/6/1 usf/frame: 14

scan period: 7 usf row period/usf: 2 pipeline depth (timeslot/row period): 2 empty row periods/frame: 0 fractionally loaded row periods/frame: 4

App Processor 815 App Processor <u>815</u> App Processor 815 FIG. 32A FIG. 32C Row-Seq Generation Parameters Seq Tablulation Expansion L Parameters Partial Row-Tabulated Row Sednence Table SeqDef Mem <u>790</u> SeqDef Mem <u>790</u> SeqDef Mem <u>790</u> **→** RG ₽TGr ♦ RG ₽TĞ **∳** RG RG ТĞ TGr SS SS RS Row n-1 Line Driver imestamp Row n-2 Clock 801 Row 0 Line Driver Driver Row 1 Line Driver Frame Logic 795 Line Row 787 ĸ rst ĸ ĸ 5 5 5 5 FIG. 31B 799 Start/Stop Timestamps 798 Row Sequence Controller 797 Rd Type Register Start/Stop Comparators 807 Rst Shift Register 803 804 805 806 SE4 SPIFF Register SF3 Shift Register SF2 Shift Register SE1 SPIE Reset-Shift-Enable-**¥** RG <u>\$</u> **₽** RG **↓**TGr 92 ₽TĞ Į Į Ď † S≥ RS RS SS Row n-1 Line Driver Row n-2 Row 0 Line Driver Row 1 Line Driver Line Driver Row Logic 780 FIG. 31A 781 787 ß ıst ß ᇗ 5 5 5 5 Row Sequence Controller 781 SeqDef Mem Rd Type Rst Addr Decoder 790 785 1bbA faЯ Read Addr Tebooed 783 Rd Addr

10° \_0 Binned (reduced-resolution) <u>0</u> Unconditonal Read Photo electrons per image pixel 937 935 · Binned global -Binned last, keep unbinned -Binned last, keep all 931 ----- Not binned 9 933 ° 35 20 5 9 30 25 [ Bb ] (Y)RNS oits AsioN-ot-IsngiS Full-Resolution (i.e., unbinned) Conditional Reads based on unbinned readgenerate pixel value for each full-resolution pixel Partial Binning to improve low-light SNR without compromising spatial resolution values extracted from out(s) and, optionally, binned read-out 913 915 ž unconditional read/reset Subframe 1: unbinned Subframe 2: unbinned conditional read/reset conditional read/reset Subframe N: Binned 917 Fig. 43 Low-Light? pased on values obtained each full-resolution pixel generate pixel value for neighboring bin-groups for pixel bin-group and Yes Hybrid (binned and subframe read-out unbinned) Row i Row i+2 Reconstruction Selective Initial Reset

FIG. 53

Sat @ 1 U=Underthresh, O S X=readout, S=Sat \*\*may also yield valid read at 2USF (or even 1 USF), depending on saturation threshold Interval after which valid read occurs S  $\times$  $\times$  $\times$  $\times$ 4 Subframe >thr @ 1\_ = 5 5  $\supset$ × က S ×  $\times$  $\supset$  $\supset$ × ~ ഗ  $\times$  $\supset$  $\supset$ ⊃ 2 USF 5 5 5 S S S S  $\times$ 0 conditional read event (unconditional read also occurs) 4 ဖ က Luminance >thr @ 2 ¬ Range FIG. 55B ®N+1 USF N USF\* Sat @ N J >thr @ N - >thr @ N - >thr @ N+1 - >thr @ N+2 - > O N+2 USF Luminance <u>@</u>@ စ  $\Theta$ Dynamically Selected Subframe Sequencing Decreased Power Consumption Increased Dynamic Range FIG. 55A FIG. 54 No OverSmp Luminance Sat .-Thresh

Oversample <del>X</del> ◆←No/negligible short-subframe luminance values beyond dynamic range of (M-1)x scan profile— Scan Family Params Luminance values yielding saturation or near saturation in shortest subexposure-Auto-Exp (AE) Control Pixel Values Histogram Constructor Exp Time, Aperture, ISO Select Oversample Flags × **Control Logic** Auto Dynamic Range (ADR) Control FIG. 58 DR Sel FIG. 60 Oversample Motion/Shake Possible And No Motion/ Shake Concerns ► Flags **→** Pixel Values No Oversample Scan Family Column Read-Out Logic Conditonal-Read Pixel Array  $\widetilde{\mathbf{x}}$ Control Logic Scan Prm (N:1:1:1) Scan Prm (N:1.5:1.5) Scan Prm (N+3) Scan Prm (N:3) **AE/ADR Control** 1231 71, DR Sel Row Drivers/ SF Shift Regs \_ Wux ₩ Row Seq Control aperture for best shadow exposure Set overall integration time, ISO, Shift among exposure family members as required by DR, Gather long/short subframe histogram statistics FIG. 57 motion, and shake 1203 1205 1201

Blur-Mitigated HDR Image Data Image Reconstructor Blur-Mitigating Exposure Merge Filtered Short Exp Merge Ratio FIG. 64 Noise Filter Actual Merge Ratio Lookup Balanced Short Exp ≅≅ Y Balanced Long Exp Minimum Merge Ratio Lookup Exposure Balance Blur-Mitigated

Output Image Long Exp Short Exp Long SF Saturation (Minimum Blur) Reconstruction with Motion Reduction Shadow (Maximum Blur) Midtones (Blur Mitigation) Two-Frame Long Exp Short Exp Sum FIG. 62 Scan-Sequence-Dependent Saturation (No Read-Out) N:1.5:1.5 N:1:1:1 Threshold -Noise Floor Reconstruction Inputs z nunsed 1.5 1.5 z nunsed nunsed S:S z က 1000 8 4

### HIGH DYNAMIC-RANGE IMAGE SENSOR

## TECHNICAL FIELD

[0001] The present disclosure relates to the field of electronic image sensors, and more specifically to a sampling architecture for use in such image sensors.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0002] The various embodiments disclosed herein are illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings and in which like reference numerals refer to similar elements and in which:

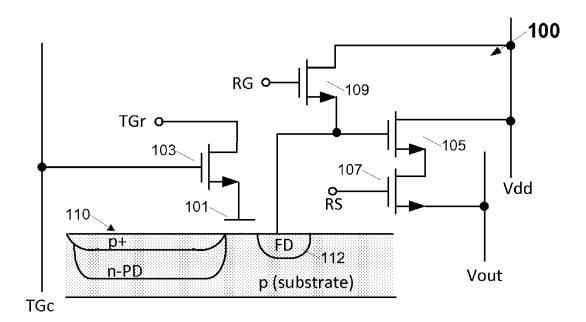

[0003] FIG. 1 illustrates an embodiment of a modified 4-transistor pixel in which a non-destructive overthreshold detection operation is executed to enable conditional-read operation in conjunction with correlated double sampling;

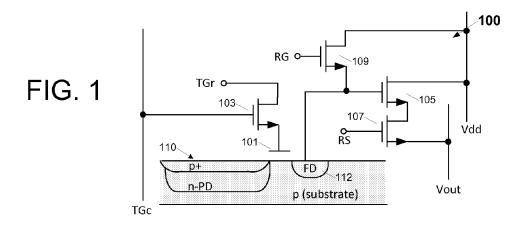

[0004] FIG. 2 is a timing diagram illustrating an exemplary pixel cycle within the progressive read-out pixel of FIG. 1;

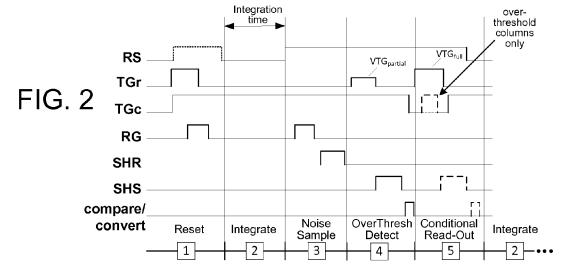

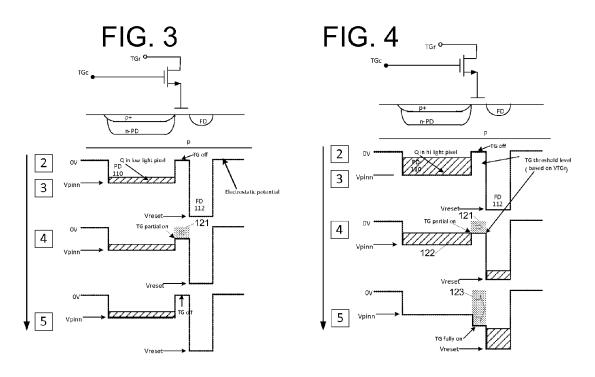

[0005] FIGS. 3 and 4 illustrate exemplary electrostatic potential diagrams for the photodiode, transfer gate and floating diffusion of FIG. 1 below their corresponding schematic cross-section diagrams;

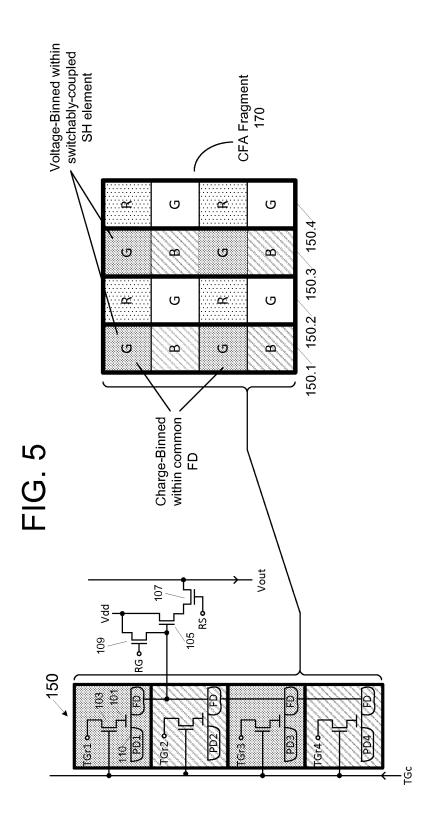

[0006] FIG. 5 illustrates an alternative binning strategy that may be executed with respect to a collection of 4×1 quad-pixel blocks in conjunction with a color filter array;

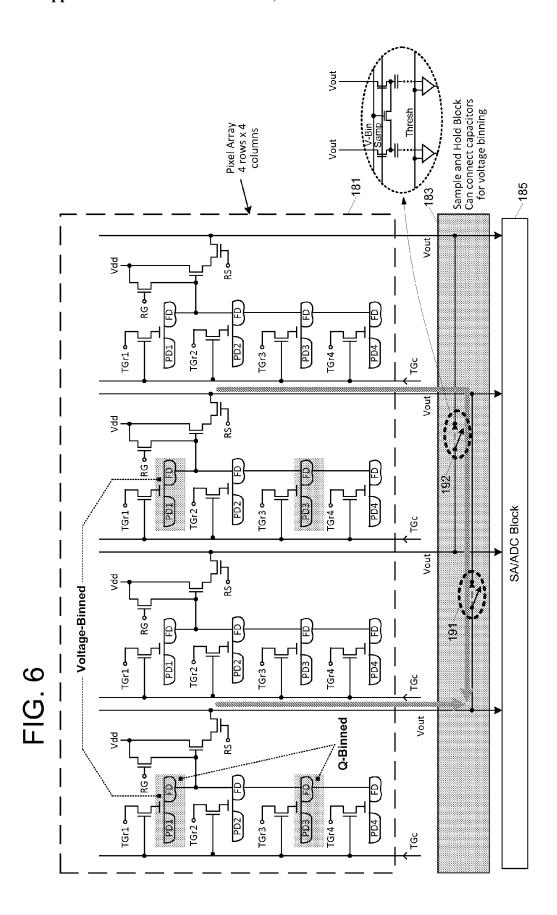

[0007] FIG. 6 illustrates a column-interconnect architecture that may be applied to enable voltage-binning of analog signals read-out from selected columns of 4×1 quad-pixel blocks:

[0008] FIG. 7 illustrates an exemplary timing diagram of binned-mode read-out operations within the 4×1 quad-pixel architecture of FIGS. 5 and 6;

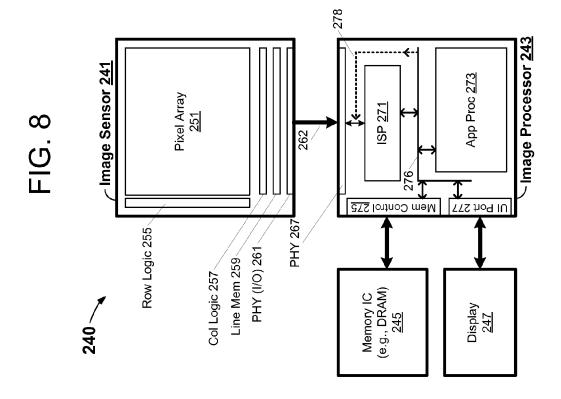

[0009] FIG. 8 illustrates an embodiment of an imaging system having a conditional-read image sensor together with an image processor, memory and display;

[0010] FIG. 9 illustrates an exemplary sequence of operations that may be executed within the imaging system of FIG. 8 in connection with an image processing operation;

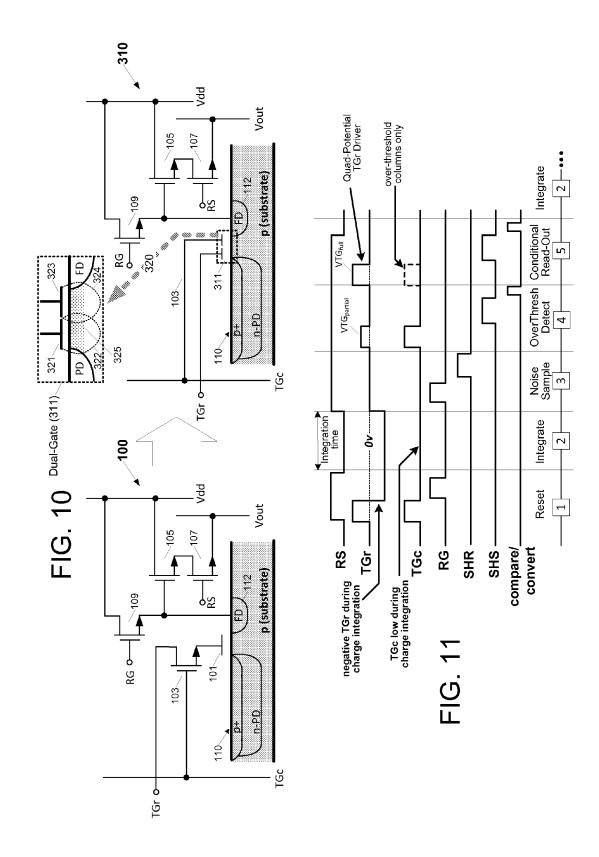

[0011] FIG. 10 contrasts embodiments of the conditional-read pixel of FIG. 1 and a "split-gate" pixel;

[0012] FIG. 11 is a timing diagram illustrating an exemplary pixel cycle (reset/charge integration/read-out) within the split-gate pixel of FIG. 10;

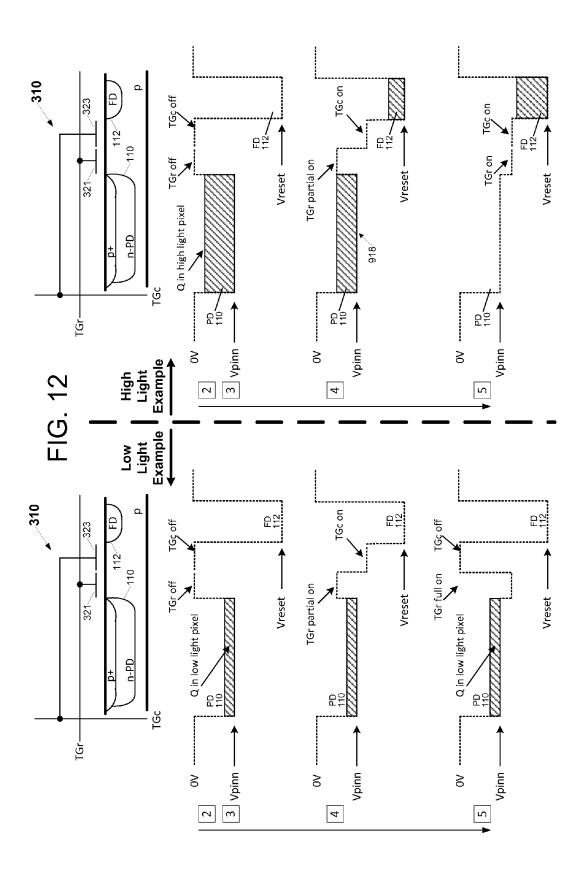

[0013] FIG. 12 illustrates exemplary low-light and highlight operation of the split-gate pixel of FIG. 10, showing electrostatic potential diagrams in each case beneath schematic cross-section diagrams of the photodetector, dual-control transfer gate and floating diffusion;

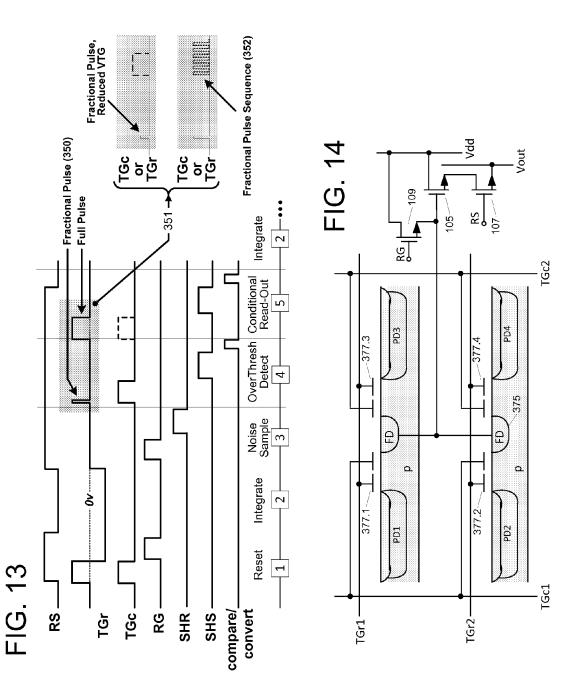

[0014] FIG. 13 illustrates an alternative overthreshold detection operation within the split-gate pixel of FIG. 10;

[0015] FIG. 14 illustrates a quad-pixel, shared floating diffusion image sensor architecture in which pairs of row and column transfer-gate control lines are coupled to a dual-gate structure within each of four split-gate pixels;

[0016] FIG. 15 illustrates a 4×1 block of split-gate pixels (a quad, split-gate pixel block) that may be operated in binned or independent-pixel modes as described above, for example, in reference to FIG. 5;

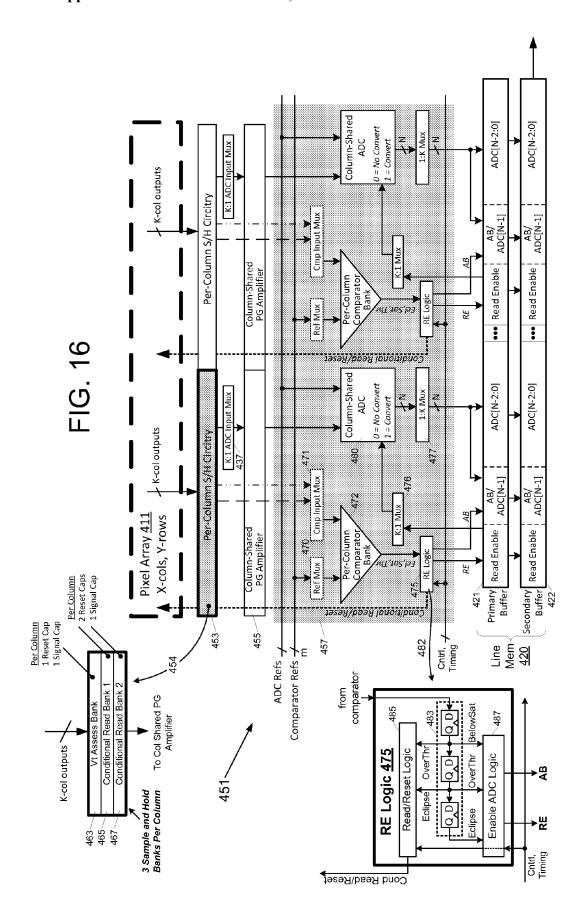

[0017] FIG. 16 illustrates an embodiment of a low power image sensor that may be used to implement component circuitry within the image sensor of FIG. 8;

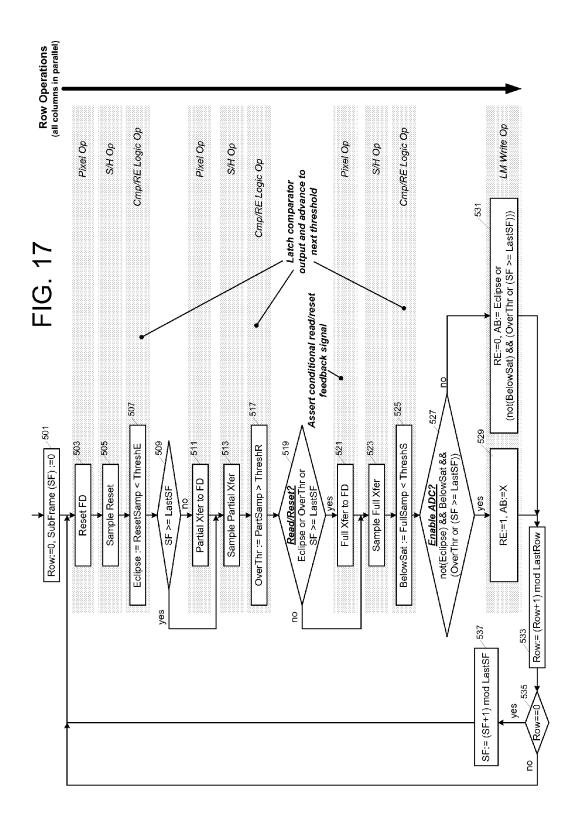

[0018] FIG. 17 illustrates a sequence of operations that may be executed within the pixel array, sample/hold banks and comparator circuitry of FIG. 16 to carry out pixel state assessment and enable subsequent ADC operation for row after row of pixels;

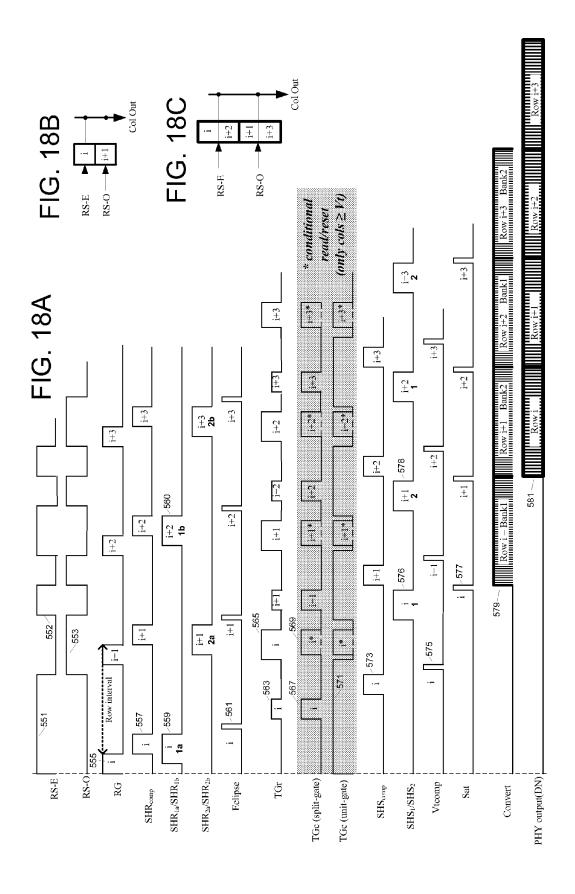

[0019] FIG. 18A illustrates an exemplary timing diagram in accordance with the sensor architecture of FIG. 16 and operational sequence of FIG. 17, including alternate TGc waveforms corresponding to split-gate and continuous-gate pixel array embodiments, respectively;

[0020] FIGS. 18B and 18C present exemplary read-out sequences that may be employed with respect to even and odd rows of pixels.

[0021] FIG. 19 illustrates an embodiment of multi-bank sample-and-hold circuit that may be used to implement the sample-and-hold (S/H) circuitry depicted in FIG. 17;

[0022] FIG. 20 illustrates an exemplary sample and hold pipeline corresponding generally to the S/H bank usage intervals within the timing arrangement of FIG. 18;

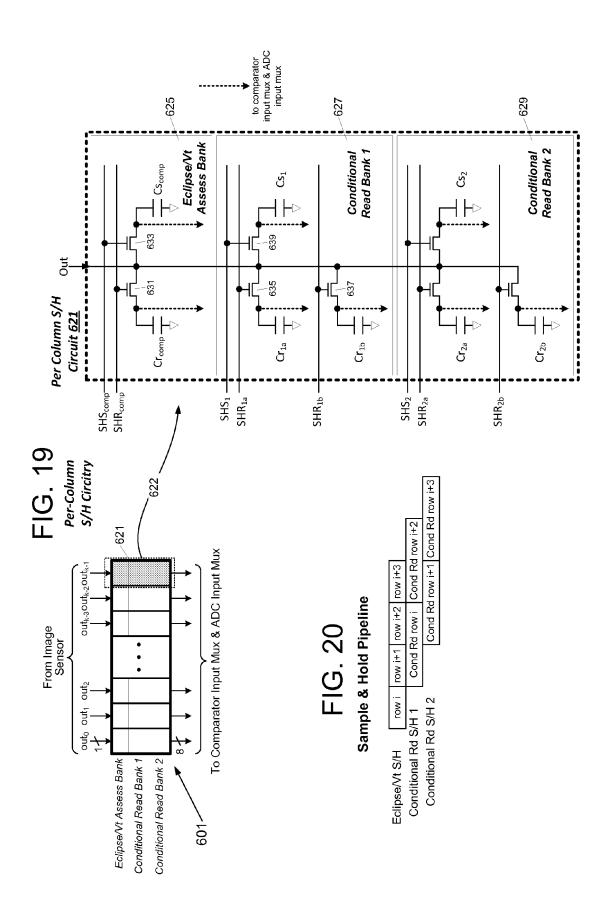

[0023] FIG. 21 illustrates embodiments of a reference multiplexer, comparator input multiplexer and comparator that may be used to implement like-named components depicted in FIG. 16;

[0024] FIG. 22 illustrates embodiments of a column-shared programmable gain amplifier and K:1 ADC input multiplexer that may be deployed within the embodiment of FIG. 16.

[0025] FIG. 23A illustrates embodiments of a read-enable multiplexer, ADC-enable logic and ADC circuit that may be used to implement the K:1 read-enable multiplexer and ADC circuitry of FIG. 16;

$[0026]~{\rm FIG}.~23{\rm B}$  illustrates a convert signal timing diagram corresponding to FIG.  $23{\rm A};$

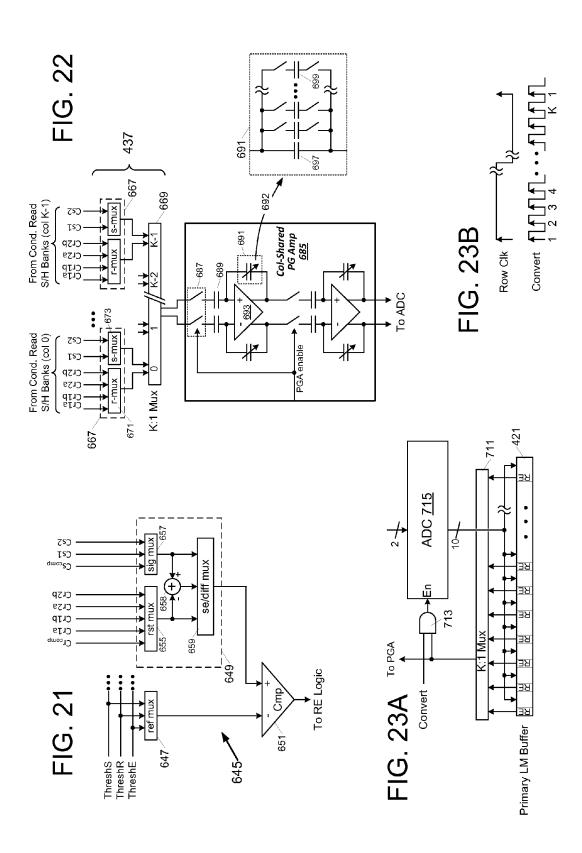

[0027] FIG. 24 illustrates an exemplary K-column section of an image sensor having logic to carry out read-dilation operations;

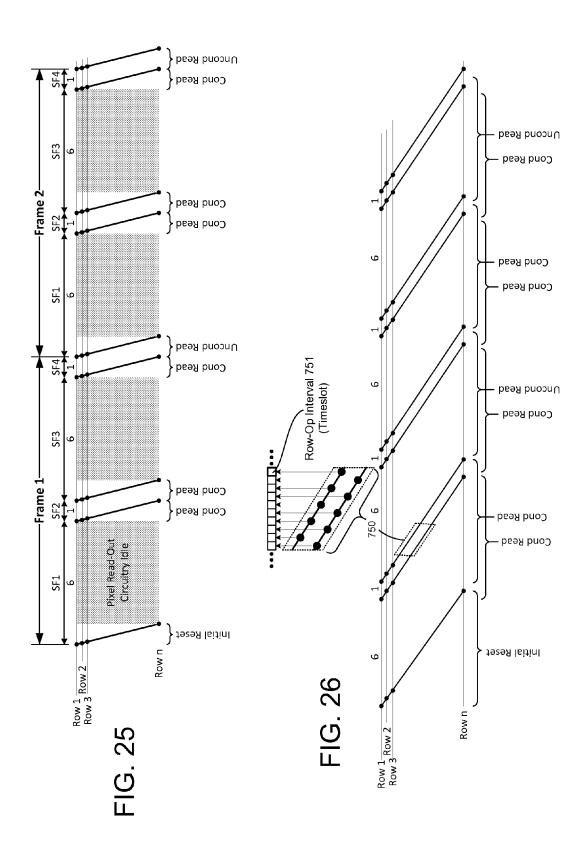

$\begin{tabular}{ll} [0028] & FIG.~25 illustrates an exemplary subframe read-out sequence within a conditional read/reset image sensor; \end{tabular}$

[0029] FIG. 26 illustrates an alternative read-out approach that expands the sub-frame read-out time and smoothes (balances) resource utilization across the frame interval;

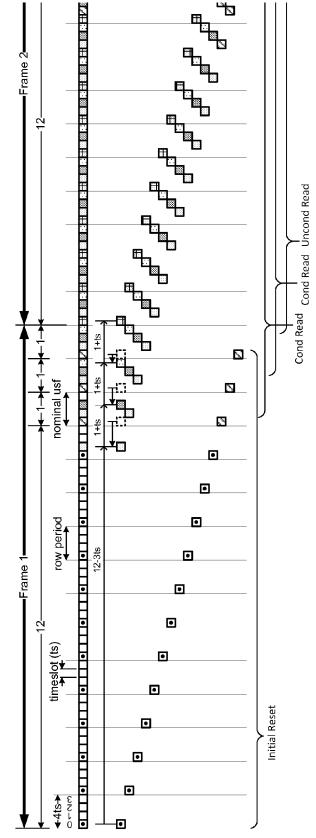

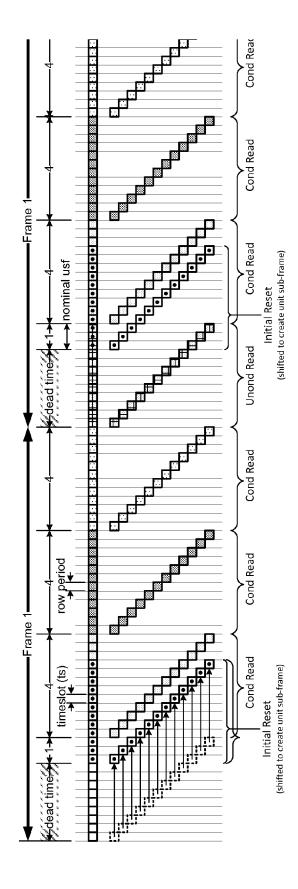

[0030] FIG. 27 illustrates an exemplary 6-1-6-1 subframe read-out in greater detail, showing timeslot utilization within an image sensor embodiment having a 12-row pixel array; [0031] FIG. 28A illustrates an alternative subframe

sequence in which a relatively long subframe is followed by a sequence of three relatively short subframes in a 12-1-1-1 pattern

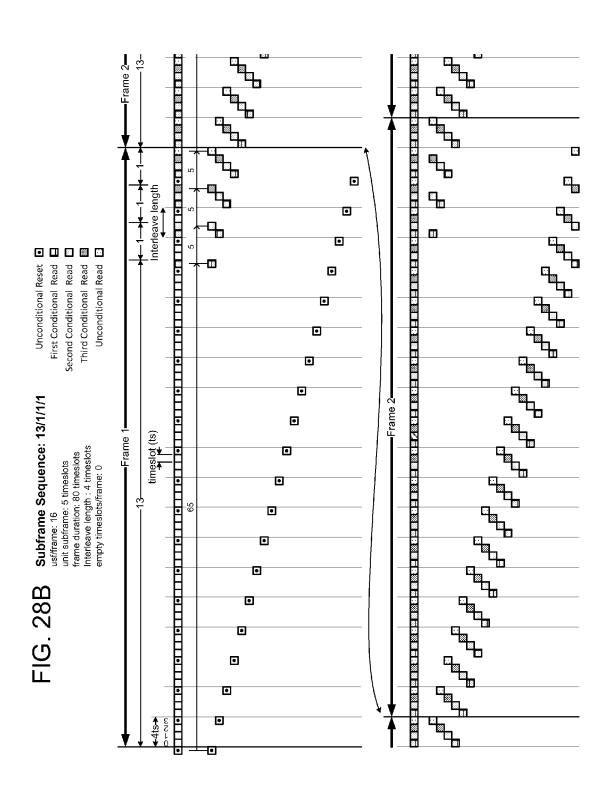

[0032] FIG. 28B illustrates an A=13, 13-1-1-1 subframe read-out sequence designed according to an alternative timing enforcement approach;

[0033] FIG. 28C illustrates an A=39, B=3, 39-3-3-3 subframe read-out sequence designed according to the alternative timing enforcement approach;

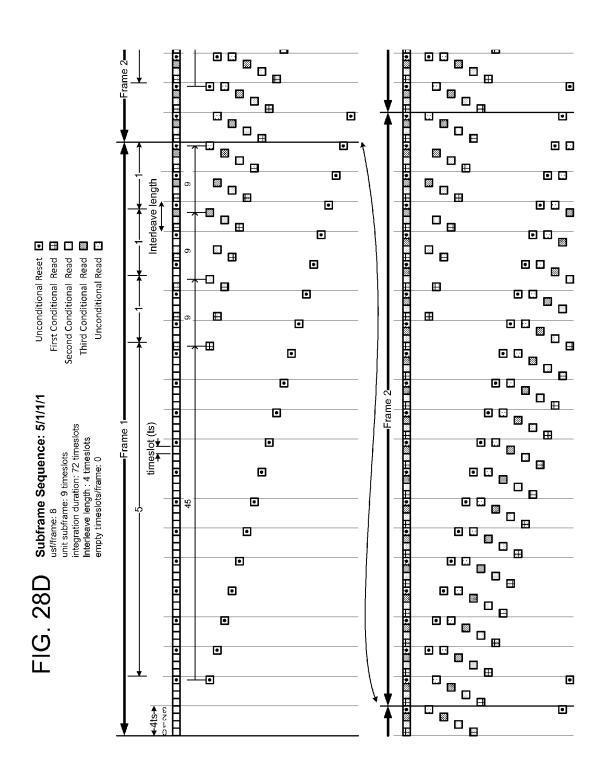

[0034] FIG. 28D shows another scheduling solution for 20 rows and 80 timeslots, this time for A=5 and a 5-1-1-1 policy;

[0035] FIG. 29 illustrates a 1-4-4-4 subframe read-out sequence that, at least in terms of subframe read-out concurrency, represents the inverse of the 12-1-1-1 subframe sequence of FIG. 28A;

[0036] FIG. 30 illustrates another dead-time subframe read-out sequence, in this case having a 3-1-6-1 pattern;

[0037] FIG. 31A illustrates an embodiment of a row logic circuit that may be used to establish a wide variety of run-time and/or production-time selectable subframe sequences including, without limitation, those depicted in FIGS. 27-30;

[0038] FIG. 31B illustrates another embodiment of a row logic circuit that may be used to establish a wide variety of subframe sequences including, without limitation, those depicted in FIGS. 27-30;

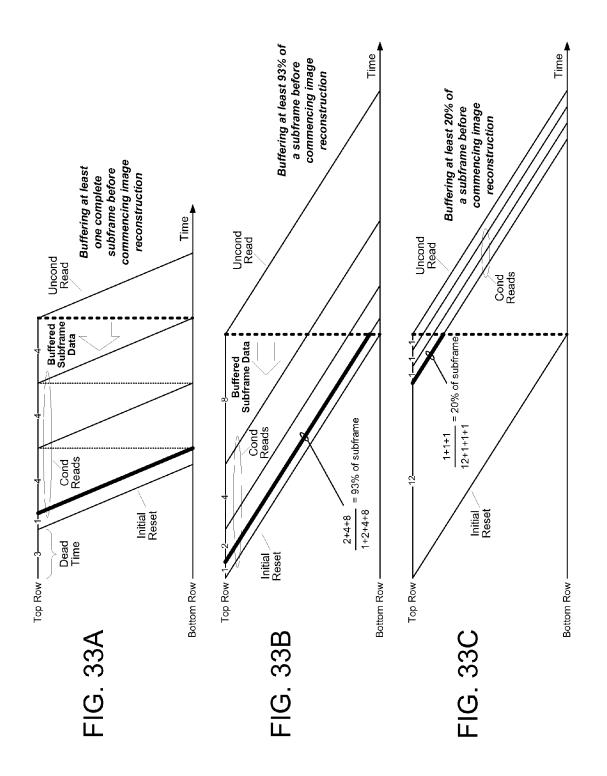

[0039] FIGS. 32A-32C illustrate alternative parameter loading operations with respect to the sequence definition memory of FIG. 31A;

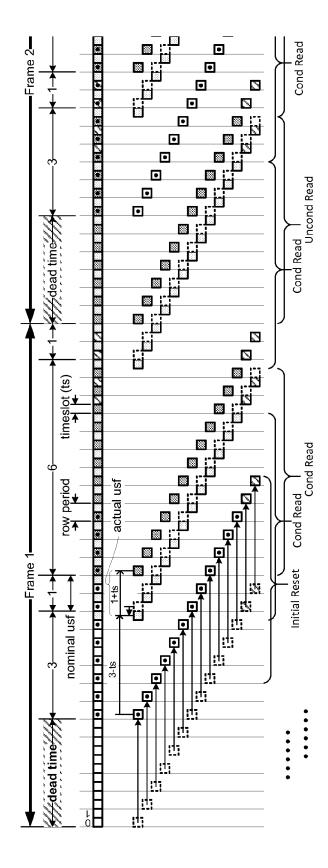

[0040] FIGS. 33A-33C contrast exemplary subframe sequences in which read-out operations are spread relatively evenly over a frame interval, front-loaded and back-loaded, respectively:

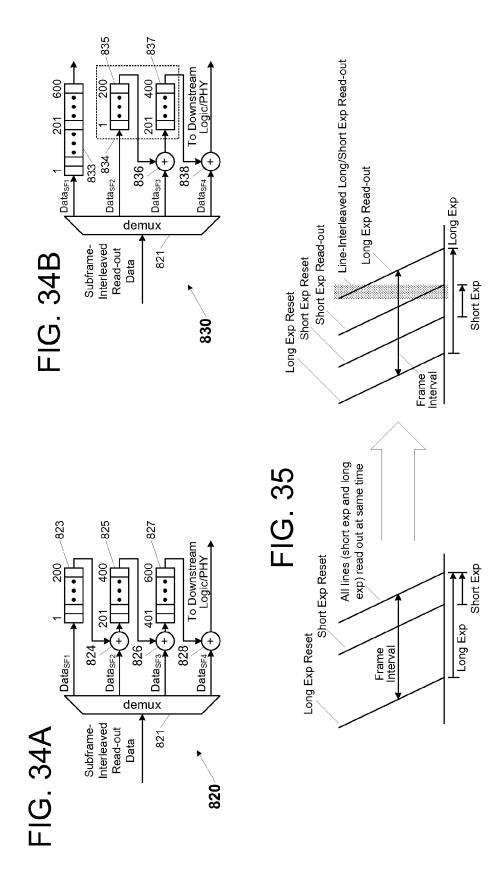

[0041] FIG. 34A illustrates an embodiment of a buffering circuit that may be used to reconstruct an image frame from the 12-1-1-1 subframe sequence of FIG. 33C with only partial subframe buffering;

[0042] FIG. 34B illustrates an alternative embodiment of a buffering circuit that enables partial image reconstruction from the 12-1-1-1 subframe sequence of FIG. 33C;

[0043] FIG. 35 contrasts a more artifact-prone fully-interleaved read-out approach (left) and a more artifact-resistant frame-centered short-exposure approach (right);

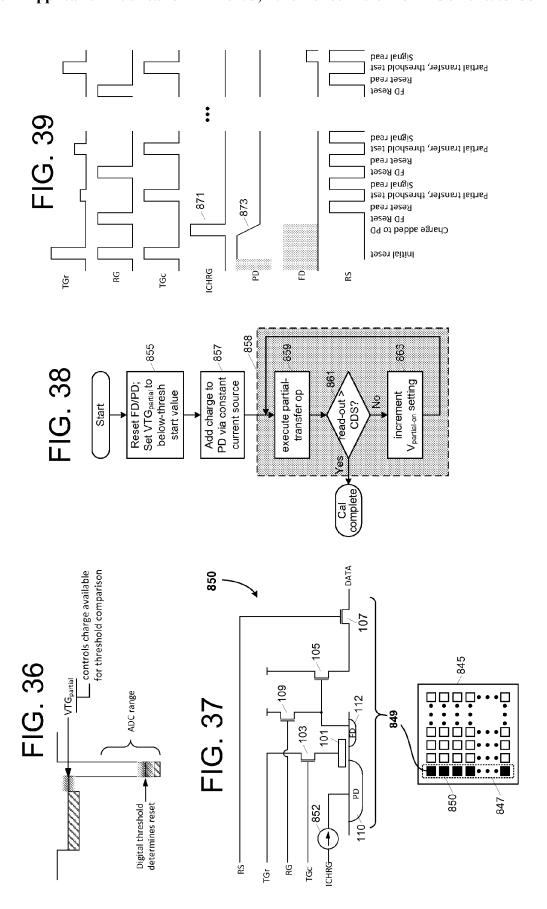

[0044] FIG. 36 illustrates the relationship between the partial-on transfer gate voltage applied to effect a partial read-out of photodiode state and the conditional read/reset threshold against which the partial-read signal is tested to determine whether to execute a full photodiode read-out and reset:

[0045] FIG. 37 illustrates an embodiment of a pixel array having a "dark" column of pixel calibration circuits disposed at a peripheral location outside the focal plane;

[0046] FIGS. 38 and 39 illustrates an exemplary sequence of calibration operations and corresponding signal waveforms within calibration circuit of FIG. 37;

[0047] FIG. 40 illustrates operations carried out within an application processor and image sensor to effect an alternative, analytically-driven calibration of the partial-on transfer gate voltage;

[0048] FIG. 41 illustrates, graphically, a determination of a threshold-correlated ADC value based on a collection of ADC values for underthreshold and overthreshold pixels;

[0049] FIG. 42 illustrates an alternative analytical calibration technique that may be applied within image sensors that lack the above-described hybrid read-out mode or for which such mode has been disabled;

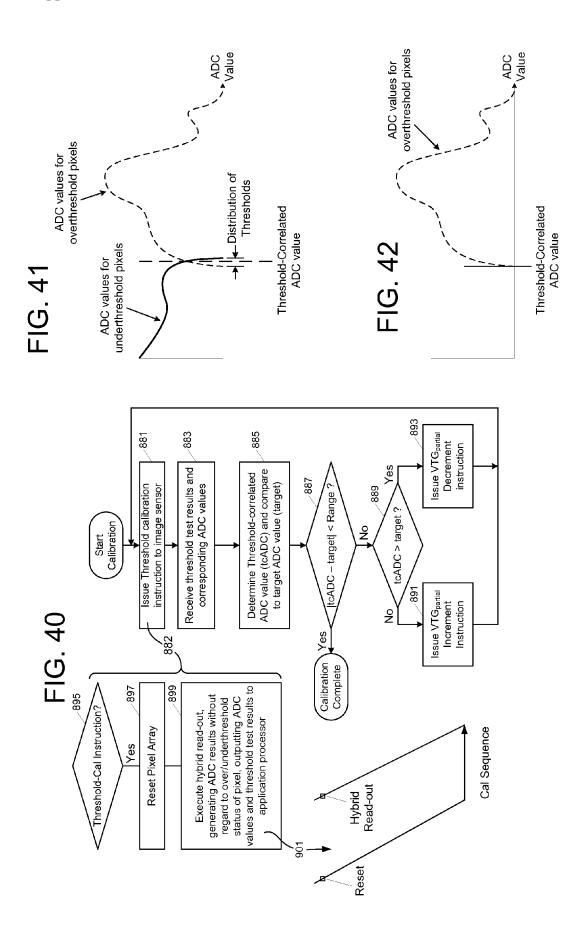

[0050] FIGS. 43 and 44 illustrate an exemplary "partial binning" imaging approach in which a pixel array is conditionally read/reset in an unbinned, full-resolution mode for all but the final subframe of a given image frame, and then unconditionally read/reset in a binned, reduced-resolution mode for the final subframe;

[0051] FIG. 45 illustrates qualitative differences between varying image frame read-out/reconstruction modes within a pixel array;

[0052] FIG. 46 illustrates an exemplary segment of a bin-enabled pixel array together with corresponding color filter array (CFA) elements;

[0053] FIG. 47 illustrates an example of selective image reconstruction with respect to a pixel bin group;

[0054] FIG. 48 illustrates an exemplary approach to combining binned and unbinned read-out results in bright-light reconstruction of full-resolution pixel values;

[0055] FIGS. 49 and 50 illustrate a more detailed example of predicting end-of-frame charge accumulation states within bin group pixels for purposes of estimating full-resolution pixel contributions to binned read-outs;

[0056] FIG. 51 illustrates a bi-linear interpolation that may be applied to generate final full-resolution pixel values for the pixels of a bin-group-bounded pixel set following determination of a low-light condition;

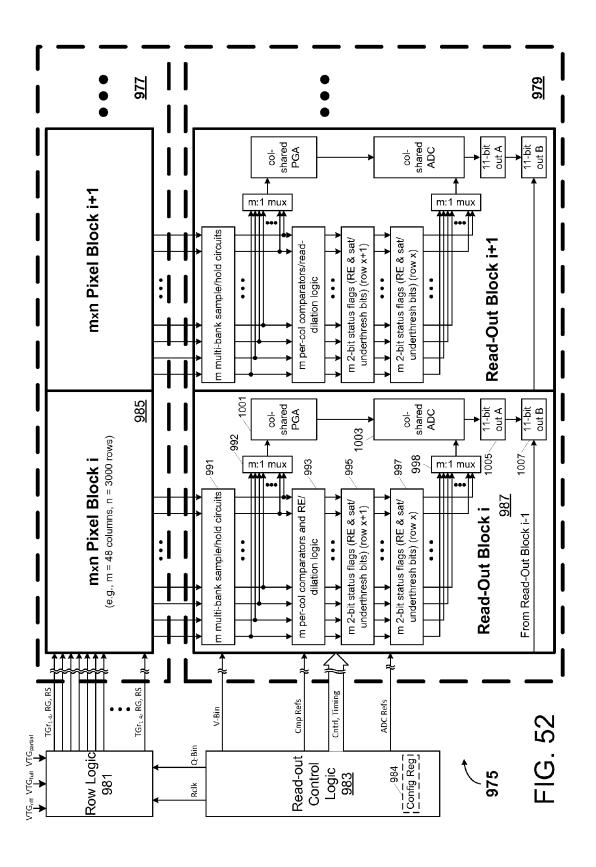

[0057] FIG. 52 illustrates an embodiment of an image sensor having a conditional read/reset pixel array, column read-out circuitry, row logic and read-out control logic;

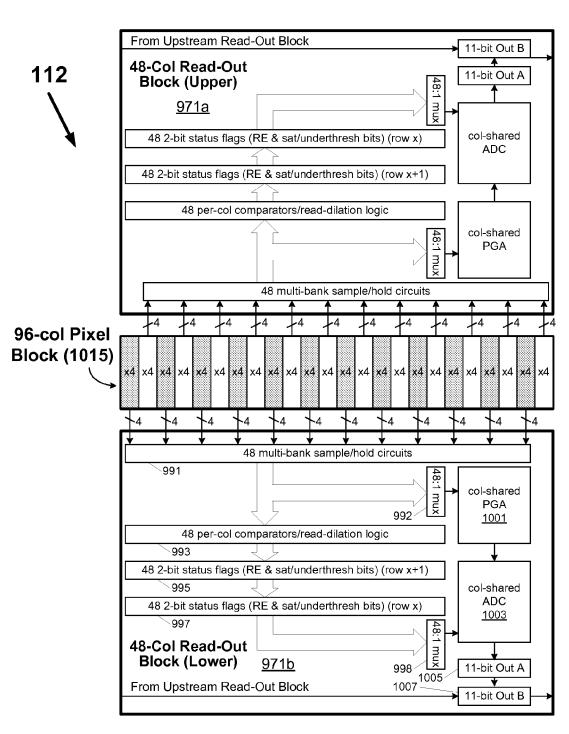

[0058] FIG. 53 illustrates an exemplary image sensor architecture in which each pixel block of a pixel array is sandwiched between upper and lower read-out blocks;

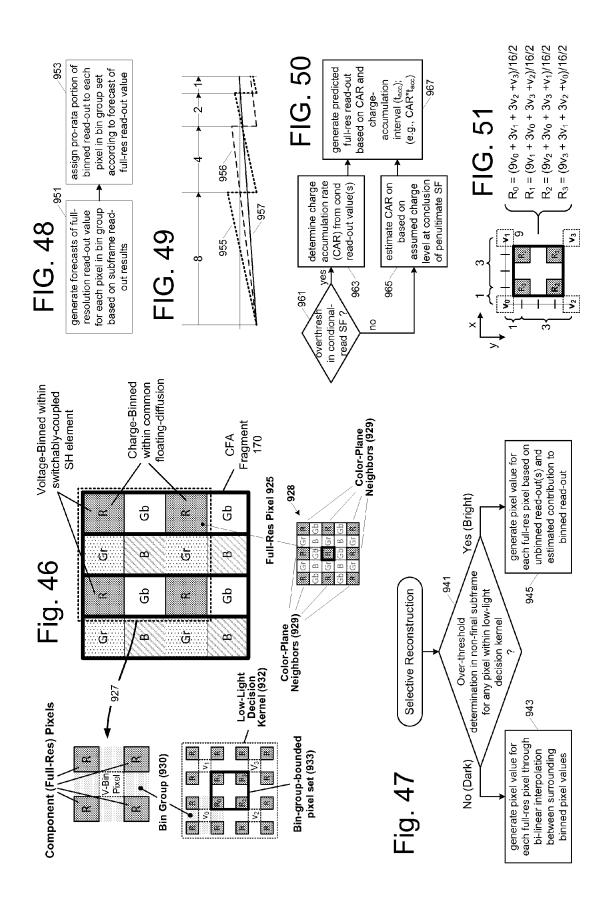

[0059] FIG. 54 illustrates an exemplary imaging sensor embodiment in which the oversampling factor is varied dynamically between minimum and maximum values;

[0060] FIG. 55A illustrates an exemplary set of pixel charge integration profiles that occur at various luminance levels and the corresponding read-out/reset events given an N:1:1:1 scan sequence;

[0061] FIG. 55B is a table illustrating exemplary pixel state assessment results and read-out events for each of the four subframes and eight luminance levels discussed in reference to FIG. 55A;

[0062] FIG. 55C illustrates the various charge integration periods corresponding to valid read-out events within the exemplary luminance ranges of FIG. 55A;

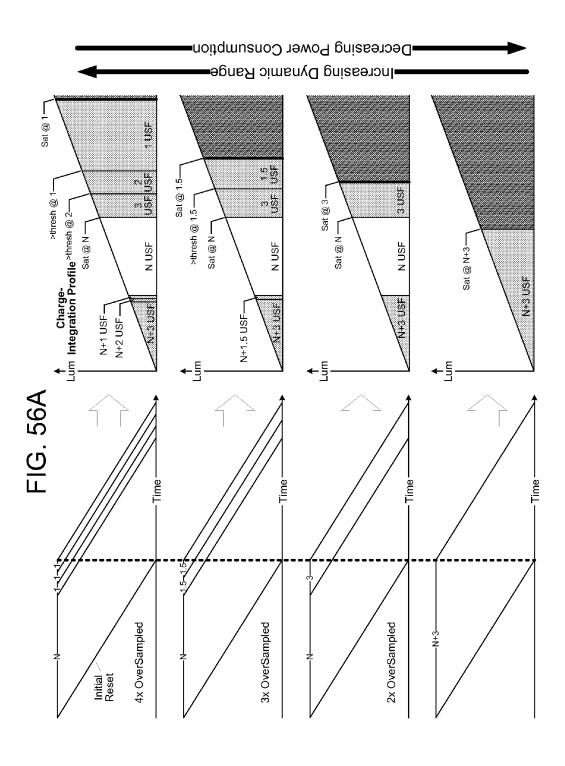

[0063] FIG. 56A illustrates the exemplary charge-integration profile of FIG. 55C adjacent an N:1:1:1 scan sequence together with corresponding charge-integration profiles that result as the oversampling factor is dropped from  $4\times$  to  $1\times$ , while maintaining the same long subframe duration and evenly splitting the remaining frame interval among one or more short subframes for each oversampled scan sequence;

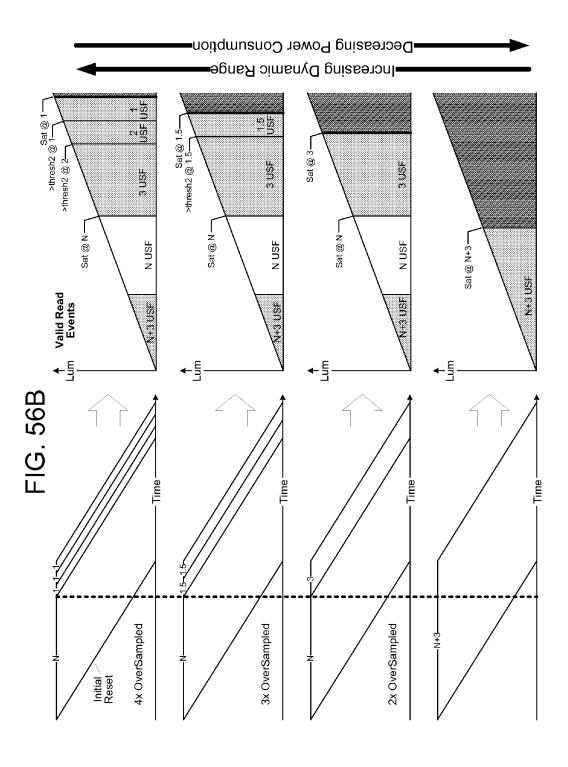

[0064] FIG. 56B illustrates charge integration profiles for the same scan sequence family shown in FIG. 56A, but with raised conditional-read thresholds applied at the conclusion of short subframes to avoid low-light conditional-read events:

[0065] FIG. 57 illustrates a set of operations that may be executed within a conditional-read image sensor or associated integrated circuit to dynamically scale the sensor's dynamic range and power consumption based, at least in part, on the scene being imaged;

[0066] FIG. 58 presents an example of dynamic transition between scan sequences of an exposure family operation;

[0067] FIG. 59 illustrates an image sensor embodiment that carries out the exposure-setting and dynamic range scaling operations as described in reference to FIGS. 57 and 58.

[0068] FIG. 60 illustrates an embodiment of a control logic circuit that may be used to implement the control logic of FIG. 59:

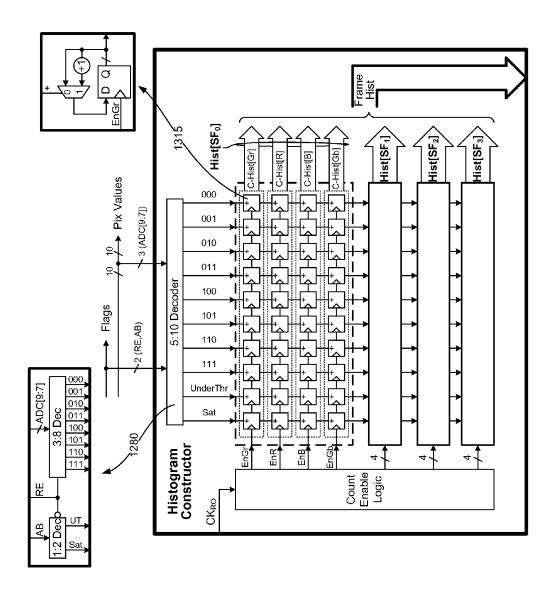

[0069] FIG. 61 illustrates an embodiment of a histogram constructor that may be used to implement the histogram constructor of FIG. 60;

[0070] FIG. 62 illustrates a photoelectric charge-integration range in log scale, showing an exemplary noise floor, conditional-read threshold, and saturation threshold;

[0071] FIG. 63 illustrates summation of short-exposure pixel values in the context of a family of scan sequences each of which includes, respectively one, two or three short subexposures:

[0072] FIG. 64 illustrates an embodiment of a blur-mitigating image reconstructor that may be used to implement the two-frame reconstruction module of FIG. 63;

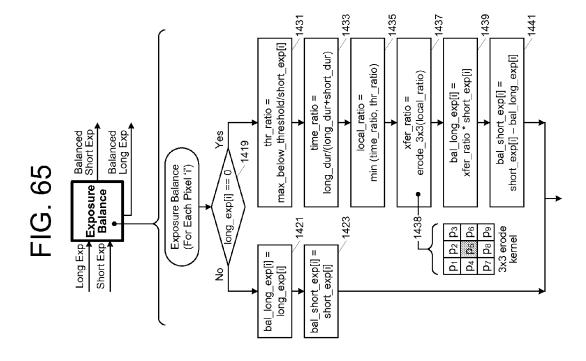

[0073] FIG. 65 illustrates an exemplary exposure balancing operation carried out within the exposure balancing unit of FIG. 64:

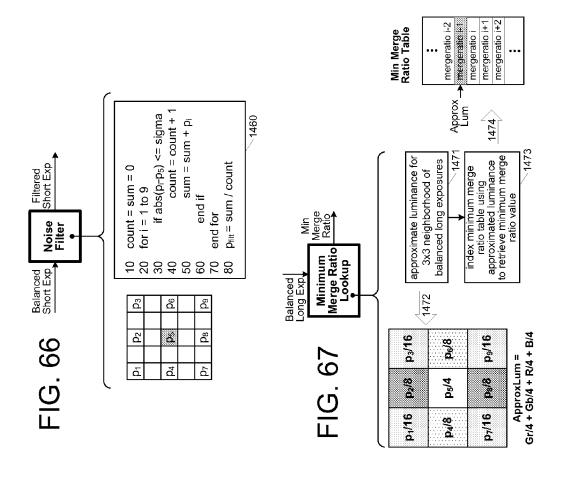

[0074] FIG. 66 illustrates an exemplary embodiment of the noise filter applied to the balanced short exposure within the two-frame reconstruction logic of FIG. 64;

[0075] FIG. 67 illustrates an embodiment of the minimum difference lookup of FIG. 64;

[0076] FIG. 68 illustrates an exemplary actual-difference lookup operation carried out using the balanced short and long exposure values and the luminance-indexed minimum difference value output from the minimum difference lookup unit:

[0077] FIG. 69 illustrates an exemplary exposure merge operation carried out using the filtered short exposure value, balanced long exposure value and difference value output from the actual difference lookup unit;

[0078] FIG. 70 illustrates an alternative scan sequence family in which an otherwise solitary long subexposure has been split into medium-duration subexposures;

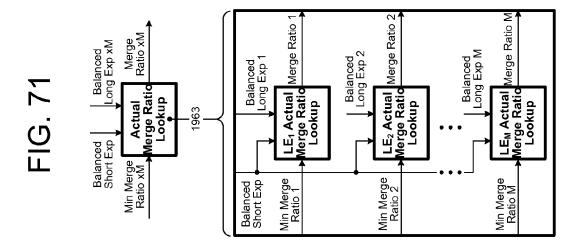

[0079] FIG. 71 illustrates an alternative implementation of the actual merge ratio lookup function in an embodiment or configuration that includes multiple long or medium exposure subframes;

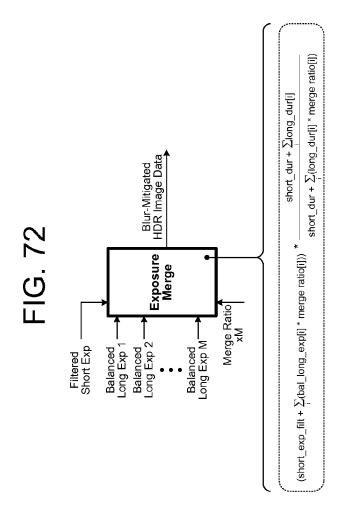

[0080] FIG. 72 illustrates an embodiment of an exposure merge function to be applied in combination with the multi-component actual merge ratio lookup of FIG. 71

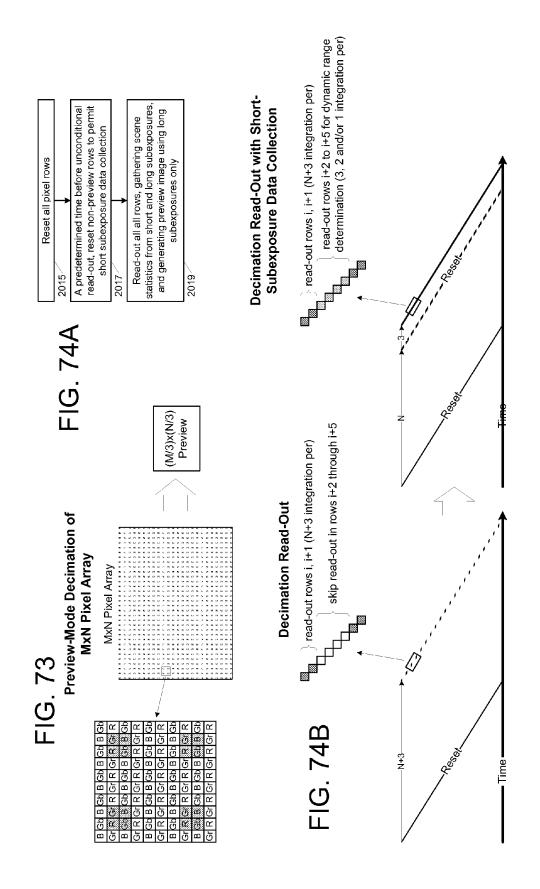

[0081] FIG. 73 illustrates an exemplary sensor-decimation mode that may be employed within the various sensor embodiments presented herein to enable generation of a reduced resolution preview image or before recording video frames;

[0082] FIG. 74A illustrates an alternative decimated readout mode in which at least some of the non-preview pixel rows are used to capture short sub-exposure data for purposes of characterizing the dynamic range and/or motion characteristics of the scene being previewed;

[0083] FIG. 74B contrasts the basic and short-exposure-data-gathering decimation readout modes described in reference to FIGS. 71 and 72A;

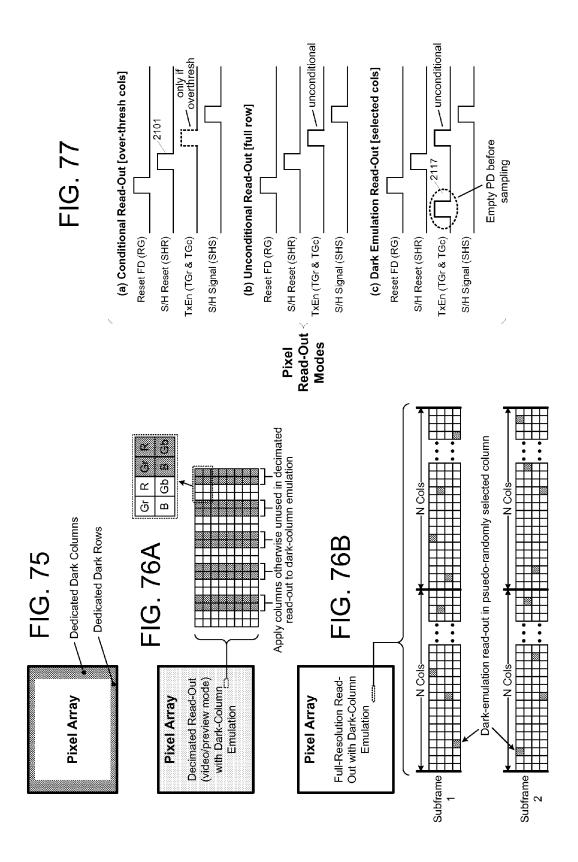

[0084] FIG. 75 illustrates a pixel array having shielded dark correction blocks;

[0085] FIG. 76A illustrates an exemplary 2:1 video-capture decimation mode in which unused pixel columns are applied to emulate a dark-column read;

**[0086]** FIG. **76**B illustrates an exemplary dark-emulation with respect to a full-resolution temporally-oversampled pixel array;

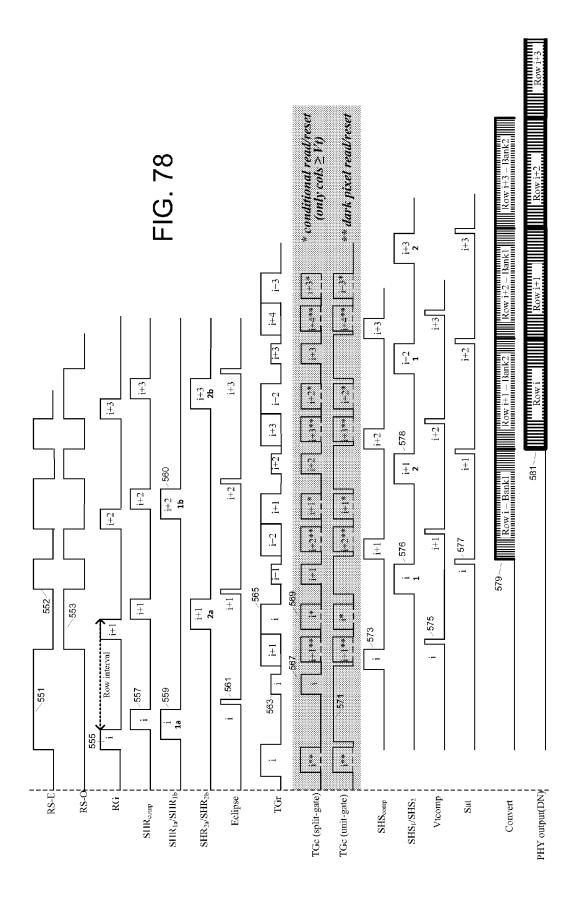

[0087] FIG. 77 illustrates exemplary timing diagrams for a number of pixel read-out modes within a conditional-read image sensor, including the conditional and unconditional read-out modes described above as well as a dark-emulation read-out mode;

[0088] FIG. 78 illustrates a more complete timing diagram for emulated dark-pixel read-out, showing the pipelined sequence of operations within the pixel array, sample-and-hold logic, comparator and ADC circuitry;

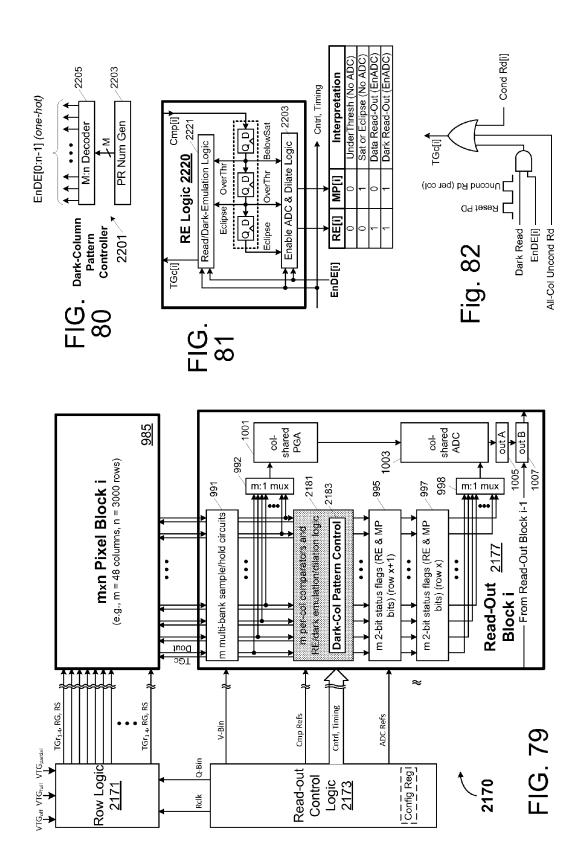

[0089] FIG. 79 illustrates an exemplary image sensor architecture that supports emulated-dark read-out operations discussed in reference to FIGS. 76 through 78;

[0090] FIG. 80 illustrates an embodiment of a dark-column pattern controller that may be used to implement the pattern controller of FIG. 79;

[0091] FIG. 81 illustrates an embodiment of a read-enable logic circuit modified to support dark-emulation read-out; [0092] FIG. 82 illustrates an embodiment of a read/dark-emulation logic circuit that may be deployed within the read-enable logic circuit of FIG. 81; and

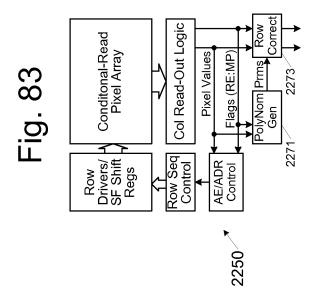

[0093] FIG. 83 illustrates an embodiment of a conditionalread image sensor that applies dark-emulation read-out data to perform row noise correction.

#### DETAILED DESCRIPTION

[0094] In various embodiments disclosed herein, an oversampled image sensor is operated in both full-resolution and reduced-resolution (enhanced low-light sensitivity) read-out modes during respective subframes of an exposure interval. By this arrangement, spatial resolution of the image sensor is preserved while also enhancing low-light sensitivity. In a number of embodiments, reduced-resolution image data is selectively applied in final image reconstruction according to a light-intensity determination based upon the subframe read-outs themselves. In other embodiments, subframe intervals are programmably controlled to balance read-out circuitry utilization and limit on-board data storage needs while achieving desired imaging results effects. In yet other embodiments, a binary threshold used to trigger conditional read-out operations is calibrated according to read-out results and/or reference charge injection. These and other features and benefits are disclosed in greater detail below. [0095] High-SNR Image Sensor with Non-Destructive Threshold Monitoring

[0096] While three-transistor (3T) pixel architectures are suitable for many applications, four-transistor (4T) designs having a "transfer gate" disposed between the photodiode and a floating-diffusion region provide a number of advantages. First, the floating diffusion, which serves as a temporary storage of charge transferred from the photodiode, may be reset (e.g., coupled to  $\mathbf{V}_{\!D\!D}\!)$  and read out without disturbing the charge state of the photodiode, thereby enabling a correlated double-sampling (CDS) operation in which the state of the floating diffusion is read twice; immediately after reset (the "reset-state" sample or noise sample) and then again after charge transfer from the photodiode (the "signal-state" sample), thus enabling the noise floor to be subtracted from the photodiode output signal (i.e., subtracting the reset-state sample from the signal-state sample), significantly improving the SNR. Another advantage is, counterintuitively, a more compact pixel design as the switched connection between the photodiode and a source follower transistor (i.e., via the transfer gate and floating diffusion) enables the source follower transistor as well as a reset transistor and access transistor to be shared among multiple photodiodes. For example, only seven transistors are required to implement a set of four "4T" pixels having a shared source follower, reset transistor and access transistor (i.e., four transfer-gates plus the three shared transistors), thus effecting an average of 1.75 transistors per pixel (1.75T).

[0097] In terms of pixel read-out, the direct connection between photodiode and source follower in a 3T pixel

permits the charge state of the photodiode to be read-out without disturbing ongoing photocharge integration. This "non-destructive read" capability is particularly advantageous in the context of the conditional reset operation described above as the 3T pixel may be sampled following an integration interval and then conditionally permitted to continue integrating charge (i.e., not be reset) if the sampling operation indicates that the charge level remains below a predetermined threshold. By contrast, the charge transfer between photodiode and floating diffusion as part of a 4T pixel readout disrupts the state of the photodiode, presenting a challenge for conditional-read operation.

[0098] In a number of embodiments described below in connection with FIGS. 1-4, a modified 4T pixel architecture is operated in a manner that dissociates the reset threshold from pixel sample generation to enable a non-destructive (and yet correlated double-sampling) overthreshold determination. That is, instead of reading out the net level of charge accumulated within the photodiode (i.e., a pixel sampling operation) and conditionally resetting the photodiode based on that read-out (i.e., as in a 3T pixel sampling operation), a preliminary overthreshold sampling operation is executed to enable detection of an overthreshold state within the photodiode, with the full photodiode read-out (i.e., pixel sample generation) being conditionally executed according to the preliminary overthreshold detection result. In effect, instead of conditionally resetting the photodiode according to the pixel value obtained from full photodiode readout, full photodiode readout is conditioned on the result of a preliminary, non-destructive determination of whether the threshold has been exceeded; an approach enabled, in at least one embodiment, by dissociating the conditional-read threshold from the pixel value generation.

[0099] FIG. 1 illustrates an embodiment of a modified 4T pixel 100, referred to herein as a "progressive read-out" or "conditional-read" pixel, in which a non-destructive over-threshold detection operation is executed to enable conditional-reset/read operation in conjunction with correlated double sampling. As explained more fully below, the over-threshold detection involves a limited read-out of the photodiode state which, when determined to indicate an over-threshold condition, will trigger a more complete read-out of the photodiode state. That is, pixel 100 is read-out in a progression from a limited overthreshold detection read-out to a complete read-out, the latter being conditional according to the overthreshold detection result and hence referred to as a conditional read.

[0100] Still referring to FIG. 1, conditional-read pixel 100 includes a transfer gate 101 disposed between a photodiode 110 (or any other practicable photosensitive element) and floating diffusion node 112, and a transfer-enable transistor 103 coupled between a transfer-gate row line (TGr) and transfer gate 101. The gate of transfer-enable transistor 103 is coupled to a transfer-gate column line (TGc) so that, when TGc is activated, the potential on TGr is applied (minus any transistor threshold) via transfer-enable transistor 103 to the gate of transfer-gate 101, thus enabling charge accumulated within photodiode 110 to be transferred to floating diffusion 112 and sensed by the pixel readout circuitry. More specifically, floating diffusion 112 is coupled to the gate of source follower 105 (an amplification and/or charge-to-voltage conversion element), which is itself coupled between a supply rail ( $V_{DD}$  in this example) and a read-out line, Vout, to enable a signal representative of the floating diffusion potential to be output to read-out logic outside the pixel.

[0101] As shown, a row-select transistor 107 is coupled between source follower 105 and the read-out line to enable multiplexed access to the read-out line by respective rows of pixels. That is, row-select lines ("RS") are coupled to the control inputs of row-select transistors 107 within respective rows of pixels and operated on a one-hot basis to select one row of pixels for sense/read-out operations at a time. A reset transistor 109 is also provided within the progressive read-out pixel to enable the floating diffusion to be switchably coupled to the supply rail (i.e., when a reset-gate line (RG) is activated) and thus reset. The photodiode itself may be reset along with the floating diffusion by fully switching on transfer gate 101 (e.g., by asserting TGc while TGr is high) and reset transistor 109 concurrently, or by merely connecting the photodiode to a reset-state floating diffusion.

[0102] FIG. 2 is a timing diagram illustrating an exemplary pixel cycle within the progressive read-out pixel of FIG. 1. As shown, the pixel cycle is split into five intervals or phases corresponding to distinct operations carried out to yield an eventual progressive read-out in the final two phases. In the first phase (phase 1), a reset operation is executed within the photodiode and floating diffusion by concurrently asserting logic high signals on the TGr, TGc and RG lines to switch on transfer-enable transistor 103, transfer gate 101 and reset transistor 109, thereby switchably coupling photodiode 110 to the supply rail via transfer gate 101, floating diffusion 112 and reset transistor 109 (the illustrated sequence can begin with an unconditional reset (e.g., at the start of a frame), and can also begin from a preceding conditional read-out/reset operation). To conclude the reset operation, the TGr and RG signals (i.e., signals applied on like-named signal lines) are lowered, thereby switching off transfer gate 101 (and reset transistor 109) so that the photodiode is enabled to accumulate (or integrate) charge in response to incident light in the ensuing integration phase (phase 2). Lastly, although the row-select signal goes high during the reset operation shown in FIG. 2, this is merely a consequence of an implementation-specific row decoder that raises the row-select signal whenever a given row address is decoded in connection with a row-specific operation (e.g., raising the TGr and RG signals during reset directed to a given row). In an alternative embodiment, the row decoder may include logic to suppress assertion of the row-select signal during reset as indicated by the dashed RS pulse in FIG. 2.

[0103] At the conclusion of the integration phase, the floating diffusion is reset (i.e., by pulsing the RG signal to couple the floating diffusion to the supply rail) and then sampled by a sample-and-hold element within the column read-out circuit. The reset and sample operation (shown as phase 3 in FIG. 2), in effect, samples the noise level of the floating diffusion and is executed in the embodiment shown by asserting the row-select signal for the pixel row of interest (i.e., the "i<sup>th</sup>" pixel row, selected by RSi) while pulsing a reset-state sample-and-hold signal (SHR) to convey the state of the floating diffusion to the sample-and-hold element (e.g., a switch-accessed capacitive element) within the column read-out circuit via read-out line, Vout.

**[0104]** After acquiring the noise sample in phase 3, an overthreshold detection operation is executed in phase 4 by raising the TGr line to a partially-on, "overthreshold-detection" potential,  $VTG_{partial}$ , concurrently with switching on

transfer-enable transistor 103 (i.e., by asserting a logic high TGc signal, although in this embodiment TGc is already on). By this operation, illustrated graphically in FIGS. 3 and 4,  ${

m VTG}_{partial}$  is applied to transfer gate 101 to switch the transfer gate to a "partial on" state ("TG partial on"). Referring to FIGS. 3 and 4, electrostatic potential diagrams for photodiode 110 (a pinned photodiode in this example), transfer gate 101 and floating diffusion 112 are shown below their corresponding schematic cross-section diagrams. Note that the depicted levels of electrostatic potential are not intended to be an accurate representation of the levels produced in an actual or simulated device, but rather a general (or conceptual) representation to illustrate the operation of the pixel read-out phases. Upon application of VTG<sub>partial</sub> to transfer gate **101**, a relatively shallow channel potential 121 is formed between photodiode 110 and floating diffusion 112. In the example of FIG. 3, the level of charge accumulated within the photodiode at the time of the overthreshold detection operation (phase 4) does not rise to the threshold level required for charge to spill over (i.e., be transferred) to the floating diffusion via the shallow channel potential of the partially-on transfer gate. Accordingly, because the accumulated charge level does not exceed the spillover threshold established by application of VTG<sub>partial</sub> to the control node of transfer gate 101, there is no spillover from the photodiode to the floating diffusion and the accumulated charge instead remains undisturbed within the photodiode. By contrast, in the example of FIG. 4, the higher level of accumulated charge does exceed the spillover threshold so that a portion of the accumulated charge (i.e., that subset of charge carriers that are above the transfer gate partially-on electrostatic potential) spills over into floating diffusion node 112, with the residual accumulated charge remaining within the photodiode as shown at 122.

[0105] Still referring to FIGS. 2, 3 and 4, prior to conclusion of overthreshold detection phase 4, the charge level of the floating diffusion is sampled and held within a signalstate sample-and-hold element (i.e., in response to assertion of signal SHS) to yield a threshold-test sample—the difference between the signal-state sample and the previously obtained reset-state sample—to be evaluated with respect to a conditional-read threshold. In one embodiment, the conditional-read threshold is an analog threshold (e.g., to be compared with the threshold-test sample in a sense amplifier in response to assertion of a compare/convert strobe signal) set or programmed to a setting above the sampling noise floor, but low enough to enable detection of minute charge spillover via the shallow transfer gate channel. Alternatively, the threshold-test sample may be digitized in response to assertion of the compare/convert signal (e.g., within an analog-to-digital converter that is also used to generate the finalized pixel sample value) and then compared with a digital conditional-read threshold, again, set (or programmed to a setting) above the noise floor, but low enough to enable detection of trace charge spillover. In either case, if the threshold-test sample indicates that no detectable spillover occurred (i.e., threshold-test sample value is less than conditional-read spillover threshold), then the photodiode is deemed to be in the underthreshold state shown in FIG. 3 and the TGc line is held low in the ensuing conditional read-out phase (phase 5, the final phase) to disable transfer gate 101 for the remainder of the progressive read-out operation—in effect, disabling further read-out from the photodiode and thus enabling the photodiode to continue integrating charge without disruption for at least another sampling interval. By contrast, if the threshold-test sample indicates a spillover event (i.e., threshold-test sample greater than conditional-read/spillover threshold), then the TGc line is pulsed during the conditional read-out phase concurrently with application of a fully-on, "remaindertransfer" potential, VTG<sub>full</sub>, to the TGr line, thereby enabling the remainder of the charge (i.e., charge 122 as shown in FIG. 4) within photodiode 110 to be transferred to floating diffusion 112 via the full-depth transfer-gate channel (123) so that, between the overthreshold transfer in phase 4 and the remainder transfer in phase 5, the charge accumulated within the photodiode since the hard reset in phase 1 is fully transferred to the floating diffusion where it may be sensed in a pixel read-out operation. In the embodiment shown, the pixel-readout operation is effected by pulsing the SHS signal and compare/convert strobe in sequence during conditional read-out phase 5, though either or both of those pulses may optionally be suppressed in absence of an overthreshold detection. Note that conditional read-out of the photodiode (i.e., effected by pulsing TGc in conjunction with application of VTG<sub>full</sub> on TGr) effectively resets the photodiode (i.e., drawing off all charge to the floating diffusion), while suppression of the conditional read-out leaves the integration state of the photodiode undisturbed. Accordingly, execution of the conditional read-out operation in phase 5 conditionally resets the photodiode in preparation for integration anew in the succeeding sampling interval (subframe) or refrains from resetting the photodiode to enable cumulative integration in the subsequent sampling interval. Thus, in either case, a new integration phase follows phase 5, with phases 2-5 being repeated for each subframe of the overall frame (or exposure) interval, before repeating the hard reset in a new frame. In other embodiments, where cumulative integration is permitted across frame boundaries, the hard reset operation may be executed to initialize the image sensor and omitted for an indeterminate period of time thereafter.

[0106] In the embodiment shown, each column of the pixel array is populated by shared-element pixels in which every four pixels form a quad pixel cell 150 and contain respective photodiodes 110 (PD1-PD4), transfer gates 101, and transfer-enable transistors 103, but share a floating diffusion node 152, reset transistor 109, source follower 105 and row-select transistor 107. By this arrangement, the average transistor count per pixel is 2.75 (i.e., 11 transistors/4 pixels), thus effecting a relatively efficient, 2.75T-pixel image sensor.

[0107] Image Decimation and Pixel Binning

[0108] A number of conditional-read image sensor embodiments described herein are operable in decimation modes that yield less than maximum image resolution. For example, in one embodiment an image sensor capable of generating an 8 MP (8 megapixel) output in a still-image mode, yields a 2 MP output in a decimated, high-definition (HD) video mode; a 4:1 decimation ratio (higher or lower resolutions may apply in each mode, and other decimation modes and ratios may be achieved in alternative embodiments; also, if the still and video frame aspect ratios differ, some areas of the sensor may not be used at all in one or the other modes).

[0109] While post-digitization logic may be provided to decimate full-resolution data (e.g., on-chip logic at the output of the ADC bank or off-chip processing logic), pixel

charge aggregation or "binning" within the pixel array and/or voltage binning within sample-and-hold storage elements is applied in a number of embodiments to effect pre-digitization (i.e., pre-ADC and thus analog) decimation, obviating die-consuming and power-consuming digital binning logic and, in many cases, yielding improved signal-to-noise ratio in the decimated output.

[0110] FIG. 5 illustrates a pixel binning/decimation strategy that may be executed with respect to a collection of 4×1 quad-pixel blocks 150 and the color filter array (CFA) fragment shown at 170. In the embodiment shown, the four pixels within each quad pixel block 150 (shown at 150.1-150-4 with respect to the CFA fragment) contain respective photodiodes 110 (PD1-PD4), transfer gates 101, and transfer-enable transistors 103, but share a floating diffusion node 152, reset transistor 109, source follower 105 and row-select transistor 107. By this arrangement, the average transistor count per pixel is 2.75 (i.e., 11 transistors/4 pixels), thus effecting a relatively efficient, 2.75T-pixel image sensor.

[0111] As shown, CFA fragment 170 (i.e., a sufficient portion of a sensor-wide CFA to demonstrate the CFA pattern) includes collections of like colored filter elements at the corner pixels of each 3×3 pixel group. Thus, green filter elements are disposed over shaded pixels 'G', blue filter elements are disposed over striped pixels 'B' and red filter elements are disposed over hashed pixels 'R'. In this arrangement, each pair of like-filtered pixels (i.e., subject to light filtered by same-color filter elements, R, G or B) disposed in the same quad-pixel block thus permit charge binning within their shared floating diffusion as detailed below. Further, referring to FIG. 6, by fixing a column offset between the pixel pair within each column and the likefiltered/same color-plane pair of pixels coupled to the same row lines (i.e., fixed at a spacing of two columns in the example shown) and by providing switching elements at the column read-out points of pixel array 181 (i.e., switching elements 191 and 192 within sample-and-hold circuitry 183), it becomes possible to "voltage-bin" the results of the two charge-binned pixel pairs within sample-and-hold circuitry 183, thus combining (i.e., aggregating, binning) the four corner pixels in each 3×3 pixel group prior to digitization within the ADC elements of SA/ADC block 185.

[0112] FIG. 7 illustrates an exemplary timing diagram of binned-mode read-out operations within the 4×1 quad-pixel architecture of FIGS. 5 and 6. In the example shown, row lines for pixel rows i and i+2 are operated in lock step to achieve 2:1 charge binning within the shared floating diffusion of a given quad-pixel block. More specifically, row signals for pixel rows 1 and 3 of a 4×1 quad pixel block (or row of such quad pixel blocks) are asserted in unison, followed by locked-step assertion of row signals for pixel rows 2 and 4, before advancing to assert row signals for the next row of 4×1 quad pixel blocks. Transverse connections are established within sample-and-hold switch elements (e.g., at 191 and 192 of sample-and-hold block 183 as shown in FIG. 6) to achieve 2:1 voltage binning and thus an overall 4:1 analog signal summing and concomitant image decimation.

**[0113]** Referring more specifically to FIG. 7, the row-select signals ( $RS_{1,3}$ ), reset-gate signals ( $RG_{1,3}$ ) and row transfer-gate signals ( $TGr_{1,3}$ ) for rows 1 and 3 are operated in lock step to reset the photodiodes and shared floating diffusion of the selected pixel rows during hard-reset phase 1, permit charge integration during integration phase 2,

determine whether the charge-binned and voltage-binned charge-accumulation results within each column-interleaved collection of four pixels (i.e., the 3x3 corner pixels as described in reference to FIGS. 5 and 6) exceed the conditional-read threshold in threshold-test phase 3, and, if an overthreshold condition is detected, conditionally read-out and digitize the full charge-binned and voltage-binned accumulated charge within the subject pixel collections in conditional read-out phase 4 before transmitting the digitized pixel value to downstream (on-chip or off-chip) processing logic in output phase 5. Considering the phases one by one, during hard-reset phase 1, the row-transfer gate signals TGr1 and TGr3 are pulsed to  $VTG_{full}$  (as shown at 200) while simultaneously raising column transfer-gate signal TGc, thus transferring accumulated charge from photodiodes PD1 and PD3 to their shared floating diffusion node. After the photodiode-to-floating-diffusion charge transfer, reset signal RG is pulsed at 202 to clear charge from the floating diffusion in preparation for the ensuing charge integration in phase 2. At the start of threshold-test phase 3, the reset signal is pulsed again (204) to reset the floating diffusions and then signals SHRsa and SHRadc are pulsed at 206 and 208 (while RSi is asserted) to capture samples of the reset-state of the floating diffusions within the respective sample-and-hold elements for the sense amplifier and ADC. After capture, switch 191 is closed to voltage-share between the reset signal sample-and-hold elements for columns 1 and 3, thus producing a reset signal representative of the average of the column 1 and 3 floating diffusions. At 210, TGr1 and TGr3 are raised to the partial-on transfer potential,  $VTG_{partial}$ , to enable charge spillover to the shared floating diffusions if an overthreshold condition exists in either or both of the photodiodes of the subject pixels in a column. The SHSsa signal is then pulsed at 212 to capture the signal-state of the floating diffusion nodes. Subsequently, switch 191 is closed to voltage-share between the threshold-compare sampleand-hold elements for columns 1 and 3, thus voltage binning the two charge-binned spillover samples. The threshold-test phase is concluded by lowering the TGc signal and asserting the compare-strobe (214) to trigger a threshold comparison within the sense amplifier of either column 1 or column 3 (the other may be deactivated), comparing the aggregated spillover charge from the four charge/voltage binned pixels against a conditional-read threshold. If the comparison result indicates an overthreshold condition, the TGc signals on both columns 1 and 3 are pulsed at 216 during application of VTG<sub>full</sub> on the TGr1 and TGr3 lines, (thus enabling a full read-out of photodiodes PD1 and PD3 to the shared floating diffusions within corresponding quad pixel blocks), and then the SHSadc signal is raised at 218 to capture the signal-state of the floating diffusion nodes within a signal-state sampleand-hold element in each column. Subsequently, switch 191 is closed to voltage-share between the signal-state sampleand-hold elements for columns 1 and 3, (i.e., voltagebinning the charge-binned floating diffusion contents). Thereafter, the convert-strobe is pulsed at 220 to trigger an ADC operation (for either column 1 or 3, but both are not necessary) with respect to the voltage/charge-binned signal state captured within the sample-and-hold circuit (if any), followed by transmission of the ADC output in phase 5. As discussed above, the ADC operation and data transmission operations may be suppressed to save power and reduce signaling bandwidth if an overthreshold condition is not detected in threshold-test phase 4.

[0114] Image Sensor Architecture, System Architecture [0115] FIG. 8 illustrates an embodiment of an imaging system 240 having an image sensor 241, image processor 243, memory 245 and display 247. The image sensor 241 includes a pixel array 251 constituted by temporally-oversampled conditional-read pixels according to any of the embodiments disclosed herein, and also includes pixel control and read-out circuitry as described above, including row logic 255, column logic 257, line memory 259 and PHY 261. Image processor 243 (which may be implemented as a system-on-chip or the like) includes an image signal processor (ISP) 271 and application processor 273, coupled to one another via one or more interconnect buses or links 276. As shown, ISP 271 is coupled to receive imaging data from the pixel array via PHY 267 (and signaling link(s) 262, which may be implemented, for example, by a Mobile Industry Processor Interface ("MIPI" bus) or any other practicable signaling interface), and the ISP and application processor are coupled to a memory control interface 275 and user-interface port 277 via interconnect 276. Further, as explained below, interconnect 276 may also be coupled to the image sensor interface of ISP 271 (i.e., the ISPs interface to PHY 267) via side-channel 278 to enable the application processor to deliver data to the ISP in a manner that emulates an image sensor.

[0116] Still referring to FIG. 8, imaging system 240 further includes one or more memory components 245 coupled to the memory control interface 275 of image processor 243. In the example shown, and in the discussion below, the memory components are assumed to include a dynamic random access memory (DRAM) which may serve as a buffer for image sub-frame data and/or as a frame buffer for other functions. The memory components may additionally include one or more non-volatile memories for long-term storage of processed images.

[0117] User-interface port 277 is coupled to a user display 247 which may itself include a frame memory (or frame buffer) to store an image to be displayed for a user (e.g., a still image frame or video frame). Though not shown, user-interface port 277 may also be coupled to a keypad, touchscreen or other user-input circuitry capable of providing information to image processor 243 corresponding to user-input, including operating mode information that may be used to configure decimation modes within the image sensor 241. Although also not shown, image processor 243 may be coupled to image sensor 241 through a sideband channel or other control interface to permit transmission of operating mode, configuration information, operation-triggering instructions (including image capture instructions, configuration-programming instructions, etc.) and the like to the image sensor.

[0118] FIG. 9 illustrates an exemplary sequence of operations that may be executed within the imaging system of FIG. 8 in connection with an image processing operation. Starting at 291, the application processor configures ISP 271 for DMA (direct-memory-access) operation with respect to memory control interface 275 and thus memory IC 245. By this arrangement, the ISP is enabled to operate as DMA controller between image sensor 241 and memory IC 245, receiving subframe data from image sensor 241 row by row (as shown at 293) and transferring the subframe data to the memory IC. Thus, the subframe data generated by temporal oversampling within image sensor 241 are, in effect, piped through the ISP directly to memory IC (e.g., a DRAM)

where they may be accessed by the application processor. Note that, in the embodiment shown, subframes are loaded into the memory one after another until a final subframe has been received and stored (i.e., the frame-by-frame storage loop and its eventual termination being reflected in decision block 295). This process may be optimized in an alternative embodiment by omitting storage of the final subframe in memory IC 245 and instead delivering the final subframe data directly to application processor 273. In other embodiments, subframe readout is interleaved, such that the ISP may be receiving successive rows from different incomplete subframes and either sorting them as they are stored, or as they are retrieved at step 297. That is, as shown at 297, the application processor retrieves and combines (e.g., sums or combines in some other fashion) the stored subframes to produce a consolidated (integrated) image frame so that, instead of storing the final subframe in memory and then reading it right back out, the final subframe may be delivered directly to the application processor to serve as a starting point for subframe data consolidation. In any case, at 299 the application processor configures ISP 271 for operation in image-processing mode and, at 301, outputs the image frame data (i.e., the consolidation of the temporally oversampled image sensor data, with any preprocessing or compression applied, as applicable) to the image-sensor interface of the ISP (i.e., to the front-end of the ISP via channel 278), thereby emulating image sensor delivery of a full image frame to ISP 271. At 303, the ISP processes the image frame delivered by the application processor to produce a finalized image frame, writing the completed (processed) image frame, for example, to DRAM or non-volatile memory (i.e., one or both of memory ICs 245), and/or directly to the frame buffer within display 247 to enable the image to be displayed to the system user.

# [0119] Split-Gate Architecture

[0120] FIG. 10 contrasts embodiments of the conditionalread pixel 100 of FIG. 1 and a modified pixel architecture 310, referred to herein as "split-gate" conditional-read pixel or split-gate pixel. In the embodiment shown, split-gate pixel 310 includes a photodiode 110 together with the same floating diffusion 112, reset transistor 109, source-follower 105, and read-select transistor 107 as pixel 100, but omits transfer-enable transistor 103 and single-control transfergate 101 in favor of a split, dual-control transfer-gate 311. Referring to detail view 320, dual-control transfer gate (or "dual-gate") includes distinct (separate) row and column transfer gate elements 321 and 323 disposed adjacent one another over the substrate region between photodetector 110 (PD) and floating diffusion 112 (FD). The row and column transfer gate elements (321 and 323) are coupled to row and column control lines, respectively, to receive row and column control signals, TGr and TGc and thus are independently (separately) controlled. As discussed in further detail below, by omitting the source/drain implant ordinarily required between series-coupled transistors (and thus between adjacent gate terminals), the row and column transfer gate elements may be disposed closely enough to one another that the resulting overlapping electrostatic fields will form a continuous enhancement channel 325 when both TGr and TGc are asserted, (at a signal level to provide charge transfer), while maintaining an ability to interrupt the channel when either of TGr and TGc are deasserted, (at a signal level to prevent charge transfer). Accordingly, the logic-AND function effected by the combined operation of transfer-gate 101 and transfer-enable transistor 103 in pixel 100 may be achieved within the substantially more compact dual-control gate 311, reducing the pixel footprint (i.e., die area consumption) by a transistor or a significant portion of a transistor relative to pixel 100. In the case of a quad pixel layout, for example, the dual-gate arrangement lowers the per-pixel transistor count from 2.75T (i.e., when pixel 100 is employed) to approximately 1.75T to 2T, depending on the dual-gate implementation. In addition to the reduced nonlight-gathering pixel footprint, the dual-gate design permits a negative potential to be applied to the transfer gate or transfer gates during the charge-integration (light accumulation) interval to reduce PD to FD leakage current and transfer gate dark current, a function not readily available in embodiment 100 as a negative TGr voltage may disruptively forward-bias the source/drain to substrate diodes in transferenable transistor 103. Further, in contrast to the floating potential that results at transfer gate 101 of pixel 100 whenever TGc is lowered, row and column transfer gate elements 321 and 323 are continuously coupled to signal driving sources and thus continuously driven to the driver output voltage (i.e., not floating), potentially reducing noise in the pixel read-out operation.

[0121] FIG. 11 is a timing diagram illustrating an exemplary pixel cycle (reset/charge integration/read-out) within the split-gate pixel of FIG. 10. As in embodiments described above, the pixel cycle is split into five intervals or phases corresponding to distinct operations carried out to yield an eventual progressive read-out in the final two phases (the pixel can also provide an unconditional readout sequence that skips phase four). Referring to both FIG. 11 and split-gate pixel 310 in FIG. 10, a reset operation is executed within the photodiode and floating diffusion in phase one by concurrently raising the TGr and TGc signals to establish a conduction channel between photodiode 110 and floating diffusion 112 (i.e., as shown at 325 in FIG. 10), and thereby reset the photodiode by enabling residual or accumulated charge within the photodiode to be transferred to the floating diffusion. After (or concurrently with) the charge transfer operation, the reset-gate signal (RG) is pulsed to switch on reset transistor 109 and thus evacuate/empty charge from the floating diffusion by switchably coupling the floating diffusion to  $V_{dd}$  or other supply voltage rail. In the embodiment shown, TGr is driven to a negative potential following the photodetector reset operation (e.g., immediately after concurrent assertion with TGc or at the conclusion of the reset phase), thereby establishing a low-leakage isolation between the photodetector and floating diffusion, and reducing dark current from the region below TGr. Also, because the row and column control signals are jointly applied to adjacent transfer gate elements, TGc may be raised and lowered as necessary following the photodetector reset operation and during the ensuing integration phase (phase 2) without floating the transfer gate. Thus, TGc is lowered following pixel reset and, while shown as remaining low throughout the ensuing integration and noise sampling phases (phases 2 and 3), will toggle between high and low states during those phases to support reset and read-out operations in other pixel

[0122] The noise or reset sampling operation within phase 3, overthreshold detection within phase 4 and conditional read-out (or conditional transfer) within phase 5 are carried out generally as discussed in reference to FIG. 2, except that TGc need only be raised in conjunction with the TGr pulses

(i.e., to VTGpartial and VTGfull) during the partial-transfer and conditional-transfer operations. In the embodiment shown, a quad-potential TGr driver is provided within the row decoder/driver to maintain TGr at the negative potential throughout the integration phase, and then step TGr up to a pre-read potential (zero volts in the example shown) at the start of the noise sampling phase before raising TGr further to VTG<sub>partial</sub> and finally to VTG<sub>full</sub> in the overthreshold detection and conditional read-out operations, respectively. In alternative embodiments, a three-potential driver may be used to maintain TGr at the negative potential except when pulsed to VTG<sub>partial</sub> or VTG<sub>full</sub> (i.e., no pre-read potential). [0123] FIG. 12 illustrates exemplary low-light and highlight operation of the split-gate pixel of FIG. 10, showing electrostatic potential diagrams in each case beneath schematic cross-section diagrams of the photodetector (photodiode 110 in this example), row and column transfer gate elements 321 and 323 (i.e., forming a dual-control transfer gate) and floating diffusion 112. As in preceding examples, the depicted levels of electrostatic potential are not intended to be an accurate representation of the levels produced in an actual or simulated device, but rather a general (or conceptual) representation to illustrate the operation of the pixel read-out phases. Starting with the low-light example, a relatively low level of charge is accumulated within the photodiode during the integration phase (phase 2) so that, when TGc is asserted and TGr is raised to the partial-on potential (VTG<sub>partial</sub>) during overthreshold detection phase 4 (i.e., after noise sample acquisition in phase 3), the charge level is insufficient to be transferred via the relatively shallow channel formed between photodiode 110 and floating diffusion 112. Because the accumulated charge level does not exceed the spillover threshold established by application of  $VTG_{partial}$  to the gate element coupled to the TGr line, there is no spillover from the photodiode to the floating diffusion and the accumulated charge instead remains undisturbed within the photodiode. Because no spillover is detected during the overthreshold phase, TGc is deasserted during conditional transfer (conditional read-out) phase 5. Although some charge may migrate to the well under the row gate during TGr assertion, that charge will move back to the photodiode well when TGr is deasserted, thus maintaining the charge level within the photodiode as a starting point for further charge accumulation in a subsequent integration interval. By contrast, in the high-light example, the higher level of accumulated charge does exceed the spillover threshold during overthreshold detection phase 4 so that a portion of the accumulated charge (i.e., that subset of charge carriers that are above the transfer gate partially-on electrostatic potential) spills over into floating diffusion node 112, with the residual accumulated charge remaining within the photodiode as shown at 918. Accordingly, the spilled charge is detected during the phase 4 read phase such that, during overthreshold phase 5, TGr is raised to the VTG<sub>full</sub> potential concurrently with assertion of TGc, thus establishing a full conduction path through the channel formed by the dualgate structure to transfer the entirety of the accumulated charge from photodiode 110 to floating diffusion 112.

[0124] FIG. 13 illustrates an alternative overthreshold detection operation within the split-gate pixel of FIG. 10. As shown, instead of driving the TGr line to a partial potential (i.e., VTG<sub>partial</sub>) for a full transfer time, a fractional (i.e., reduced-width) TGr pulse 350 is applied in conjunction with the TGc pulse (which may also have a fractional pulse

width) thus limiting the time available for charge transfer between the photodetector and floating diffusion. In one embodiment, for example, fractional pulse 350 is a shortduration pulse having a time constant shorter than required to transfer all charge above the threshold defined by the voltage applied to the dual-control transfer gate and therefore transfers the charge only partially, in contrast to a full-width pulse which is long enough to transfer all of that charge. Accordingly, due to the time constant and subthreshold characteristics of the photodetector-to-diffusion charge transfer, below-threshold charge integration within the photodetector will yield little or no charge transfer during the fractional pulse interval, while overthreshold charge integration will yield a detectable charge transfer, analogous, in effect, to application of VTG<sub>partial</sub> for the full pulse interval. Pulse width control may provide superior performance (i.e., relative to voltage-level control) in terms of repeatability and/or threshold precision, particularly in noisy environments (e.g., where switching noise may couple to the TGr line) or where programmable threshold trimming or calibration may be needed. As shown at 351, the partialreadout control, whether pulse-width or voltage-level controlled, alternatively (or additionally) may be applied to the TGc line, particularly where the TGc signal is used to control the gate element nearest the photodetector. Also, pulse-width control and voltage control may be combined, for example, by driving a fractional pulse having a reduced voltage onto the TGc or TGr line. Further, the full pulse applied to the TGr and/or TGc line during a conditional read-out operation (and/or during a reset operation) may be replaced by a burst of fractional pulses as shown at 352, thus establishing a uniform (fractional) width for each pulse applied. In one embodiment, the full pulse width during conditional-readout phase 5 is on the order of 200 to 1000 nanoseconds (nS), while the fractional pulse width is on the order of 2 to 200 nanoseconds, though other fractional and/or full pulse widths may apply in alternative embodiments. Although shown as operative for a split-gate embodiment, similar fractional pulse methods are applicable to embodiments having a transfer-enable transistor coupled between the transfer-gate row line (TGr) and transfer gate. [0125] FIG. 14 illustrates a quad-pixel, shared floating diffusion image sensor architecture in which pairs of row and column transfer-gate control lines (TGr1/TGr2 and TGc1/TGc2) are coupled to a dual-gate structure (377.1-377.4) within each of four split-gate pixels in the manner described above. More specifically, by centralizing a shared floating diffusion 375 between four pixels (each also including a respective one of photodiodes PD1-PD4 and one of dual-control transfer gates 377.1-377.4, together with shared

**[0126]** FIG. **15** illustrates a 4×1 block of split-pixels (a quad, split-pixel block) that may be operated in binned or independent-pixel modes as described above, for example, in reference to FIG. **5**. As shown, floating diffusion regions  ${\rm FD}_{12}$  and  ${\rm FD}_{34}$  for upper and lower pixel pairs, respectively, are interconnected via conductor **392** (or alternatively

reset-gate transistor 109, source follower 105 and read-

select transistor 107) and splitting the column transfer-gate

control line TGc into separate odd and even column-enable

lines (TGc1 and TGc2, each coupled to a respective column-

line driver), a highly compact pixel layout may be achieved.

In alternative embodiments, split-gate pixels may be dis-

posed in a 4×1 quad pixel group similar to that shown in

formed by a single floating diffusion region), thus permitting, for example, the states of photodiodes PD1 and PD3 or photodiodes PD2 and PD4 to be read conjunctively (i.e., read concurrently or as one). Each photodiode in the 4×1 pixel block is switchably coupled to a floating diffusion node via a dual-control gate, with a row gate element 393 coupled to a respective one of the four row lines (i.e., TGr1-TGr4 for photodiodes PD1-PD4, respectively) and a column gate element 394 coupled to the per block column line. In the implementation shown, a shared column-line contact is coupled to each of the two column gate elements adjacent a given floating diffusion, thus halving the required number of column line interconnects. Shared transistors 395, 396 and 397 (i.e., reset-gate, source follower and read-select transistors) are disposed in regions between photodiodes PD1-PD4, though any or all of those transistors may be disposed at other positions. Also, while the row line is coupled to the dual-control gate element nearest the photodiode and column line coupled to the gate element nearest the floating diffusion, that arrangement may be reversed in alternative implementations.

[0127] Low Power, Pipelined Image Sensor

[0128] FIG. 16 illustrates an embodiment of a low power image sensor that may be used to implement component circuitry within the image sensor of FIG. 8. In the example shown, image sensor 451 includes a pixel array 411, multibank sample-and-hold (S/H) circuitry 453, column-shared programmable-gain (PG) amplifier bank 455 (PGA), comparator/ADC circuitry 457 (including per-column comparator circuitry and column-shared ADC circuitry as discussed below), and line memory 420. Pixel array output lines convey pixel read-out signals to sample-and-hold circuitry 453, which in turn supplies analog samples of the read-out signals, with and without gain from the PGA 455, to comparator/ADC circuitry 457. To conserve die area, a single programmable gain amplifier 455 and single ADC circuit 480 are shared among K columns of the pixel array and cycled K times for each row of the pixel array (for an unconditional readout operation). By contrast, a dedicated (separate) threshold comparator 472 is provided for each column of pixels to enable pixel state (e.g., eclipse, under/ over threshold, saturation) to be assessed across an entire row of pixels in parallel. In the embodiment shown, such "per-column" threshold comparators 472 are operated cyclically to perform multiple pixel state evaluations per pixel row (i.e., in parallel for each pixel in the row), including an eclipse assessment to determine, for each pixel in the row, whether the reset-state of the floating diffusion has fallen below an eclipse threshold; an underthreshold assessment to determine whether charge integration within the pixel has exceeded a conditional read/reset threshold, and a saturation assessment to determine whether the pixel charge integration level sampled in a conditional read/reset operation exceeds a saturation threshold (i.e., a threshold corresponding to a saturation point of ADC circuit 480). Thresholds corresponding to the various pixel state assessments (e.g., eclipse threshold, conditional read/reset threshold, saturation threshold) are applied one after another to the input of the per-column comparators 472 via corresponding reference multiplexers 470, and a comparator input multiplexer 471 is provided to select between multiple sample-and-hold circuit outputs as discussed below.

[0129] Comparator results for each pixel column are captured within a respective read-enable logic circuit 475 which

conditionally drives a conditional read/reset signal (e.g., TGc) back to the pixel column and also outputs read-enable and above/below-range bits (RE and AB) to primary buffer 421 of line memory 420. After pixel state assessment is complete for a given pixel row, the read-enable bit for each of K columns is passed, one after another via multiplexer 476, to the enable input of column-shared ADC (analog-todigital converter) circuit 480 and to column-shared PGA 455, thereby selectively enabling digitization of individual column read-outs (i.e., according to the logic state of the selected RE bit), suppressing signal amplification and digitization (and thus conserving power) for pixels that are eclipsed, below the conditional read/reset threshold, or saturated. Multiplexer 477 is provided to demultiplex (i.e., distribute) digitized samples from column-shared ADC circuit 480 into respective per-column storage locations within the primary line-memory buffer 421 including, in the embodiment shown, overwriting the AB bit location.

[0130] Still referring to FIG. 16, pipelined operation within the various data read-out stages (i.e., pixel state assessment, conditional ADC, and line memory read-out) is enabled, at least in part, by multi-bank sample-and-hold circuitry 453. In the embodiment shown in detail view 454, for example, three separate sample-and-hold banks are provided for sequentially executed read-out operations, including an "Eclipse/Vt" bank 463 that stores pixel samples evaluated to detect eclipse events and determine whether the conditional read/reset threshold is exceeded (the latter referred to alternately as "Vt assessment" or conditional read/reset threshold assessment); an even-row conditional read S/H bank 465 (Conditional Read Bank 1) to store pixel samples that enable saturation detection and read-out digitization (ADC operation) for even-numbered pixel rows, and an odd-row conditional read S/H bank 467 (Conditional Read Bank 2) to store pixel samples that enable saturation detection and read-out digitization for odd-numbered pixel rows. As explained in greater detail below, by providing a separate (dedicated) Eclipse/Vt bank 463, S/H for the comparator operation can be pipelined with storage into the conditional read S/H banks. Thus, by providing separate conditional read S/H banks for even and odd rows and alternately storing samples therein for eventual digitization within the column-shared ADC circuitry, it becomes possible to pipeline pixel state assessment and ADC operations from row to row.

[0131] Referring to detail view 482, an exemplary implementation of RE logic 475 includes shift register 483 to capture the output of comparator 472 following a sequence of per-row pixel assessment evaluations, latching each new assessment result (i.e., comparator output, including an eclipse flag, overthreshold flag and below-saturation flag) in response to a timing signal from the sensor control logic (e.g., element 983 of FIG. 52). Read/reset logic 485 evaluates the states of the eclipse and overthreshold (i.e., above Vt) flags when enabled by another timing signal (or state transition signal), asserting a conditional read/reset signal according to their states as discussed below. Similarly, Enable-ADC logic 487 outputs read-enable and above/ below-range bits (RE) and (AB) for the pixel under evaluation in response to another control/timing signal and according to the states of the eclipse, overthreshold and below-saturation flags.

[0132] FIG. 17 illustrates a sequence of operations that may be executed within the pixel array, sample/hold banks

and comparator circuitry of FIG. 16 to carry out pixel state assessment and enable subsequent PGA and ADC operation for row after row of pixels. In the implementation shown, each image frame is assumed to contain a sequence of conditional-read subframes that conclude with conditional read/reset operations, and a final unconditional-read subframe in which the integration states of pixels within the subject row are unconditionally read-out and, if no saturation or eclipse condition is detected, digitized to yield a subframe output. This approach of conditionally reading out pixel data during non-final subframes of a given image frame and then concluding the image frame with an unconditional read/reset operation is carried forward in a number of embodiments described below. In all cases, conditional read/reset operations may be carried out unconditionally (i.e., regardless of threshold comparison results) and unconditional read/reset operations may be replaced by conditional read/reset operations.