## (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2019/0305927 A1 Bhunia et al.

## Oct. 3, 2019 (43) **Pub. Date:**

#### (54) BITSTREAM SECURITY BASED ON NODE LOCKING

(71) Applicant: University of Florida Research

Foundation Incorporated, Gainesville,

FL (US)

(72) Inventors: Swarup Bhunia, Gainesville, FL (US);

Robert A. Karam, Gainesville, FL (US); Tamzidul Hoque, Gainesville, FL

(21) Appl. No.: 16/081,027

PCT Filed: Mar. 17, 2017

(86) PCT No.: PCT/US2017/023017

§ 371 (c)(1),

(2) Date: Aug. 29, 2018

### Related U.S. Application Data

(60) Provisional application No. 62/310,543, filed on Mar. 18, 2016.

#### **Publication Classification**

(51) Int. Cl.

H04L 9/00 (2006.01)H03K 19/177

(2006.01)

G06F 21/44 (2006.01)G06F 21/76 (2006.01)H04L 29/06 (2006.01)H04L 9/08 (2006.01)

(52) U.S. Cl.

CPC ...... H04L 9/002 (2013.01); H03K 19/17768 (2013.01); G06F 21/44 (2013.01); H04L 2209/16 (2013.01); H04L 63/0457 (2013.01); H04L 9/0866 (2013.01); G06F 21/76

(2013.01)

#### (57)ABSTRACT

A technique to generate node locked bitstreams for FPGAs to simultaneously protect against malicious reconfiguration as well as FPGA IP piracy is provided. According to some aspects, modifications in FPGA architecture along with an associated mapping flow enable authenticating and programming a device in a way that maintains FPGA security while requiring low overhead. The technique is more robust against side channel and destructive reverse-engineering attacks in comparison with key-based encryption methods, and has less area, power, and latency overhead. The node locked bitstream approach is attractive in many existing and emerging applications including IoTs, which may require field upgrade of FPGA.

FIG. 1

232

FIG. 2

FIG. 5a

FIG. 5b

FIG. 7

FIG. 8

FIG 10

FIG. 11

FPGA 1

FIG. 12

FPGA N

FPGA 2

FIG. 14

# BITSTREAM SECURITY BASED ON NODE LOCKING

#### RELATED APPLICATIONS

[0001] This application claims priority to and the benefit of U.S. Provisional Patent Application No. 62/310,543, entitled "BITSTREAM SECURITY BASED ON NODE LOCKING," filed Mar. 18, 2016. The entire contents of the foregoing are hereby incorporated herein by reference.

#### BACKGROUND OF INVENTION

[0002] Embedded and wearable computing devices have proliferated in recent years in a large diversity of form factors, performing cooperative computation to provide the new regime of Internet-of-Things (IoT). This proliferation trend is expected to continue, with an estimated 50 billion smart, connected devices by 2020. A key feature in such devices is the need for in-field reconfigurability to adapt to changing requirements in energy-efficiency, functionality, and security. Field Programmable Gate Arrays (FPGAs) have emerged as a popular architecture for addressing this reconfigurability demand. FPGAs provide a high flexibility compared to custom Application-Specific Integrated Circuit (ASIC), while consuming less energy than designs based on firmware running in microcontrollers. Furthermore, FPGAbased designs are known to be more secure than both ASIC and microcontrollers against supply-chain attacks, e.g., design details are not exposed to foundries or entrusted outsourcing.

[0003] Bitstreams contain configuration information for programming a programmable device, such as an FPGA. FPGA bitstreams are susceptible to a variety of attacks, including unauthorized reprogramming, reverse-engineering, and cloning/piracy. Therefore there is a need to provide protection of FPGA bitstreams, both during wireless reconfiguration and after in-field deployment in FPGA-based designs.

#### BRIEF SUMMARY

[0004] Disclosed herein is an approach to FPGA security that provides protection against in-field bitstream reprogramming as well as Intellectual Property (IP) piracy, while permitting wireless reconfiguration without encryption.

[0005] The inventors have recognized and appreciated that traditional countermeasures against FPGA bitstream attacks, such as shielding, noise injection, etc., use more energy than desired for most modern embedded and IoT devices that have aggressive energy constraints. The present disclosure details aspects of an approach to FPGA security, which can prevent unauthorized in-field reprogramming as well as FPGA IP piracy without encryption. In some embodiments, a node-locked bitstream approach, where the device-to-bitstream association is changed from device to device, is employed.

[0006] According to some embodiments, a programmable device is provided. The programmable device may include an external interface, a first circuit configured to generate an identifier and a second circuit configured to transmit through the external interface at least one response to one or more messages received through the external interface. At least a portion of the at least one response may be based at least in part on the identifier. The programmable device may further include a third circuit configured to perform a de-obfuscat-

ing function on a bitstream. The de-obfuscating function may be based at least in part on the identifier. According to some embodiments, the programmable device may be a field programmable gate array (FPGA). The at least a portion of the identifier generated by the first circuit may be based on a plurality of selectively blown fuses in the programmable device. At least a portion of the identifier may have a value that varies over time. The third circuit may include at least one sub-circuit configured to selectively permutate the bitstream such that a position within the bitstream of at least a portion of the bitstream is changed based at least in part on the identifier. The third circuit may include a plurality of sub-circuits, connected in series, wherein each of the plurality of sub-circuits is configured to selectively permutate the bitstream such that a position within the bitstream of at least a portion of the bitstream is changed based at least in part on the identifier.

[0007] According to some embodiments, a method of securely programming a programmable device is provided. The method may include obtaining an identifier from the programmable device; obfuscating a bitstream based at least in part on the identifier; and sending the obfuscated bitstream to the programmable device. Obtaining the identifier may include sending a sequence of challenges to the programmable device; receiving a sequence of responses to the sequence of challenges from the programmable device; and determining, based on the sequence of responses, the identifier for the programmable device. The method of securely programming a programmable device may further include authenticating the programmable device based on the identifier in relation with an authorized identifier list. Authenticating the programmable device based on the identifier in relation with an authorized identifier list may include obtaining the authorized identifier list from an external source. Obtaining the authorized identifier list from an external source may include communicating with the external source using secure communications. Obfuscating the bitstream may include permutating the bitstream. Obfuscating the bitstream may also include iteratively permutating the bitstream such that a position within the bitstream of at least a portion of the bitstream is changed based at least in part on the identifier. Obfuscating the bitstream further may include generating a key based on the identifier and obfuscating the bitstream by performing a plurality of obfuscation functions. Each of the plurality of obfuscation functions may be based on the key. Performing a plurality of obfuscation functions may include iteratively permutating the bitstream such that a position within the bitstream of at least a portion of the bitstream is changed based at least in part on the key. Obfuscating the bitstream based on the at least one identifier may include applying a plurality of permutation levels. The plurality of permutation levels may have a first level, a second level and a third level. The first level may include permutation of portions of the bitstream that specify an input ordering of a look up table (LUT); the second level may include permutation of the portion of the bitstream that specifies a content of the LUT and the third level may include a block based permutation of the entire bitstream.

[0008] According to some embodiments, a method of securely operating a programmable device that receives a programming bitstream is provided. The method may include generating a pseudo-random identifier and transmitting a sequence of responses based on the identifier in response to receiving a sequence of challenges. At least a

portion of the sequence of responses may be based at least in part on the identifier. The method may also include deobfuscating a received bitstream based on the identifier; and programming programmable circuitry within the programmable device based on the de-obfuscated bitstream. De-obfuscating the bitstream based on the identifier may include permutating the bitstream based on the identifier. De-obfuscating the bitstream based on the identifier may include transforming the bitstream based on a plurality of fuses in the programmable device that are selectively blown. De-obfuscating the bitstream based on the identifier may further include applying a plurality of permutation levels. The plurality of permutation levels further may include a first de-obfuscation level, a second de-obfuscation level and a third de-obfuscation level. The first de-obfuscation level may include permutating the bitstream on a first portion of the programmable device; the second de-obfuscation level may include permutating the bitstream on a second portion of the programmable device; the third de-obfuscation level may include permutating the bitstream on a third portion of the programmable device.

[0009] The foregoing is a non-limiting summary of the invention, which is defined by the appended claims.

#### BRIEF DESCRIPTION OF DRAWINGS

[0010] Various aspects and embodiments will be described with reference to the following figures. It should be appreciated that the figures are not necessarily drawn to scale. In the drawings, each identical or nearly identical component that is illustrated in various figures may be represented by a like numeral. For purposes of clarity, not every component may be labeled in every drawing.

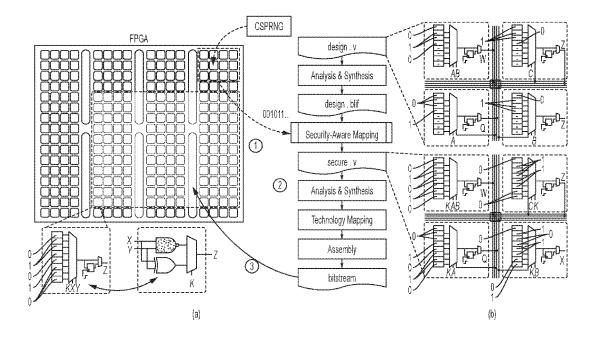

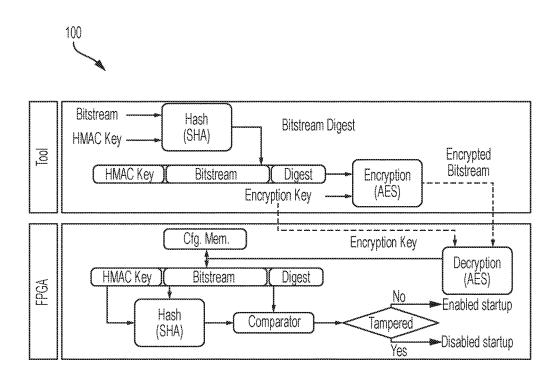

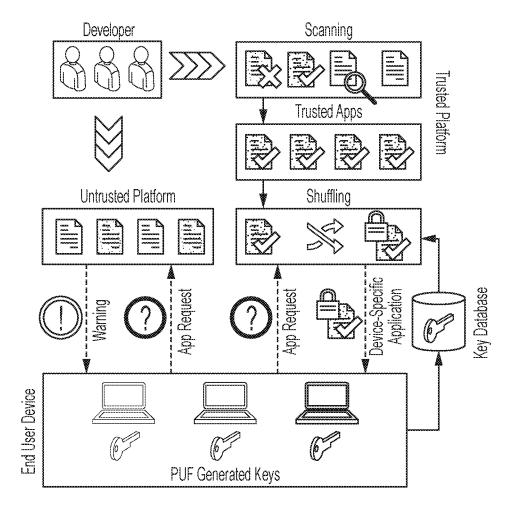

[0011] FIG. 1 is a schematic diagram for an exemplary flow for FPGA bitstream encryption and authentication;

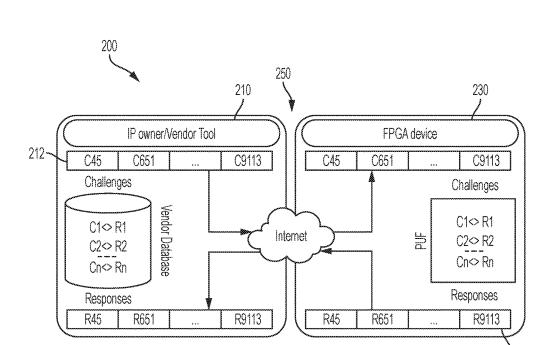

[0012] FIG. 2 is a schematic diagram for an exemplary Challenge/Response-based Communication Protocol (CRCP) in some embodiments;

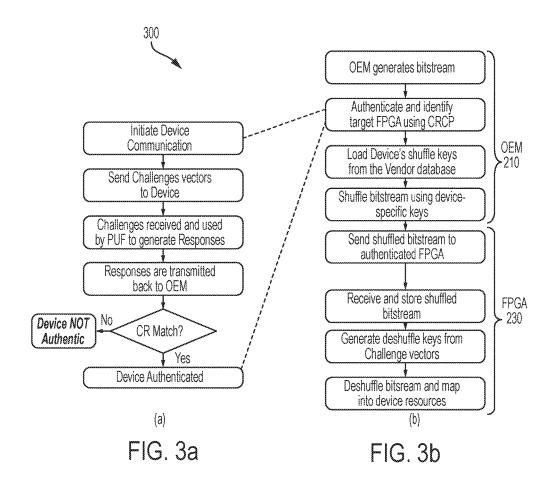

[0013] FIG. 3a is a schematic diagram showing an exemplary system flow when the Challenge/Response Communication Protocol (CRCP) identifies and authenticates a device in some embodiments;

[0014] FIG. 3b is a schematic diagram showing an exemplary system flow of the node locked bitstream approach in some embodiments;

[0015] FIG. 4 is a schematic diagram of an exemplary mapping flow in some embodiments;

[0016] FIG. 5a is a schematic diagram showing an exemplary bitstream transform key generation process, according to some embodiments:

[0017] FIG. 5b is a schematic diagram for an exemplary three level transformation scheme;

[0018] FIG. 6a is a schematic diagram for an exemplary three level transformation scheme showing three levels of transformation by the Vendor tool and three levels of inverse-transformation in the FPGA;

[0019] FIG. 6b is a schematic diagram showing an exemplary inverse transformation in some embodiments;

[0020] FIG. 6c is a schematic diagram for an example Level 1 inverse transform network operating on 16 bits of input, using 4 bits of key to transform data;

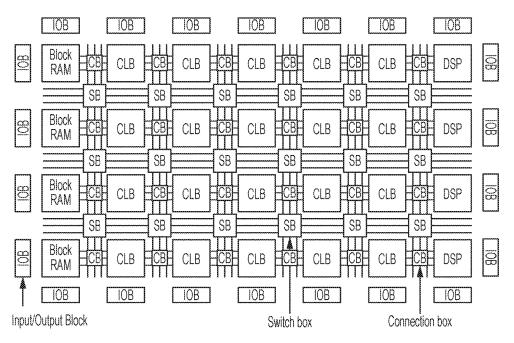

[0021] FIG. 7 is a schematic diagram showing a simplified exemplary architecture of an FPGA fabric containing CLBs, Block RAMs, DSP blocks, routing resources, and IO Blocks in some embodiments;

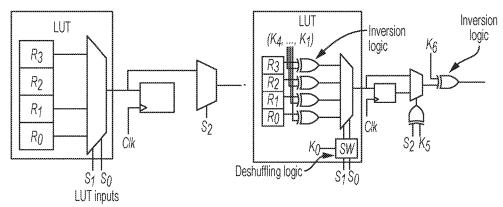

[0022] FIG. 8 is a schematic diagram of an example LUT structure containing SRAM cell and MUX with peripheral logics such as Flip Flops and MUX according to one embodiment. Various inversion and transformation logic is applied to implement permutation and selective inversion based security;

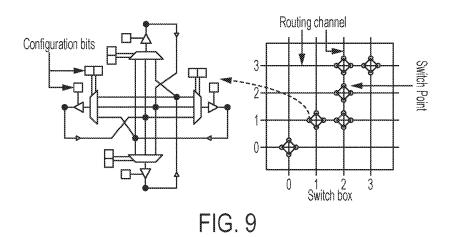

[0023] FIG. 9 is a schematic diagram showing an example of routing resources such as a switch box and gate level design of switch points;

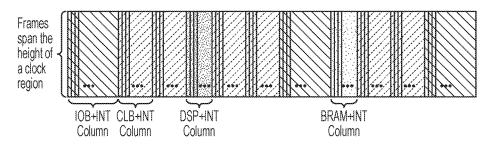

[0024] FIG. 10 is a schematic diagram showing an exemplary structure of a bitstream frame containing bits for JOB, CLB, BRAM, DSP, and their interconnects according to prior art [Ref. 19]. A single frame may represent a tiny portion of the physical FPGA layout. The whole design may be implemented through a large number of such frames;

[0025] FIG. 11 is a schematic diagram of an exemplary protocol for PUF-based application security using a trusted cloud server;

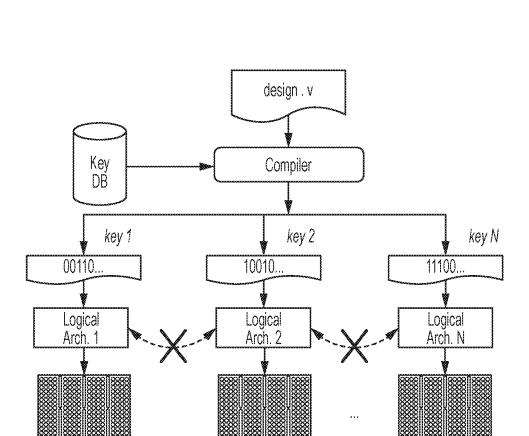

[0026] FIG. 12 is a schematic diagram showing an exemplary scheme of key-based bitstream obfuscation;

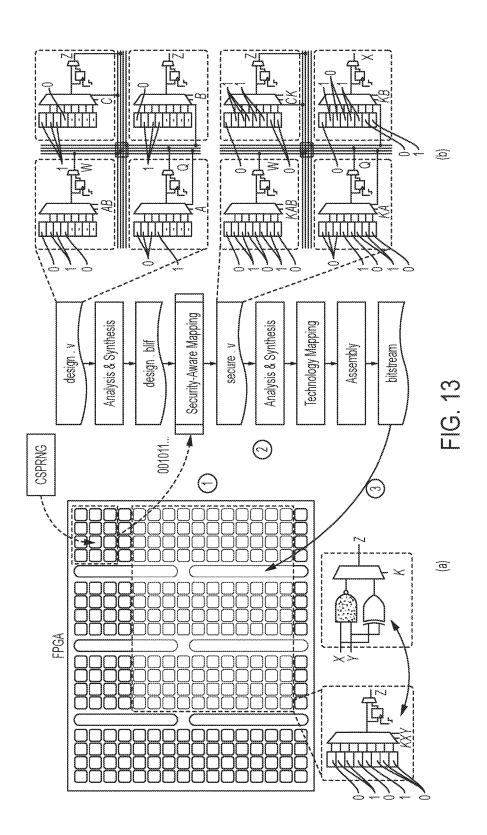

[0027] FIG. 13 is a schematic diagram showing an exemplary security-aware mapping for FPGA bitstreams;

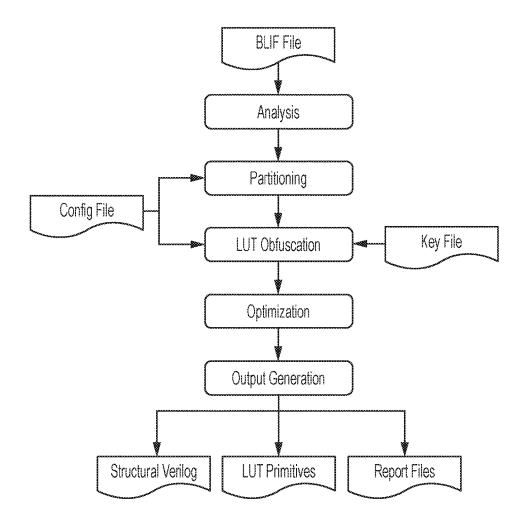

[0028] FIG. 14 is a schematic flow diagram of an exemplary software flow leveraging FPGA dark silicon for design security through key-based obfuscation.

#### DETAILED DESCRIPTION OF INVENTION

[0029] The inventors have recognized and appreciated security techniques for programmable devices that ameliorate limitations of existing security techniques, improving the usefulness of programmable devices for low cost, widely used devices, such as those that can be used to implement the IoT. For example, on-board encryption technologies used in modern FPGA-based devices incur large area and power overhead, particularly for area/energy-constrained applications. Furthermore, since the attacker typically has physical access to the device, most on-board encryption techniques are susceptible to side-channel attacks, e.g., by key extraction through power profile signatures [Ref. 1]. Moreover, they are still vulnerable to piracy and malicious alteration during in-field upgrade.

[0030] Therefore, there exists a need for a secure programmable device and programming method to safeguard against bitstream attacks, without incurring large area and energy overhead. Techniques that provide one or more of these characteristics are described herein. The inventors have recognized that two primary attack models exist for programmable devices: unauthorized reprogramming and reverse engineering. Unauthorized reprogramming using a bitstream maliciously modified by insertion of a Trojan may alter system functionality, leak information, or cause a failure. A reverse-engineered design can be sold as original, leading to Intellectual Property (IP) piracy.

[0031] To combat unauthorized reprogramming in the first attack model, the inventors have recognized that bitstream encryption may be used. FIG. 1 shows an example of such an encryption process 100. Bitstream encryption using a symmetric cypher such as Triple DES (3DES) or AES, is typically used for protecting the configuration files in the bitstream. An decryption engine inside the FPGA is used to decrypt the configuration bits before it is mapped to FPGA resources. In many cases, these keys are generated by a vendor's mapping tool and are transmitted along with the

bitstream itself. If transmitted over a network, this can greatly compromise system security.

[0032] The use of FPGA-specific keys has also been investigated. For example, a public key cryptography scheme which uses a trusted third party for key transportation and installation has been proposed [Ref. 2]. However, this scheme relies on the assumption that the FPGA has built-in fault tolerance and tamper resistance countermeasures, including multiple instances of identical cryptographic blocks for detecting operational faults, which would not be viable for area- and power-limited systems.

[0033] FPGAs like the Xilinx Zynq-7000 [Ref. 3] integrate an SoC and FPGA in a single system, and use public key cryptography for authentication during a secure boot process. The public key used to decrypt configuration files is stored in the device's nonvolatile memory, and its integrity is checked before every use [Ref. 4]. These security measures rely on a CPU to control the secure boot process, and are therefore viable only in such hybrid systems. A common feature among these encryption-based techniques is that key storage is resilient to physical attacks; however, this feature is often lacking in practice [Ref. 5].

[0034] Mathematically, the encryption algorithms are known to be highly secure against brute force attacks. However, successful Side-Channel Attacks (SCA) have been mounted against these systems, enabling decryption of the IP [Refs. 6-8]. The inventors have recognized that unless additional countermeasures are in place (e.g. obfuscation), an adversary can easily convert the bitstream to a netlist [Ref. 9], making malicious modifications possible. Therefore, even state-of-the-art methods for FPGA bitstream encryption cannot ensure IP security.

[0035] On the other hand, to counter the second model of bitstream attack such as bitstream tampering, hashed codes are often used as authentication, similar to checksums on software. While this can help prevent malicious modification, it cannot prevent reverse engineering of the IP. This method also provides key storage in nonvolatile memory, for which successful differential power analysis (DPA) attacks have been demonstrated [Ref. 10].

[0036] As discussed above, the inventors have recognized that neither encryption nor authentication alone is capable of protecting bitstreams against a motivated attacker. To mitigate this, it is desirable to design an IP protection scheme that has the following properties:

[0037] Resilient to brute force, side channel, and destructive reverse engineering attacks;

[0038] Independent of non-volatile storage, which is known to be vulnerable;

[0039] Economical in terms of production and recurring costs:

[0040] Low area and power overhead, and viable for use in IoT and other embedded devices;

[0041] Capable of restricting reconfiguration to authorized parties.

[0042] The inventors have appreciated and recognized the need to provide bitstream security against both primary bitstream attack modes. An aspect of the present disclosure provides a device and method based on changing the underlying architectural configuration of FPGA from device to device such that a bitstream can only work in a specific FPGA device. In some embodiments, an application mapping tool, such as may be used in initially programming or reprogramming an FPGA, queries a device to learn about its

architecture and then generates an appropriate node-locked bitstream (NLB) for a specific device. The query may be clone using a Challenge/Response (CR) device authentication approach. The tool then uses device-specific keys to generate a bitstream. To be effective, the NLB is unique to each device according to aspects of an embodiment. In other words, a bitstream compiled for one device may not physically map the same functions on a second. Furthermore, in some embodiments architectural changes may be achieved post-silicon, making the device and method compatible with existing processes while requesting minor adjustments to software tool flow. In some embodiments, device authentication does not rely on a key stored in a nonvolatile memory (NVM). Rather, in some embodiments, a device may use a pseudo-random function to generate an identifier for itself that may be time varying, but revealed in the CR protocol. [0043] Example embodiments of such a programmable device with protocols for device identification, authentication, reconfiguration and secure transmission of bitstreams to remote devices during field upgrade are discussed in detail below.

[0044] Furthermore, details of a security analysis are provided below demonstrating protection in some embodiments against key extraction from a bitstream and bitstream reverse-engineering with significantly decreased area and power overhead compared with area-optimized encryption blocks.

[0045] The inventors have recognized that for devices that support in-field upgrades, preventing unauthorized reprogramming of a device and ensuring unauthorized or counterfeit devices do not receive valuable upgrades are important security goals, and additional steps may be taken instead of or in addition to a Challenge Response Communication Protocol (CRCP). In one embodiment, through the use of Challenge/Response (CR)-based device authentication and device-specific keys for IP antipiracy, a solution may be provided to render FPGAs more secure against IP piracy and unauthorized reprogramming. According to an aspect, the authentication protocol involves communication between the FPGA Vendor and the Original Equipment Manufacturer (OEM), which produces the bitstream.

[0046] In one non-limiting example, CRCP is an authentication mechanism transmitting through an external interface a sequence of 64 bit Challenges as inputs to a circuit such as a Physically Unclonable Function (PUF) on the FPGA. In some embodiments, the circuit may be a MECCA PUF. Although 64 bit Challenges are used as input, any other suitable bit length may be used as the sequence of Challenges to increase the difficulty for brute force attacks to deduce the sequence. A circuit on the FPGA may be used to generate a sequence of Responses to the sequence of Challenges. The sequence of Responses is unique to the particular device and in some embodiments may be based on a unique identifier to the particular device. The unique identifier may include physical modifications performed by the FPGA manufacturer; the identifier may also include timevariant modifications based on a logical-key as described in further detail in the sections below.

[0047] FIG. 2 shows an illustrative example of the CRCP-based authentication process 200, while FIGS. 3a and 3b show another exemplary CRCP-based authentication process 300. To authenticate a device, the OEM 210 sends a predetermined number of challenges 212 through an external interface 250, and the device 230 responds in turn, as

shown in the illustrative examples in FIG. 2 and FIG. 3 by transmitting a sequence of responses 232 through the external interface. In some embodiments, the number of challenges may be variable over time. CR pairs may be batched and sent to the Vendor server, which returns a set of device-specific identifiers. In some embodiments, the Vendor/OEM communication may be through secure channels, for example via encrypted communication using industry standard methods. According to one aspect, the authentication scheme may comprise two important components: 1) the Vendor precharacterizes the devices after fabrication through an enrollment process, which ensures that only legitimate devices will receive in-field upgrades; 2) the software tools used by the OEM have access to the Vendor database containing an authorized identifier list.

[0048] In some embodiments, once the device has been authenticated, an upgrade procedure using a bitstream may begin. Because the bitstream may be wirelessly transmitted to the device and stored in NVM, it is important to transform it in some way to prevent reverse engineering. According to an aspect of some embodiments, Node Locking a bitstream is provided to an individual FPGA using a two-layer obfuscation scheme which uses both physical and logical keybased architectural modifications to provide a unique identifier to ensure a unique bitstream-to-device mapping. Example techniques to implement the two-layer obfuscation scheme are provided herein.

[0049] According to an aspect, the first of two obfuscation layers is based on physical architectural modifications to the underlying FPGA fabric. This layer is comprised of a network of fuses programmed by the FPGA manufacturer after fabrication. The selectively blown fuses may represent a portion of the unique identifier to the FPGA device as manufactured in order to enable bitstream node-locking. In some embodiments, the programming of the network of fuses may be pseudo-random. Devices which do not need reprogramming during their lifetimes (e.g. a printer) may use only the physical obfuscation layer and retain a high degree of security through architectural diversity. Furthermore, in some embodiments because each FPGA is programmed with its vendor's specific toolset, the physical modification may prevent the fabrication facility from overproducing and selling functional devices.

[0050] In some embodiments, once the device has been authenticated, the bitstream may be modified by the vendor tool prior to FPGA programming. Based on the configuration of the physical modifications, LUT content bits, programmable interconnect switches, or other configuration bits may be inverted, permuted, or otherwise transformed to fit the target architecture. In some embodiments, no additional hardware cores (e.g. decryption modules) are provided when using just the physical obfuscation layer because these are physical changes made to the FPGA, and the customized bitstream will work only with that particular FPGA. Additionally as will be discussed in relation to some embodiments below, at least one hardware core in the FPGA may be provided in combination with a logical key-based timevariant obfuscation layer.

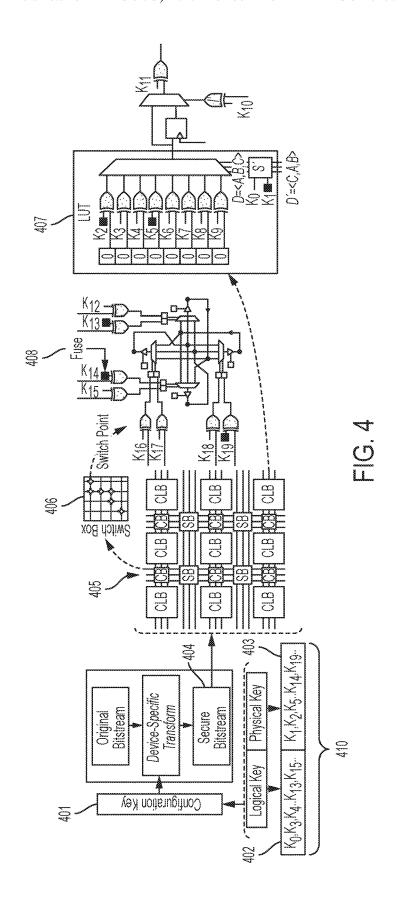

[0051] In some embodiments, logical key-based and timevariant modifications are also made to the architecture. The modifications may be realized through the addition of permutation networks which modify the functions mapped to the FPGA. The time-variant logical-key may represent a portion of the unique identifier to the FPGA device in order to enable bitstream node-locking. In some embodiments, the time-variant logical-key may be pseudo-randomly generated. The time-variant logical-key effectively evolves the architecture of the programmable device with time during, for example, each time a device such as an FPGA is reprogrammed. Similar to physical-obfuscation, the vendor tool may make modifications to the bitstream at the end of the tool flow to implement the time-variant layer of obfuscation. For example, the tool will perform a series of obfuscation functions or transformations (e.g. permutations) on the configuration bits based on the unique logical key. [0052] FIG. 4 is an illustrative diagram showing the mapping flow according to some embodiments. As shown in FIG. 4, a device key K<sub>D</sub> 401 is generated based on two portions 402 and 403 of the identifier 410 representing the physical and logical obfuscation layer, respectively. Each portion of the identifier 410 controls some aspect of the bitstream-to-device mapping via the device key 401 to generate a secure bitstream 404. The secure bitstream 404 is mapped into the FPGA fabric 405, including programmable

interconnects 406 and lookup tables (LUTs) 407. LUTs

contain physical (fuse 408-based) and time-variant (logical)

selective inversion logic.

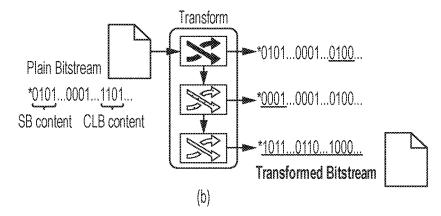

[0053] According to a non-limiting example, a multilayer transformation may be provided which operates on different portions of the bitstream in a serial fashion, such as 1) the LUT input ordering, 2) the LUT content ordering, and 3) block based transformation of the entire bitstream. FIG. 5b shows an illustrative example of a three level transformation scheme. A fourth level, which performs selective (keybased) inversion of the LUT contents, may be added after Level 2. In some embodiments, inclusion of the key-based inversion stage helps reduce the risk that functions like and with a truth table of 0001 may be used to deduce the transform key by observing the position of the "1". In some embodiments, these modifications to the bitstream are made in addition to, and with full knowledge of, the particular physical architectural changes already made to the device. [0054] In some embodiments, the obfuscated and nodelocked bitstream based on the unique device identifier is transmitted through an external interface to the authenticated

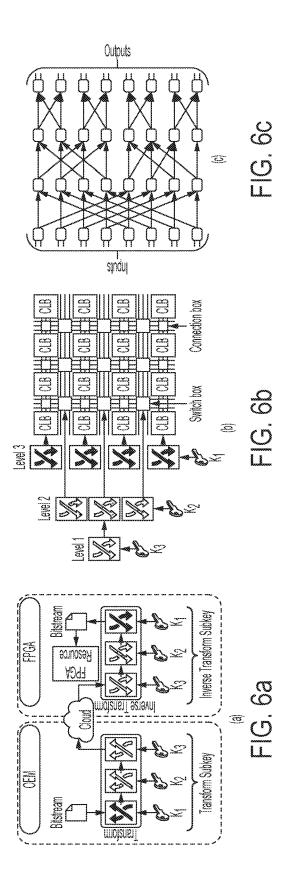

FPGA. [0055] In some embodiments, unlike the physical layer, additional hardware blocks are provided for the logical layer to perform the inverse transform. In one non-limiting example, for a multilayer transform structure, a set of three hardware cores perform serially the transform operations in reverse order of those performed by the Vendor tool. In this example, Levels 1 and 2 are both localized; that is, there are individual hardware modules which perform the inverse transform. Further according to the example, Level 3 is distributed along every row of the FPGA fabric; however, only some of these modules actually operate on data; the others may be "dummy" units which serve to further obfuscate the nature of the transform network. In this example, a successful Level 1 inverse transform may result in a valid bitstream; however, it may not function as expected unless the proper Level 2 and 3 inverse transform keys are applied. [0056] FIG. 6a shows an illustrative example of a three level transformation scheme in the embodiments discussed above. In FIG. 6a, the Vendor tool transforms the bitstream using the three device-specific keys. Level 1 reorders the LUT inputs; Level 2 permutes the LUT content; and Level

3 performs a bit-level key-based bitstream permutation. In

the example in FIG. 6b, inverse-transforming occurs in reverse order using the appropriate inverse transform keys to recover the original bitstream. FIG. 6c shows an example Level 1 inverse transform network, operating on 16 bits of input, using 4 bits of key to transform data. Although three transformation levels and three inverse transform keys are shown in the example in FIG. 6a, any number of transform levels and any number of transform/inverse transform keys may be used to apply transformation to any of the FPGA resources. In some examples, a transformation level may apply selective inversion of a portion of LUT content bits based on the key, or selective inversion of a portion of LUT outputs based on the key, where the key can be physical or logical, or a combination of each.

[0057] Thus, with the combination of physical and logical architectural changes, the embodiments discussed above allow a unique bitstream-to-device mapping to be obtained. Though both physical and logical layers depend on a key, the physical changes may be accomplished using fuses, which cannot be changed at a later time. However, the logical key-based modifications may be time variant, which means that the architecture may effectively change with every reprogram cycle, making it impractical for an adversary to mount a known design attack.

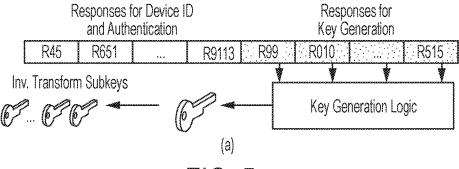

[0058] FIG. 5a provides an illustrative diagram showing an embodiment of a device key management protocol. Responses from the PUF that are not retransmitted for authentication purposes may be used instead to generate the key, as shown in FIG. 5. Furthermore, the responses used to generate the keys are selected by a decoder in the generation module; as an added measure of security, select bits may be randomly disconnected from the supply circuit using a series of fuses during enrollment.

[0059] A complete bitstream generation flow according to some embodiments is shown in the illustrative diagram in FIG. 3(b). Each time the FPGA is upgraded, a different set of challenges may be issued, from which a different set of transform keys are generated. Such a moving target defense may help further secure the IP and prevent unauthorized reprogramming with previously used transform keys. Therefore, only after the device is authenticated and identified can the transformed bitstream be generated and sent to the device.

[0060] Having thus described several aspects of some embodiments of this invention, the following provides exemplary security analysis and overhead analysis of the device and method in the aforementioned embodiments comparing power, performance, and area overhead to commodity AES encryption cores.

[0061] Security Analysis

**[0062]** In some embodiments, a security analysis is provided for three attack scenarios, namely 1) brute force, 2) side channel attacks, and 3) destructive reverse engineering. The attacker may intend to reverse engineer the design either for monetary gain, or perform malicious modification and reprogram the device.

[0063] Brute Force Attack

[0064] A brute force attack represents the most challenging and time consuming attack on the system. Four attack stages are analyzed; for each stage, the attacker begins with incrementally more information.

#### Example Case 1.1.1

[0065] The attacker has, by some means, obtained a copy of the transformed bitstream.

[0066] Result: Without knowledge of the bitstream structure (e.g. fixed header contents), the attacker cannot identify the correct inverse transform key, even for Level 1. Thus, a brute force attack cannot be properly mounted, and the IP remains secure.

#### Example Case 1.1.2

[0067] The attacker has a copy of the transformed bitstream and knows the bitstream structure (e.g. typical contents of the header).

[0068] Result: The attacker can mount a brute force attack and attempt to deduce the Level 1 transform key. In this example, a 128 bit key may operate on 16 bit blocks, each of which is permuted using 4 bits. Thus, the number of possible permutations for each of the (128/4=32) blocks is  $16^{32}=2^{128}$ . This provides the first level of defense. Even if this is broken, Levels 2 and 3 are intact and the IF remains secure.

#### Example Case 1.1.3

**[0069]** The attacker begins with a Level 1 inverse transformed bitstream, and intends to break Levels 2 and 3.

[0070] Result: A Level 1 inverse transformed bitstream may be mapped to an FPGA or simulated using a bitstream-to-netlist tool. For each possible combination of the LUT inputs and outputs, the attacker performs the conversion, provides the proper stimuli, and observes I/O patterns. Without detailed knowledge of the intended functionality, or a sufficiently large set of test vectors, the process cannot be automated. Even with sufficient test vectors, brute force is not feasible: in an example of a set of 4×1 LUTs with four content bits and the possibility that some of the content bits may be inverted, the LUT can take 1 of L!×I possible states, where L is the LUT size, and I is the number of possible inverted.

**[0071]** I is computed as  $\Sigma_{r=1}{}^{LL}C_r$ , which for L=4 gives 15 inversions; thus, each LUT can take 1 of 4!×15=360 combinations. Transforming the 4 bit LUT requires 2 bits of the key; thus, the 128 bit key operates on 64 blocks a search space of  $360^{64}$ = $2^{543.5}$ . When considering the Level 3 transform, 2 transform bits may be provided, requiring 1 key bit, giving us up to 128 Level 3 inverse transformers. Depending on the size of the FPGA, only a portion of these may be used. With all 128 inverse transformers, this yields  $21^{28}$  possibilities

#### Example Case 1.1.4

**[0072]** The attacker has obtained all three transform keys, and has applied the Level 1 and 2 inverse transformers, leaving only the Level 3 transform intact.

[0073] Result: Without the architectural knowledge of which rows in the FPGA fabric have an active transformer, the attacker cannot know to which bits the Level 3 inverse transformer should be applied. Let R represent the number of rows in the FPGA fabric, and D the number of active inverse transformers. The possible permutations is represented by  $^{R}P_{D}$ . For a small FPGA (e.g. Xilinx XC3S50) with R=16 and D=12, we have  $^{16}P_{12}\approx 2^{39.7}$  possible inverse transform networks. On a larger FPGA, with R=512 and

D=128, this would increase to  $^{512}\mathrm{P}_{128}{\approx}^{1127}$  possible networks. If D is unknown, these values represent the lower bound of attempts in a brute force attack.

[0074] Thus, in the example brute force attack scenarios discussed above, by itself, the Level 1 inverse transform presents a challenge to a brute force attacker; in the example case where the Level 1 inverse transform is compromised, Level 2, including the key-based inversion, and Level 3, including both the key-based input transform and the "dummy" inverse transformers make a brute force attack impractical.

[0075] Side Channel Attack (SCA)

[0076] Compared with brute force, a SCA is a more refined attack. Two example scenarios are presented herein in which one or more of the keys have been discovered in this manner.

#### Example Case 1.2.1

[0077] The attacker uses power analysis (e.g. DPA) to discover the challenge vectors stored in NVM.

[0078] Result: Responses are generated on-the-fly using a PUF, so leaking the challenge bits is not useful without an accurate PUF model. The generation procedure is purely combinational, using no latches of flip flops, and therefore is less vulnerable to power analysis.

#### Example Case 1.2.2

[0079] The attacker has discovered one or more of the CR pairs, for example through the use of wireless packet analysis.

[0080] Result: With sufficient CR pairs, the attacker may be able to refine a model of some kinds of PUFs (e.g. arbiter or ring oscillator PUF), making the choice of PUF crucial to system security. In some embodiments MECCA PUF may be a good choice because it is resistant to these attacks. In any case, very few pairs are sent each upgrade, limiting the attacker's potential knowledge of the system.

[0081] SCA attacks may be used to leak the Challenge vectors or isolate CR pairs from packet analysis. However, as discussed above in Example case 1.4 under the Brute Force Attack scenario, knowledge of the Level 3 key is insufficient to fully inverse transform the design. Thus, in the example SCA scenarios discussed above even if modeling attacks are successful, the IP remains secure.

[0082] Destructive Reverse Engineering (DRE)

[0083] DRE is an expensive and time consuming process, but it can reveal the inner workings of the device. Two example scenarios of using DRE attacks are discussed.

#### Example Case 1.3.1

[0084] DRE is used to reveal the structure of the Level 3 transform network, including which rows contain deactivated inverse transformers.

[0085] Result: This reduces the number of possible bitstream permutations. However, without further analysis (e.g. successful PUF modeling), the IP remains secure.

#### Example Case 1.3.2

[0086] DRE is used to reveal the PUF structure, potentially making the device vulnerable to these attacks and reducing the search space for the correct transform key.

[0087] Result: Modeling attacks have been proposed and successfully executed for certain PUFs (e.g. Arbiter PUF

[Ref. 12]). Nevertheless, there is inherent uncertainty in the probabilistic approach employed by the attack models, and some PUFs have been proposed [Ref. 13, 14] which are resistant to these attacks. Even if the transform key is revealed, knowledge of the Level 3 transform network, which may demand further DRE, is desired to make use of it.

[0088] Therefore, from the above analysis of three types of example attack scenarios, it is clear that even with a combination of SCA and DRE attacks, some level of brute force is still necessary to inverse transform a single bitstream for a single device. Of all the attacks presented above, the only one with wide-ranging consequences is the discovery of the Level 3 transform network. By itself, this does not fully compromise the system; significant analysis, and some brute force, may still be required. Furthermore, the device-specific keys and CRCP disclosed in some embodiments also ensure that unauthorized reprogramming on other IoT connected devices will not be possible, since only one specific device can acquire the targeted upgrade, making malicious modification and reprogramming infeasible. This approach reduces, and perhaps entirely mitigates, the economic motivation for an attacker.

[0089] 2) Overhead Analysis

[0090] In this section, the power, performance, and area overhead incurred using the bitstream security system disclosed in some embodiments are analyzed. Components are implemented in Verilog, simulated to verify functionality, and synthesized with Synopsys Design Compiler using a 90 nm cell library. Results for Area, Power, Delay, and Energy of the various modules are listed in Table 1. Results represent an FPGA with one Device Key Module (DKM), three Response Generator Modules (RGM), one Level 1 and one Level 2 Inverse transform Logic Module (DLM1 and DLM2), and 32 DLM3 modules.

TABLE 1

Synthesis results at 90 nm. "Num Inst." is the number of instances considered in the results.

Delay and Energy are for a 512 kB bitstream.

Mod. Num Area Area Pow. Delay En.

Name Inst. (µm2) (Gates) (mW) (ns) (pJ)

| Mod.<br>Name | Num<br>Inst. | Area<br>(µm2) | Area<br>(Gates) | Pow.<br>(mW) | Delay<br>(ns) | En.<br>(pJ) |

|--------------|--------------|---------------|-----------------|--------------|---------------|-------------|

| DKM          | 1            | 9398          | 827             | 1.08         | 1.38          | 1.49        |

| RGM          | 1            | 145           | 34              | 0.02         | 1.18          | 0.02        |

| DLM1         | 1            | 1063          | 115             | 0.18         | 6200          | 1120        |

| DLM2         | 1            | 4273          | 406             | 0.77         | 33.0          | 25.4        |

| DLM3         | 32           | 4328          | 460             | 0.67         | 0.17          | 3.64        |

| Total        |              | 19207         | 1842            | 2.72         | 6236          | 1150        |

[0091] 2.1) Device Key Modules

[0092] In this example, the DKM is a purely combinational circuit with no memory elements. The input selects 2 of 8 PUF-generated responses, each 64 bits in length.

[0093] 2.2) Response Generator Modules (RGMs)

[0094] In this example, the RGMs are based on the MECCA PUF [Ref. 13], which uses an existing SRAM memory array to generate a response. A programmable pulse generator using a tapped inverter chain interfaces with existing SRAM peripheral logic; very little extra hardware may be needed.

[0095] 2.3) Inverse Transform Logic Modules

[0096] In some embodiments, inverse-transformation may occur in three separate stages, each controlled by a separate

128 hit key. Note that timing is reported for each module independent of external factors, such as serial to parallel (or parallel to serial) conversion in and out of the modules.

[0097] 2.3.1) Example with Level 1: In this example, a 16 input Banyan switch network implements the Level 1 inverse-transformation logic. Four bits of the transform key are used as inputs to each column of switches.

[0098] 2.3.2) Example with Level 2: The second level inverse transforms the LUT content Like Level 1, the key determines the mapping from input to output ordering. In this example, LUT responses are defined by 4 bits; thus, the network operates on 16 inputs, each a 4 bit vector. Selective inversion of the transform bits is determined by the transform key.

[0099] 2.3.3) Example with Level 3: The third level inverse transforms the LUT inputs, and inverse transformers are distributed among the rows in the FPGA fabric. An immense FPGA fabric is provided in this example with 1024 rows, and therefore 1024 transform networks (some are deactivated). All LUTs are 4×1 in this example, and thus have two select inputs.

[0100] 3) Comparative Analysis

[0101] The total area, power, and latency overhead may be analyzed in the embodiments disclosed above as the sum of the respective parameters for each module. Table 2 compares the analysis results with several AES cores (from both IP vendors and literature).

TABLE 2

Comparing the Node Locked Bitstream (NLB) with

| AES ASIC cores. Delay and Energy are calculated from throughput for a 512 kB bitstream. |              |                 |              |               |              |  |  |

|-----------------------------------------------------------------------------------------|--------------|-----------------|--------------|---------------|--------------|--|--|

| Mod.<br>Name                                                                            | Tech<br>(nm) | Area<br>(Gates) | Pow.<br>(mW) | Delay<br>(µS) | EDP<br>(J*s) |  |  |

| NLB                                                                                     | 90           | 1.8k            | 2.72         | 6.2           | 1.07e-13     |  |  |

| [Ref. 15]                                                                               | 180          | <3k             | _            | 64000         | _            |  |  |

| [Ref. 16]                                                                               | 130          | 3.1k            | 5.62         | 33850         | 6.44e-6      |  |  |

| Tiny [Ref. 17]                                                                          | 130          | <5k             | _            | 40960         | _            |  |  |

| Std. [Ref 18]                                                                           | 90           | 8.8k            | _            | 2800          | _            |  |  |

| Std. [Ref 17]                                                                           | 130          | <9.5k           | _            | 630           | _            |  |  |

[0102] Table 2 shows that in some embodiments, even after scaling power and throughput to the 90 nm node, the Node Locked Bitstream method is faster than the area- and power-optimized crypto cores, and incurs a lower area and power overhead, making it ideal for power- and area-constrained systems. Furthermore, like the crypto cores, it offers excellent security against brute force attacks. In addition, it is more resilient to SCA and even DRE attacks.

[0103] The NLB system disclosed herein is capable of protecting FPGA bitstreams against a number of attacks, including brute force, side channel, known design attacks and destructive reverse engineering, effectively preventing IP piracy and malicious modification. Having thus described several aspects of some embodiments of this invention, it is to be appreciated that various alterations, modifications, and improvements will readily occur to those skilled in the art.

[0104] For example, the NLB concept may be extended, first by adding additional layers of security beyond those previously listed for FPGA, and by applying these concepts

to the domain of software security for microcontrollers (firmware) and more complex processors (full software applications, including those compiled to machine language or interpreted code, for example Java). These extensions are attractive for a number of reasons:

[0105] Additional security makes it less likely for an attacker to successfully pirate, reverse engineer, or maliciously modify the IP by including terms which exhibit factorial growth.

[0106] It allows for the consideration of additional FPGA hardware structures, and presents opportunities to identify more cost effective modifications, providing equivalent-orbetter security using the same or fewer key bits; this in turn provides an empirical means to optimize security versus area/power/delay overhead in different FPGA implementations.

[0107] The inventors have recognized that microcontrollers (and their various application domains, including automotive, communication, consumer electronics, among others) present an even larger market than FPGA, and receive firmware upgrades at least as frequently as an FPGA-based device from trusted vendors (e.g. Original Equipment Manufacturers, OEM). Ensuring the integrity of these firmware upgrades, especially those transmitted Over the Air (OTA) is essential to maintaining device security.

[0108] A discussion of microcontroller firmware security further leads to methods which can improve security for systems with more complex General Purposes Processors (GPPs), including desktop and laptop computers. Users of these systems can download software from a plethora of online sources, many of which can be counterfeit or malicious, resulting in malware which can wreak havoc on a system or leak personal information to an attacker. Controlling the sources of these applications and judiciously restricting the ability of a target architecture to execute them can help curb both the distribution of malicious software, as well as the unauthorized distribution of proprietary software, thus doubling as an alternative to software node-locking.

**[0109]** The following three sections describe additional embodiments providing extensions to the NLB framework discussed above for the application in (1) FPGA bitstream security. (2) microcontroller firmware security, and (3) general purpose processor security.

[0110] Extensions of NLB for FPGA

[0111] In some embodiments, FPGA security can be extended using additional permutation and selective inversion networks, operating not only on the LUT content, LUT input, and the bitstream as a whole, but on any amenable hardware structure on the FPGA. These resources include, but are not limited to, the following: configurable logic blocks (CLBs), routing/programmable interconnects, block RAM/embedded memories, DSP blocks, IO blocks and clocks/PLLs.

[0112] A simplified example of the FPGA architecture combining the mentioned resources is shown in FIG. 7. Tables 3, 4 and 5 summarize different aspects of implementing the obfuscation model on different resources according to some embodiments. The NLB model may be implemented on individual resources, or on multiple resources in parallel to increase the level of security.

TABLE 3

|                      | Various aspects of implementing permute and selective inversion networks on CLB resources. |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                      | Sub-                                                                                       |                                                                                                                                                                                                                             | Architectural change required to                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Resource             | resource                                                                                   | Resource Description                                                                                                                                                                                                        | map the IP from obfuscated bits                                                                                                                                                                                                                                                                                                                                   | Required Key bits                                                                                                                                                                                                                                                                                      | Resultant Diversity                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| CLB content (FIG. 8) | LUT<br>Content<br>LUT<br>Content<br>Selective<br>Inversion                                 | Lookup Tables (LUTs) contain SRAM cells which old function responses ("Current") required for the design.                                                                                                                   | The actual content bits to the configuration bitstream will be permuted using the compilation tool. In the FPGA, a harware block within the LUT undoes this operation. Forward and inverse transforms are done using a key.  Certain content bits will be inverted inside the tool based on a Key. Symmetric inverse transform The recovery of original key bits. | Assume number of LUT inputs is 1 and number of Content bit $\mathfrak{D}=\mathfrak{D}$ . The required key to shuffle L bits is $\log_2(L)$ . Example: for 4 input LUT with 16 content the key size is $\log_2(16) = 4$ . To invert, one key bit is required per content bit. Key size equals LUT size. | For LUT with $\mathfrak{D}$ , $\mathfrak{D}$ the number of different possibilities would be $1\mathfrak{D}$ . Example: Let $\mathfrak{D} = 4$ , there are $4\mathfrak{D}$ (24) possible combinations. In practice, $\mathfrak{D} = \mathfrak{D}$ or $\mathfrak{D}$ are more common. For a certain LUT. the number of content bits to be $\mathfrak{D}$ is equivalent to the number of logic $\mathfrak{D}$ 's in the subkey, given $\mathfrak{D}$ r. Attackers must |  |  |  |  |  |

|                      |                                                                                            |                                                                                                                                                                                                                             | bits. The inversion logic take the key and inverts based on ①. The resultant bits in the SRAM cell maps the original design.                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                        | search all possible values of $\mathfrak{D}$ , requiring $\mathfrak{D}^L(\mathfrak{D})$ Example: Let L = 4. This gives $\mathfrak{D}$ possible combinations. LUTs where L = $\mathfrak{D}$ or $\mathfrak{D}$ are common in $\mathfrak{D}$ ,                                                                                                                                                                                                                         |  |  |  |  |  |

|                      | Funtion<br>Input<br>Multiplier                                                             | LUT function evaluation results from the selection of certain content bits being selected by a multiplexor (mux). the mux inputs represent function inputs. These can be selectively modified.                              | One hardware block performs the inverse transform on the function input, resulting in correct function output from the LUT.                                                                                                                                                                                                                                       | Requires $\mathfrak{O} = \log_2(L)$ key bits to permute the inputs for $\mathfrak{O}$ LUT with $\mathfrak{O}$ funtion responses.                                                                                                                                                                       | <ul> <li>⑦ large search spaces.</li> <li>For a LUT of ⑦ inputs, there can be ℚ possible orderings.</li> <li>Example: for ℚ 4 input LUT, an attacker ℚ to consider ℚ = 24 different possibilities.</li> </ul>                                                                                                                                                                                                                                                        |  |  |  |  |  |

| CLB<br>content       | FF-Mux<br>bit<br>inversion                                                                 | Content bits in LUTs only implement combinational logic. To map sequential logic, Flip Flops (FF) are needed. A mux selects if the LUT output will be                                                                       | A single bit in the configuration bitstream is responsible for the FF selection via MUX. The select bit of the MUX that Tbypasses the FF can be                                                                                                                                                                                                                   | The selection of FF is done by a 2:1 MUX which has one select bit. The key size is therefore 1 for each $\mathfrak{D}$ .                                                                                                                                                                               | For each LUT, 2 different probability. Either the LUT goes to the FF, or bypasses the FF.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| CLB content          | LUT<br>output<br>inversion                                                                 | connected with the FF. The final LUT output  with or without FF) can be inverted. This outpu  connect to the inputs of multiple LUTs.                                                                                       | For a single LUT, one inversion logic is required with the output. Based on the key, the output will be inverted.                                                                                                                                                                                                                                                 | 1 Key bit required for a single output.                                                                                                                                                                                                                                                                | For any LUT, 2 different probabilities are present. However, this effects other LUTs that take this output as an input. Therefore the search space increases. If the output Y is input to some other LUT; while ② each possible ③ of the connected LUT, the adversary has to consider both Y and Y②,                                                                                                                                                                |  |  |  |  |  |

| CLB<br>content       | Carry<br>logic<br>Mux bits<br>inversion                                                    | Carry logic is available inside CLBs with each LUT fo propagation of carry bits while long digits.                                                                                                                          | Carry logic of LUT is selected MUX. For 2:1 MUX the selection bit is a single . This single configuration bit can be altered inverted using one inversion logic.                                                                                                                                                                                                  | Only 1 Key bit is required per LUT.                                                                                                                                                                                                                                                                    | for each LUT the design can either have or not have $\mathfrak{O}$ logic based on the key bit. For N number of LUTs the chances are $2^N$                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| CLB<br>content       | Inter-<br>connect<br>matrix<br>inside<br>CLB                                               | © channels (wires) go inside the CLB and connect to LUTs. LUT outputs also connect to the input of adjacent LUTs of the same CLB or feedback to itself. Such connections are done by an interconnect matrix inside the CLB. | To our knowledge the low level architecture of the interconnect matrix is not revealed by the ①. However, it should be similar to Switch ② architecture which is known. Therefore we can refer to the analysis of the Switch Box.                                                                                                                                 | Refer to the analysis of<br>the Switch Box.                                                                                                                                                                                                                                                            | Refer to the analysis of the Switch Box.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

$<sup>\</sup>ensuremath{\mathfrak{D}}$  indicates text missing or illegible when filed

TABLE 4

| Resource                                           | Sub-<br>resource  | Resource Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Architectural change required to map the IP from obfuscated bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Required Key bits                                                                                                                                                                                                                                                                                                                 | Resultant Diversity                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Routing<br>resources<br>outside<br>CLB<br>(FIG. 9) | Connection<br>box | Connection boxes connect<br>wires to and from CLBs<br>with the main channel<br>outside the CLB.                                                                                                                                                                                                                                                                                                                                                                             | Refer to the analysis of the Switch Box.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Refer to the analysis of the Switch Box.                                                                                                                                                                                                                                                                                          | Refer to the analysis of the Switch Box.                                                                                                                                                                                                                                                                                                                                                                             |

|                                                    | Switch<br>Box     | The Switch boxes connect horizontal and vertical routing channels. Each Switch Box is composed of a number of switch points which can connect certain wires. The low level design is shown in the . Based on the configuration bits the switch point routes certain wires to different directions. Inside the switch points, SRAM cells connect with the MUXs and tristate buffers that control the routing. These cells hold the configuration bits for the switch points. | There are 12 configuration bits for each switch point. If the bits are shuffled, 12 bits would require a deshuffler block controlled by 4 key bits.  If the bits are inverted inside the tool, the inverted configuration bits have to pass through the inversion logic before programming the switch point.  As there are multiple switch point per switch box, and a large number of switch boxes inside the FPGA, we may obscure only a selected number of switch boxes. It will keep the key size limited and improve the difficulty of deobfuscation. | For a single switch point with B configuration bits, N switch points in a switch box, and the S different switches to consider, then total key bits required for shuffling would be, N * S * Log <sub>2</sub> (B). For inversion. If r bits are inverted the required key for whole FPGA would add a factor of r bits to the key. | For shuffling, the possible search space is $\mathbb{R}^{\mathfrak{D}}$ for switch point. If r bits are inverted among B, the search space is $= \Sigma_r^{BB} C_r$ . If both $\mathfrak{D}$ and inversion are done, the search space increases to $\mathbb{R}^{\mathfrak{D}}$ $\Sigma_r^{BB} C_r$ for a single point. Therefore, for the whole FPGA it is $N + S + \mathbb{R}^{\mathfrak{D}}$ $\Sigma_r^{BB} C_r$ . |

$<sup>\</sup>ensuremath{\mathfrak{D}}$  indicates text missing or illegible when filed

TABLE 5

| Resource      | Sub-<br>resource                                                                                                                                                              | Resource Description                                                                                                                                                                                                                                                                                                                                                                | Architectural change required to map the IP from obfuscated bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Required<br>Key bits                                                | Resultant<br>Diversity      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------|

| Block<br>RAM  | RAM Content  RAM Size (8 KB, 36 KB etc.) Data width and address width ② made ②/Single) Multi-RAM Interconnect Logic Read/Write Operation Sequence Specification Interconnects | Embedded block RAM are actually kilobytes of SRAM for storing data. These RAMs are hard blocks and can be initialized in different sizes and operational modes which is defined in the bit stream. The block RAM content, the programmable interconnects, and the specifications are defined by specific groups of bits in the bitstream frame. A sample frame is shown in FIG. 10. | If the initial contents of the RAM are shuffled or inverted inside the tool, the inverse transform can be applied internally using shuffle blocks and inversion logic. However, if the content bits of the SRAM are readable while the FPGA is operating, the adversary may be able to exploit this to determine the shuffling pattern. Therefore, it may be more secure to not modify the memory configuration if there is also an external memory interface.  Operational mode and RAM size are defined while writing the HDL code of the IP which turns into configuration bits. These bits are placed into specific frames. The exact frame structure which shows exactly which bits are responsible for certain specification is not open to the public. But as the vendors have the information, they can shuffle those bits and later deshuffle them using a centralized deshuffler inside the FPGA | Valid assur<br>depends or<br>the bitstrea<br>configuring<br>RAMs.   | n details of<br>um used for |