# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2018/0315750 A1 Hoffman

Nov. 1, 2018 (43) **Pub. Date:**

### (54) GRAPHENE FET DEVICES, SYSTEMS, AND METHODS OF USING THE SAME FOR SEQUENCING NUCLEIC ACIDS

(71) Applicant: **Agilome, Inc.**, San Diego, CA (US)

Inventor: Paul Hoffman, San Diego, CA (US)

(21) Appl. No.: 16/025,794

(22) Filed: Jul. 2, 2018

#### Related U.S. Application Data

(60) Division of application No. 15/225,764, filed on Aug. 1, 2016, now Pat. No. 10,020,300, which is a continuation-in-part of application No. 15/182,533, filed on Jun. 14, 2016, now Pat. No. 9,859,394, said application No. 15/225,764 is a continuation-in-part of application No. 15/065,744, filed on Mar. 9, 2016, now Pat. No. 9,618,474, which is a continuation-in-part of application No. 14/963,253, filed on Dec. 9, 2015, said application No. 15/225,764 is a continuation-inpart of application No. 14/963,253, filed on Dec. 9, 2015.

(60) Provisional application No. 62/175,351, filed on Jun. 14, 2015, provisional application No. 62/130,621, filed on Mar. 10, 2015, provisional application No. 62/206,228, filed on Aug. 17, 2015, provisional application No. 62/199,987, filed on Aug. 1, 2015, provisional application No. 62/130,594, filed on Mar. 9, 2015, provisional application No. 62/094,016, filed on Dec. 18, 2014, provisional application No. 62/130, 598, filed on Mar. 9, 2015, provisional application No. 62/130,594, filed on Mar. 9, 2015, provisional application No. 62/130,601, filed on Mar. 9, 2015, provisional application No. 62/199,987, filed on Aug. 1, 2015, provisional application No. 62/199,956, filed on Jul. 31, 2015.

#### **Publication Classification**

(51) Int. Cl. H01L 27/085 (2006.01)(2006.01)G01N 27/414 (2006.01)H01L 29/16

(52) U.S. Cl. CPC ...... H01L 27/085 (2013.01); G01N 27/4145 (2013.01); G01N 27/4146 (2013.01); C12O 1/6874 (2013.01); **H01L 29/1606** (2013.01)

#### (57)ABSTRACT

Provided herein are integrated circuits for use in performing analyte measurements and methods of fabricating the same. Such arrays may be employed to detect a presence and/or concentration changes of various analyte types in chemical and/or biological processes, including DNA hybridization and/or sequencing reactions. The methods for fabricating the integrated circuits include steps of depositing an insulating layer on a semiconducting substrate, and forming trenches in the insulating dielectric layer. Conductive material may be deposited in the trenches to form electrodes, and the insulating layer may be conditioned so that the electrodes protrude above the insulating layer. A 2D material, such as graphene, may be deposited on to electrodes to form a channel between the electrodes.

FIG. 1J

FIG. 1K

FIG. 1L

FIG. 1M

FIG. 1N

FIG. 10

FIG. 1P

FIG. 1Q

FIG. 1R

FIG. 1S

FIG. 1T

FIG. 1U

FIG. 1V

FIG. 1W

FIG. 1X

FIG. 1Y

FIG. 1Z

FIG. 1AA

FIG. 1BB

31

39b

39a

34

24

FIG. 2E

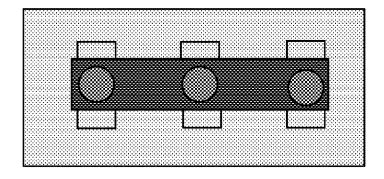

FIG. 3C

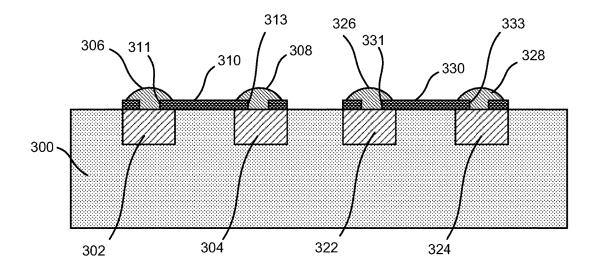

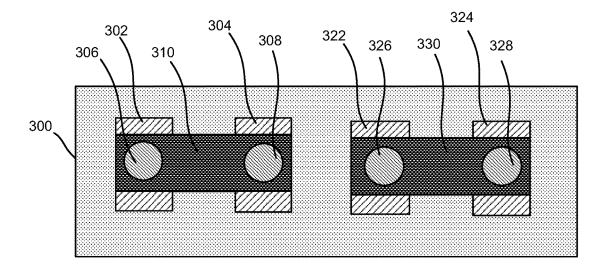

FIG. 4C

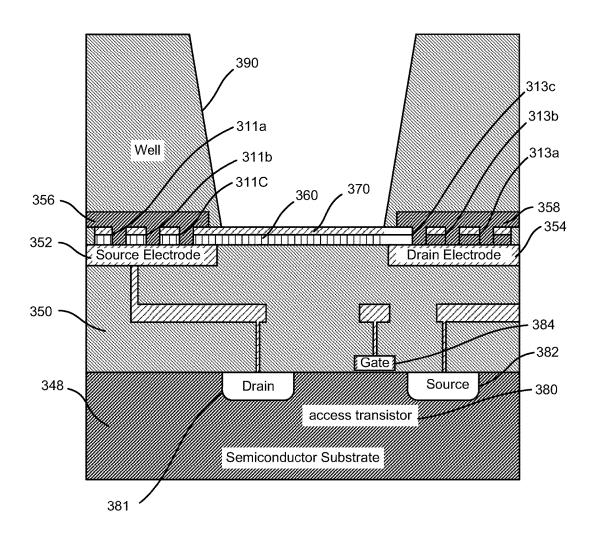

FIG. 5E

FIG. 6A

FIG. 6B

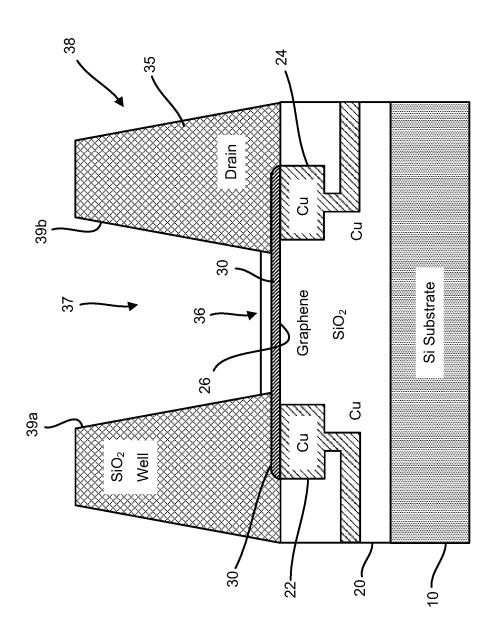

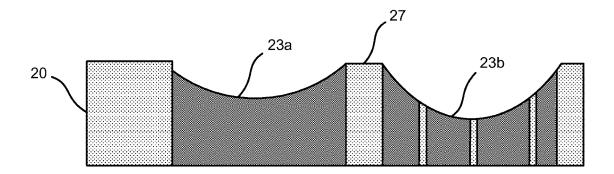

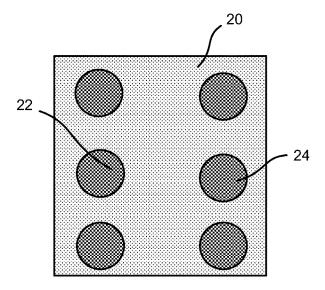

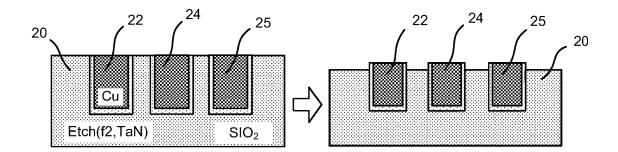

FIG. 6C

FIG. 6D

FIG. 6E

FIG. 6F

= K +aVg + bVg2 + cVg3...

$$I2 = K +xVg + yVg2 + zVg3...$$

FIG. 6H

FIG. 6I

FIG. 7B

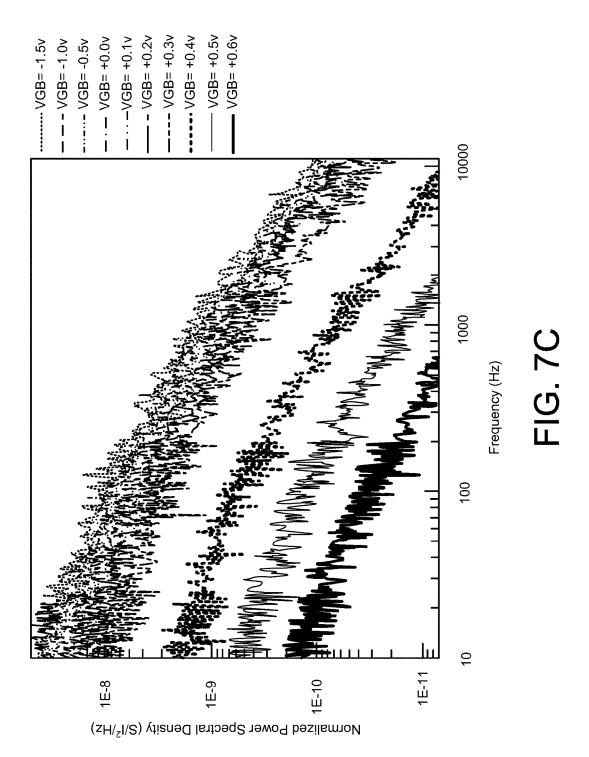

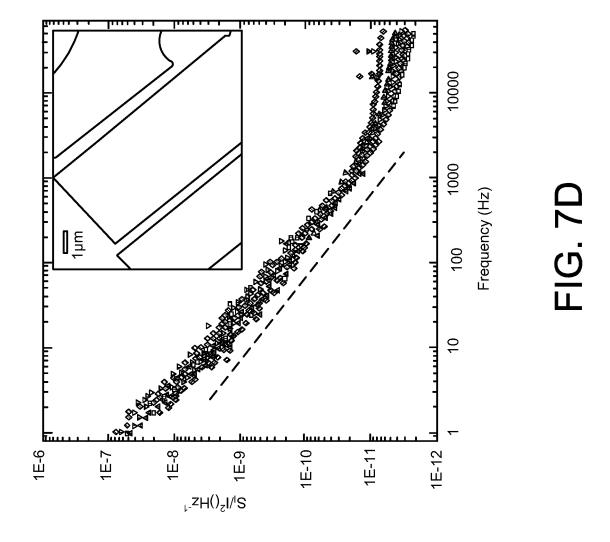

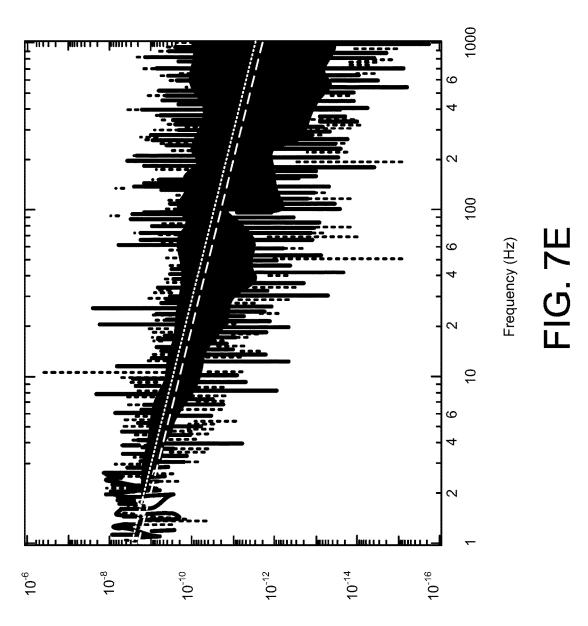

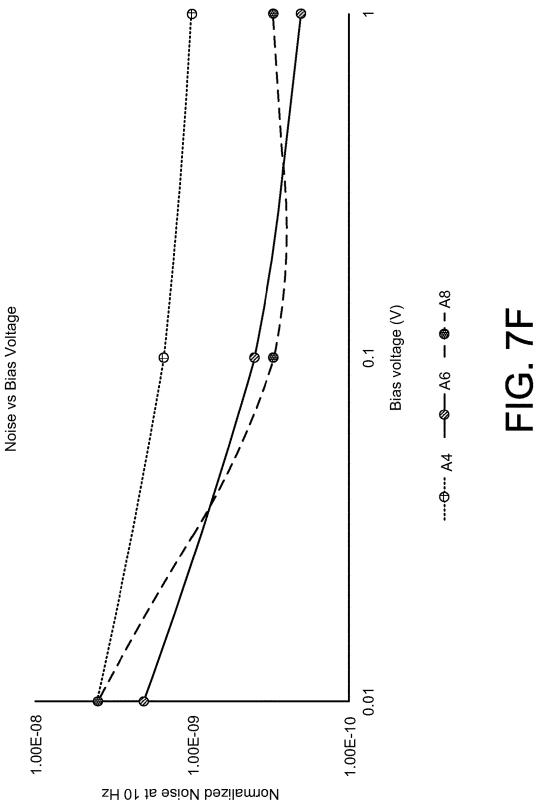

Normalized Power Spectral Density  $(S/I^2 \setminus Hz)$

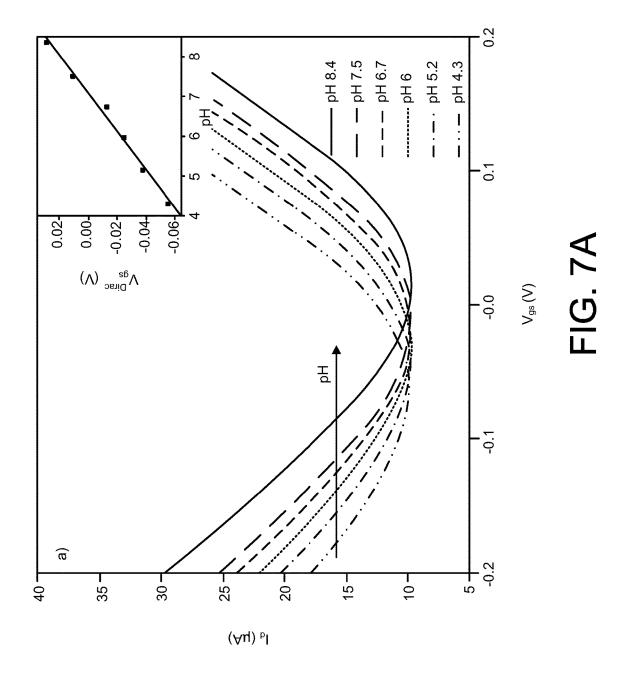

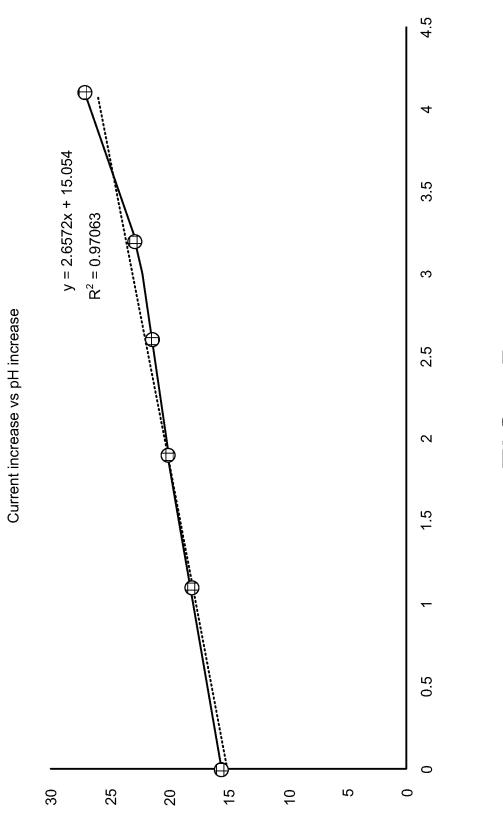

30 25 y = 0.0079x - 0.1794Dirac Voltage vs Current increase 15 10 2 0.04 0.02 0 -0.02 -0.04 -0.06 -0.08

**FIG. 7G**

FIG. 8B

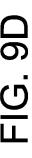

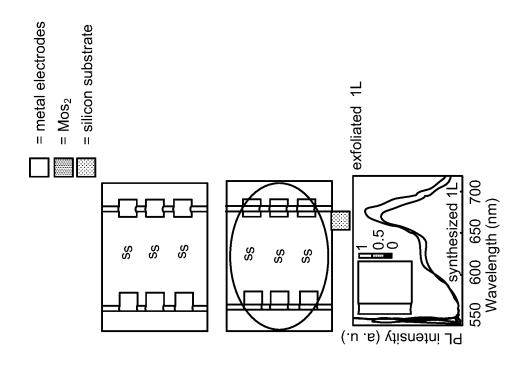

FIG. 9A

= metal electrodes = silicon substrate = graphene

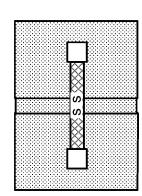

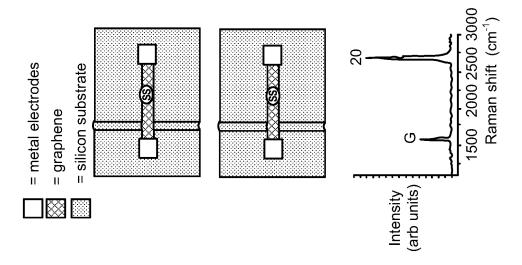

FIG. 9C

FIG. 11

FIG. 12

FIG. 15

FIG. 16

FIG. 17A

FIG. 17B

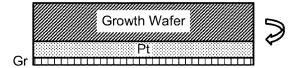

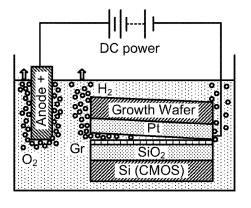

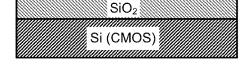

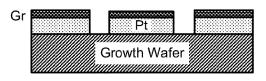

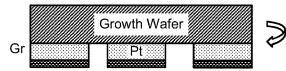

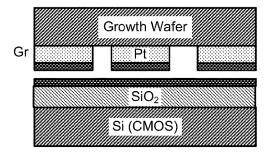

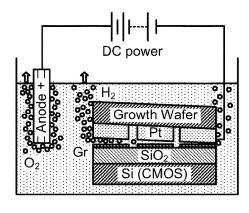

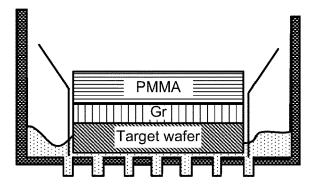

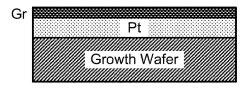

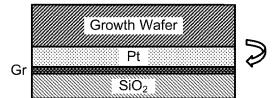

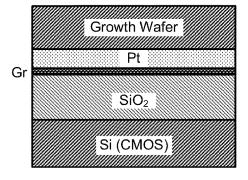

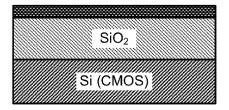

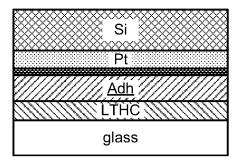

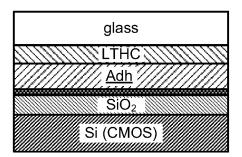

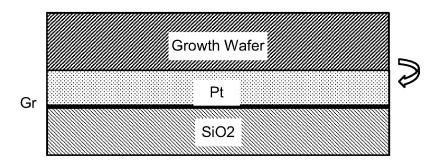

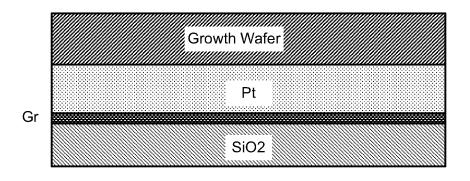

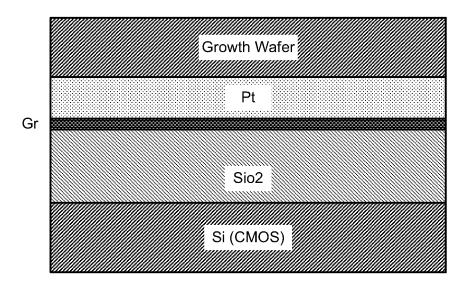

Gr Pt SiO<sub>2</sub> Si (CMOS)

Growth Wafer

FIG. 17C

FIG. 17D

FIG. 17E

FIG. 17F

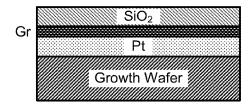

FIG. 18A

FIG. 18B

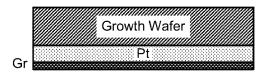

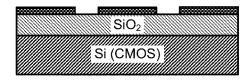

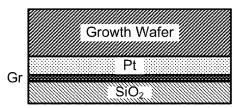

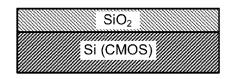

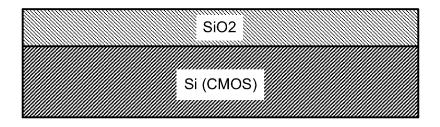

Growth Wafer

Pt

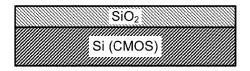

SiO<sub>2</sub>

Si (CMOS)

FIG. 18C

FIG. 18D

FIG. 18E

FIG. 18F

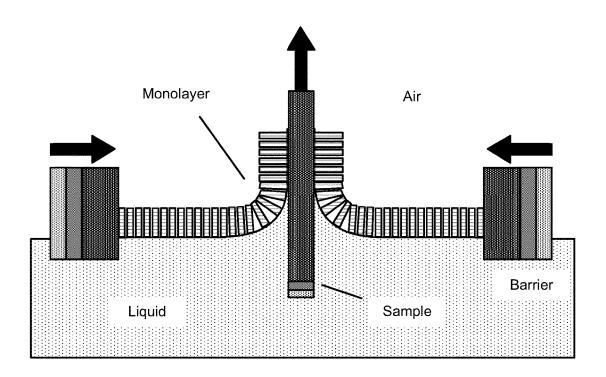

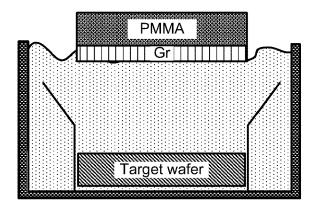

## LANGMUIR-BLODGETT DEPOSITION

FIG. 19A

FIG. 19B

FIG. 19C

FIG. 19D

FIG. 20A

FIG. 20B

FIG. 20C

FIG. 20E

FIG. 20D

FIG. 20F

**FIG. 21A**

FIG. 21B

FIG. 21C

FIG. 21D

**FIG. 21E**

**FIG. 21F**

FIG. 21G

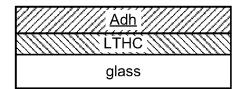

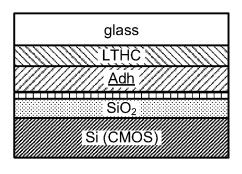

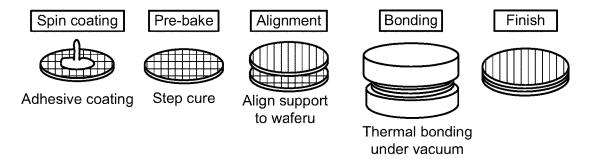

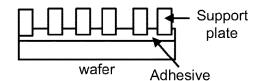

Adhesive spin coating → Bake → Bonding. A very simple process. ➤ Low Bonding pressure (0.12MPa)

## **FIG. 22A**

FIG. 22B

|                                          |                        |                        |                        |                        | -                      |             |                        |                          | ********        |                                |                                         |

|------------------------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|-------------|------------------------|--------------------------|-----------------|--------------------------------|-----------------------------------------|

|                                          |                        |                        |                        | 0091                   | PRESPUEN               | -           | -                      | -                        | -               | -                              | CONTRACTOR OF STREET                    |

|                                          |                        |                        |                        |                        |                        |             |                        |                          |                 |                                |                                         |

|                                          |                        |                        |                        |                        |                        |             |                        |                          |                 |                                |                                         |

|                                          |                        |                        |                        |                        | 1000                   | • • • • • • |                        | $\cdots$                 |                 |                                |                                         |

|                                          |                        |                        |                        |                        |                        |             |                        |                          |                 |                                | • • • • • • • • • • • • • • • • • • • • |

|                                          |                        |                        |                        |                        |                        |             |                        |                          |                 |                                |                                         |

| $\sim\sim$                               | $\sim\sim$             | $\sim\sim$             | $\sim\sim$             | $\sim\sim$             | $\sim$                 | $\sim$      | $\sim\sim$             | $\sim$                   | $\vee \vee$     | $\sim$                         | $\sim$                                  |

| $\times \times \times \times$            | xxxx                   | xxx                    | $\times \times \times$ | $\times \times \times$ | $\mathbf{x}\mathbf{x}$ | XX          | XX)                    | $^{\circ}$               | $\infty$        | XX                             | xx                                      |

| $\times\!\times\!\times\!\times$         | $\times \times \times$ | $\sim$                 | $\sim\sim$             | V                      | ' X X                  | VV.         | XX                     | XX                       | XX.             | $\times\!\!\times\!\!\!\times$ | VXX                                     |

| $\times\!\times\!\times\!\times\!\times$ | $\infty \infty$        | $\infty$               | $\infty$               | െ                      | < ^×                   | $\infty$    | $\propto \propto$      | XX                       | XX              | $\times \times \times$         | $\sim$                                  |

| XXXX                                     | XXXX                   | $\times \times \times$ | $\times \times \times$ | × oi                   | X                      | XX.         | $\times \times \times$ | $\langle \times \rangle$ | (XX             | XX                             | XX.                                     |

| $\sim\sim$                               | $\sim\sim$             | $\sim\sim$             | $\vee\!\!\vee\!\!\vee$ | · - ·                  | ~~                     | $\sqrt{N}$  | $\sqrt{N}$             | $\sim$                   | $\wedge \wedge$ | $\sim\sim$                     | $\sim$                                  |

| xxxxy                                    | $\sim \sim \sim$       | $\sim$                 | $\sim\sim$             | Cx x x                 | : x'x                  | $^{\prime}$ | $^{\prime}$ YY         | ΥY                       | XX.             | x x y                          | $r \times r$                            |

| XXXX                                     | XXXX                   | xxx                    | XXX                    | xxx                    | $\times \times$        | XX.         | $\times \times$        | $^{\circ}$               | $\infty$        | $\times$                       | xx                                      |

|                                          |                        |                        |                        |                        |                        |             |                        |                          |                 |                                |                                         |

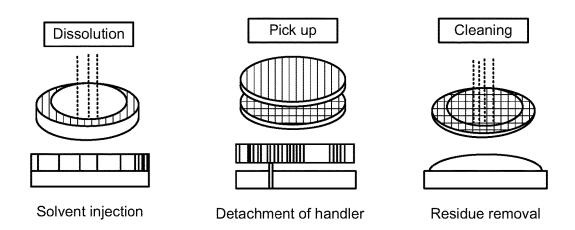

FIG. 23A

|  | Та | ре          |  |  |

|--|----|-------------|--|--|

|  | /  | li <u> </u> |  |  |

|  | P  | 't          |  |  |

|  | S  | Si 🎺        |  |  |

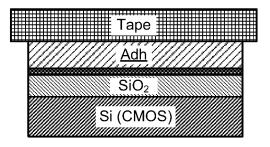

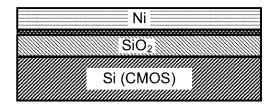

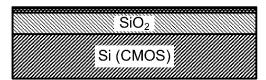

FIG. 23B

| Tape             |   |

|------------------|---|

| Ni =             |   |

| SiO <sub>2</sub> |   |

| Si (CMOS         | ) |

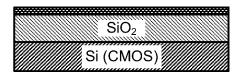

FIG. 23C

FIG. 23D

FIG. 23E

FIG. 24A

FIG. 24B

FIG. 24C

FIG. 24D

FIG. 24E

FIG. 24F

FIG. 25A

FIG. 25B

FIG. 25C

FIG. 25D

FIG. 25E

FIG. 25F

FIG. 26A

FIG. 26B

FIG. 26C

FIG. 26D

FIG. 26E

FIG. 26F

FIG. 26G

FIG. 26H

FIG. 261

FIG. 26J

FIG. 26K

FIG. 26L

FIG. 26M

FIG. 29

FIG. 30

FIG. 33

# GRAPHENE FET DEVICES, SYSTEMS, AND METHODS OF USING THE SAME FOR SEQUENCING NUCLEIC ACIDS

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This Divisional application claims the benefit of priority to U.S. Continuation in part application Ser. No. 15/225,764, filed Aug. 1, 2016, which claims the benefit of priority to U.S. Provisional Application Ser. No. 62/199,956, filed on Jul. 31, 2015 and U.S. Provisional Application Ser. No. 62/199,987, filed on Aug. 1, 2015. This application is a continuation in part of U.S. application Ser. No. 15/065,744, filed on Mar. 9, 2016, which in turn claims benefit of U.S. Provisional Application Ser. No. 62/130,598, filed on Mar. 9, 2015; U.S. Provisional Application Ser. No. 62/130,594, filed on Mar. 9, 2015; U.S. Provisional Application Ser. No. 62/130,601, filed on Mar. 9, 2015; U.S. Provisional Application Ser. No. 62/130,621, filed on Mar. 10, 2015; U.S. application Ser. No. 15/065,744 is a continuation in part of U.S. application Ser. No. 14/963,253, filed on Dec. 9, 2015, which in turn claims benefit of U.S. Provisional Application Ser. No. 62/094,016, filed on Dec. 18, 2014; U.S. Provisional Application Ser. No. 62/130,594, filed on Mar. 9, 2015; U.S. Provisional Application Ser. No. 62/199,987, filed on Aug. 1, 2015; and U.S. Provisional Application Ser. No. 62/206,228, filed on Aug. 17, 2015. This application is a continuation in part of U.S. application Ser. No. 15/182, 533, filed on Jun. 14, 2016, which in turn claims benefit of U.S. Provisional Application Ser. No. 62/175,351, filed on Jun. 14, 2015. This Divisional application claims the benefit of priority to U.S. Continuation in part application Ser. No. 15/225,764, filed Aug. 1, 2016, which claims the benefit of priority to U.S. application Ser. No. 14/963,253, filed on Dec. 9, 2015, which in turn claims benefit of U.S. Provisional Application Ser. No. 62/094,016, filed on Dec. 18, 2014; U.S. Provisional Application Ser. No. 62/130,594, filed on Mar. 9, 2015; U.S. Provisional Application Ser. No. 62/199,987, filed on Aug. 1, 2015; and U.S. Provisional Application Ser. No. 62/206,228, filed on Aug. 17, 2015, the disclosures of which are incorporated herein in their entirety.

### FIELD OF THE DISCLOSURE

[0002] The present disclosure relates, generally, to field effect transistors, such as integrated field-effect devices, systems including the devices, and methods of using the same for the analysis of biological and/or chemical materials, such as for molecular, e.g., nucleic acid, analysis and/or sequencing. More specifically, the present disclosure relates to field effect transistors having a reaction layer that includes one or two-dimensional materials associated therewith.

## BACKGROUND TO THE DISCLOSURE

[0003] The sequencing of Nucleic Acids, such as deoxyribonucleic acid (DNA) or Ribonucleic acid (RNA), is a fundamental part of biological discovery. Such sequencing and/or the detection of the same is useful for a variety of purposes and is often used in scientific research, as well as medical advancement. For instance, the genomics and bioinformatics fields are concerned with the application of information technology and computer science to the field of molecular biology. In particular, bioinformatics techniques can be applied to process and analyze various genomic data,

such as from an individual so as to determine quantitative and qualitative information about that data that can then be used by various practitioners in the development of diagnostic, prophylactic, and/or therapeutic methods for detecting, preventing, or at least ameliorating diseased states, and thus, improving the safety, quality, and effectiveness of health care. The need for such diagnostic, therapeutic, and prophylactic advancements have led to a high demand for low-cost sequencing, which in turn has driven the development of high-throughput sequencing, termed as Next generation sequencing (NGS).

[0004] Generally, the approach to DNA and/or RNA analysis, such as for genetic diagnostics and/or sequencing, involves nucleic acid hybridization and detection. For example, various typical hybridization and detection approaches include the following steps. Particularly, for genetic analysis, a DNA or RNA sample of a subject to be analyzed may be isolated and immobilized on a substrate. In such instances, the immobilized genetic material acts as a template for new nucleic acid synthesis. A probe of a known sequence identity, e.g., a disease marker, may be labeled and washed across the substrate. If the disease marker is present, a binding event will occur, e.g., hybridization, and because the probe has been labeled the hybridization event may either be or not be detected thereby indicating the presence or absence of the disease marker in the subject's sample.

[0005] For DNA sequencing, first, an unknown nucleic acid sequence to be identified, e.g., a single-stranded sequence of DNA of a subject, composed of a combination of unknown nucleotides, e.g., As, Cs, Gs, and Ts, is isolated, amplified, and immobilized on the substrate. Next, a known nucleotide labeled with an identifiable tag is contacted with the unknown nucleic acid sequence in the presence of a polymerase. When hybridization occurs, the labeled nucleotide binds to its complementary base in the unknown sequence immobilized on the surface of the substrate. The binding event can then be detected, e.g., optically or electrically. These steps are then repeated until the entire DNA sample has been completely sequenced, e.g., sequencing by synthesis. Typically, these steps are performed by a Next Gen Sequencer wherein thousands to millions of sequences may concurrently be produced in the next-generation sequencing process.

[0006] For example, a central challenge in DNA sequencing is assembling full-length genomic sequence data, e.g., of chromosomal sequences, from a sample of genetic material obtained from a subject. Particularly, such assembling includes one or more genomic analysis protocols, such as employing a mapping and/or an aligning algorithm, and involves mapping and aligning a fragment of identified sample sequence to a reference genome, yielding sequence data in a format that can be compared to a reference genomic sequence, such as to determine the variants in the sampled full-length genomic sequences. In particular, the methods employed in sequencing protocols do not produce full-length chromosomal sequences of the sample DNA.

[0007] Rather, in a typical sequencing protocol, sequence fragments, typically from 100-1,000 nucleotides in length, are produced without any indication as to where in the genome they map and align. Therefore, in order to generate full-length chromosomal genomic constructs, or determine their variance with respect to a reference genomic sequence, these fragments of DNA sequences need to be mapped, aligned, merged, and/or compared to the reference genomic

sequence. Through such processes the variants of the sample genomic sequences from the reference genomic sequences may be determined.

[0008] However, as the human genome is comprised of approximately 3.1 billion base pairs, and as each sequence fragment is typically only from about 100 to 500 to 1,000 nucleotides in length, the time and effort that goes into building such full length genomic sequences and determining the variants therein is quite extensive, often requiring the use of several different computer resources applying several different algorithms over prolonged periods of time. In a particular instance, thousands to millions of fragments or even billions of DNA sequences are generated, mapped, aligned, and merged in order to construct a genomic sequence that approximates a chromosome in length. A step in this process may include comparing the sequenced DNA fragments to a reference sequence so as to determine where in the genome the fragments align.

[0009] In such instances, the raw genetic material must be processed so as to derive usable genetic sequence data therefrom. This processing may be done manually or via an automated sequencer. Typically, such processing involves obtaining a biological sample from a subject, such as through venipuncture, hair, etc. and treating the sample to isolate the DNA therefrom. Once isolated the DNA may be denatured, strand separated, and/or portions of the DNA may then be multiplied, e.g., via polymerase chain reaction (PCR), so as to build a library of replicated strands that are now ready to be sequenced, e.g., read, such as by an automated sequencer, which sequencer is configured to "read" the replicate strands, e.g., by synthesis, and thereby determine the nucleotide sequences that makes up the DNA. Further, in various instances, such as in building the library of replicated strands, it may be useful to provide for overcoverage when preprocessing a given portion of the DNA. To perform this over-coverage, e.g., using PCR, may require increased sample preparation resources and time, and therefore be more expensive, but it often gives an enhanced probability of the end result being more accurate.

[0010] More particularly, once the library of replicated strands has been generated they may be injected into an automated sequencer that may then "read" the strands, such as by synthesis, so as to determine the nucleotide sequences thereof. For instance, the replicated single stranded DNA may be attached to a glass bead and inserted into a test vessel, e.g., an array. All the necessary components for replicating its complementary strand, including labeled nucleotides, are also added to the vessel but in a sequential fashion. For example, all labeled "A", "C", "G", and "T's" are added, either one at a time or all together to see which of the nucleotides is going to bind at position one. After each addition a light, e.g., a laser, is shone on the array. If the composition fluoresces then an image is produced indicating which nucleotide bound to the subject location. More particularly, where the nucleotides are added one at a time, if a binding event occurs, then its indicative fluorescence will be observed. If a binding event does not occur, the test vessel may be washed and the procedure repeated until the appropriate one of the four nucleotides binds to its complement at the subject location, and its indicative fluorescence is observed. Where all four nucleotides are added at the same time, each may be labeled with a different fluorescent indicator, and the nucleotide that binds to its complement at the subject position may be determined, such as by the color of its fluorescence. This greatly accelerates the synthesis process.

[0011] Once a binding event has occurred, the complex is then washed and the synthesis steps are repeated for position two. For example, a marked nucleotide "A" may be added to the mix to determine if the complement at the position is a "T", and if so, all the sequences having that complement will bind to the labeled "T" and will therefore fluoresce, and the samples will all be washed. Where the binding happened the bound nucleotide is not washed away, and then this will be repeated for all positions until all the over-sampled nucleic acid segments, e.g., reads, have been sequenced and the data collected. Alternatively, where all four nucleotides are added at the same time, each labeled with a different fluorescent indicator, only one nucleotide will bind to its complement at the subject position, and the others will be washed away, such that after the vessel has been washed, a laser may be shone on the vessel and which nucleotide bound to its complement may be determined, such as by the color of its fluorescence. This continues until the entire strand has been replicated in the vessel.

[0012] A typical length of a sequence replicated in this manner is from about 100 to about 500 base pairs, such as between 150 to about 400 base pairs, including from about 200 to about 350 base pairs, such as about 250 base pairs to about 300 base pairs dependent on the sequencing protocol being employed. Further, the length of these segments may be predetermined, e.g., engineered, to accord with any particular sequencing machinery and/or protocol by which it is run. The end result is a readout, or read, that is comprised of a replicated DNA segment, e.g., from about 100 to about 1,000 nucleotides in length, that has been labeled in such a manner that every nucleotide in the sequence, e.g., read, is known because of its label. Hence, since the human genome is comprised of about 3.1 billion base pairs, and various known sequencing protocols usually result in labeled replicated sequences, e.g., reads, from about 100 or 101 bases to about 250 or about 300 or about 400 bases, the total amount of segments that need to be sequenced, and consequently the total number of reads generated, can be anywhere from about 10,000,000 to about 40,000,000, such as about 15,000, 000 to about 30,000,000, dependent on how long the label replicated sequences are. Therefore, the sequencer may typically generate about 30,000,000 reads, such as where the read length is 100 nucleotides in length, so as to cover the genome once.

[0013] However, in part, due to the need for the use of optically detectable, e.g., fluorescent, labels in the sequencing reactions being performed, the required instrumentation for performing such high throughput sequencing is bulky, costly, and not portable. For this reason, a number of new approaches for direct, label-free detection of DNA hybridization reactions have been proposed. For instance, among the new approaches are detection methods that are based on the use of various electronic analytic devices. Such direct electronic detection methods have several advantages over the typical NGS platform. For example, the detector may be incorporated in the substrate itself, such as employing a biosystem-on-a-chip device, such as a complementary metal oxide semiconductor device, "CMOS". More particularly, in using a CMOS device in genetic detection, the output signal representative of a hybridization event can be directly acquired and processed on a microchip. In such an instance,

automatic recognition is theoretically achievable in real time and at a lower cost than is currently achievable using NGS processing. Moreover, standard CMOS devices may be employed for such electronic detection making the process simple, inexpensive, and portable.

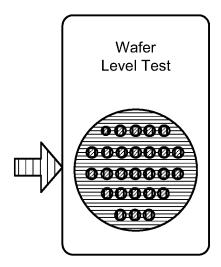

[0014] However, in order for next-generation sequencing to become widely used as a diagnostic in the healthcare industry, sequencing instrumentation will need to be mass produced with a high degree of quality and economy. One way to achieve this is to recast DNA sequencing in a format that fully leverages the manufacturing base created for computer chips, such as complementary metal oxide semiconductor (CMOS) chip fabrication, which is the current pinnacle of large scale, high quality, low-cost manufacturing of high technology. To achieve this, ideally the entire sensory apparatus of the sequencer could be embodied in a standard semiconductor chip, manufactured in the same fab facilities used for logic and memory chips. Recently, such a sequencing chip, and the associated sequencing platform, has been developed and commercialized by Ion Torrent, a division of Thermo-Fisher, Inc. The promise of this idea has not been realized commercially due to the fundamental limits of applying a metal oxide semiconductor field effect transistor, or MOSFET, as a biosensor. When a MOSFET is used in solution as a biosensor, it is referred to as an ISFET. A particular limitation, however, includes a lack of sensor sensitivity and signal to noise characteristics as the semiconductor node scales down to lower geometries of the transistor (gate length).

[0015] More particularly, a field effect transistor, FET, typically includes a source electrode and a drain electrode together forming a gate, and further including a channel region connecting the source and drain electrodes. The FET may also include an insulating barrier separating the gate from the channel. The operation of a conventional FET relies on the control of the channel conductivity, and thus the drain current, by a voltage, VGS, applied between the gate and source. For high-speed applications, and for the purposes of increasing sensor sensitivity, FETs should respond quickly to variations in VGS. However, this requires short gates and fast carriers in the channel.

[0016] Unfortunately, FETs with short gates frequently suffer from degraded electrostatics and other problems (collectively known as short channel effects), such as threshold-voltage roll-off, drain-induced barrier lowering, and impaired drain-current saturation, results in a decrease in sensor sensitivity. However, scaling theory predicts that a FET with a thin barrier and a thin gate-controlled region (measured in the vertical direction) will be robust against short-channel effects down to very short gate lengths (measured in the horizontal direction). Nevertheless, these effects make the use of such technologies difficult to employ in sequencing reactions.

[0017] Accordingly, the possibility of having channels that are very thin in the vertical dimension would allow for high-speed transmission of carriers as well as for increased sensor sensitivity and accuracy. What is needed, therefore, is a FET device that is configured in such a manner as to include a shorter gate than is currently achievable in present FET applications, which will allow such technologies to be fully deployed in sequencing reactions. Hence, a solution that includes such a FET device designed for use in biological applications, such as for nucleic acid sequencing and/or genetic diagnostics would especially be beneficial.

#### SUMMARY OF THE DISCLOSURE

[0018] Provided herein are devices, systems, and methods of employing the same for the performance of genomics and/or bioinformatics analysis. The devices, systems, and methods of the disclosure are directed in part to field effect transistor (FET) sensors, integrated circuits, and arrays employing the same for analyte measurements. The present FET sensors, arrays, and integrated circuits may be fabricated using conventional CMOS processing techniques based on improved FET sensor and array designs that increase measurement sensitivity and accuracy, and at the same time facilitate significantly small sensor sizes and dense gFET sensor based arrays. Particularly, improved fabrication techniques, as well as improved sensor devices, and their use, employing one dimensional (1D) or two dimensional (2D) reaction layers and/or having a threedimensional (3D) structured layer incorporated therein, provide for rapid data acquisition from small sensors to large, including dense arrays of sensors.

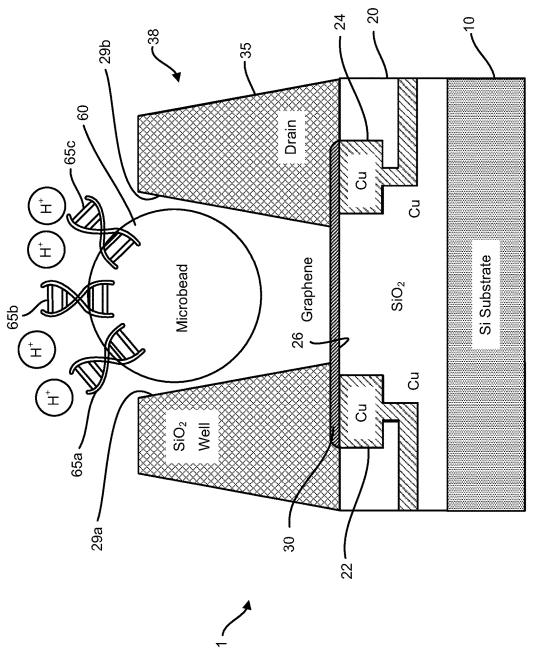

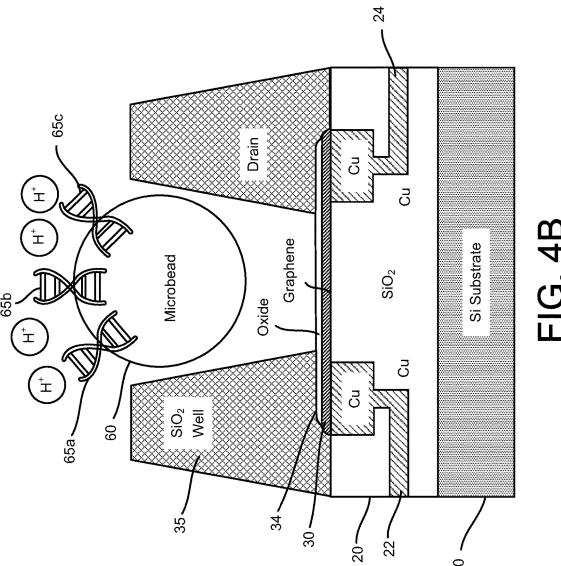

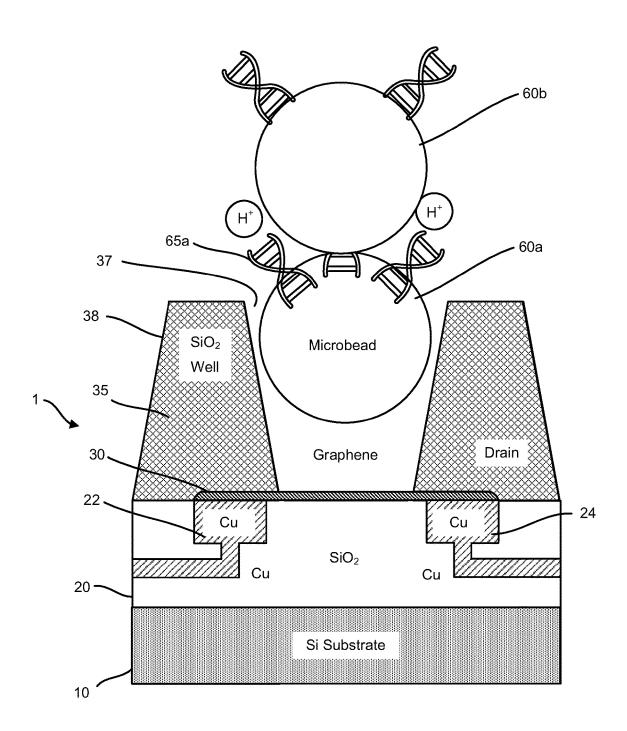

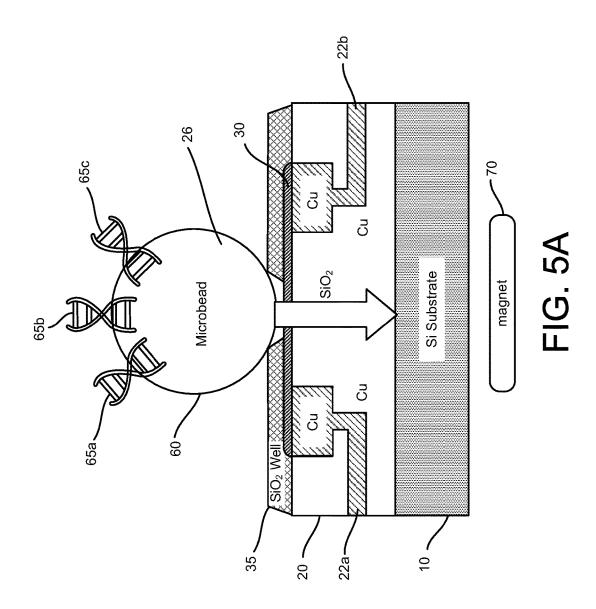

[0019] Such arrays may be fabricated, as described herein, and employed to detect the presence of an analyte, changes in analyte concentration, and/or the identity of various analyte types in a wide variety of chemical and/or biological processes, including DNA hybridization and/or sequencing reactions. More particularly, presented herein are FET based sensor arrays that have been configured to facilitate DNA hybridization and sequencing techniques, as well as the resultant detection of the same, which take place proximate a reaction zone that has been adapted to include a 1D or 2D or 3D surface element. Specifically, in various embodiments, complementary metal oxide semiconductor (CMOS) field effect transistor (FET) devices are provided, where the devices include a plurality of reaction zones that have been adapted to have a 1D or 2D surface characteristic associated therewith so as to decrease sensor length at the same time as increasing sensor sensitivity. Further, in various instances, a 3D structural layer may be included, such as to extend the vertical dimension of the reaction zone. In such instances, the devices may include a number of reaction zones that have been configured to receive a solution containing one or more reactants that when conditions are such to favor a reaction result in a detectable product.

[0020] Accordingly, presented herein are improved biochemical sensor devices that are configured for detecting changes in a gate region and/or solution that result from the occurrence of a binding event between two reactants proximate a reaction zone of the device, such as within the gate region. In particular instances, the detectable changes may be based on monitoring fluctuations in hydrogen ion concentration (pH), variations in analyte concentration, and/or binding events associated with chemical processes relating to DNA synthesis, such as within a gated reaction chamber of a 1D or 2D or 3D based biosensor chip. More specifically, the present disclosure is at least in part directed to a chemically-sensitive field-effect transistor for analysis of biological or chemical materials that solves many of the current problems associated with nucleic acid sequencing and genetic diagnostics. Methods of fabricating such devices as well as their use in the performance of biochemical reactions are also provided.

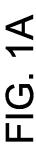

[0021] For instance, in one aspect of the present disclosure, a chemically-sensitive transistor, such as a field effect transistor (FET) that is fabricated on a primary structure, such as a wafer, e.g., a silicon wafer, is provided. In various

instances, the primary structure may include one or more additional structures, for instance, in a stacked configuration, such as including at least an insulator material layer. For example, the primary structure may include a secondary structure, such as composed of an insulator material, which may be included on top of, or otherwise be associated with, the primary structure, and may be an inorganic material, such as a silicon oxide, e.g., a silicon dioxide, or a silicon nitride, or an organic material, such as a polyimide, BCB, or other like material.

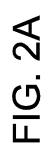

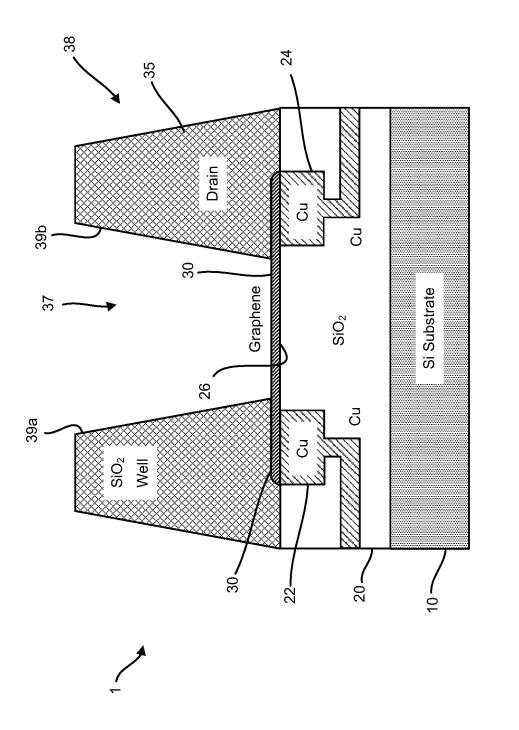

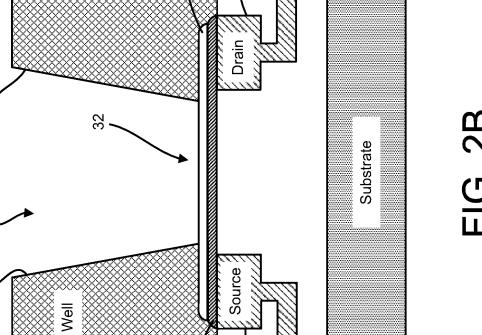

[0022] The secondary structure and/or insulator layer may include a further structure containing one or more of a conductive source and/or a conductive drain, such as separated one from another by a space, and embedded in the primary and/or secondary structure materials and/or may be planar with a top surface of the insulator. In various instances, the structures may further include a processor, such as for processing generated data, such as sensorderived data. Accordingly, the structures may be configured as, or otherwise include, an integrated circuit, and/or may be an ASIC, a structured ASIC, or an FPGA. In particular instances, the structures may be configured as a complementary metal-oxide semiconductor (CMOS), which in turn may be configured as a chemically-sensitive FET containing one or more of a conductive source, a conductive drain, a gate, and/or a processor. For instance, the FET may include a CMOS configuration having an integrated circuit that is fabricated on a silicon wafer, which may further be adapted to include an insulator layer. In such an instance, the insulator layer may include the conductive source and drain such as where the source and drain are composed of metal, such as a damascene copper source and a damascene copper

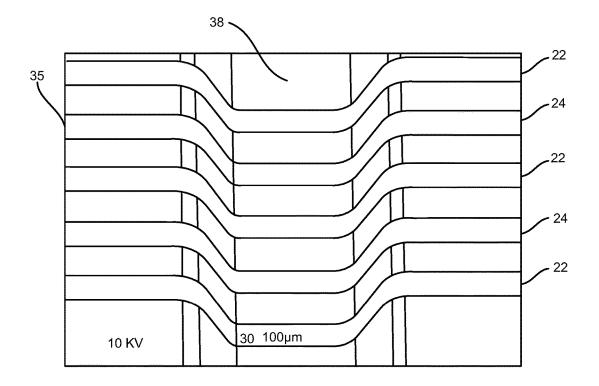

[0023] In various instances, one or more of the structures may include a surface, e.g., a top surface, which surface may include a channel, such as where the surface and/or channel may be configured to extend from the conductive source to the conductive drain. An exemplary length of the surface and/or channel from the source to the drain may range from about 0.001 microns to about 10 microns, such as from about 0.01 microns to about 5 microns, for instance, from about 0.05 micron to 3 microns, including about 0.1 or about 0.5 microns to about 1 or about 1.5 or about 2 microns in the horizontal and/or vertical directions. An exemplary width of the surface and/or channel from side to side may range from about 0.001 microns to about 10 microns, such as from about 0.01 microns to about 5 microns, for instance, from about 0.05 microns to 3 microns, including about 0.1 or 0.5 microns to about 1 or about 1.5 or about 2 microns.

[0024] Particularly, in particular instances, it may be useful to maximize conductance, such as by decreasing the channel length, so as to increase the sensitivity of the sensors, such as in a sensor array. For instance, to achieve enhanced transistor transconductance, the channel may be configured so as to include a short channel length, e.g., as short a length as possible, while at the same time including a larger channel width, e.g., as large as width as possible, within the sensor array, in a manner adapted for keeping the over all dimensions of the array as compact as possible. For example, the equation for transconductance of a field effect transistor, such as for a transistor presented herein, is:  $g_m \propto \mu C_{ov}$ ,  $W/L V_{sd}$ ; where  $g_m$  is the transconductance,  $\mu$  is the carrier mobility,  $C_{ov}$  is the overall capacitance of the oxide or other layers over the transistor, W is the channel

width, L is the channel length, and  $V_{sd}$  is the voltage from the source to the drain. Since  $g_m$  directly relates to the sensitivity of the sensor it may be desirable to increase gm through moderating the terms shown in the equation.

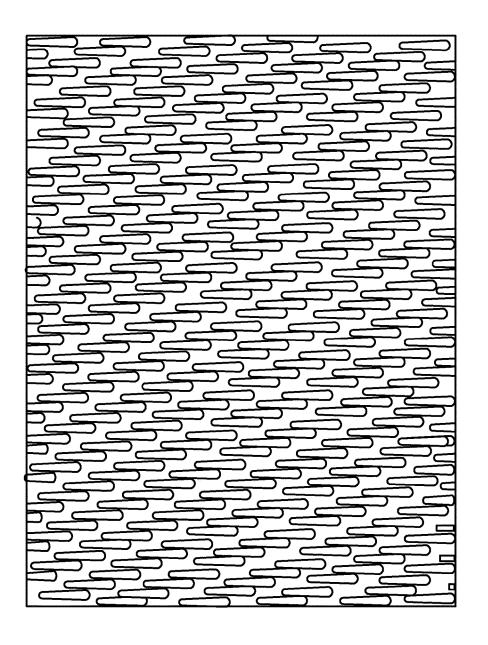

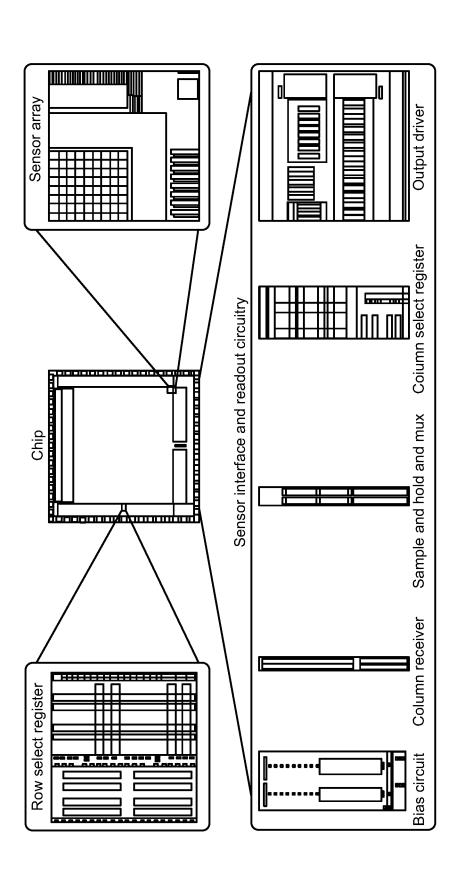

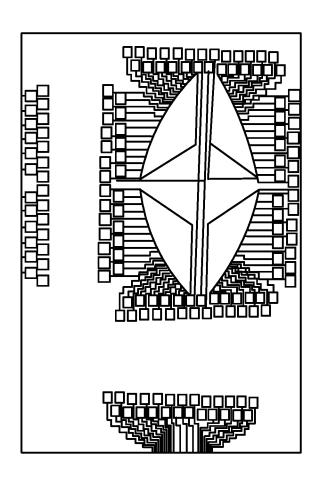

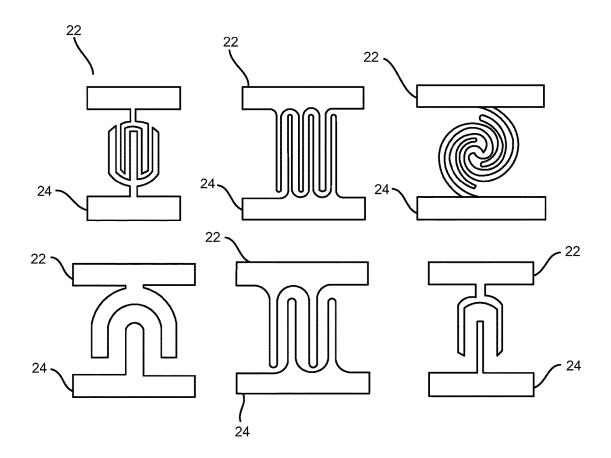

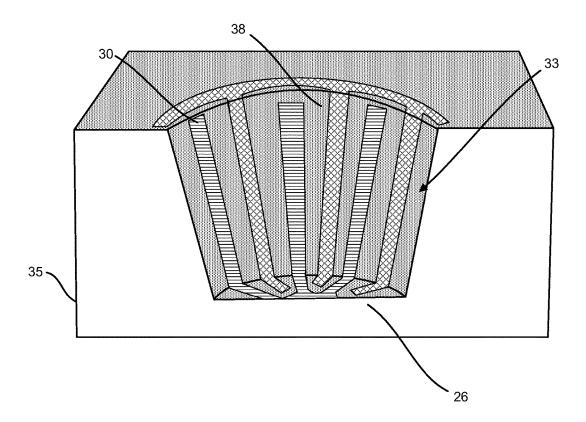

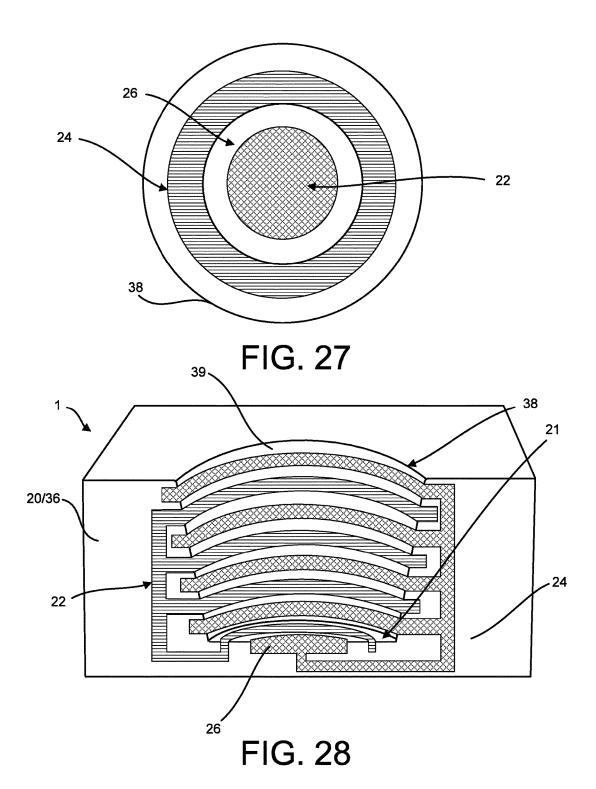

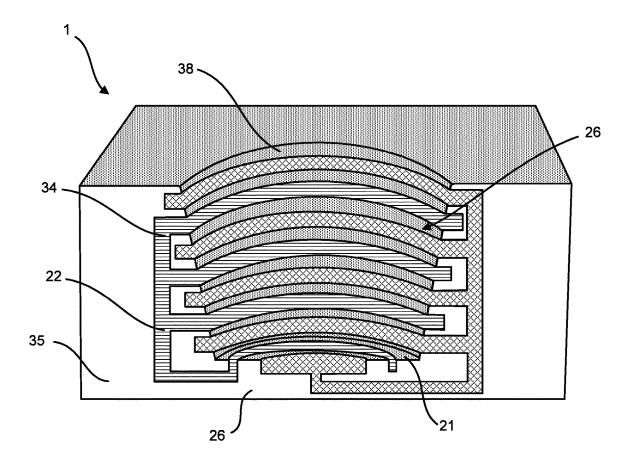

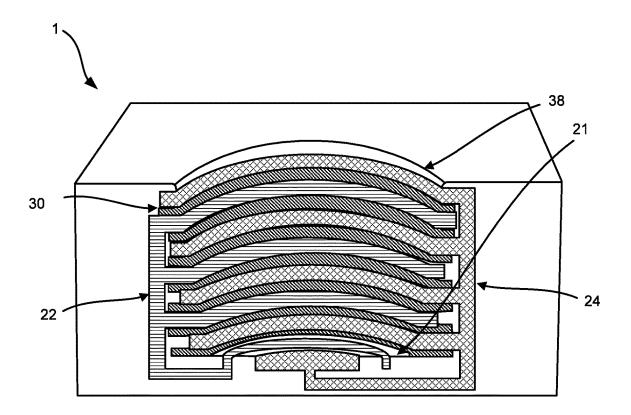

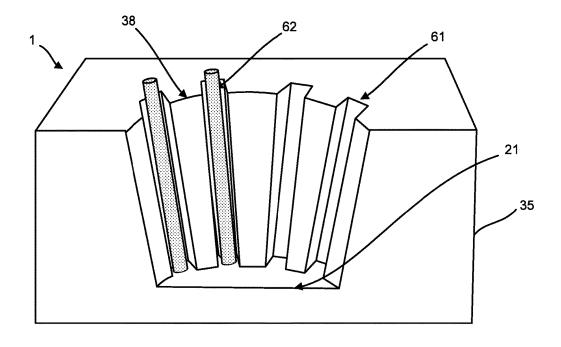

[0025] In particular increasing the W/L ratio (maximizing W and minimizing L) will increase  $g_m$ . In particular instances, a useful length of the channel from the source to the drain ranges is less than 1 micron, such as less than 500 nm, such as less than 50 nm, and may be as short as the fabrication process will allow without generating defects or results that render the device unusable. A particularly useful channel length may be 20 nm or less. Conversely, the width of the channel may be as wide as possible. In such instances, the width of the channel is not governed by the fabrication process as much as by the design requirements of the overall sensor chip. In various instances, many millions of sensors may be positioned on the sensor chip. With this large number of sensors the individual sensor size and pitch (e.g., which may directly affect the channel width) may be kept small, such as reasonably small, so as to prevent the chip from being so large as to be unable to be fabricated (e.g., exceeds the photolithography reticle size) or too expensive (due to the effect of defect density on a large chip size). A practical range of channel width in particular instances may be from 0.1 micron to 2 microns, e.g., for a simple rectangular channel design. In some cases, it may be desirable to increase the channel length to channel width ratio through the use of design techniques—for example, structured and/ or an interdigitated 3D tooth and comb design can provide for short channel lengths and large channel widths within a relatively compact area.

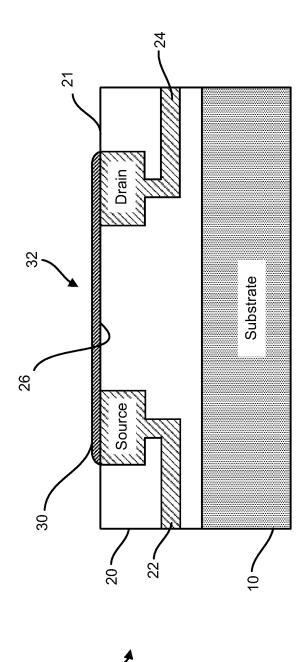

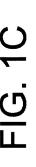

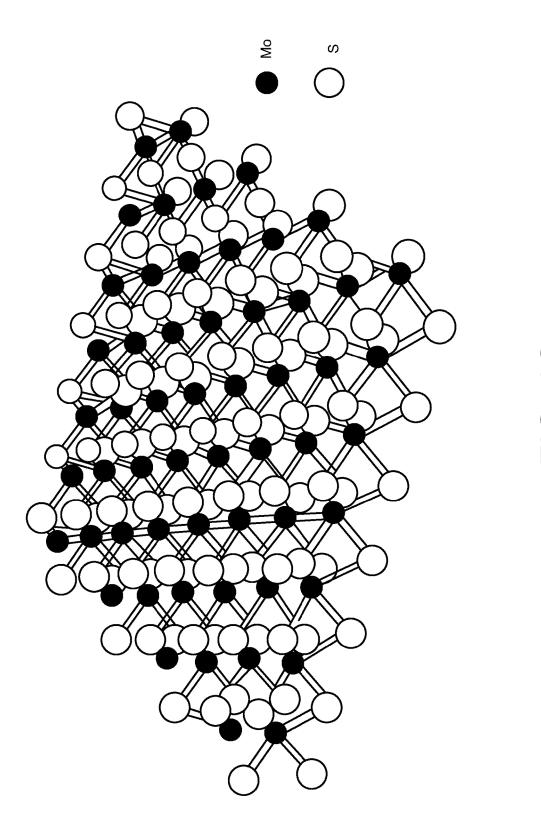

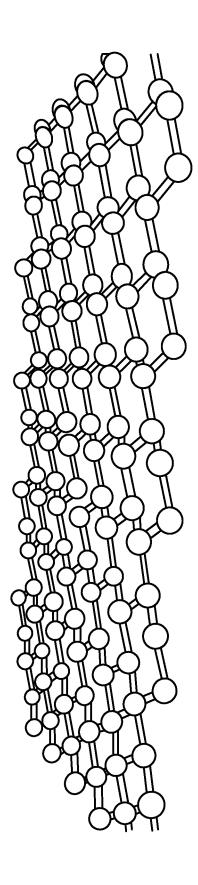

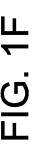

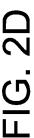

[0026] In certain instances, the surface and/or channel may include a one-dimensional transistor material, a twodimensional transistor material, a three-dimensional transistor material, and/or the like. In various instances, a onedimensional (1D) transistor material may be included, which 1D material may be composed of a carbon nanotube or a semiconductor nanowire. In various instances, a two-dimensional (2D) transistor material may be included, which 2D material may be composed of a graphene layer, silicene, molybdenum disulfide, black phosphorous, and/or metal dichalcogenides. In particular instances, a three-dimensional (3D) structural material, such as proximate a reaction zone and/or channel layer may be provided. In various embodiments, the surface and/or channel may further include a dielectric layer. In particular instances, the surface and/or channel may include a graphene layer.

[0027] Additionally, in various instances, a reaction layer, e.g., an oxide layer, may be disposed on the surface and/or channel, such as layered or otherwise deposited on the 1D, 2D, e.g., graphene, or 3D layer, and/or an included dielectric layer. Such an oxide layer may be an aluminum oxide or a silicon oxide, such as silicon dioxide. In some embodiments, the oxide layer may have a thickness of about 20 nanometers, such as about 15 nanometers, such as 10 or 9 or 7 or 5 nanometers or less. In various instances, a passivation layer may be disposed on the surface and/or channel, such as layered or otherwise deposited on the 1D, 2D, or 3D layer and/or on an associated reaction layer on the surface and/or channel. Such a passivation layer may have a thickness of about 0.5 microns or less, such as about 0.1 microns or about 50 nanometers or about 20 nanometers, such as about 15 nanometers, such as 10 or 9 or 7 or 5 nanometers or less.

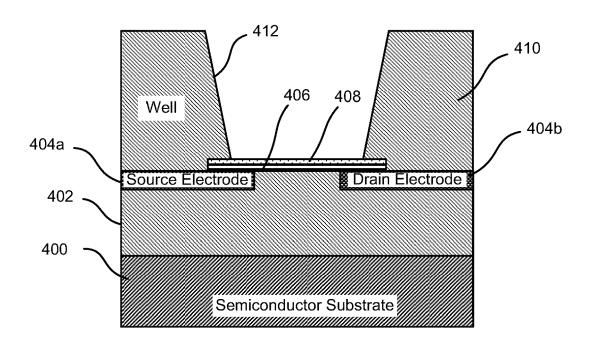

[0028] In particular instances, the primary and/or secondary and/or tertiary structures may be fabricated or otherwise configured so as to include a chamber or well structure in and/or on the surface. For instance, a well structure may be positioned on a portion of a surface, e.g., an exterior surface, of the primary and/or secondary structures. In some instances, the well structure may be formed on top of, or may otherwise include, at least a portion of the 1D, 2D, and/or 3D material, and/or may additionally include the reaction, e.g., oxide, and/or passivation layers. In various instances, the chamber and/or well structure may define an opening, such as an opening that allows access to an interior of the chamber, such as allowing direct contact with the 1D, e.g., carbon nanotube or nanowire, 2D, e.g., graphene, surface and/or channel. In such instances, the FET device may be configured as a solution gated sensor device.

[0029] Accordingly, a further aspect of the present disclosure is a bio-sensor. The bio-sensor includes a CMOS structure that may include a metal containing source, e.g., a damascene copper source, as well as a metal containing drain, e.g., a damascene copper drain, a 1D or 2D layered, e.g., a graphene layered, surface or channel extending from the source to the drain, and a well or chamber structure that may be positioned on a portion of an exterior surface of the 1D or 2D and/or 3D layered well. In particular instances, the well structure may be configured so as to define an opening that allows for direct, fluidic contact with the 1D, e.g., nanotube, nanowire, and/or 2D, e.g., graphene, well or chamber surface. In various instances, the well structure is further configured to include a 3D structural element, such as incorporated into one or more of the well bounding members. Further, an oxide and/or passivation layer may be disposed in or on the chamber surfaces. Hence, in certain instances, a chemically-sensitive transistor, such as a field effect transistor (FET) including one or more nano- or micro-wells may be provided.

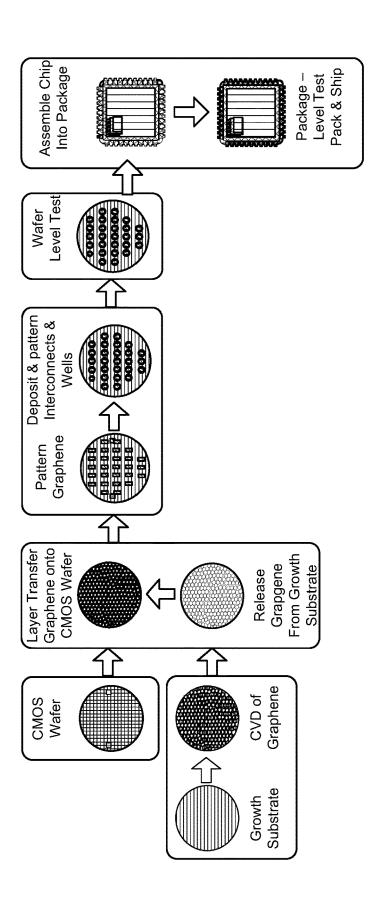

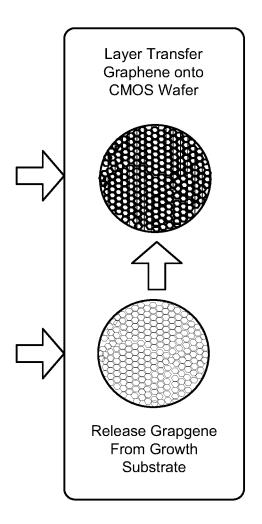

[0030] In view of the above, in one aspect, the present disclosure is directed to a method of fabricating a field effect transistor, such as a transistor having one or more of a 1D, 2D, or 3D material associated therewith, such as in proximity to a reaction zone configured within the FET. Any suitable method may be employed in such a fabrication process, however, in various instances, the method may involve the growing and/or transferring of the one-dimensional (1D0 or two-dimensional (2D) material for use as in the sensor. In such an instance, the method may include the growing of the 1D or 2D material layer, such as on a suitable growth platform, which may be a silicon platform or substrate. Particularly, the method may also include releasing the 1D and/or 2D material layer from the growth platform and/or transferring the material layer to the semiconductor structure or substrate.

[0031] Accordingly, in some embodiments, the chemically-sensitive field effect transistor may include a plurality of wells and may be configured as an array, e.g., a sensor array. Such an array or arrays may be employed such as to detect a presence and/or concentration change of various analyte types in a wide variety of chemical and/or biological processes, including DNA hybridization and/or DNA or RNA sequencing reactions. For instance, the devices herein described and/or systems including the same may be employed in a method for the analysis of biological or chemical materials, such as for whole genome analysis, genome typing analysis, micro-array analysis, panels analy-

sis, exome analysis, micro-biome analysis, and/or clinical analysis, such as cancer analysis, NIPT analysis, and/or UCS analysis. In a particular embodiment, one or more surfaces within the wells of the field effect transistor may be configured as a reaction zone, which reaction zone may include an additional structure, such as a 1D, 2D, e.g., graphene, or 3D layer, and hence, the FET may be a graphene FET (gFET) array.

[0032] Such FET sensors as herein described may be employed to facilitate DNA hybridization and/or sequencing techniques, such as based on monitoring changes in hydrogen ion concentration (pH), changes in other analyte concentrations, and/or binding events associated with chemical processes (e.g., relating to DNA synthesis), such as within a gated reaction chamber or well of the gFET based sensor, such as proximate the reaction zone(s). For example, the chemically-sensitive field effect transistor may be configured as a CMOS biosensor and/or may be adapted to increase the measurement sensitivity and/or accuracy of the sensor and/or associated array(s), such as by including one or more surfaces or wells having a surface layered with a 1D and/or 2D and/or 3D material, a dielectric or reaction layer, a passivation layer, and the like. In particular instances, the increased sensitivity of the sensors may, in part, be due to the presence of the presence of the 1D or 2D material, and/or further enhanced by its relationship to one or more of the reaction and/or passivation layers, which in turn allows for smaller sensor configurations, therefore smaller channels and/or gates, and thus a greater density of sensors and/or

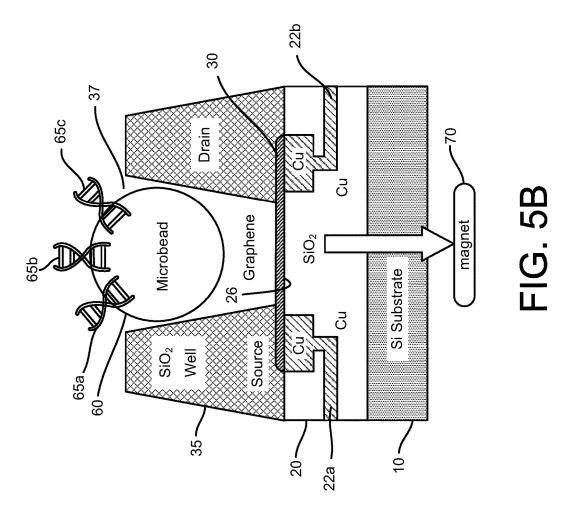

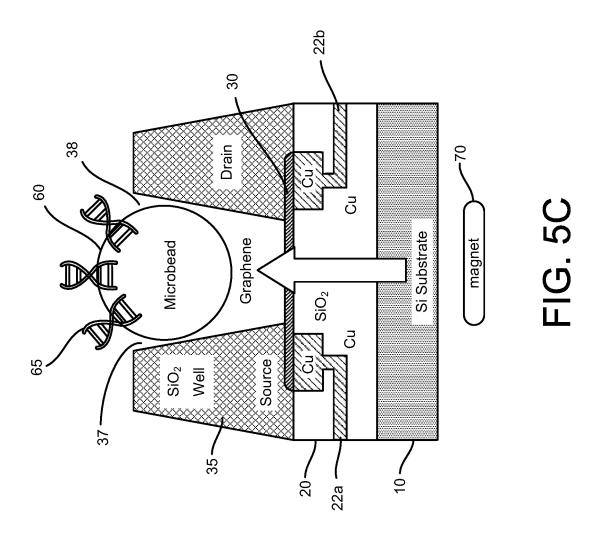

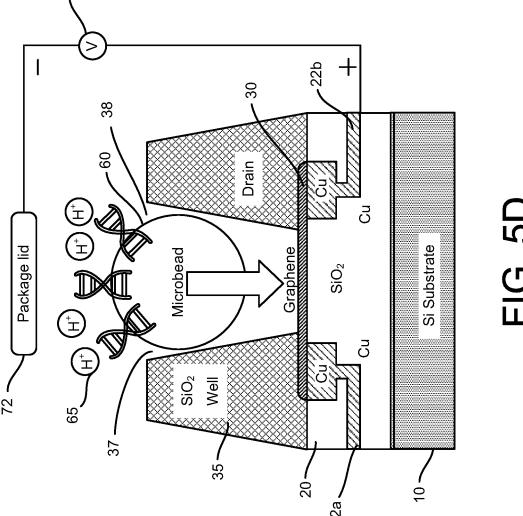

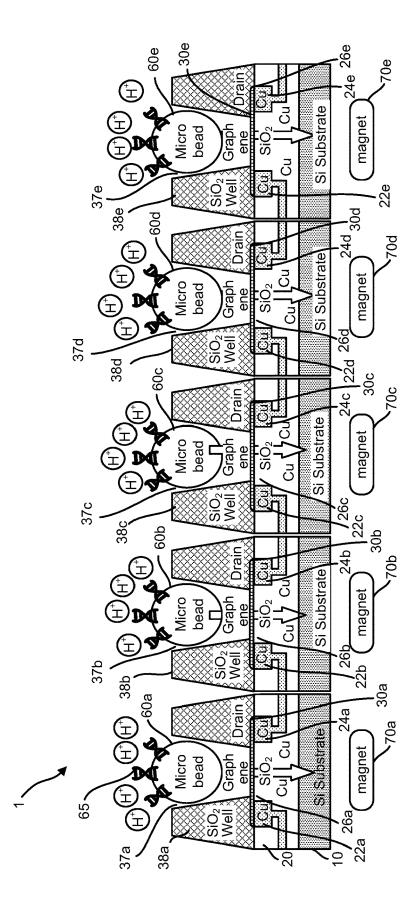

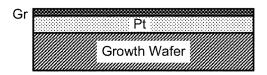

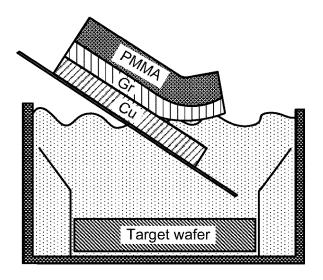

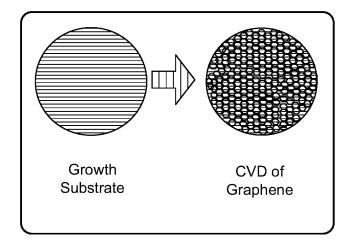

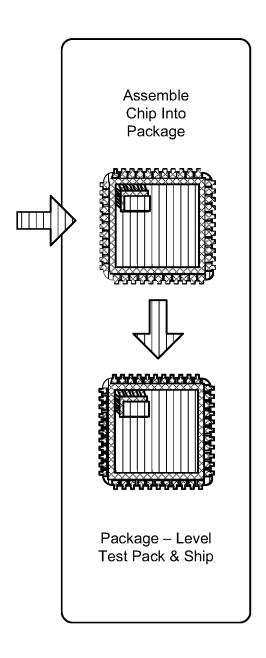

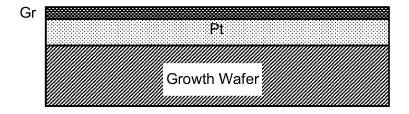

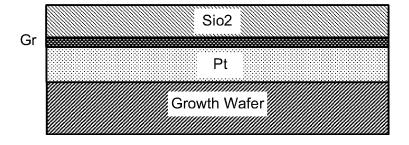

[0033] For instance, in a particular embodiment, a chemically-sensitive graphene containing field effect transistor (gFET), such as a gFET having a CMOS structure is provided, where the gFET sensor, e.g., biosensor, may include a substrate and at least a first insulating layer that may itself be configured so as to incorporate one or more of a 1D, 2D, and/or 3D structure therein. For example, a 1D structure may be layered within or coated on top of the insulation layer, such as via chemical vapor deposition, e.g., PVC/CNT deposition, spin coating, physical vapor deposition, and the like. Additionally, or alternatively, a 2D structure or material layer may be applied to the first insulating layer of the CMOS structure, such as by the growth, or release, and/or transfer of the 2D material thereon. Particularly, in various embodiments, the 2D material may be graphene, Molybdenum disulfide (MoS<sub>2</sub>), Phosphorene (black phosphorous), Silicene, Borophene, Tungsten disulfide (WS<sub>2</sub>), Boron Nitride, WSe<sub>2</sub>, Stanene (2D tin), Graphane, Germanane, Nickel HITP, and Mxenes (Ti2C, (Ti0.5,Nb0.5), V2C, Nb2C, Ti3C2, Ti3CN, Nb4C3, Ta4C3). [0034] More particularly, in certain embodiments, the 2D material may be grown and/or transferred onto the substrate and/or insulating surface of the CMOS structure, which structure may therefore be a read-out integrated circuit (ROIC). For instance, there are several growth mechanisms that may be implemented for the growth of such a 2D material on a growth substrate, such as including the growth on a metal plate, a metal foil, a thin film metal, or a metal, e.g., silicon, wafer, and the like. Likewise, the 2D material may be applied to the material by chemical vapor deposition ("CVD") (atmospheric, low or very low pressure), PECVD, ALD, or grown in a hot wall or cold wall reactor. Once gown, the 2D material may be transferred to the CMOS/ ROIC structured materials, such as by one or more of the following transfer mechanisms including direct transfer from the growth substrate to a ROIC wafer using Van der Waal's forces, fusion bonding, and/or using temporary bonding. Further, there are several release mechanisms that may be implemented for effectuating the release of the 2D material from the growth medium and/or substrate pursuant to the transfer of the 2D material to the ROIC, which release mechanisms may include aqueous electrolyte electrolysis, e.g., with the growth platform as the cathode, and separation due to hydrogen evolution. Another release mechanism may be by separating a temporary adhesive from the growth platform using a laser, a UV light, a temperature increase, or physical peeling or pulling, and the like.

[0035] Additionally, in various embodiments, the CMOS structure may additionally include a further insulating layer, such as positioned on top of the second insulating layer, which first and/or second insulating layer(s) may be positioned one on top of the other, such as with the 1D or 2D material deposited there between. In particular instances, the first and/or second insulating layers may include a well structure, such as a well or chamber having a 3D structural layer, such as within or otherwise associated with a surface of the well or chamber. Further, in various embodiments, the CMOS structure may include an oxide and/or passivation layer, such as a layer that is deposited, e.g., via CVD deposition, or may be otherwise disposed on the surface of the well or chamber so as to increase the measurement sensitivity and/or accuracy of the sensor and/or associated array(s). The oxide layer, when present, may be composed of an aluminum oxide, a silicon oxide, a silicon dioxide, and the like. Particularly, the oxide and/or passivation layers may have a suitable thickness such as of from about 100 nm to about 75 nm, such as from about 50 nm to about 30 nm, from about 40 nm to about 25 nm, such as from about 20 nm to about 10 nm or 9 nm or less, respectively.

[0036] Accordingly, the present FET integrated circuits, sensors, and/or arrays of the disclosure may be fabricated such as using any suitable complementary metal-oxide semiconductor (CMOS) processing techniques known in the art. In certain instances, such a CMOS processing technique may be configured to increase the measurement sensitivity and/or accuracy of the sensor and/or array, and at the same time facilitate significantly small gates having relatively smaller sensor sizes and more dense FET chamber sensor regions. Particularly, in various embodiments, the improved fabrication techniques herein described result in sensor devices containing reaction zones employing a 1D or 2D material layer, and/or may include a 3D structural layer. For instance, a 1D or 2D material layer may be grown, such as on a growth platform, and once grown may be released from the growth platform, and then be transferred to a semiconductor structure, such a CMOS substrate, so as to be employed as a sensor therein.

[0037] Additionally, during or after manufacture one or more surfaces or layers of the CMOS transistor structure may be treated so as to contain one or more additional reaction layers, such as an oxide and/or passivation layers, which structures and layers, alone or in combination provide for rapid data acquisition, such as from small sensors to large and dense arrays of sensors. In certain embodiments, one or more of such layers may be fabricated along with the manufacture of the array, such as via one or more chemical vapor deposition techniques. Further, in particular embodiments, an ion-selective permeable membrane may be

included, such as where the membrane layer may include a polymer, such as a perfluorosulphonic material, a perfluorocarboxylic material, PEEK, PBI, Nafion, and/or PTFE. In some embodiments, the ion-selective permeable membrane may include an inorganic material, such as an oxide or a glass. In more particular embodiments, one or more of the various layers disclosed herein, e.g., the 1D or 2D layer, the reaction, passivation, and/or permeable membrane layers, and the like may be fabricated or otherwise applied by a spin-coating, anodization, PVD, and/or sol gel method.

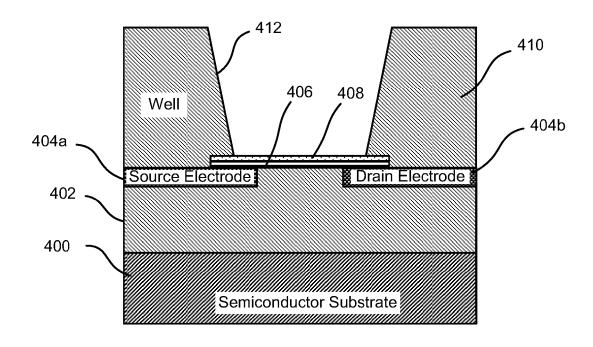

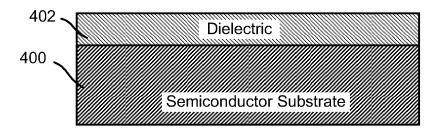

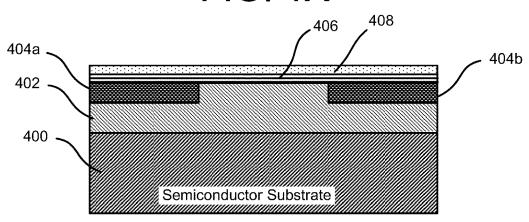

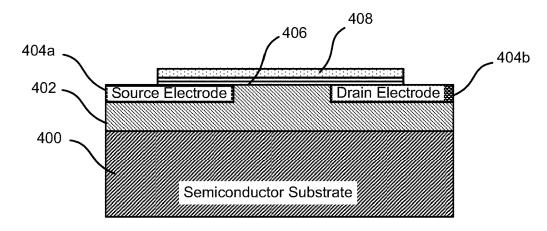

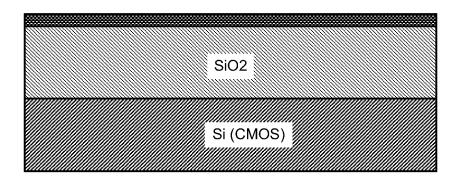

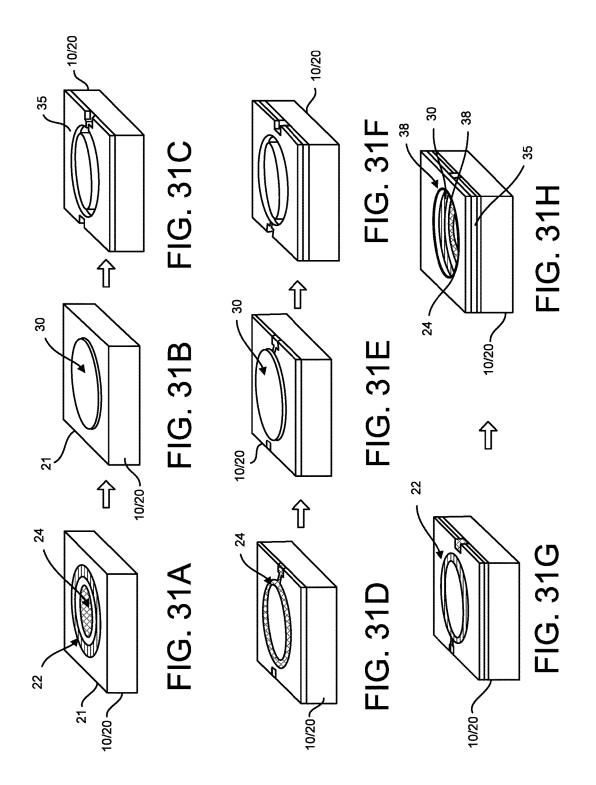

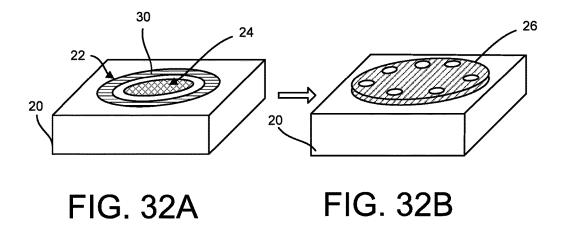

[0038] Accordingly, in a particular fabrication process, a method of forming an integrated circuit, such as for use in performing a reaction, such as a nucleic acid sequencing reaction, is provided. The method includes one or more steps of providing a semi-conducting substrate having a plurality of extended planar surfaces, such as a top and a bottom surface, that are offset from one another by a first thickness, and are surrounded by one or more side members, such as a circumferential side member, if the substrate is circular, elliptical, or round, or a plurality of opposed side members contacting each other at their edges, such as if the substrate is square, and the like. In various instances, the substrate may include one or more transistor elements and/or interconnects that may be positioned within the thickness between the plurality of surfaces.

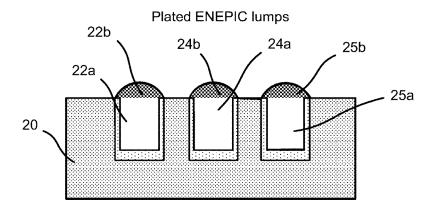

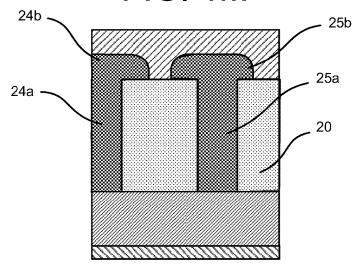

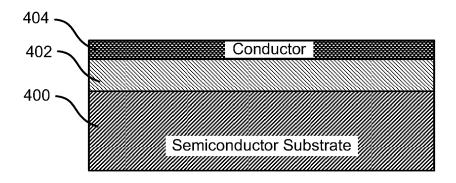

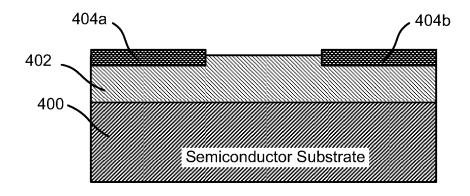

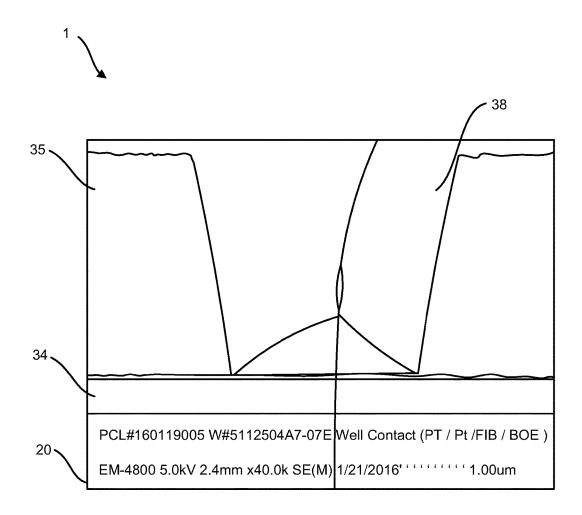

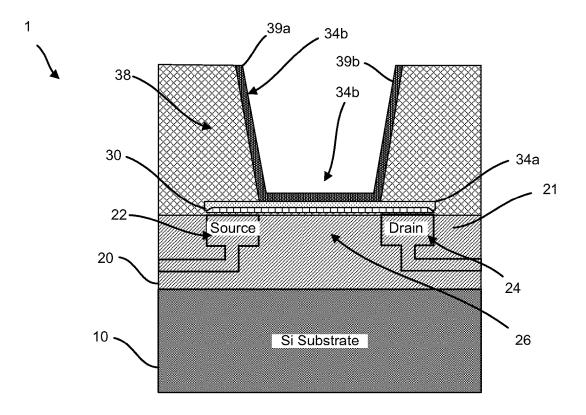

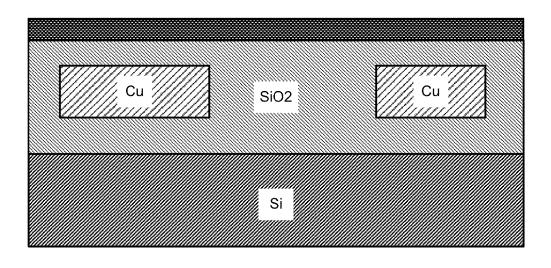

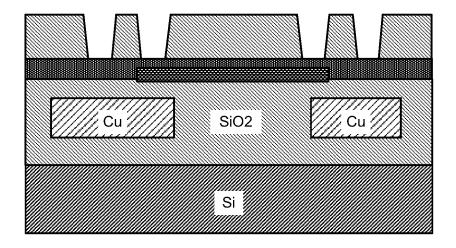

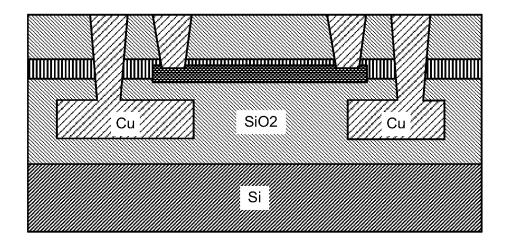

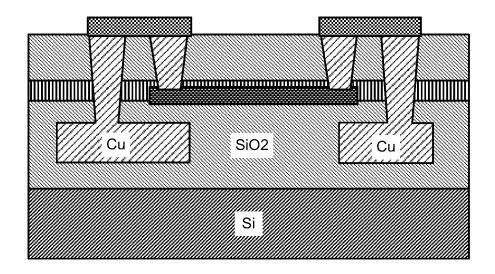

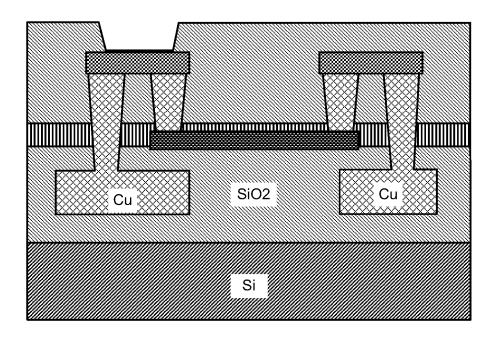

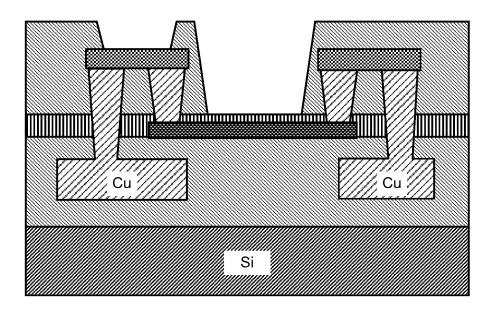

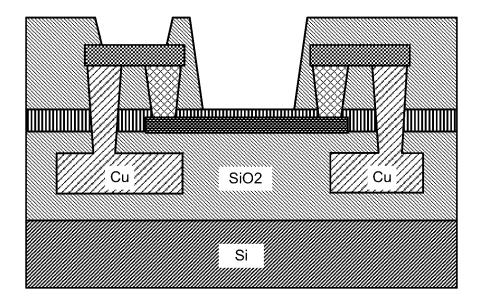

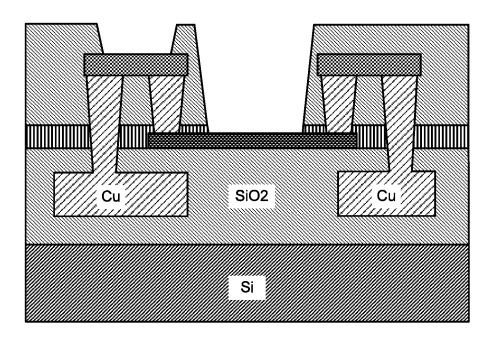

[0039] Additionally, a second step may include depositing a first insulating dielectric layer onto the top of the planar surface of the substrate so that the dielectric layer extends at least partially across the planar surface, such as from one side portion to another side portion, e.g., edge to edge. A plurality of trenches, e.g., opposed trenches, may then be formed in the first insulating dielectric layer, such as where each trench is offset from the other by a distance, which distance may be configured so as to form a channel region. [0040] A third step may include depositing a first layer of conductive material into each of the trenches so as to form an electrode within each trench. For instance, a first electrode in a first trench may be configured so as to serve as a source electrode, and a second electrode in a second trench may be configured to serve as a drain electrode, such as where the source and drain electrodes are offset by the channel region, and may be in contact with the one or more transistor elements.

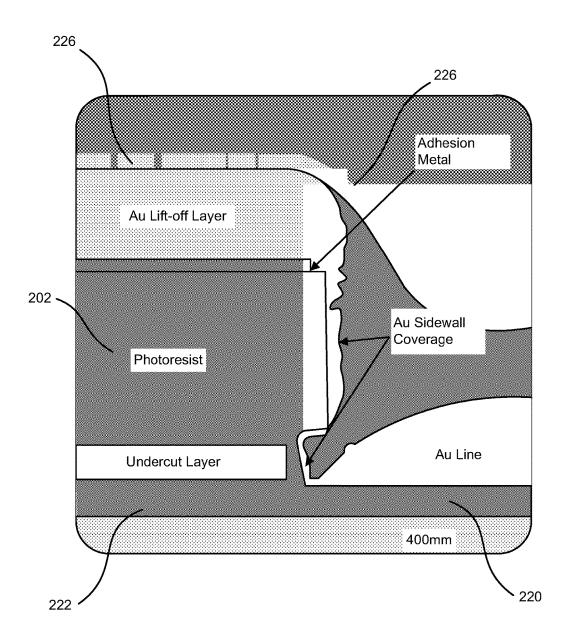

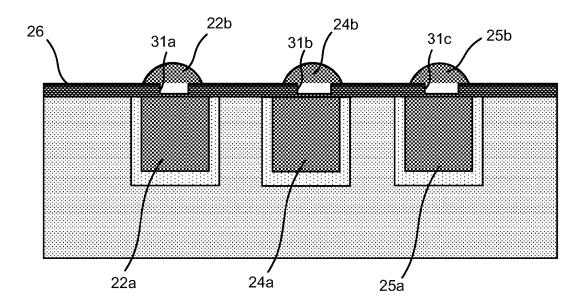

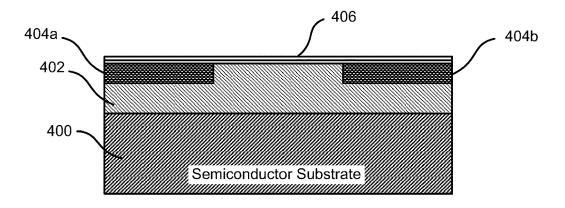

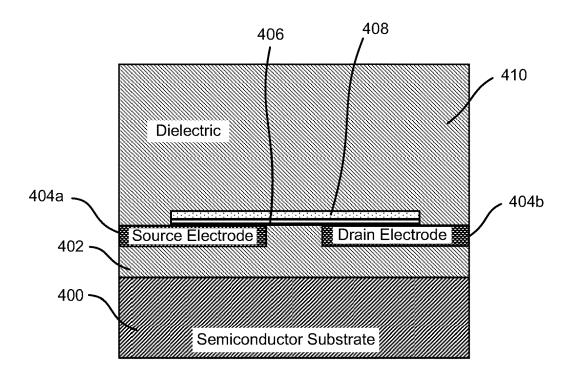

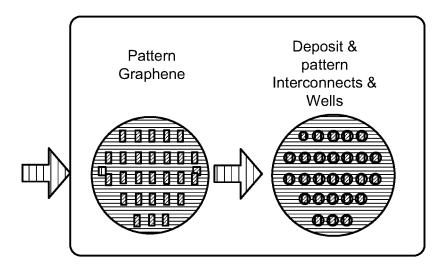

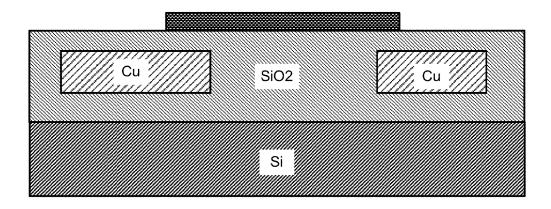

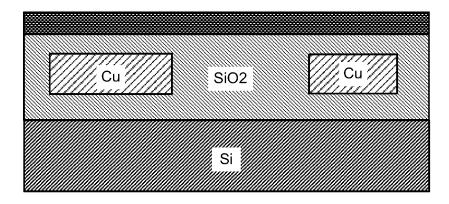

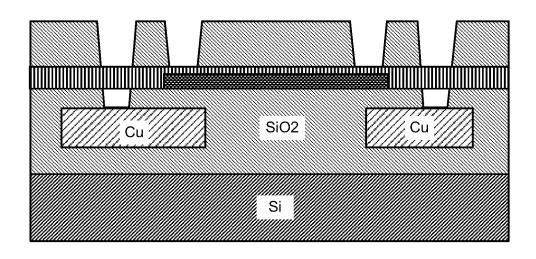

[0041] In certain instances, once the electrodes have been formed a 1D or 2D material layer, e.g., graphene, may be positioned over the insulating layer in a manner to cover the source and drain electrodes as well as the channel region between, thereby forming the channel. However, in some instances, the first insulating dielectric layer may be conditioned prior to depositing the 1D or 2D material layer over it, such as in a manner so that a side and/or top surface of each of the plurality of electrodes is made to extend above the surface of the surrounding insulating dielectric layer, and in some instances, only after this conditioning is the 1D or 2D, e.g., graphene, layer deposited or otherwise formed over the insulating layer, such as onto the side and top surface of each of the plurality of electrodes and across the channel region to thereby form a channel between the electrodes.

[0042] In various embodiments, the conditioning may be accomplished by etching, such as wet or dry etching. Likewise, an additional plating and/or polishing, e.g., electroless chemical polishing, and/or other conditioning steps may be included, such as by being inserted between one or more of the other recited. For example, in some embodiments, after

the first conductive material is added and/or the 1D or 2D material layer is to be added, one or more openings may be made in the 1D or 2D material so as to allow the conductive electrode material to push through and rise above the surface of the 1D or 2D material layer. Such a step as this may be performed in addition to or substitution for the conditioning step. In such an instance, a second layer of conductive material may then be deposited on at least a portion of the 2D material so as to contact each of the plurality of electrodes so that combined conductive material of each of the plurality of electrodes extends further above the surface of the insulating dielectric layer.

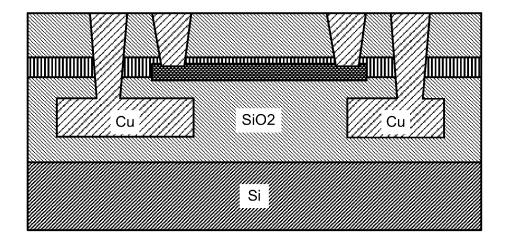

[0043] Nevertheless, where conditioning takes place, an opening of the 1D or 2D material layer may take place so as to form an opening in the 2D material layer, such as proximate each electrode, so as to expose at least the top surface of each electrode. In such an instance, a second layer of conductive material may be deposited over each opening of the 2D material layer so that the second layer of conductive material contacts the first conductive material, fills the opening, and further extends above the 2D material layer so as to contact at least one of a side and top surface of the 2D material layer. In any of these instances, a patterning step may take place, such as employing a mask and photoresist process, so as to pattern the 1D or 2D material layer forming the channel.

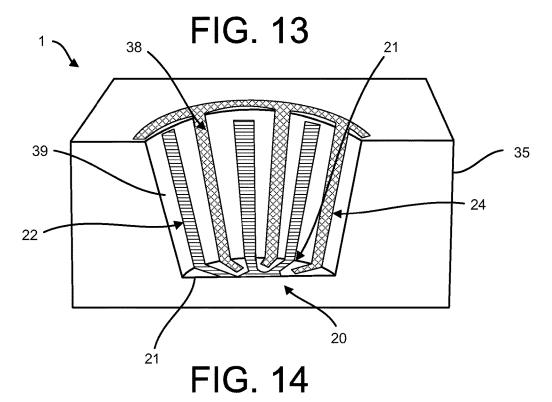

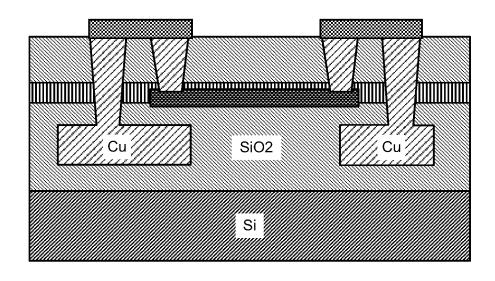

[0044] Additionally, in various embodiments, a second insulating material layer may be deposited over the patterned 2D material layer, which second insulating layer may itself be patterned so as to form a chamber having a bottom surface proximate the channel region. In particular instances, this chamber may be configured as a well so as to form a reaction chamber wherein a nucleic acid sequencing reaction, or other reaction, may take place.

[0045] Consequently, in various instances, the result of these methods is the production of an integrated circuit, which as indicated above, may be used in performing a nucleic acid sequencing reaction. In such an instance, the integrated circuit may include one or more of a semiconducting substrate that includes a plurality of extended planar surfaces offset from one another by a first thickness, which are surrounded by one or more circumferential or edged side members, such as where the substrate may be configures as a CMOS-FET, and therefore may have one or more transistor elements positioned between the plurality of surfaces. Hence, in particular embodiments, the substrate may include an array of field effect transistors that may be arranged in or on the substrate.

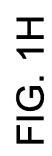

[0046] Accordingly, the substrate may form or otherwise include a primary layer that forms a base layer for the integrated circuit. Additionally included may be a secondary layer that is positioned over the primary layer. Such a secondary layer may be formed of a first non-conductive material, so as to be an insulator and may include a plurality of trenches, such as where each trench is offset by a distance one from the other, where that distance forms a channel region. The trench may be configured so as to include an electrically conductive material so as to form an electrode, and the trench may further be configured in such a manner that a side and top surface of the electrode extends above the top surface of the of the insulating layer. Further, each of the electrodes may be orientated with respect to one another so as to form a channel region there between, and thus, each

electrode on either side of the channel region may be either a source electrode or a drain electrode.

[0047] Further, a tertiary layer may be included and positioned over the secondary layer, such as where the tertiary layer includes a 1D and/or 2D material, which may be formed over one or more of the side and top of the source and drain electrodes. In such an instance, the 2D material may be formed over the channel region so as to electrically connect the source and the drain electrodes and thereby form the channel. In some embodiments, the structure of the integrated circuit may include a fourth layer, which fourth layer may extend across the surfaces of the second and/or third layers, and may further include a surface structure that overlaps the source and the drain in the secondary layer. For example, the surface structure may rise above the second and third layers but may include a chamber that defines a well having sidewalls and a bottom, such as a bottom that corresponds with the channel region and/or extends over at least a portion of the 2D material so as to form a reaction chamber for the performance of a sequencing reaction.

[0048] Accordingly, in a further aspect, a system is provided, such as a system configured for running one or more reactions so as to detect a presence and/or concentration change of various analyte types in a wide variety of chemical and/or biological processes, including DNA hybridization and/or sequencing reactions. As such, the system may include an array including one or more, e.g., a plurality of sensors, such as where each of the sensors includes a chemically-sensitive field-effect transistor having a conductive source, a conductive drain, and a reaction surface or channel extending from the conductive source to the conductive drain. In particular instances, the array may include one or more wells configured as one or more reaction chambers having the reaction surface or channel positioned therein. In some instances, the surface and/or channel of the chamber may include a one-dimensional (1D) or two-dimensional (2D) transistor material, a three-dimensional (3D) structural layer may be included, as well as a dielectric or reaction layer, a passivation layer, and/or the like.

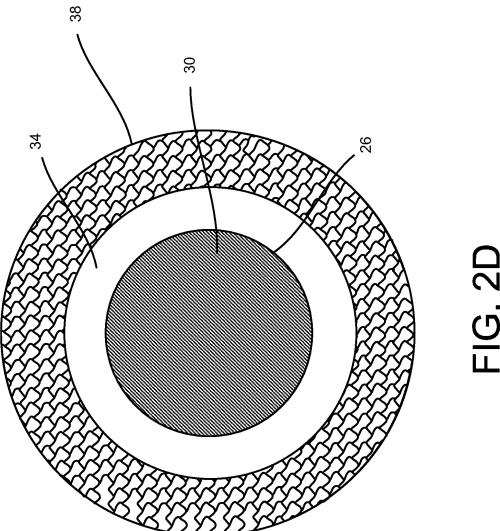

[0049] The system may further include one or more of a fluidic component, such as for performing the reaction, a circuitry component, such as for running the reaction processes, and/or a computing component, such as for controlling and/or processing the same. For instance, a fluidics component may be included where the fluidic component is configured to control one or more flows of reagents over the array and/or one or more chambers thereof. Particularly, in various embodiments, the system includes a plurality of reaction locations, such as surfaces or wells, which in turn includes a plurality of sensors and/or a plurality of channels, and further includes one or more fluid sources containing a fluid having a plurality of reagents and/or analytes for delivery to the one or more surfaces and/or wells for the performance of one or more reactions therein. In certain instances, a mechanism for generating one or more electric and/or magnetic fields is also included.

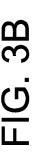

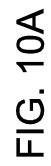

[0050] The system may additionally include a circuitry component, such as where the circuitry component may include a sample and hold circuit, an address decoder, a bias circuitry, and/or at least one analog-to-digital converter. For instance, the sample and hold circuit may be configured to hold an analog value of a voltage to be applied to or on a selected column and/or row line of an array of a device of the disclosure, such as during a read interval. Additionally,

the address decoder may be configured to create column and/or row select signals for a column and/or row of the array, so as to access a sensor with a given address within the array. The bias circuitry may be coupled to one or more surfaces and/or chambers of the array and include a biasing component such as may be adapted to apply a read and/or bias voltage to selected chemically-sensitive field-effect transistors of the array, e.g., to a gate terminal of the transistor. The analog to digital converter may be configured to convert an analog value to a digital value

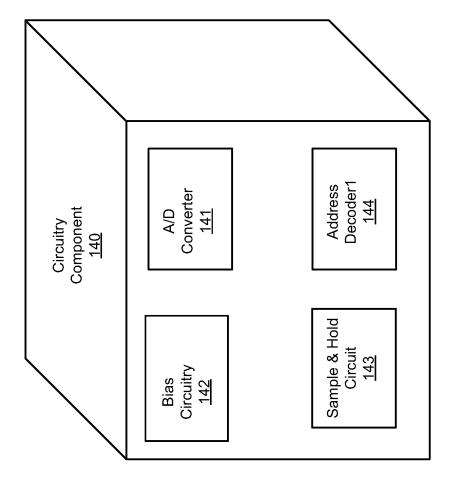

[0051] A computing component may also be included, such as where the computing component may include one or more processors, such as a signal processor; a base calling module, configured for determining one or more bases of one or more reads of a sequenced nucleic acid; a mapping module, configured for generating one or more seeds from the one or more reads of sequenced data and for performing a mapping function on the one or more seeds and/or reads; an alignment module, configured for performing an alignment function on the one or more mapped reads; a sorting module, configured for performing a sorting function on the one or more mapped and/or aligned reads; and/or a variant calling module, configured for performing a variant call function on the one or more mapped, aligned, and/or sorted reads. In particular instances, the base caller of the base calling module may be configured to correct a plurality of signals, such as for phase and signal loss, to normalize to a key, and/or to a generate a plurality of corrected base calls for each flow in each sensor to produce a plurality of sequencing reads. In various instances, the device and/or system may include at least one reference electrode.

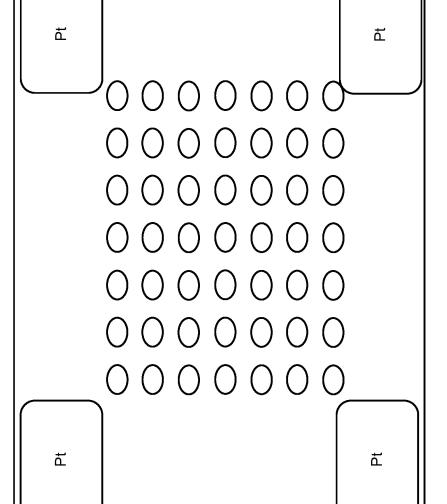

[0052] Particularly, the system may be configured for performing a sequencing reaction. In such an instance, the FET sequencing device may include an array of sensors having one or more chemically-sensitive field-effect transistors associated therewith. Such transistors may include a cascade transistor having one or more of a source terminal, a drain terminal, and or a gate terminal, such as composed of a damascene copper. In such an instance, the source terminal of the transistor may be directly or indirectly connected to the drain terminal of the chemically-sensitive field-effect transistor. In some instances, a one or two dimensional channel or other suitably configured surface element may be included and may extend from the source terminal to the drain terminal, such as where the 1D channel material may be a carbon nanotube or nanowire, and the two-dimensional channel material may be composed of graphene, silicene, a phosphorene, a molybdenum disulfide, and a metal dichalcogenide. The device may further be configured to include a plurality of column and row lines coupled to the sensors in the array of sensors. In such an instance, each column line in the plurality of column lines may be directly or indirectly connected to or otherwise coupled to the drain terminals of the transistors, e.g., cascade transistors, of a corresponding plurality of sensors and/or pixels in the array, and likewise each row line in the plurality of row lines may be directly or indirectly connected to or otherwise coupled with the source terminals of the transistors, e.g., cascade transistors, of a corresponding plurality of sensors in the array.

[0053] In some instances, a plurality of source and drain terminals having a plurality of reaction surfaces, e.g., channel members, extended there between may be included, such as where each channel member includes a one or two or even

three dimensional material. In such an instance, a plurality of first and/or second conductive lines, and so forth, may be coupled to the first and second source/drain terminals of the chemically-sensitive field-effect transistors in respective columns and rows in the array, and so forth. Additionally, control circuitry may be provided and coupled to the plurality of column and row lines such as for reading a selected sensor connected to a selected column line and/or a selected row line. The circuitry may also include a biasing component having a bias circuitry such as is configured to apply a read voltage, while the sample and hold circuit may be configured to hold an analog value of a voltage on a selected column line of the array during a read interval. Particularly, the bias circuitry may be configured for applying a read voltage to the selected row line, and/or to apply a bias voltage such as to the gate terminal of a transistor, such as FET and/or cascade transistor of the selected sensor. In a particular embodiment, the bias circuitry may be coupled to one or more chambers of the array and be configured to apply a read bias to selected chemically-sensitive field-effect transistors via the conductive column and/or row lines. Particularly, the bias circuitry may be configured to apply a read voltage to the selected row line, and/or to apply a bias voltage to the gate terminal of the transistor, e.g., cascade transistor, such as during a read interval.

[0054] A sense circuitry may also be included and coupled to the array so as to sense a charge coupled to one or more of the gate configurations of a selected chemically-sensitive field-effect transistor. The sense circuitry may be configured to read the selected sensor based on a sampled voltage level on the selected row and/or column line. In such an instance, the sense circuitry may include one or more of a pre-charge circuit, such as to pre-charge the selected column line to a pre-charge voltage level prior to the read interval; and a sample circuit such as to sample a voltage level at the drain terminal of the selected transistor, such as during the read interval. A sample circuit may further be included and contain a sample and hold circuit configured to hold an analog value of a voltage on the selected column line during the read interval, and may further include an analog to digital converter to convert the analog value to a digital value.

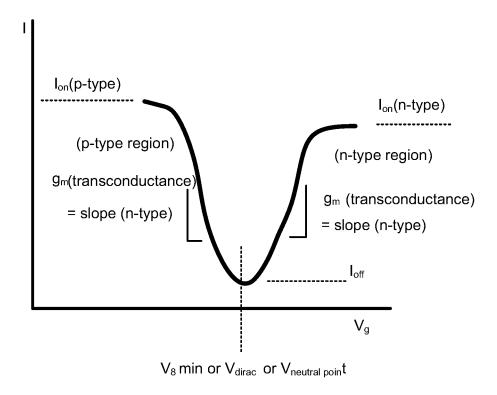

[0055] In particular embodiments, the computer component of the FET, e.g., CMOS, structure may include a processor configured for controlling the performance of one or more reactions involving a biological or chemical material so as to obtain reaction results, and for analyzing those results, for instance, based on detecting and/or measuring changes in a voltage (V) potential, current (I), or capacitance occurring on the chemically-sensitive field effect transistor. Particularly, the processor, such as a signal processor, may be configured so as to generate one or more current (I) vs. voltage (V) curves, such as where the current I of the I-V curve is the current applied between the source and drain of the chemically sensitive field effect transistor and/or where the gate voltage (Vg) of the I-Vg curve is a gate or channel voltage applied to the chemically-sensitive field effect transistor. In such an instance, the gate voltage Vg of the I-Vg curve is a top and/or a back gate voltage that may be applied to the chemically sensitive field effect transistor through a top (or front) and/or back of the device, respectively. Hence, a suitably configured device of the disclosure may be adapted as a front and/or back-gated device, which may further be configured as a solution gate. Accordingly, in various embodiments, a device of the disclosure may be a field-effect transistor that includes a chamber adapted for measuring ion concentrations in a solution; such as where, when the ion concentration (such as H<sup>+</sup> or OH<sup>-</sup> in a pH scale) within the chamber changes, the current through the transistor, e.g., a gate region thereof, will change accordingly. In such an instance, the solution, when added to the chamber forms, or otherwise serves as, a gate electrode.

[0056] Hence, in specific embodiments, the gate voltage Vg of the I-Vg curve may be a solution gate voltage such as applied to the chemically sensitive field effect transistor through a solution flowed over a portion, e.g., a chamber, of the device. In some embodiments, the reference I-Vg curve and/or a chemical reaction I-Vg curve may be generated in response to the biological material and/or chemical reaction that is to be detected and/or occurs over or near the chemically-sensitive field effect transistor, such as within a chamber or well of the FET structure. In various embodiments, the processor may be configured to determine differences in relationships between a generated reference I-Vg curve and/or chemical reaction I-Vg curve. In certain instances, the circuitry component may include at least one analog-todigital converter that is configured for converting analog signals, such as obtained as a result of the performance of the reaction(s) within the reaction well, or array of wells, into digital signals.

[0057] Accordingly, in another aspect, a chemically-sensitive field effect transistor device may be provided, wherein the device may include a structure having a conductive source and drain as well as having a surface or channel or other functionally equivalent surface structure extending from the conductive source to the conductive drain, such as where the surface or channel may include a one-, two-, or three-dimensional transistor material. The device may also include a processor such as where the processor is configured for generating a reference I-Vg curve and/or generating a chemical reaction I-Vg curve, in response to the chemical reaction occurring within a chamber of the chemically-sensitive field effect transistor, and may be configured to determine a difference between the reference I-Vg curve and the chemical reaction I-Vg curve.

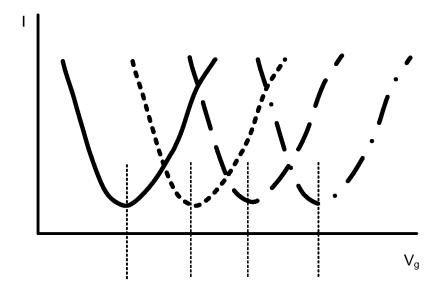

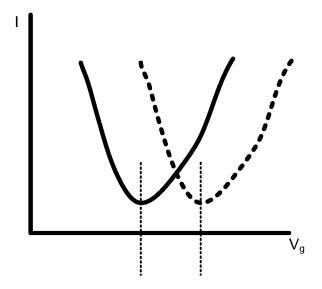

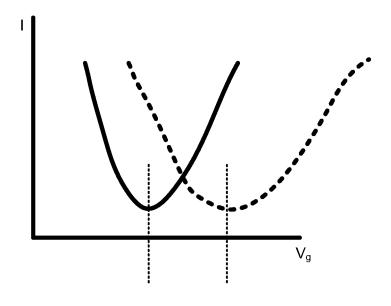

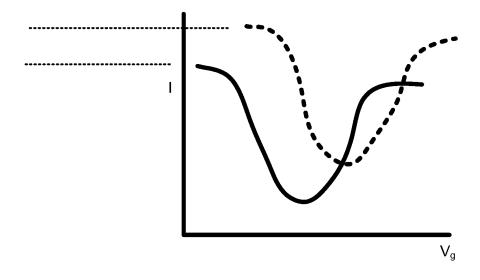

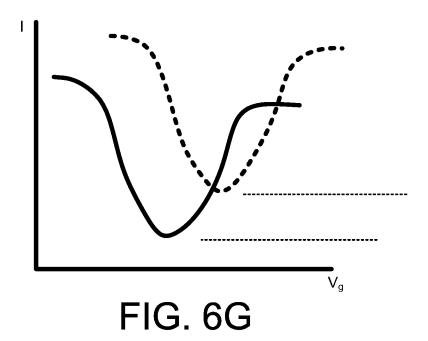

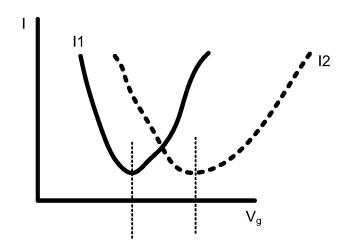

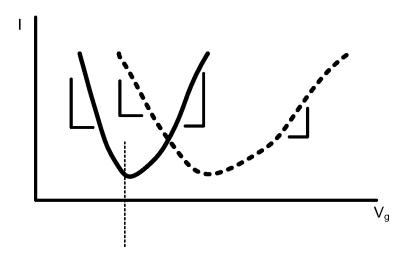

[0058] In some instances, the difference between the reference I-Vg curve measurement and the chemical reaction I-Vg curve measurement is a shift in a minimum point of the Vg value of the chemical reaction I-Vg curve relative to a minimum point of the Vg value of the reference I-Vg curve. In other instances, the difference between the reference I-Vg curve and the chemical reaction I-Vg curve is a shift in an ion value of the chemical reaction I-Vg curve relative to an ion value of the reference I-Vg curve, for instance, where the ion values are taken from a p-type or n-type section of the I-Vg curve. For example, the measurements of the slopes may be taken from the steepest and/or flattest sections on the p-type and/or n-type portions of the I-Vg curves. In particular instances, the difference between the reference I-Vg curve and the chemical reaction I-Vg curve is a shift in an Ioff value of the chemical reaction I-Vg curve relative to an Ioff value of the reference I-Vg curve. In one embodiment, the difference between the reference I-Vg curve and the chemical reaction I-Vg curve is a change in the slope of the chemical reaction I-Vg curve relative to a change in the slope of the reference I-V g curve. In another embodiment, the difference between the reference I-Vg curve and the chemical reaction I-Vg curve is an overall change in shape of the chemical reaction I-Vg curve relative to an overall change in shape of the reference I-Vg curve. In other embodiments, the difference in overall shape of the I-Vg curves is determined by first fitting a polynomial or other fitting line to each of the I-Vg curves and then comparing the coefficients of those fitting lines. In other embodiments, the difference between a reference I-Vg curve and the chemical reaction I-Vg curve is based on more than one chemical reaction I-V g curve.

[0059] Accordingly, in particular embodiments, the FET and/or processor may be configured to respond to a shift in the I-V or I-Vg curve, such as where the curve is shifted in response to the detection of a biological compound and/or the result of a reaction taking place in or on a surface of the FET device. In some instances, the I-V/I-Vg curve may be produced and/or shifted in response to a chemical reaction occurring on a reaction layer and/or the surface of a 1D or 2D, e.g., graphene, surface of the field effect transistor, such as resulting from the detection of a biological compound or reaction occurring within the well structure of the device. Hence, the FET and/or processor may be configured so as to shift the I-V curve or I-Vg curve such as in response to the chemical reaction. In various embodiments, one or more elements and/or methods, as herein described, may be used to shift a reference I-V or I-Vg curve and/or a chemical reaction I-Vg curve so that the difference between the reference I-Vg curve and a chemical reaction I-Vg is more pronounced. For instance, the device may include a structure, such as a membrane, other surface layer, and/or other element configured for enhancing the ability of the processor to determine the difference between various I-V and/or I-Vg curves.

[0060] Hence, in a further aspect, a chemically-sensitive FET transistor that is fabricated on a primary structure having a stacked configuration including an inorganic base layer, e.g., a silicon layer; a dielectric and/or an organic or inorganic insulator layer, such as a silicon dioxide layer; a 1D, 2D, or 3D material layer, such as a carbon nanotube, nanowire, or graphene layer; a reaction, e.g., oxidation, and/or passivation layer; and further having a conductive source and drain embedded in one or more of the layers, such as between and/or forming a gate structure, e.g., a solution gate region, may be provided. In various embodiments, the gate region may be configured so as to form a chamber or well and the 1D or 2D material and/or oxidation layers may be positioned between the conductive source and drain in such a manner as to form a bottom surface of the chamber. The structures may further include or otherwise be associated with an integrated circuit and/or a processor, such as for generating and/or processing generated data, such as sensor derived data.

[0061] Accordingly, in particular embodiments, a further structured layer, e.g., a secondary or tertiary structure, may also be provided, such as where the further structured layer may be included and/or present within the well or chamber, such as to enhance the ability of the processor to determine the difference between the current and/or voltages as well as their respective associated curves. More particularly, the additional structure may include an ion-selective permeable membrane, such as an ion-selective permeable membrane while blocking other ions, such as to enhance the ability of the processor to determine the difference between the reference I-V or I-Vg curve and the chemical reaction I-V or

I-Vg curve, and thus enhance the ability of the processor to detect a desired chemical reaction. In various instances, the FET may be configured such that the I-V or I-Vg curve(s) may be shifted so as to better respond to, detect, and/or otherwise determine a biological compound and/or a chemical reaction, such as a biological compound and/or a chemical reaction occurring on the 1D or 2D, e.g., graphene, surface of the chemically-sensitive field effect transistor. In particular instances, the ion-selective permeable membrane may include a 2D transistor material, e.g., graphene, which may or may not be electrically connected to the source and/or drain layer and/or channel.

[0062] Accordingly, in various instances, the ion-selective permeable membrane may be positioned within the well and/or over a passivation layer, an ion sensitive or reaction layer, a 1D and/or a 2D transistor material layer, and/or a dielectric layer that itself may be positioned over and/or otherwise form a part of the chamber or channel. In certain embodiments, the membrane layer may be or otherwise be associated with an ion getter material, such as an ion getter material that traps ions that may or may not be relevant to the biological species and/or chemical reaction to be sensed and/or determined, such as to enhance the ability of the processor to determine the difference between the reference I-V or I-Vg curve and/or the chemical reaction I-V or I-Vg curve, e.g., because there are fewer interfering ions, thus enhancing the ability of the processor to detect the desired biological species and/or results of the chemical reactions. Particularly, the ion getter material may be arranged within proximity to the chamber and/or surface thereof so that the action of gettering the unwanted ions improves the detection capability of the chemically-sensitive field effect transistor. In some instances, one or more of the various layers herein, such as the ion getter material may be placed over one or more of the other layers, such as the dielectric layer, oxide layer, or 1D or 2D or 3D layers, positioned in proximity to one or more of the chambers, channels, or surfaces of the FET device.