US 20150333838A1

### (19) United States

# (12) Patent Application Publication HORIKOSHI et al.

### (10) Pub. No.: US 2015/0333838 A1

(43) **Pub. Date:** Nov. 19, 2015

## (54) OPTICAL RECEIVING DEVICE AND PHASE CYCLE REDUCTION METHOD

# (71) Applicant: NIPPON TELEGRAPH AND TELEPHONE CORPORATION,

Chiyoda-ku, Tokyo (JP)

(72) Inventors: Kengo HORIKOSHI, Yokosuka-shi

(JP); Kohki SHIBAHARA, Yokosuka-shi (JP); Etsushi YAMAZAKI, Yokosuka-shi (JP); Mitsuteru YOSHIDA, Yokosuka-shi (JP); Koichi ISHIHARA, Yokosuka-shi

(JP); Takayuki KOBAYASHI, Yokosuka-shi (JP); Yoshiaki KISAKA, Yokosuka-shi (JP); Takuya OHARA,

Yokosuka-shi (JP); Masahito TOMIZAWA, Yokosuka-shi (JP); Tomoyoshi KATAOKA, Yokosuka-shi

(JP)

(73) Assignee: **NIPPON TELEGRAPH AND**

TELEPHONE CORPORATION,

Tokyo (JP)

(21) Appl. No.: 14/758,941

(22) PCT Filed: Jan. 24, 2014

(86) PCT No.: **PCT/JP2014/051501**

§ 371 (c)(1),

(2) Date: **Jul. 1, 2015**

### (30) Foreign Application Priority Data

| Jan. 25, 2013 | (JP) | 2013-012403 |

|---------------|------|-------------|

| Feb. 26, 2013 | (JP) | 2013-036126 |

#### **Publication Classification**

| (51) | Int. Cl.   |           |

|------|------------|-----------|

|      | H04B 10/61 | (2006.01) |

|      | H04L 27/38 | (2006.01) |

|      | H04L 7/00  | (2006.01) |

|      | H04L 27/06 | (2006.01) |

(52) U.S. Cl.

CPC ............. H04B 10/6165 (2013.01); H04L 27/066 (2013.01); H04L 27/389 (2013.01); H04L 7/0041 (2013.01); H04L 7/0075 (2013.01)

#### (57) ABSTRACT

An optical receiving device receives an optical signal that has been modulated by means of phase modulation or quadrature amplitude modulation, converts the received optical signal into an electrical signal using coherent detection, and performs phase compensation on the converted received signal, and includes: a carrier phase estimation unit that estimates carrier phase errors in a received symbol string obtained from the received signal; a gain adjustment unit that performs gain adjustment on symbols input into the carrier phase adjustment unit; a phase cycle slip reduction unit that, by performing statistical processing on an output from the carrier phase estimation unit, detects general noise that causes a phase cycle slip, and reduces the phase cycle slip; and a phase compensation circuit that compensates carrier phase errors contained in the received signal using an output from the carrier phase estimation unit.

COMPENSATION DELAY DIFFERENCE **DETERMINATION** DETERMINATION/COMPENSATION UNIT PHASE CYCLE SLIP DELAY CIRCUIT LPF 55 \* COMPLEX NUMBER CALCULATION CIRCUIT S S ಗ್ಳ ಪ್ರ ANGLE CALCULATION CIRCUIT DIVIDER CIRCUIT CARRIER PHASE COMPENSATION UNIT CARRIER PHASE ESTIMATION UNIT AVERAGING CIRCUIT Ç DELAY CIRCUIT GAIN ADJUSTMENT CIRCUIT دكنا

Ġ

FIG. 2

FIG. 3

FIG. 7

٥

(ESTIMATION ERROR PHASE)

Ö

HG. C

offline DSP OPTICAL SIGNAL RECEIVER DEVICE ADC ADC ADC ADC Polarization-diversity 90 degree Hybrid NA NA NA 4h 현 PLC-based Local Turnable LD OBPF EDF. 벌 ςο Χ TRANSMISSION PATH EDFA GEO Raman Pump Loss 28dB Lo **X** EDFA OPTICAL SIGNAL TRANSMISSION DEVICE \_ 0 3 3 3 Tx Even Channeles 27.75Gb/s PSK Bod. Tx Odd Channele 64ch WDM Tx 9320₽

E.

FIG. 17

- BER PHASE CYCLE SLIP WITH COMPENSATION

- ----- SLIP RATE PHASE CYCLE SLIP WITHOUT COMPENSATION

- --- SLIP RATE PHASE CYCLE SLIP WITH COMPENSATION

FIG. 19

FIG. 20B

FIG. 2

FIG. 2

3C. 2

FIG. 25

FIG. 26

42,7

HG. 2

IG. 28

FIG. 30

£ 5

FIG. 32

Ö

FIG. 36

METHOD A METHOD Ļ 25 23 ~ AVERAGED WINDOW WIDTH M ದ್ m U <del>س</del> دی

PHASE CYCLE SLIP RATE

FIG. 38

# OPTICAL RECEIVING DEVICE AND PHASE CYCLE REDUCTION METHOD

#### TECHNICAL FIELD

[0001] The present invention relates to a communication system, and to a technology that reduces the occurrence of cycle slips in a carrier synchronous circuit.

[0002] Priority is claimed on Japanese Patent Applications Nos. 2013-12403, filed Jan. 25, 2013, and 2013-36126 filed Feb. 26, 2013, the contents of which are incorporated herein by reference.

#### **BACKGROUND ART**

[0003] In a trunk optical transmission system there is a need to store high-speed client signals economically, and transmit huge volumes of information. As part of the process to achieve this objective, from the standpoint of improving the frequency utilization efficiency, a digital coherent transmission method which employs a combination of coherent detection and digital signal processing is being investigated, and it is anticipated that it will be possible to achieve high-speed, high-volume information transmissions by means of wavelength division multiplexing using the aforementioned transmission method. In this transmission method, carrier phase synchronization is established via digital signal processing. In consideration of the circuit scale and modulation format, various types of algorithms and packaging methods are being investigated for the structure of the carrier phase synchronization circuit (CPR: Carrier Phase Recovery).

[0004] In contrast, in an optical transmission system in which coherent detection is utilized, because amplitude and amplitude information are used, such a system is conspicuously affected by phase noise (i.e., noise in the phase direction). Main sources of such phase noise include phase noise arising from the line width of the lasers used in the transmission and receiving terminals, frequency offset caused by the frequency of the lasers used in the transmission and receiving terminals, and phase noise arising from a non-linear optical effect. For example, the Viterbi-Viterbi algorithm (see Nonpatent document 1) is one algorithm for performing carrier phase synchronization blindly on the receiving side.

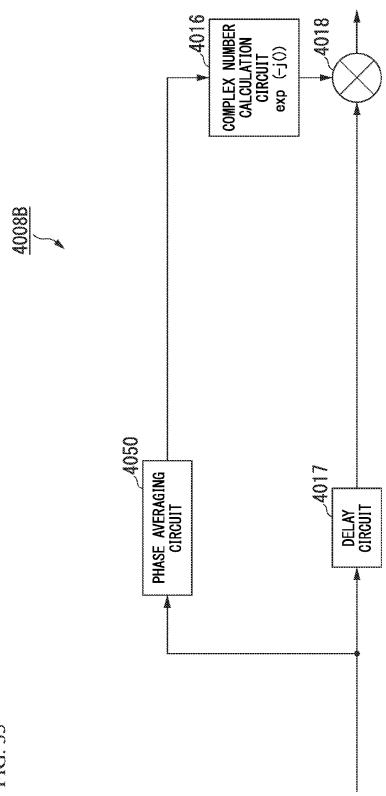

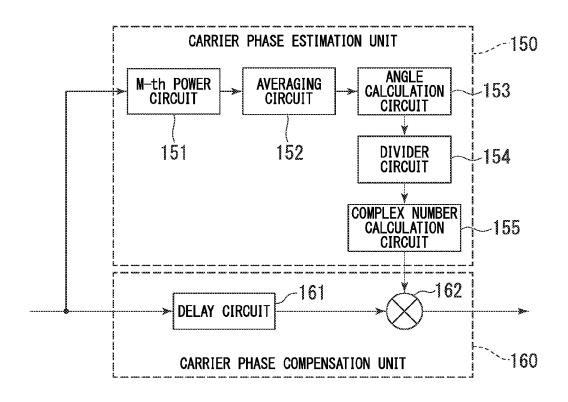

[0005] FIG. 38 is a block diagram showing the structure of a carrier phase synchronization circuit (CPR) that utilizes the Viterbi-Viterbi algorithm. Here, a description is given of when QPSK (Quadrature Phase Shift Keying) is used as the modulation format. In this case, M corresponds to 4. The input symbols are shown as complex values having an inphase component I and a quadrature component Q.

[0006] This CPR is formed by a carrier phase estimation unit 150 and a carrier phase compensation unit 160. The carrier phase estimation unit 150 is formed by an M-power circuit 151, an averaging circuit 152, an angle calculation circuit 153, an unwrapping circuit (not shown), a divider circuit 154, and a complex number calculation circuit 155. The carrier phase compensation unit 160 is provided with a delay circuit 161 and a multiplier circuit 162.

[0007] The input symbols that are input sequentially into the CPR are shown by the following Formula (1).

$$r_k = A_k \exp(j\theta_k + \phi_k) + w_k \tag{1}$$

[0008] Here, k is the time,  $s_k = A_k \exp(j\theta_k)$  is the transmission symbol, wk is the additive noise, and  $\phi_k$  is the phase

noise. In the Viterbi-Viterbi algorithm, by assuming an M-PSK (M-ary Phase Shift Keying) for the modulation technique, the fact that  $A_k$  is constant and  $\theta_k$  is expressed as  $2\pi mk/M$  is utilized. Note that mk is an integer between 0 and M-1.

**[0009]** The input symbol  $r_k$  is input into the M-power circuit **151** and the delay circuit **161**. The M-power circuit **151** raises the input symbol to the M-th power. As a result of this M-power operation on the input symbol, when  $w_k \approx 0$ , the output is as is shown in Formula (2).

(Formula 2)

$$r_k^M = A_k^M \exp(jM\theta_k + jM\phi_k)$$

$$= A_k^M \exp(j2\pi m_k + jM\phi_k)$$

$$= A_k^M \exp(jM\phi_k)$$

(2)

[0010] In actual fact, because  $w_k\neq 0$ , the output from the M-power circuit 151 is input into the averaging circuit 152, and the effects of noise are reduced. The averaging circuit 152 obtains an average, for example, by adding up the M-power values of the input symbols calculated by the M-power circuit 151 on a complex plane for every L number of averaged window widths which include the M-power values of the previous and subsequent input symbols, and thereby reduces the noise components. Next, the output from the averaging circuit 152 is input into the angle calculation circuit 153.

[0011] The angle calculation circuit 153 calculates the angle of deviation of the symbols (i.e., complex numbers) that have been averaged by the averaging circuit 152. If the noise has been sufficiently reduced by the averaging circuit 152, then the output from the angle calculation circuit 153 is Mφk. In this calculation method, the symbols are converted into an angle by, for example, calculating in-phase components (I) and quadrature components (Q) in the output from the averaging circuit 152, and then calculating the arctan (Q/I). The unwrapping circuit corrects the arbitrariness (360°×n, wherein n is an integer) remaining in the angle calculated by the angle calculation circuit 153. Specifically, the unwrapping circuit corrects the angle such that the difference between the angle for the immediately prior input symbol and the current angle is reduced.

[0012] The divider circuit 154 calculates carrier phase estimation values by multiplying by (1/M) the angle that was corrected by the unwrapping circuit. The complex number calculation circuit 155 calculates a size 1 complex number in order to make the carrier phase estimation value calculated by the divider circuit 154 into an angle of deviation, and outputs this to the multiplier circuit 162.

[0013] The delay circuit 161 attaches to an input symbol a delay for the time required for the calculations from the M-power circuit 154 to the complex number calculation circuit 155, and outputs the input symbol to the multiplier circuit 162 at the same timing as it outputs the size 1 complex number which corresponds to that particular input symbol. The multiplier circuit 162 multiplies the input symbol to which a delay was attached by the delay circuit 161 by the complex number calculated by the complex number calculation circuit 155, and synchronizes the result with the carrier phase of the input symbol.

# PRIOR ART DOCUMENTS

# Non-Patent Documents

[0014] Non-patent document 1: A. J. Viterbi, A. M. Viterbi "Nonlinear Estimation of PSK-Modulated Carrier Phase with Application to Burst Digital Transmission," IEEE Trans. On Info. Theory, vol. IT-29, July 1983.

# SUMMARY OF THE INVENTION

# Problems to be Solved by the Invention

[0015] Because the symbol phase is quadrupled (in the case of QPSK), the carrier phase estimation values estimated using the aforementioned algorithm can only be estimated in a range from 0 degrees to 90 degrees. Consequently, there are four possibilities for the angle where the estimation result will be contained: namely, between 0 degrees and 90 degrees, 90 degrees and 180 degrees, 180 degrees and 270 degrees, and 270 degrees and 360 degrees, and it is not possible to make a correct estimate from among these four possibilities for each input symbol. Even if the correct phase shift amount were already known as an initial value, and it were possible to perform carrier phase estimation continuously for each symbol, if there is a sudden incursion of sizable noise in the phase direction or interference from a non-linear optical effect, then a discontinuity that is not correct for the estimated phase amount is generated. If this type of discontinuity is generated, then it becomes impossible to correctly perform carrier phase estimation for any subsequent input symbols. This phenomenon is known as phase cycle slip.

[0016] In order to counter phase cycle slip, for example, a differential coding technique and a correction technique based on pilot symbols are considered to be effective. In a differential coding technique, the phase difference between adjacent symbols is transmitted as an optical phase modulation symbol so that, even if phase cycle slip is generated, the effects thereof can be restricted to the bit errors within the preceding and subsequent symbols. However, if a case in which the differential coding technique is applied is compared to a case in which it is not applied, then the former has the drawback that the bit error rate increases twofold. This drawback has the problem that it raises the signal to noise power ratio of the transmission path that is needed in order to establish trustworthy communication using forward error correction approximately 1.11 to 1.4 dB.

[0017] In contrast, the correction technique that is based on pilot symbols is a technique in which a phase cycle slip is detected and corrected by transmitting a known signal pattern. However, if a phase cycle slip is generated, burst errors are generated during the period up until the absolute phase is subsequently synchronized once again using a known signal pattern. If the cycle at which the known signal patterns are inserted is shortened in order to shorten the period during which burst errors are generated, the problem arises that overheads increase and there is a decrease in the transmission efficiency.

[0018] The present invention was conceived in view of the above-described circumstances, and it is an object thereof to provide a phase cycle slip reduction system and a phase cycle slip reduction method that make it possible to reduce the frequency of phase cycle slip occurrence without causing the bit error rate to increase or causing any deterioration in the transmission efficiency.

#### Means for Solving the Problems

[0019] In order to achieve the above-described objects, an aspect of the present invention is a phase cycle slip reduction system in which an optical signal that has been created from an electrical signal that has been modulated using phase modulation or quadrature amplitude modulation is received, the received optical signal is converted into an electrical signal using coherent detection, and phase compensation is performed on the received signal that is obtained by converting this electrical signal into a digital signal, the phase cycle slip reduction system comprising: a gain adjustment unit configured to perform gain adjustment using power and multiplication on the amplitude and phase of a symbol input from the CPR; a slip determination unit configured to determine whether or not a phase cycle slip exists using carrier phase estimation values output from a carrier phase estimation unit; and a slip compensation unit configured to compensate the phase cycle slip based on determination results from the phase cycle slip determination unit.

# Advantageous Effects of the Invention

[0020] According to this invention, even if phase cycle slip does occur, by detecting and compensating this phase cycle slip in a phase cycle slip determination/compensation unit, it is possible to reduce the frequency of phase cycle slip occurrence. Furthermore, by using a gain adjustment circuit to improve the estimation accuracy of carrier phase estimation values created by the carrier phase estimation unit, it is possible to improve the accuracy of the detections of the phase cycle slip determination/compensation unit, and to further reduce the frequency of phase cycle slip occurrence.

[0021] As a consequence, because it is possible to accurately predict phases without having to transmit symbols that have undergone prior processing, it is possible to reduce the frequency of phase cycle slip occurrence without increasing the bit error rate or reducing the transmission efficiency.

# BRIEF DESCRIPTION OF DRAWINGS

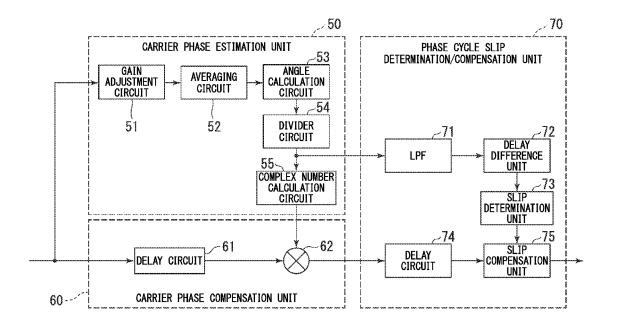

[0022] FIG. 1 is a block diagram showing a carrier phase synchronization circuit (CPR) according to a first embodiment of the present invention.

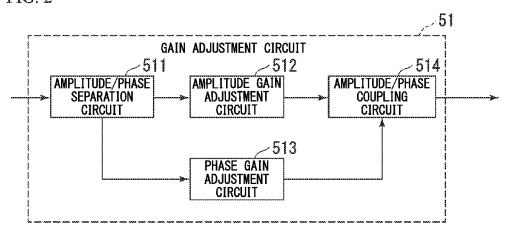

[0023] FIG. 2 is a block diagram showing the gain adjustment circuit shown in FIG. 1.

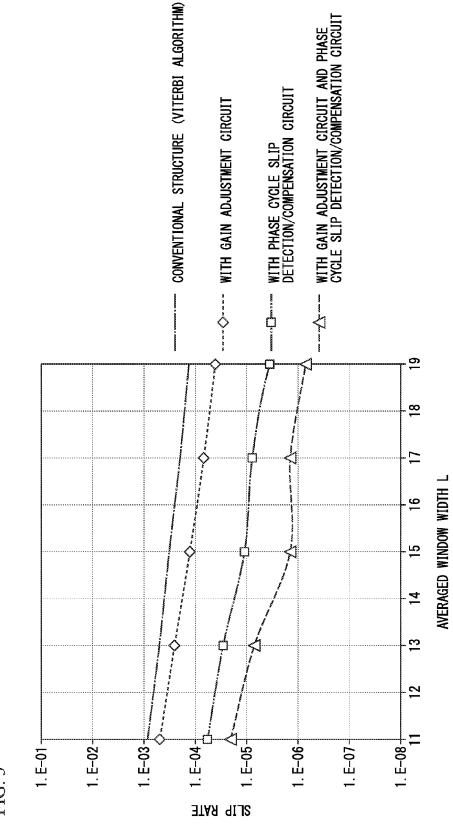

[0024] FIG. 3 is a graph showing the reduction effects of the phase cycle slip ratio of an embodiment of the present invention.

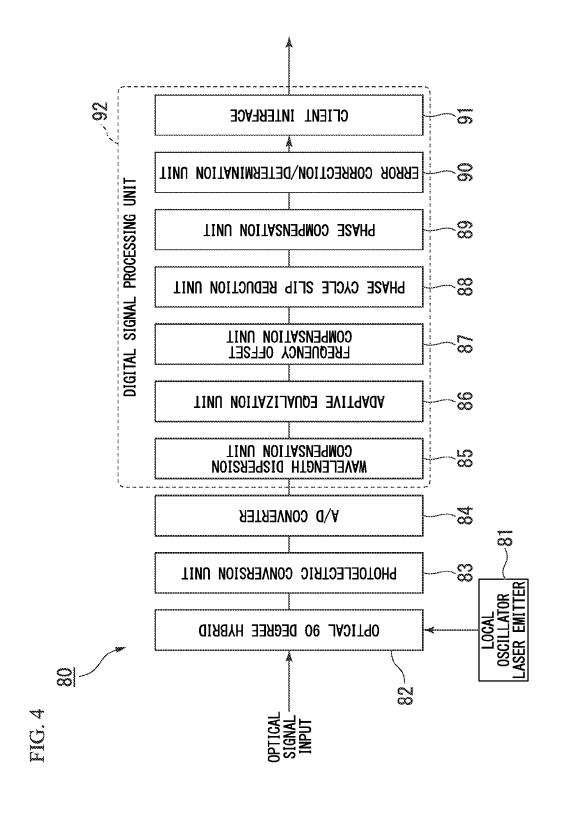

[0025] FIG. 4 is a block diagram showing a receiver device according to a second embodiment of the present invention.

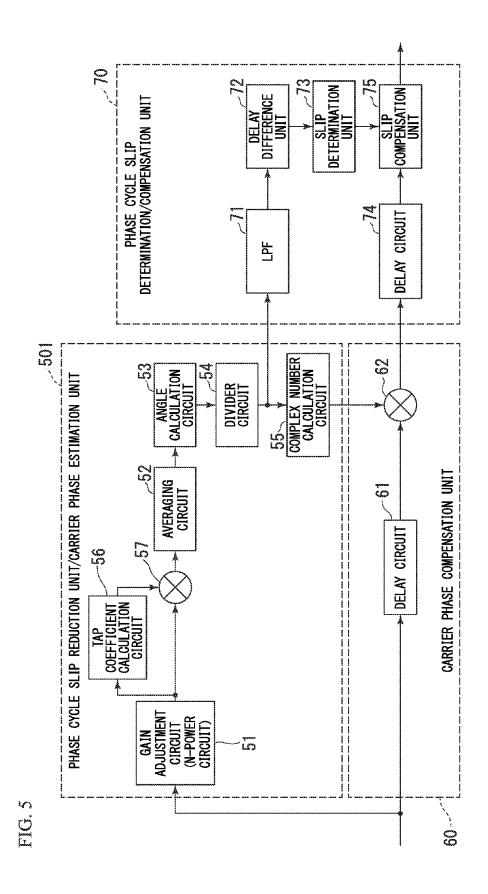

[0026] FIG. 5 is a block diagram showing a phase compensation circuit according to a third embodiment of the present invention.

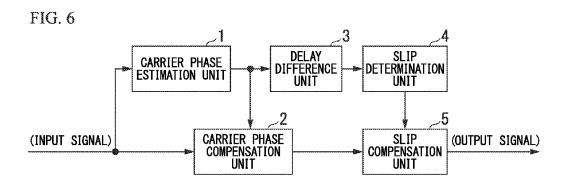

[0027] FIG. 6 is a block diagram showing the structure of a phase compensation circuit according to a fourth embodiment of the present invention

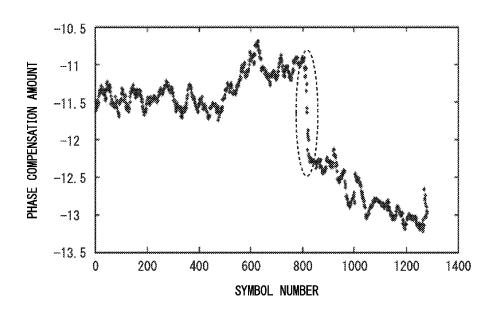

[0028] FIG. 7 is a graph showing an example of an estimation error phase output by the carrier phase estimation unit shown in FIG. 6.

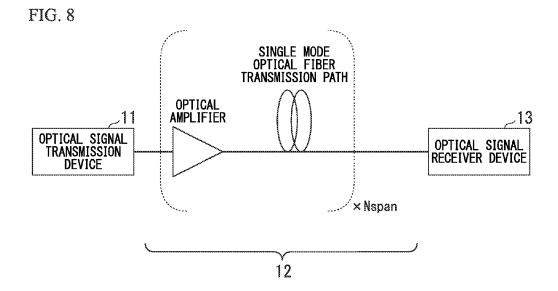

[0029] FIG. 8 is a block diagram showing an example of the structure of an optical communication system according to a fifth embodiment of the present invention.

[0030] FIG. 9 is a block diagram showing an example of the structure of an optical signal receiver device according to the fifth embodiment.

[0031] FIG. 10 is a block diagram showing an example of the structure of a phase compensation circuit according to the fifth embodiment.

[0032] FIG. 11 is a block diagram showing an example of the structure of a carrier phase estimation circuit according to the fifth embodiment.

[0033] FIG. 12 is a block diagram showing an example of the structure of a phase-m multiplier circuit according to the fifth embodiment.

[0034] FIG. 13 is a block diagram showing an example of the structure of a K symbol averaging circuit according to the fifth embodiment.

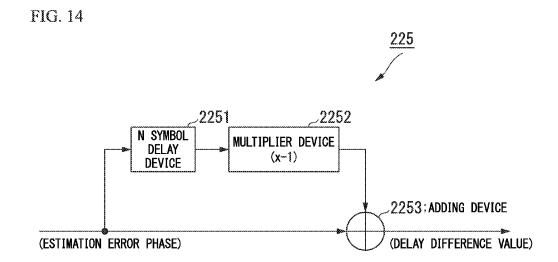

[0035] FIG. 14 is a block diagram showing an example of the structure of a delay difference circuit according to the fifth embodiment.

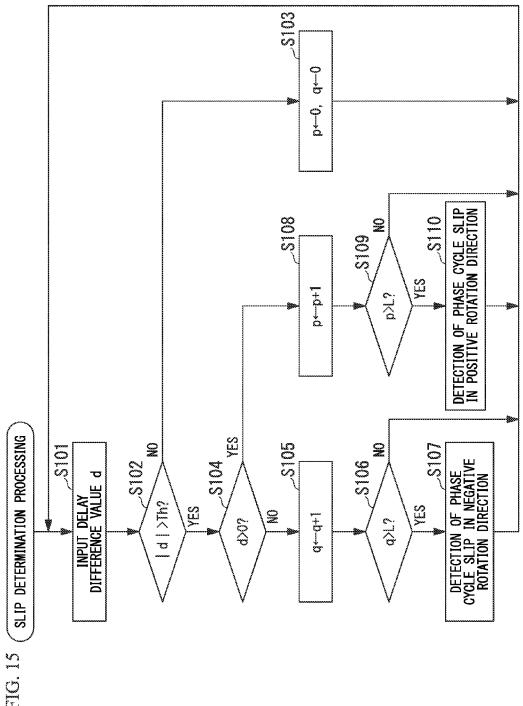

[0036] FIG. 15 is a flowchart showing slip determination processing performed by a slip determination circuit according to the fifth embodiment.

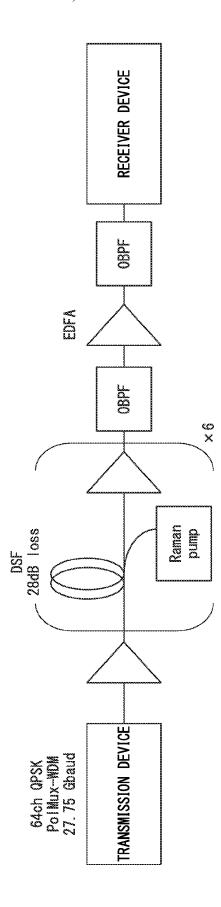

[0037] FIG. 16 is a schematic block diagram showing the structure of a test device used to acquire optical transmission test data.

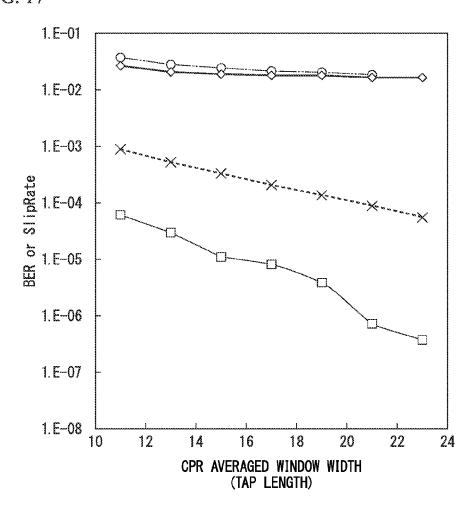

[0038] FIG. 17 is a graph showing the results when off-line demodulation was performed on the optical transmission test data obtained by the test device shown in FIG. 16.

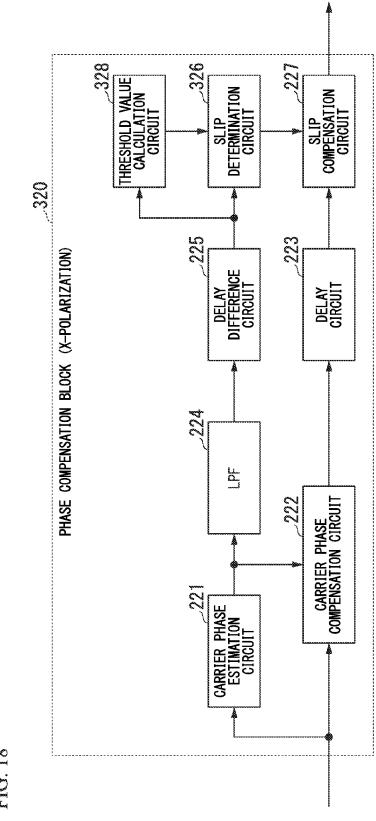

[0039] FIG. 18 is a block diagram showing the structure of a phase compensation block according to a sixth embodiment of the present invention.

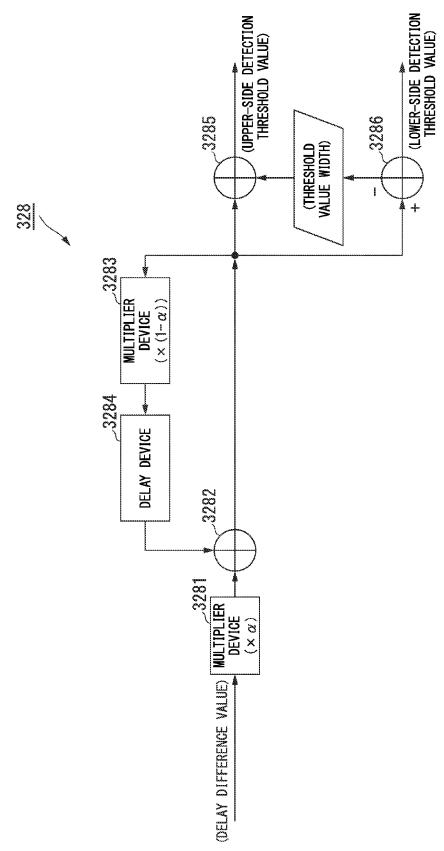

[0040] FIG. 19 is a block diagram showing an example of the structure of the threshold value calculation circuit according to the sixth embodiment.

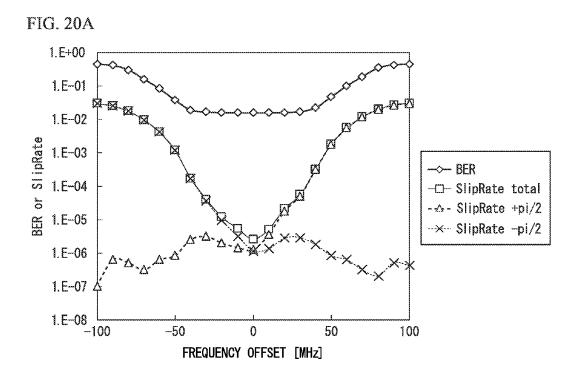

[0041] FIG. 20A is a graph showing a relationship between a bit error rate and symbol slip rate and a frequency offset when the detection threshold value is set as a fixed value according to the sixth embodiment.

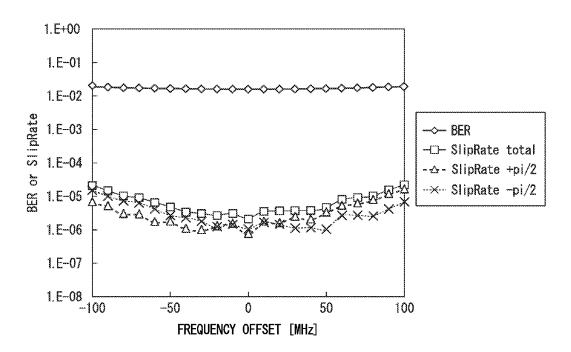

[0042] FIG. 20B is a graph showing a relationship between the bit error rate and symbol slip rate and the frequency offset when the detection threshold value is determined in accordance with a delay difference value according to the sixth embodiment.

[0043] FIG. 21 is a block diagram showing the structure of a phase compensation block according to a seventh embodiment of the present invention.

[0044] FIG. 22 is a block diagram showing the structure of a phase compensation block according to an eighth embodiment of the present invention.

[0045] FIG. 23 is a block diagram showing an example of the structure of a receiver device according to a ninth embodiment of the present invention.

[0046] FIG. 24 is a block diagram showing an example of the structure of a phase compensation unit according to the ninth embodiment.

[0047] FIG. 25 is a graph showing an example of a constellation map after a symbol has been multiplied N times by an N multiplier circuit according to the ninth embodiment.

[0048] FIG. 26 is a block diagram showing an example of the structure of a tap coefficient calculation circuit according to the ninth embodiment.

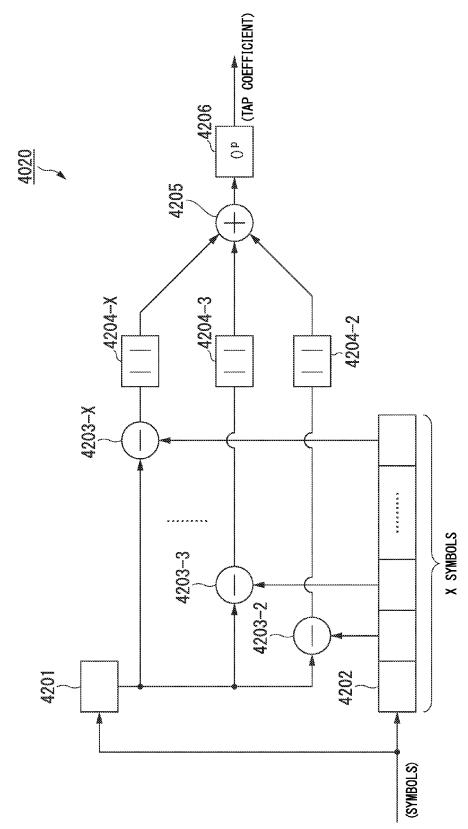

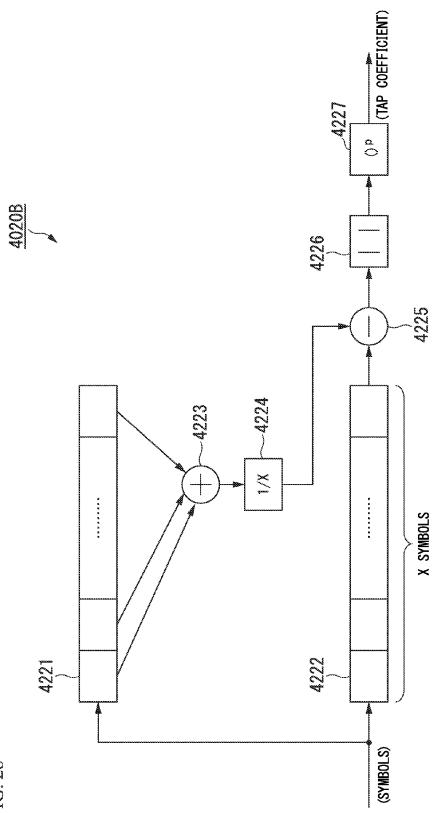

[0049] FIG. 27 is a block diagram showing an example of the structure of a tap coefficient calculation circuit according to a tenth embodiment of the present invention.

[0050] FIG. 28 is a block diagram showing an example of the structure of a tap coefficient calculation circuit according to an eleventh embodiment of the present invention.

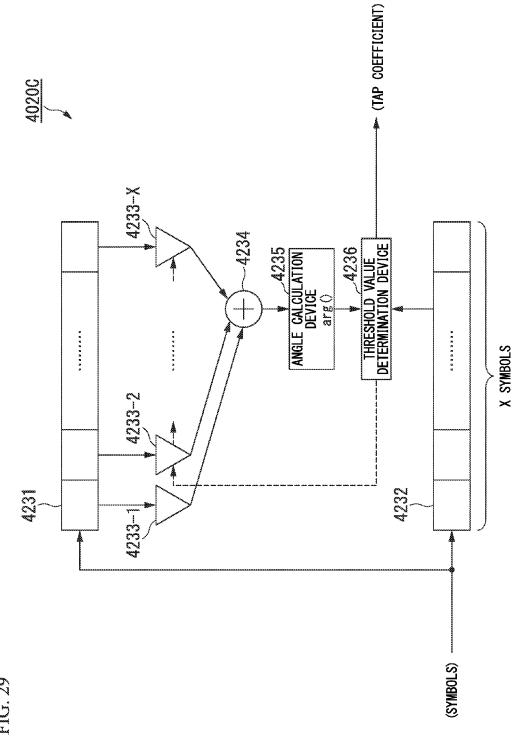

[0051] FIG. 29 is a block diagram showing the structure of a tap coefficient calculation circuit according to a twelfth embodiment of the present invention.

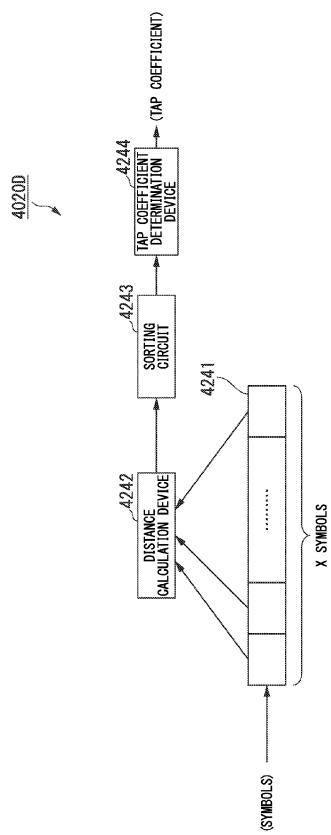

[0052] FIG. 30 is a block diagram showing the structure of a tap coefficient calculation circuit according to a thirteenth embodiment of the present invention.

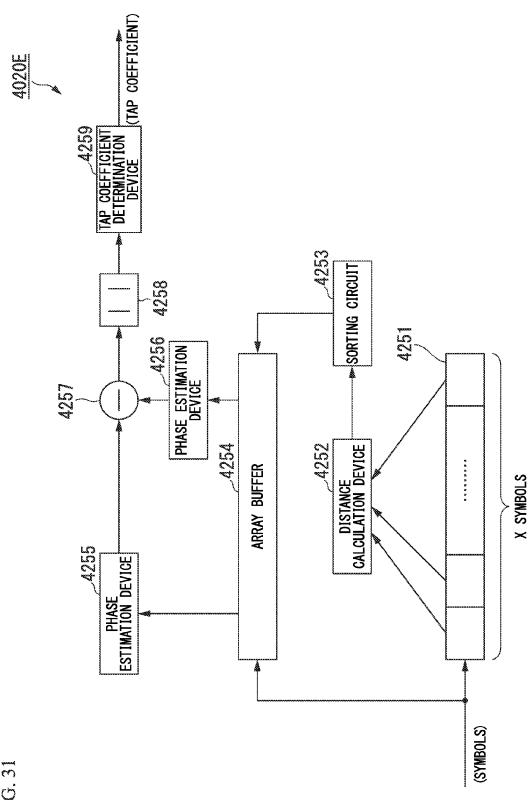

[0053] FIG. 31 is a block diagram showing the structure of a tap coefficient calculation circuit according to a fourteenth embodiment of the present invention.

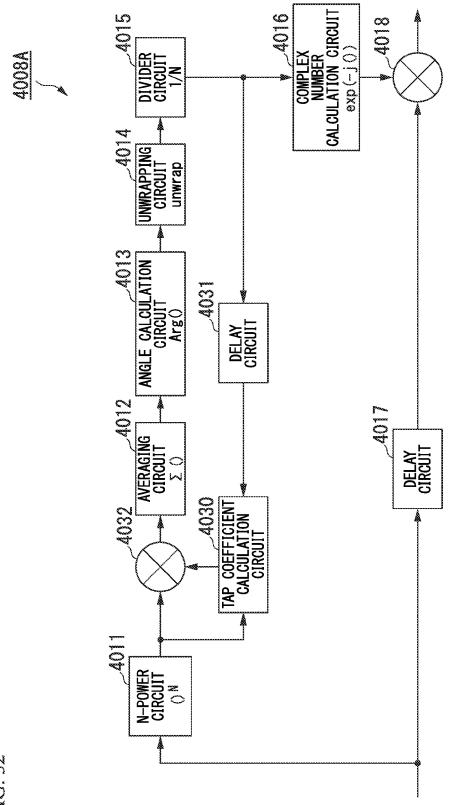

[0054] FIG. 32 is a block diagram showing the structure of a phase compensation unit according to a fifteenth embodiment of the present invention.

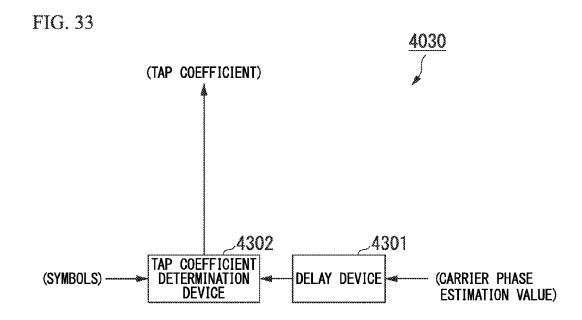

[0055] FIG. 33 is a block diagram showing the structure of a tap coefficient calculation circuit according to the fifteenth embodiment.

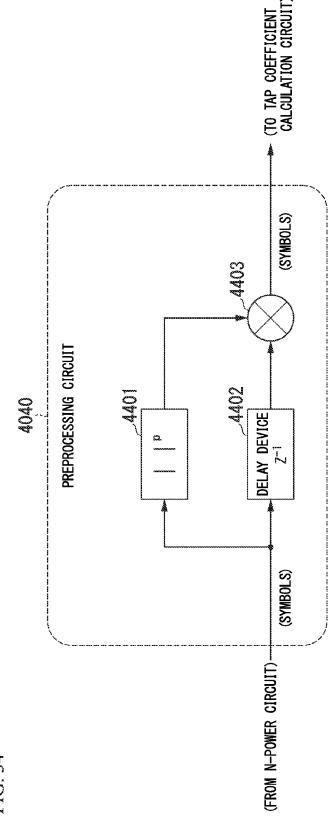

[0056] FIG. 34 is a block diagram showing the structure of a preprocessing circuit according to a variant example.

[0057] FIG. 35 is a block diagram showing the structure of a phase compensation unit according to a sixteenth embodiment of the present invention.

[0058] FIG. 36 is a view showing an outline of a test device used to acquire optical transmission test data.

[0059] FIG. 37 is a graph showing the evaluation results of a phase cycle slip rate for the phase compensation unit according to the fifteenth embodiment.

[0060] FIG. 38 is a block diagram showing a conventional carrier phase synchronization circuit.

# EMBODIMENTS FOR CARRYING OUT THE INVENTION

**[0061]** Hereinafter, a phase cycle slip reduction system and phase cycle slip reduction method according to embodiments of the present invention will be described with reference made to the drawings.

# First Embodiment

[0062] FIG. 1 is a block diagram showing the structures of a carrier phase synchronization circuit (CPR) and a phase cycle slip determination/compensation unit according to embodiments of the present invention.

[0063] Symbols input into the CPR are input into both a carrier phase estimation unit 50 and a carrier phase compensation unit 60. In the carrier phase estimation unit 50, the input symbols are input into a gain adjustment circuit 51.

[0064] As is shown in FIG. 2, the gain adjustment circuit 51 is formed by an amplitude/phase separation circuit 511 that calculates and separates amplitude values and phase values of input symbols, an amplitude gain adjustment circuit 512 into which the amplitude values separated by the amplitude/phase separation circuit 511 are input, a phase gain adjustment circuit 513 into which the phase values separated by the amplitude/phase separation circuit 511 are input, and an amplitude/phase recombination circuit 514 that recombines the output from the amplitude gain adjustment circuit 512 with the output from the phase gain adjustment circuit 513, and converts the result into a complex number.

[0065] For example, in the amplitude gain adjustment circuit 512, the amplitude is raised to the M-th power, and if the phase is multiplied M-times in the phase gain adjustment circuit 513, then the operation becomes equivalent to one performed in the M-power circuit in the CPR to which the Viterbi-Viterbi algorithm has been applied. In this example, by holding, for example, amplitude values in the amplitude

gain adjustment circuit 512, and multiplying the phase M-times in the phase gain adjustment circuit 513, the detection accuracy of the phase cycle slip determination/compensation unit 70 (described below) is improved. Namely, the operation of the present example is different from that of the M-power circuit in the CPR to which the Viterbi-Viterbi algorithm has been applied.

[0066] Here, the setting values in the gain adjustment circuit 51 are not limited solely to the aforementioned setting values. The setting values for the gain in the amplitude gain adjustment circuit 512 and the phase gain adjustment circuit 513 are set based on the averaged window width of an averaging circuit 52, on the tap length and band width of a low-pass filter (LPF) 71 of a phase cycle slip determination/compensation circuit 70, and on the delay width of a delay difference unit.

[0067] The output from the gain adjustment circuit 51 is input into the averaging circuit 52. In the averaging circuit 52, for example, averaging is performed by adding together the symbols calculated by the gain adjustment circuit 51 on a complex plane for every L number of averaged window widths which include the symbols calculated before and after that particular symbol, and the noise components are thereby reduced.

[0068] Next, the output from the averaging circuit 52 is input into the angle calculation circuit 53. The angle calculation circuit 53 calculates the angle of deviation of the symbols (i.e., complex numbers) that have been averaged by the averaging circuit 52. If the noise has been sufficiently reduced by the averaging circuit 52, then the output from the angle calculation circuit 53 is  $M\phi k$ .

[0069] In the calculation method performed by the angle calculation circuit 53, the symbols are converted into an angle by, for example, calculating an in-phase component (I) and a quadrature component (Q) in the output from the averaging circuit 52, and then calculating the arctan (Q/I). An unwrapping circuit corrects the arbitrariness (360°×n, wherein n is an integer) remaining in the angle calculated by the angle calculation circuit 53. Specifically, the unwrapping circuit corrects the angle such that the difference between the angle for the immediately prior input symbol and the current angle is reduced.

[0070] A divider circuit 54 calculates carrier phase estimation values by multiplying by (1/M) the angle that was corrected by the unwrapping circuit. The complex number calculation circuit 55 calculates a size 1 complex number that changes the carrier phase estimation value calculated by the divider circuit 54 into an angle of deviation, and outputs this to a multiplier circuit 62.

[0071] The delay circuit 61 attaches to an input symbol the delay for the length of time required for the operations from the gain adjustment circuit 51 to the complex number calculation circuit 55, and outputs the input symbol to the multiplier circuit 62 at the same timing as it outputs the size 1 complex number which corresponds to that particular input symbol. The multiplier circuit 62 multiplies the input symbol to which a delay was attached by the delay circuit 61 by the complex number calculation circuit 55, and synchronizes the result with the carrier phase of the input symbol.

[0072] In contrast, the estimation error phase calculated by the divider circuit 54 is input into a delay difference circuit 72 via the LPF 71. The delay difference circuit 72 calculates temporal changes in the estimation error phases. A slip deter-

mination unit 73 determines, based on the temporal changes in the estimation error phases calculated by the delay difference unit 72, whether or not a phase cycle slip has been generated in the input signal. There are three types of determination of the phase cycle slip, namely, at 90 degrees, –90 degrees, and 180 degrees, and these can be determined using the polarity and absolute value of the temporal changes.

[0073] When it is determined in the slip determination unit 73 that a phase cycle slip has occurred, a slip compensation unit 75 compensates the phase cycle slip in an input signal in which the phase error has been reduced by the carrier phase compensation unit 60.

[0074] In this phase cycle slip compensation, in the case of a 90 degree slip determination, 90 degrees is subtracted from the phase estimation values subsequent to the time when the phase cycle slip occurred. In the case of a -90 degree slip determination, 90 degrees is added to the phase estimation values. In the case of a 180 degree slip determination, 180 degrees is added to (or subtracted from) the phase estimation values.

[0075] The slip compensation unit 75 outputs as output signals the signals obtained when it performs phase cycle slip compensation on input signals. Moreover, when it is determined in the slip determination unit 73 that a phase cycle slip has not occurred, the slip compensation unit 75 outputs as output signals the input signals in which the phase error has been reduced by the carrier phase compensation unit 60.

[0076] The effects of this example are shown in FIG. 3. FIG. 3 shows the reduction effect on the phase cycle slip rate when the present invention is applied to a conventional structure of a CPR.

[0077] Compared with a conventional structure in which the Viterbi-Viterbi algorithm has been applied, by providing the gain adjustment circuit 51, because the accuracy of the estimation of the carrier phase estimation values in the carrier phase estimation unit 50 is improved, the slip rate is reduced. Moreover, if a phase cycle slip determination/compensation unit 70 is provided without the gain adjustment circuit being provided, by compensating any phase cycle slip that occurs, the slip rate is reduced.

[0078] In the present example, by providing the gain adjustment circuit 51 and providing the phase cycle slip determination/compensation unit 70, the accuracy of the estimation of the carrier phase estimation unit 50 is improved and, furthermore, the accuracy of the phase cycle slip detection by the phase cycle slip determination unit 73 is also improved. Because of this, in a conventional structure, reduction to a slip rate of approximately  $\frac{1}{100}$  is possible.

#### Second Embodiment

[0079] FIG. 4 is a block diagram showing an example of the structure of a receiver device according to a second embodiment. In a receiver device 80 shown in FIG. 4, the present invention is applied to a digital coherent transmission system.

[0080] Optical signals transmitted on an optical fiber transmission path are input into the receiver device 80. The receiver device 80 acquires data contained in the input optical signals, and outputs this acquired data to devices and the like that are connected downstream from it. The receiver device 80 is equipped with a local oscillator laser emitter 81, an optical 90 degree hybrid 82, a photoelectric conversion unit 83, an A/D converter 84, a wavelength dispersion compensation unit 85, an adaptive equalization unit 86, a frequency offset compensation unit 87, a phase cycle slip reduction unit

88, a phase compensation unit 89, an error correction/determination unit 90, and a client interface 91.

[0081] The optical signals input into the receiver device 80 are input into the optical 90 degree hybrid 82. They are then mixed with a local oscillation laser output by the local oscillator laser emitter 81 in the optical 90 degrees hybrid 82 so as to form a homodyne detection wave or a heterodyne detection wave. The optical signal obtained from this detection wave is then converted into a baseband analog electrical signal in the photoelectric conversion unit 83. This analog electrical signal is then digitalized in the A/D converter 84, and is then output to the wavelength dispersion compensation unit 85. The digital signal output from the A/D converter 84 is a signal showing a symbol that is expressed as a complex number having an in-phase component I and a quadrature component Q.

[0082] The wavelength dispersion compensation unit 85 compensates waveform distortion that is caused by wavelength dispersion in the symbols that are input from the A/D converter 84. The adaptive equalization unit 86 compensates distortion that is generated by linear polarization crosstalk and by polarization mode dispersion and the like in the symbols whose waveform distortion has been compensated in the wavelength dispersion compensation unit 85. The frequency offset compensation unit 87 compensates the effects of frequency offset that occurs between transmitting devices that transmit optical signals and the receiver device 80 in the symbols whose distortion has been compensated by the adaptive equalization unit 86. This frequency offset, for example, is caused by frequency shift in the local oscillation lasers used by the transmission devices and the receiver device.

[0083] The phase cycle slip reduction unit 88 and the phase compensation unit 89 perform phase compensation on symbols whose frequency offset has been compensated by the frequency offset compensation unit 87, so as to reduce the occurrence of phase cycle slip. The error correction/determination unit 90 demodulates symbols whose phase has been compensated by the phase compensation unit 89, and after performing error detection and error correction on the data obtained from this demodulation, it inputs the data into the client interface 91. The client interface 91 converts data input from the error correction/determination unit 90 in accordance with the signal format and frame structure that are used in devices connected downstream from the receiver device, and then outputs the converted data.

[0084] In the receiver device 80, received optical signals are converted into electrical signals using coherent detection, and the reception signals obtained by converting these electrical signals into digital signals are then input into a digital signal processing unit 92, which includes the various units from the wavelength dispersion compensation unit 85 through to the client interface 91. The reception signals input into the digital signal processing unit 92 are signals that show a symbol string in which data has been mapped based on the modulation format used in the transmission device. In the receiver device 80, waveform distortion and noise that have been added by the optical fiber transmission path, the transmission device, and the receiver device are either reduced or compensated in the wavelength dispersion compensation unit 85 and the adaptive equalization unit 86.

[0085] The purpose of the phase compensation unit 89 of the present example is to estimate phase noise superimposed on the carrier wave, and to then remove or reduce this phase noise. Here, the phase cycle slip reduction unit 88 and the phase compensation unit 89 will be described in detail.

[0086] In the phase compensation unit 89, carrier phase estimation is performed from the received signal string. If what are known as outliers are mixed in with the symbols of the received symbol string that is used in the carrier phase estimation, then it is not possible for accurate carrier phase estimation to be performed, and phase cycle slips are generated. The phase compensation unit 89 performs the following function. Namely, it detects these so-called outliers by performing statistical processing on each symbol of the received symbol string, and after the effects of these outlier symbols have been reduced, it performs the carrier phase estimation. [0087] In the phase cycle slip reduction unit 88, the occurrence of phase cycle slip is detected using the output from the frequency offset compensation unit 87, and, for those reception signals on which incorrect phase compensation was performed due to the phase cycle slip, phase compensation is performed on the incorrect portion that was caused by that phase cycle slip.

#### Third Embodiment

[0088] FIG. 5 is a block diagram showing the structure of a phase compensation circuit according to a third embodiment. In this phase compensation unit, a phase cycle slip reduction unit/carrier phase estimation unit 501 and the carrier phase compensation unit 60 correspond to the phase cycle slip reduction unit 88 shown in FIG. 4, and the phase cycle slip determination/compensation unit 70 corresponds to the phase compensation unit 89 shown in FIG. 4.

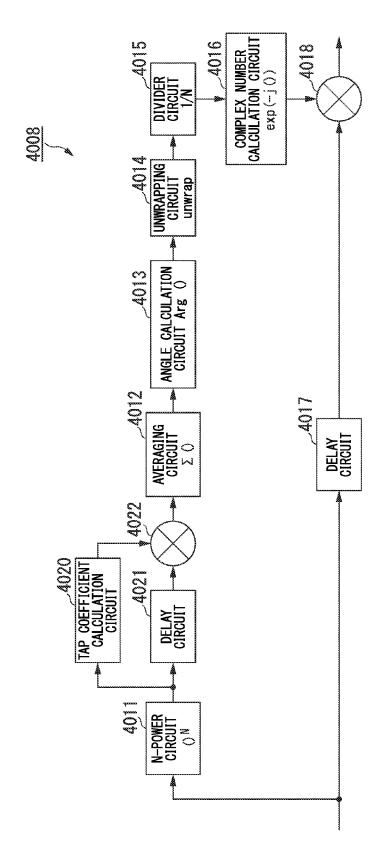

**[0089]** Input symbols that are input in sequence into the phase compensation circuit are input into the gain adjustment circuit 51, which is functioning as an N-power circuit (hereinafter, referred to as an N-power circuit), and the delay circuit 61. It should be noted, however, that the N-power circuit is described simply as one example of the gain adjustment circuit 51, and the present invention is not limited to this. The N-power circuit 51 raises input symbols to the N-th power. This operation to raise input symbols to the N-th power is in order to eliminate the data dependency of two redundant bits (1, 1), (1, -1), (-1, 1), and (-1, -1) in each symbol.

[0090] A tap coefficient calculation circuit 56 detects outliers by performing statistical processing on the input symbols that have been raised to the N-th power. The tap coefficient calculation circuit 56 calculates tap coefficients that correspond to the symbols in the outliers in order to reduce the effects of these outliers, and then outputs the tap coefficients. After the tap coefficient has been multiplied by the N-th power values of the preceding and subsequent symbols by the multiplication circuit 57, the averaging circuit 52 obtains an average by adding up the N-th power values of the input symbols calculated by the N-power circuit on a complex plane for every M number of averaged window widths, and thereby reduces the noise component.

[0091] The angle calculation circuit 53 calculates the angle of deviation of the symbols (i.e., complex numbers) that have been averaged by the averaging circuit 52. In the angle calculation circuit 53, the symbols are converted into an angle using, for example, an arctan (Q/I). An unwrapping circuit that is included in the angle calculation circuit 53 corrects the arbitrariness (360°×n, wherein n is an integer) remaining in the angle calculated by the angle calculation circuit 53. Specifically, the unwrapping circuit corrects the angle such that the difference between the angle for the immediately prior input symbol and the current angle is reduced.

[0092] The divider circuit 54 calculates carrier phase estimation values by multiplying by (1/N) the angle that was corrected by the unwrapping circuit. The complex number calculation circuit 55 calculates a size 1 complex number that changes the carrier phase estimation value calculated by the divider circuit 54 into an angle of deviation, and outputs this to the multiplier circuit 62.

[0093] The delay circuit 61 attaches to an input symbol the delay for the time required for the calculations from the N-power circuit 51 to the complex number calculation circuit 55, and outputs the input symbol to the multiplier circuit 62 at the same timing as it outputs the size 1 complex number which corresponds to that particular input symbol. The multiplier circuit 62 multiplies the input symbol to which a delay was attached by the delay circuit 61 by the complex number calculated by the complex number calculation circuit 55, and compensates the phase noise and the like contained in the input symbol.

[0094] In contrast, the calculated estimation error phase is input into the delay difference circuit 72 via the LPF 71. The delay difference circuit 72 calculates temporal changes in the estimation error phases. The slip determination unit 73 determines, based on the temporal changes in the estimation error phases calculated by the delay difference unit 72, whether or not a phase cycle slip has occurred in the input signal. There are three types of determination of the phase cycle slip, namely, at 90 degrees, –90 degrees, and 180 degrees, and these can be determined using the polarity and absolute value of the temporal changes.

[0095] When it is determined in the slip determination unit 73 that a phase cycle slip has occurred, the slip compensation unit 75 compensates the phase cycle slip in an input signal in which the phase error has been reduced by the carrier phase compensation unit 60.

[0096] In this phase cycle slip compensation, in the case of a 90 degree slip determination, 90 degrees is subtracted from the phase estimation values subsequent to the time when the phase cycle slip occurred. In the case of a –90 degree slip determination, 90 degrees is added to the phase estimation values. In the case of a 180 degree slip determination, 180 degrees is added to (or subtracted from) the phase estimation values.

[0097] The slip compensation unit 75 outputs as output signals the signals obtained when phase cycle slip compensation is performed on input signals. Moreover, when it is determined in the slip determination unit 73 that a phase cycle slip has not occurred, the slip compensation unit 75 outputs as output signals the input signals in which the phase error has been reduced by the carrier phase compensation unit 60.

#### Fourth Embodiment

[0098] Next, an outline of a phase compensation circuit according to an embodiment of the present invention will be described. FIG. 6 is a block diagram showing the structure of a phase compensation circuit according to a fourth embodiment of the present invention. The phase compensation circuit is used in an optical receiver device in an optical communication system. As is shown in FIG. 6, the phase compensation circuit is provided with a carrier phase estimation unit 1, a carrier phase compensation unit 2, a delay difference unit 3, a slip determination unit 4, and a slip compensation unit 5.

[0099] Once photoelectric conversion has been performed on received optical signals, the signals undergo analog/digital

conversion and the digital signals thereby obtained are input as input signals into the phase compensation circuit. If necessary, before the input signals are input into the phase compensation circuit, wavelength dispersion compensation and compensation for any distortion during transmission and the like may also be performed on the input signals.

[0100] The carrier phase estimation unit 1 performs either feedback or feed-forward carrier phase estimation on the input signals. The carrier phase estimation unit 1 outputs estimation error phases, which are estimated values for carrier phase errors, to the carrier phase compensation unit 2 and the delay difference unit 3. Based on these estimation error phases, the carrier phase compensation unit 2 reduces phase errors contained in the input signal.

[0101] The delay difference unit 3 calculates temporal changes in the estimation error phases. The slip determination unit 4 determines whether or not a phase cycle slip has occurred in the input signal based on the temporal changes in the estimation error phases calculated by the delay difference unit 3.

[0102] When it is determined in the slip determination unit 4 that a phase cycle slip has occurred, the slip compensation unit 5 performs phase cycle slip compensation on the input signal in which the phase errors have already been reduced by the carrier phase compensation unit 2. The slip compensation unit 5 outputs as an output signal the signal obtained as a result of the phase cycle slip compensation being performed on the input signal. Moreover, when it is determined in the slip determination unit 4 that a phase cycle slip has not occurred, the slip compensation unit 5 outputs as an output signal the input signal in which the phase errors have already been reduced by the carrier phase compensation unit 2.

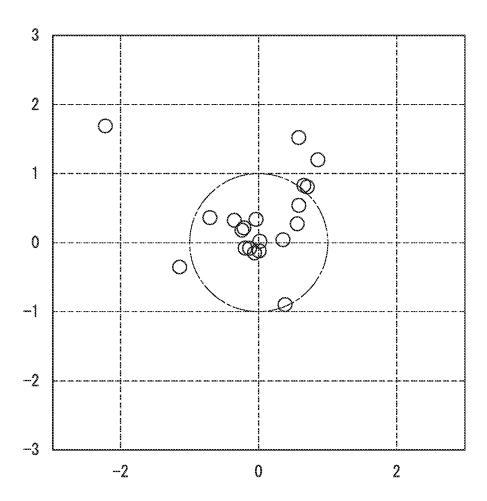

[0103] FIG. 7 is a graph showing an example of estimation error phases output by the carrier phase estimation unit 1. Namely, FIG. 7 is a graph showing phase compensation amounts of the past 1280 symbols (corresponding to a protected section) when a phase slip is detected. In FIG. 7, the horizontal axis shows the symbol number in the input signal, while the vertical axis shows the phase compensation amount. The phase compensation amount is the phase amount when the phase errors are reduced based on the estimation error phases. In FIG. 7, in the area shown by the broken line, namely, in the area where the symbol number is 800, a steep change is generated in the estimation error phases. This steep change is due to the occurrence of a phase cycle slip.

[0104] As is shown in FIG. 7, looking at the variations in the estimation error phases, when the phase cycle slip occurs, a change of approximately  $(\pi/2)$  radian is generated in a short time of approximately several times the average of the tap length of the filter in the carrier phase estimation unit 1 (i.e., approximately 100 symbols when the tap length average is 17). In contrast, when a phase cycle slip has not occurred, a change in the estimation error phase in excess of one radian does not occur in a short time.

[0105] Phase cycle slip detection and phase cycle slip compensation are performed using these estimation error phase characteristics. Specifically, the estimation error phases output by the carrier phase estimation unit 1 are monitored, and it is determined that a phase cycle slip has occurred when a steep change is detected within a short time, and phase cycle slip compensation is then performed on the input signal. A steep change is, for example, a change that exceeds one radian. By compensating a phase cycle slip in the phase compensation circuit, it is possible to suppress the frequency

at which phase cycle slips occur in signal processing performed downstream from the phase compensation circuit.

[0106] As a result of this, the substantial frequency at which phase cycle slips occur can be reduced to ((phase cycle slip occurrence frequency)×(1–(detection rate))+(number of incorrect detections)). The detection rate is the proportion of phase cycle slips that were detected in the slip determination unit 4, while the number of incorrect detections is the number of times that the slip determination unit 4 incorrectly determined that a phase cycle slip had occurred.

# Fifth Embodiment

[0107] FIG. 8 is a block diagram showing an example of the structure of an optical communication system according to a fifth embodiment of the present invention. An optical communication system of the present embodiment is equipped with an optical signal transmission device 11, a transmission path 12 that is formed by a single mode optical fiber transmission path and by an optical amplifier, and an optical signal receiver device 13. The optical signal transmission device 11 outputs via the transmission path 12 to the optical signal receiver device 13 optical signals obtained by performing polarization multiplexing on signals obtained using, for example, a QPSK modulation format.

[0108] In the optical communication system of the present embodiment, differential encoding is not performed. Note that in the following description, a structure is described in which QPSK is used for the modulation format, and signals that have undergone polarization multiplexing are transmitted and received. However, it is also possible to use an m-QAM modulation format such as BPSK (Binary Phase Shift Keying) and 16 QAM (Quadrature Amplitude Modulation), or to employ a structure in which single polarization signals are transmitted and received.

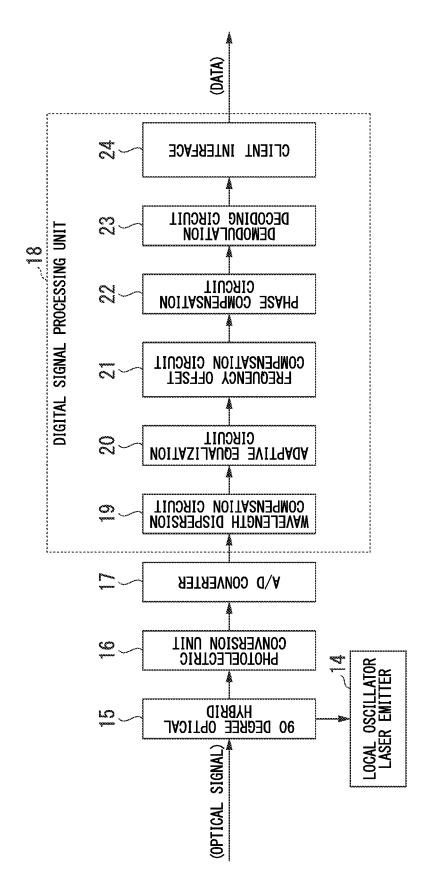

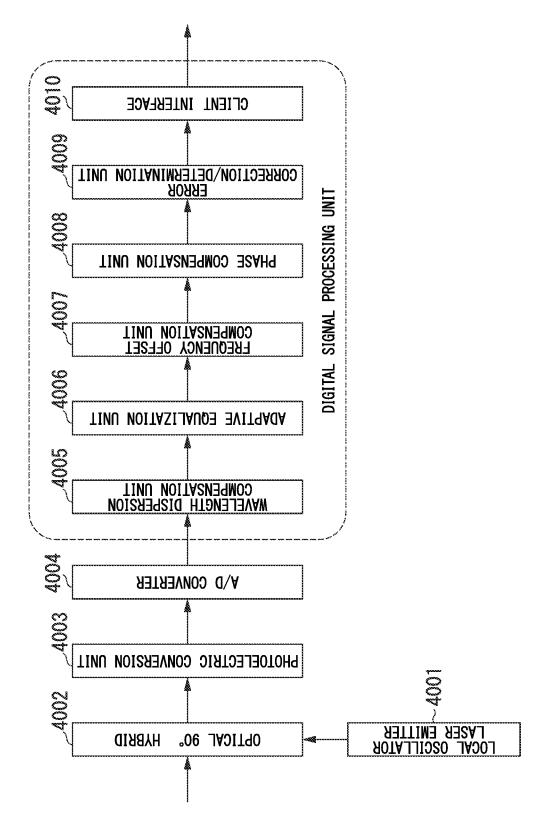

[0109] FIG. 9 is a block diagram showing an example of the structure of the optical signal receiver device 13 according to the present embodiment. The optical signal receiver device 13 acquires data that has been converted into an optical signal by the optical signal transmission device 11 from optical signals that it receives via the transmission path 12. The optical signal receiver device 13 is provided with a local oscillator laser emitter 14, an optical 90 degree hybrid 15, a photoelectric converter 16, an analog/digital converter (i.e., an A/D converter) 17, and a digital signal processing unit 18.

[0110] The optical signals input into the optical signal receiver device 13 are mixed with a local oscillation laser output by the local oscillator laser emitter 14 in the optical 90 degree hybrid 15 so as to form a homodyne detection wave or a heterodyne detection wave. The optical signal obtained from this detection wave is then converted into four-lane baseband analog electrical signals in the photoelectric conversion unit 16. These analog electrical signals are then digitalized in the A/D converter 17, and are then output to the digital signal processing unit 18 as two-lane (X-polarization and Y-polarization) complex digital signals. The digital signal processing unit 18 firstly performs linear waveform distortion compensation, and then performs demodulation decoding on the X-polarization and Y-polarization complex digital signals. The digital signal processing unit 18 then outputs the data obtained by this demodulation decoding to devices and the like that are connected downstream from it.

[0111] The digital signal processing unit 18 has a wavelength dispersion compensation circuit 19, an adaptive equalization circuit 20, a frequency offset compensation circuit 21,

a phase compensation circuit 22, a demodulation decoding circuit 23, and a client interface 24. The X-polarization and Y-polarization complex digital signals (i.e., reception signals) input into the digital signal processing unit 18 are linearly mixed by the effects of the rotation of the polarization state in the transmission path 12 and the like.

[0112] The wavelength dispersion compensation circuit 19 uses wavelength dispersion to compensate linear waveform distortion in the X-polarization and Y-polarization complex digital signals that are input into the digital signal processing unit 18. The adaptive equalization circuit 20 compensates signals distorted on the transmission path by linear polarization crosstalk and polarization mode dispersion (PMD) in the X-polarization and Y-polarization complex digital signals whose wavelength dispersion has been compensated by the wavelength dispersion compensation circuit 19.

[0113] The frequency offset compensation circuit 21 compensates the effects from frequency offset that occurs between the optical signal receiving device and the optical signal transmitting device in the X-polarization and Y-polarization complex digital signals whose distortion has been compensated by the adaptive equalization circuit 20. This frequency offset, for example, is caused by the frequency shift in the local oscillation lasers used by the optical signal transmitting device 11 and the optical signal receiver device 13. The phase compensation circuit 22 performs phase cycle slip compensation on the X-polarization and Y-polarization complex digital signals in which the frequency offset has been compensated by the frequency offset compensation circuit 21

[0114] The demodulation decoding circuit 23 performs demodulation that corresponds to the modulation format used in the optical signal transmitting device 11 and also performs error correction decoding on the X-polarization and Y-polarization complex digital signals in which the phase cycle slip has been compensated by the phase compensation circuit 22. The demodulation decoding circuit 23 then outputs the data obtained by this demodulation and error correction decoding to the client interface 24. The client interface 24 converts data input from the demodulation decoding circuit 23 in accordance with the signal format and frame structure that are used in devices connected downstream from the digital signal processing unit 18, and then outputs the converted data.

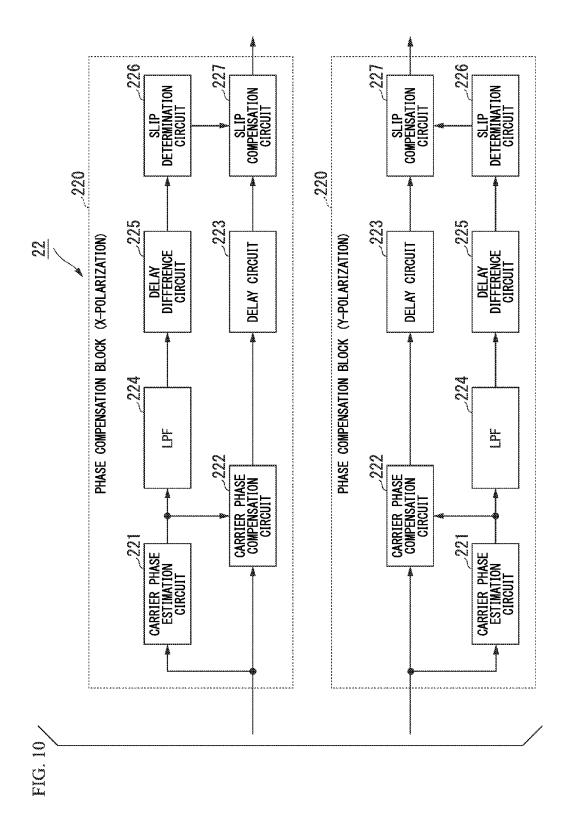

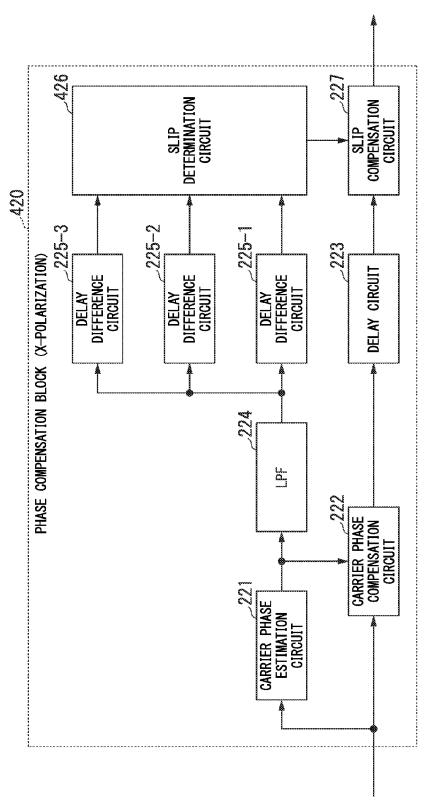

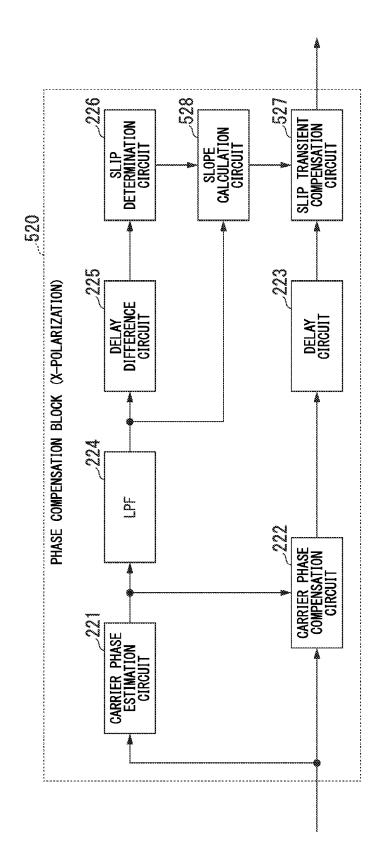

[0115] FIG. 10 is a block diagram showing an example of the structure of the phase compensation circuit 22 according to the present embodiment. The phase compensation circuit 22 has a phase compensation block 220 for X-polarization, and a phase compensation block 220 for Y-polarization. In the following description, the phase compensation block 220 for X-polarization will be described, and a description of the phase compensation block 220 for Y-polarization which has the same structure is omitted.

[0116] The phase compensation block 220 has a carrier phase estimation circuit 221, a carrier phase compensation circuit 222, a delay circuit 223, a low-pass filter (LPF) 224, a delay difference circuit 225, a slip determination circuit 226, and a slip compensation circuit 227. X-polarization complex digital signals are input into the phase compensation block 220.

[0117] The carrier phase estimation circuit 221 performs either feed-forward carrier phase error estimation such as is described in Non-patent document 1, or feedback carrier phase error estimation such as is described in Reference document 1 (Reference document 1: T. Kobayashi et al, "160-

Gb/s Polarization-Multiplexed 16-QAM long-haul transmission over 3,123 km using digital coherent receiver with digital PLL based frequency offset compensator", OTuD1 OFC/NFOEC2010).

[0118] The carrier phase estimation circuit 221 estimates phase differences that are caused by local oscillation lasers in the optical signal transmission device 11 and the optical signal receiver device 13. Because this phase difference changes temporally, the carrier phase estimation circuit 221 continuously performs carrier phase estimation, and this estimation tracks the changes in the phase difference. For example, when OPSK is used for the modulation format, feed-forward carrier phase estimation is performed based on the four squares method. When BPSK is used for the modulation format, carrier phase estimation is performed based on the two squares method, and when m-QAM is used for the modulation format, carrier phase estimation is performed based on the maximum likelihood (ML) method. Namely, in the carrier phase estimation circuit 221, a phase estimation method that is appropriate to the modulation format is used.

[0119] Moreover, the carrier phase estimation circuit 221 also estimates phase errors contained in the X-polarization complex digital signals. The carrier phase estimation circuit 221 outputs estimation error phases, which are the phase errors it has estimated, to the carrier phase compensation circuit 222 and the low-pass filter 224.

[0120] Based on the estimation error phases output from the carrier phase estimation circuit 221, the carrier phase compensation circuit 222 performs compensation on phase errors contained in the X-polarization complex digital signals. The carrier phase compensation circuit 222 outputs X-polarization complex digital signals in which the phase errors have been compensated to the delay circuit 223. Note that phase errors are phases from among the complex digital signal phases that are not dependent on modulation components. They are generated, for example, by phase differences between the optical signal transmission device 11, the optical signal receiver device 13, and the local oscillation laser, and by the non-linearity and the like of the transmission path.

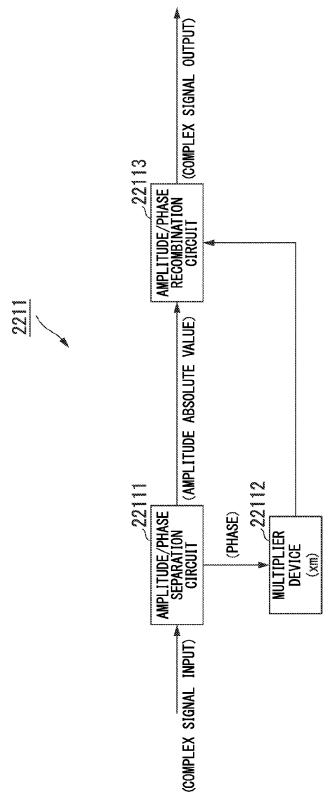

[0121] FIG. 11 is a block diagram showing an example of the structure of the carrier phase estimation circuit 221. As is shown in FIG. 11, the carrier phase estimation circuit 221 has a feed-forward type of structure. The carrier phase estimation circuit 221 has a phase-m multiplier circuit 2211, a K symbol averaging circuit 2212, a phase extraction circuit 2213, and a phase continuity circuit 2214. The phase-m multiplier circuit 2211 performs m-multiplication on phase components of the input complex signals that include phase errors. If QPSK is used as the modulation format, then m=4, if BPSK is used as the modulation format, then m=2. Because the signal components degenerate to a uniform value as a result of the phase components undergoing m-multiplication, the phase of output signals from the phase m-multiplier circuit 2211 contain only phase errors. The output from the phase m-multiplier circuit 2211 is input into the K symbol averaging circuit 2212. [0122] FIG. 12 is a block diagram showing an example of the structure of the phase m-multiplier circuit 2211 according to the present embodiment. The phase m-multiplier circuit 2211 has an amplitude/phase separation circuit 22111, a multiplier 22112, and an amplitude/phase recombination circuit 22113. Signals input into the phase m-multiplier circuit 2211 are separated into phase components and amplitude compo-

nents by the amplitude/phase separation circuit 22111. The

phase components separated by the amplitude/phase separa-

tion circuit 22111 are multiplied m-times by the multiplier circuit 22112. The phase components that are multiplied m-times by the multiplier circuit 22112 and the amplitude components that are separated by the amplitude/phase separation circuit 22111 are reconstructed into a complex signal by the amplitude/phase recombination circuit 22113, and are then output.

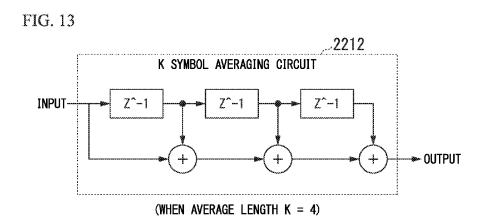

[0123] FIG. 13 is a block diagram showing an example of the structure of the K symbol averaging circuit 2212. As is shown in FIG. 13, the K symbol averaging circuit 2212 is formed as a tap length K limited impulse response filter. In FIG. 13, an example of the structure of a K symbol averaging circuit 2212 in which the average length K=4 is shown.

[0124] Returning to FIG. 11, the description of the structure of the carrier phase estimation circuit 221 will now be continued.

[0125] The output from the K symbol averaging circuit 2212 is input into the phase extraction circuit 2213. The phase extraction circuit 2213 removes phase components of input signals which are complex numbers and outputs these. The output from the phase extraction circuit 2213 has a value of, for example,  $2\pi$  the diameter of a radian of  $\pi \sim +\pi$ . At this time, when the phase changes beyond a point of  $\pm \pi$ , the output is discontinuous. Because of this, ideally, the range of the phase that can be extracted by the phase continuity circuit 2214 is increased to ±infinity (in reality, to a sufficiently large range), and phase discontinuities are removed therefrom. A variety of methods have been proposed historically for the phase continuation algorithm, and the method disclosed, for example, in Reference document 2 can be used (Reference document 2: Kazuyoshi Itoh et al, APPLIED OPTICS/Vol. 21, No. 14/15 July 1982). Signals from which phase discontinuities have been removed by the phase continuity circuit 2214 are output as estimation error phases, which serve as the output from the carrier phase estimation circuit 221.

[0126] Returning to FIG. 10, the description of the phase compensation block 220 will now be continued.

[0127] The delay circuit 223 attaches a delay to the times (i.e., the number of symbols) required for the signal processing by the low-pass filter 224, the delay difference circuit 225, and the slip determination circuit 226 of the complex digital signals output from the carrier phase compensation circuit 222, and then outputs them to the slip compensation circuit 227. Namely, the delay circuit 223 attaches a delay such that the timing at which the complex digital signals output from the carrier phase compensation circuit 222 are input into the slip compensation circuit 227 matches the timing at which the determination results from the slip determination circuit 226 for these same complex digital signals are input into the slip compensation circuit 227. The delay circuit 223 can be constructed using, for example, a shift register. In this case, a single shift delay amount is taken as the time for a single symbol.

[0128] The low-pass filter 224 smoothes out changes in the estimation error phases output by the carrier phase estimation circuit 221, removes high-frequency components from these estimation error phases, and then outputs the result to the delay difference circuit 225. The delay difference circuit 225 outputs signals that are proportional to the temporal changes in the estimation error phases that have been smoothed out by the low-pass filter 224.

[0129] The signals output by the delay difference circuit 225 are signals that show a delay difference value d. The delay difference value d is calculated using the following Formula

(3) by monitoring for N number of symbols estimation error phases  $(\phi(T))$  that change over time. The delay difference circuit 225 outputs to the slip determination circuit 226 a signal showing the calculated delay difference value d. In Formula (3), n is the symbol number and is a natural number, T is the symbol time interval.

$$d = \phi(nT) - \phi((n-N)T) \tag{3}$$

[0130] FIG. 14 is a block diagram showing an example of the structure of the delay difference circuit 225 according to the present embodiment. The delay difference circuit 225 has an N symbol delay device 2251, a multiplier device 2252, and an adding device 2253. The smoothed estimation error phases  $(\phi(n\,T))$  in the low-pass filter 224 are input into the N symbol delay device 2251 and the adding device 2253. The N symbol delay device 2251 outputs the N symbol number of prior estimation error phases  $(\phi((n-N)\,T))$ . The N symbol delay device 2251 can be constructed using, for example, a shift register. In this case, a single shift delay amount corresponds to the time for a single symbol, and the range to be stored is approximately five times the filter tap length K in the K symbol averaging circuit 2212.

[0131] The multiplier device 2252 multiplies (-1) by the N symbol number of prior estimation error phases that are output from the N symbol delay device 2251, and outputs the result to the adding device 2253. The adding device 2253 adds together the estimation error phases output from the low-pass filter 24 and the values output from the multiplier device 2252. Namely, the adding device 2253 performs the operation given in Formula (3), and outputs the operation result as the delay difference value d.

[0132] N (i.e., the number of delay symbols) in the N symbol delay device 2251 is set in advance within a range of approximately 1 through 5 times the average value of the tap number of the filter in the K symbol averaging circuit 2212. N is set to a value such that it is possible to detect a steep change in the estimation error phases, for example, such as is shown in FIG. 7, and such that it is difficult for incorrect detections that are caused by changes arising from oscillations and the like in the estimation error phases to occur. Signals output from the delay differential circuit 225 which has this type of structure show a quantity that is in proportion to the temporal slope (i.e., the amount of change in the slope per unit time) of the estimation error phases. The optimum value for N can be determined by means of a simulation or the like. For example, when the tap length K of the filter in the K symbol averaging circuit 2212 is 17, then it can be inferred by means of simulation or the like that the optimum value lies in the vicinity of N=50 which is approximately three times K.

[0133] Returning to FIG. 10, the description of the phase compensation block 220 will be continued.

[0134] The slip determination circuit 226 compares the delay difference value d that is output from the delay difference circuit 225 with a previously set detection threshold value, and determines whether or not a phase cycle slip has occurred, and if a phase cycle slip has occurred, determines the direction thereof. As is shown in FIG. 7, if a steep change is generated in the estimation phase error, the absolute value of the delay difference value d increases. This determination of whether or not a phase cycle slip has occurred is performed based on whether or not d is continuously in excess of the threshold value over approximately L number of symbols. Here, L is a value that corresponds to a delay value N of the aforementioned delay difference circuit 225, and is set to a

value that satisfies 0<L<N. For example, L may be set to approximately 60% of N(N×0.6). The slip determination circuit **226** outputs to the slip compensation circuit **227** a slip determination signal that shows the determination result as to whether or not a phase cycle slip has occurred, and when a phase cycle slip has occurred, it also shows the rotation direction thereof.

[0135] The detection threshold value for the delay difference value d varies depending on the modulation format. For example, when a QPSK format or QAM format is used, a value of approximately 1 radian is used. However, in actuality, in accordance with conditions such as the amount of phase noise and the like, it is appropriate to set a detection threshold value that minimizes the frequency of occurrence of phase cycle slip remaining in the complex digital signal (i.e., the remaining slip frequency) output by the phase compensation block 220. The frequency of occurrence of phase cycle slip is calculated, for example, by (number of times phase cycle slip has occurred)/(number of transmission symbols).

[0136] The detection threshold value for the delay difference value d is set, for example, based on simulations and measurement results. Note that for a modulation format where the phase difference between symbols in a constellation such as QPSK or QAM is  $(\pi/2)$  radians, the range where the most suitable value can be obtained is a range from 0 radians to  $(\pi/2)$  radians. For an m-PSK modulation format, the range is from 0 radians to  $(2\pi/m)$  radians.

[0137] Moreover, in cases such as when frequency offset that is generated by the difference between the local oscillation laser in the optical signal transmission device 11 and the local oscillation laser in the optical signal receiver device 13 is present, and this frequency offset cannot be adequately compensated by the frequency offset compensation circuit 21, then it is desirable for the detection threshold value to be altered in accordance with the remaining frequency offset.

[0138] Slip determination signals output from the slip determination circuit 226 and complex digital signals output from the delay circuit 223 are input into the slip compensation circuit 227. Based on the phase compensation amount which is switched in accordance with the slip determination signal, the slip compensation circuit 227 compensates the phase of the complex digital signal. When the modulation format is a QPSK format or a QAM format, the phase compensation amount of the slip compensation circuit 227 may be any of 0°, 90°, 180°, and 270°. The initial value for the phase compensation amount may be, for example, 0°, and the phase compensation amount is switched in either a positive rotation or a negative rotation in 90° units in accordance with the slip determination signal. Here, a positive rotation is a rotation in which the phase increases, while a negative rotation is a rotation in which the phase decreases.

[0139] Specifically, when the slip determination signal indicates that a phase cycle slip in a positive rotation direction has occurred, updating to switch the phase compensation amount to a value obtained by subtracting  $90^{\circ}$  from the current phase compensation amount is performed. Moreover, when the slip determination signal indicates that a phase cycle slip in a negative rotation direction has occurred, updating to switch the phase compensation amount to a value obtained by adding  $90^{\circ}$  to the current phase compensation amount is performed.

[0140] When m-PSK is used for the modulation format, the switching of the phase compensation amount for the complex digital signal is performed in (360°/m) units. In addition, the

phase compensation amount that is switched in accordance with the slip determination signal is maintained until the next phase cycle slip occurrence is detected. The slip compensation circuit 227 constantly performs the compensating of the phase using phase compensation amounts switched by the slip determination signal for the complex digital signals output from the delay circuit 223.

[0141] FIG. 15 is a flowchart showing the slip determination processing performed by the slip determination circuit 226 according to the present embodiment. When the processing is started, the slip determination circuit 226 receives an input of the delay difference value d output by the delay difference circuit 225 (step S101).

[0142] The slip determination circuit 226 then determines whether or not the absolute value of the input delay difference value d is greater than a predetermined detection threshold value Th (step S102).

[0143] If the absolute value is not greater than the detection threshold value Th (step S102: NO), the slip determination circuit 226 initializes by substituting 0 for the parameters p and q (step S103), and returns the processing to step S101. The parameter p is a parameter used for counting the number of symbols that the delay difference value d continuously exceeds the detection threshold Th in the positive rotation direction. The parameter q is a parameter used for counting the number of symbols that the delay difference value d continuously exceeds the detection threshold Th in the negative rotation direction.

[0144] If, on the other hand, the absolute value is larger than the detection threshold value Th (step S102: YES), the slip determination circuit 226 determines whether or not the delay difference value d is larger than 0 (step S104).

[0145] If the delay difference value d is not larger than 0 (step S104: NO), the slip determination circuit 226 increases the parameter q by 1 (step S105), and determines whether or not the parameter q has exceeded a determination threshold value L (step S106).

[0146] The determination threshold value L is determined in advance so as to correspond to the delay value N of the delay difference circuit 225, as is described above, and may be set, for example, to a value of approximately 60 percent of  $N(N\times0.6)$ . Note that the determination threshold value L may also be determined in accordance with the level of dispersion of the delay difference value d, or in accordance with the time interval between symbols or the like, or it may be determined based on simulations and measurement values such that phase cycle slip incorrect detections are not more than a predetermined value.

[0147] If the value of the parameter q does not exceed the determination threshold value L (step S106: NO), the slip determination circuit 226 returns the processing to step S101.

[0148] If the value of the parameter q does exceed the determination threshold value L (step S106: YES), the slip determination circuit 226 determines that a phase cycle slip has occurred in the negative rotation direction, and outputs to the slip compensation circuit 227 a slip determination signal indicating that a phase cycle slip in the negative rotation direction has occurred (step S107). It then returns the processing to step S101.

[0149] If, in step S104, it is determined that the delay difference value d is greater than 0 (step S104: YES), the slip determination circuit 226 increases the parameter p by 1 (step S108), and determines whether or not the parameter p exceeds the predetermined threshold value L (step S109).

[0150] If the value of the parameter p does not exceed the determination threshold value L (step S109: NO), the slip determination circuit 226 returns the processing to step S101.

[0151] If the value of the parameter p does exceed the determination threshold value L (step S109: YES), the slip determination circuit 226 determines that a phase cycle slip in the positive rotation direction has occurred, and outputs to the slip compensation circuit 227 a slip determination signal indicating that a phase cycle slip in the positive rotation direction has occurred (step S110). It then returns the processing to step S101.

[0152] As is described above, when the absolute value of the delay difference value d continuously exceeds the detection threshold value Th over L number of symbols, namely, when the delay difference value d has changed markedly, the slip determination circuit 226 determines that a phase cycle slip has occurred. At this time, the slip determination circuit 226 determines that a positive rotation phase cycle slip has occurred when the delay difference value d exceeds a detection threshold value Th having a positive value (i.e., Th>0; an upper-side detection threshold value). Moreover, the slip determination circuit 226 determines that a negative rotation phase cycle slip has occurred when the delay difference value d exceeds a detection threshold value Th having a negative value (i.e., -Th; a lower-side detection threshold value).

[0153] The slip compensation circuit 227 switches the phase compensation amount based on the slip determination signal indicating the determination result made by the slip determination circuit 226, and performs compensation on the complex digital signal output from the delay circuit 223.

[0154] A time lag is generated between when the phase cycle slip occurred and when it is detected by the slip determination circuit 226 and the phase compensation amount is switched by the slip compensation circuit 227. This time lag is the processing time required by the low-pass filter 224, the delay difference circuit 225, the slip determination circuit 226, and the slip compensation circuit 227. The delay circuit 223 compensates this time lag. As a consequence, compensation of the phase cycle slip based on the phase compensation amount that corresponds to the slip determination signal is performed by the slip compensation circuit 227 for the complex digital signals output from the carrier phase compensation circuit 222.

[0155] In this way, by monitoring the output from the carrier phase estimation circuit 221 in the phase compensation circuit 22, without using redundant signals such as pilot symbols and the like, it is possible to immediately detect and correct phase cycle slips that have occurred. As a consequence of this, it is possible to suppress the effective frequency of occurrence of phase cycle slips, and coherent optical communication utilizing absolute phases becomes possible, at the same time as signal redundancy using pilot symbols and the like is kept to a minimum. Note that this redundancy is calculated, for example, by means of (number of pilot symbols per unit time)/(total number of transmitted symbols per unit time).

[0156] Moreover, by providing the low-pass filter 224 in the phase compensation circuit 22 between the carrier phase estimation circuit 221 and the delay difference circuit 225, changes that are caused by fluctuations and noise in the estimation error phases are smoothed out. As a consequence, it is possible to improve the accuracy of phase cycle slip detection that uses the delay difference value d.

[0157] The results when each circuit of the digital signal processing unit 18 according to the present embodiment was packaged on a computer, and the off-line demodulation of optical transmission test data was performed will now be shown. Here, the bit error rate and the symbol slip rate are evaluated. FIG. 16 is a schematic block diagram showing the structure of a test device used to acquire optical transmission test data. In FIG. 16, the block indicated by [off-line DSP] corresponds to the digital signal processing unit 18.

[0158] FIG. 17 is a graph showing the results when the off-line demodulation of the optical transmission test data obtained by the test device shown in FIG. 16 was performed. In FIG. 17, the horizontal axis shows the tap length in the carrier phase estimation circuit 221 and the K symbol averaging circuit 2212, while the vertical axis shows the bit error rate (BER) and the symbol slip rate (SlipRate). In FIG. 17 the results when phase cycle slip compensation according to the present embodiment was performed are shown, with the results when phase cycle slip compensation was not performed being shown as a comparative example. As is shown in FIG. 17, by performing phase cycle slip compensation, the frequency of occurrence of phase cycle slips downstream from the phase compensation circuit 22 can be suppressed to approximately ½0th. Moreover, even under severe conditions such as a bit error rate of  $2 \times 10^{-2}$ , the frequency of phase cycle slips can be limited to the  $10^{-6}$  band.

[0159] If the frequency of phase cycle slip occurrence is suppressed in this way, then because the effects of burst errors caused by phase cycle slips are limited to less than the tolerance threshold value for forward error correction using pilot signals having a redundancy of approximately 1%, it is possible to avoid differential coding. For example, the optical signal-to-noise ratio conditions needed obtain a bit error rate of  $1 \times 10^{-2}$  can be relaxed to approximately  $1.1 \sim 1.4$  decibels by avoiding differential coding.

#### Sixth Embodiment

[0160] In the slip determination circuit 226 according to the fifth embodiment, the detection threshold value used when detecting the occurrence of phase cycle slip was a fixed value. In the sixth embodiment, as a variant example of the fifth embodiment, a structure is described in which the detection threshold value is determined adaptively by changing the detection threshold value in accordance with the delay difference value d.

[0161] FIG. 18 is a block diagram showing the structure of a phase compensation block 320 according to the sixth embodiment. Here, the phase compensation block 320 corresponding to X-polarization is shown, however, the same phase compensation block 320 is also used for Y-polarization. [0162] The phase compensation block 320 according to the present embodiment has a carrier phase estimation circuit 221, a carrier phase compensation circuit 222, a delay circuit 223, a low-pass filter 224, a delay difference circuit 225, a slip determination circuit 326, a slip compensation circuit 227, and a threshold value calculation circuit 328. The phase compensation block 320 differs from the phase compensation block 220 according to the fifth embodiment (see FIG. 10) in that it has the slip determination circuit 326 instead of the slip determination circuit 226, and in that it has the threshold value calculation circuit 328. Note that in the phase compensation block 320, any structure that is the same as in the fifth embodiment is given the same descriptive symbols and a description thereof is omitted.