## (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2016/0333475 A1 Gomm et al.

(43) **Pub. Date:**

Nov. 17, 2016

### (54) SUBSTRATE PEDESTAL MODULE INCLUDING BACKSIDE GAS DELIVERY TUBE AND METHOD OF MAKING

(71) Applicant: Lam Research Corporation, Fremont, CA (US)

(72) Inventors: Troy Alan Gomm, Sherwood, OR (US); Nick Ray Linebarger, JR., Beaverton, OR (US)

(73) Assignee: LAM RESEARCH CORPORATION,

Fremont, CA (US)

(21) Appl. No.: 14/710,132

(22) Filed: May 12, 2015

#### **Publication Classification**

(51) **Int. Cl.** C23C 16/458 (2006.01)C23C 16/455 (2006.01)B32B 37/10 (2006.01)(2006.01)H01L 21/687 B32B 37/16 (2006.01)C23C 16/505 (2006.01)C23C 16/52 (2006.01)

#### (52) U.S. Cl.

CPC ....... C23C 16/4586 (2013.01); C23C 16/505 (2013.01); C23C 16/45544 (2013.01); C23C 16/45536 (2013.01); C23C 16/52 (2013.01); H01L 21/68742 (2013.01); H01L 21/68757 (2013.01); H01L 21/68785 (2013.01); B32B 37/16 (2013.01); B32B 37/10 (2013.01)

#### (57)**ABSTRACT**

A semiconductor substrate processing apparatus includes a vacuum chamber having a processing zone in which a semiconductor substrate may be processed, a process gas source in fluid communication with the vacuum chamber for supplying a process gas into the vacuum chamber, a showerhead module through which process gas from the process gas source is supplied to the processing zone of the vacuum chamber, and a substrate pedestal module. The substrate pedestal module includes a platen made of ceramic material having an upper surface configured to support a semiconductor substrate thereon during processing, a stem made of ceramic material having an upper stem flange that supports the platen, and a backside gas tube made of ceramic material that is located in an interior of the stem. The backside gas tube includes an upper gas tube flange that is located between a lower surface of the platen and an upper surface of the upper stem flange wherein the backside gas tube is in fluid communication with at least one backside gas passage of the platen and the backside gas tube is configured to supply a backside gas to a region below a lower surface of a semiconductor substrate that is to be supported on the upper surface of the platen during processing.

### SUBSTRATE PEDESTAL MODULE INCLUDING BACKSIDE GAS DELIVERY TUBE AND METHOD OF MAKING

#### FIELD OF THE INVENTION

[0001] This invention pertains to semiconductor substrate processing apparatuses for processing semiconductor substrates, and may find particular use in plasma-enhanced chemical vapor depositions processing apparatuses operable to deposit thin films.

### **BACKGROUND**

[0002] Semiconductor substrate processing apparatuses are used to process semiconductor substrates by techniques including etching, physical vapor deposition (PVD), chemical vapor deposition (PECVD), plasma-enhanced chemical vapor deposition (PECVD), atomic layer deposition (ALD), plasma-enhanced atomic layer deposition (PEALD), pulsed deposition layer (PDL), plasma-enhanced pulsed deposition layer (PEPDL), and resist removal. One type of semiconductor substrate processing apparatus is a plasma processing apparatus that includes a reaction chamber containing upper and lower electrodes wherein a radio frequency (RF) power is applied between the electrodes to excite a process gas into plasma for processing semiconductor substrates in the reaction chamber.

#### **SUMMARY**

[0003] Disclosed herein is a semiconductor substrate processing apparatus for processing semiconductor substrates. The semiconductor substrate processing apparatus comprises a vacuum chamber including a processing zone in which a semiconductor substrate may be processed, a process gas source in fluid communication with the vacuum chamber for supplying a process gas into the vacuum chamber, a showerhead module through which process gas from the process gas source is supplied to the processing zone of the vacuum chamber, and a substrate pedestal module. The substrate pedestal module includes a platen made of ceramic material having an upper surface configured to support a semiconductor substrate thereon during processing, a stem made of ceramic material having an upper stem flange that supports the platen, and a backside gas tube made of ceramic material that is located in an interior of the stem. The backside gas tube includes an upper gas tube flange that is located between a lower surface of the platen and an upper surface of the upper stem flange wherein the backside gas tube is in fluid communication with at least one backside gas passage of the platen and the backside gas tube is configured to supply a backside gas to a region below a lower surface of a semiconductor substrate that is to be supported on the upper surface of the platen during process-

[0004] Also disclosed herein is a substrate pedestal module of a semiconductor substrate processing apparatus. The substrate pedestal module comprises a platen having an upper surface configured to support a semiconductor substrate thereon during processing, a stem having an upper stem flange that supports the platen, and a backside gas tube that is located in an interior of the stem. The backside gas tube includes an upper gas tube flange that is located between a lower surface of the platen and an upper surface of the upper stem flange wherein the backside gas tube is in

fluid communication with at least one backside gas passage of the platen and the backside gas tube is configured to supply a backside gas to a region below a lower surface of a semiconductor substrate that is to be supported on the upper surface of the platen during processing.

[0005] Further disclosed herein is a method of making a substrate pedestal module of a semiconductor substrate processing apparatus. The method of making the substrate pedestal module includes positioning an upper ceramic surface of an upper gas tube flange against a lower ceramic surface of a platen, and diffusion bonding the upper ceramic surface of the upper gas tube flange to the lower ceramic surface of the platen so as to form a vacuum seal.

# BRIEF DESCRIPTION OF THE DRAWING FIGURES

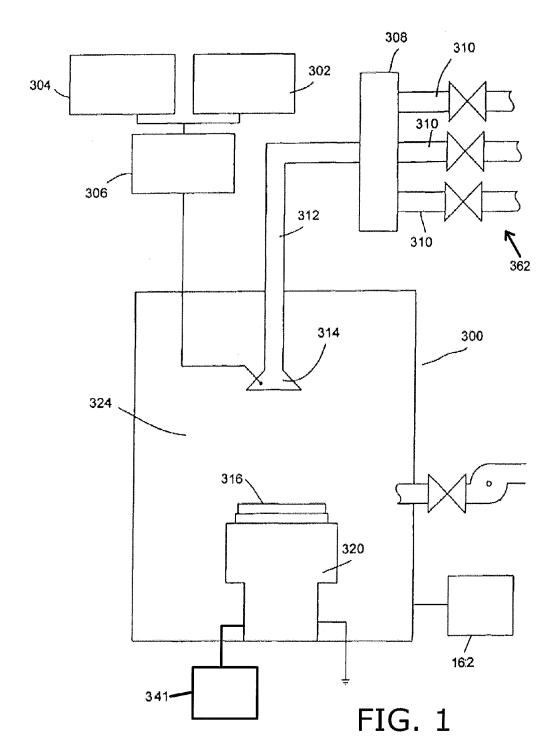

[0006] FIG. 1 illustrates a schematic diagram showing an overview of a chemical deposition apparatus in accordance with embodiments disclosed herein.

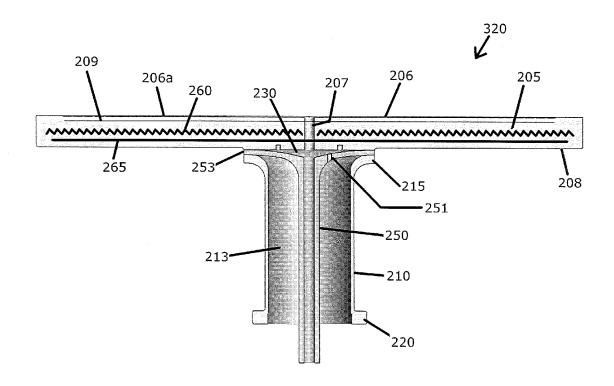

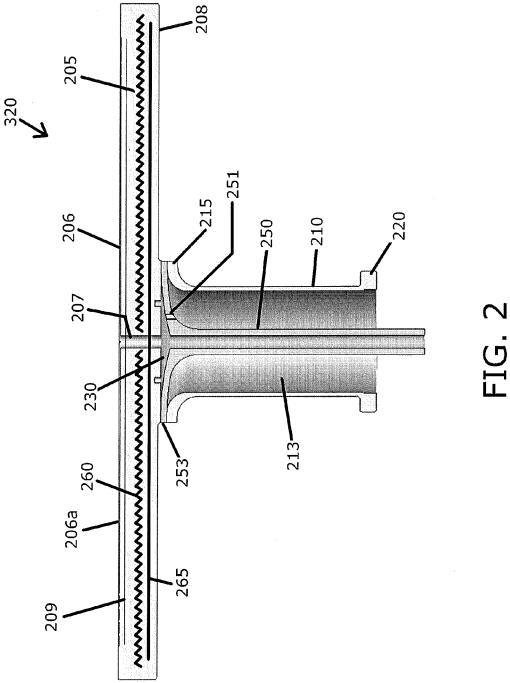

[0007] FIG. 2 shows a cross section of a substrate pedestal module in accordance with an embodiment as disclosed herein

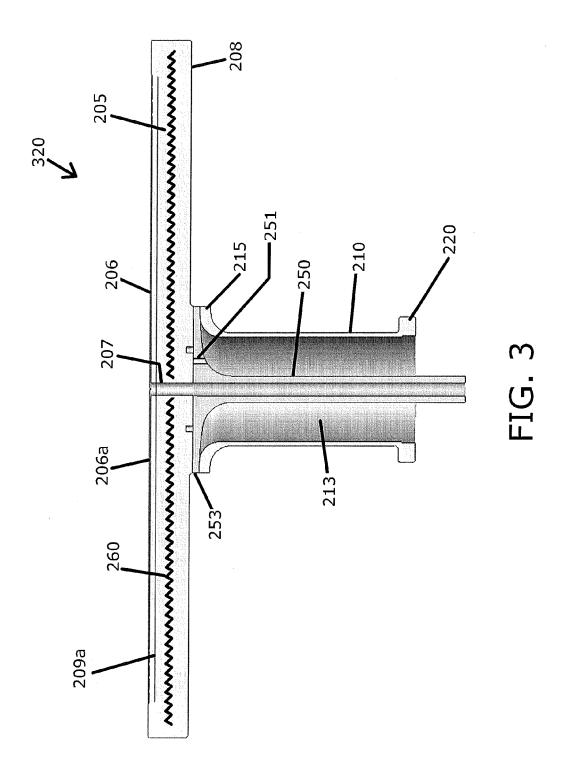

[0008] FIG. 3 illustrates a cross section of a substrate pedestal module in accordance with an embodiment as disclosed herein.

### DETAILED DESCRIPTION

[0009] In the following detailed description, numerous specific embodiments are set forth in order to provide a thorough understanding of the apparatus and methods disclosed herein. However, as will be apparent to those skilled in the art, the present embodiments may be practiced without these specific details or by using alternate elements or processes. In other instances, well-known processes, procedures, and/or components have not been described in detail so as not to unnecessarily obscure aspects of embodiments disclosed herein. As used herein the term "about" refers to ±10%.

[0010] As indicated, present embodiments provide apparatus and associated methods for processing a semiconductor substrate in a semiconductor substrate processing apparatus such as a chemical vapor deposition apparatus or a plasma-enhanced chemical vapor deposition apparatus. The apparatus and methods are particularly applicable for use in conjunction with high temperature processing of semiconductor substrates such as a high temperature deposition processes wherein a semiconductor substrate being processed is heated to temperatures greater than about 550° C., such as about 550° C. to about 650° C. or more.

[0011] Embodiments disclosed herein are preferably implemented in a plasma-enhanced chemical deposition apparatus (i.e. PECVD apparatus, PEALD apparatus, or PEPDL apparatus), however, they are not so limited. FIG. 1 provides a simple block diagram depicting various semiconductor substrate plasma processing apparatus components arranged for implementing embodiments as disclosed herein. As shown, a semiconductor substrate plasma processing apparatus 300 includes a vacuum chamber 324 that serves to contain plasma in a processing zone, which is generated by a capacitor type system including a showerhead module 314 having an upper RF electrode (not shown) therein working in conjunction with a substrate pedestal module 320 having a lower RF electrode (not shown)

therein. At least one RF generator is operable to supply RF energy into a processing zone above an upper surface of a semiconductor substrate 316 in the vacuum chamber 324 to energize process gas supplied into the processing zone of the vacuum chamber 324 into plasma such that a plasma deposition process may be performed in the vacuum chamber 324. For example, a high-frequency RF generator 302 and a low-frequency RF generator 304 may each be connected to a matching network 306, which is connected to the upper RF electrode of the showerhead module 314 such that RF energy may be supplied to the processing zone above the semiconductor substrate 316 in the vacuum chamber 324.

[0012] The power and frequency of RF energy supplied by matching network 306 to the interior of the vacuum chamber 324 is sufficient to generate plasma from the process gas. In an embodiment both the high-frequency RF generator 302 and the low-frequency RF generator 304 are used, and in an alternate embodiment, just the high-frequency RF generator 302 is used. In a process, the high-frequency RF generator 302 may be operated at frequencies of about 2-100 MHz; in a preferred embodiment at 13.56 MHz or 27 MHz. The low-frequency RF generator 304 may be operated at about 50 kHz to 2 MHz; in a preferred embodiment at about 350 to 600 kHz. The process parameters may be scaled based on the chamber volume, substrate size, and other factors. Similarly, the flow rates of process gas, may depend on the free volume of the vacuum chamber or processing zone.

[0013] An upper surface of the substrate pedestal module 320 supports a semiconductor substrate 316 during processing within the vacuum chamber 324. The substrate pedestal module 320 can include a chuck to hold the semiconductor substrate and/or lift pins to raise and lower the semiconductor substrate before, during and/or after the deposition and/or plasma treatment processes. In an alternate embodiment, the substrate pedestal module 320 can include a carrier ring to raise and lower the semiconductor substrate before, during and/or after the deposition and/or plasma treatment processes. The chuck may be an electrostatic chuck, a mechanical chuck, or various other types of chuck as are available for use in the industry and/or research. Details of a lift pin assembly for a substrate pedestal module including an electrostatic chuck can be found in commonly-assigned U.S. Pat. No. 8,840,754, which is incorporated herein by reference in its entirety. Details of a carrier ring for a substrate pedestal module can be found in commonlyassigned U.S. Pat. No. 6,860,965, which is incorporated herein by reference in its entirety. A backside gas supply 341 is operable to supply a heat transfer gas or purge gas through the substrate pedestal module 320 to a region below a lower surface of the semiconductor substrate during processing. The substrate pedestal module 320 includes the lower RF electrode therein wherein the lower RF electrode is preferably grounded during processing, however in an alternate embodiment, the lower RF electrode may be supplied with RF energy during processing.

[0014] To process a semiconductor substrate in the vacuum chamber 324 of the semiconductor substrate plasma processing apparatus 300, process gases are introduced from a process gas source 362 into the vacuum chamber 324 via inlet 312 and showerhead module 314 wherein the process gas is formed into plasma with RF energy such that a film may be deposited onto the upper surface of the semiconductor substrate. In an embodiment, multiple source gas lines 310 may be connected to a heated manifold 308. The

gases may be premixed or supplied separately to the chamber. Appropriate valving and mass flow control mechanisms are employed to ensure that the correct gases are delivered through the showerhead module 314 during semiconductor substrate processing. During the processing, a backside heat transfer gas or purge gas is supplied to a region below a lower surface of the semiconductor substrate supported on the substrate pedestal module 320. Preferably, the processing is at least one of chemical vapor deposition processing, plasma-enhanced chemical vapor deposition processing, atomic layer deposition processing, plasma-enhanced atomic layer deposition processing, pulsed deposition layer processing, or plasma-enhanced pulsed deposition layer processing.

[0015] In certain embodiments, a system controller 162 is employed to control process conditions during deposition, post deposition treatments, and/or other process operations. The controller 162 will typically include one or more memory devices and one or more processors. The processor may include a CPU or computer, analog and/or digital input/output connections, stepper motor controller boards, etc.

[0016] In certain embodiments, the controller 162 controls all of the activities of the apparatus. The system controller 162 executes system control software including sets of instructions for controlling the timing of the processing operations, frequency and power of operations of the low-frequency RF generator 304 and the high-frequency RF generator 302, flow rates and temperatures of precursors and inert gases and their relative mixing, temperature of a semiconductor substrate 316 supported on an upper surface of the substrate pedestal module 320 and a plasma exposed surface of the showerhead module 314, pressure of the vacuum chamber 324, and other parameters of a particular process. Other computer programs stored on memory devices associated with the controller may be employed in some embodiments.

[0017] Typically there will be a user interface associated with controller 162. The user interface may include a display screen, graphical software displays of the apparatus and/or process conditions, and user input devices such as pointing devices, keyboards, touch screens, microphones, etc.

[0018] A non-transitory computer machine-readable medium can comprise program instructions for control of the apparatus. The computer program code for controlling the processing operations can be written in any conventional computer readable programming language: for example, assembly language, C, C++, Pascal, Fortran or others. Compiled object code or script is executed by the processor to perform the tasks identified in the program.

[0019] The controller parameters relate to process conditions such as, for example, timing of the processing steps, flow rates and temperatures of precursors and inert gases, temperature of the semiconductor substrate, pressure of the chamber and other parameters of a particular process. These parameters are provided to the user in the form of a recipe, and may be entered utilizing the user interface.

[0020] Signals for monitoring the process may be provided by analog and/or digital input connections of the system controller. The signals for controlling the process are output on the analog and digital output connections of the apparatus.

[0021] The system software may be designed or configured in many different ways. For example, various chamber

component subroutines or control objects may be written to control operation of the chamber components necessary to carry out deposition processes. Examples of programs or sections of programs for this purpose include substrate timing of the processing steps code, flow rates and temperatures of precursors and inert gases code, and a code for pressure of the vacuum chamber 324.

[0022] FIGS. 2 and 3 illustrate cross sections of a substrate pedestal module 320 according to embodiments as disclosed herein. As shown in FIGS. 2 and 3, the substrate pedestal module 320 includes a platen 205 made of ceramic material having an upper surface 206 that supports a semiconductor substrate thereon during processing of the semiconductor substrate. A stem 210 made of ceramic material extends downwardly from a lower surface 208 of the platen 205 wherein the stem 210 includes an upper stem flange 215 that supports the platen 205 and a lower stem flange 220 that may be attached to a base or adapter (not shown) such that the substrate pedestal module 320 may be supported in a vacuum chamber of a semiconductor substrate processing apparatus. By making the substrate pedestal module 320 from ceramic materials rather than a metal material, such as aluminum or an aluminum alloy, the substrate pedestal module 320 may withstand high temperatures achieved during high temperature substrate processing, such as temperatures greater than about 550° C. or temperatures greater than about 650° C.

[0023] The substrate pedestal module 320 includes a backside gas tube 250 made of ceramic that is located in an interior 213 of the stem 210. In an embodiment, the backside gas tube 250 is centrally located in the interior 213 of the stem 210. In an alternate embodiment, the backside gas tube 250 is located off-center in the interior of the stem 210. The backside gas tube 250 includes an upper gas tube flange 253 that is located between a lower surface 208 of the platen 205 and an upper surface of the upper stem flange 215. The backside gas tube 250 is in fluid communication with at least one backside gas passage 207 of the platen 205 such that a backside gas may be supplied through the backside gas tube 250 and the backside gas passage 207 to a region below a lower surface of a semiconductor substrate that is supported on the upper surface 206 of the platen 205 during processing. In an embodiment, an outer diameter of the upper stem flange 215 and an outer diameter of the upper gas tube flange 253 can be equal to or about equal to an outer diameter of the platen 205. Preferably, the outer diameter of the upper stem flange 215 and an outer diameter of the upper gas tube flange 253 are less than the outer diameter of the platen 205. The outer diameter of the upper stem flange 215, the outer diameter of the upper gas tube flange 253 and the outer diameter of the stem 210, as well as the thickness of the stem 210 wall are selected such that the interior 213 of the stem 210, which is maintained at atmospheric pressure during processing, can accommodate electrical connections that are disposed in the interior 213 thereof as well as withstand the pressure differential between the vacuum pressure surrounding the stem 210 and the atmospheric pressure in the interior 213 of the stem 210. Preferably, an outer periphery of the upper gas tube flange 253 is located on a radius no greater than 1/4 the outer diameter of the platen 205.

[0024] The platen 205 can include at least one electrostatic clamping electrode 209 embedded therein wherein the at least one electrostatic clamping electrode 209 is operable to electrostatically clamp a semiconductor substrate on the

upper surface 206 of the platen 205 during processing. As shown in FIG. 2 the platen 205 can also include a lower RF electrode 265 that may be grounded or supplied with RF power during processing of a semiconductor substrate. Preferably, as shown in FIG. 3, the platen 205 includes only a single electrode 209a embedded therein that serves as both an electrostatic clamping electrode and a RF electrode. Referring back to FIGS. 2 and 3, the platen 205 can also include at least one heater 260 embedded therein that is operable to control the temperature across the upper surface 206 of the platen 205 and thereby the temperature across the semiconductor substrate during processing. The at least one heater 260 can include electrically resistive heater film and/or one or more thermoelectric modules. Preferably, electrical connections to the at least one electrostatic clamping electrode 209, the at least one heater 260, the single electrode 209a, and/or the lower RF electrode 265 that are disposed in the interior 213 of the stem 210 extend through respective openings 251 in the upper gas tube flange 253 such that the electrical connections may be respectively connected to electrical contacts (not shown) formed in the platen 205 that are in electrical communication with the respective at least one electrostatic clamping electrode 209, the at least one heater 260, the single electrode 209a and/or the lower RF electrode 265. In this manner, the at least one electrostatic clamping electrode 209, the at least one heater 260, the single electrode 209a, and/or the lower RF electrode 265 may be powered during processing of a semiconductor substrate.

[0025] In an embodiment, the platen 205 can include discrete layers that are diffusion bonded together wherein the at least one electrostatic clamping electrode 209, the lower RF electrode 265 (or the single electrode 209a), and the at least one heater 260 can be sandwiched between the discrete layers of the platen 205. The upper surface 206 of the platen 205 preferably includes a mesa pattern 206a formed therein wherein a lower surface of a semiconductor substrate is supported on the mesa pattern 206a and a backside purge gas or a backside heat transfer gas can be supplied to the region below the semiconductor substrate between the mesas of the mesa pattern 206a. An exemplary embodiment of a mesa pattern and method of forming a mesa pattern can be found in commonly assigned U.S. Pat. No. 7,869,184, which is hereby incorporated herein in its entirety.

[0026] The exposed surfaces of the platen 205, the stem 210, and the backside gas tube 250 are made of ceramic material which preferably does not lead to substrate contamination during processing when the platen 205, stem 210, and/or backside gas tube 250 are exposed to processing conditions. Preferably, exposed surfaces of the platen 205, the stem 210, and/or the backside gas tube 250 are formed of aluminum nitride. The upper surface of the upper gas tube flange 253 is preferably diffusion bonded to the lower surface 208 of the platen 205 and the lower surface of the upper gas tube flange 253 is preferably diffusion bonded to an upper surface of the upper stem flange 215 so as to form a vacuum seal between the interior 213 of the stem 210 and a vacuum chamber in which the substrate pedestal module 320 is disposed. Preferably, the contact area between the upper surface of the upper gas tube flange 253 and the lower surface 208 of the platen 205 is about equal to the contact area between the lower surface of the upper gas tube flange 253 and the upper surface of the upper stem flange 215.

More preferably, the contact area between the upper surface of the upper gas tube flange 253 and the lower surface 208 of the platen 205 is equal to the contact area between the lower surface of the upper gas tube flange 253 and the upper surface of the upper stem flange 215. FIG. 2 illustrates an embodiment of the substrate pedestal module 320 wherein the contact area between the upper surface of the upper gas tube flange 253 and the lower surface 208 of the platen 205 is equal to the contact area between the lower surface of the upper gas tube flange 253 and the upper surface of the upper stem flange 215. In this embodiment, a gap 230 is formed between a portion of the upper gas tube flange 253 and the lower surface 208 of the platen 205. In an alternate embodiment, as illustrated in FIG. 3, the substrate pedestal module 320 can be formed such that there is no gap between the upper surface of the upper gas tube flange 253 and the lower surface 208 of the platen 205.

[0027] Further disclosed herein is a method of making a substrate pedestal module 320. The method of making the substrate pedestal module 320 includes positioning an upper ceramic surface of an upper gas tube flange 253 against a lower ceramic surface 208 of a platen 205. The upper ceramic surface of the upper gas tube flange 253 is diffusion bonded to the lower ceramic surface 208 of the platen 205. In an embodiment, an upper ceramic surface of an upper stem flange 215 is simultaneously positioned against a lower ceramic surface of the upper gas tube flange 253 wherein the upper ceramic surface of the upper gas tube flange 253 is simultaneously diffusion bonded to the lower ceramic surface of the platen 205 while the upper ceramic surface of the upper stem flange 215 is diffusion bonded to the lower ceramic surface of the upper gas tube flange 253. To simultaneously diffusion bond the upper ceramic surface of an upper stem flange 215 to the lower ceramic surface of the upper gas tube flange 253 and the upper ceramic surface of the upper gas tube flange 253 to the lower ceramic surface of the platen 205 the contact area between the upper ceramic surface of the upper stem flange 215 and the lower ceramic surface of the upper gas tube flange 253 as well as the contact area between the upper ceramic surface of the upper gas tube flange 253 and the lower ceramic surface 208 of the platen 205 are equal or about equal such that the ceramic surfaces that are diffusion bonded together form a vacuum seal. In this manner, the platen 205, the stem 210, and the backside gas tube 250 can be integrally connected in a single diffusion bonding process.

[0028] In an alternate embodiment, if the contact area between the upper ceramic surface of the upper gas tube flange 253 and the lower ceramic surface 208 of the platen 205 is not equal to the contact area between the lower ceramic surface of the upper gas tube flange 253 and the upper ceramic surface of the upper stem flange 215 then the upper ceramic surface of the upper gas tube flange 253 is first diffusion bonded to the lower ceramic surface 208 of the platen 205 wherein the upper ceramic surface of the upper stem flange 215 is subsequently bonded to a lower ceramic surface of the upper gas tube flange 253.

[0029] While the substrate pedestal module of the semiconductor substrate processing apparatus has been described in detail with reference to specific embodiments thereof, it will be apparent to those skilled in the art that various changes and modifications can be made, and equivalents employed, without departing from the scope of the appended claims. What is claimed is:

- 1. A semiconductor substrate processing apparatus for processing semiconductor substrates, comprising:

- a vacuum chamber including a processing zone in which a semiconductor substrate may be processed;

- a process gas source in fluid communication with the vacuum chamber for supplying a process gas into the vacuum chamber;

- a showerhead module through which process gas from the process gas source is supplied to the processing zone of the vacuum chamber; and

- a substrate pedestal module including a platen made of ceramic material having an upper surface configured to support a semiconductor substrate thereon during processing; a stem made of ceramic material having an upper stem flange that supports the platen; and a backside gas tube made of ceramic material that is located in an interior of the stem, the backside gas tube including an upper gas tube flange that is located between a lower surface of the platen and an upper surface of the upper stem flange wherein the backside gas tube is in fluid communication with at least one backside gas passage of the platen and the backside gas tube is configured to supply a backside gas to a region below a lower surface of a semiconductor substrate that is to be supported on the upper surface of the platen during processing.

- 2. The semiconductor substrate processing apparatus of claim 1, wherein the semiconductor substrate processing apparatus includes:

- (a) an RF energy source adapted to energize the process gas into a plasma state in the processing zone;

- (b) a control system configured to control processes performed by the semiconductor substrate processing apparatus; and/or

- (c) a non-transitory computer machine-readable medium comprising program instructions for control of the semiconductor substrate processing apparatus.

- 3. The semiconductor substrate processing apparatus of claim 1, wherein an upper surface of the upper gas tube flange is diffusion bonded to a lower surface of the platen and a lower surface of the upper gas tube flange is diffusion bonded to an upper surface of the upper stem flange so as to form a vacuum seal between the interior of the stem and the vacuum chamber.

- 4. The semiconductor substrate processing apparatus of claim 3, wherein the contact area between the upper surface of the upper gas tube flange and the lower surface of the platen is about equal to the contact area between the lower surface of the upper gas tube flange and the upper surface of the upper stem flange.

- **5**. The semiconductor substrate processing apparatus of claim **1**, wherein a gap is formed between a portion of the gas tube flange and the lower surface of the platen or there is no gap between the upper surface of the upper gas tube flange and the lower surface of the platen.

- **6**. The semiconductor substrate processing apparatus of claim **1**, wherein:

- (a) the backside gas tube, the platen and/or the stem is formed of aluminum nitride;

- (b) the backside gas tube includes at least one opening in, the upper gas tube flange such that at least one respective electrical connection can extend through the upper gas tube flange;

- (c) the backside gas tube is centrally located in the interior of the stem or the backside gas tube is located off-center in the interior of the stem; and/or

- (d) the semiconductor substrate processing apparatus is chemical vapor deposition apparatus, plasma-enhanced chemical vapor deposition apparatus, atomic layer deposition apparatus, plasma-enhanced atomic layer deposition apparatus, pulsed deposition layer apparatus, or plasma-enhanced pulsed deposition layer apparatus.

- 7. The semiconductor substrate processing apparatus of claim 1, wherein the substrate pedestal module further comprises:

- (a) at least one electrostatic clamping electrode embedded in the platen;

- (b) a lower RF electrode embedded in the platen;

- (c) at least one heater embedded in the platen;

- (d) a plurality of lift pins configured to lower and raise a semiconductor substrate to and from the upper surface of the platen;

- (e) a mesa pattern formed on the upper surface of the platen;

- (f) a carrier ring configured to lower and raise a semiconductor substrate to and from the upper surface of the platen; or

- (g) a single electrode embedded therein that is operable to serve as an electrostatic clamping electrode and a RF electrode.

- 8. The semiconductor substrate processing apparatus of claim 1, further comprising a backside gas supply operable to supply backside gas through the backside gas tube that is in fluid communication with the at least one backside gas passage of the platen such that a backside gas may be supplied to the region below a lower surface of a semiconductor substrate that is to be supported on the upper surface of the platen during processing.

- **9**. The semiconductor substrate processing apparatus of claim **1**, wherein an outer periphery of the upper gas tube flange is located on a radius no greater than ½ the outer diameter of the platen.

- 10. A substrate pedestal module of a semiconductor substrate processing apparatus, the substrate pedestal module comprising:

- a platen made of ceramic material having an upper surface configured to support a semiconductor substrate thereon during processing;

- a stem made of ceramic material having an upper stem flange that supports the platen; and

- a backside gas tube made of ceramic material that is located in an interior of the stem, the backside gas tube including an upper gas tube flange that is located between a lower surface of the platen and an upper surface of the upper stem flange wherein the backside gas tube is in fluid communication with at least one backside gas passage of the platen and the backside gas tube is configured to supply a backside gas to a region below a lower surface of a semiconductor substrate that is to be supported on the upper surface of the platen during processing.

- 11. The semiconductor substrate processing apparatus of claim 10, wherein an upper surface of the upper gas tube flange is diffusion bonded to a lower surface of the platen

- and a lower surface of the upper gas tube flange is diffusion bonded to an upper surface of the upper stem flange so as to form a vacuum seal.

- 12. The semiconductor substrate processing apparatus of claim 11, wherein the contact area between the upper surface of the upper gas tube flange and the lower surface of the platen is about equal to the contact area between the lower surface of the upper gas tube flange and the upper surface of the upper stem flange.

- 13. The semiconductor substrate processing apparatus of claim 10, wherein a gap is formed between a portion of the upper gas tube flange and the lower surface of the platen or there is no gap between the upper surface of the upper gas tube flange and the lower surface of the platen.

- 14. The semiconductor substrate processing apparatus of claim 10, wherein:

- (a) the backside gas tube, the platen and/or the stem is formed of aluminum nitride;

- (b) the backside gas tube includes at least one opening in the upper gas tube flange such that at least one respective electrical connection can extend through the upper gas tube flange; and/or

- (c) the backside gas tube is centrally located in the interior of the stem or the backside gas tube is located off-center in the interior of the stem.

- 15. The semiconductor substrate processing apparatus of claim 10, wherein the substrate pedestal module further comprises:

- (a) at least one electrostatic clamping electrode embedded in the platen;

- (b) a lower RF electrode embedded in the platen;

- (c) at least one heater embedded in the platen;

- (d) a plurality of lift pins configured to lower and raise a semiconductor substrate to and from the upper surface of the platen;

- (e) a mesa pattern formed on the upper surface of the platen;

- (f) a carrier ring configured to lower and raise a semiconductor substrate to and from the upper surface of the platen; or

- (g) a single electrode embedded therein that is operable to serve as an electrostatic clamping electrode and a RF electrode

- **16**. A method of making a substrate pedestal module of a semiconductor substrate processing apparatus, the method comprising:

- positioning an upper ceramic surface of an upper gas tube flange against a lower ceramic surface of a platen; and

- diffusion bonding the upper ceramic surface of the upper gas tube flange to the lower ceramic surface of the platen so as to form a vacuum seal.

- 17. The method of claim 16 further comprising:

- positioning an upper ceramic surface of an upper stem flange against a lower ceramic surface of the upper gas tube flange; and

- simultaneously diffusion bonding the upper ceramic surface of the upper gas tube flange to the lower ceramic surface of the platen and the upper ceramic surface of the upper stem flange to the lower ceramic surface of the upper gas tube flange so as to form a vacuum seal, or diffusion bonding the upper ceramic surface of the upper stem flange to the lower ceramic surface of the upper gas tube flange so as to form a vacuum seal after

the upper ceramic surface of the upper gas tube flange is diffusion bonded to the lower ceramic surface of the platen.

**18**. A method of processing a semiconductor substrate in the semiconductor substrate processing apparatus according to claim **1**, comprising:

supplying the process gas from the process gas source into the processing zone; and

processing a semiconductor substrate that is supported on the upper surface of the platen.

- 19. The method of claim 18, further comprising supplying a backside heat transfer gas or purge gas through the backside gas tube to a region below a lower surface of a semiconductor substrate supported on the upper surface of the platen during processing.

- 20. The method of claim 18, wherein the processing is at least one of chemical vapor deposition, plasma-enhanced chemical vapor deposition, atomic layer deposition, plasma-enhanced atomic layer deposition, pulsed deposition layer, and/or plasma-enhanced pulsed deposition layer.

\* \* \* \* \*