US 20180323699A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2018/0323699 A1

## Carpenter, JR. et al.

#### (54) POWER LOSS PROTECTION INTEGRATED **CIRCUIT WITH AUTONOMOUS** CAPACITOR HEALTH CHECK

- (71) Applicant: Active-Semi, Inc., Tortola (VG)

- (72)Inventors: John H. Carpenter, JR., Allen, TX (US); Brett E. Smith, McKinney, TX (US)

- (21) Appl. No.: 16/030,865

- (22) Filed: Jul. 10, 2018

#### **Related U.S. Application Data**

- (63) Continuation of application No. 15/201,288, filed on Jul. 1, 2016, now Pat. No. 10,020,723.

- (60) Provisional application No. 62/357,739, filed on Jul. 1, 2016, provisional application No. 62/354,733, filed on Jun. 25, 2016, provisional application No. 62/354, 734, filed on Jun. 25, 2016, provisional application No. 62/354,740, filed on Jun. 25, 2016, provisional application No. 62/354,741, filed on Jun. 25, 2016, provisional application No. 62/354,732, filed on Jun. 25, 2016, provisional application No. 62/354,738, filed on Jun. 25, 2016.

### **Publication Classification**

(51) Int. Cl.

| H02M 1/32  | (2007.01) |

|------------|-----------|

| H02M 1/08  | (2006.01) |

| G01R 31/36 | (2006.01) |

| G05B 11/28 | (2006.01) |

| H02M 3/158 | (2006.01) |

| H02M 3/156 | (2006.01) |

| G01R 19/25 | (2006.01) |

| H02J 9/06  | (2006.01) |

|            |           |

#### Nov. 8, 2018 (43) **Pub. Date:**

| H02H 3/08  | (2006.01) |

|------------|-----------|

| H01H 85/02 | (2006.01) |

| G05F 1/66  | (2006.01) |

| G05B 15/02 | (2006.01) |

| H02M 1/00  | (2006.01) |

| H03M 1/12  | (2006.01) |

| H03M 1/76  | (2006.01) |

|            |           |

<sup>(52)</sup> U.S. Cl.

CPC ..... H02M 1/32 (2013.01); H03M 1/765 (2013.01); G01R 31/362 (2013.01); G05B 11/28 (2013.01); H02M 3/1588 (2013.01); H02M 3/1582 (2013.01); H02M 3/158 (2013.01); H02M 3/156 (2013.01); G01R 19/2513 (2013.01); H02J 9/061 (2013.01); H02H 3/08 (2013.01); H01H 85/0241 (2013.01); G05F 1/66 (2013.01); G05B 15/02 (2013.01); H02M 2001/0009 (2013.01); H03M 1/122 (2013.01); H02M 1/08 (2013.01)

#### (57)ABSTRACT

A power loss protection integrated circuit includes a storage capacitor terminal (STR), an autonomous capacitor health check circuit, and a capacitor fault terminal (CF). The capacitor health check circuit autonomously performs periodic capacitor check operations. In a check operation, current is sinked from the STR terminal for a predetermined time and in a predetermined way. If during this time the voltage on the STR terminal STR drops below a predetermined voltage, then a digital signal CF is asserted onto the CF terminal. Immediately following each capacitor check, a charging voltage is driven onto the STR terminal to recharge the external capacitors coupled to the STR terminal. In one example, the integrated circuit further includes a current switch circuit (eFuse) and a buck/boost controller. The capacitor health check circuit is only enabled during normal mode operation of the integrated circuit, and the check circuit disables boost operation during capacitor checks.

FIG. 13

#### POWER LOSS PROTECTION INTEGRATED CIRCUIT WITH AUTONOMOUS CAPACITOR HEALTH CHECK

#### CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of, and claims priority under 35 U.S.C. § 120 from, nonprovisional U.S. patent application Ser. No. 15/201,288 entitled "POWER LOSS PROTECTION INTEGRATED CIRCUIT WITH AUTONOMOUS CAPACITOR HEALTH CHECK," filed on Jul. 1, 2016, now U.S. patent Ser. No. 10/020,723. Application Ser. No. 15/201,288 in turn claims the benefit under 35 U.S.C. § 119 of each of the following seven U.S. Provisional Applications: 1) U.S. Provisional Application Ser. No. 62/354,732, entitled "POWER INTEGRATED CIRCUIT WITH AUTONOMOUS LIMIT CHECKING OF ADC CHANNEL MEASUREMENTS," filed Jun. 25, 2016; 2) U.S. Provisional Application Ser. No. 62/354,733, entitled "POWER LOSS PROTECTION INTEGRATED CIRCUIT," filed Jun. 25, 2016; 3) U.S. Provisional Application Ser. No. 62/354,734, entitled "AUTONOMOUS CAPACITOR HEALTH CHECK IN A POWER LOSS PROTECTION INTEGRATED CIRCUIT," filed Jun. 25, 2016; 4) U.S. Provisional Application Ser. No. 62/354,738, entitled "PROGRAMMABLE VOLTAGE SETTING WITH OPEN AND SHORT CIRCUIT PROTECTION," filed Jun. 25, 2016; 5) U.S. Provisional Application Ser. No. 62/354, 740, entitled "OPTIMIZED GATE DRIVER FOR LOW VOLTAGE POWER LOSS PROTECTION SYSTEM," filed Jun. 25, 2016; 6) U.S. Provisional Application Ser. No. 62/354,741, entitled "FAST SETTLEMENT OF SUPPLE-MENT CONVERTER FOR POWER LOSS PROTECTION SYSTEM," filed Jun. 25, 2016, and 7) U.S. Provisional Application Ser. No. 62/357,739, entitled "GATE DRIVER TO DECREASE EMI WITH SHORTER DEAD-TIME," filed Jul. 1, 2016. The entire subject matter of the aforementioned patent documents is incorporated herein by reference.

#### TECHNICAL FIELD

**[0002]** The present disclosure relates generally to power loss protection systems, and to related circuits and methods.

#### BACKGROUND INFORMATION

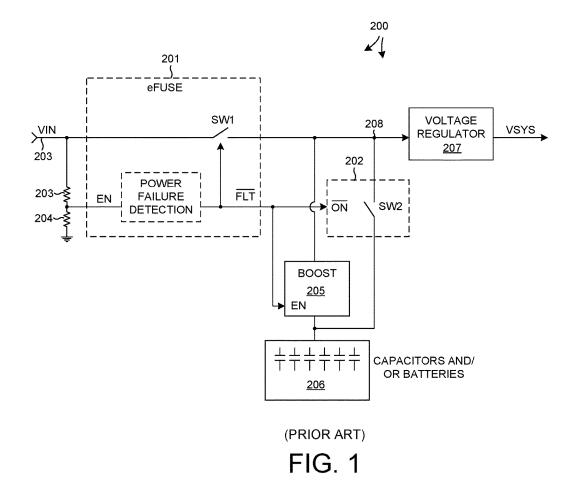

[0003] Capacitors and/or batteries are used to store energy in power loss protection systems. FIG. 1 (Prior Art) illustrates one example of a power loss protection system 200 involving a so-called "eFuse" 201, a switch component 202, enable trip point resistors 203 and 204, a boost converter circuit 205, a bank of capacitors and/or batteries 206, and a voltage regulator 207. This circuitry is soldered onto a printed circuit board. During normal operation of the system, the boost converter 201 receives some of the power from the eFuse output and uses that to charge the capacitors and/or batteries 202. If VIN at input 203 is then suddenly lost, for example due to a condition like a power brown out condition or a power cord disconnection event, then the eFuse turns off immediately and the fault signal is asserted. The fault signal is received by the second switch SW2 202. The second switch SW2 202 responds by turning on so that power can then be supplied onto node 208 from the capacitors and/or batteries 202 in the place of the lost power. The linear voltage regulator 207 reduces the capacitor voltage down to the supply voltage "VSYS" required by the device being powered. The required system power and supply voltage VSYS can therefore be maintained for long enough to allow data that is stored in the device in volatile memory to be transferred into non-volatile storage before system power is lost altogether. This kind of prior art power loss protection system is used to power devices where high reliability is required, such as in computers like laptops and servers. If capacitors are used for block 206, then the capacitance of the capacitors must be large enough that the energy stored in the capacitors can sustain system power long enough to allow the device to complete a safe power-off sequence involving backup of configuration information and status after a loss of VIN is detected. The capacitors are sized accordingly to account for anticipated system operation and the needs of the device being powered.

#### SUMMARY

**[0004]** In a power loss protection system as described above in the background information section, in which capacitors and not batteries are used for block **202**, one or more of the capacitors of block **202** may degrade for various reasons. In other systems of the very same type, the corresponding capacitors do not degrade. Due to the degradation, the capacitor or capacitors may have a smaller capacitance. When the power loss protection system is needed in a power loss event, the remainder of the circuit works but there may be inadequate energy stored due to the lower than required capacitance where the backup energy is stored.

[0005] In a first novel aspect, a power loss protection integrated circuit includes a current switch circuit portion (that can perform the eFuse function) and an autonomous limit checking circuit. The autonomous limit checking circuit includes an input analog multiplexer, an Analog-to-Digital Converter (ADC), a plurality of capture registers, a digital state machine, and a flag output terminal. For each capture register, the autonomous limit checking circuit further includes an associated lower limit register and an associated upper limit register. The digital state machine controls the input analog multiplexer and the capture registers so the ADC digitizes a voltage on a first of a plurality of nodes to be monitored. The digitized value from the ADC is then stored under control of the digital state machine in a corresponding first one of the capture registers. After this capture event, the digital state machine controls the input analog multiplexer and the capture registers so that the ADC digitizes a voltage on a second one of a plurality of nodes, and the resulting second digitized value is then stored in a corresponding second one of the capture registers. One by one, the voltages on the various nodes to be monitored are digitized, and the resulting digital capture values are stored one by one into the corresponding ones of the capture registers. The capture value in each capture register is compared to an upper limit value stored in the associated upper limit register and is also compared to a lower limit value stored in the associated lower limit register. These comparisons may be masked. A digital value indicative of a result of the comparisons is obtained. In one example, the digital value is true if the capture value is smaller than the lower limit value or is greater than the upper limit value. If any of these digital values for any of the capture registers is asserted, then a flag signal indicative of this condition is output onto the flag output terminal. This capturing and comparing operation of the limit checking circuit is "autonomous" from any associated digital processor or microcontroller that might be coupled to the integrated circuit in that once it is set up, it operates autonomously. The power loss protection integrated circuit is a power integrated circuit device that includes rugged power transistors and circuitry in its current switch portion that are not found in typical purely digital logic integrated circuits. In one example, a node voltage that is monitored can have a voltage that is substantially higher than the supply voltage that powers the digital logic circuitry on the power loss protection integrated circuit. For example, a twenty-volt node voltage may be monitored and a capture value obtained that is indicative of the magnitude of this voltage, whereas the digital logic circuitry is powered from a VDD supply voltage of five volts or less. In addition, the power loss protection includes current sense circuitry that allows the monitoring of a large through-current flowing through the current switch circuit. This through-current (for example, a constant two amperes) is much larger than the typical small currents that would ordinarily be monitored by a discrete ADC. The ADC is capable of monitoring the magnitude of this large throughcurrent. Advantageously, the power loss protection integrated circuit includes no processor that fetches, decodes and executes any instructions. The limit checking circuit can operate autonomously of any such processor. Associated with each limit register is a corresponding register of nonvolatile memory, such as FLASH. These non-volatile registers are preloaded with data at the time of integrated circuit device manufacture by the integrated circuit manufacturer and supplier. The very same type of power loss protection integrated circuit that is used in a larger circuit involving a processor can also be used in another customer's system that has no processor. Upon power up and/or at another suitable time, the pre-loaded content of each non-volatile register is automatically loaded into its associated limit register. In one case, the flag output terminal is usable to supply an interrupt signal to a processor, such as a microcontroller of the device being powered. In another case, the flag output terminal is usable to drive a LED that gives a visible indication of a detected limit situation in a case where the user's system might have no processor.

[0006] In a second novel aspect, a single power loss protection integrated circuit includes a current switch circuit (that can perform the eFuse function), an input voltage terminal (VIN), an output voltage terminal (VOUT), a buck/boost controller, and a storage capacitor terminal (STR). The buck/boost controller is adapted to work, along with discrete components external to the integrated circuit such as a discrete inductor, as either a buck converter in a buck mode of operation, or as a boost converter in a boost mode of operation. The same external inductor is used as the inductor in both modes. In the boost mode, the buck/boost controller drives a switch terminal so that the buck/boost controller in combination with the external inductor receives a relatively low voltage as output by the current switch circuit (the eFuse) and outputs a relatively high voltage onto the storage capacitor terminal (STR) thereby charging any external capacitor coupled to this terminal. In the buck mode, the buck/boost controller receives the relatively high voltage from the storage capacitor terminal (STR) and bucks it down to the relatively low voltage that is required at the output voltage terminal VOUT by the device to be powered. The current switch circuit in performing its eFuse function can pass a through-current of up to a maximum current from the input voltage terminal VIN to the output voltage terminal VOUT, where this maximum input current is a large current of at least two amperes. The through-current is large as compared to currents that typically pass through digital logic circuits. The current switch circuit outputs a digital undervoltage signal and a digital high current signal. The digital undervoltage signal (UV), if asserted, indicates that the input voltage on the VIN terminal is lower than a predetermined voltage. The digital high current signal (HC), if asserted, indicates that the through-current is greater than a predetermined current. If the digital undervoltage signal UV is asserted, then the buck/boost converter is made to begin operating in the buck mode. If the digital high current signal HC is asserted, then the buck/boost converter is prevented from operating in the boost mode. Advantageously, the intercommunication of the necessary signals between the current switch circuit portion of the integrated circuit and the buck/boost controller portion of the integrated circuit to accomplish these conditional disabling functions are on the integrated circuit. This allows the signaling to be fast, and allows the signals to be lower power signals because the environment on-chip is relatively free of potential noise problems that otherwise might be present were the intercommunication to have to pass across conductors on a printed circuit board. Potential board level complexities and noise problems are avoided. The speed and efficiency of the intercommunication allows the size of the storage capacitor bank for a given application to be made smaller and less expensive because the buck/boost converter is controlled faster in a fault condition as compared to a prior art situation as illustrated in FIG. 1 of the background information section.

[0007] In a third novel aspect, a power loss protection integrated circuit includes a storage capacitor terminal (STR), a novel autonomous capacitor health check circuit, and a capacitor fault terminal (CF). The novel autonomous capacitor health check circuit is "autonomous" in that it can be set up to operate autonomously of any instruction fetching and executing processor as described above in connection with the autonomous limit checking circuit. The capacitor health check circuit performs a periodic capacitor check operation by sinking a predetermined current from the storage capacitor terminal for a predetermined time duration. During the predetermined time duration it detects whether the voltage on the storage capacitor terminal STR drops below a predetermined threshold voltage. If the voltage on the storage capacitor terminal STR is detected to have dropped below the predetermined threshold voltage, then a sequential logic element in the capacitor health check circuit is set, and this in turn causes a digital logic capacitor fault signal CF to be asserted onto the capacitor fault terminal CF. Immediately following the capacitor health check operation, a buck/boost controller portion of the integrated circuit may again operate in a boost mode so that a charging voltage is again driven onto the storage capacitor terminal (STR), thereby recharging the external storage capacitor back up to its initial, fully charged, voltage. Such a capacitor health check operation is carried out periodically by the capacitor health check circuitry without having to be repeatedly prompted to do such a check by any digital processor. In one example, the power loss protection integrated circuit includes a buck/boost controller as discussed above. The capacitor health check circuit outputs a digital control signal

that disables the controller from operating when a capacitor health check operation is occurring. In one example, the predetermined time duration actually involves a first time portion and a second time portion. During the first time portion, a first predetermined and fixed current is "sinked" from (drawn from to a current sink) the STR terminal. During the second time portion, a second predetermined and fixed current is sinked from the STR terminal. After the capacitor health check operation is completed, the overall power loss protection integrated circuit automatically resumes operating in its normal mode. The first time portion of the test is tailored to detect a first failure characteristic of a degraded capacitor, and the second time portion of the test is tailored to detect a second failure characteristic of a degraded capacitor. In one example, an external processor can detect whether the sequential logic element of the capacitor health check circuit has been set or not. The external processor does this by reading a register of the integrated circuit through a serial digital bus interface. If a bit in this register is read as having been set, this indicates to the processor that the sequential logic element of the capacitor health check circuit was set. The reading of the register causes the sequential logic element to be reset. The very same type of power loss protection integrated circuit is usable both with a digital processor that can read the register, and without such a processor. In one example, after a certain amount of time has elapsed, the sequential logic element of the health check circuit is automatically reset regardless of whether the register was read or not. In one example, there are various modes for how the capacitor fault signal is communicated out of the integrated circuit, and how the sequential logic element is reset. There is a default mode. The mode used at a given time can be changed by an external processor by writing to a control register on the integrated circuit via the serial bus interface.

**[0008]** The foregoing is a summary and thus contains, by necessity, simplifications, generalizations and omissions of detail; consequently it is appreciated that the summary is illustrative only. Still other methods, and structures and details are set forth in the detailed description below. This summary does not purport to define the invention. The invention is defined by the claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0009]** The accompanying drawings, where like numerals indicate like components, illustrate embodiments of the invention.

**[0010]** FIG. **1** is a diagram of an example of a power loss protection system.

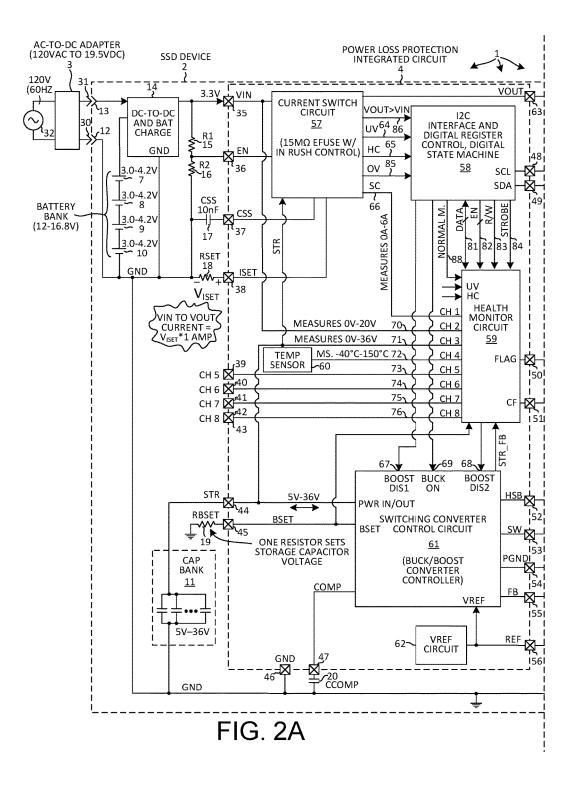

**[0011]** FIG. **2**A is a first part of a larger diagram of a system involving a novel power loss protection integrated circuit.

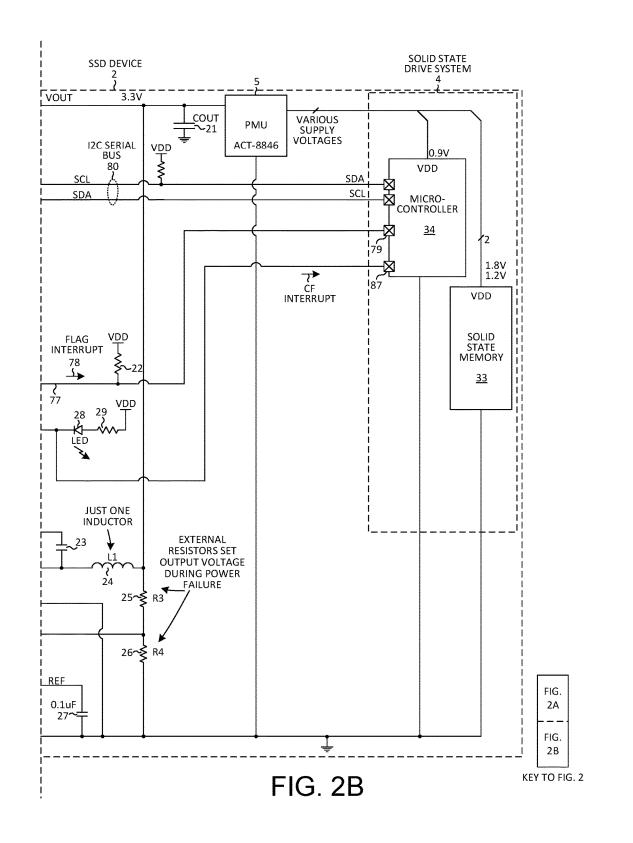

**[0012]** FIG. 2B is a second part of a larger diagram of a system involving a novel power loss protection integrated circuit. FIG. 2A and FIG. 2B together form the larger diagram of FIG. 2.

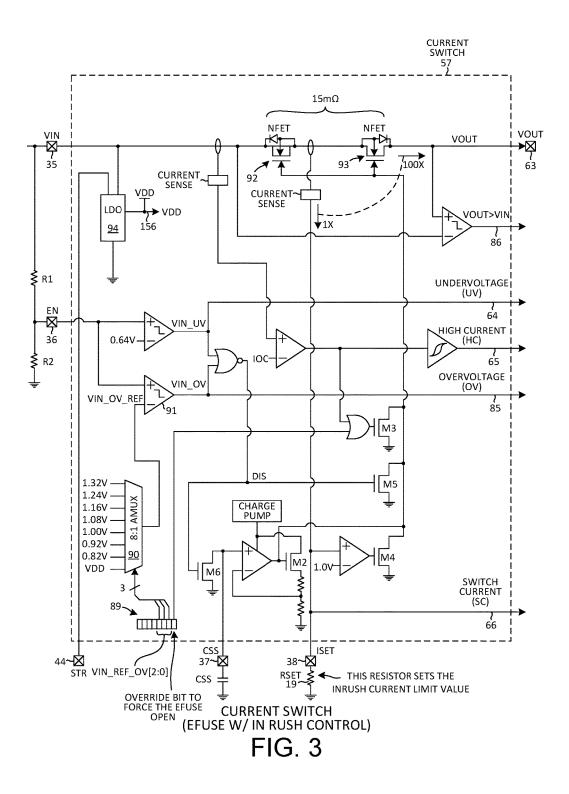

[0013] FIG. 3 is a more detailed diagram of the current switch circuit 57 of FIG. 2.

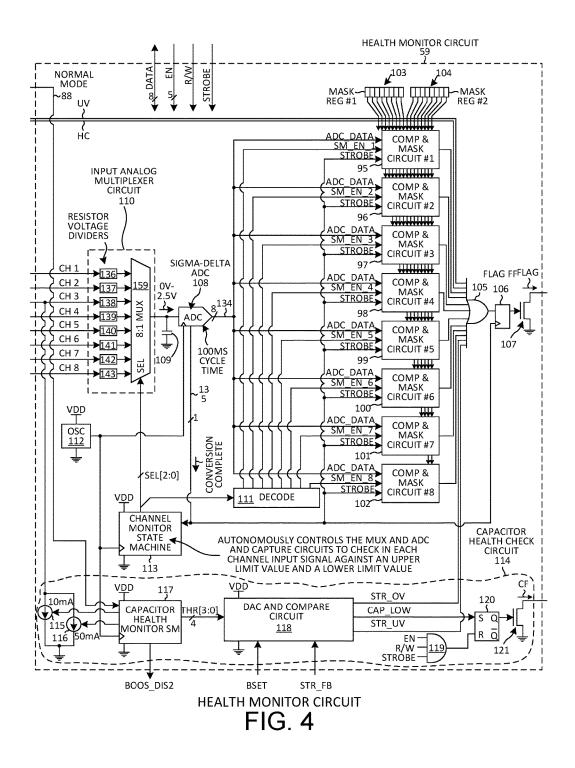

[0014] FIG. 4 is a more detailed diagram of the health monitor circuit 59 of FIG. 2.

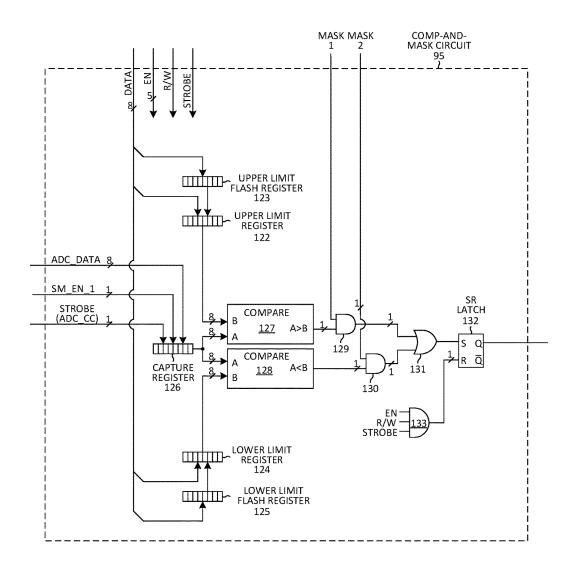

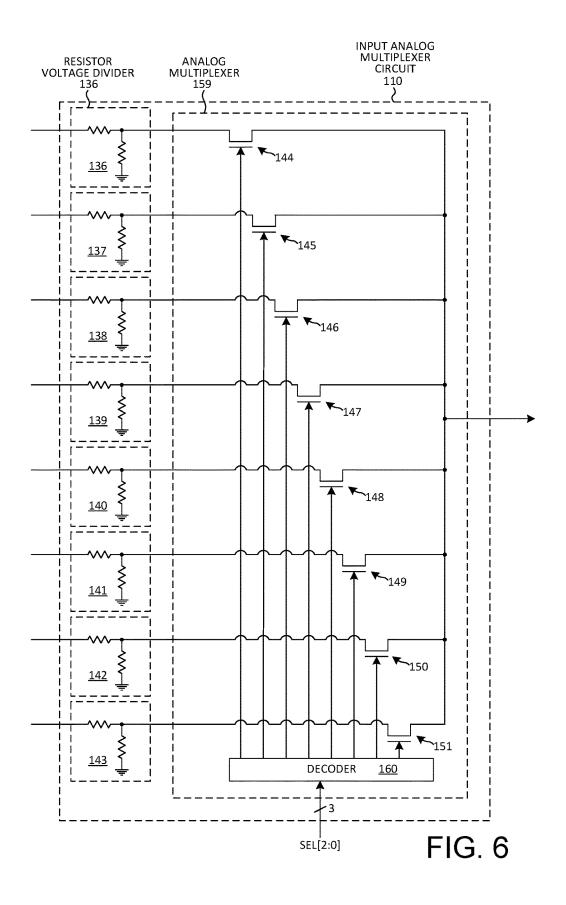

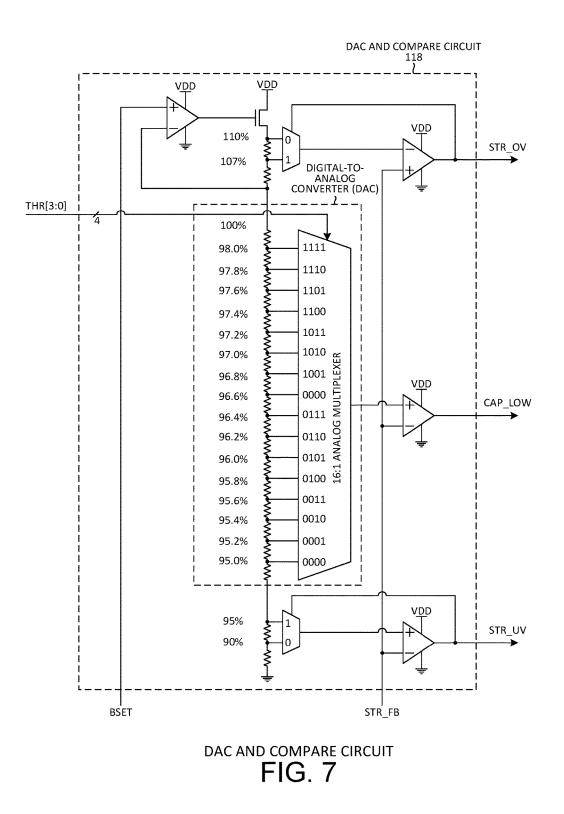

[0015] FIG. 5 is a more detailed diagram of a compareand-mask circuit 95 within the health monitor circuit 59 of FIG. 4. [0016] FIG. 6 is a more detailed diagram of the input analog multiplexer circuit 110 of the health monitor circuit 59 of FIG. 4.

[0017] FIG. 7 is a more detailed diagram of the DAC and compare circuit **118** of the health monitor circuit **59** of FIG. **4**.

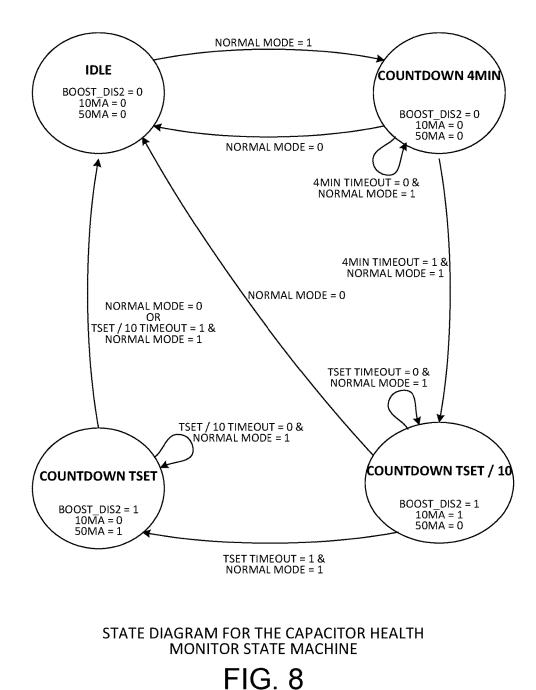

[0018] FIG. 8 is a state diagram for the capacitor health monitor state machine 117 of FIG. 4.

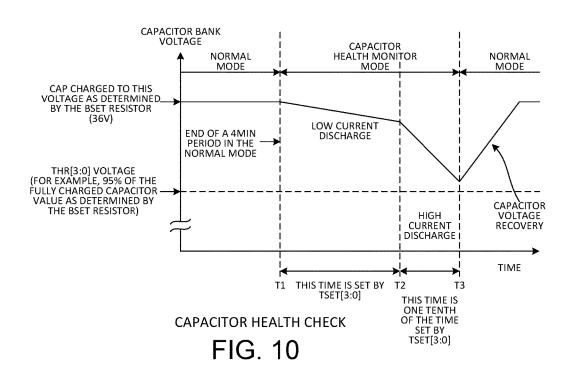

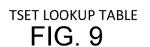

[0019] FIG. 9 is a table that indicates, for each 4-bit TSET[3:0] value, the corresponding time period throughout which the ten milliampere current sink 115 of the health monitor circuit 114 of FIG. 4 is enabled during a capacitor health check operation.

**[0020]** FIG. **10** is a timeline diagram that illustrates one capacitor health check operation as carried out by the capacitor health check circuit **114** of FIG. **4**.

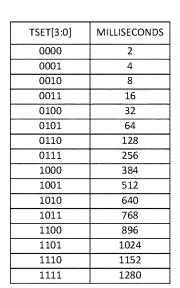

**[0021]** FIG. **11** is a more detailed diagram of the switching converter control circuit **61** of FIG. **1**.

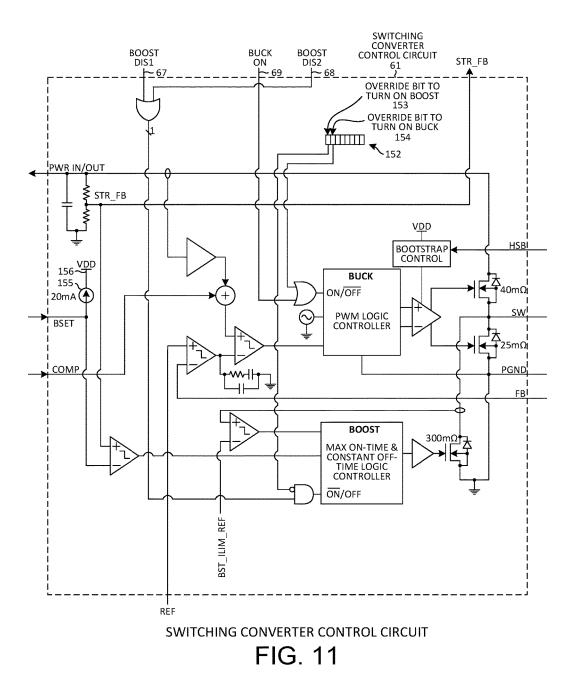

**[0022]** FIG. **12** is a more detailed diagram of the voltage reference circuit **62** of FIG. **2**.

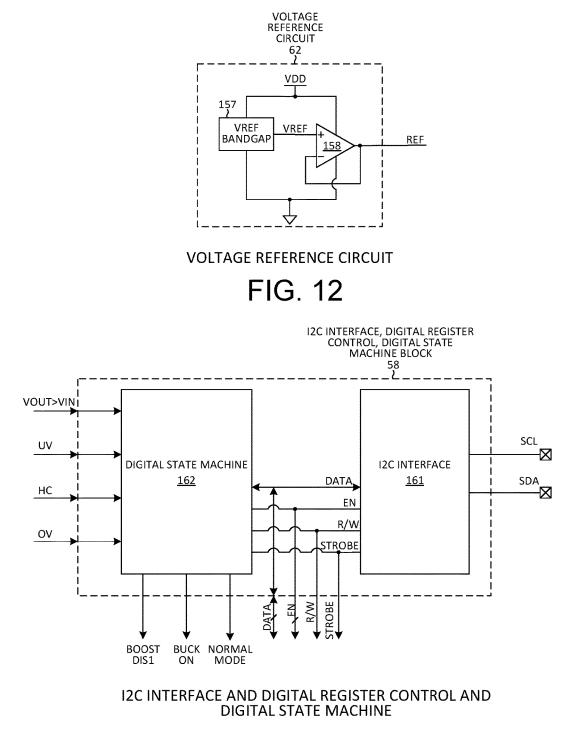

**[0023]** FIG. **13** is a more detailed block diagram of the I2C interface and digital register control and digital state machine block **58** of FIG. **2**.

#### DETAILED DESCRIPTION

[0024] FIG. 2 is a diagram of a system 1 that involves a device to be powered 2 and an AC-to-DC adapter 3. The device 2 in this particular example is a Solid State Drive (SSD) device. It includes a solid state device system 4, a Power Management Unit (PMU) integrated circuit 5, a power loss protection integrated circuit 6, a bank of seriesconnected batteries 7-10, a bank of parallel-connected capacitors 11, a socket portion 12 and 13 of a connector, a DC-to-DC converter and battery charger 14, and other discrete components 15-29. The solid state drive system 4 includes, among other components not shown, a solid state memory portion 33 and a microcontroller integrated circuit 34. The AC-to-DC adapter 3 can be connected to the SSD device 2 by plugging its plug portion 30 and 31 into the socket portion 12 and 13 of the SSD device, and the AC-to-DC adapter 3 can be disconnected from the SSD device by unplugging it from the socket portion. The AC-to-DC adapter 3 is coupled to receive power from a 120 volt RMS VAC 60 Hz supply voltage source 32 such as, for example, a standard residential wall socket. The SSD device 2 further includes a printed circuit board (not shown) disposed within an enclosure (not shown). The integrated circuits and other components of the SSD device 2 are mounted to the PCB and are contained in the enclosure.

[0025] Power loss protection integrated circuit 6 includes a VIN terminal 35, an EN terminal 36, a CSS terminal 37, an ISET terminal 38, several analog input terminals 39-43, a STR terminal 44, a BSET terminal 45, a ground terminal GND 46, a CCOMP terminal 47, a VOUT terminal 63, an SCL terminal 48, a SDA terminal 49, a flag output terminal 50, a capacitor flat terminal CF 51, an HSB terminal 52, a SW terminal 53, a PGND terminal 54, an FB terminal 55, a REF terminal 56, a current switch circuit 57, an I2C interface and digital register control and digital state machine circuit 58, a health monitor circuit 59, an on-chip temperature sensor 60, a buck/boost switching converter control circuit 61, and a reference voltage circuit 62.

**[0026]** The current switch circuit **57** is also called an eFuse circuit. The current switch circuit **57** can couple the VIN

terminal 35 to the VOUT terminal 63 such that current can freely flow from the VIN terminal 35, through the current switch circuit 57, and to the VOUT terminal 63. When the current switch circuit 57 is ON in this way, it only introduces a 15 milliohm resistance in that current path. The current switch circuit 57 monitors the voltage on the VIN terminal. If the voltage on the VOUT terminal 63 is greater than the voltage on the VIN terminal 35, then the switch circuit 57 asserts the VOUT>VIN digital signal on conductor 86 to a digital logic high, otherwise the VOUT>VIN digital signal is a digital logic low. If the voltage on the VIN terminal is below an undervoltage value set by resistors 15 and 16, then the current switch circuit 57 is OFF such that the VIN terminal is not coupled to the VOUT terminal through the switch circuit 57. If the current switch circuit 57 detects the "UV" undervoltage condition, then it asserts the UV digital signal on conductor 64 to a digital logic high, otherwise the UV digital signal is a digital logic low. If the voltage on the VIN terminal is above a programmable overvoltage value, then the current switch circuit 57 is OFF such that the VIN terminal is not coupled to the VOUT terminal through the switch circuit 57. If the current switch 57 detects the "OV" overvoltage condition, then it asserts the OV digital signal on the OV conductor 85.

[0027] In addition to sensing voltages, the current switch circuit 57 also senses the magnitude of current flowing through the current switch between the VIN terminal and the VOUT terminal. If the current is below a predetermined high current value (AHC), and if the current switch 57 is to be ON as determined by the voltage on the VIN terminal, then the current switch is fully ON (to have a resistance of 15 milliohms or less). If, however, the current is detected to reach the high current value (AHC), then the current switch circuit begins to regulate the through-current so that the through-current remains at the high current value amount AHC but does not exceed AHC. The current switch 57 does this by controlling the gate voltages on a pair of series field effect transistors through which the through-current flows. Increasing the drain-to-source resistance RDS of these field effect transistors allows the flow of current to be maintained at the AHC amount. If, however, the RDS across the transistors becomes too high, or if the voltage on the VOUT terminal decreases too much, then the field effect transistors are not linearly regulated by controlling their RDS resistances, but rather the field effect transistors are turned on and off repeatedly with a duty cycle. The duty cycle is regulated in an attempt to limit the power dropped in the current switch circuit 57. In this way, the current switch circuit 57 serves a function of limiting the magnitude of a possible large inrush current (inrush power) that might otherwise flow into the system when the SSD device is initially plugged into the AC-to-DC adapter 3 when the storage capacitors 11 are fully discharged and when the COUT capacitor 21 is fully discharged. In the present example, the inrush current limit set by the resistance of resistor RSET 18 is a current (for example, two amperes) that is larger than a typical digital logic or analog signaling input terminal or output terminal could handle.

**[0028]** The CSS capacitor **17** slows down the start up slew rate of the current switch circuit **57**, thereby providing a "soft start" operation. The board designer can select the capacitance value of the CSS capacitor to tailor the start up slew rate as desired. If left open, the startup slew rate defaults to one millivolt per microsecond. The high current

value (AHC) is set by setting the resistance value of resistor RSET 18. The high current value AHC is roughly equal to one volt divided by the RSET value in ohms. If the current switch circuit 57 detects the "HC" high current condition, then it asserts the HC digital signal on conductor 65 to digital logic high, otherwise the HC digital signal is a digital logic low. The current switch circuit 57 includes a current sensor/mirror that provides a small auxiliary current flow whose magnitude is proportional to the magnitude of the main current flow through the current switch circuit 57 from the VIN terminal to the VOUT terminal. This small mirrored auxiliary current is converted into a voltage signal by making the current flow across the RSET resistor 18. The resulting voltage signal, whose magnitude is proportional to the current flow through the switch circuit 57, is output from the current switch circuit 57 via the switch current (SC) conductor 66. The voltage signal on the switch current SC conductor 66 is indicative of the magnitude of the current flowing through the current switch 57.

[0029] The buck/boost switching converter control circuit 61, together with external components 20, 21 and 23-27 is operable as a buck switching converter or as a boost switching converter. When it is operating in a boost mode, the converter receives a relatively low voltage from the VOUT terminal, and outputs a boosted up relatively high voltage onto the STR terminal 44. In one example, the voltage on the VOUT terminal is 3.3 volts DC, and the voltage that the converter drives onto the STR terminal 44 is 36 volts DC. This relatively high voltage serves to charge the capacitor bank 11 capacitors up to 36 volts. The magnitude of this charging voltage is set by the value of the RBSET resistor 19. When the converter is operating in a buck mode, the converter receives a relatively high voltage from the STR terminal 44, and outputs a bucked down relatively low voltage onto the VOUT terminal 63. In one example, the voltage on the STR terminal 44 is 36 volts (as set by the RBSET resistor), and the voltage that the converter drives onto the VOUT terminal is 3.3 volts DC. The buck/boost switching converter control circuit 61 has an active high boost disable digital signal input lead BOOST\_DIS1 67 and another active high boost disable digital input lead BOOST DIS2 68. If a digital logic high signal is present on either of these inputs, then the converter is prevented (disabled) from operating in the boost mode. The buck/boost switching converter control circuit 58 also has an active high digital signal input lead BUCK ON 69. If a digital logic high signal is present on this input 69, then the converter is made to start operating in the buck mode.

[0030] The health monitor circuit 59 includes an eightchannel sigma-delta Analog-to-Digital Converter (ADC), a set of compare-and-mask circuits, and a digital state machine. The health monitor circuit 59 autonomously monitors the voltages on eight input conductors 66, 70, and 71-76 (8 channels). If any one of these voltages is detected to be below a corresponding lower voltage limit or is detected to be above a corresponding upper voltage limit, then this undervoltage or overvoltage condition is latched into a latch of the detecting compare-and-mask circuit, and the voltage on flag terminal 50 is pulled down to ground potential. The voltage on the open-drain flag terminal 50 is otherwise not pulled down, but rather is pulled up to the VDD by external pullup resistor 22. The low voltage (ground potential) on flag terminal 50 and conductor 77 constitutes an interrupt signal 78. This active low interrupt signal 78 is supplied via conductor 77 onto the active low interrupt input terminal 79 of microcontroller 34. The low interrupt signal therefore interrupts the microcontroller 34. The microcontroller 34 can respond to the interrupt, as further explained below, by accessing the power loss protection integrated circuit 6 via the two-wire I2C bus 80. The two conductors SDL and SDA are the two conductors of the I2C bus. The values of the lower voltage limit and the upper voltage limit for each of the eight channels is user programmable (changeable via the microcontroller 34 under software control) via the I2C interface of terminals 48 and 49. In the present example, the measurable voltage range on conductor 66 corresponds to a measured through-current flowing through the current switch 57 in the range of from zero amperes to six amperes. In the present example, the measurable voltage range on conductor 70 corresponds to a measured voltage on the VIN terminal in the range of from zero volts to twenty volts. In the present example, the measurable voltage range on conductor 71 corresponds to a measured storage capacitor voltage on the STR terminal in the range of from zero volts to thirty-six volts. In the present example, the measurable voltage range on conductor 72 corresponds to a measured on-chip temperature in the range of from minus forty degrees Celsius to plus one hundred and fifty degrees Celsius.

[0031] The health monitor circuit 59 also includes a capacitor health check circuit. The capacitor health check circuit includes a digital state machine. If the power loss protection integrated circuit 6 is not operating in the normal mode as indicated by the active high NORMAL MODE digital signal on conductor 88, then the capacitor health check circuit is disabled. If, however, the power loss protection integrated circuit 6 has been operating in the normal mode for a least four minutes, at the conclusion of the four minute period the state machine disables the boost converter and enables a ten milliampere current source. The ten milliampere current source sinks current from the STR terminal 44. At the end of a time period determined by the programmable value TSET[3:0], the state machine disables the ten milliampere current source and enables a fifty milliampere current source that sinks current from the STR terminal 44. The fifty milliampere current source remains enabled for a period of time determined by the value TSET[3:0]. In one example, this time period is one tenth the period of time the ten milliampere current source was enabled. If at any time during the period of time when either of the two sinking current sources is enabled the voltage on the STR terminal 44 falls below a programmable voltage, then a latch is set. The programmable voltage is determined by the user programmable value THR[3:0]. The setting of the latch causes the voltage on the capacitor fault terminal CF 51 to be pulled down to ground potential. This is an indication of a capacitor fault condition. This active low fault signal may, for example, be supplied onto a second interrupt input terminal 87. In addition, the LED 28 is on during the time when then capacitor fault signal is asserted low.

**[0032]** The I2C interface and digital register control and digital state machine circuit **58** is a digital block that includes an I2C serial bus interface circuit and a digital state machine circuit. There are various digital registers disposed in various places across the integrated circuit. The digital outputs of various ones of the bits of these registers are coupled to various circuits in the integrated circuit so that the

stored digital values will control and affect operation of the circuitry. Other selected bits of the registers are used to capture the digital states of corresponding nodes in the circuitry. The I2C interface is usable to read and to write to any selected one of these registers via the DATA conductors **81**, the enable conductors **82**, the R/W conductor **83** and the strobe conductor **84**. The DATA conductor **81**, the R/W conductor **83**, and the strobe conductor **84** extend to all these registers. For each register, there is one dedicated enable conductor that extends from the I2C interface logic to an enable input lead of that register.

[0033] To write an 8-bit value into a particular register, the I2C interface places the data to be written onto the DATA conductors 81. Because the access is a write, the voltage on the R/W conductor 82 is driven to a digital logic low level. The enable conductors to all the registers are driven to be disabled (digital logic low), except for the one desired register that is to be written. The enable conductor to that register is driven with a digital logic high signal. After these signals are set up, the strobe signal on conductor 84 is pulsed high to clock the data into the enabled register. The 8-bit value stored in a particular register can be read by the I2C interface in similar fashion except that the I2C interface does not drive data out on the DATA conductors, but rather the I2C is setup to read in data from the DATA conductors. In addition, the digital logic value driven onto the R/W conductor is a digital logic high value. When the data bus conductors are set up this way, a pulsing of the strobe signal causes the enabled register to output its 8-bit value onto the 8-bit DATA bus, so that the 8-bit value will then be latched into the I2C interface logic. In this way, the I2C interface can read from, and can write to, any selected one of the registers on the integrated circuit.

[0034] FIG. 3 is a more detailed diagram of the current switch circuit 57 of FIG. 2. The current switch circuit 57 includes an 8-bit register 89 that is accessible via the I2C interface and digital register control and digital state machine block 58 of FIG. 2. Three of the bits are a VIN\_REF\_OV[2:0] value. This 3-bit value is supplied onto the select inputs of the 8:1 analog multiplexer 90. The multiplexer determines the magnitude of a voltage VIN\_ OV\_REF that is supplied onto an input lead of comparator 91. The voltage on the other input lead of comparator 91 is a voltage-divided version of the VIN voltage on the terminal 35. Accordingly, the 3-bit value is a programmable value that the voltage on the VIN terminal, above which the digital signal OV is asserted to indicate an overvoltage condition. The register 89 also includes a bit that is called an "override" bit. Setting this bit to a digital logic high forces the current switch circuit 57 to open (to disconnect and to decouple the VIN terminal from the VOUT terminal). The throughcurrent flowing through the NFETs 92 and 93 is sensed and mirrored, and the mirrored smaller current is then converted into a SC voltage signal by passing the mirrored current across the RESET resistor 19. The voltage signal SC is directly proportional to the magnitude of the through-current passing through the NFETs. If there is a supply voltage present on either the VIN terminal or on the STR terminal, then the LDO 94 outputs a supply voltage VDD that is used throughout the integrated circuit.

[0035] FIG. 4 is a more detailed diagram of the health monitor circuit 59 of FIG. 2. The circuit of FIG. 4 includes eight compare-and-mask circuits 95-102, a first mask register 103, a second mask register 104, an OR gate 105, a flag

flip-flop 106, a pull-down transistor 107, a sigma-delta ADC 108, a capacitor 109, an input analog multiplexer circuit 110, a decoder 111, a free-running on-chip RC relaxation oscillator 112, a channel monitor state machine 113, and a capacitor health check circuit 114. FIG. 5 is a more detailed diagram of one of the compare-and-mask circuits 95 of FIG. 4. FIG. 6 is a more detailed diagram of the input analog multiplexer circuit 110 of FIG. 4. The capacitor health check circuit sink 115, a fifty milliampere current sink 116, a capacitor health monitor state machine 117, a DAC and compare circuit 118, an AND gate 119, an SR latch 120, and a pull-down transistor 121. FIG. 7 is a more detailed diagram of the DAC and compare circuit 118 of FIG. 4.

[0036] The structure of each of the compare-and-mask circuits is the same. As shown in FIG. 5, compare-and-mask circuit 95 includes an 8-bit upper limit register 122, an 8-bit upper limit FLASH register 123, an 8-bit lower limit register 124, an 8-bit lower limit FLASH register 125, an 8-bit capture register 126, two 8-bit digital comparators 127 and 128, masking AND gate 129, masking AND gate 130, OR gate 131, an SR latch 132, and a gate 133 that causes the SR latch to be reset. Each of the registers 122-125 can be individually written with eight bits of data via the I2C interface block 58 of FIG. 2. Each of the registers 122-126 can be read via the I2C interface block 58 of FIG. 2. Also, the mask registers 103 and 104 can be separately written with eight bits of data via the I2C interface block 58 of FIG. 2. A counter in the channel monitor state machine 113 of FIG. 4 counts up from 000 up to 111 and then rolls over. Accordingly, the 3-bit SEL[2:0] values increment from 000 up to 111, and then roll over back to 000, and this repeats. In this way, the digital state machine sequentially selects the compare-and-mask circuits, one at a time. The same selecting SEL[2:0] value is also supplied onto the select inputs of the input analog multiplexer circuit 110. Consequently, the input analog multiplexer circuit 110 selects analog voltages on its analog data input leads, one at a time. In the case of the first count SEL[2:0] being 000, the input analog multiplexer circuit is controlled to receive the analog voltage on the first data input (CH1), and to supply a corresponding analog voltage onto the input of the ADC 108. At the same time, the SEL[2:0] of 000 causes the first compare-and-mask circuit #1 95 to be selected. The ADC 108 performs an analog-to-digital conversion, and outputs an 8-bit digital value onto conductors 134. The conversion complete signal output by the ADC onto conductor 135 causes the 8-bit digital value to be clocked into the capture register (see FIG. 5) of the enabled first compare-and-mask circuit 95. A comparison is made by the compare-and-mask circuit as described below, and the new OR-ed result of all eight compare-and-mask circuits is clocked into the flag flip-flop 106 at the conclusion of the one hundred millisecond ADC conversion operation. The digital state machine 113 then increments the SEL[2:0] value, and this process is repeated, except the second channel (CH2) is selected and the ADC result is captured into the second compare-and-mask circuit 96. The voltage dividers 136-143 of the input analog multiplexer circuit 110 scale the input voltage ranges of the various channels such that the range of the multiplexed analog signal at the input of the ADC is in the 0 volt to 2.5 volt range. As shown in FIG. 6, the input analog multiplexer circuit 110, in addition to the eight voltage dividers 136-143, includes an analog multiplexer 159 made up of N-channel field effect transistors **144-151** and a decoder **160**. The digital state machine **113** controls the overall circuit such that each successive input channel voltage conversion is captured into the capture register of each successive compare-and-mask circuit.

[0037] Consider the case in which a given 8-bit ADC output value is clocked into the capture register **126** of FIG. 5. Comparator 127 compares the capture value to the value in the upper limit register 122. If the capture value is greater than the upper limit value, then a digital logic high is output by the comparator 127. Comparator 128 compares the capture value to the value in the lower limit register 12. If the capture value is smaller than the lower limit value, then a digital logic high is output by the comparator 128. Each of the comparator output can be separately and independently masked by setting an corresponding bit in the appropriate mask registers. If both of the mask bits MASK1 and MASK2 of FIG. 5 are digital logic highs, however, there is no masking. OR gate 131 outputs a digital logic high value if the capture value is detected to be either lower than the lower limit value or if it is higher than the upper limit value. If the output of the OR gate 131 is a digital logic high, then the SR latch 132 is set. Otherwise it is not set. The setting of the SR latch 132 indicates a condition of the capture value being out of the range between the upper limit value and the lower limit value. As seen in the circuit diagram of FIG. 4, the outputs of all of the eight SR latches of the eight compare-and-mask circuits are ORed by OR gate 105, and if one or more of the ST latches are set, then the flag flip-flop 106 is set at the end of the conversion cycle. The setting of the flag flip-flop 106 causes the pull-down transistor 107 to be turned on, which in turns causes the interrupt signal 78 (see FIG. 1) to be asserted, which in turn interrupts the microcontroller 34. The microcontroller 34 responds to the interrupt by reading one or more registers within the power loss protection integrated circuit 6 via the I2C block 58. In the present example, the microcontroller causes the I2C block 58 to read the 8-bit capture value in register 126. The 8-bit value is returned to the I2C block 58 via the DATA lines 81, and then the 8-bit value is communicated back across the I2C bus 80 to the microcontroller 34. The gate 133 within the compare-and-mask circuit that was read detects that its capture register is being read, and this causes the gate 133 to pulse a digital logic high pulse onto the reset input of the SR latch 132. This clears (resets) the latch. One of the registers (not shown) of the integrated circuit is a read-only register consisting of the eight SR latch values, considered together as an 8-bit value. The microcontroller 34 can read this one "register" and thereby obtain the values of the eight SR latches. From this information, the microcontroller 34 can determine which one of the eight compare-and-mask circuits it was that caused the fault. From this information, the microcontroller 34 can read the capture register of that compare-and-mask circuit, thereby obtaining the 8-bit capture value and at the same time resetting the SR latch.

[0038] Note that the undervoltage signal UV and the high current signal HC are supplied to inputs leads of the OR gate 105 of FIG. 4. An undervoltage condition or a high current condition will also cause the flag flip-flop 106 to be set.

**[0039]** The capacitor health check circuit **114** has its own controlling state machine **117**. If the overall integrated circuit is not operating in the normal mode as indicated by the digital signal NORMAL MODE on conductor **88**, then the state machine **177** prevents the capacitor health check

circuit 114 from performing an capacitor health check operation. If, on the other hand, the overall integrated circuit is operating in the normal mode as indicated by the digital signal NORMAL MODE on conductor 88, then at end of each four period the state machine 177 disables the converter from operating in the boost mode by asserting the BOOST\_DIS2 signal, and enables the ten milliampere current sink 115. The current drain of this current sinking from the STR terminal causes the voltage on the external capacitor bank 11 to decrease. This current drain condition is maintained for a period of time determined by a 4-bit TSET[3:0] value in a register of the capacitor health check circuit. At the end of this time period, the state machine 117 disables the ten milliampere current sink and simultaneously enables the fifty milliampere current sink 116. The fifty milliampere current sink 116 then draws more current from the external capacitor bank 11 via terminal STR. This condition persists for one tenth of the time period through which the ten milliampere current source was enabled. If at any time during these two time periods the DAC and compare circuit 118 detects that the voltage on the STR terminal has fallen below a programmable voltage, then the CAP LOW digital signal is asserted and the SR latch 120 is set. The setting of the SR latch 120 indicates a capacitor fault condition. The pull-down transistor 121 is turned on, and the capacitor fault signal CF is asserted low. The programmable voltage is set, via the I2C interface block 58, by setting the 4-bit value THR[3:0] in a programmable register (not shown) of the capacitor health check circuit 114. The signal STR\_FB coming into the DAC and compare circuit 118 of FIG. 7 is a voltage-divided version of the voltage on the STR terminal 44. If the voltage on the STR terminal is detected during these two periods as having gone below an STR undervoltage value STR\_UV, then the DAC and compare circuit 118 of FIG. 7 asserts the STR\_UV digital signal and this signal is communicated to the OR gate 105 of FIG. 4, which in turn causes the flag signal on flag terminal 50 to be asserted low. If the voltage on the STR terminal is detected during these two periods as having gone above an STR overvoltage value STR\_OV, then the DAC and compare circuit 118 of FIG. 7 asserts the STR\_OV digital signal and this signal is communicated to the OR gate 105 of FIG. 4, which in turn causes the flag signal on flag terminal 50 to be asserted low. The value of the SR latch 120 can be read via the I2C block 58 in the same way that the SR latches of the compare-and-mask circuits 95-102 can be read. The reading of the SR latch 120 is detected by AND gate 119, which causes the SR latch 120 to be reset at the end of the reading. In FIG. 7, the notation "110%" on a node of the voltage divider indicates that the voltage on that node is 110 percent of the voltage VDD, the notation "107%" on a node indicates that the voltage on that node is 107 percent of the voltage VDD, and so forth.

**[0040]** FIG. **8** is a state diagram that sets forth the operation of the capacitor health monitor state machine **117** of the capacitor health check circuit **114**. The signal name assignments in each state indicate the state to which the state machine forced that signal when the state machine is in that state. For example, in the IDL state, the notations "BOOST\_DIS2=0", "10MA=0" and "50MA=0" indicate that the digital signal BOOST\_DIS2 is forced to be a digital logic low, and the ten milliampere current sink is disabled, and the fifty milliampere current sink is disabled.

**[0041]** FIG. **9** is a table that indicates, for each 4-bit TSET[3:0] value, the corresponding time period throughout which the ten milliampere current sink is enabled.

[0042] FIG. 10 is a diagram that illustrates one capacitor health check operation as carried out by the capacitor health check circuit 114. Time T1 is the end of a four minute period during which the overall integrated circuit has been operating in the normal mode, and during which the boost converter has been enabled. Due to the boost converter having been enabled this long, the capacitor bank 11 should be fully charged to the voltage level set by the resistor RBSET 19. In the present example, this is 36 volts. At time T1, the capacitor health monitor state machine 117 disables the boost converter (by asserting BOOST\_DIS2) and enables the ten milliampere current sink 115. The ten milliampere current sink 115 remains enabled for the time period determined by the TSET[3:0] value. This period of time ends at time T2. The state machine 117 then disables the ten milliampere current sink 115 and enables the fifty milliampere current sink 116. This condition of having the fifty milliampere current source enabled persists for one tenth of the TSET determined time. The diagram of FIG. 10 is not drawn to scale. This second period of time ends at time T3. The CF signal on terminal 51 may be asserted at any time between time T1 and time T3. Once it is asserted low, it remains asserted low due the setting of SR latch 120. At time T3, the capacitor health check operation is over, and the overall integrated circuit resumes operating in the normal mode. This means that the boost converter resumes operation. The capacitor bank 11 is therefore charged back up to the fully charged capacitor voltage (in this case, 36 volts). [0043] FIG. 11 is a diagram of the switching converter control circuit 61 of FIG. 2. In the boost mode of operation, the controller 61 and the external components 20, 21, 23-27 operate as a boost converter. The relatively low DC voltage on terminal 63 and external capacitor 21 is boosted up to a relatively high voltage (for example, 36 volts DC), which is driven out onto the STR terminal 44 so as to charge the capacitor bank 11 up to the relatively high voltage. In the buck mode of operation, the controller 61 and the external components 20, 21, 23-27 operate as a buck converter. The relatively high voltage on capacitor bank 11 and the STR terminal 44 is bucked down to a relatively low DC voltage. This relatively low voltage is driven onto the VOUT terminal 63 and external capacitor 21. The magnitude of the relatively low voltage, which in the present example is 3.3 volts, is set by the external resistors 25 and 26 (see FIG. 2). Advantageously, the same inductor 24 is used in both the boost mode and in the buck mode. The switching converter control circuit 61 of FIG. 11 includes an 8-bit register 152. The microcontroller 34 can write an 8-bit value into this 8-bit register 152 via the I2C bus 80 and the I2C interface block 58. The register 152 includes an override bit 153. When this bit is set, the boost converter is forced on. The register 152 also includes override bit 154. When this bit is set, the buck converter is forced on. If set, either of these override bits takes precedence over the BOOST\_DIS1 signal, the BUCK\_ON signal, the BOOST\_DIS2 signal, and normal mode operation of the circuit 61. It is an illegal condition that both these override bits 153 and 154 be set at the same time.

**[0044]** The magnitude of the relatively high voltage to which the converter boosts in the boost mode is user programmable, and is set by providing only one external

resistor RBSET **19** of the appropriate resistance. The magnitude of the resistance of this one RBSET resistor corresponds directly to the magnitude of the relatively high voltage to which the STR terminal is driven in the boost mode. The relatively high voltage to which the STR terminal is driven in the boost mode is a gained-up version of the voltage on the BSET terminal **45**. If no external resistor RBSET is provided, then a twenty-microampere current source **155** pulls the voltage on BSET terminal **45** up to the LDO voltage level VDD of the VDD supply bus and node **156**.

[0045] FIG. 12 is a more detailed diagram of the voltage reference circuit 62 of FIG. 2. The voltage reference circuit 62 includes a bandgap voltage reference 157 and a comparator 158.

[0046] FIG. 13 is a block diagram of the I2C interface and digital register control and digital state machine circuit 58 of FIG. 2. The block 58 includes an I2C interface portion 161 and a digital state machine portion 162.

**[0047]** Although certain specific embodiments are described above for instructional purposes, the teachings of this patent document have general applicability and are not limited to the specific embodiments described above. Accordingly, various modifications, adaptations, and combinations of various features of the described embodiments can be practiced without departing from the scope of the invention as set forth in the claims.

1-21. (canceled)

22. An integrated circuit comprising:

an output voltage terminal (VOUT);

a storage capacitor terminal (STR);

a switch terminal (SW);

- a feedback terminal (FB);

- a buck/boost controller coupled to the switch terminal SW and to the feedback terminal FB; and

- an autonomous capacitor health check circuit adapted to sink a current from the storage capacitor terminal STR.

23. The integrated circuit of claim 22, wherein the current that the autonomous capacitor health check circuit is adapted to sink from the storage capacitor terminal STR comprises a first predetermined current during a first portion of a predetermined time duration and a second predetermined current during a second predetermined time duration, and wherein the maximum input current is at least two amperes.

24. The integrated circuit of claim 22, wherein the autonomous capacitor health check circuit comprises:

a register, wherein a value stored in the register determines a predetermined time duration, wherein during the predetermined time duration, the autonomous capacitor health check circuit detects whether a voltage on the storage capacitor terminal STR drops below a predetermined threshold voltage.

**25**. The integrated circuit of claim **22**, wherein the autonomous capacitor health check circuit comprises:

a register, wherein a value stored in the register determines a magnitude of the current that is sinked from the storage capacitor terminal STR.

**26**. The integrated circuit of claim **23**, wherein the autonomous capacitor health check circuit comprises:

a plurality of registers, wherein a first value stored in the plurality of registers determines a magnitude of the first predetermined current, and wherein a second value stored in the plurality of registers determines a magnitude of the second predetermined current.

27. The integrated circuit of claim 24, wherein the autonomous capacitor health check circuit comprises:

a register, wherein a value stored in the register determines the predetermined threshold voltage.

**28**. The integrated circuit of claim **22**, wherein the autonomous capacitor health check circuit periodically performs a capacitor check by sinking a current from the storage capacitor terminal STR and detecting whether a voltage on the storage capacitor terminal STR drops below a predetermined threshold voltage within a time duration, wherein the autonomous capacitor health check circuit performs the periodic checking without repeated external prompting from any device outside the integrated circuit.

**29**. The integrated circuit of claim **22**, wherein the autonomous capacitor health check circuit comprises:

a current source adapted to sink the current from the storage capacitor terminal STR.

**30**. The integrated circuit of claim **22**, wherein the buck/ boost controller is not coupled to an external inductor but rather is adapted to be coupled to the external inductor, wherein the buck/boost controller is not operating as part of any buck converter or as part of any boost converter but rather is adapted to operate as part of a buck converter and as part of a boost converter, and wherein the storage capacitor terminal STR is not coupled to an external storage capacitor but rather is adapted to be coupled to an external storage capacitor.

31. An integrated circuit, comprising:

a first terminal;

a second terminal;

an eFuse circuit that can receive a current from the first terminal and can conduct the current to the second terminal in a non-fault condition, and that is adapted to decouple the first terminal from the second terminal in a fault condition;

a third terminal;

a fourth terminal; and

an autonomous capacitor health check circuit adapted to perform a capacitor health check operation, wherein a capacitor health check operation involves sinking a current from the fourth terminal for a predetermined time duration, and during the predetermined time duration detecting whether a voltage on the fourth terminal drops below a predetermined threshold voltage.

**32.** The integrated circuit of claim **31**, wherein the autonomous capacitor health check circuit comprises a register, wherein a multi-bit digital value stored in the register determines the predetermined threshold voltage.

**33.** The integrated circuit of claim **31**, wherein the autonomous capacitor health check circuit comprises a register, wherein a multi-bit digital value stored in the register determines the predetermined time duration.

**34**. The integrated circuit of claim **31**, wherein the autonomous capacitor health check circuit comprises a bit, wherein a setting of the bit causes digital logic signal to be asserted onto the third terminal, and wherein a reading of the bit causes the bit to be reset.

**35**. The integrated circuit of claim **31**, wherein the autonomous capacitor health check circuit comprises a first current source and a second current source, wherein the first current source is coupled to sink a first predetermined current from

an input voltage terminal (VIN);

a current switch circuit;

the fourth terminal during the health check operation, and wherein the second current source is coupled to sink a second predetermined current from the fourth terminal during the health check operation.

36. The integrated circuit of claim 31, further comprising:

- a boost controller, wherein the autonomous capacitor health check circuit supplies a digital boost disable signal to the boost controller.

- **37**. The integrated circuit of claim **31**, further comprising: a switching converter control circuit, wherein the autonomous capacitor health check circuit supplies a digital boost disable signal to the switching converter control circuit.

38. The integrated circuit of claim 31, further comprising:

- a serial bus interface, where a multi-bit digital value stored in a plurality of sequential logic elements determines the predetermined time duration of the capacitor health check operation, and wherein the multi-bit digital value stored in the plurality of sequential logic elements can be changed via the serial bus interface.

- **39**. The integrated circuit of claim **31**, further comprising: a serial bus interface, where a multi-bit digital value stored in a plurality of sequential logic elements determines the predetermined threshold voltage of the capacitor health check operation, and wherein the multi-bit digital value stored in the plurality of sequential logic elements can be changed via the serial bus interface.

**40**. The integrated circuit of claim **31**, wherein the current that the eFuse circuit can receive from the first terminal and can conduct to the second terminal in the non-fault condition can be a current of two amperes, wherein the eFuse circuit can conductor the two ampere current conduct a current with a resistance of less than one ohm between the first and second terminals.

41. An integrated circuit, comprising:

- a boost controller;

- a terminal; and

- means for performing periodic autonomous capacitor health check operations on a capacitor coupled to the terminal, wherein a capacitor health check operation involves conducting a current from the terminal and detecting a voltage on the terminal.

**42**. The integrated circuit of claim **41**, further comprising: a second terminal: and

a third terminal, wherein the eFuse circuit can receive a current from the second terminal and can conduct the current to the third terminal in a non-fault condition, wherein the current can be a current of two amperes that is conducted through the eFuse circuit with a resistance of less than one ohm between the second the third terminals.

\* \* \* \* \*

an eFuse circuit;