## (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2016/0343573 A1 HORII et al.

Nov. 24, 2016 (43) **Pub. Date:**

### (54) SEMICONDUCTOR DEVICE HAVING ELECTRODE MADE OF HIGH WORK FUNCTION MATERIAL, METHOD AND APPARATUS FOR MANUFACTURING THE **SAME**

- (71) Applicant: HITACHI KOKUSAI ELECTRIC INC., TOKYO (JP)

- (72) Inventors: Sadayoshi HORII, TOYAMA (JP); Arito OGAWA, TOYAMA (JP); Hideharu ITATANI, TOYAMA (JP)

- (73) Assignee: HITACHI KOKUSAI ELECTRIC INC., TOKYO (JP)

- (21) Appl. No.: 15/228,840

- (22) Filed: Aug. 4, 2016

### Related U.S. Application Data

(60) Division of application No. 14/629,345, filed on Feb. 23, 2015, now Pat. No. 9,437,704, Continuation of application No. 12/984,018, filed on Jan. 4, 2011, now abandoned.

#### (30)Foreign Application Priority Data

Jan. 7, 2010 (JP) ...... 2010-002256

#### **Publication Classification**

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

| ` ′  | H01L 21/28  | (2006.01) |

|      | C23C 16/455 | (2006.01) |

|      | C23C 16/06  | (2006.01) |

|      | C23C 16/34  | (2006.01) |

|      | H01L 49/02  | (2006.01) |

|      | H01L 29/49  | (2006.01) |

(52) U.S. Cl.

CPC ...... H01L 21/28088 (2013.01); H01L 28/75 (2013.01); H01L 29/4966 (2013.01); C23C 16/06 (2013.01); C23C 16/34 (2013.01); C23C 16/45529 (2013.01)

#### (57)**ABSTRACT**

Provided is a semiconductor device including a metal film which can be formed with lower costs but still manage to have a necessary work function and oxidation resistance. The semiconductor device includes an insulating film disposed on a substrate; and a metal film disposed on the insulating film. The metal film includes a stacked structure of: a first metal film disposed on the insulating film to directly contact the insulating film; a second metal film disposed on the first metal film to directly contact the first metal film; and the first metal film disposed on the second metal film to directly contact the second metal film, the second metal film having a work function greater than 4.8 eV and being different from the first metal film in material, wherein an oxidation resistance of the first metal film is greater than that of the second metal film.

Fig. 1

vd2

220d

$22^{\circ}$ PUMP 213d APC 202 262-210 SUB-HEATER 206a 263. vb5 203 Ni(PF3)4 220b 220a TiCl4 val 220e vel

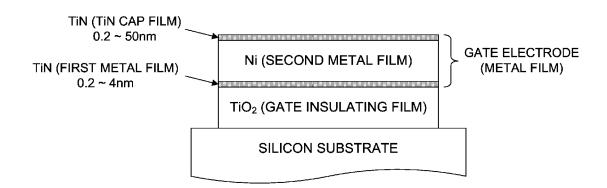

GATE ELECTRODE (METAL FILM) TiO<sub>2</sub> (GATE INSULATING FILM) Ni (SECOND METAL FILM) SILICON SUBSTRATE TIN (FIRST METAL FILM) TiN (TiN CAP FILM)  $0.2 \sim 50 \text{nm}$ 0.2 ~ 4nm

GATE ELECTRODE (METAL FILM) TiO<sub>2</sub> (GATE INSULATING FILM) SILICON SUBSTRATE Fig. 5B Ni (SECOND METAL FILM) -TIN (FIRST METAL FILM) / TIN (TIN CAP FILM) Z

Fig. 6A

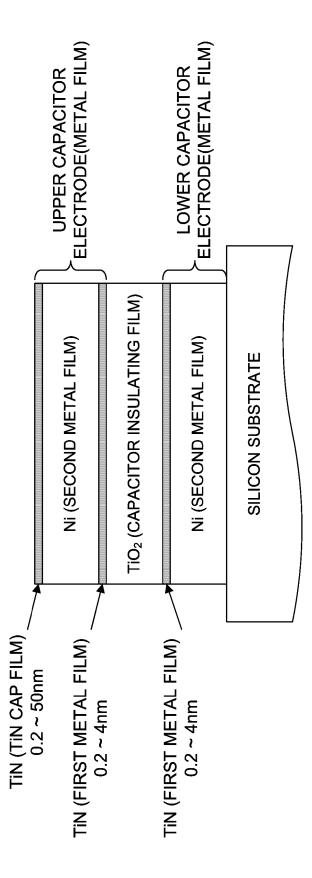

ELECTRODE(METAL FILM) ELECTRODE(METAL FILM) LOWER CAPACITOR UPPER CAPACITOR TiO<sub>2</sub> (CAPACITOR INSULATING FILM) SILICON SUBSTRATE iz iz iz Ž H TIN (FIRST METAL FILM) Z TIN (TIN CAP FILM) NI (SECOND METAL FILM) Z

- · VACUUM LEVEL Z H Z

| METAL | ELECTRONEGATIVITY WORK FUNCTION (eV) | WORK FUNCTION (eV) |

|-------|--------------------------------------|--------------------|

| Be    | 1.57                                 | 4.98               |

| O     | 2.55                                 | 2                  |

| °C°   | 1.88                                 | 5                  |

| Ë     | 1.91                                 | 5.15               |

| Se    | 2.55                                 | 5.9                |

| Те    | 2.1                                  | 4.95               |

| Re    | 1.9                                  | 4.96               |

Fig. 11

Bottom Metal deposition (TiN)

High-k Deposition Al doped  $HfO_2$  (Hf/Al=19/1)

PDA (700°C)

Top Metal deposition TiN, Ni/TiN-laminate (Ni or TiN start)

TiN deposition 50nm

Gate patterning

FGA (400°C)

Back Side Al deposition

**1**0nm 50nm 1/1nm x 5 cycles +TiN <Laminate Structure> Laminate (Ni start) Sample C Ni/TiN = Si-sub High-k Z |-Z / \ <u>Z</u> <del>Z</del> : N Z direction of electron flow 1/1nm x 5 cycles +TiN <Laminate Structure> Laminate (TiN start) Fig. 12 Sample B = iN/Ni Si-sub High-k Z H Z ï Ņ : Ż ź Sample A TiN High-k Si-sub Ζ Z F

Top electrode

**Fig. 14**

Fig. 15

**Fig. 16A**

# Sample D

Ni TiN  ${\rm SiO_2}$ Si-sub

**Fig. 17A**

**Fig. 18**

### SEMICONDUCTOR DEVICE HAVING ELECTRODE MADE OF HIGH WORK FUNCTION MATERIAL, METHOD AND APPARATUS FOR MANUFACTURING THE SAME

## CROSS-REFERENCE TO RELATED PATENT APPLICATION

[0001] This U.S. non-provisional patent application and is a division of U.S. patent application Ser. No. 14/629,345 filed on Feb. 23, 2015 which is a Continuation of U.S. patent application Ser. No. 12/984,018 filed on Jan. 4, 2011, and claims priority under 35 U.S.C. §119 of Japanese Patent Application No. 2010-002256, filed on Jan. 7, 2010, respectively, in the Japanese Patent Office, the entire contents of which are hereby incorporated by reference.

### BACKGROUND OF THE INVENTION

[0002] Field of the Invention

[0003] The present invention relates to a semiconductor device, a method of manufacturing a semiconductor device, and a substrate processing apparatus.

[0004] Description of the Related Art

[0005] To highly integrate metal-oxide-semiconductor field effect transistors (MOSFETs) and increase the performance of the MOSFETs, the use of a high-k/metal gate structure is considered, which is constituted by a gate insulating film made of a high permittivity insulating material (high-k material) and a gate electrode made of a metal. In the case of a p-channel metal-oxide semiconductor (PMOS) transistor, it is preferable that a gate electrode is made of a metal having a high work function of about 4.8 eV to 5.1 eV, and for example, it is considered that a gate electrode is made of a noble metal such as platinum (Pt).

[0006] Furthermore, in the case of a dynamic random access memory (DRAM), it is considered that a capacitor insulating film is made of a high permittivity insulating material such as a hafnium dioxide (HfO2), a zirconium dioxide (ZrO<sub>2</sub>), a titanium dioxide (TiO<sub>2</sub>), a tantalum pentoxide (Ta<sub>2</sub>O<sub>5</sub>), and a niobium pentoxide (Nb<sub>2</sub>O<sub>5</sub>). In addition, a leak current of a capacitor part can be effectively reduced by forming a capacitor electrode using a metal having a high work function. Thus, when a capacitor insulating film is made of HfO<sub>2</sub> or ZrO<sub>2</sub> having a wide band gap, a capacitor electrode is made of a material such as a titanium nitride (TiN) having a work function of about 4.6 eV. In addition, when a capacitor insulating film is made of TiO<sub>2</sub> or Nb<sub>2</sub>O<sub>5</sub> having a narrow band gap, a capacitor electrode is made of a noble metal such as Pt having a high work function of about 5.1 eV.

[0007] However, if a metal film (for example, a gate electrode, a capacitor electrode, etc.) is made of an expensive noble metal such as Pt, the manufacturing costs of a semiconductor device may be increased. In addition, it is difficult to form a thin film by using a noble metal such as Pt. It can be considered that another metal having a high work function such as nickel (Ni) or cobalt (Co) is used instead of a noble metal such as Pt. However, such a metal is easily oxidized, and if a metal film (a gate electrode or a capacitor electrode) is oxidized, the equivalent oxide thickness (EOT) of the metal film may be increased.

### SUMMARY OF THE INVENTION

[0008] An object of the present invention is to provide a semiconductor device including a metal film which can be formed with lower costs but have a necessary work function and oxidation resistance. Another object of the present invention is to provide a method of manufacturing a semiconductor device and a substrate processing apparatus, which are designed to form a metal film having a necessary work function and oxidation resistance with lower costs.

[0009] According to an aspect of the present invention, there is provided a semiconductor device including: an insulating film disposed on a substrate; and a metal film disposed on the insulating film, the metal film including a stacked structure of: a first metal film disposed on the insulating film to directly contact the insulating film; a second metal film disposed on the first metal film to directly contact the first metal film to directly contact the second metal film; and the first metal film disposed on the second metal film to directly contact the second metal film, the second metal film having a work function greater than 4.8 eV and being different from the first metal film in material, wherein an oxidation resistance of the first metal film is greater than that of the second metal film.

[0010] According to another aspect of the present invention, there is provided a method of manufacturing a semiconductor device, the method including: forming an insulating film on a substrate; and forming a metal film including a stacked structure of: a first metal film disposed on the insulating film to directly contact the insulating film; and a second metal film disposed on the first metal film to directly contact the first metal film, the second metal film having a work function greater than 4.8 eV and being different from the first metal film in material, wherein an oxidation resistance of the first metal film is greater than that of the second metal film.

[0011] According to another aspect of the present invention, there is provided a substrate processing apparatus including: a process chamber configured to process a substrate; a first process gas supply system configured to supply a first process gas into the process chamber to form a first metal film; a second process gas supply system configured to supply a second process gas into the process chamber to form a second metal film; and a controller configured to control the first process gas supply system and the second process gas supply system, wherein an oxidation resistance of the first metal film is greater than that of the second metal film, the second metal film has a work function greater than 4.8 eV and is different from the first metal film in material, and the controller controls the first process gas supply system and the second process gas supply system to form a metal film having a stacked structure of the first metal film and the second metal film adjacent to an insulating film disposed on the substrate by supplying the first process gas and the second process gas into the process chamber where the substrate is accommodated such that the first metal film is formed between the second metal film and the insulating

### BRIEF DESCRIPTION OF THE DRAWINGS

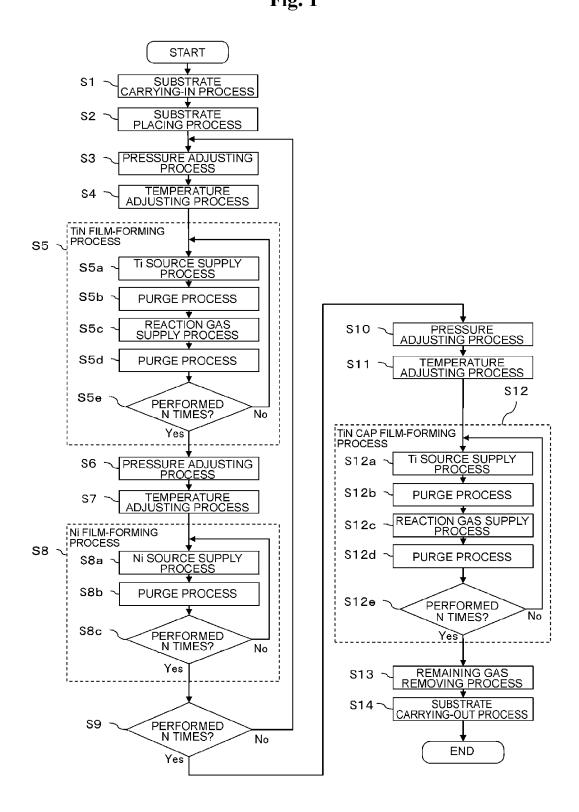

[0012] FIG. 1 is a flowchart for explaining substrate processing processes according to an embodiment of the present invention.

[0013] FIG. 2 is a view illustrating a gas supply system of a substrate processing apparatus relevant to the embodiment of the present invention.

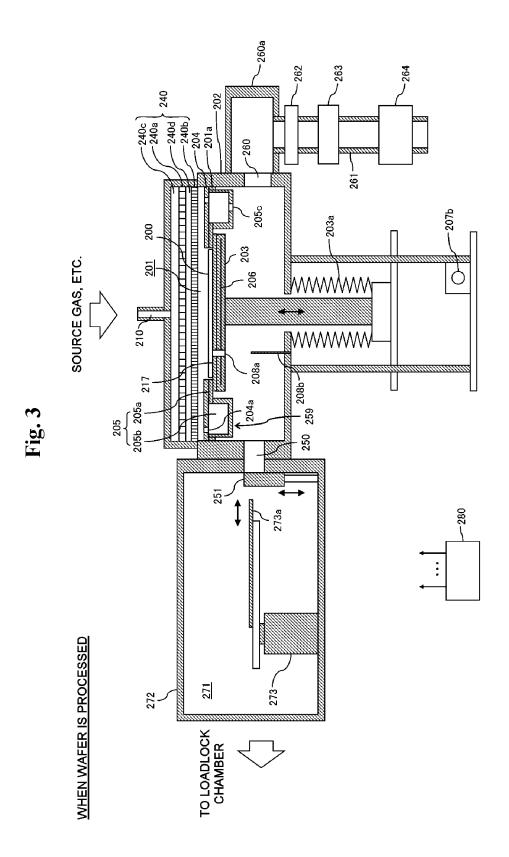

[0014] FIG. 3 is a sectional view illustrating the substrate processing apparatus when a wafer is processed according to the embodiment of the present invention.

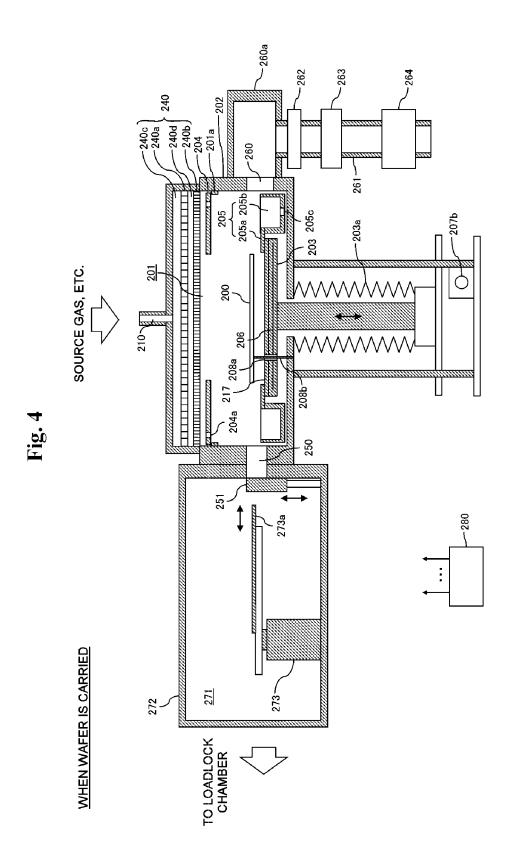

[0015] FIG. 4 is a sectional view illustrating the substrate processing apparatus when a wafer is carried according to the embodiment of the present invention.

[0016] FIG. 5A is a sectional view illustrating a gate electrode formed by performing a TiN film-forming process and a Ni film-forming process once, and FIG. 5B is sectional view illustrating a gate electrode formed by performing the TiN film-forming process and the Ni film-forming process a plurality of times.

[0017] FIG. 6A is a sectional view illustrating a capacitor electrode formed by performing a TiN film-forming process and a Ni film-forming process once, and FIG. 6B is sectional view illustrating a capacitor electrode formed by performing the TiN film-forming process and the Ni film-forming process a plurality of times.

[0018] FIG. 7 is a schematic view illustrating the energy level of a conventional capacitor electrode constituted by a single layer of TiN film.

[0019] FIG. 8 is a schematic view illustrating the energy levels of a metal film formed by performing a TiN film-forming process and a Ni film-forming process once.

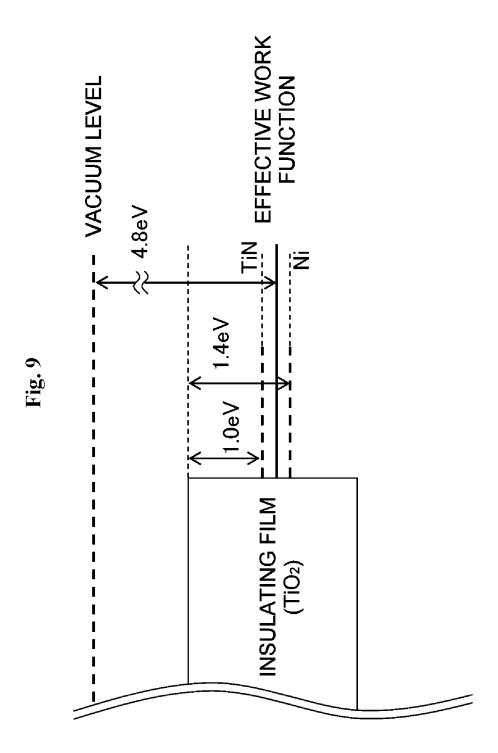

[0020] FIG. 9 is a schematic view illustrating the energy levels of a metal film formed by setting a TiN film-forming process and a Ni film-forming process as one cycle and performing the cycle a plurality of times.

[0021] FIG. 10 is a table illustrating a group of metals having work functions higher than 4.8 eV which can be used for forming a second metal film.

[0022] FIG. 11 is a flowchart for explaining processes of forming an example 1 (sample B) and a comparative example (sample C) illustrated in FIG. 12.

[0023] FIG. 12 is a schematic view for explaining the stacked structure of the example 1 (sample B) of the present invention together with the stacked structure of a conventional example (sample A) and the stacked structure of the comparative example (sample C).

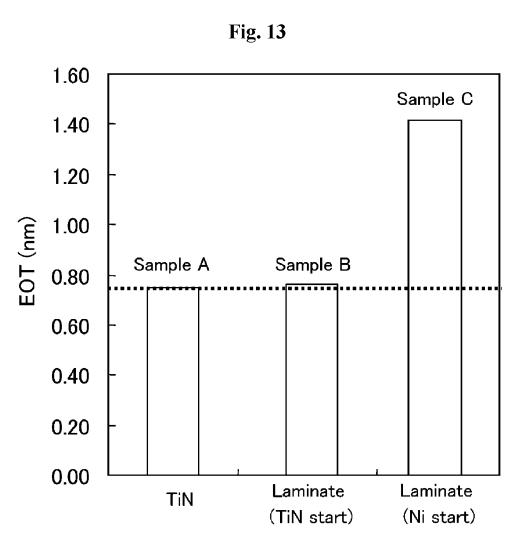

[0024] FIG. 13 is a graph illustrating the equivalent oxide thicknesses (EOTs) of the samples A, B, and C illustrated in FIG. 12.

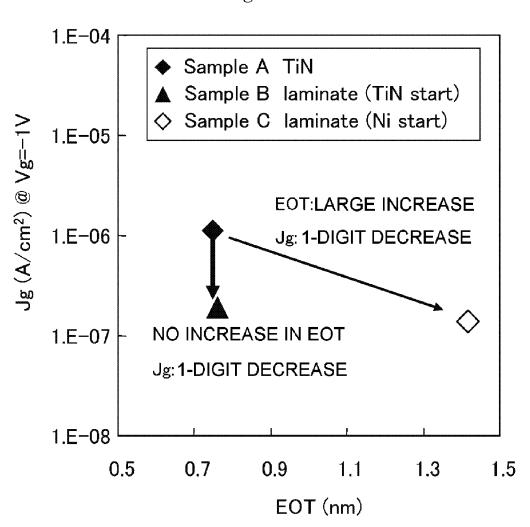

[0025] FIG. 14 is a graph illustrating relationships between leak current densities and EOTs of the respective samples A, B, and C illustrated in FIG. 12.

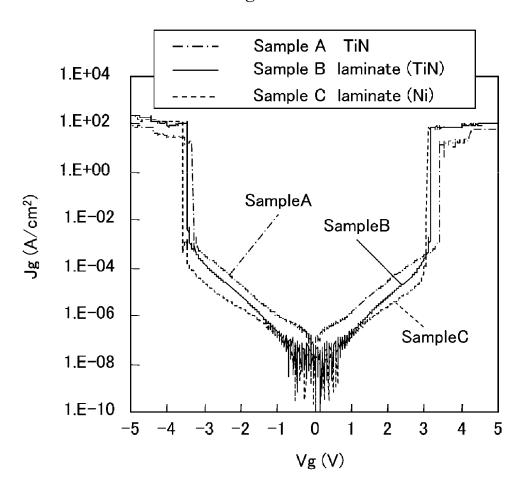

[0026] FIG. 15 is a graph illustrating relationships between leak current densities and applied voltages of the respective samples A, B, and C illustrated in FIG. 12.

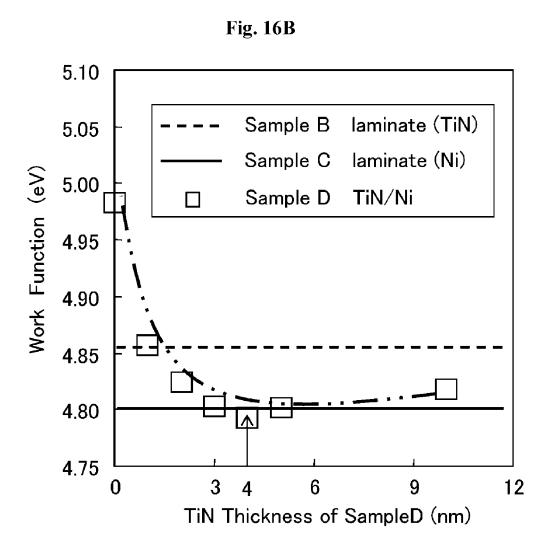

[0027] FIG. 16A is a schematic view illustrating the stacked structure of an example 2 (sample D) of the present invention, and FIG. 16B is a graph illustrating a relationship between work function and TiN film thickness of the sample D together with those of the sample B and sample C.

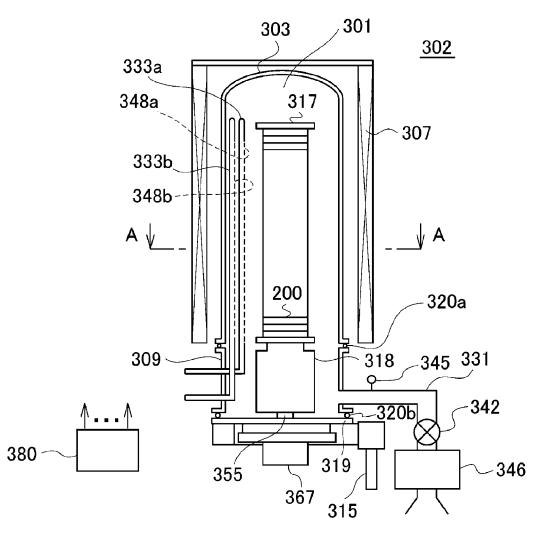

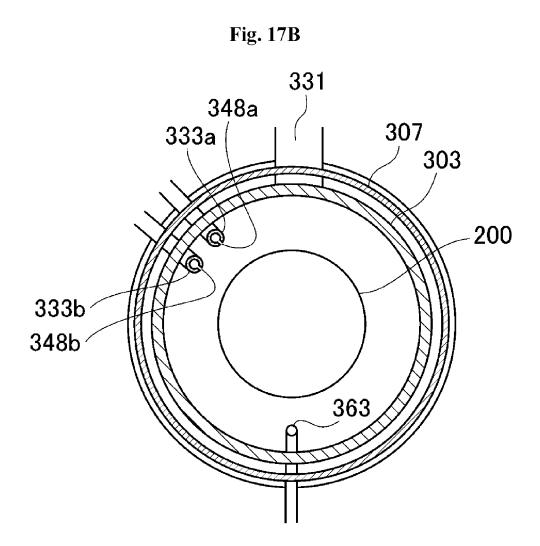

[0028] FIG. 17A and FIG. 17B are schematic views illustrating a vertical process furnace of a vertical apparatus according to another embodiment of the present invention, in which FIG. 17A is a vertical sectional view illustrating the vertical process furnace and FIG. 17B is a sectional view of the vertical process furnace taken along line A-A of FIG. 17A.

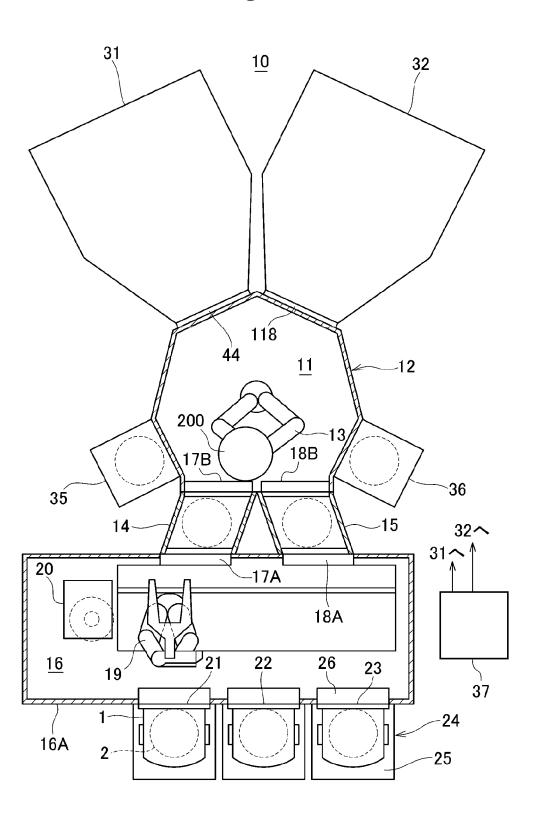

[0029] FIG. 18 is a schematic view illustrating a cluster apparatus according to another embodiment of the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

### Embodiment of Invention

### (1) Structure of Substrate Processing Apparatus

[0030] First, the structure of a substrate processing apparatus relevant to the current embodiment will be described with reference to FIG. 3 and FIG. 4. FIG. 3 is a sectional view illustrating the substrate processing apparatus when a wafer is processed according to an embodiment of the present invention, and FIG. 4 is a sectional view illustrating the substrate processing apparatus when the wafer is carried according to the embodiment of the present invention.

[0031] (Process Chamber)

[0032] As shown in FIG. 3 and FIG. 4, the substrate processing apparatus relevant to the current embodiments includes a process vessel 202. For example, the process vessel 202 is a flat airtight vessel having a circular cross sectional shape. In addition, the process vessel 202 is made of a metal material such as aluminum or stainless steel (e.g., SUS described in the Japanese industrial standard). In the process vessel 202, a process chamber 201 is formed to process a substrate such as a wafer 200 (e.g., a silicon wafer).

[0033] (Support Stage)

[0034] In the process chamber 201, a support stage 203 is installed to support a wafer 200. On the top surface of the support stage 203 that makes direct contact with the wafer 200, a susceptor 217 made of a material such as quartz (SiO $_2$ ), carbon, a ceramic material, silicon carbide (SiC), aluminum oxide (Al $_2$ O $_3$ ), or aluminum nitride (AlN) is installed as a support plate.

[0035] In the support stage 203, a heater 206 is built as a heating unit (heating source) configured to heat the wafer 200. The lower end part of the support stage 203 penetrates the bottom side of the process vessel 202.

[0036] (Elevating Mechanism)

[0037] At the outside of the process chamber 201, an elevating mechanism 207b is installed to raise and lower the support stage 203. By operating the elevating mechanism 207b to raise and lower the support stage 203, the wafer 200 supported on the susceptor 217 can be raised and lowered. When the wafer 200 is carried, the support stage 203 is lowered to a position (wafer carrying position) shown in FIG. 4, and when the wafer 200 is processed, the support stage 203 is raised to a position (wafer processing position) shown in FIG. 3. The lower end part of the support stage 203 is surrounded by a bellows 203a so that the inside of the process chamber 201 can be hermetically maintained.

[0038] (Lift Pins)

[0039] In addition, on the bottom surface (floor surface) of the process chamber 201, for example, three lift pins 208b are installed in a manner such that the lift pins 208b are vertically erected. Furthermore, in the support stage 203 (including the susceptor 217), penetration holes 208a are respectively formed at positions corresponding to the lift pins 208b so that the lift pins 208b can be inserted through the penetration holes 208a. Therefore, when the support stage 203 is lowered to the wafer carrying position, as shown

in FIG. 4, upper parts of the lift pins 208b protrude from the top surface of the susceptor 217 so that the lift pins 208b can support the wafer 200 from the bottom side of the wafer 200. [0040] In addition, when the support stage 203 is raised to the wafer processing position, as shown in FIG. 3, the lift pins 208b are retracted from the top surface of the susceptor 217 so that the susceptor 217 can support the wafer 200 from the bottom side of the wafer 2. Since the lift pins 208b make direct contact with the wafer 200, it is preferable that the lift pins 208b are made of a material such as quartz or alumina. [0041] (Wafer Carrying Entrance)

[0042] At a side of the inner wall of the process chamber 201 (process vessel 202), a wafer carrying entrance 250 is installed so that a wafer 200 can be carried into and out of the process chamber 201 through wafer carrying entrance 250. At the wafer carrying entrance 250, a gate valve 251 is installed so that the inside of the process chamber 201 can communicate with the inside of a carrying chamber (preliminary chamber) 271 by opening the gate valve 251. The carrying chamber 271 is formed in a carrying vessel (airtight vessel) 272. In the carrying chamber 271, a carrying robot 273 is installed to carry a wafer 200. The carrying robot 273 includes a carrying arm 273a to support a wafer 200 when the wafer 200 is carried. In a state where the support stage 203 is lowered to the wafer carrying position, if the gate valve 251 is opened, a wafer 200 can be carried between the inside of the process chamber 201 and the inside of the carrying chamber 271 by using the carrying robot 273. A wafer 200 carried into the process chamber 201 is temporarily placed on the lift pins 208b as described above. In addition, at a side of the carrying chamber 271 opposite to the wafer carrying entrance 250, a loadlock chamber (not shown) is installed, and a wafer 200 can be carried between the inside of the loadlock chamber and the inside of the carrying chamber 271 by using the carrying robot 273. The loadlock chamber is used as a preliminary chamber to temporarily accommodate a non-processed or processed wafer 200.

[0043] (Exhaust System)

[0044] At a side of the inner wall of the process chamber 201 (process vessel 202) opposite to the wafer carrying entrance 250, an exhaust outlet 260 is installed for exhausting the inside atmosphere of the process chamber 201. An exhaust pipe 261 is connected to the exhaust outlet 260 through an exhaust chamber 260a, and at the exhaust pipe 261, a pressure regulator 262 such as an auto pressure controller (APC) configured to control the inside pressure of the process chamber 201, a source collection trap 263, and a vacuum pump 264 are sequentially connected in series. An exhaust system (exhaust line) is constituted mainly by the exhaust outlet 260, the exhaust chamber 260a, the exhaust pipe 261, the pressure regulator 262, the source collection trap 263, and the vacuum pump 264.

[0045] (Gas Inlet)

[0046] At the top surface (the ceiling wall) of a shower head 240 (described later) installed at an upper part of the process chamber 201, a gas inlet 210 is installed to introduce various gases into the process chamber 201. A gas supply system connected to the gas inlet 210 will be described later. [0047] (Shower Head)

[0048] Between the gas inlet 210 and the process chamber 201, the shower head 240 is installed as a gas distributing mechanism. The shower head 240 includes a distributing plate 240a configured to distribute a gas introduced through

the gas inlet 210, and a shower plate 240b configured to distribute the gas passing through the distributing plate 240a more uniformly and supply the gas to the surface of the wafer 200 placed on the support stage 203. A plurality of ventilation holes are formed in the distributing plate 240a and the shower plate 240b. The distributing plate 240a is disposed to face the top surface of the shower head 240 and the shower plate 240b, and the shower plate 240b is disposed to face the wafer 200 placed on the support stage 203. Between the top surface of the shower head 240 and the distributing plate 240a and between the distributing plate **240***a* and the shower plate **240***b*, spaces are provided which function as a first buffer space (distributing chamber) 240c through which gas supplied through the gas inlet 210 is distributed and a second buffer space 240d through which gas passing through the distributing plate 240a is diffused. [0049] (Exhaust Duct)

[0050] In the side surface of the inner wall of the process chamber 201 (process vessel 202), a stopper 201a is installed. The stopper 201a is configured to hold a conductance plate 204 at a position adjacent to the wafer processing position. The conductance plate 204 is configured as a doughnut-shaped (ring-shaped) circular disk having an opening to accommodate the wafer 200 in its inner circumferential part. A plurality of discharge outlets 204a are formed in the outer circumferential part of the conductance plate 204 in a manner such that the discharge outlets 204a are arranged at predetermined intervals in the circumferential direction of the conductance plate 204. The discharge outlets 204a are discontinuously formed so that the outer circumferential part of the conductance plate 204 can support the inner circumferential part of the conductance plate 204.

[0051] A lower plate 205 latches onto the outer circumferential part of the support stage 203. The lower plate 205 includes a ring-shaped concave part 205b and a flange part 205a formed in one piece with the inner upper side of the concave part 205b. The concave part 205b is installed to close a gap between the outer circumferential part of the support stage 203 and the side surface of the inner wall of the process chamber 201. At a part of the lower side of the concave part 205b adjacent to the exhaust outlet 260, a plate exhaust outlet 205c is formed to discharge (distribute) gas from the inside of the concave part 205b toward the exhaust outlet 260. The flange part 205a functions as a latching part that latches onto the upper outer circumferential part of the support stage 203. Since the flange part 205a latches onto the upper outer circumferential part of the support stage 203, the lower plate 205 can be lifted together with the support stage 203 when the support stage 203 is lifted.

[0052] When the support stage 203 is raised to the wafer processing position, the lower plate 205 is also raised to the wafer processing position. As a result, the top surface of the concave part 205b of the lower plate 205 is blocked by the conductance plate 204 held at a position adjacent to the wafer processing position, and thus a gas flow passage region is formed in the concave part 205b as an exhaust duct 259. At this time, by the exhaust duct 259 (the conductance plate 204 and the lower plate 205) and the support stage 203, the inside of the process chamber 201 is divided into an upper process chamber higher than the exhaust duct 259 and a lower process chamber lower than the exhaust duct 259. Preferably, the conductance plate 204 and the lower plate 205 may be formed of a material that is durable at a high

temperature, for example, high temperature resistant and high load resistant quartz, for the case where reaction products deposited on the inner wall of the exhaust duct 259 are etched away (for the case of self cleaning).

[0053] An explanation will now be given on a gas flow in the process chamber 201 during a wafer processing process. First, gas supplied from the gas inlet 210 to the upper side of the shower head 240 flows from the first buffer space (distributing chamber) 240c to the second buffer space 240d through the plurality of holes of the distributing plate 240a, and is then supplied to the inside of the process chamber 201 through the plurality of holes of the shower plate 240b, so that the gas can be uniformly supplied to the wafer 200. Then, the gas supplied to the wafer 200 flows outward in the radial directions of the wafer 200. After the gas makes contact with the wafer 200, remaining gas is discharged to the exhaust duct 259 disposed at the outer circumference of the wafer 200: that is, the remaining gas flows outward on the conductance plate 204 in the radial directions of the wafer 200 and is discharged to the gas flow passage region (the inside of the concave part 205b) of the exhaust duct 259through the discharge outlets 204a formed in the conductance plate 204. Thereafter, the gas flows in the exhaust duct 259 and is exhaust through the plate exhaust outlet 205c and the exhaust outlet 260. Since gas is guided to flow in this manner, the gas may be prevented from flowing to the lower part of the process chamber 201. That is, the gas may be prevented from flowing to the rear side of the support stage 203 or the bottom side of the process chamber 201.

[0054] <Gas Supply System>

[0055] Next, the configuration of the gas supply system connected to the gas inlet 210 will be described with reference to FIG. 2. FIG. 2 illustrates the configuration of the gas supply system (gas supply lines) of the substrate processing apparatus relevant to the embodiment of the present invention.

[0056] The gas supply system of the substrate processing apparatus of the current embodiment includes: a bubbler as a vaporizing unit configured to vaporize a liquid source which is liquid at room temperature; a source gas supply system configured to supply a source gas, which is obtained by vaporizing the liquid source using the bubbler, into the process chamber 201; and a reaction gas supply system configured to supply a reaction gas different from the source gas into the process chamber 201. In addition, the substrate processing apparatus of the current embodiment includes a purge gas supply system configured to supply a purge gas into the process chamber 201, and a vent (bypass) system so as not to supply a source gas generated from the bubbler into the process chamber 201 but to exhaust the source gas through a passage bypassing the process chamber 201. Next, the structure of each part will be described.

[0057] <Bubbler>

[0058] At the outside of the process chamber 201, a first source container (first bubbler) 220a is installed which contains a first source (source A) which is a liquid source, and a second source container (second bubbler) 220b is installed which contains a second source (source B) which is a liquid source. Each of the first and second bubblers 220a and 220b is configured as a tank (airtight container) in which a liquid source can be stored (filled). In addition, the first and second the bubblers 220a and 220b are configured as vaporizing units capable of generating a first source gas and a second source gas by vaporizing a first source and a second

source through bubbling. In addition, sub-heaters 206a are installed around the first bubbler 220a and the second bubbler 220b to heat the first and second bubblers 220a and 220b and liquid sources filled in the first and second bubblers 220a and 220b. For example, a metal liquid source containing titanium (Ti) such as titanium tetrachloride (TiCl<sub>4</sub>) may be used as the first source, and a metal liquid source containing nickel (Ni) such as tetrakis(trifluorophosphine)nickel (Ni(PF<sub>3</sub>)<sub>4</sub>) may be used as the second source. [0059] A first carrier gas supply pipe 237a and a second carrier gas supply pipe 237b are connected to the first bubbler 220a and the second bubbler 220b, respectively. Carrier gas supply sources (not shown) are connected to the upstream end parts of the first carrier gas supply pipe 237a and the second carrier gas supply pipe 237b. In addition, the downstream end parts of the first carrier gas supply pipe 237a and the second carrier gas supply pipe 237b are placed in the liquid sources filled in the first bubbler 220a and the second bubbler 220b, respectively. A mass flow controller (MFC) 222a which is a flow rate controller configured to control the supply flow rate of a carrier gas, and valves val and va2 configured to control supply of the carrier gas are installed at the first carrier gas supply pipe 237a. A mass flow controller (MFC) 222b which is a flow rate controller configured to control the supply flow rate of a carrier gas, and valves vb1 and vb2 configured to control supply of the carrier gas are installed at the second carrier gas supply pipe 237b. Preferably, a gas that does not react with the liquid sources may be used as the carrier gas. For example, inert gas such as N<sub>2</sub> gas and Ar gas may be used as the carrier gas. A first carrier gas supply system (first carrier gas supply line) is constituted mainly by the first carrier gas supply pipe 237a, the MFC 222a, and the valves va1 and va2, and a second carrier gas supply system (second carrier gas supply line) is constituted mainly by the second carrier gas supply pipe 237b, the MFC 222b, and the valves vb1 and vb2.

[0060] In the above-described structure, the valves va1, va2, vb1, and vb2 are opened, and a carrier gas the flow rates of which are controlled by the MFC 222a and the MFC 222b is supplied from the first carrier gas supply pipe 237a and the second carrier gas supply pipe 237b into the first bubbler 220a and the second bubbler 220b. Then, the liquid sources filled in the first and second bubblers 220a and 220b are vaporized by bubbling, and thus source gases are generated. [0061] The supply flow rates of the first source gas and the second source gas may be calculated from the supply flow rates of the carrier gas. That is, the supply flow rates of the

first source gas and the second source gas may be controlled by adjusting the supply flow rates of the carrier gas.

[0062] <Source Gas Supply System>

[0063] A first source gas supply pipe 213a and a second source gas supply pipe 213b are respectively connected to the first bubbler 220a and the second bubbler 220b to supply the first source gas and the second source gas generated in the first bubbler 220a and the second bubbler 220b into the process chamber 201. The upstream end parts of the first and second source gas supply pipes 213a and 213b communicate with inner upper spaces of the first and second bubblers 220a and 220b. The downstream end parts of the first and second source gas supply pipes 213a and 213b are joined together and then connected to the gas inlet 210.

[0064] In addition, valves va5 and va3 are sequentially installed from the upstream side of the first source gas supply pipe 213a. The valve va5 is configured to control

supply of the first source gas from the first bubbler 220a to the first source gas supply pipe 213a, and the valve va5 is installed at a position adjacent to the first bubbler 220a. The valve va3 is configured to control supply of the first source gas from the first source gas supply pipe 213a to the process chamber 201, and the valve va3 is installed at a position adjacent to the gas inlet 210. In addition, valves vb5 and vb3 are sequentially installed from the upstream side of the second source gas supply pipe 213b. The valve vb5 is configured to control supply of the second source gas from the second bubbler 220b to the second source gas supply pipe 213b, and the valve vb5 is installed at a position adjacent to the second bubbler 220b. The valve vb3 is configured to control supply of the second source gas from the second source gas supply pipe 213b to the process chamber 201, and the valve vb3 is installed at a position adjacent to the gas inlet 210. The valves va3 and vb3, and a valve ve3 (described later) are highly-durable, high-speed valves. Highly-durable, high-speed valves are integrated valves configured to rapidly switch supply of gas, interruption of gas supply, and exhaustion of gas. The valve ve3 controls introduction of a purge gas so as to rapidly purge a space of the first source gas supply pipe 213a between the valve va3 and the gas inlet 210 and a space of the second source gas supply pipe 213b between the valve vb3 and the gas inlet 210, and then to purge the inside of the process chamber 201.

[0065] In the above-described structure, the liquid sources are vaporized in the first and second bubblers 220a and 220b to generate the first and second source gases, and along with this, the valves va5, va3, vb5, and vb3 are opened, so that the first and second source gases can be supplied into the process chamber 201 from the first and second source gas supply pipes 213a and 213b. A first source gas supply system (first source gas supply line) is constituted mainly by the first source gas supply pipe 213a and the valve va5 and va3, and a second source gas supply system (second source gas supply line) is constituted mainly by the second source gas supply pipe 213b and the valves vb5 and vb3.

[0066] A first source supply system (first source supply line) is constituted mainly by the first carrier gas supply system, the first bubbler 220a, and the first source gas supply system; and a second source supply system (second source supply line) is constituted mainly by the second carrier gas supply system, the second bubbler 220b, and the second source gas supply system. A first process gas supply system is constituted by the first source supply system and a reaction gas supply system (described later), and a second process gas supply system is constituted by the second source gas supply system.

[0067] < Reaction Gas Supply System>

[0068] In addition, at the outside of the process chamber 201, a reaction gas supply source 220c is installed to supply a reaction gas. The upstream end part of a reaction gas supply pipe 213c is connected to the reaction gas supply source 220c. The downstream end part of the reaction gas supply pipe 213c is connected to the gas inlet 210 through a valve vc3. An MFC 222c which is a flow rate controller configured to control the supply flow rate of a reaction gas, and valves vc1 and vc2 configured to control supply of the reaction gas are installed at the reaction gas supply pipe 213c. For example, ammonia (NH<sub>3</sub>) gas may be used as the reaction gas. A reaction gas supply system (reaction gas supply line) is constituted mainly by the reaction gas supply

source 220c, the reaction gas supply pipe 213c, the MFC 222c, and the valves vc1, vc2, and vc3.

[0069] <Purge Gas Supply System>

[0070] In addition, at the outside of the process chamber 201, purge gas supply sources 220d and 220e are installed to supply a purge gas. The upstream end parts of purge gas supply pipes 213d and 213e are connected to the purge gas supply sources 220d and 220e, respectively. The downstream end part of the purge gas supply pipe 213d is joined to the reaction gas supply pipe 213c and is connected to the gas inlet 210 through the valve vc3. The downstream end part of the purge gas supply pipe 213e is joined to the first source gas supply pipe 213a and the second source gas supply pipe 213b and is connected to the gas inlet 210through the valve ve3. At the purge gas supply pipes 213d and 213e, MFCs 222d and 222e are respectively installed as flow rate controllers configured to control the supply flow rates of purge gas, and valves vd1, vd2, ve1, and ve2, are respectively installed to control supplies of purge gas. For example, inert gas such as N2 gas and Ar gas may be used as a purge gas. A purge gas supply system (purge gas supply line) is constituted mainly by the purge gas supply sources 220d and 220e, the purge gas supply pipes 213d and 213e, the MFCs 222d and 222e, the valves vd1, vd2, vc3, ve1, ve2, and ve3.

[0071] <Vent (Bypass) System>

[0072] In addition, the upstream end parts of a first vent pipe 215a and a second vent pipe 215b are respectively connected to the upstream sides of the valves va3 and vb3 of the first and second source gas supply pipes 213a and 213b. In addition, the downstream end parts of the first and second vent pipes 215a and 215b are joined together and connected between the downstream side of the pressure regulator 262 and the upstream side of the source collection trap 263 of the exhaust pipe 261. At the first and second vent pipes 215a and 215b, valves va4 and vb4 are respectively installed to control flows of gases.

[0073] In the above-described structure, by closing the valves va3 and vb3 and opening the valves va4 and vb4, gases flowing in the first and second source gas supply pipes 213a and 213b can be allowed to bypass the process chamber 201 through the first and second vent pipes 215a and 215b without being supplied into the process chamber 201, and then the gases can be exhausted to the outside of the process chamber 201 through the exhaust pipe 261. A first vent system is constituted mainly by the first vent pipe 215a, the valve va4, and a second vent system is constituted mainly by the second vent pipe 215b and the valve vb4.

[0074] The sub-heaters 206a are also installed around the first and second vent pipes 215a and 215b. In addition, the sub-heaters 206a are also installed around other members such as the first carrier gas supply pipe 237a, the second carrier gas supply pipe 237b, the first source gas supply pipe 213a, the second source gas supply pipe 213b, the exhaust pipe 261, the process vessel 202, and the shower head 240. The sub-heater 206a is configured to heat such members to, for example, 100° C. or lower, so as to prevent the first and second source gases from changing back to liquid in the members.

[0075] <Controller>

[0076] The substrate processing apparatus relevant to the current embodiment includes a controller 280 configured to control each part of the substrate processing apparatus. The controller 280 controls operations of parts such as the gate

valve 251, the elevating mechanism 207*b*, the carrying robot 273, the heater 206, the sub-heater 206*a*, the pressure regulator (APC) 262, the vacuum pump 264, the valves va1 to va5, vb1 to vb5, vc1 to vc3, vd1 and vd2, and ve1 to ve3, and the MFCs 222*a*, 222*b*, 222*c*, 222*d*, and 222*e*.

### (2) Substrate Processing Processes

[0077] Next, with reference to FIG. 1, as one of semiconductor device manufacturing processes, a substrate processing process for forming a thin film on a wafer by a chemical vapor deposition (CVD) method and an atomic layer deposition (ALD) method using the above-described substrate processing apparatus will be explained according to the embodiment of the present invention. FIG. 1 is a flowchart for explaining substrate processing processes according to the embodiment of the present invention. In the following description, operations of parts constituting the substrate processing apparatus are controlled by the controller 280.

[0078] In the following description, an explanation will be given on an exemplary case where a metal film having a stacked structure constituted by a TiN film being a first metal film and a Ni film being a second metal film is formed on a  ${\rm TiO_2}$  film which is previously formed on a substrate such as a wafer 200 as an insulating film (gate insulating film or capacitor insulating film).

[0079] The TiN film which is a first metal film is formed according to an ALD method by alternately supplying a first source gas (Ti source), which is generated by vaporizing a first source (TiCl $_4$ ), and a reaction gas (NH $_3$  gas) into the process chamber 201 in which the wafer 200 is accommodated. The Ni film which is a second metal film is formed according to a CVD method by supplying a second source gas (Ni source) generated by vaporizing a second source (Ni(PF $_3$ ) $_4$ ) into the process chamber 201 in which the wafer 200 is accommodated. The first source gas and the reaction gas constitute a first process gas, and the second source gas constitutes a second process gas.

[0080] In this specification, the term "metal film" is used to denote a film formed of a conductive material containing metal atoms. Examples thereof include a conductive elemental metal film formed of an elemental metal, a conductive metal nitride film, a conductive metal oxide film, a conductive metal composite film, a conductive metal alloy film, and a conductive metal silicide film. The TiN film is a conductive metal nitride film, and the Ni film is a conductive elemental metal film. The exemplary case will now be explained in detail.

[0081] <Substrate Carrying-in Process S1, Substrate Placing Process S2>

[0082] First, the elevating mechanism 207b is operated to lower the support stage 203 to the wafer carrying position as shown in FIG. 4. Next, the gate valve 251 is opened so that the process chamber 201 can communicate with the carrying chamber 271. Next, a wafer 200 to be processed is carried from the carrying chamber 271 to the process chamber 201 by using the carrying robot 273 in a state where the wafer 200 is supported on the carrying arm 273a (S1). A TiO<sub>2</sub> film is previously formed as an insulating film (gate insulating film or capacitor insulating film) on the wafer 200 to be processed. The wafer 200 loaded in the process chamber 201 is temporarily placed on the lift pins 208b which protrude upward from the top surface of the support stage 203. Thereafter, the carrying arm 273a of the carrying robot 273

is moved from the inside of the process chamber 201 back to the carrying chamber 271, and the gate valve 251 is closed.

[0083] Next, the elevating mechanism 207b is operated to raise the support stage 203 to the wafer processing position as shown in FIG. 3. As a result, the lift pins 208b are retracted from the top surface of the support stage 203, and the wafer 200 is placed on the susceptor 217 disposed at the top surface of the support stage 203 (S2).

[0084] <Pressure Adjusting Process S3, Temperature Adjusting Process S4)

[0085] Subsequently, by using the pressure regulator (APC) 262, the inside pressure of the process chamber 201 is adjusted to a predetermined process pressure (S3). In addition, power supplied to the heater 206 is controlled to increase the surface temperature of the wafer 200 to a predetermined process temperature (S4). The temperature adjusting process S4 may be performed in parallel with or prior to the pressure adjusting process S3. The predetermined process temperature and process pressure are set in a manner such that a TiN film can be formed in a TiN film-forming process S5 (described later) by an ALD method. That is, the process temperature and the process pressure are set in a manner such that a first source gas supplied in a Ti source supply process S5a does not decompose by itself.

[0086] In the substrate carrying-in process S1, the substrate placing process S2, the pressure adjusting process S3, and the temperature adjusting process S4, the vacuum pump 264 is operated in a state where the valves va3 and vb3 are closed and the valves vd1, vd2, vc3, ve1, ve2, and ve3 are opened, so as to create a flow of  $N_2$  gas in the process chamber 201. By this, adhesion of particles to the wafer 200 can be suppressed.

[0087] Along with the processes S1 to S4, a first source  $(TiCl_{4})$  is vaporized to generate a first source gas (Ti source). That is TiCl<sub>4</sub> gas is generated (preliminary vaporization). That is, the valves va1, va2, and va5 are opened, and a carrier gas the flow rate of which is controlled by the MFC 222a is supplied from the first carrier gas supply pipe 237a into the first bubbler 220a so as to vaporize a first source filled in the first bubbler 220a by bubbling to generate a first source gas (preliminary vaporization process). In this preliminary vaporization process, while operating the vacuum pump 264, the valve va4 is opened in a state where the valve va3 is closed, so that the first source gas is not supplied into to the process chamber 201 but is exhausted through a route bypassing the process chamber 201. A predetermined time is necessary for the first bubbler 220a to stably generate the first source gas. For this reason, in the current embodiment, the first source gas is preliminary generated, and the flow passage of the first source gas is changed by selectively opening and closing the valves va3 and va4. That is, by selectively opening and closing the valves va3 and va4, stable supply of the first source gas into the process chamber 201 can be quickly started and stopped. This operation is preferable.

[0088] <TiN Film-Forming Process S5>

[0089] (Ti Source Supply Process S5a)

[0090] Next, while operating the vacuum pump 264, the valve va4 is closed and the valve va3 is opened to start supply of the first source gas (Ti source) into the process chamber 201.

[0091] The first source gas is distributed by the shower head 240 so that the first source gas can be uniformly supplied to the wafer 200 disposed in the process chamber 201. Surplus first source gas flows in the exhaust duct 259 and is exhausted to the exhaust outlet 260 and the exhaust pipe 261. At this time, the process temperature and process pressure are set in a manner such that the first source gas does not decompose by itself. Therefore, molecules of the first source gas are adsorbed on the TiO<sub>2</sub> film which is previously formed on the wafer 200 as an insulating film (gate insulating film or capacitor insulating film).

[0092] When the first source gas is supplied into the process chamber 201, so as to prevent permeation of the first source gas into the reaction gas supply pipe 213c and facilitate diffusion of the first source gas in the process chamber 201, it is preferable that the valves vc1, vc2, and vc3 are kept in an opened state to continuously supply  $N_2$  gas into the process chamber 201.

[0093] After a predetermined time from the start of supply of the first source gas by opening the valve va3, the valve va3 is closed, and the valves va4 is opened to stop supply of the first source gas into the process chamber 201.

[0094] (Purge Process S5b)

[0095] After stopping supply of the first source gas by closing the valve va3, the valves vd1, vd2, vc3, ve1, ve2, and ve3 are opened to supply  $N_2$  gas into the process chamber 201. The  $N_2$  gas is dispersed by the shower head 240 and uniformly supplied to the wafer 200 disposed in the process chamber 201, and then the  $N_2$  gas flows in the exhaust duct 259 and is exhausted to the exhaust outlet 260 and the exhaust pipe 261. In this way, the first source gas remaining in the process chamber 201 is removed, and the inside of the process chamber 201 is purged with  $N_2$  gas.

[0096] (Reaction Gas Supply Process S5c)

[0097] After the inside of the process chamber 201 is purged, the valves vc1, vc2, and vc3 are opened to start supply of a reaction gas (NH<sub>3</sub> gas) into the process chamber 201. The reaction gas is dispersed by the shower head 240 and uniformly supplied to the wafer 200 disposed in the process chamber 201 so that the reaction gas reacts with the molecules of the first source gas adsorbed on the TiO<sub>2</sub> film previously formed on the wafer 200. Thus, a TiN film constituted by about less than one atomic layer (less than 1 Å) is formed on the TiO2 film. Surplus reaction gas or reaction byproducts are allowed to flow in the exhaust duct 259 and are exhausted to the exhaust outlet 260 and the exhaust pipe 261. After a predetermined time from the start of supply of the reaction gas by opening the valve vc1, vc2, and vc3, the supply of the reducing gas into the process chamber 201 is interrupted by closing the valves vc1 and vc2.

[0098] When the reaction gas is supplied into the process chamber 201, so as to prevent permeation of the reaction gas into the first source gas supply pipe 213a and the second source gas supply pipe 213b and facilitate diffusion of the reaction gas in the process chamber 201, it is preferable that the valves ve1, ve2, and ve3 are kept opened to continue supply of  $N_2$  gas into the process chamber 201.

[0099] (Purge Process S5d)

[0100] After stopping supply of the reaction gas by closing the valve vc1 and vc2, the valves vd1, vd2, vc3, ve1, ve2, and ve3 are opened to supply  $N_2$  gas into the process chamber 201. The  $N_2$  gas is dispersed by the shower head 240 and uniformly supplied to the wafer 200 disposed in the

process chamber 201, and then the  $N_2$  gas flows in the exhaust duct 259 and is exhausted to the exhaust outlet 260 and the exhaust pipe 261.

[0101] In this way, reaction gas and reaction byproducts remaining in the process chamber 201 are removed, and the inside of the process chamber 201 is purged with the  $N_2$  gas. [0102] (Predetermined-Time Executing Process S5e)

[0103] The Ti source supply process S5a, the purge process S5b, the reaction gas supply process S5c, and the purge process S5d are set as one cycle, and the cycle (ALD cycle) is performed predetermined times (n1 cycles) so that a titanium nitride (TiN) film having a predetermined thickness can be formed as a first metal film on the TiO<sub>2</sub> film previously formed on the wafer 200. The TiN film which is a first metal film has an oxidation resistance greater than that of a Ni film that will be formed as a second metal film (described later).

[0104] <Pressure Adjusting Process S6, Temperature Adjusting Process S7)

[0105] Subsequently, by using the pressure regulator (APC) 262, the inside pressure of the process chamber 201 is adjusted to a predetermined process pressure (S6). In addition, power supplied to the heater 206 is controlled to increase the surface temperature of the wafer 200 to a predetermined process temperature (S7). The temperature adjusting process S7 may be performed in parallel with or prior to the pressure adjusting process S6. The predetermined process temperature and process pressure are set in a manner such that a Ni film can be formed in a Ni film-forming process S8 (described later) by a CVD method. That is, the process temperature and the process pressure are set in a manner such that a second source gas supplied in a Ni source supply process S8a can decompose by itself.

[0106] Along with the pressure adjusting process S6 and the temperature adjusting process S7, a second source (Ni (PF<sub>3</sub>)<sub>4</sub>) is vaporized to previously generate a second source gas (Ni source), that is, Ni(PF<sub>3</sub>)<sub>4</sub> gas for the next Ni film-forming process S8 (preliminary vaporization). That is, the valves vb1, vb2, and vb5 are opened, and a carrier gas, the flow rate of which is controlled by the MFC 222b, is supplied from the second carrier gas supply pipe 237b into the second bubbler 220b so as to vaporize a second source filled in the second bubbler 220b by bubbling to generate a second source gas (preliminary vaporization process). In this preliminary vaporizing process, while operating the vacuum pump 264, the valve vb4 is opened in a state where the vb3 is closed so as not to supply the second source gas into the process chamber 201 but exhaust the second source gas through a route bypassing the process chamber 201. A predetermined time is necessary for the second bubbler 220b to stably generate the second source gas. For this reason, in the current embodiment, the second source gas is preliminary generated, and the flow passage of the second source gas is changed by selectively opening and closing the valves vb3 and vb4. That is, by selectively opening and closing the valves vb3 and vb4, stable supply of the second source gas into the process chamber 201 can be quickly started and stopped. This operation is preferable.

[0107] <Ni Film-Forming Process S8>

[0108] (Ni Source Supply Process S8a)

[0109] Next, while operating the vacuum pump 264, the valve va4 is closed and the valve va3 is opened to supply the second source gas (Ni source) into the process chamber 201. The second source gas is distributed by the shower head 240

so that the second source gas can be uniformly supplied to the wafer 200 disposed in the process chamber 201. Surplus second source gas flows in the exhaust duct 259 and is exhausted to the exhaust outlet 260 and the exhaust pipe 261. At this time, the process temperature and process pressure are set in a manner such that the second source gas can decompose. Therefore, the second source gas supplied to the wafer 200 thermally decomposes and participates in a CVD reaction, and accordingly a Ni film is formed on the wafer 200.

[0110] When the second source gas is supplied into the process chamber 201, so as to prevent permeation of the second source gas into the reaction gas supply pipe 213c and facilitate diffusion of the second source gas in the process chamber 201, it is preferable that the valves vd1, vd2, and vd3 are kept in an opened state to continuously supply  $N_2$  gas into the process chamber 201.

[0111] After a predetermined time from the start of supply of the second source gas by opening the valve vb3, the valve vb3 is closed and the valves vb4 is opened to stop supply of the second source gas into the process chamber 201.

[0112] (Purge Process S8b)

[0113] After stopping supply of the second source gas by closing the valve vb3, the valves vd1, vd2, vc3, ve1, ve2, and ve3 are opened to supply  $N_2$  gas into the process chamber 201. The  $N_2$  gas is dispersed by the shower head 240 and supplied into the process chamber 201, and then the  $N_2$  gas flows in the exhaust duct 259 and is exhausted to the exhaust outlet 260 and the exhaust pipe 261. In this way, the second source gas remaining in the process chamber 201 is removed, and the inside of the process chamber 201 is purged with  $N_2$  gas.

[0114] (Predetermined-Time Executing Process S8c)

[0115] The Ni source supply process S8a and the purge process S8b are set as one cycle, and the cycle is performed predetermined times (n2 cycles) so that a nickel film (Ni film) having a predetermined thickness can be formed as a second metal film on the TiN film which is formed as a first metal film over the wafer 200. The Ni film which is a second metal film is made of a material having a work function greater than 4.8 eV and different from a material used to form the first metal film.

[0116] < Predetermined-Time Executing Process S9>

[0117] The pressure adjusting process S3 to the TiN filmforming process S5 and the pressure adjusting process S6 to the Ni film-forming process S8 are set as one cycle, and the cycle is performed predetermined times (n3 cycles) so that a metal film having a stacked structure constituted by the TiN film being the first metal film and the Ni film being the second metal film can be formed on the TiO<sub>2</sub> film previously formed on the wafer 200. As described above, the TiN film which is the first metal film has an oxidation resistance greater than the oxidation resistance of the Ni film which is the second metal film. In addition, the Ni film which is the second metal film is made of a material having a work function greater than 4.8 eV and being different from the first metal film. The TiN film which is the first metal film is formed between the Ni film (second metal film) and the TiO<sub>2</sub> film.

[0118] <Pressure Adjusting Process S10, Temperature Adjusting Process S11)

[0119] Next, like in the pressure adjusting process S3 and the temperature adjusting process S4, the inside pressure of the process chamber 201 is adjusted to a predetermined

process pressure (S10), and the surface temperature of the wafer 200 is adjusted to a predetermined process temperature (S11).

[0120] <TiN Cap Forming Process S12>

[0121] (Ti Source Supply Process S12a)

[0122] Next, like in the Ti source supply process S5a, the first source gas (Ti source) is supplied into the process chamber 201 for a predetermined time, and then the supply of the first source gas into the process chamber 201 is stopped.

[0123] (Purge Process S12b)

[0124] After stopping the supply of first source gas, the inside of the process chamber 201 is purged with  $N_2$  gas like in the purge process S5b.

[0125] (Reaction Gas Supply Process S12c)

[0126] After the inside of the process chamber 201 is purged, like in the reaction gas supply process S5c, the reaction gas (NH<sub>3</sub> gas) is supplied into the process chamber 201 for a predetermined time, and then the supply of the reaction gas into the process chamber 201 is stopped.

[0127] (Purge Process S12*d*)

[0128] After stopping the supply of the reaction gas, the inside of the process chamber 201 is purged with  $N_2$  gas like in the purge process S5d.

[0129] (Predetermined-Time Executing Process S12e)

[0130] The Ti source supply process S12a, the purge process S12b, the reaction gas supply process S12c, and the purge process S12d are set as one cycle, and the cycle is performed predetermined times (n4 cycles) so that a TiN film (TiN cap film) having a predetermined thickness can be formed as a first metal film on the metal film (having a stacked structure constituted by TiN film and Ni film) formed through the predetermined-time executing process S9.

[0131] By performing the processes S3 to S12, the metal film can be formed adjacent to the TiO2 film which is previously formed on the wafer 200 as an insulating film (gate insulating film or capacitor insulating film). The metal film has a stacked structure constituted by the TiN film which is the first metal film and the Ni film which is the second metal film. The first metal film is made of a material (TiN) having an oxidation resistance greater than the oxidation resistance of the second metal film, and the second metal film is made of a material (Ni) having a work function greater than 4.8 eV and being different from the material used to make the first metal film. In addition, the TiN film is formed between the Ni film and the TiO2 film. Furthermore, the TiN film (TiN cap film) is formed on the outermost surface of the metal film. If the execution number (n3 cycles) of the predetermined-time executing process S9 is set to one (one cycle), a metal film can be formed as a gate electrode as shown in FIG. 5A or a top capacitor electrode as shown in FIG. 6A. If the execution number (n3 cycles) of the predetermined-time executing process S9 is set to two or more (two or more cycles), a metal film can be formed as a gate electrode as shown in FIG. 5B or a top capacitor electrode as shown in FIG. 6B. A bottom capacitor electrode as shown in FIG. 6B may also be formed through a process similar to the process of forming the top capacitor electrode.

[0132] <Remaining Gas Removing Process S13>

[0133] After the TiN cap film having a predetermined thickness is formed on the metal film (having a stacked structure constituted by TiN film and Ni film) formed through the predetermined-time executing process S9, the

inside of the process chamber 201 is vacuum-evacuated, and the valves vd1, vd2, vc3, ve1, ve2, and ve3 are opened to supply  $N_2$  gas into the process chamber 201. The  $N_2$  gas is dispersed by the shower head 240 and supplied into the process chamber 201, and then the  $N_2$  is exhausted to the exhaust pipe 261. In this way, gas and reaction byproducts remaining in the process chamber 201 are removed, and the inside of the process chamber 201 is purged with the  $N_2$  gas.

[0134] <Substrate Carrying-Out Process S14>

[0135] Thereafter, in the reverse order to that of the substrate carrying-in process S1 and the substrate placing process S2, the wafer 200, over which the metal film (having a stacked structure constituted by TiN film and Ni film) and the TiN cap film are formed to predetermined thicknesses, is carried out from the process chamber 201 to the carrying chamber 271, thereby completing the substrate processing process of the current embodiment.

[0136] Furthermore, in the current embodiment, the TiN film-forming process S5 may be performed to a wafer 200 under the following exemplary conditions.

[0137] Process temperature: 250° C. to 550° C., preferably, 350° C. to 550° C.,

[0138] Process pressure: 50 Pa to 5,000 Pa,

[0139] Supply flow rate of carrier gas  $(N_2)$  for bubbling: 10 sccm to 1,000 sccm,

[0140] Supply flow rate of first source gas (TiCl<sub>4</sub>): 0.1 sccm to 2 sccm,

[0141] Supply flow rate of reaction gas  $(NH_3)$ : 10 sccm to 1,000 sccm,

[0142] Supply flow rate of purge gas  $(N_2)$ : 100 sccm to 10.000 sccm, and

[0143] Film thickness (TiN film): 0.2 nm to 4 nm.

[0144] Furthermore, in the current embodiment, the Ni film-forming process S8 may be performed to a wafer 200 under the following exemplary conditions.

[0145] Process temperature: 150° C. to 250° C., preferably, 150° C. to 200° C.,

[0146] Process pressure: 50 Pa to 5,000 Pa,

[0147] Supply flow rate of carrier gas  $(N_2)$  for bubbling: 10 sccm to 1,000 sccm,

[0148] Supply flow rate of second source gas  $(Ni(PF_3)_4)$ : 0.1 sccm to 2 sccm,

[0149] Supply flow rate of purge gas  $(N_2)$ : 100 sccm to 10,000 sccm, and

[0150] Film thickness (Ni film): 0.5 nm to 10 nm, preferably, 4 nm to 5 nm.

[0151] In addition, total film thickness in the predetermined-time executing process S9, that is, the thickness of a metal film having a stacked structure constituted by TiN film being first metal film and Ni film being second metal film may be, for example, 10 nm to 30 nm.

[0152] Furthermore, in the current embodiment, the TiN cap film-forming process S12 may be performed to a wafer 200 under the following exemplary conditions.

[0153] Process temperature: 250° C. to 550° C., preferably, 350° C. to 550° C.,

[0154] Process pressure: 50 Pa to 5,000 Pa,

[0155] Supply flow rate of carrier gas  $(N_2)$  for bubbling: 10 sccm to 1,000 sccm,

[0156] Supply flow rate of first source gas ( $TiCl_4$ ): 0.1 sccm to 2 sccm,

[0157] Supply flow rate of reaction gas  $(NH_3)$ : 10 sccm to 1,000 sccm,

[0158] Supply flow rate of purge gas  $(N_2)$ : 100 sccm to 10,000 sccm, and

[0159] Film thickness (TiN film): 0.2 nm to 50 nm, preferably, 1 nm to 10 nm.

[0160] If a TiN film is formed to have a thickness of less than 0.2 nm in the TiN film-forming process S5, the TiN film may not be constituted by one or more continuous layers between a Ni film and a TiO<sub>2</sub> film. That is, the TiN film may be constituted by a discontinuous layer, and thus the Ni film and the TiO2 may make contact with each other. Therefore, an oxygen component included in the TiO2 film may permeate into the Ni film through a contact part, and thus the Ni film may be oxidized. In addition, if a TiN film is formed to have a thickness greater than 4 nm in the TiN filmforming process S5, the effective work function of an entire metal film may not be the work function of a Ni film (about 5.15 eV) but may be close to the work function of the TiN film (about 4.6 eV). Thereafter, it is preferable that a TiN film is formed to have a thickness of 0.2 nm to 4 nm in the TiN film-forming process S5.

[0161] In addition, if the process temperature of the Ni film-forming process S8 is lower than 150° C., in the Ni film-forming process S8a, the second source (Ni(PF<sub>3</sub>)<sub>4</sub>) may not decompose by itself, and thus, a CVD film-forming reaction may not occur. In addition, if the process temperature is higher than 250° C. in a state where the process pressure is kept in the above-mentioned range, the film-forming rate may increase excessively, and thus it may be difficult to control a film thickness. Therefore, in the Ni film-forming process S8, it is necessary to keep the process temperature in the range from 150° C. to 250° C. for inducing a CVD film-forming reaction and controlling a film thickness.

[0162] In the current embodiment, it is preferable that the TiN film-forming process S5 and the Ni film-forming process S8 are performed at the same process temperature and/or the same process pressure. That is, in the current embodiment, it is preferable that the TiN film-forming process S5 and the Ni film-forming process S8 are performed at a constant process temperature and/or a constant process pressure. If the process temperature and the process pressure are set to predetermined values in the abovementioned ranges, ALD film formation and CVD film formation can be performed under the same conditions. In this case, when the procedure goes from the TiN film-forming process S5 to the Ni film-forming process S8 or from the Ni film-forming process S8 to the TiN film-forming process S5, a process of changing the process temperature and a process of changing the process pressure may not be necessary, and thus the throughput may be improved.

### (3) Effects of the Embodiment

[0163] According to the current embodiment, one or more of the following effects can be obtained.

[0164] (a) According to the current embodiment, the TiN film having an oxidation resistance greater than that of the Ni film is formed as the lowermost layer of the metal film, that is, the layer (interfacial surface) between the Ni film and the  ${\rm TiO_2}$  film. Since the TiN film has an oxidation resistance greater than that of the Ni film, for example, when the Ni film is formed by a CVD method or the wafer 200 on which the metal film is formed is heated to about 400° C. to perform an annealing treatment, it can be prevented that the Ni film is oxidized by an oxygen component permeated from

the  ${\rm TiO_2}$  film into the Ni film through an interfacial surface therebetween. Particularly, in the current embodiment, the TiN film is formed to have a thickness of 0.2 nm or greater in the TiN film-forming process S5. Thus, the TiN film formed between the Ni film and the  ${\rm TiO_2}$  film can be surely constituted by one or more continuous layers, and thus the Ni film and the  ${\rm TiO_2}$  film can be prevented from directly making contact with each other and oxidation of the Ni film can be effectively suppressed. Hence, oxidation of the metal film can be suppressed, and an increase of equivalent oxide thickness (EOT) can be prevented.

[0165] (b) In addition, according to the current embodiment, the TiN film (TiN cap layer) having an oxidation resistance greater than that of the Ni film is formed as the uppermost layer of the metal film, that is, the exposed surface layer of the metal film. Thus, permeation of oxygen from the atmosphere to the Ni film through the exposed surface of the metal film can be prevented, and thus oxidation of the Ni film can be suppressed. For example, when the wafer 200 on which the metal film is exposed is carried for the next process, it can be prevented that the Ni film is oxidized at room temperature by oxygen permeated into the Ni film from the atmosphere through the exposed surface of the metal film. Particularly, according to the current embodiment, in the TiN cap forming process S12, the TiN film is formed to have a thickness of 0.2 nm to 50 nm, preferably, 1 nm to 10 nm, and thus the TiN film covering the surface of the Ni film can be surely constituted by one or more continuously layers. Therefore, the Ni film can be prevented from making direct contact with the atmosphere, and thus oxidation of the Ni film can be effectively suppressed. Hence, oxidation of the metal film can be suppressed, and an increase of EOT can be prevented.

[0166] (c) In addition, according to the current embodiment, the second metal film is formed of Ni (different from the first metal film in material) having a work function greater than 4.8 eV. Although the work function of TiN used to form the first metal film is estimated to be 4.6 eV, the work function of Ni is 5.15 eV as shown in FIG. 10. Thus, the effective work function of the entire metal film having a stacked structure constituted by the TiN film and the Ni film can be close to the work function of the Ni film (about 5.15 eV). Particularly, according to the current embodiment, the thickness of the Ni film formed in the Ni film-forming process S8 is greater than the thickness of the TiN film formed in the TiN film-forming process S5. Thus, the effect of the work function of the thicker Ni film is increased, and thus the effective work function of the entire work function of the metal film having a stacked structure constituted by the TiN film and the Ni film can be closer to the work function of the Ni film (about 5.15 eV). Therefore, when the metal film is used as a capacitor electrode, a leak current of a capacitor part can be reduced.

[0167] For example, if a metal film as shown in FIG. 5A or FIG. 6A is formed by performing the TiN film-forming process S5 and the Ni film-forming process S8 once in a manner such that a TiN film is formed to have a thickness ranging from 0.2 nm to 4 nm in the TiN film-forming process S5 and a thicker Ni film is formed to have a thickness ranging from 0.5 nm to 10 nm, preferably, 4 nm to 5 nm in the Ni film-forming process S8, the effect of the work function of the thicker Ni film is high so that the effective work function of the entire metal film can approach about 5.0 eV. For example, when a metal film as shown in FIG. 5B

or FIG. 6B is formed by setting the TiN film-forming process S5 and the Ni film-forming process S8 as one cycle and performing the cycle a plurality of times, the effective work function of the entire metal film can be adjusted to a desired value. That is, in this case, since the work functions of TiN films and Ni films are affected by each other, the effective work function of the entire metal film can be adjusted to a desired value between 4.6 eV and 5.0 eV by adjusting a thickness ratio of the TiN films and the Ni films. In either case, if the thickness of the TiN film formed in the TiN film-forming process S5 is greater than 4 nm, the effective work function of the entire metal film may be decreased to be close to the work function (4.6 eV) of the TiN film.

[0168] FIG. 7 is a schematic view illustrating the energy level of a conventional capacitor electrode constituted by a single layer of TiN film. The leak current of a capacitor structure (metal-insulator-metal (MIM) structure), in which a capacitor insulating film (for example, a  $\text{TiO}_2$  film) is disposed between TiN films, is determined mainly by the work function of capacitor electrodes and the band offset (conduction band offset) of the conduction band side of the capacitor insulating film. Since a voltage of  $\pm 1$  V is generally applied between capacitor electrodes, it is preferable that a conduction band offset is greater than 1.0 eV. In addition, since the work function of TiN is about 4.6 eV, if a  $\text{TiO}_2$  film is used as a capacitor insulating film, a conduction band offset of only about 1.0 eV may be ensured, and thus leak current may be increased.

[0169] However, if the metal film of the current embodiment is used as a capacitor electrode, the leak current of an MIM structure can be largely reduced. FIG. 8 is a schematic view illustrating the energy levels of a metal film formed by performing the TiN film-forming process S5 and the Ni film-forming process S8 once. In this case, as described above, the work function of the metal film having a structure in which a TiN film and a Ni film are stacked can approach almost the same level (for example, 5.0 eV) as the work function of the Ni film (about 5.15 eV). Therefore, if a TiO<sub>2</sub> film is used as an insulating film, a conduction band offset of about 1.4 eV can be ensured, and thus leak current can be largely reduced. In addition, FIG. 9 is a schematic view illustrating the energy levels of a metal film formed by setting the TiN film-forming process S5 and the Ni filmforming process S8 as one cycle and performing the cycle a plurality of times. In this case, as described above, the work function of the metal film having a structure in which TiN films and Ni films are stacked can be adjusted to a desired value (for example, 4.8 eV) in the range of, for example, 4.6 eV to 5.0 eV. Therefore, if a TiO2 film is used as an insulating film, a conduction band offset can be set to a desired value (for example, 1.2 eV) in the range of 1.0 eV to 1.4 eV, and thus leak current can be effectively reduced. [0170] (d) In addition, according to the current embodi-

ment, a second metal film having a work function greater than 4.8 eV is formed by using a Ni film which is a metal film (non-noble metal film), instead of using an expensive noble metal film such as an Au, Ag, Pt, Pd, Rh, Ir, Ru, or Os film. In this way, manufacturing costs of semiconductor devices can be reduced.

[0171] (e) In addition, according to the current embodiment, in a metal film having a stacked structure of a TiN film and a Ni film, the Ni film is formed by a CVD method. Therefore, the total film-forming rate of the metal film can

be increased as compared with the case of using only an ALD method, and the throughput can be improved.

### Other Embodiments of the Present Invention

[0172] In the above-described embodiment, a liquid source filled in the bubbler is vaporized by bubbling. However, the present invention is not limited thereto. For example, the liquid source may be vaporized by using a vaporizer instead of using the bubbler.

**[0173]** Furthermore, in the above-described embodiment,  $TiCl_4$  is used as a Ti source in the TiN film-forming process S5. However, the present invention is not limited thereto. For example, a Ti source such as TDMAT (tetrakis(dimethylamino)titanium:  $Ti[N(CH_3)_2]_4$ ) may be used instead of TiCl.

[0174] Furthermore, in the above-described embodiment, a  $\mathrm{TiO}_2$  film having a high permittivity is used as an insulating film. However, the present invention is not limited thereto. For example, the present invention can be applied to the case of using another insulating film or a high permittivity insulating film such as a hafnium oxide ( $\mathrm{HfO}_2$ ) film, a zirconium oxide ( $\mathrm{ZrO}_2$ ) film, a niobium oxide ( $\mathrm{Nb}_2\mathrm{O}_3$ ) film, a tantalum oxide ( $\mathrm{Ta}_2\mathrm{O}_3$ ) film, a hafnium oxide film doped with aluminum ( $\mathrm{HfAlO}$  film), a zirconium oxide film doped with aluminum ( $\mathrm{ZrAlO}_3$ ) film, a strontium titanate ( $\mathrm{SrTiO}_3$ ) film, a barium strontium titanate ( $\mathrm{BaSrTiO}_3$ ) film, and a lead zirconate titanate ( $\mathrm{PZT}_3$ ) film.

[0175] Furthermore, in the above-described embodiment, a TiN film is used as a first metal film. However, the present invention is not limited thereto. For example, the present invention can be properly applied to the case where another film, such as a tantalum nitride (TaN) film, a titanium aluminum nitride (TaAlN) film, film, or tantalum aluminum nitride (TaAlN) film, is used as a first metal film. All the TaN film, the TiAlN film, and the TaAlN film have an oxidation resistance greater than that of a second metal film (Ni film). Furthermore, all the TaN film, the TiAlN film, and the TaAlN film have an oxidation resistance greater than that of a TiN film and can be usefully used as an oxidation barrier film. The TaN film is a conductive metal nitride film, the TiAlN film is a conductive composite metal film and the TaAlN film is a conductive composite metal film.

[0176] Furthermore, in the above-described embodiment, a Ni film is used as a second metal film. However, the present invention is not limited thereto. For example, the present invention can be properly applied to the case where a non-noble metal film having a work function greater than 4.8 eV, such as a beryllium (Be) film, a carbon (C) film, a cobalt (Co), a selenium (Se) film, a tellurium (Te) film, or a rhenium (Re) film, is used as a second metal film. All the listed films are conductive elemental metal films. FIG. 10 is a table illustrating a group of metals having work functions higher than 4.8 eV which can be used for forming a second metal film.

### **EXAMPLES**

[0177] Hereinafter, examples 1 and 2 of the present invention will be described together with a conventional example and a comparative example with reference to FIG. 12 to FIG. 16

### Example 1

[0178] FIG. 12 is a schematic view for explaining a stacked structure of the example 1 (sample B) of the present invention together with a stacked structure of the conventional example (sample A) and a stacked structure of the comparative example (sample C).

[0179] In addition, FIG. 11 is a flowchart for explaining processes of forming the sample A (conventional example), the sample B (example 1), and the sample C (comparative example) that are illustrated in FIG. 12.