US 20150348985A

# (19) United States

# (12) Patent Application Publication LOIKO et al.

(10) **Pub. No.: US 2015/0348985 A1** (43) **Pub. Date: Dec. 3, 2015**

# (54) METHOD OF MAKING A SPLIT GATE NON-VOLATILE MEMORY (NVM) CELL AND A LOGIC TRANSISTOR

- (71) Applicants: **KONSTANTIN V. LOIKO**, AUSTIN, TX (US); **BRIAN A. WINSTEAD**, BRIDGETOWN (CA)

- (72) Inventors: **KONSTANTIN V. LOIKO**, AUSTIN, TX (US); **BRIAN A. WINSTEAD**, BRIDGETOWN (CA)

- (21) Appl. No.: 14/291,224

- (22) Filed: May 30, 2014

#### **Publication Classification**

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

| , ,  | H01L 27/115 | (2006.01) |

|      | H01L 21/28  | (2006.01) |

|      | H01L 21/285 | (2006.01) |

|      | H01L 29/66  | (2006.01) |

|      | H01L 29/49  | (2006.01) |

**H01L 29/423** (2006.01) **H01L 29/78** (2006.01)

(52) U.S. Cl.

CPC .... H01L 27/11568 (2013.01); H01L 27/11573 (2013.01); H01L 29/42344 (2013.01); H01L 21/28282 (2013.01); H01L 29/7843 (2013.01); H01L 29/6656 (2013.01); H01L 29/4916 (2013.01); H01L 21/28525 (2013.01)

### (57) ABSTRACT

Semiconductor structures and methods for making semiconductor structures include a split gate non-volatile memory (NVM) cell in an NVM region. A charge storage layer, a first conductive layer, and a capping layer are formed over the substrate, which are patterned to form a control gate stack in the NVM region of the substrate. A high-k dielectric layer, a metal layer, and a second conductive layer are formed over the substrate. The second conductive layer and the metal layer are patterned to form remaining portions of the second conductive layer and the metal layer over and adjacent to a first side of the control gate stack. The remaining portion of the second conductive layer is removed to form a select gate stack, which includes the remaining portion of the metal layer. A stressor layer is formed over the substrate.

### METHOD OF MAKING A SPLIT GATE NON-VOLATILE MEMORY (NVM) CELL AND A LOGIC TRANSISTOR

#### **BACKGROUND**

[0001] 1. Field

[0002] This disclosure relates generally to integrated non-volatile memory (NVM) and logic transistor manufacturing, and more specifically, to the making split gate NVM cells integrated with high-k, metal gate (HKMG) logic transistors.

[0003] 2. Related Art

[0004] Non-volatile memories (NVMs) have become very significant in the semiconductor industry and thus the manner of making them has also become very significant. On the same integrated circuits are logic transistors, and in cases where the NVM is embedded in a much larger system, the logic transistor performance is the dominant concern. The cost of making the NVM is accordingly kept as low as possible while achieving the needed performance. Ways of achieving this normally includes using techniques that can be implemented with commonly available equipment and using materials that are well characterized. An effective approach for achieving the desired performance has been found to be the use of split gate NVM cells which utilize a select gate and a control gate over a continuous channel while using HKMG transistors for the logic transistors.

[0005] Accordingly there is a need to provide further improvement in achieving both low cost and high performance for split gate NVM cells in an integration with high-k, metal gate transistors.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0006] The present invention is illustrated by way of example and is not limited by the accompanying figures, in which like references indicate similar elements. Elements in the figures are illustrated for simplicity and clarity and have not necessarily been drawn to scale.

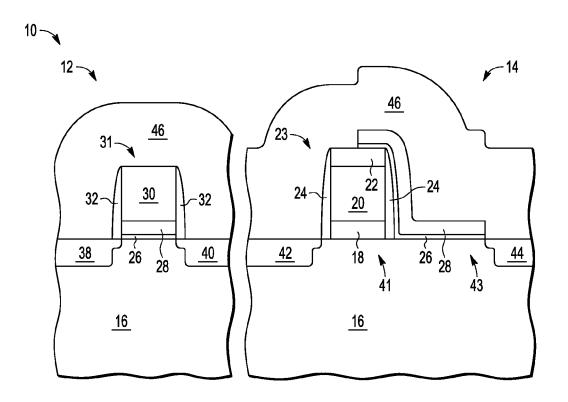

[0007] FIG. 1 is a cross section of a split gate non-volatile memory (NVM) cell and logic transistor according to a first embodiment at a stage in processing;

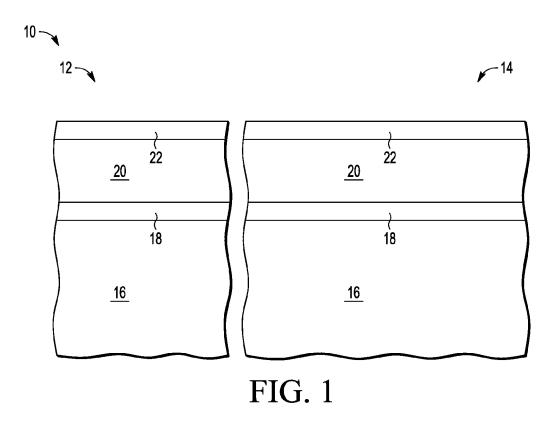

[0008] FIG. 2 is a cross section of the split gate NVM cell and logic transistor of FIG. 1 at a subsequent stage in processing;

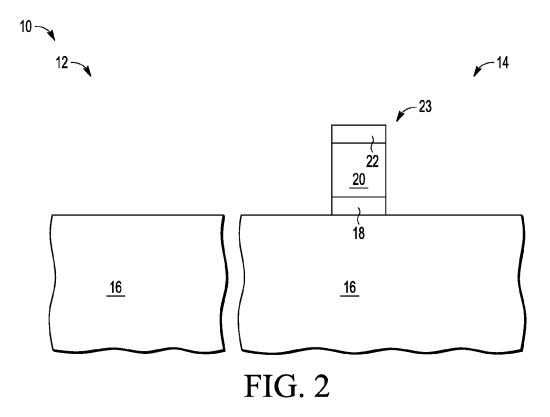

[0009] FIG. 3 is a cross section of the split gate NVM cell and logic transistor of FIG. 2 at a subsequent stage in processing:

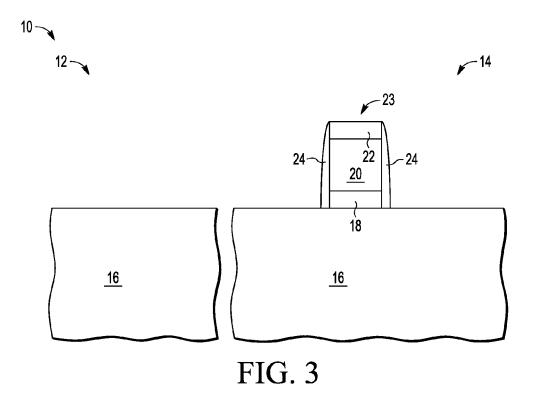

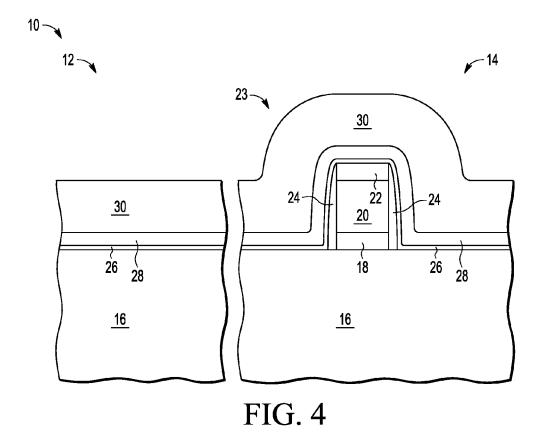

[0010] FIG. 4 is a cross section of the split gate NVM cell and logic transistor of FIG. 3 at a subsequent stage in processing;

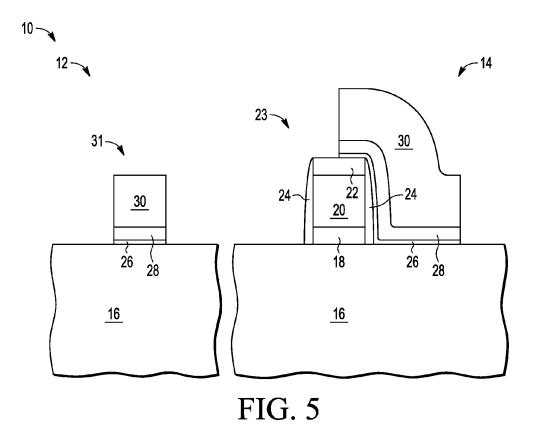

[0011] FIG. 5 is a cross section of the split gate NVM cell and logic transistor of FIG. 4 at a subsequent stage in processing;

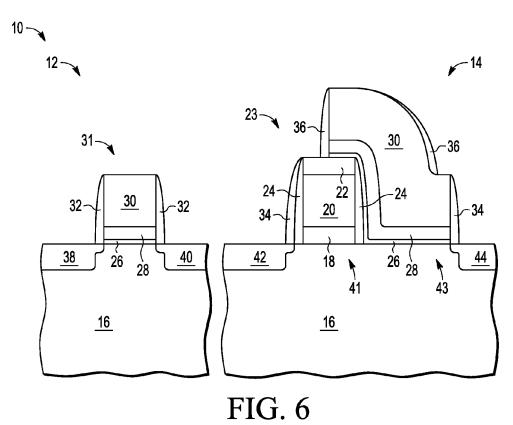

[0012] FIG. 6 is a cross section of the split gate NVM cell and logic transistor of FIG. 5 at a subsequent stage in processing:

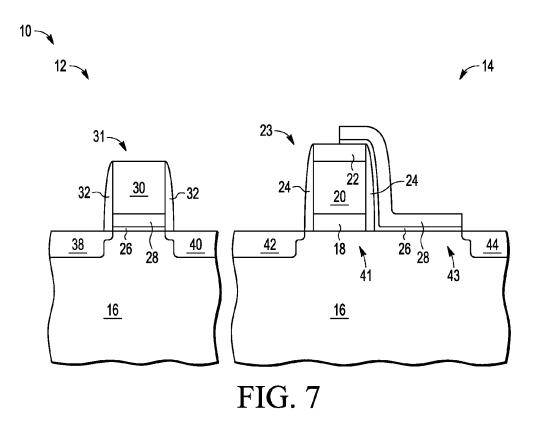

[0013] FIG. 7 is a cross section of the split gate NVM cell of and logic transistor FIG.  $\bf 6$  at a subsequent stage in processing; and

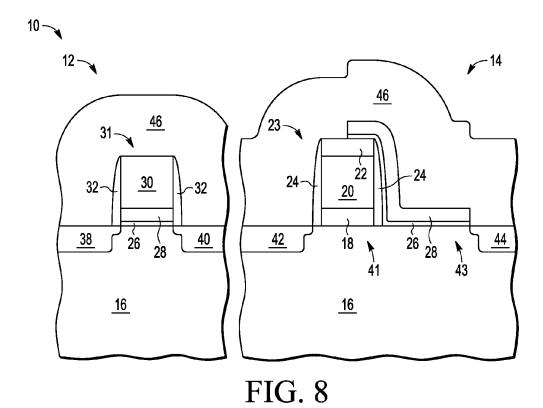

[0014] FIG. 8 is a cross section of the split gate NVM cell and logic transistor of FIG. 7 at a subsequent stage in processing.

#### DETAILED DESCRIPTION

[0015] In one aspect, a split gate NVM cell and logic transistor is formed by first forming a control gate over a charge storage layer in an NVM region. A stack of a high-k dielectric, a metal gate material, and a conductive layer is formed over both the NVM region and a logic region. The stack is patterned to leave a portion of the stack in the logic region as a logic gate and a portion adjacent to the control gate as the select gate. The conductive layer is removed from the select gate while leaving the conductive layer as part of the logic gate. A stressor layer is deposited over the logic region and the NVM region. The result is that source/drains adjacent to the logic gate are in relatively close proximity to the stressor layer while the channel of the logic transistor is significantly further from the stressor layer due to the logic gate having the conductive layer between the channel and the stressor layer. The result is that a first type of stress is applied to the source/ drains which in turn results in a second type of stress, which is opposite the first type of stress, is applied to the channel of the logic transistor. For the NVM cell, the result is that the source/drain adjacent to the control gate is in relatively close proximity to the stressor layer, that the portion of the channel of the NVM cell under the select gate is in relatively close proximity to the stressor layer due to the removal of the conductive layer from the select gate, and the portion of the channel under the control gate is significantly further from the stressor layer. The stressor layer thus applies the first type of stress to the source/drain adjacent to the control gate and to the portion of the channel of the NVM cell under the select gate which results in the second type of stress being applied to the portion of the channel of the NVM cell under the control gate. This is better understood by reference to the drawings and the following written description.

[0016] The semiconductor substrate described herein can be any semiconductor material or combinations of materials, such as gallium arsenide, silicon germanium, silicon-on-insulator (SOI), silicon, monocrystalline silicon, the like, and combinations of the above.

[0017] FIG. 1 is a partial cross-sectional view of a first example semiconductor device or structure 10 formed on a semiconductor substrate 16, which includes a logic region 12 and a non-volatile memory (NVM) region 14. Logic region 12 includes an area in which logic devices (e.g., CMOS, PMOS, NMOS transistors) are generally formed. NVM region 14 includes an area in which non-volatile memory devices (e.g., NVM bitcells) are generally formed. Though various structures and layer regions are illustrated throughout the figures with straight lines and curved or corner regions, it will be appreciated that the actual profile(s) for the different structures and layer regions will not necessarily conform to simplified depictions, but will instead depend on the specific fabrication process(es) used. In addition, the depicted device structures may be formed with different semiconductor materials having P-type conductivity and N-type conductivity. With the P-type materials, the dopant concentrations vary from lowest dopant concentrations (P-), higher dopant concentration (P), even higher dopant concentration (P+), and the highest dopant concentration (P++). Similarly, the dopant concentrations for the N-type materials vary from lowest dopant concentrations (N), higher dopant concentration (N+), and the highest dopant concentration for (N++). The semiconductor substrate described herein can be any semiconductor material or combinations of materials, such as gallium

arsenide, silicon germanium, silicon-on-insulator (SOI), silicon, monocrystalline silicon, the like, and combinations of the above.

[0018] As described below, one or more split gate thin film storage non-volatile memory bitcells may be formed in NVM region 14 with one or more control gates and one or more HKMG select gates using any desired processing steps. A non-limiting example of processing steps that may be used is provided herein. In the semiconductor structure 10, a charge storage layer 18 is formed over substrate 16 (e.g., deposited over the entirety of the substrate). Charge storage layer 18 includes discrete storage elements, such as silicon nanocrystals. In other embodiments, the discrete storage elements are made of other types of materials, such as, for example, polysilicon nanocrystals, silicon germanium nanocrystals, nanoclusters of a metal (e.g. gold, ruthenium, nickel, cobalt, tungsten), or nanoclusters of a silicide (e.g. cobalt silicide, nickel silicide). The discrete storage elements are used to selectively store charge introduced during a programming operation to selectively adjust a voltage threshold of a transistor depending upon whether a "1" or "0" value is to be stored in the memory cell. In selected embodiments, the charge storage layer 18 is formed as a nanocrystal stack, thereby forming a polysilicon-nitrided-silicon dioxide (poly-SiON) stack. While any desired charge storage layer sequence may be used, in selected example embodiments, the charge storage layer 18 may include an insulating layer formed over the substrate 16, such as by depositing a high-k dielectric layer or other appropriate insulating layer to a predetermined thickness (e.g., approximately 40-150 Angstroms), though other thicknesses may be used. On the insulating layer, a layer of conductive nanocrystals may be formed, where the nanocrystals having predetermined diameters (e.g., approximately 3-10 nanometers) and spacing (e.g., about 5 nanometers apart). After depositing the nanocrystals, another insulating layer is formed over and around the nanocrystals, such as by depositing a suitable high-k dielectric with a low pressure chemical vapor deposition (LPCVD) to a predetermined thickness (e.g., approximately 100-200 Angstroms), though other materials or thicknesses may be used.

[0019] Subsequently, a first conductive layer 20 that forms a control gate layer is formed over charge storage layer 18 (e.g., deposited over the entirety of the substrate). Conductive layer 20 may be polysilicon and may be referenced as a poly layer. Poly layer 20 may be deposited as a doped poly layer, or may be subsequently doped with appropriate impurities to make poly layer 20 conductive. It is noted that poly layer 20 may be thinner than a traditional control gate poly layer. Subsequently, a capping layer 22 is formed over poly layer 20 (e.g., deposited over the entirety of substrate 10). Capping layer 22 may be an anti-reflective coating (ARC) material, such as silicon nitride.

[0020] FIG. 2 illustrates processing of semiconductor structure 10 subsequent to FIG. 1. One or more control gate stacks 23 are formed in NVM region 14 by patterning and etching charge storage layer 18, poly layer 20, and capping layer 22. For example, a patterned etch mask is placed over the intended control gate region(s) and is used to etch and remove exposed regions of charge storage layer 18, poly layer 20, and capping layer 22 to form one or more control gate stacks 23 in NVM region 14. Although not shown, the patterned etch mask may be formed by patterning a photoresist layer or other hard mask layer, which is formed on the capping layer 22 to protect the intended control gate regions(s).

The exposed regions are then selectively etched with a dry etch, such as a reactive ion etch process. Any etch mask or photoresist layers are then stripped or removed from the one or more control gate stacks 23. As will be appreciated, any desired gate patterning and etch sequence may be used to form one or more control gate stacks 23, including but not limited to photoresist or a hard mask formation, TEOS etch (using the photoresist as a mask), ARC etch (using the remnant TEOS as a mask), pre-etch cleaning, oxide break through, main poly plasma etch, soft landing etch, poly clean overetch, and post-etch cleaning.

[0021] FIG. 3 illustrates processing of semiconductor structure 10 subsequent to FIG. 2. A first set of sidewall spacers 24 are formed around control gate stack 23 in NVM region 14. For example, one or more dielectric layers (e.g., silicon dioxide or nitride) are formed over the substrate including over the one or more control gate stacks 23 (e.g., deposited over the entirety of the substrate) and are anisotropically etched to form sidewall spacers 24.

[0022] Shown in FIG. 4 is semiconductor structure 10 after depositing a high-k dielectric layer 26 over NVM region 14 and logic region 12 which is over substrate 16. A portion of high-k dielectric layer 26 in NVM region 14 is over control gate stack 23 and according along the sides of sidewall spacer 24. Also shown in FIG. 4 is semiconductor structure 10 after depositing a metal gate layer 28 over high-k dielectric layer 26 in NVM region 14 and logic region 12 and after depositing a conductive layer 30, which may be poly, over metal gate layer 28. Metal gate layer may contain different layers that include metal such as a barrier layer directly on high-k dielectric layer 26 and a thicker metal-containing layer having a different composition than the barrier layer. In such a case, the barrier layer may be used as a work-function setting material. Conductive layer 30 is thicker than metal gate layer 28. Preferably, metal gate layer 28 plus high-k dielectric layer 26 is thinner than charge storage layer 18, which may be easier to achieve if charge storage layer 18 comprises nanocrystals.

[0023] Shown in FIG. 5 is semiconductor structure 10 after patterning conductive layer 30, metal gate layer 28, and high-k dielectric layer 36. The result is a logic gate stack 31 over substrate 16 in logic region 12 and a portion of conductive layer 30, metal gate layer 26, and high-k dielectric layer 26 over a portion of control gate stack 23, along a first side of sidewall spacer 24, and over a portion of substrate adjacent to the first side of sidewall spacer 24.

[0024] Shown in FIG. 6 is semiconductor structure 10 after sidewall spacers and source/drains. Sidewall spacer 32 is formed around logic gate stack 31. A sidewall spacer 34 is formed adjacent to control gate stack 23 and adjacent to the portion of conductive layer 30, metal gate layer 26, and high-k dielectric layer 26 that is over the portion of substrate 16 adjacent to the first side of sidewall spacer 24. A sidewall spacer 36 is formed around an upper portion of the portion of conductive layer 30, metal gate layer 26, and high-k dielectric layer 26 in NVM region 14. Source/drains 38 and 40 are formed in substrate 16 in logic region 12 adjacent to the sides of logic gate stack 31. A source/drain 42 is formed in substrate 16 in NVM region 14 adjacent to a side of sidewall spacer 24 that is adjacent to control gate stack 23. A source/drain 44 is formed in substrate 16 in NVM region 14 adjacent to the portion of conductive layer 30, metal gate layer 28, and high-k dielectric layer 26 that is over the portion of substrate 16 adjacent to the first side of sidewall spacer 24. This results in a control gate channel region 41 in substrate 16 under control

gate stack 23 and select gate channel region 43 under the portion of conductive layer 30, metal gate layer 28, and high-k dielectric layer 26 that is over the portion of substrate 16 adjacent to the first side of sidewall spacer 24. This also results in a logic channel region in substrate 16 that is under logic gate stack 31.

[0025] Shown in FIG. 7 is semiconductor structure 10 after removing the portion of conductive layer 30 in NVM region 14 to expose a top surface of the portion of metal gate layer 28 adjacent to control gate stack 23. This is a patterned etch so that the portion of conductive layer 30 that is part of logic gate stack 31 is not removed. This etch greatly reduces the height of material above select gate channel 43. Only the thickness of high-k dielectric layer 26 and metal gate layer 28 are above the select gate channel. On the other hand the height of control gate stack, which includes charge storage layer 18, conductive layer 20, and capping layer 22, is above control gate channel region 41. In addition to removing the portion of conductive layer 30 in the NVM region, sidewall spacers 34 and 36 are removed. Sidewall spacers 34 and 36 are preferably of a different material than sidewall spacer 24. For example, sidewall spacers 34 and 36 may be nitride and sidewall spacer 24 may be oxide.

[0026] Shown in FIG. 8 is semiconductor structure 10 after depositing a stressor layer 46 over substrate 16 in logic region 12 and NVM region 14. In addition to being over substrate 16, stressor layer 46 is over logic gate stack 31, control gate stack 23, and metal gate layer 28 in NVM region 14. Stressor layer 46 may be nitride and is useful for increasing the mobility of carriers and thus the performance of transistors. N channel transistors, for example, have increased performance when the channel in the direction of current flow is under tensile stress. Stressor layer 46 is separated from control gate channel region and source/drain 42 by comparatively small distance compared to the separation of stressor layer 46 from control gate channel 41. The stress of stressor layer 46 is chosen so that source/drain regions 38, 40, 42, and 44 and select gate channel region 43 are placed under a desired stress which in this case is compressive stress. In the case of inducing compressive stress in source/drain regions 38, 40, 42, and 44 and select gate channel region 43 stressor layer may be considered to have tensile stress. Stressor layer 46, being a much greater distance from the logic gate channel and control gate channel 41, applies minimal stress to the logic gate channel and control gate channel region 41. The compressive stress, or at least less tensile stress, of source/drain regions 38 and 40 results in the channel under logic gate stack 31 being tensile, or at least less compressive, and thus enhancing for an N channel transistor. The compressive stress, or at least less tensile stress, of source/drains 42 and 44 and select gate channel region 43 results in control gate channel region 41 being tensile, or at least less compressive, and thus enhancing for the control gate transistor. This also results in charge storage layer 18 responding to this compressive stress by becoming more tensile laterally, or at least less compressive laterally. Particularly with having relatively thick charge storage layer 18, the control gate transistor inherently has a significantly lower Gm than does the select gate transistor that has a high-k dielectric. An improvement in the mobility in control gate channel region has much more impact in the overall Gm of the memory device than does a corresponding decline in the mobility in the select gate channel. The overall mobility of the NVM cell is a type of sum of the mobility of control gate channel region 41 and select gate channel region 43. The select gate channel region mobility is much greater than that of the control gate region mobility. Any percentage increase in performance of the control gate will have a bigger effect on the overall performance of the NVM cell than the same percentage decrease in the select gate channel region mobility.

[0027] Thus it is seen that the removal of the portion of conductive layer 30 in NVM region 14 gives greater stress transfer to the select gate channel region 43. The result is increased compressive stress, or at least reduced tensile stress, in select gate channel region 43 and a corresponding increase in the tensile stress, or at least reduced compressive stress, in control gate channel region 41. The increase in mobility in control gate channel region 41 more than offsets the decrease in mobility in select gate channel region 43 to result in an overall increase in the net mobility combining the select gate and control gate channel regions being series. In addition, for the NVM cell, charge retention is improved with tensile stress on the charge storage layer. In improving both charge retention and mobility, the desired stress is a lateral stress running in the channel direction.

[0028] By now it is apparent that a method of making a semiconductor structure using a substrate has been disclosed, wherein the semiconductor structure comprises a split gate non-volatile memory (NVM) cell in an NVM region of the substrate, The method further includes forming a charge storage layer over the substrate. The method further includes depositing a first conductive layer over the charge storage layer. The method further includes patterning the capping layer, the first conductive layer, and the charge storage layer to form a control gate stack in the NVM region. The method further includes depositing a capping layer over the first conductive layer. The method further includes forming a high-k dielectric layer over the substrate including over the control gate stack. The method further includes forming a metal layer over the high-k dielectric layer. The method further includes depositing a second conductive layer over the metal layer. The method further includes patterning the second conductive layer and the metal layer to form a remaining portion of the second conductive layer and a remaining portion of the metal layer over a portion of the control gate stack and adjacent to a first side of the control gate stack. The method further includes removing the remaining portion of the second conductive layer to form a select gate stack, wherein the select gate stack comprises the remaining portion of the metal layer. The method further includes depositing a stressor layer over the substrate including over the control gate stack and over the select gate stack. The method may further include forming an insulating sidewall spacer on each side of the control gate stack prior to the forming the high-k dielectric layer. The method may have a further characterization by which the semiconductor structure further comprises a logic transistor in a logic region of the substrate, the method further include removing the capping layer, the first conductive layer, and the charge storage layer from the logic region prior to forming the high-k dielectric layer. The method may further include patterning the second conductive layer, the metal layer, and the high-k dielectric layer to form a logic gate stack in the logic region. The method may further include forming a first set of sidewall spacers on sides of the logic gate stack prior to the depositing the stressor layer and forming a second set of sidewall spacers on sides of the split gate NVM cell prior to the depositing the stressor layer. The method may further include removing the second set of sidewall spacers from

each side of the split gate NVM cell prior to the depositing the stressor layer. The method have a further characterization by which the patterning the second conductive layer and the metal layer further includes patterning the high-k dielectric layer to leave a remaining portion of the high-k dielectric layer over the portion of the control gate stack and adjacent to the first side of the control gate stack, wherein the removing the remaining portion of the second conductive layer further leaves the remaining portion of the high-k dielectric layer between the control gate stack and the remaining portion of the metal layer and. The method may have a further characterization by which the select gate stack further comprises the remaining portion of the high-k dielectric layer. The method may have a further characterization by which the stressor layer has tensile stress, the stressor layer induces lateral compressive stress in a channel direction in a first region of the substrate under the select gate stack and in a second region of the substrate adjacent to a second side of the control gate stack, the second side of the control gate stack is on an opposite side of the split gate NVM cell from the select gate stack, the stressor layer has tensile stress, and lateral stress in a first region in the substrate under the select gate stack is less tensile than lateral stress in a second region in the substrate under the control gate stack.

[0029] Also disclosed is a semiconductor structure using a substrate having a non-volatile memory (NVM) region. The semiconductor structure further includes a split gate NVM cell. The split gate NVM cell includes a control gate stack comprising a charge storage layer over the substrate, a first conductive layer over the charge storage layer, and a capping layer over the first conductive layer. The split gate NVM cell further includes a select gate stack laterally adjacent to a first side of the control gate stack, the select gate stack comprising a high-k dielectric layer over the substrate, along the first side of the control gate stack, and over a top surface of the control gate stack, and a metal layer over the high-k dielectric layer. The split gate NVM cell further includes a stressor layer over the split gate NVM cell. The semiconductor structure may have a logic region and the semiconductor structure may further include a logic gate stack in the logic region, the logic gate stack comprising the high-k dielectric layer over the substrate, the metal layer over the high-k dielectric layer, and a second conductive layer over the metal layer. The semiconductor structure may further include an insulating sidewall spacer on each side of the logic gate stack. The semiconductor structure may further include the stressor layer over the logic gate stack. The semiconductor structure may further include an insulating sidewall spacer on each side of the control gate stack. The semiconductor structure may further include source/drain implant regions in the substrate adjacent to a second side of the control gate stack and adjacent to a first side of the select gate stack, wherein the second side of the control gate stack is on an opposite side of the split gate NVM cell from the first side of the select gate stack. The semiconductor structure may further include source/drain implant regions in the substrate adjacent to a first side of the logic gate stack and adjacent to a second side of the logic gate stack, wherein the first side of the logic gate stack is opposite from the second side of the logic gate stack.

[0030] Disclosed also is a method of making a semiconductor structure using a substrate, wherein the semiconductor structure comprises a split gate non-volatile memory (NVM) structure in an NVM region of the substrate. The method further includes forming a charge storage layer over the sub-

strate. The method further includes depositing a first polysilicon layer over the charge storage layer. The method further includes depositing a capping layer over the first polysilicon layer. The method further includes patterning the capping layer, the first polysilicon layer, and the charge storage layer to leave a control gate stack in the NVM region, wherein the control gate stack comprises remaining portions of the capping layer, the first polysilicon layer, and the capping layer. The method further includes forming a high-k dielectric layer over the substrate including over the control gate stack. The method further includes forming a metal layer over the high-k dielectric layer. The method further includes depositing a second polysilicon layer over the metal layer. The method further includes patterning the second polysilicon layer and the metal layer to leave a remaining portion of the metal layer over the substrate, along a first side of the control gate stack, and over a top surface of the remaining portion of the capping layer, and to leave a remaining portion of the second polysilicon layer over the remaining portion of the metal layer. The method further includes removing the remaining portion of the second polysilicon layer to expose the remaining portion of the metal layer and to leave a select gate stack laterally adjacent to the first side of the control gate stack wherein the select gate stack comprises the remaining portion of the metal layer. The method further includes depositing a stressor layer over the substrate including over the control gate stack and over the remaining portion of the metal layer. The method may have a further characterization by which the patterning the second polysilicon layer and the metal layer further includes patterning the high-k dielectric layer to leave a remaining portion of the high-k dielectric layer over the portion of the capping layer and adjacent to the first side of the control gate stack. The method has a further characterization by which the removing the remaining portion of the second polysilicon layer further leaves the remaining portion of the high-k dielectric layer between the control gate stack and the remaining portion of the metal layer and the select gate stack further comprises the remaining portion of the high-k dielectric layer. The method has a further characterization by which the stressor layer has tensile stress, the stressor layer induces lateral compressive stress in a channel direction in a first region of the substrate under the select gate stack and in a second region of the substrate adjacent to a second side of the control gate stack, the second side of the control gate stack is on an opposite side of the split gate NVM cell from the select gate stack, a third region of the substrate is located under the control gate stack between the first region and the second region, and lateral tensile stress is induced in the third region of the substrate. The method has a further characterization by which the select gate stack is thinner than the charge storage layer of the control gate stack.

[0031] Although the invention is described herein with reference to specific embodiments, various modifications and changes can be made without departing from the scope of the present invention as set forth in the claims below. For example, materials used for metal gates and high-k dielectrics as well as other features can be varied. Accordingly, the specification and figures are to be regarded in an illustrative rather than a restrictive sense, and all such modifications are intended to be included within the scope of the present invention. Any benefits, advantages, or solutions to problems that are described herein with regard to specific embodiments are not intended to be construed as a critical, required, or essential feature or element of any or all the claims.

[0032] The term "coupled," as used herein, is not intended to be limited to a direct coupling or a mechanical coupling.

[0033] Furthermore, the terms "a" or "an," as used herein, are defined as one or more than one. Also, the use of introductory phrases such as "at least one" and "one or more" in the claims should not be construed to imply that the introduction of another claim element by the indefinite articles "a" or "an" limits any particular claim containing such introduced claim element to inventions containing only one such element, even when the same claim includes the introductory phrases "one or more" or "at least one" and indefinite articles such as "a" or "an." The same holds true for the use of definite articles.

[0034] Unless stated otherwise, terms such as "first" and "second" are used to arbitrarily distinguish between the elements such terms describe. Thus, these terms are not necessarily intended to indicate temporal or other prioritization of such elements.

1. A method of making a semiconductor structure using a substrate, wherein the semiconductor structure comprises a split gate non-volatile memory (NVM) cell in an NVM region of the substrate, the method comprising:

forming a charge storage layer over the substrate;

depositing a first conductive layer over the charge storage layer:

depositing a capping layer over the first conductive layer; patterning the capping layer, the first conductive layer, and the charge storage layer to form a control gate stack in the NVM region;

forming a high-k dielectric layer over the substrate including over the control gate stack;

forming a metal layer over the high-k dielectric layer;

depositing a second conductive layer over the metal layer; patterning the second conductive layer and the metal layer to form a remaining portion of the second conductive layer and a remaining portion of the metal layer over a portion of the control gate stack and adjacent to a first side of the control gate stack;

removing the remaining portion of the second conductive layer to form a select gate stack, wherein the select gate stack comprises the remaining portion of the metal layer; and

depositing a stressor layer over the substrate including over the control gate stack and over the select gate stack.

2. The method of claim 1, further comprising:

forming an insulating sidewall spacer on each side of the control gate stack prior to the forming the high-k dielectric layer.

3. The method of claim 1, wherein the semiconductor structure further comprises a logic transistor in a logic region of the substrate, the method further comprising:

removing the capping layer, the first conductive layer, and the charge storage layer from the logic region prior to forming the high-k dielectric layer.

4. The method of claim 3, further comprising:

patterning the second conductive layer, the metal layer, and the high-k dielectric layer to form a logic gate stack in the logic region.

5. The method of claim 4, further comprising:

forming a first set of sidewall spacers on sides of the logic gate stack prior to the depositing the stressor layer; and forming a second set of sidewall spacers on sides of the split gate NVM cell prior to the depositing the stressor

- **6**. The method of claim **5**, further comprising:

- removing the second set of sidewall spacers from each side of the split gate NVM cell prior to the depositing the stressor layer.

- 7. The method of claim 1, further comprising:

the patterning the second conductive layer and the metal layer further comprises patterning the high-k dielectric layer to leave a remaining portion of the high-k dielectric layer over the portion of the control gate stack and adjacent to the first side of the control gate stack, wherein

the removing the remaining portion of the second conductive layer further leaves the remaining portion of the high-k dielectric layer between the control gate stack and the remaining portion of the metal layer, and the select gate stack further comprises the remaining portion of the high-k dielectric layer.

8. The method of claim 1, wherein

the stressor layer has tensile stress,

the stressor layer induces lateral compressive stress in a channel direction in a first region of the substrate under the select gate stack and in a second region of the substrate adjacent to a second side of the control gate stack,

the second side of the control gate stack is on an opposite side of the split gate NVM cell from the select gate stack,

a third region of the substrate is located under the control gate stack between the first region and the second region, and

lateral tensile stress is induced in the third region of the substrate.

9. The method of claim 1, wherein

the stressor layer has tensile stress, and

lateral stress in a first region in the substrate under the select gate stack is less tensile than lateral stress in a second region in the substrate under the control gate stack.

**10**. A semiconductor structure using a substrate having a non-volatile memory (NVM) region, comprising:

a split gate NVM cell comprising:

- a control gate stack comprising a charge storage layer over the substrate, a first conductive layer over the charge storage layer, and a capping layer over the first conductive layer, and

- a select gate stack laterally adjacent to a first side of the control gate stack, the select gate stack comprising a high-k dielectric layer over the substrate, along the first side of the control gate stack, and over a top surface of the control gate stack, and a metal layer over the high-k dielectric layer; and

a stressor layer over the split gate NVM cell.

- 11. The semiconductor structure of claim 10, the substrate further having a logic region, wherein the semiconductor structure further comprises:

- a logic gate stack in the logic region, the logic gate stack comprising the high-k dielectric layer over the substrate, the metal layer over the high-k dielectric layer, and a second conductive layer over the metal layer.

- 12. The semiconductor structure of claim 11, wherein the semiconductor structure further comprises:

- an insulating sidewall spacer on each side of the logic gate

- 13. The semiconductor structure of claim 11, wherein the semiconductor structure further comprises:

the stressor layer over the logic gate stack.

- 14. The semiconductor structure of claim 10, wherein the semiconductor structure further comprises:

- an insulating sidewall spacer on each side of the control gate stack.

- **15**. The semiconductor structure of claim **10**, wherein the semiconductor structure further comprises:

- source/drain implant regions in the substrate adjacent to a second side of the control gate stack and adjacent to a first side of the select gate stack, wherein the second side of the control gate stack is on an opposite side of the split gate NVM cell from the first side of the select gate stack.

- **16.** The semiconductor structure of claim **11**, wherein the semiconductor structure further comprises:

- source/drain implant regions in the substrate adjacent to a first side of the logic gate stack and adjacent to a second side of the logic gate stack, wherein the first side of the logic gate stack is opposite from the second side of the logic gate stack.

- 17. A method of making a semiconductor structure using a substrate, wherein the semiconductor structure comprises a split gate non-volatile memory (NVM) structure in an NVM region of the substrate, the method comprising:

forming a charge storage layer over the substrate;

depositing a first polysilicon layer over the charge storage layer;

depositing a capping layer over the first polysilicon layer; patterning the capping layer, the first polysilicon layer, and the charge storage layer to leave a control gate stack in the NVM region, wherein the control gate stack comprises remaining portions of the capping layer, the first polysilicon layer, and the capping layer;

forming a high-k dielectric layer over the substrate including over the control gate stack;

forming a metal layer over the high-k dielectric layer; depositing a second polysilicon layer over the metal layer; patterning the second polysilicon layer and the metal layer to leave a remaining portion of the metal layer over the substrate, along a first side of the control gate stack, and over a top surface of the remaining portion of the capping layer, and to leave a remaining portion of the second polysilicon layer over the remaining portion of the metal layer;

removing the remaining portion of the second polysilicon layer to expose the remaining portion of the metal layer and to leave a select gate stack laterally adjacent to the first side of the control gate stack, wherein

the select gate stack comprises the remaining portion of the metal layer; and

depositing a stressor layer over the substrate including over the control gate stack and over the remaining portion of the metal layer.

18. The method of claim 17, wherein:

the patterning the second polysilicon layer and the metal layer further comprises

patterning the high-k dielectric layer to leave a remaining portion of the high-k dielectric layer over the portion of the capping layer and adjacent to the first side of the control gate stack, wherein

the removing the remaining portion of the second polysilicon layer further leaves the remaining portion of the high-k dielectric layer between the control gate stack and the remaining portion of the metal layer, and

the select gate stack further comprises the remaining portion of the high-k dielectric layer.

19. The method of claim 17, wherein

the stressor layer has tensile stress,

the stressor layer induces lateral compressive stress in a channel direction in a first region of the substrate under the select gate stack and in a second region of the substrate adjacent to a second side of the control gate stack,

the second side of the control gate stack is on an opposite side of the split gate NVM cell from the select gate stack,

a third region of the substrate is located under the control gate stack between the first region and the second region, and

lateral tensile stress is induced in the third region of the substrate.

20. The method of claim 17, wherein

the select gate stack is thinner than the charge storage layer of the control gate stack.

\* \* \* \* \*