## (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 23 June 2005 (23.06.2005)

**PCT**

# (10) International Publication Number WO 2005/057789 A1

(51) International Patent Classification<sup>7</sup>: 19/0948

H03K 19/23,

(21) International Application Number:

PCT/NO2004/000381

(22) International Filing Date:

10 December 2004 (10.12.2004)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

20035537

11 December 2003 (11.12.2003) NO

- (71) Applicant (for all designated States except US): LEIV EIRIKSSON NYSKAPING AS [NO/NO]; Leiv Eiriksson Senter, N-7462 Trondheim (NO).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): AUNET, Snorre [NO/NO]; Dybdahls v 17C, N-7051 Trondheim (NO).

- (74) Agent: CURO AS; Box 38, Arnenvg., N-7231 Lundamo (NO).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: CIRCUIT ELEMENT

(57) Abstract: A circuit element comprising N paired complementary transistors. The transistors are connected to an upper  $(V_{DD})$  and lower voltage level  $(V_{SS})$ , in such a way that the paired transistors operate in subthreshold. N input terminals  $(X_1, X_2, ... X_N)$  are connected to the respective paired transistors. Control terminals (BP, BN) are connected to control input nodes of the transistors. The circuit element provides the possibility of real time configuration between various logic functions with a minimum of transistors and wiring.

#### Circuit Element

The present invention relates to a circuit element according to the introductory part of claim

1. The circuit element has a relatively low power consumption, and will be particularly

5 suitable for general ultra-low power consumption applications, like niches such as space

technology, biological implants, and neuromorphic electronics. However, the application of

the circuit element is not restricted to such niches.

## **Background**

Digital systems are used for a range of different purposes when it comes to processing and calculation of data, such as in control systems, communication systems, and measuring systems. Digital circuits use discreet signals, which are usually binary, i.e. only two values are used. The advantage with this is that the reliability with regard to errors is good, ensuring that the circuits are accurate.

15

Analog systems use analog signals, which vary continously within a range. Thus analog systems are more vulnerable to errors.

Digital systems normally comprise a central prosessing unit (CPU) that executes arithmetic functions (for instance addition, subtraction, and division), and logic functions (for instance AND, OR, NAND, NOR, and NOT). The arithmetic and logic functions are executed by a number of logic gates, or circuit elements, which are interconnected, and form a network with multiple logic depths. The logic circuit elements normally include one or more inputs, and an output. The number of inputs are described as the "fan-in" of the circuit element.

25 Usually, AND denotes the logic function AND with two inputs, whereas AND3 denotes the same function with three inputs. The notation "'" denotes inversion.

When designing circuits, a range of considerations must be taken into accout, particularly with regard to the requirements of the application. The circuit elements include, for example, different types of transistors, capacitors, and resistors, which are selected with regard to these requirements.

CMOS-transistors are devices with four nodes or electrodes, namely the source, drain, gate, and well. In this context, two types of such transistors exist, p-channel MOSFET transistors and n-channel MOSFET transistors. In most applications of such transistors, the well is connected to the source.

5

Within the development of processor units, there is a large focus on speed. As the speed of the processor units increase, so does the power requirement and the operating temperature. Processing units are used, for example, in laptop computers, where the power consumption should not be too great in relation to the battery capacity.

10

In a range of other applications, the power consumption is far more important than the speed. This applies to space technology, units for biological implants, neuromorph electronics, and nano technology, for instance. In neuromorph electronics, such as electric circuits that model or simulate neural networks, both digital and analog signals are often used in the inputs and the outputs of the circuits.

It is known to reduce the operating voltage in electric circuits, so that the transistors operate in what is called subthreshold, or weak inversion. From the paper "Robust Ultra-Low Power Sub-threshold DTMOS Logic", Soeleman, H., Roy, K. and Paul, B., ISLPED 2000,

20 Rapallo, Italy, it is known that operation in this area results in a significant reduction in power consumption. However, a consequence is that the circuit becomes slower, compared to the classic operation area.

Threshold logic uses discreet signals with two or more values. For instance, ternary logic uses three values on the output, whereas quaternary logic uses four. Threshold logic can also have multiple discreet levels on the input signals, while the output signal is binary, i.e. logic 0 or 1.

The following formula yields the sign f of the weighted sum of a series of inputs  $x_1...x_n$ :

30

$$f(x_1,...,x_n) = sgn(\sum_{i=1}^n \omega_i x_i - \theta)$$

[1]

where  $\omega_i$  denotes the weight of the input  $x_i$ ,  $\theta$  denotes the threshold value, and n denotes the number of inputs, or fan-in. This is known from Beiu et al., mentioned below.

It is known that circuit elements, which use threshold logic, may reduce the number of transistors and the amount of wiring. This reduces the chip area, which results in a reduction in the production costs.

The paper "VLSI Implementations of Threshold Logic - A Comprehensive Survey", Beiu, Valeriu et al, IEEE Transactions on neural networks, vol. 14, No. 5. September 2003 provides an historical overview of the technical developments in the field of threshold logic. Here, US patent 3,715,603 is mentioned, which describes a majority-minority circuit element, which is achieved with six transistors. This will function as a logic NOR2 or a logic NAND2 circuit element. The drawback with this circuit is that an inverter is required to amplify the signal before the output.

15

## **Object**

The main object of the present invention is to provide a logic circuit element with very low power consumption. The circuit element shall contain very few transistors and very little wiring.

20

An additional object is that the function of the circuit element shall be reconfigurable in real time.

#### The invention

25 The present invention is indicated in the characterizing part of claim 1. An additional aspect of the invention is indicated in the characterizing part of claim 5. Further embodiments appear from the dependent claims.

In the following example of embodiment, MOS transistors are used. However, the invention should not be restricted to the use of MOS transistors. Transistor units in general may also be used. With transistor unit is meant any device having the possibility of controlling the current and/or voltage characteristics between nodes of the unit, by applying voltage and/or current to an additional node. In the circuit element according to the invention, the

transistor units have at least four nodes. Such a unit can be a MOS-transistor with the nodes DRAIN, SOURCE, GATE, and WELL.

## Example

- 5 The present invention will be described in the following, with reference to the accompanying drawings, where

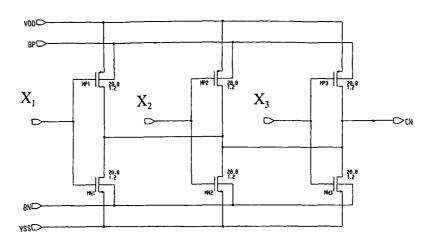

- Fig. 1 illustrates a circuit diagram of an embodiment of the circuit element according to the invention,

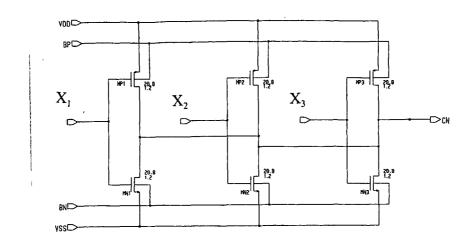

- Fig. 2 illustrates a circuit diagram of an embodiment used as a full adder,

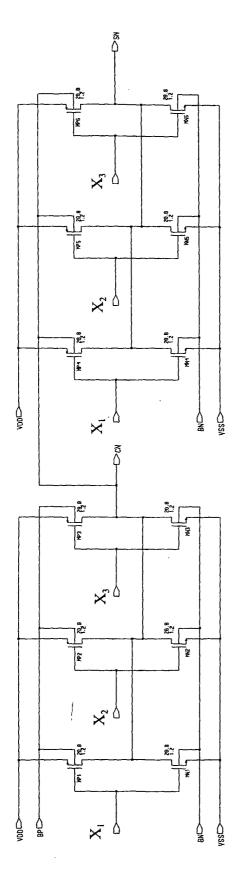

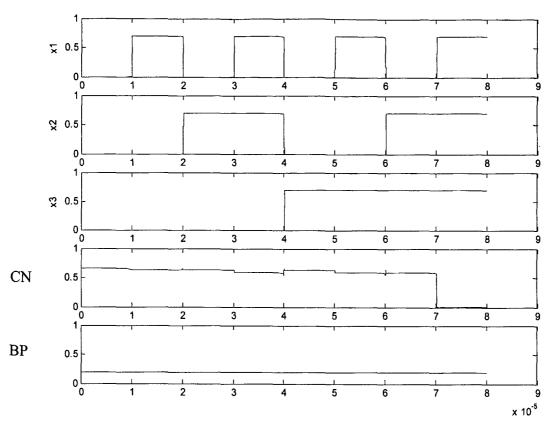

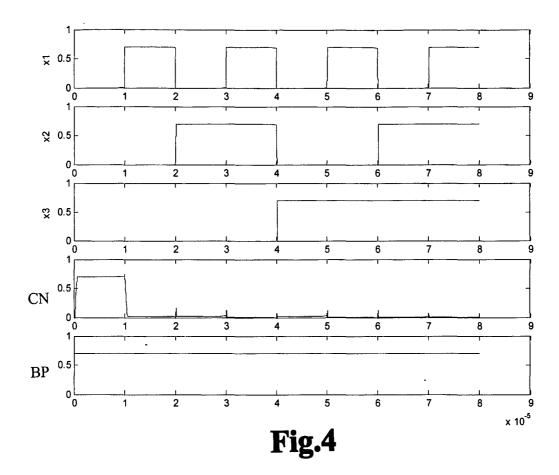

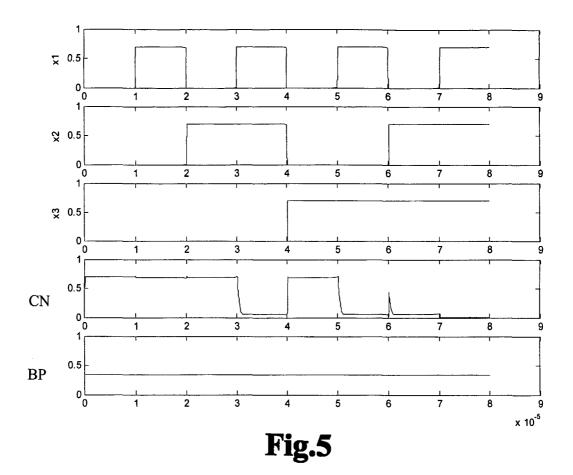

- 10 Fig. 3-5 illustrate the result of AimSpice-simulations of the circuit element, where the horizontal axis indicates time and the vertical axis indicates voltage in volts, and

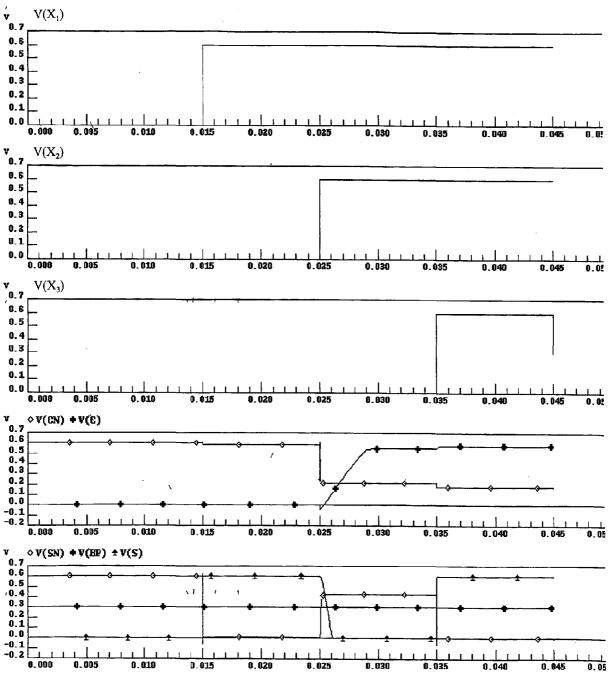

- Fig. 6 illustrates the result of an ELDO-simulation of the circuit element/full adder.

- Fig. 1 illustrates an embodiment of the invention. Here, the circuit element comprises N=3 pairs of transistors, but N can vary from N=2 upwards. There is one pair of transistors per input terminal, which means that N also denotes the number of input terminals. If a digital output signal shall be used, the delays in the circuit element will limit the number of input terminals.

- 20 Each pair of transistors comprises an NMOS transistor MN, and a PMOS transistor MP. The first pair of transistors comprises the NMOS transistor MN<sub>1</sub> and the PMOS transistor MP<sub>1</sub>, the second pair comprises the NMOS transistor MN<sub>2</sub> and the PMOS transistor MP<sub>2</sub>, whereas the third pair of transistors comprises the NMOS transistor MN<sub>3</sub> and the PMOS transistor MP<sub>3</sub>. In this embodiment, the transistors are devices with four nodes or

- 25 electrodes, namely source, drain, gate, and well. The drain node of the NMOS transistor MN is connected to the drain node of the PMOS transistor MP. Furthermore, the drain terminal of the first pair of transistors is connected to the drain terminal of the second pair of transistors, which in turn is connected to the drain terminal of the third pair of transistors.

- 30 The source node of the NMOS transistor is connected to a lower voltage level V<sub>SS</sub>, which is typically earth or 0 V. The source node of the PMOS transistor is connected to an upper voltage level V<sub>DD</sub>. The supply voltage in many of the standard CMOS integrated circuits of

today is 3.3 V. The voltage level  $V_{DD}$  will therefore typically be less than 1 V, so that the transistors operate in subthreshold, or weak inversion.

The circuit element further comprises N = 3 input terminals X<sub>1</sub>, X<sub>2</sub> and X<sub>3</sub>. The input terminal X<sub>1</sub> is connected both to the gate node of the PMOS transistor MP<sub>1</sub>, and to the gate node of the NMOS transistor MN<sub>1</sub>, whereas the input terminal X<sub>2</sub> is connected both to the gate node of the PMOS transistor MP<sub>2</sub>, and to the gate node of the NMOS transistor MN<sub>2</sub>, and the input terminal X<sub>3</sub> is likewise connected both to the gate node of the PMOS transistor MP<sub>3</sub>, and to the gate node of the NMOS transistor MN<sub>3</sub>.

10

Furthermore, the circuit element comprises an output terminal CN, which is connected to the drain node of the PMOS transistor MP<sub>3</sub> and to the drain terminal of the NMOS transistor MN<sub>3</sub>. Off course, the output terminal CN may be connected to any of the drain nodes of the transistor pairs.

15

The circuit element also comprises a control terminal BN connected to the well nodes of the NMOS transistors MN<sub>1</sub>, MN<sub>2</sub>, and MN<sub>3</sub>, and a control terminal BP, connected to the well nodes of the PMOS transistors MP<sub>1</sub>, MP<sub>2</sub>, and MP<sub>3</sub>.

20 This circuit element has a range of applications, of which some will be described in further detail by means of the following examples:

## Example 1: The circuit element as logic NAND3, NOR3, or CARRY'

The following example is described with reference to Fig. 1. In this example, the voltage levels of the terminals V<sub>SS</sub> and BN are 0 V, and the voltage of the terminal V<sub>DD</sub> is 0.7 V. This implies that the transistors operate in the subthreshold area. By varying the voltage level of the control terminal BP, the voltage level of the output terminal CN is simulated for different logic voltage levels on the input terminals X<sub>1</sub>, X<sub>2</sub>, X<sub>3</sub>.

30 In this example, as both of the terminals V<sub>ss</sub> and BN are 0 V, the control terminal BN could be omitted. Also, instead of controlling the logic function with BP, the terminal BP could be omitted, and the circuit could be controlled with BN. The well node of the PMOS-transistors would then normally be connected to the source nodes. One could also imagine

controlling the circuit with the control terminals BN and BP short circuited. Furthermore, both of the terminals BN and BP could be used simultaneously to control the function of the circuit.

5 These simulations are carried out by means of the computer program AimSpice, and the simulation results are fed into the computer program MatLab, for presentation of the results in the form of graphs, as shown in Figs. 3, 4, and 5.

In Fig. 3, the voltage level of the control terminal BP is 0.2 V. The result of the simulation 10 is presented as logic values in the following table:

|    | Time [x 10 <sup>-5</sup> s] | $X_1$ | X <sub>2</sub> | X <sub>3</sub> | CN |

|----|-----------------------------|-------|----------------|----------------|----|

|    | 0.5                         | 0     | 0              | 0              | 1  |

|    | 1.5                         | 1     | 0              | 0              | 1  |

| 15 | 2.5                         | 0     | 1              | 0              | 1  |

|    | 3.5                         | 1     | 1              | 0              | 1  |

|    | 4.5                         | 0     | 0              | 1              | 1  |

|    | 5.5                         | 1     | 0              | 1              | 1  |

|    | 6.5                         | 0     | 1              | 1              | 1  |

| 20 | 7.5                         | 1     | 1              | 1              | 0  |

Table 1: NAND-function

As is apparent from the table, the output terminal has logic value 0, only when all of the input terminals have logic value 1. This corresponds to a NAND-function.

In Fig. 4, the voltage level of the control terminal BP is 0.7 V. The result of the simulation is shown as logic values in the following table:

|   | Time [x 10 <sup>-5</sup> s] | $X_1$ | $X_2$ | $X_3$ | CN |

|---|-----------------------------|-------|-------|-------|----|

| 5 | 0.5                         | 0     | 0     | 0     | 1  |

|   | 1.5                         | 1     | 0     | 0     | 0  |

|   | 2.5                         | 0     | 1     | 0     | 0  |

|   | 3.5                         | 1     | 1     | 0     | 0  |

|   | 4.5                         | 0     | 0     | 1     | 0  |

|   | 5.5                         | 1     | 0     | 1     | 0  |

|   | 6.5                         | 0     | 1     | 1     | 0  |

|   | 7.5                         | 1     | 1     | 1     | 0  |

10

Table 2: NOR-function

As is apparent from table 2, the output terminal has logic value 1, only when all the input terminals have logic value 0. This corresponds to a NOR-function.

15

In Fig. 5, the voltage level of the control terminal BP is 0.342 V. The result of the simulation is shown as logic values in the following table:

| Time [x 10 <sup>-5</sup> s] | X <sub>1</sub>                                | $X_2$                                                                                                                               | $X_3$                                                                                                                                               | CN                                                                                                                                                                                                                                                  |

|-----------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.5                         | 0                                             | 0                                                                                                                                   | 0                                                                                                                                                   | 1                                                                                                                                                                                                                                                   |

| 1.5                         | 1                                             | 0                                                                                                                                   | 0                                                                                                                                                   | 1                                                                                                                                                                                                                                                   |

| 2.5                         | 0                                             | 1                                                                                                                                   | 0                                                                                                                                                   | 1                                                                                                                                                                                                                                                   |

| 3.5                         | 1                                             | 1                                                                                                                                   | 0                                                                                                                                                   | 0                                                                                                                                                                                                                                                   |

| 4.5                         | 0                                             | 0                                                                                                                                   | 1                                                                                                                                                   | 1                                                                                                                                                                                                                                                   |

| 5.5                         | 1                                             | 0                                                                                                                                   | 1                                                                                                                                                   | 0                                                                                                                                                                                                                                                   |

| 6.5                         | 0                                             | 1                                                                                                                                   | 1                                                                                                                                                   | 0                                                                                                                                                                                                                                                   |

| 7.5                         | 1                                             | 1                                                                                                                                   | 1                                                                                                                                                   | 0                                                                                                                                                                                                                                                   |

|                             | 0.5<br>1.5<br>2.5<br>3.5<br>4.5<br>5.5<br>6.5 | 0.5       0         1.5       1         2.5       0         3.5       1         4.5       0         5.5       1         6.5       0 | 0.5     0     0       1.5     1     0       2.5     0     1       3.5     1     1       4.5     0     0       5.5     1     0       6.5     0     1 | 0.5       0       0       0         1.5       1       0       0         2.5       0       1       0         3.5       1       1       0         4.5       0       0       1         5.5       1       0       1         6.5       0       1       1 |

Table 3: CARRY'-function

PCT/NO2004/000381 8

From table 3, it is apparent that when none, or only one of the inputs has logic value 1, the output terminal has logic value 1. When two or three of the input terminals have logic value 1, the output terminal has logic value 0. This corresponds to a CARRY'-function.

5 Accordingly, by use of only six transistors, a circuit element that can be reconfigured in real time between logic NAND3, logic NOR3, or CARRY', depending on the signal of the control terminal BP, is achieved in this example. Of course, a separate control circuit is required for the control terminal BP, but the same control circuit can sumultaneously control many such circuit elements on one chip, so that the total reduction in the number of 10 transistors can be substantial.

### Example 2: The circuit element as a full adder

The following example is described with reference to Fig. 2. A full adder is obtained by connecting two circuit elements as described above in series as is described below. All of 15 the input terminals  $x_1$ ,  $x_2$ ,  $x_3$ , the terminal for the lower voltage level  $V_{SS}$ , and the terminal for the upper voltage level V<sub>DD</sub>, as well as the control terminal BN of both circuit elements, are connected as described above. The circuit elements are connected in series, in such a way that the output terminal CN of the first circuit element is connected to the control terminal BP of the second circuit element. The first circuit element comprises the transistor 20 pairs MP<sub>1-3</sub>, MN<sub>1-3</sub>, whereas the second circuit element comprises the transistor pairs MP<sub>4-6</sub>,  $MN_{4-6}$ .

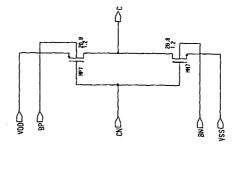

The control terminal BP of the first circuit element is as described above. An output terminal SN of the second circuit element is connected to the drain node of the PMOS 25 transistor MP<sub>6</sub>, and to the drain node of the NMOS transistor MN<sub>6</sub>, in the same way as the output terminal CN is connected to the drain nodes of MP<sub>3</sub> and MN<sub>3</sub>.

Two additional transistor pairs are used to achieve a full adder according to the invention. The output terminal CN of the first circuit element is connected both to the gate node of the 30 PMOS transistor MP<sub>2</sub> and to the gate node of the NMOS transistor MN<sub>2</sub>. Furthermore, the output terminal SN of the second circuit element is connected both to a gate node of a PMOS transistor MP<sub>8</sub> and to a gate node of a NMOS transistor MN<sub>8</sub>. The voltage supply for these four transistors occurs by means of the voltage terminals V<sub>SS</sub> and V<sub>DD</sub>, and the control

terminal BN is connected to the well nodes of the NMOS transistors MN<sub>7</sub> and MN<sub>8</sub>, and the control terminal BP is connected to the well nodes of the PMOS transistors MP<sub>7</sub>, and MP<sub>8</sub>, in the same way as described above.

5 An output terminal C is connected to the drain terminals of the transistor pair MP<sub>7</sub> and MN<sub>7</sub>, and an output terminal S is connected to the drain terminals of the transistor pair MP<sub>8</sub> and MN<sub>8</sub>.

The operation of the full adder according to the invention will be described with reference to Figs. 2 and 6. In the three upper graphs of Fig. 6, the voltage levels  $V(X_1)$ ,  $V(X_2)$ , and  $V(X_3)$  are shown as functions of time. In the fourth graph, the voltage levels V(CN) and V(C) are shown, and in the lowest graph, the voltage levels V(SN), V(BP), and V(VS) are shown as a function of time, as a result of the changes in the voltage levels  $V(X_1)$ ,  $V(X_2)$ , and  $V(X_3)$ .

15

In this example, V<sub>DD</sub> is 0.6 V and V<sub>SS</sub> is 0 V, which means (in this case) that the transistors operate in the subthreshold area. Logic 0 is represented by a voltage level in the range of 0 - 0.25 V, and logic 1 is represented by a voltage level in the range of 0.3 - 0.6 V. The voltage level of the control terminal BN is 0 V, and the voltage level of the control terminal BP is 0.3 V, as shown in the lowest graph of Fig. 6.

The simulation results shown in Fig. 6 are represented below in the form of a table:

|    | Time  | In X <sub>1</sub> | In X <sub>2</sub> | In X <sub>3</sub> | SUM | CARRY | SUM' SN | CARRY' |

|----|-------|-------------------|-------------------|-------------------|-----|-------|---------|--------|

|    | [ms]  |                   |                   |                   | S   | С     |         | CN     |

| 25 | 0.010 | 0                 | 0                 | 0                 | 0   | 0     | 1       | 1      |

|    | 0.020 | 1                 | 0                 | 0                 | 1   | 0     | 0       | 1      |

|    | 0.030 | 1                 | 1                 | 0                 | 0   | 1     | 1       | 0      |

|    | 0.040 | 1                 | 1                 | 1                 | 1   | 1     | 0       | 0      |

30 Table 4: Full adder

In this circuit, all of the transistor pairs are alike. Hence, it does not matter which of the input signals are low or high. As is apparent from the table, when all of the input terminals are logic 0, the sum, represented by the output terminal S, and carry, represented by the output terminal C, is 0. If one input terminal is logic 1, then S is 1 and C is 0. If two input terminals are 1, then S is 0 and C is 1. If all the input terminals are 1, then both S and C are 1. With that, the full adder function is shown.

When configured for the full adder function, it is known by a person skilled in the art, that by fixing one of the inputs at 0 or 1, NAND2 and NOR2 can be achieved, and by short circuiting all of the inputs, INVERT can be achieved, with the first circuit element of example two. This signal would then be provided on the CARRY' terminal. At the same time the CARRY terminal would provide OR2, AND2 and BUFFER function, respectively.

From the examples above, it is illustrated that the circuit element according to the invention (shown in Fig. 1) has multiple fields of application, both when used solely and when a plurality are used together. It is known that transistors operating in the subthreshold area have very low power consumption per transistor. With the circuit element, a circuit with a range of application fields is achieved. The circuit element comprises very few transistors, which will contribute to a reduction in power consumption. Also achieved with the circuit element, is that very little wiring is required. This results in the circuit requiring less chip area, and the probability of production errors is also reduced. In addition, a reconfigurable circuit element is achieved, which means that the function of the circuit element can be reconfigured when desired, between different logic functions. This can result in a total reduction of chip area in a large, complex chip, which comprises such circuit elements.

In the examples, it is shown that the input terminals have two logic values, 0 or 1. It is naturally also possible to use this circuit with more discreet levels on the input terminals, as indicated by equation [1].

30 A person skilled in the art will be able to make variations to the present invention in multiple ways, within the scope of the claims.

25

#### **Claims**

- 1. Circuit element, comprising:

- N pairs of transistor units, each pair including a first (MP) and a second (MN) complementary transistor unit with at least four nodes, where the first transistor unit

- 5 includes

- a first node, which is connected to an upper (V<sub>DD</sub>) voltage level,

- a second node connected to the second node of a complementary transistor unit,

- an input node that controls the current through, and the voltage over the first and second node,

- 10 a control input node that controls the current/voltage characteristics of the transistor unit,

and the second transistor unit includes

- a first node, which is connected to a lower (V<sub>ss</sub>) voltage level,

- a second node connected to the second node of a complementary transistor unit,

- an input node that controls the current through, and the voltage over the first and second node,

- a control input node that controls the current/voltage characteristics of the transistor unit,

where the second nodes of the respective paired transistor units also are connected to

20 each other, and the upper and lower voltage levels (V<sub>DD</sub>, V<sub>SS</sub>) are such that the transistor

units operate in subthreshold,

- N input terminals (X<sub>1</sub>, X<sub>2</sub>, ... X<sub>N</sub>) connected to input nodes of the respective paired transistor units,

- an output terminal (CN) connected to the interconnected second nodes of the paired

- 25 transistor units, and

- at least one of the following:

- a control terminal (BP) connected to the control input nodes of the first transistor units, of the N paired transistors,

- a control terminal (BN) connected to the control input nodes of the second 30 transistor units, of the N paired transistors,

where N is an integer.

2. Circuit element according to claim 1, **characterized in** that the first transistor units are PMOS transistors, and the second transistors are NMOS transistors.

12

- 3. Circuit element according to claim 1 or 2, characterized in that the circuit element can

5 be reconfigured in real time, between a logic NAND-function, a logic NOR-function, and a CARRY'-function, by a change in the voltage level of at least one of the control terminals (BN, BP).

- 4. Circuit element according to claim 1, 2, or 3 characterized in that  $2 \le N \le 8$ , preferably  $10 \ 2 \le N \le 4$ .

- 5. Threshold element circuit with full adder function, **characterized in** that the circuit comprises two circuit elements according to claim 1, in which circuit elements N is 3, where the output terminal (CN) of the first circuit element is connected to the control

- 15 terminal (BP) for the PMOS well terminals of the second circuit element, and where the first output, in the form of the carry terminal (C), is connected to the second nodes of a pair of transistor units according to claim 1, where the input terminal of this transistor unit pair is connected to the output terminal (CN) of the first circuit element, and where the second output, in the form of the sum terminal (S), is connected to the second nodes of a pair of

- 20 transistor units according to claim 1, where the input terminal of this transistor unit pair is connected to the output terminal (SN) of the second circuit element.

Fig.1

Fig.2

Fig.3

Fig.6

#### INTERNATIONAL SEARCH REPORT

International application No.

#### PCT/NO 2004/000381

## A. CLASSIFICATION OF SUBJECT MATTER IPC7: H03K 19/23, H03K 19/0948 According to International Patent Classification (IPC) or to both national classification and IPC **B. FIELDS SEARCHED** Minimum documentation searched (classification system followed by classification symbols) IPC7: H03K Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched SE,DK,FI,NO classes as above Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) EPO-INTERNAL, WPI DATA, PAJ C. DOCUMENTS CONSIDERED TO BE RELEVANT Relevant to claim No. Category<sup>†</sup> Citation of document, with indication, where appropriate, of the relevant passages A US 4091293 A (ANDO, H), 23 May 1978 (23.05.1978), 1,2,4 the whole document A US 6177811 B1 (FUSE, T ET AL), 23 January 2001 1-4 (23.01.2001), the whole document 1-4 A HENDRAWAN SOELEMAN ET AL: "Robust subthreshold logic for ultra-low power operation". IEEE Transactions on Very Large Scale Integration (VLS) Systems, Vol 9. No 1, February 2001. Pages 90-99 xl Further documents are listed in the continuation of Box C. See patent family annex. Special categories of cited documents: "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention "A" document defining the general state of the art which is not considered to be of particular relevance earlier application or patent but published on or after the international "X" document of particular relevance: the claimed invention cannot be filing date considered novel or cannot be considered to involve an inventive document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other step when the document is taken alone "Y" document of particular relevance: the claimed invention cannot be special reason (as specified) considered to involve an inventive step when the document is combined with one or more other such documents, such combination "O" document referring to an oral disclosure, use, exhibition or other being obvious to a person skilled in the art document published prior to the international filing date but later than "&" document member of the same patent family the priority date claimed Date of the actual completion of the international search Date of mailing of the international search report 26 April 2005 0 4 -05- 2005 Name and mailing address of the ISA/ Authorized officer Swedish Patent Office Box 5055, S-102 42 STOCKHOLM Bo Gustavsson /LR Facsimile No. +46 8 666 02 86 Telephone No. +46 8 782 25 00

# INTERNATIONAL SEARCH REPORT

International application No.

PCT/NO 2004/000381

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                           | Relevant to claim No |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| A         | PATENT ABSTRACTS OF JAPAN Vol.009, no.091, 26 April 1984 (1984-04-26) & JP 59 011036 A (NIPPON DENKI KK), 20 January 1984 (1984-01-20) abstract              | 1,2,4                |  |

| Р,Х       | AUNET, SNORRE ET AL: "Reconfigurable subthreshold<br>CMOS perceptron". 2004 Int. Conf. on Neural<br>Networks, 25-29 July 2004. Pages 1983-1988<br>AN 8231229 | 1-5                  |  |

|           | , <b></b>                                                                                                                                                    |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           | ·                                                                                                                                                            |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              | <u> </u>             |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              | ·                    |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

|           |                                                                                                                                                              |                      |  |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

01/04/2005

International application No.

PCT/NO 2004/000381

| US | 4091293 | A  | 23/05/1978 | DE<br>JP<br>JP<br>JP<br>JP | 2659199 A<br>52070412 U<br>52083054 A<br>55045548 Y<br>52070835 U<br>52083055 A | 14/07/1977<br>25/05/1977<br>11/07/1977<br>25/10/1980<br>26/05/1977<br>11/07/1977 |

|----|---------|----|------------|----------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| US | 6177811 | B1 | 23/01/2001 | JP<br>JP<br>DE             | 19622646 A,B<br>3195203 B<br>9055652 A<br>9162408 A                             | 19/12/1996<br>06/08/2001<br>25/02/1997<br>20/06/1997                             |