US 20150365049A1

### (19) United States

## (12) Patent Application Publication OZAWA et al.

# (10) **Pub. No.: US 2015/0365049 A1** (43) **Pub. Date: Dec. 17, 2015**

# (54) SEMICONDUCTOR INTEGRATED CIRCUIT DEVICE AND MANUFACTURING METHOD OF ELECTRONIC DEVICE USING THE SAME

(71) Applicant: Renesas Electronics Corporation,

Kanagawa (JP)

(72) Inventors: Osamu OZAWA, Kanagawa (JP);

Soshiro NISHIOKA, Kanagawa (JP);

Takashi NAKAMURA, Kanagawa (JP);

Susumu ABE, Kanagawa (JP); Kazuya

TANIGUCHI, Kanagawa (JP); Masaaki

TANIMURA, Kanagawa (JP)

(21) Appl. No.: 14/738,066

(22) Filed: Jun. 12, 2015

(30) Foreign Application Priority Data

#### **Publication Classification**

(51) Int. Cl. *H03B 5/36* (2006.01) *H03K 3/03* (2006.01)

(52) U.S. Cl. CPC ...... *H03B 5/36* (2013.01); *H03K 3/0307* (2013.01)

#### (57) ABSTRACT

A semiconductor integrated circuit device having a function to perform oscillation in combination with a crystal oscillator, includes: a first impedance element including a first external terminal coupled to one terminal of the crystal oscillator, a second external terminal coupled to the other terminal of the crystal oscillator, and first and second terminals coupled to the first and second external terminals when the oscillation is performed; a first variable capacitance circuit coupled to the first terminal of the feedback impedance element, and a configuration circuit for setting a capacitance value of the first variable capacitance circuit. A measurement signal is supplied to the second terminal of the feedback impedance element, and in response to this, the capacitance value of the first variable capacitance circuit is set by the configuration circuit based on the delay time of an observation signal generated at the first terminal with respect to the measurement signal.

FIG. 2

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11 8.00 -MAX 7.00 6.00 -TYP DELAY TIME (us) 5.00 4.00 MIN 3.00 2.00 1.00 0.00 + 2 3 5 6 7 8 9 4 CAPACITANCE

FIG. 14

1600 5 1608 1603 1610 8 1602 1502 1501 엉 SE1 SEL Vck2 1202 R ... 1200 1201 107 弦 OSCILLATOR CIRCUIT T2 307

FIG. 18

FIG. 19A

FIG. 19B

|                      |     | $-\leftarrow$ |     |     |      |

|----------------------|-----|---------------|-----|-----|------|

| CAPACITANCE<br>VALUE | 0pF | 2pF           | 4pF | 6pF | 10pF |

| DELAY TIME           | 2us | 4us           | 6us | 8us | 10us |

|                      |     |               |     |     |      |

ADOPTED

FIG. 20A

FIG. 20B

| CAPACITANCE VALUE              | 0pF | 2pF\                        | 4pF | 6p <b>F</b> | 10pF |

|--------------------------------|-----|-----------------------------|-----|-------------|------|

| DELAY TIME (T2)                | 2us | 4us                         | 6us | 8us         | 10us |

| DELAY TIME<br>COMPARISON T1>T2 | 0   | $\setminus \circ \setminus$ | ×   | ×           | ×    |

|                                |     |                             |     |             |      |

**ADOPTED**

#### SEMICONDUCTOR INTEGRATED CIRCUIT DEVICE AND MANUFACTURING METHOD OF ELECTRONIC DEVICE USING THE SAME

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] The disclosure of Japanese Patent Application No. 2014-123581 filed on Jun. 16, 2014 including the specification, drawings and abstract is incorporated herein by reference in its entirety.

#### BACKGROUND

[0002] The present invention relates to a semiconductor integrated circuit device and a manufacturing method of an electronic device using the same. More particularly, the present invention relates to a semiconductor integrated circuit device having a function to perform oscillation in combination with a crystal oscillator, and to a manufacturing method of an electronic device including the crystal oscillator mounted in an electronic substrate (hereinafter, also referred to as a substrate) as well as the semiconductor integrated circuit device.

[0003] For example, techniques for performing oscillation using a crystal oscillator are described in Patent Documents 1 and 2 (Japanese Patent Application Laid-Open No. 2000-134036 and No. 2003-283249). Patent Document 1 describes a method for forming a variable capacitance element for frequency adjustment in a semiconductor integrated circuit device to adjust the oscillation frequency when performing oscillation by using a crystal oscillator. Further, Patent Document 2 describes a method for providing a crystal oscillator outside a semiconductor integrated circuit device, as well as a plurality of capacitances inside the semiconductor integrated circuit device to configure an oscillator circuit with the crystal oscillator and the capacitance elements.

#### **SUMMARY**

[0004] An electronic device includes a substrate, a crystal oscillator mounted in the substrate, one or a plurality of semiconductor integrated circuit devices and passive elements (resistive elements and/or capacitance elements) mounted in the substrate. The electronic device achieves a predetermined function by these components mounted in the substrate. In this case, clock signals and the like are formed in order to operate the electronic device by using the crystal oscillator and using the semiconductor integrated circuit device.

[0005] In order to oscillate a clock signal of a desired frequency by using the crystal oscillator, it is required that a capacitance element or the like having an appropriate capacitance value is coupled to the crystal oscillator and the semiconductor integrated circuit device through a wiring pattern over the substrate. When the capacitance element, and the like, is mounted in the substrate, the number of mounting parts increases and thus the cost will increase. Further, the area for mounting the capacitance element, and the like, is required in the substrate, leading to an increase in the size of the substrate. In addition, a terminal of the capacitance element, and the like, may be removed from the wiring pattern of the substrate. As a result, the reliability will be reduced.

[0006] Meanwhile, the substrate or the wiring pattern over the substrate has parasitic resistance and parasitic capacitance. Thus, in order to oscillate a clock signal of a desired frequency, it is required to set the value of the capacitance element and the like coupled to the crystal oscillator, by also taking into account the parasitic resistance and the parasitic capacitance. In order to allow the oscillation of the clock signal of desired frequency by taking into account the parasitic resistance and parasitic capacitance, for example, the manufacturer of an electronic device (hereinafter referred to as the electronic device manufacture) provides a substrate in which a wiring patter is formed to the manufacturer of a crystal oscillator (hereinafter referred to as the crystal oscillator manufacturer), and the appropriate capacitance value and the like is obtained in the crystal oscillator manufacturer. In this case, work occurs in the crystal oscillator manufacturer, resulting in a delay in the production of the electronic device. Further, when the electronic device manufacturer changes the substrate and/or the wiring pattern over the substrate, the parasitic resistance and the parasitic capacitance change as well. Thus, each time the substrate and/or the wiring pattern over the substrate is changed, it is required to also change the value of the capacitance, and the like, which is coupled to the crystal oscillator and to the semiconductor integrated circuit device. In other words, there is a concern that work may occur in the crystal oscillator manufacturer each time the substrate and/or the wiring pattern over the substrate is changed, resulting in further delay in the production of the electronic device.

[0007] As described in Patent Documents 1 and 2, for example, by placing a capacitance element inside of the semi-conductor integrated circuit device, it is possible to reduce the number of capacitance elements mounted in the substrate. As a result, it is possible to reduce the increase in the cost and the increase in the mounting area. Further, it is possible to reduce the number of connections between the wiring pattern over the substrate and the terminals of the capacitance element and the like, which can also prevent the reduction of the reliability.

[0008] Further, there may be a case in which a variable capacitance circuit is used as the capacitance element placed inside the semiconductor integrated circuit device, and the capacitance value of the variable capacitance circuit is set from the outside of the semiconductor integrated circuit device. In this way, it is possible to oscillate a clock signal of a desired frequency by changing the capacitance value from outside the semiconductor integrated circuit. However, also in such a case, the crystal oscillator manufacturer should obtain the appropriate capacitance value and the like. In this case, it is necessary for the crystal oscillator manufacturer to obtain the appropriate capacitance value by changing the capacitance value of the variable capacitance circuit from outside the semiconductor integrated circuit device. From the point of view of the crystal oscillator manufacturer, it is necessary to work with an unfamiliar semiconductor integrated circuit device, so that the work of obtaining the appropriate capacitance value may be a considerable burden. As a result, the time required for the work in the crystal oscillator manufacturer may increase and the production of the electronic device may further be delayed.

**[0009]** Both Patent Documents 1 and 2 are not aware of the work imposed on the crystal oscillator manufacturer, namely, the work of obtaining the capacitance value and the like in order to obtain a desired frequency. Further, they are not also aware of the delay that occurs due to the process through the crystal oscillator manufacturer.

[0010] These and other objects and advantages will become apparent from the following description of the present specification and the accompanying drawings.

[0011] A typical one of the aspects of the invention disclosed in this application will be briefly described as follows. [0012] That is, there is provided a semiconductor integrated circuit device having a function to perform oscillation in combination with a crystal oscillator. The semiconductor integrated circuit device includes a first external terminal to which one terminal of the crystal oscillator is coupled, and a second external terminal to which the other terminal of the crystal oscillator is coupled. Here, the semiconductor integrated circuit device includes: a feedback impedance element having a first terminal coupled to the first external terminal, and a second terminal coupled to the second external terminal when the oscillation is performed; a first variable capacitance circuit coupled to the first terminal of the feedback impedance element; and a configuration circuit for setting a capacitance value of the first variable capacitance circuit. The semiconductor integrated circuit device supplies a first measurement signal to the second terminal of the feedback impedance element. In response to the supply of the first measurement signal, the capacitance value of the first variable capacitance circuit is set by the configuration circuit, based on the delay time for the first measurement signal which is a first observation signal generated at the first terminal of the feedback impedance element.

[0013] A delay circuit can be considered being configured by the feedback impedance element, the first variable capacitance circuit, and a parasitic capacitance associated with the first external terminal. When the first measurement signal is supplied as the input signal of the delay circuit, a signal having a delay time is generated as the first observation signal. Here, the delay time is determined by the impedance value of the feedback impedance element configuring the delay circuit, and by the capacitance value of the capacitance circuit (including the first variable capacitance circuit and the parasitic capacitance associated with the first external terminal). In this case, the delay time varies according to the value of the first variable capacitance circuit coupled to the feedback impedance element and according to the value of the parasitic capacitance associated with the first external terminal, so that the delay time can be considered changing depending on the value of the parasitic capacitance. Thus, the capacitance value of the first variable capacitance circuit can be set taking into account the value of the parasitic capacitance associated with the first external terminal, by setting the capacitance value of the first variable capacitance circuit based on the delay time.

[0014] For example, the delay time when the clock signal of desired frequency is oscillated is obtained and presented in advance. Then, in the electronic device manufacturer, the capacitance value of the first variable capacitance circuit is sets by the configuration circuit so as to match the presented delay time. This allows the electronic device manufacturer to set the appropriate capacitance value to the semiconductor integrated circuit device by itself. In other words, there is no need to provide the substrate to the crystal oscillator manufacturer to obtain the appropriate capacitance value in the crystal oscillator manufacturer. As a result, it is possible to reduce the delay in the production.

[0015] In an embodiment from the point of view of the semiconductor integrated circuit device, the feedback impedance element is a feedback resistive element. A measurement

circuit is placed in the semiconductor integrated circuit device to measure the time difference between the change in a first signal at the first terminal of the feedback resistive element, and the change in a second signal at the second terminal of the feedback resistive element. Here, the time difference corresponds to the delay time. It is possible to obtain the delay time by measuring the first signal at the first terminal and the second signal at the second terminal, and to facilitate the measurement.

[0016] Further, in an embodiment from the point of view of a manufacturing method of an electronic device, there is provided a manufacturing method of an electronic device including a crystal oscillator combined with a wiring pattern formed in a substrate, and a semiconductor integrated circuit device having a first external terminal and a second external terminal that are combined with the wiring pattern. Here, the semiconductor integrated circuit device includes: a feedback impedance element having a first terminal coupled to the first external terminal as well as a second terminal coupled to the second external terminal when oscillation is performed by use of the crystal oscillator; a first variable capacitance circuit coupled to the first terminal of the feedback impedance element; and a configuration circuit for setting a capacitance value of the first variable capacitance circuit. The semiconductor integrated circuit device supplies a first measurement signal to the second terminal of the feedback impedance element. Then, in response to the supply of the first measurement signal, the capacitance value of the first variable capacitance circuit is set by the configuration circuit so that the delay time of the signal generated at the first terminal of the feedback impedance element becomes a predetermined value.

[0017] The first external terminal is coupled to the wiring pattern formed in the substrate. Thus, a parasitic capacitance is associated with the first external terminal. The capacitance value of the first variable capacitance circuit is determined so as to be able to oscillate a clock signal of a desired frequency when the parasitic capacitance is associated with the first external terminal. Then, the delay time at this time is provided as a predetermined value. In the manufacturing method of the electronic device, the capacitance value of the first variable capacitance is set by the configuration circuit so as to match the predetermined value provided as described above. In this way, it is possible to produce the electronic device capable of oscillating the clock signal of desired frequency.

[0018] According to an embodiment of the present invention, it is possible to provide a semiconductor integrated circuit device that can easily oscillate a clock signal of a desired frequency.

#### BRIEF DESCRIPTION OF THE DRAWINGS

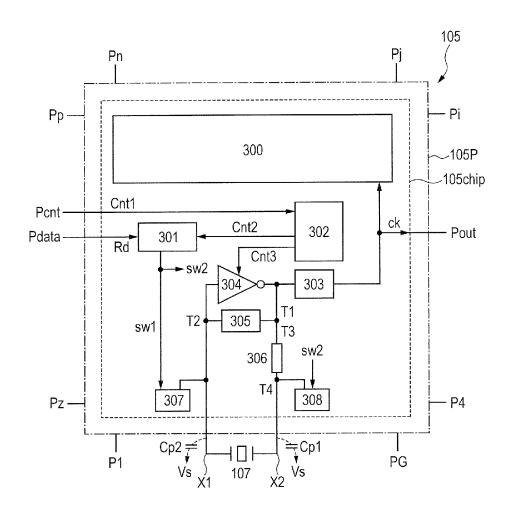

[0019] FIG. 1 is a block diagram showing the configuration of an electronic device;

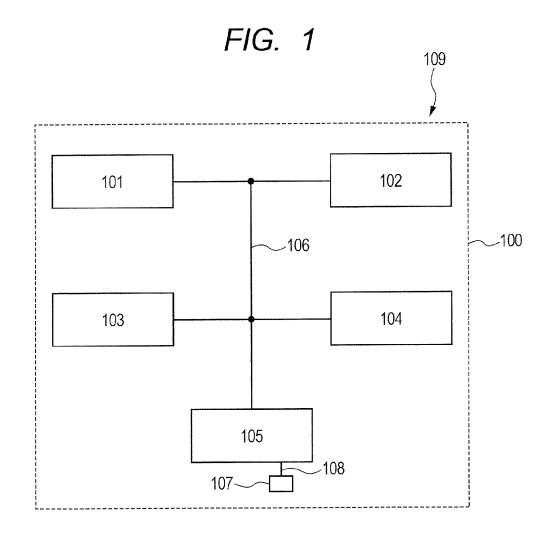

[0020] FIG. 2 is a plan view showing an arrangement on a substrate according to a first embodiment;

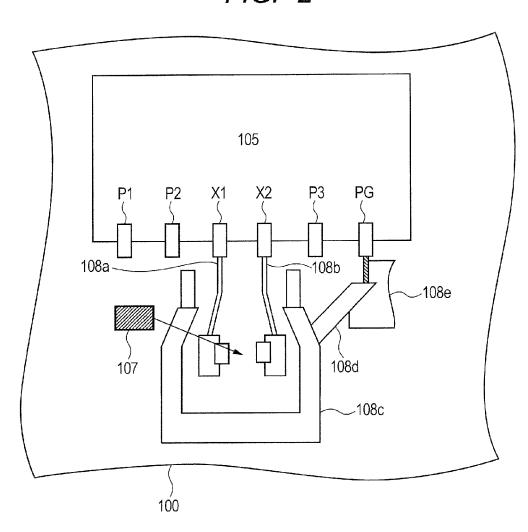

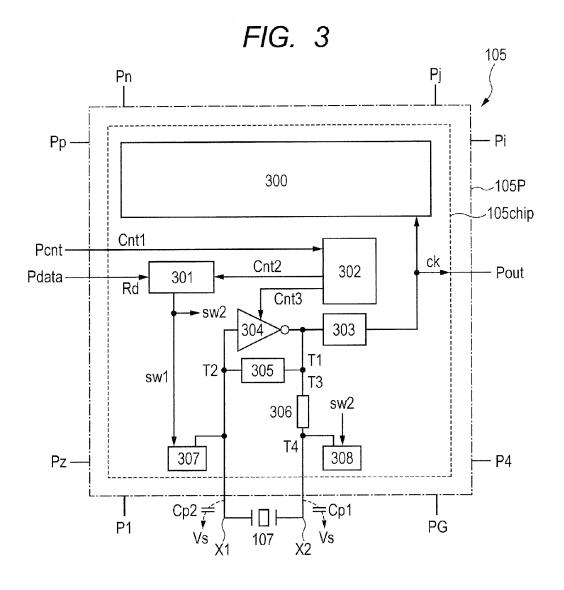

[0021] FIG. 3 is a block diagram showing the configuration of a semiconductor integrated circuit device according to the first embodiment;

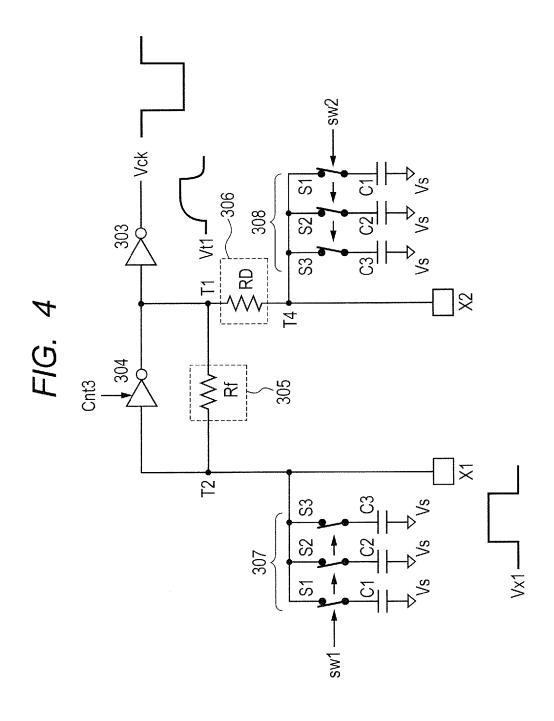

[0022] FIG. 4 is a circuit diagram showing the principle according to the first embodiment;

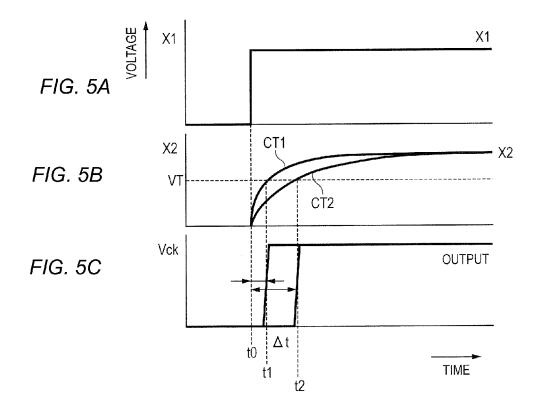

[0023] FIGS. 5A to 5C are voltage waveform diagrams showing the principle according to the first embodiment;

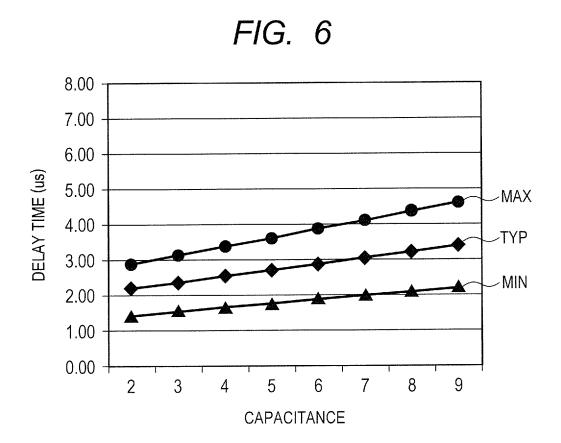

[0024] FIG. 6 is a characteristic diagram showing the relationship between delay time and capacitance value according to the first embodiment;

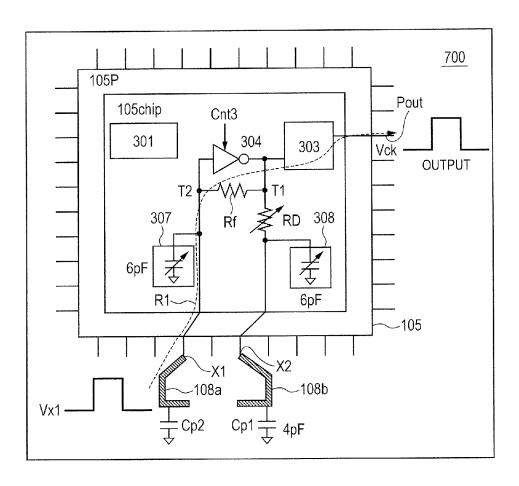

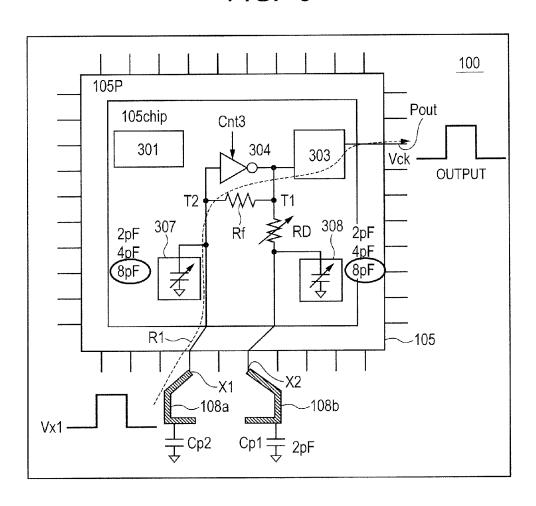

[0025] FIG. 7 is a block diagram showing the measurement of the delay time according to the first embodiment;

[0026] FIG. 8 is a block diagram showing the setting of the capacitance value according to the first embodiment;

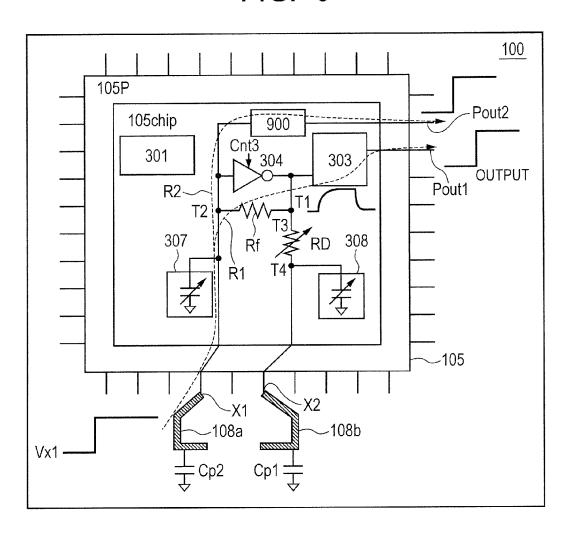

[0027] FIG. 9 is a block diagram showing the configuration of a board according to a second embodiment;

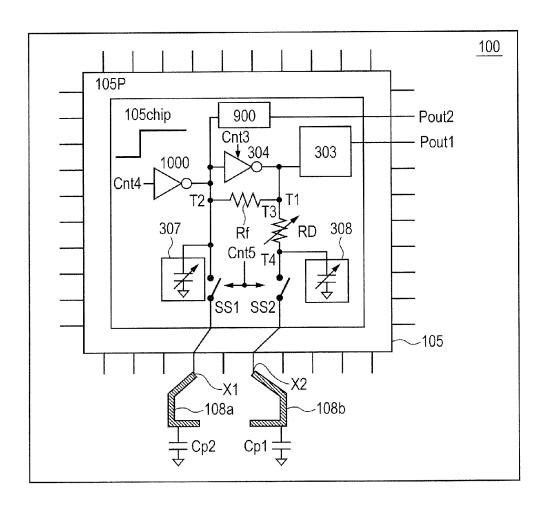

[0028] FIG. 10 is a block diagram showing the configuration of a board according to a variation of the second embodiment:

[0029] FIG. 11 is a characteristic diagram showing the relationship between delay time and capacitance value according to a third embodiment;

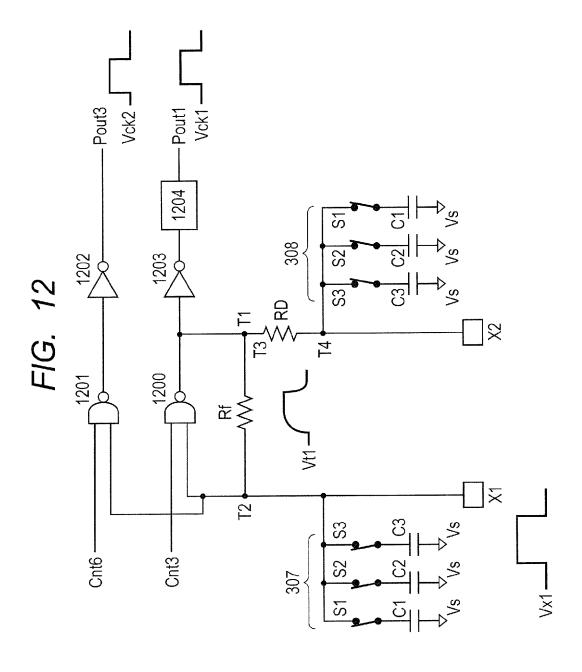

[0030] FIG. 12 is a circuit diagram showing the configuration of the main part of a semiconductor integrated circuit device according to the third embodiment;

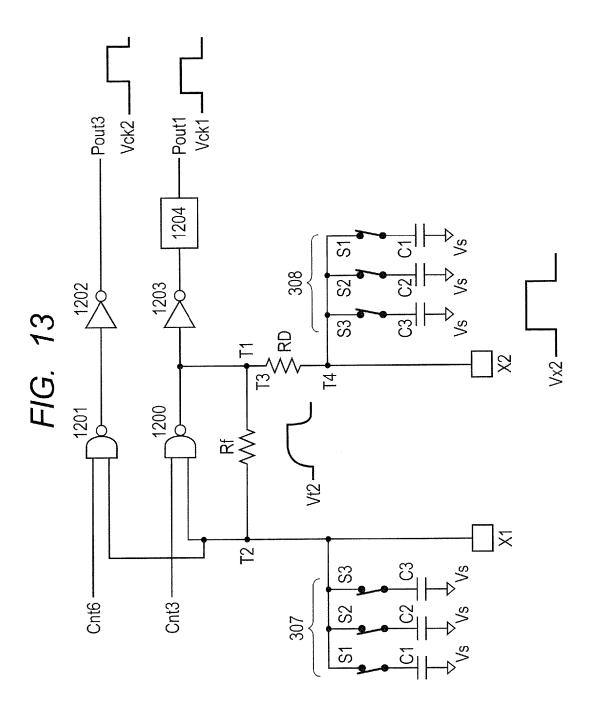

[0031] FIG. 13 is a circuit diagram showing the configuration of the main part of the semiconductor integrated circuit device according to the third embodiment;

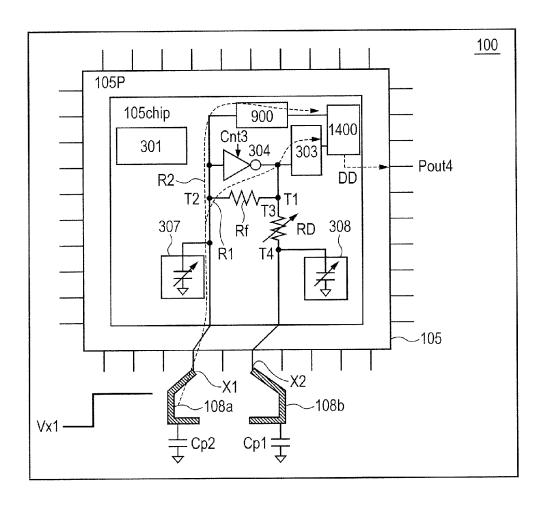

[0032] FIG. 14 is a block diagram showing the configuration of a board according to a fourth embodiment;

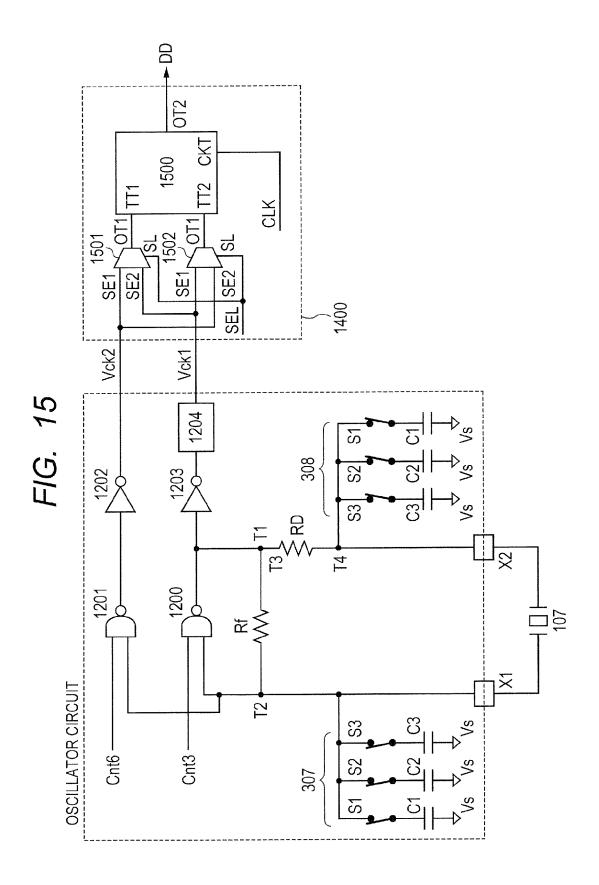

[0033] FIG. 15 is a block diagram showing the configuration of a measurement circuit according to the fourth embodiment;

[0034] FIG. 16 is a block diagram of another configuration of the measurement circuit according to the fourth embodiment:

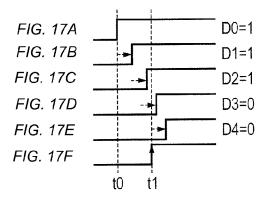

[0035] FIGS. 17A to 17F are timing diagrams showing the operation of the measurement circuit according to the fourth embodiment;

[0036] FIG. 18 is a block diagram showing the configuration of a board according to a variation of the fourth embodiment;

[0037] FIG. 19A is a block diagram showing the configuration of a board according to a fifth embodiment;

[0038] FIG. 19B is a table diagram showing the configuration of the board according to the fifth embodiment;

[0039] FIG. 20A is a block diagram according to a variation of the fifth embodiment; and

[0040] FIG.  $20\mathrm{B}$  is a table diagram according to the fifth embodiment.

#### DETAILED DESCRIPTION

[0041] Hereinafter, preferred embodiments of the present invention will be described in detail with reference to the accompanying drawings. Note that in all the drawings for explaining the embodiments, the same reference numerals are given in principle to the same components, and the repetitive description thereof will be omitted.

#### First Embodiment

[0042] <Electronic Device>

[0043] First, the configuration of an electronic device according to a first embodiment will be described. In some embodiments described below, it is assumed that the electronic device has the configuration shown in FIG. 1 as an example. In FIG. 1, reference numeral 109 denotes an electronic device. The electronic device 109 includes a wiring pattern formed in a substrate 100 (the area surrounded by a dashed line), a plurality of semiconductor integrated circuit devices 101 to 105 mounted in the substrate 100, a crystal oscillator 107 mounted in the substrate 100, a plurality of passive elements (not shown) mounted in the substrate 100, and the like. In FIG. 1, reference numerals 106 and 108 show

examples of wiring patterns formed in the substrate 100. The wiring pattern 106 shown in FIG. 1 is an example of the wiring pattern for electrically coupling the semiconductor integrated circuit devices 101 to 105 to each other. The wiring pattern 108 shows an example of the wiring pattern for electrically coupling the semiconductor integrated circuit device 105 and the crystal oscillator 107 to each other.

[0044] Of course, the semiconductor integrated circuit devices 101 to 105, the crystal oscillator 107, and the wiring patterns 106 and 108, which are shown in FIG. 1, are an example. The number of pieces and/or the arrangement, and the like, of the respective components are not limited to this example. Further, in FIG. 1, the electrical coupling of the external terminals of the semiconductor integrated circuit devices 101 to 105 to the respective wiring patterns 106 and 108, as well as the electrical coupling of the terminal of the crystal oscillator 107 to the wiring pattern 108 are simplified. However, the external terminals of the respective semiconductor integrated circuit devices 101 to 105 as well as the external terminal of the crystal oscillator 107 are electrically coupled to the wiring patterns 106 and 108, respectively, for example, by means of solder.

[0045] The semiconductor integrated circuit device 105 is combined with the crystal oscillator 107 through the wiring pattern 108. The semiconductor integrated circuit device 105 has a function to oscillate a clock signal of a predetermined (desired) frequency by use of the crystal oscillator 107. The oscillated clock signal of predetermined frequency is used to operate a circuit block placed inside the semiconductor integrated circuit device 105. Further, the oscillated clock signal can also be supplied to the other semiconductor integrated circuit devices 101 to 104, to be used to operate these semiconductor integrated circuit devices.

[0046] FIG. 2 is a plan view mainly showing the area in which the semiconductor integrated circuit device 105 is located in the substrate 100 shown in FIG. 1. The semiconductor integrated circuit device 105 has a plurality of external terminals. In FIG. 2, external terminals P1 to P3, PG, X1, and X2 are shown as an example. Although the details will be described later, the external terminals X2 (first external terminal) and X1 (second external terminal) are coupled with the external terminals (terminals) of the crystal oscillator 107, respectively. Further, the external terminal PG is supplied with a ground voltage of the circuit to the semiconductor integrated circuit device 105.

[0047] A plurality of lines 108a to 108e, each having a unique pattern shape, are formed in the substrate 100. The lines 108a to 108e are shown as the wiring pattern 108 in FIG.

1. The external terminal X2 of the semiconductor integrated circuit device 105 is electrically coupled to the line 108b, and the external terminal X1 is electrically coupled to the line 108a. Each of the lines 108a and 108b forms a pattern with a flat and wide area (on the lower side in the figure). Each of the external terminals of the crystal oscillator 107 is electrically coupled to the wide area.

[0048] FIG. 2 shows the state before the crystal oscillator 107 is coupled to the lines 108a and 108b. The crystal oscillator 107 is coupled to the lines 108a and 108b in such a way that, in FIG. 2, the crystal oscillator 107 is moved in the direction shown by the arrow, and the area in which the external terminals of the crystal oscillator 107 and the lines 108a, 108b overlap is fixed by solder. In this way, the external terminals of the crystal oscillator 107 are electrically coupled to the lines 108a and 108b, respectively. The line 108c is

formed over the substrate 100 so as to surround the area in which the crystal oscillator 107 is fixed. The line 108c is formed over the substrate 100 so as to surround the periphery of the area in which the crystal oscillator 107 is fixed. The line 108c is coupled to the line 108e of the ground voltage Vs, together with the external terminal PG of the semiconductor integrated circuit device 105, through the line 108d. In this way, the ground voltage Vs propagates along the line 108e and is supplied to the external terminal PG of the semiconductor integrated circuit device 105. At the same time, the ground voltage Vs is also supplied to the line 108c surrounding the crystal oscillator 107. By converting the line 108c surrounding the crystal oscillator 107 into the ground voltage Vs, it is possible to prevent the noise or other disturbance caused by the operation of the crystal oscillator 107 from propagating to other parts.

[0049] Note that the lines 108a to 108e are formed in one main surface of the substrate 100. In the back surface (the surface facing the one main surface) of the substrate 100 corresponding to the area in which the crystal oscillator 107 is located, a metal wiring is formed, but the present invention is not particularly limited to this. The meal wiring formed in the back surface reduces the emission of the noise the crystal oscillator 107 generates from the back surface side of the substrate 100. Note that in the following description, the substrate in which the wiring pattern is formed may also be referred to as the board.

<Configuration of the Semiconductor Integrated Circuit Device 105>

[0050] Next, a description will be given of the configuration of the semiconductor integrated circuit device 105 having a function of oscillating a clock signal of a predetermined frequency by use of the crystal oscillator 107. FIG. 3 is a block diagram showing the configuration of the semiconductor integrated circuit device 105 according to the embodiment. In FIG. 3, an area 105P surrounded by a dot-dashed line represents the package of the semiconductor integrated circuit device 105. Further, an area 105 chip surrounded by a dashed line represents a semiconductor chip produced by the wellknown semiconductor production techniques. In other words, the semiconductor integrated circuit device 105 is configured in such a way that a plurality of circuit blocks are formed in one semiconductor chip 105 chip by the well-known semiconductor production techniques, and are sealed by the package 105P. As described above, the semiconductor integrated circuit device 105 is provided with a plurality of external terminals (lead terminals, ball terminals). In FIG. 3, these external terminals are shown projecting from the package 105P. Further, in FIG. 3, P1 to Pz, X2, X1, PG, Pout, Pcnt, and Pdata are shown as an example of the external terminals. In FIG. 3, only the external terminals X2, X1, Pout, Pcnt, and Pdata related to the description are shown as being coupled to the semiconductor chip 105 chip. However, the remaining external terminals are also coupled to the semiconductor chip 105 chip.

[0051] The semiconductor integrated circuit device 105 has not only the function of oscillating a clock signal of a predetermined frequency by use of the crystal oscillator 107, but also a specific function to achieve a function required for the electronic device. The semiconductor integrated circuit device 105 shown in FIG. 3 includes circuit blocks, which are roughly classified into two blocks: a circuit block for achieving the specific function, and a circuit block for configuring

an oscillator circuit by use of the crystal oscillator 107. In FIG. 3, the circuit block for achieving the specific function is designated by reference numeral 300. Then, the circuit block for configuring the oscillator circuit is designated by reference numerals 301 to 308. In this embodiment, a clock signal ck of predetermined frequency formed by the oscillator circuit is supplied to the circuit block 300 and to the external terminal Pout. Although not particularly limited, the circuit block 300 operates according to the clock signal ck to perform a predetermined function. The clock signal ck supplied to the external terminal Pout is, for example, supplied to the other semiconductor integrated circuit devices 101 to 104 and is used in the other semiconductor integrated circuit devices.

[0052] Next, a description will be given of the circuit blocks 301 to 308 that operate as the oscillator circuit by use of the crystal oscillator 107.

[0053] In FIG. 3, reference numeral 304 denotes an inverter circuit (active circuit) whose operation is controlled by an activation signal Cnt3. When viewed as the oscillator circuit, the inverter circuit 304 functions as a negative resistance amplifier to keep the oscillation going. Reference numerals 305 and 306 respectively denote impedance elements. When viewed as the oscillator circuit, 305 functions as a feedback impedance element and 306 functions as an amplitude control impedance element. The feedback impedance element 305 has a pair of terminals T1 (first terminal) and T2 (second terminal). Also the amplitude control impedance element 306 has a pair of terminals T3 (third terminal) and T4 (fourth terminal). The inverter circuit 304 is coupled in parallel to the feedback impedance element 305. In other words, the input of the inverter circuit 304 is coupled to the terminal T2 of the feedback impedance element 305, and the output of the inverter circuit 304 is coupled to the terminal T1 of the feedback impedance element 305. Further, the terminal T3 of the amplitude control impedance element 306 is coupled to the terminal T1 of the feedback impedance element 305. Then, the terminal T4 is coupled to the external terminal X2 (first external terminal).

[0054] The terminal T2 (second terminal) of the feedback impedance element 305 is coupled to the external terminal X1 (first terminal). Further, the terminal T1 (first terminal) of the feedback impedance element 305 can also be seen as being coupled to the external terminal X2 (first external terminal) through the amplitude control impedance element 306. In FIG. 3, reference numerals 307 and 308 denote variable capacitance circuits, respectively. When viewed as the oscillator circuit, the variable capacitance circuits function as load capacitances. The variable capacitance circuit 307 (second variable capacitance circuit) is coupled between the terminal T2 of the feedback impedance element 305 and the ground voltage, in which the capacitance value between the terminal T2 and the ground voltage changes according to the capacitance control signal sw1. Further, the variable capacitance circuit 308 (first variable capacitance circuit) is coupled between the terminal T4 of the amplitude control impedance element 306 and the ground voltage, in which the capacitance value between the terminal T4 and the ground voltage changes according to the capacitance value control signal sw2.

[0055] The clock signal output from the inverter circuit 304 is supplied to a buffer circuit 303. The buffer circuit 303 has a predetermined threshold voltage, and compares the voltage of the clock signal output from the inverter circuit 304 with the predetermined threshold voltage as a reference voltage.

Then, the buffer circuit 303 shapes the clock signal from the inverter circuit 304, and outputs the shaped clock signal as the clock signal ck. In this way, the shaped clock signal ck is supplied to the circuit block 300 and to the external terminal Pout. In FIG. 3, reference numeral 301 denotes a register (configuration circuit). The register 301 receives a capacitance data Rd from the external terminal Pdata, generates the capacitance value control signals sw1 and sw2 corresponding to the capacitance data Rd, and supplies to the variable capacitance circuits 307 and 308. In this way, the capacitance values of the variable capacitance circuits 307 and 308 are converted to the values according to the capacitance data Rd. [0056] In FIG. 3, reference numeral 302 denotes a control circuit. The control circuit 302 receives a capacitance control signal Cnt1 from the external terminal Pcnt. Then, the control circuit 302 generates the activation signal Cnt3 and register control signal Cnt2, and supplied to the inverter circuit 304 and the register 301. The control circuit 302 receives the capacitance control signal the Cnt1 and puts the inverter circuit 304 into an inactive state. In this way, the inverter circuit 304 will not output a signal inverted from the signal supplied to its input. In other words, at this time, the signal supplied to the external terminal X1 or the terminal T2 of the feedback impedance element 305 is transmitted to the terminal T1 of the feedback impedance element 305 only through the feedback impedance element 305. In this way, it is possible to obtain an observation signal according to the value of the capacitance coupled to the terminal T1 of the feedback impedance element 305, including the parasitic capacitance associated with the external terminal X2, which will be described in detail below.

[0057] Further, when receiving the capacitance control signal Cnt1, the control circuit 302 supplies the register control signal Cnt2 to the register 301. When receiving the register control signal Cnt2, the register 301 generates the capacitance value control signals sw1, sw2 according to the capacitance data Rd and supplies to the variable capacitance circuits 307, 308 as described above.

[0058] The crystal oscillator 107 has a pair of terminals (external terminals). One of the pair of terminals is coupled to the external terminal X2 of the semiconductor integrated circuit device 105, and the other terminal is coupled to the external terminal X1. When the capacitance control single Cnt1 is not supplied to the control circuit 302 through the external terminal Pcnt, namely, in the case of normal operation, the control circuit 302 generates the activation signal Cnt3 so that the inverter circuit 304 is put into an active state. In this way, the inverter circuit 304 inverts and outputs the signal supplied to the input of the inverter circuit 304. In this way, the clock signal corresponding to the resonance frequency of the crystal oscillator 107 is generated by the oscillator circuit that is configured by the inverter circuit 304, the negative feedback impedance element 305, the variable capacitance circuits 307 and 308, the amplitude control impedance element 306, and the crystal oscillator 107. In other words, the clock signal corresponding to the resonance frequency of the crystal oscillator 107 is oscillated.

<Capacitance Value Measurement by the Delay Time>

[0059] There is a parasitic capacitance in the substrate 100 and/or the wiring pattern 108. In FIG. 3, parasitic capacitances Cp1, Cp2 associated with the external terminals X2, X1 are schematically shown by the dashed line. Each of the parasitic capacitances Cp1 and Cp2 includes the parasitic

capacitance of the wiring pattern coupled to the external terminals X2 and X1, respectively. The frequency of the clock signal ck generated by the oscillator circuit described above varies depending on the values of the parasitic capacitances Cp1 and Cp2. Further, as described above, the capacitance value of the parasitic capacitances Cp1 and Cp2 changes when the substrate 100 and/or the wiring pattern 108 is changed. The capacitance value of the Cp1 and Cp2, which is for example 4 pF, is changed to 2 pF when the wiring pattern is changed. In order to generate the clock signal ck of desired frequency in response to the change in the capacitance value of the parasitic capacitance, it is necessary to change the capacitance value of the variable capacitance circuits 308 and 307, for example, from 6 pF to 8 pF. In other words, in this example, the parasitic capacitance is reduced due to the change in the board, so that the capacitance value of the variable capacitance circuits 308 and 307 is increased to compensate so that the value of the capacitance including the parasitic capacitance is the same before and after the change in the board.

[0060] In the first embodiment, it is possible to generate a clock signal of a desired frequency by indicating (measuring) the value of the capacitance including the parasitic capacitance by the delay time, and by adjusting the capacitance value of the variable capacitance circuits 308 and 307 so that the delay time becomes a predetermined (desired) value. Here, a description will be given of the principle of indicating and measuring the capacitance value by the delay time.

[0061] FIG. 4 is a circuit diagram showing the principle of indicating the capacitance value by the delay time. First, the correspondence between FIG. 4 and FIG. 3 will be described. FIG. 4 is a circuit diagram showing an example of the inverter circuit 304, the feedback impedance element 305, the amplitude control impedance element 306, the variable capacitance circuits 307 and 308, and the buffer circuit 303, which are shown in FIG. 3. Of course, the same parts are designated by the same reference numerals in FIGS. 3 and 4.

[0062] In FIG. 4, the feedback impedance element 305 is formed by a feedback resistive element Rf, and the amplitude control impedance element 306 is formed by an amplitude control resistive element RD. Further, in this example, the variable capacitance circuits 307 and 308 are formed by capacitance elements C1 to C3 and switches S1 to S3, respectively. In other words, the variable capacitance circuit 308 has three series circuits coupled in parallel to each other between the terminal T4 of the amplitude control resistive element RD and the ground voltage Vs. Each of the series circuits has the same configuration, but the present invention is not particularly limited to this. When citing the series circuit shown in the rightmost side of the figure, the switch S1 and the capacitance element C1, which are switched and controlled by the capacitance value control signal sw2, are coupled in series between the terminal T4 and the ground voltage Vs. In the remaining two series circuits, the switches S2 and S3 are coupled in series to the capacitance elements C2 and C3, respectively. Although not particularly limited, the capacitance values of the capacitance elements 1 to C3 are different from each other in this example. Also the variable capacitance circuit 307 has the same configuration as the variable capacitance circuit 308. However, the switches S1 to S3 in the variable capacitance circuit 307 are switched and controlled by the capacitance value control signal sw1.

[0063] Each of the capacitance value control signals sw1 and sw2 is shown as one signal but includes a plurality of

capacitance value control signals. Thus, these capacitance control signals are collectively referred to as the capacitance control signals sw1 and sw2. In each variable capacitance circuit 308 (307), the switches S1 to S3 are switched and controlled separately by different capacitance control signals. In this way, the three capacitance elements C1 to C3 in the variable capacitance circuit 308 (307) are selected, and the selected capacitance elements are electrically coupled between the terminal T4 (T2) and the ground voltage Vs. For example, it is assumed that the capacitance values of the capacitance elements C1, C2, C3 are 2 pF, 4 pF, 8 pF, respectively. In this case, the capacitance value of the variable capacitance circuit 308 (307) can be changed between 0 pF to 14 pF, by selecting from the switches S1 to S3 on a timely basis according to the capacitance value control signal. In other words, it is possible to change the capacitance value of the variable capacitance circuit 308 (307) coupled between the terminal T4 (T2) and the ground voltage Vs, between 0 pF to 14 pF according to the capacitance value control signal sw2 (sw1).

[0064] The resistance value R of the feedback resistive element Rf is set to, for example, 200 K ohms. The resistance value of the amplitude control resistive element RD is set to, for example, 2 K ohms because the amplitude of the clock signal is much more limited than expected when the resistance value is set to a too high value. In general, the resistance value of the amplitude control resistive element RD configuring the oscillator circuit is set to about one hundredth of the resistance value R of the feedback resistive element Rf.

[0065] FIG. 4 shows the waveforms of three voltages Vx1, Vt1, and Vck, together with a circuit diagram. In each of the waveformes of the three voltages Vx1, Vt1, and Vck, the horizontal axis represents the time and the vertical axis represents the voltage. The waveform of the voltage Vx1 is the voltage waveform of the measurement signal (first measurement signal) supplied to the external terminal X1. Further, the waveform of the voltage Vt1 shows the voltage change at the terminal T1 of the feedback resistive element Rf. Then, the waveform of the voltage Vck shows the voltage waveform of the clock signal ck.

[0066] When the measurement signal whose voltage value changes into a rectangular shape along with the time, as shown in the voltage waveform Vx1, is supplied to the external terminal X1, the voltage waveform occurring in the external terminal X2 is expressed by the equation (1). Here, Vx2 represents the voltage occurring in the external terminal X2, V0 represents the voltage of the voltage waveform Vx1, and T represents the time constant (RC) given by the resistance value R of the feedback resistive element Rf as well as the capacitance value C of the variable capacitance circuit 308. [0067] In this embodiment, upon measurement of the

[0067] In this embodiment, upon measurement of the capacitance value of the capacitance element the oscillator circuit has, including the parasitic capacitance associated with the external terminals X1, X2 to which the crystal oscillator is coupled, the inverter circuit 304 is put into an inactive state according to the activation signal Cnt3. Thus, the inverter circuit 304 does not invert the voltage at the terminal T2 and does not transmit to the terminal T1. For this reason, the resistance component at the time constant T in the equation (1) is determined by the feedback resistive element Rf and the amplitude control resistive element RD. Further, the resistance value of the amplitude control resistive element RD is about one hundredth of the resistance value R of the feedback resistive element Rf as described above, so that the

resistance value of the amplitude control resistive element RD can be ignored. Thus, the resistance component at the time constant T of the equation (1) is the resistance value R of the feedback resistive element Rf.

$$V \times 2 = V0 \left( 1 - e^{-\frac{t}{T}} \right)$$

Equation 1

[0068] Further, since the resistance value of the amplitude control resistive element RD can be ignored, the change in the voltage at the terminal T1 of the feedback resistive element Rf is the same as the change in the voltage at the external terminal X2. Thus, the voltage waveform Vt1 at the terminal T1 shown in FIG. 4 can also be regarded as the voltage waveform at the external terminal X2. In other words, it is possible to regard the voltage Vx2 shown in the equation (1) as the voltage Vt1 of the terminal T1.

[0069] The voltage waveform Vck of the clock signal ck varies depending on whether or not the voltage Vt1 (=Vx2) at the terminal T1 exceeds the threshold voltage VT (logic threshold voltage) of the buffer circuit 303. A delay time t from when the rectangular wave (measurement signal) supplied to the external terminal X1 reaches the voltage V0 to when the voltage of the clock signal ck, which is the output of the buffer circuit 303, is inverted is expressed by the equation (2). As can be understood from the equation (2), the delay time t is linear to the time constant (T:RC).

$$t = -RC \times \ln\left(1 - \frac{VT}{V0}\right)$$

Equation 2

[0070] FIGS. 5A to 5C are voltage waveform diagrams showing the principle of measuring the capacitance value by the delay time. FIG. 5A shows the voltage waveform of the measurement signal (first measurement voltage) supplied to the external terminal X1 in FIG. 4. FIG. 5B shows the voltage change at the external terminal X2. As described above, the voltage at the external terminal X2 is practically the same as the voltage at the terminal T1. Thus, it can also be seen that FIG. 5B shows the voltage waveform at the terminal T1. Further, FIG. 5C shows the voltage waveform of a clock signal Vck which is the output of the buffer circuit 303.

[0071] In FIG. 5A, the measurement signal (X1 in the figure) supplied to the external terminal X1 changes from the ground voltage to the voltage V0 at time to. In response to the change in the measurement signal (X1), the voltage at the external terminal X2 (=terminal T1) increases according to the time constant (RC) determined by the resistance value of the feedback resistive element Rf, and by the capacitance value of the variable capacitance circuit 308 as well as the capacitance value of the parasitic capacitance Cp1. FIG. 5B shows the case in which the capacitance value of the variable capacitance circuit 308 is set to CT1 and to CT2, respectively. For example, the capacitance value of the variable capacitance circuit 308 is 2 pF for the capacitance value CT1, and capacitance value is 4 pF for the capacitance value CT2. In FIG. 5B, the threshold voltage VT of the buffer circuit 303 is also shown by the dashed line. When the voltage (X2) at the external terminal X2 (terminal T1) exceeds the threshold voltage VT, the voltage of the clock signal ck, which is the output of the buffer circuit 303, changes as shown in FIG. 5C. In this example, the clock signal ck is the observation signal (first observation signal).

[0072] In other words, when the capacitance value of the variable capacitance circuit 308 is set to CT1, the voltage Vck of the clock signal ck rises to a high level at time t1. On the other hand, when the capacitance value of the variable capacitance circuit 308 is set to CT2, the voltage Vck of the clock signal ck rises to a high level at time t2. In other words, the voltage of the clock signal ck changes after the delay time (t1 or t2) that is determined by the combined capacitance of the parasitic capacitance Cp1 and the variable capacitance circuit 308, from the time (t0) when the measurement signal (X1) is supplied. In FIG. 4, the buffer circuit 303 is formed by a one-stage inverter circuit, so that the voltage of the clock signal ck falls when the voltage of the external terminal X2 increases, which is, however, shown as a rising voltage in FIG. 5 in order to simplify the explanation.

[0073] The delay times, namely, the time intervals from time t0 to time t1 and from time t0 to time t2, are determined by the combined capacitance of the parasitic capacitance and the variable capacitance circuit 308. In other words, the delay time corresponds to the capacitance value including the parasitic capacitance. Because the combined capacitance includes the capacitance value of the parasitic capacitance, the delay time does not correspond to the absolute value of the capacitance value of the variable capacitance circuit 308. However, it is possible to obtain the relative value of the capacitance value of the variable capacitance circuit 308, in which the influence of the capacitance value of the parasitic capacitance is removed, by changing the capacitance value of the variable capacitance circuit 308 to obtain delay times, and by calculating the difference ( $\Delta t$ ) of the obtained delay times. In this way, it is also possible to test the variable capacitance of the variable capacitance circuit 308 (307).

[0074] FIG. 6 is a characteristic diagram showing the principle of measuring the capacitance value by the delay time. FIG. 6 is a characteristic diagram showing the change in the delay time when the capacitance value of the variable capacitance circuit 308 is changed in series. In FIG. 4, the description has assumed that the range of the capacitance variable of the variable capacitance circuits 308 and 307 is between 2 pF to 14 pF. However, FIG. 6 shows the delay time when the capacitance of the variable capacitance circuit 308 is sequentially changed from 2 pF to 10 pF on a trial basis. In FIG. 6, there are three types of change in the delay time when the capacitance value of the variable capacitance circuit 308 is changed in series. Of the three types, the characteristic represented by TYP shows the characteristic when the buffer circuit 303, the insulated gate type transistors (hereinafter referred to as MOSFETs) configuring the switches S1 to S3 and the like, and the capacitance elements C1 to C3 or other components are produced in the normal state. Further, MAX represents the characteristic when the fluctuations are the largest in the MOSFETs and the capacitance elements C1 to C3, which are described above. MIN represents the characteristic when the fluctuations are the smallest in the MOSFET and the capacitance elements C1 to C3, which are described above. As shown in FIG. 6, when the capacitance value of the variable capacitance circuit 308 is increased, the delay time is also linearly increased in any of the characteristics.

[0075] FIG. 6 shows the characteristics when the measurement signal (X1) is raised from the ground voltage Vs to a predetermined voltage (V0), which are the same as the characteristics when the measurement signal (X1) is raised from the ground voltage (V0).

acteristics when the measurement signal (X1) is decreased from the predetermined voltage (V0) to the ground voltage Vs. In other words, also in the case of decreasing the measurement signal (X1), the delay time linearly increases when the capacitance value of the variable capacitance circuit is increased.

[0076] As shown in FIG. 6, the relationship between the capacitance value of the variable capacitance circuit and the delay time is linearly proportional. Thus, the capacitance coupled to the external terminal X2, namely, the value of the combined capacitance of the variable capacitance circuit 308 and the parasitic capacitance Cp1 can be indicated (measured) by the delay time and can be specified by the delay time.

<Capacity Value Setting by the Delay Time>

[0077] In the foregoing, it has been described that the value of the capacitance combined with the external terminal X2 can be measured by the delay time and can be specified by the time. Next, the setting of the capacitance value by the delay time will be described.

[0078] FIG. 7 is a block diagram showing the measurement of the delay time, namely, the signal propagation delay time. Further, FIG. 8 is a block diagram showing the selection and setting of the capacitance according to the delay time.

[0079] FIG. 7 shows an evaluation board that is provided, for example, by the semiconductor manufacturer. The evaluation board includes a substrate 700 similar to the substrate 100 shown in FIG. 1, and a wiring pattern formed in the substrate. Further, the evaluation board of this example is provided with a plurality of semiconductor integrated circuit devices mounted in the substrate 700. The semiconductor integrated circuit device 105 shown in FIGS. 3 and 4 is included in the semiconductor integrated circuit devices mounted in the substrate 700. FIG. 7 only shows the semiconductor integrated circuit device 105 and the associated lines 108a and 108b. Further, the semiconductor integrated circuit device 105 shown in FIG. 7 has the configuration shown in FIGS. 3 and 4, however, only the part related to the description is shown in FIG. 7.

[0080] In this embodiment, the semiconductor manufacturer measures the delay time corresponding to the capacitance value that can form the clock signal ck of desired frequency in the evaluation board, and provides the measured delay time to the electronic device manufacturer.

[0081] In other words, the semiconductor manufacturer couples the crystal oscillator 107 between the lines 108a and 108b formed over the substrate 700, and determines the capacitance value of the variable capacitance circuit 308 so as to be able to form the clock signal ck of desired (predetermined) frequency. At this time, the activation signal Cnt3 is supplied to the inverter circuit 304 from the control circuit 302 so that the inverter circuit 304 can be put into an active state. FIG. 7 shows the case in which the clock signal ck of desired frequency is formed when the capacitance value of each of the variable capacitance circuits 308 and 307 is 6 pF. At this time, the parasitic capacitance Cp1 associated with the external terminal X2 is set to 4 pF for descriptive convenience.

[0082] If it is determined that 6 pF is appropriate for the capacitance value of each of the variable capacitance circuits 308 and 307, the control circuit 302 controls to maintain the capacitance value control signals sw1 and sw2 with respect to

the register 301 so that the capacitance values of the variable capacitance circuits 308 and 307 is continuously 6 pF.

[0083] Next, the control circuit 302 is instructed to perform the measurement by the capacitance control signal Cnt1. In this way, the control circuit 302 puts the inverter circuit 304 into an inactive state by the activation signal Cnt3.

[0084] Then, the control circuit 302 supplies a measurement signal (voltage Vx1) changing to a rectangular shape, to the external terminal X1. The measurement signal propagates through a signal transmission path R1 shown by the dashed line in FIG. 7, and reaches the external terminal Pout. In this embodiment, the clock signal ck output from the external terminal Pout becomes the observation signal. FIG. 7 shows the waveform of the voltage Vx1 of the measurement signal, as well as the waveform of the voltage Vck of the observation signal formed in response to the measurement signal. The propagation delay time from the rising of the measurement signal supplied to the external terminal X1 to the rising of the observation signal, is the time corresponding to the capacitance value of the capacitance combined with the external terminal X2 as described above. In other words, in this example, the propagation delay time is the delay time corresponding to 10 pF which is the value of the combined capacitance of the capacitance value 6 pF in the variable capacitance circuit 308 and the capacitance value 4 pF of the parasitic capacitance Cp1.

[0085] Note that when the propagation delay time is measured, the crystal oscillator 107 may be or may not be coupled between the lines 108a and 108b. Of course, it is also possible that one external terminal of the crystal oscillator 107 is coupled only to the line 108b (external terminal X2). This is because the parasitic capacitance associated with the external terminal of the crystal oscillator 107 is smaller than the parasitic capacitance associated with the lines 108a and 108b. Further, in FIG. 7, the measurement signal has the same phase as that of the observation signal. However, their phases may be inverted as shown in FIG. 4.

[0086] In this way, the semiconductor manufacturer measures the delay time corresponding to the capacitance value that can form the clock signal ck of predetermined frequency in the evaluation board. Then, the semiconductor manufacturer also presents the measured delay time, for example, when providing the semiconductor integrated circuit device 105 to the electronic device manufacturer. In this case, the capacitance value corresponding to the presented delay time is the combined capacitance value of the capacitance element combined with the external terminal X. In other words, this is the combined value of the capacitance value of the variable capacitance circuit 308 and the capacitance value of the parasitic capacitance Cp1 associated with the external terminal X2. Here, the parasitic capacitance associated with the external terminal X2 includes the parasitic capacitance of the line 108b.

[0087] FIG. 8 shows the substrate 100 produced in the electronic device manufacturer. The substrate 100 shown in FIG. 8 is configured in such a way that a plurality of semiconductor integrated circuit devices including the semiconductor integrated circuit device 105, and the like are mounted in the substrate 100 as shown in FIG. 1. Similarly to FIG. 7, FIG. 8 shows only the semiconductor integrated circuit device 105 and the lines 108a and 108b. Further, the semiconductor integrated circuit device 105 has the same configuration as the one shown in FIGS. 3 and 5. However, the part related to the description is only shown in FIG. 8.

[0088] The control circuit 302 is instructed by the capacitance control signal Cnt1 to generate the activation signal Cnt3 so as to put the inverter circuit 304 into an inactive state. The control circuit 302 supplies the measurement signal with the rectangular waveform of the voltage Vck to the external terminal X1, while changing the capacitance value of the variable capacitance circuit 308, according to the capacitance value control signal sw2 formed by the register 301. Then, the control circuit 302 observes the clock signal ck (observation signal) output from the external terminal Pout. For example, the control circuit 302 sets the capacitance value of the variable capacitance circuit 308 to 2 pF according to the capacitance value control signal sw2, and supplies the measurement signal (voltage Vx1) to the external terminal X1. Then, in response to the measurement signal at this time, the control circuit 320 observes the observation signal (voltage Vck) output from the output terminal. Here, in the observation, the transmission delay time from the rising of the measurement signal to the rising of the observation signal is measured. This observation is performed by changing the capacitance value of the variable capacitance circuit 308. FIG. 8 shows an example of the capacitance values which are changed according to the variable capacitance circuits 308 and 307, as 2 pF, 4 pF, and 8 pF.

[0089] In the observation, when the transmission delay time which is the same or close to the delay time presented by the semiconductor manufacturer is observed, the control circuit 302 issues an instruction to the register 301 to continuously set the capacitance value of the variable capacitance circuit 308 at this time. In this way, the capacitance value of the variable capacitance circuit 308 is set to form the clock signal ck of desired frequency.

[0090] The board (the substrate 100, the wiring patterns, and the components mounted in the substrate) shown in FIG. 8 in the electronic device manufacturer is different from the evaluation board of the semiconductor manufacturer. For example, the material of the substrate and/or the lines, as well as the wiring patterns, and the like, are different between the two boards. Thus, the parasitic capacitance associated with the external terminal X2 is different even with the same semiconductor integrated circuit device 105. For example, in the board of the electronic device manufacturer, the capacitance Cp1 of the line 108b may also be 2 pF as shown in FIG. 8. In such a case, the value of the combined capacitance combined with the external terminal X2 is 8 pF (6 pF+2 pF), even when the value is set so that the capacitance value of the variable capacitance circuit 308 becomes 6 pF similar to the setting in the evaluation board of the semiconductor manufacturer. Thus, it is difficult to form the clock signal ck of desired frequency.

[0091] However, the delay time is obtained with the combined capacitance of the parasitic capacitance associated with the external terminal X2 and the variable capacitance circuit 308, as the time constant. Then, as described in the present embodiment, the obtained delay time is matched between the evaluation board of the semiconductor manufacturer and the board of the electronic device manufacturer. Thus, the capacitance value of 8 pF is selected and set in the variable capacitance circuit 308 in the semiconductor integrated circuit device 105 in the electronic device manufacturer. In this way, in the board of the electronic device manufacturer, the combined capacitance combined with the external terminal X2 of the semiconductor integrated circuit device 105 is 10 pF (8 pF+2 pF). Thus, the same value of the combined capacitance

as in the evaluation board of the semiconductor manufacturer is coupled to the external terminal X2. As a result, it is possible to form the clock signal ck of desired frequency also in the board of the electronic device manufacturer.

[0092] Further, in this case, the electronic device manufacturer can set the value of the variable capacitance circuit 308 based on the delay time presented by the semiconductor manufacturer. Thus, it is possible to eliminate the need to request on the crystal oscillator manufacturer and to prevent the delay in the production.

[0093] Note that in FIGS. 7 and 8, the amplitude control resistive element RD is configured by the variable element. In this way, it is possible to control the amplitude of the clock signal.

[0094] Although the above description focused on the example of controlling the register by the control circuit 302, the present invention is not limited to this example. For example, it may be possible that the capacitance value of the variable capacitance circuit is supplied from the external terminal Pdata and is stored in the register 301 each time the observation is performed.

#### Second Embodiment

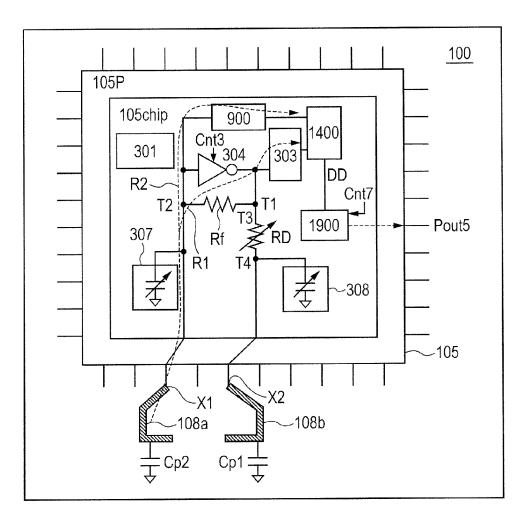

[0095] FIG. 9 is a block diagram showing the configuration of a board according to a second embodiment. FIG. 9 is similar to the configuration of the board shown in FIG. 8. Here, the description mainly focuses on the difference from FIG. 8.

[0096] One of the external terminals provided in the semi-conductor integrated circuit device 105 is assigned as an external terminal Pout2 to output the observation signal. Further, the external terminal Pout descried in FIG. 8 is assigned as an external terminal Pout1. In the semiconductor chip 105 chip, there is provided a buffer circuit 900 between the terminal T2 (second terminal) of the feedback resistive element Rf and the external terminal Pout2. The buffer circuit 900 has the same configuration as that of the buffer circuit 303, buffering the signal at the terminal T2 and transmitting to the external terminal Pout2.

[0097] When the inverter circuit 304 is put into an inactive state by the activation signal Cnt3 to observe the delay time, in the second embodiment, the measurement signal is transmitted to the external terminals Pout1 and Pout2, respectively, through the signal transmission paths R1 and R2 indicated by the dashed lines. In other words, the observation signal according to the time constant given by the feedback resistive element Rf, the variable capacitance circuit 308, and the parasitic capacitance associated with the external terminal X2, reaches the external terminal Pout1 through the signal transmission path R1 shown in FIGS. 7 and 8. On the other hand, the measurement signal (Vx1) with a rectangular voltage waveform, which is supplied to the external terminal X1, is transmitted to the terminal T2 of the feedback resistive element Rf and reaches the external terminal Pout2 through the signal transmission path R2.

[0098] In the first embodiment, the time difference between the measurement signal supplied to the external terminal X1 and the observation signal output from the external terminal Pout, is observed as the transmission delay time. However, in the second embodiment, the observation signal corresponding to the measurement signal supplied to the external terminal X1 is output from the external terminal Pout2. Thus, it is possible to obtain the transmission delay time by obtaining the time difference between the observation signal output

from the external terminal Pout2 and the observation signal output from the external terminal Pout1. In other words, it is possible to obtain the delay time by the relative difference between the observation signals, instead of the absolute value with respect to the measurement signal. Thus, the improvement in the accuracy can be achieved. Further, since the delay time is measured as the time difference between the output observation signals, it is possible to simplify the measurement in the measurement device (tester).

[0099] In FIG. 9, it is assumed that the semiconductor integrated circuit device 105 is mounted in the board of the electronic device manufacturer. However, the same effect can be obtained when the semiconductor integrated circuit device 105 is mounted in the evaluation board of the semiconductor manufacturer.

#### <Variation>

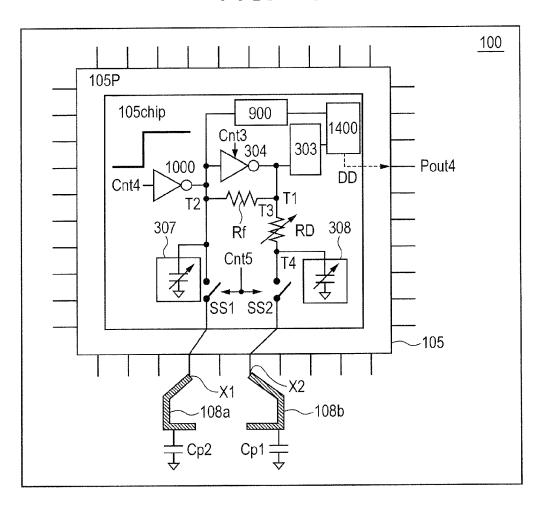

[0100] FIG. 10 is a block diagram showing the configuration of a board according to a variation of the second embodiment. The difference between FIG. 9 and FIG. 10 is in that the semiconductor chip 105 chip includes: a measurement single generating circuit for generating a measurement signal; a switch circuit SS1 (isolation circuit) coupled between the terminal T2 of the feedback resistive element Rf and the external terminal X1; and a switch circuit SS2 (isolation circuit) coupled between the terminal T4 of the amplitude control resistive element RD and the external terminal X2.

[0101] In FIG. 10, although the measurement signal generating circuit is configured by an inverter circuit 1000, the present invention is not limited to this. Although not particularly limited, a measurement signal Cnt4 is supplied to the inverter circuit 1000 from the control circuit 302 (FIG. 3), and the measurement signal which is inverted from the measurement signal Cnt4 is supplied to the terminal T2 of the feedback resistive element Rf. Further, although not particularly limited, a test signal Cnt5 is supplied to the switch circuits SS1 and SS2 from the control circuit 302.

[0102] The control circuit 302 supplies the measurement signal Cnt4 to the inverter circuit 1000 when measuring the capacitance value of the combined capacitance including the capacitance combined with the external terminal X2, and when setting the capacitance value of the variable capacitance circuit 308 so as to match the presented delay time. In this way, as shown in FIG. 9, the measurement signal is supplied to the terminal T2 of the feedback resistive element Rf from the inverter circuit 1000, without supplying the measurement signal to the external terminal X1. In this case also, it is possible to obtain the time difference between the observation signals output to the external terminals Pout1 and Pout2, respectively, as the delay time. Thus, it is possible to present the delay time from the semiconductor manufacturer. While in the electronic device manufacturer, it is possible to form a clock signal of a desired frequency by setting the capacitance value of the variable capacitance circuit 308 so that the time difference between the output terminals Pout1 and Pout2 matches the presented delay time. In this variation, the need for providing the measurement single to the external terminal is eliminated, allowing the handling to be facilitated.

[0103] Further, for example, when the capacitance value of the variable capacitance circuits 308 and 307 is checked, the control circuit 302 forms a test signal Cnt5 to put the switch circuits SS1 and SS2 into an OFF state. The capacitance value is checked, for example, during the test of the semiconductor integrated circuit device 105 in the semiconductor manufac-

turer. The terminal T4 and the external terminal X2 as well as the terminal T2 and the external terminal X1 are electrically separated from each other by putting the switch circuits SS1 and SS2 into an OFF state. At this time, the variable capacitance circuits 308 and 307 are coupled to the terminals  $T\bar{1}$  and T2, respectively. As described above, the control circuit 302 puts the switch circuits SS1 and SS2 into an OFF state and supplies the measurement signal from the inverter circuit 1000 to the terminal T2. In this way, it is possible to measure the capacitance value of the variable capacitance circuit 308. In this case, the external terminals X1 and X2 are electrically separated from each other. Thus, it is possible to reduce the influence on the measurement value of the variable capacitance circuit 308 measured by the parasitic capacitances Cp1 and Cp2 associated with the external terminals X1 and X2. [0104] Note that it may also be possible to provide only the switch circuit SS2 in order to measure the capacitance value of the variable capacitance circuit 308 while reducing the influence on the parasitic capacitance Cp1 associated with the external terminal X2. Of course, when performing the oscillation operation, the control circuit 302 puts the switch circuits SS1 and SS2 into an ON state. It is desirable that not only the switch circuit SS2 but also the switch circuit SS1 is provided so that the on-resistances of the switch circuits SS1 and SS2 are present when in the ON sate.

[0105] In this variation, the switch circuits SS1, SS2 and the measurement signal generating circuit (inverter 1000) are provided in the semiconductor chip 105 chip. However, the switch circuits SS1 and SS2 may not be provided. When the switch circuits SS1 and SS2 are provided, it is desirable to provide the measurement signal generating circuit (inverter 1000) to form the measurement signal inside the circuit.

#### Third Embodiment

[0106] In the first and second embodiments, the description has focused on the measurement and setting of the combined capacitance combined with the external terminal X2 of the external terminals X1 and X2 to which the external terminal of the crystal oscillator 107 is coupled. With respect to the combined capacitance coupled to the external terminal X1, similarly to the case of the external terminal X2, it is possible to measure the value of the combined capacitance coupled to the external terminal X1 by the transmission delay time and to set the value of the combined capacitance by the transmission delay time. The third embodiment will describe the configuration to measure and set the combined capacitance combined with the external terminal X1 according to the transmission delay time.

[0107] FIG. 11 is a characteristic diagram generated by supplying a measurement signal (second measurement signal) with the rectangular waveform of the voltage (Vx2) to the external terminal X2, and by measuring the delay time of the signal at the terminal T2 (second terminal) of the feedback resistive element Rf while changing the capacitance value in the variable capacitance circuit 307. Here, the delay time is the time from when the voltage (Vx2) of the measurement signal supplied to the external terminal X2 rises to when the voltage of the signal at the terminal T2 of the feedback resistive element Rf reaches a predetermined value (corresponding to the threshold voltage VT) in response to the rising of the voltage. Similar to FIG. 6, FIG. 11 shows three characteristics. The three characteristics TYP, MAX, MIN are the same as the characteristics TYP, MAX, MIN described in FIG. 6. Further, similar to FIG. 6, the horizontal axis of FIG. 11 represents the capacitance value of the variable capacitance circuit 307, while the vertical axis represents the delay time. The difference between FIG. 6 and FIG. 11 is that whether the capacitance value of the variable capacitance circuit 308 is changed and whether the capacitance value of the variable capacitance circuit 307 is changed.

[0108] Similar to FIG. 6, also in FIG. 11, when the capacitance value of the variable capacitance circuit 307 is increased, the delay time is also linearly increased. In other words, it is possible to indicate the capacitance value of the variable capacitance circuit 307 by the delay time, and to specify the capacitance value of the variable capacitance circuit 307 according to the delay time.

[0109] In FIG. 11, the delay time is the time interval from the rising of the measurement signal supplied to the external terminal X2 to when the voltage of the signal at the terminal T2 changes in response to this rise. However, the time (delay time) from the falling of the measurement signal supplied to the external terminal X2 to when the signal at the terminal T2 changes in response to this fall, also changes according to the characteristics similar to the characteristics shown in FIG. 11. In other words, in this case also, when the capacitance value of the variable capacitance circuit 307 is increased, the delay time is also linearly increased. Thus, also in the falling edge of the measurement signal supplied to the external terminal X2, it is possible to indicate the capacitance value of the variable capacitance circuit 307 by the delay time, and to specify the capacitance value according to the delay time.

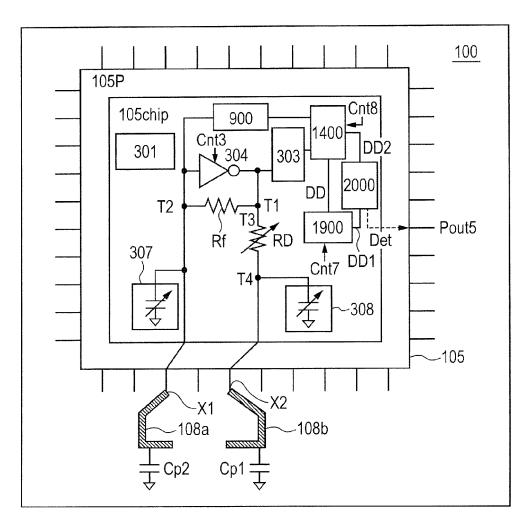

[0110] FIGS. 12 and 13 are circuit diagrams showing the configuration of the main part of the semiconductor integrated circuit device 105 according to the third embodiment. Similar to FIG. 4, FIGS. 12 and 13 show the main part of the oscillator circuit in the semiconductor integrated circuit device 105 shown in FIG. 3. In other words, FIGS. 12 and 13 show the part corresponding to the inverter circuit 304, the feedback impedance element 305, the amplitude control impedance element 306, and the variable capacitance circuits 308 and 307, which are shown in FIG. 3. FIGS. 12 and 13 show the configuration of the same circuit, in which FIG. 12 shows the operation of measuring the transmission delay time corresponding to the capacitance value of the combined capacitance combined with the external terminal X2 by supplying the measurement signal (Vx1) to the external terminal X1. While FIG. 13 shows the operation of measuring the delay time corresponding to the capacitance value of the combined capacitance combined with the external terminal X1 by supplying the measurement signal (Vx2) to the external terminal X2. In other words, with the configuration of the circuit shown in FIGS. 12 and 13, it is possible to measure the delay time corresponding to the capacitance value of each of the external terminals X1 and X2 with which the external terminals of the crystal oscillator 107 are combined, respectively.

[0111] First, the configuration of the circuit shown in FIGS. 12 and 13 will be described. In FIG. 4, the inverter circuit 304 is used as the negative resistance amplifier to perform oscillation. However, in FIGS. 12 and 13, an NAND circuit 1200 with two inputs is used as a load resistance amplifier. One input of the NAND circuit 1200 is supplied with the activation signal Cnt3. The other input is coupled to the terminal T2 of the feedback resistive element Rf, and the output of the NAND circuit 1200 is coupled to the terminal T1 of the feedback resistive element Rf. The terminal T2 of the feedback resistive element Rf is coupled to the variable capaci-

tance circuit 307 and the external terminal X1. Then, the terminal T1 is coupled to the terminal T3 of the amplitude control resistive element RD as well as the input of the inverter circuit 1203. The terminal T4 of the amplitude control resistive element RD is coupled to the variable capacitance circuit 308 and the external terminal X2. In other words, the terminal T1 of the feedback resistive element Rf is coupled to the external terminal X2 through the amplitude control resistive element RD, similarly to the first embodiment.

[0112] Further, the variable capacitance circuits 308 and 307 are the same as the variable capacitance circuits 308 and 307 in the configuration, respectively. In other words, in FIGS. 12 and 13, the variable capacitance circuit 308 (307) has three series circuits coupled in parallel between the terminal T1 (T2) and the ground voltage Vs. Here, the series circuit has switches S1 to S3 and capacitance elements C1 to C3, which are coupled in series to each other. The capacitance elements C1 to C3 have different capacitance values, respectively. Although not shown in FIGS. 12 and 13, the switches S1 to S3 are switched and controlled by the capacitance value control signals sw1 and sw2 as shown in FIG. 4. Further, the output of an inverter circuit 1203 is coupled to the external terminal Pout1 through a buffer circuit 1204. Although not particularly limited, in the third embodiment, the buffer circuit 1204 inverts the phase of the supplied signal and output the inverted signal.

[0113] In the third embodiment, the two-input NAND circuit 1201 is added to forma signal path through which a measurement signal is transmitted when the measurement signal is supplied to the external terminal X2. In other words, one input of the two-input NAND circuit 1201 is coupled to the terminal T2 of the feedback resistive element Rf, and the other input is supplied with an activation signal Cnt6 from the control circuit 302 (FIG. 3).

[0114] When the value of the combined capacitance combined with the external terminal X1 or X2 is measured as the delay time, the control circuit 302 changes the activation signal Cnt3 to a low level and the activation signal Cnt6 to a high level. In this way, when the value of the combined capacitance combined with the external terminal X1 or X2 is measured as the delay time, the NAND circuit 1200 does not transit the signal at the terminal T2 to the terminal T1. On the other hand, at this time, the NAND circuit 1201 inverts the phase of the signal at the terminal T2 and outputs the inverted signal. The output of the NAND circuit is inverted in phase by the inverter circuit 1202 and is transmitted to the external terminal Pout3. Note that when the oscillation is performed, the control circuit 302 changes the activation signal Cnt3 to a high level and the activation signal Cnt6 to a low level. In this way, the NAND circuit 1200 inverts the phase of the signal at the terminal T2 and transmits to the terminal T1. At this time, the NAND circuit 1201 does not transmit the signal at the terminal T2 to the terminal T1 and, for example, supplies a high level to the input of the inverter circuit 1202.

[0115] FIG. 12 also shows the voltage waveform when the measurement signal (first measurement signal) is supplied to the external terminal X1 to measure the value of the combined value combined with the external terminal X2 as the transmission delay time. In FIG. 12, Vx1 represents the voltage of the measurement signal supplied to the external terminal X1, and Vt1 represents the voltage at the terminal T1 of the feedback resistive element Rf. Further, Vck1 represents the voltage of the signal (first observation signal) output from the