| (19) | Europäisches<br>Patentamt<br>European<br>Patent Office<br>Office européen<br>des brevets<br>EUROPEAN PATE<br>published in accordance                                                                                                               |                                                                                                                                                                                                                                                                            |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) | Date of publication:<br>15.09.2021 Bulletin 2021/37<br>Application number: 19880986.5                                                                                                                                                              | <ul> <li>(51) Int CI.:<br/><i>H01L 27/146</i> <sup>(2006.01)</sup></li> <li>(86) International application number:<br/>PCT/JP2019/041608</li> </ul>                                                                                                                        |

| (22) | Date of filing: <b>24.10.2019</b>                                                                                                                                                                                                                  | (87) International publication number:<br>WO 2020/095689 (14.05.2020 Gazette 2020/20)                                                                                                                                                                                      |

| (84) | Designated Contracting States:<br>AL AT BE BG CH CY CZ DE DK EE ES FI FR GB<br>GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO<br>PL PT RO RS SE SI SK SM TR<br>Designated Extension States:<br>BA ME<br>Designated Validation States:<br>KH MA MD TN | <ul> <li>(72) Inventors:</li> <li>OHURA, Masashi<br/>Atsugi-shi, Kanagawa 243-0014 (JP)</li> <li>KOHYAMA, Yusuke<br/>Atsugi-shi, Kanagawa 243-0014 (JP)</li> <li>(74) Representative: MFG Patentanwälte<br/>Meyer-Wildhagen Meggle-Freund<br/>Gerhard PartG mbB</li> </ul> |

| (30) | Priority: 06.11.2018 JP 2018208679<br>26.06.2019 JP 2019118399                                                                                                                                                                                     | Amalienstraße 62<br>80799 München (DE)                                                                                                                                                                                                                                     |

| (71) | Applicant: Sony Semiconductor Solutions<br>Corporation<br>Atsugi-shi, Kanagawa 243-0014 (JP)                                                                                                                                                       |                                                                                                                                                                                                                                                                            |

# (54) IMAGING ELEMENT AND ELECTRONIC APPARATUS

(57) The present technology relates to an imaging element and electronic equipment that enable an increase in the amount of saturated charge.

The imaging element includes a substrate, a first photoelectric conversion region provided in the substrate, a second photoelectric conversion region provided in the substrate, the second photoelectric conversion region being adjacent to the first photoelectric conversion region, a pixel isolation section provided in the substrate and between the first photoelectric conversion region and the second photoelectric conversion region, and a junction region provided in a side wall of the pixel isolation section, the junction region including a first impurity region including first impurities and a second impurity region including second impurities. The length of a side of the first impurity region formed in the side wall of the pixel isolation section, the side perpendicularly intersecting two parallel sides of four sides of the pixel isolation section enclosing the first photoelectric conversion region, is larger than the length between the two parallel sides of the pixel isolation section. The present technology is applicable to, for example, an imaging apparatus.

Printed by Jouve, 75001 PARIS (FR)

# Description

#### [Technical Field]

**[0001]** The present technology relates to an imaging element and electronic equipment, and in particular, to an imaging element and electronic equipment in which a P-type solid phase diffusion layer and an N-type solid phase diffusion layer are formed in a side wall of an interpixel light shielding wall formed between pixels, to form an intense electric field region in which charge is held, thus increasing the amount of saturated charge Qs of each pixel.

### [Background Art]

**[0002]** In the related art, known is a technology in which, for the purpose of increasing the amount of saturated charge Qs in each pixel in an imaging element, a P-type diffusion layer and an N-type diffusion layer are formed in a side wall of a trench formed between pixels, to form an intense electric field region in which charge is held (see, for example, PTL 1).

[Citation List]

[Patent Literature]

[PTL 1]

[0003] Japanese Patent Laid-Open No. 2015-162603

[Summary]

[Technical Problems]

**[0004]** However, in a structure disclosed in PTL 1, pinning on a light incidence side of an Si (silicon) substrate may be weakened, and charge generated may flow into a photodiode, degrading a Dark property. This may lead to, for example, occurrence of voids and generation of a dark current. Additionally, a further increase in the amount of saturated charge is desired.

**[0005]** In view of these circumstances, an object of the present technology is to enable inhibition of degradation of the Dark property and to increase the amount of saturated charge.

# [Solution to Problems]

**[0006]** An imaging element of an aspect of the present technology includes a substrate, a first photoelectric conversion region provided in the substrate, a second photoelectric conversion region provided in the substrate, the second photoelectric conversion region being adjacent to the first photoelectric conversion region, a pixel isolation section provided in the substrate and between the first photoelectric conversion region and the second

photoelectric conversion region, and a junction region provided in a side wall of the pixel isolation section, the junction region including a first impurity region including first impurities and a second impurity region including second impurities, and a length of a side of the first impurity region formed in the side wall of the pixel isolation section, the side perpendicularly intersecting two parallel sides of four sides of the pixel isolation section enclosing the first photoelectric conversion region, is larger than a length between the two parallel sides of the pixel isolation

<sup>10</sup> length between the two parallel sides of the pixel isolation section.

**[0007]** Electronic equipment of an aspect of the present technology is electronic equipment including an imaging element, the imaging element including a sub-

<sup>15</sup> strate, a first photoelectric conversion region provided in the substrate, a second photoelectric conversion region provided in the substrate, the second photoelectric conversion region being adjacent to the first photoelectric conversion region, a pixel isolation section provided in

20 the substrate and between the first photoelectric conversion region and the second photoelectric conversion region, and a junction region provided in a side wall of the pixel isolation section, the junction region including a first impurity region including first impurities and a second

<sup>25</sup> impurity region including second impurities. In the electronic equipment, a length of a side of the first impurity region formed in the side wall of the pixel isolation section, the side perpendicularly intersecting two parallel sides of four sides of the pixel isolation section enclosing the

<sup>30</sup> first photoelectric conversion region, is larger than a length between the two parallel sides of the pixel isolation

section. [0008] The imaging element of the aspect of the

present technology includes the substrate, the first photoelectric conversion region provided in the substrate, the second photoelectric conversion region provided in the substrate, the second photoelectric conversion region being adjacent to the first photoelectric conversion region, the pixel isolation section provided in the substrate and between the first photoelectric conversion region and the second photoelectric conversion region, and the junction region provided in the side wall of the pixel isolation section, the pixel isolation section provided the pixel isolation section provided in the side wall of the pixel isolation section, the junction region including the first

impurity region including first impurities and the second

impurity region including second impurities. Additionally,

the imaging element is configured such that the length

of the side of the first impurity region formed in the side

wall of the pixel isolation section, the side perpendicularly

intersecting the two parallel sides the four sides of the

pixel isolation section enclosing the first photoelectric

pixel isolation section enclosing the first photoelectric conversion region, is larger than the length between the two parallel sides of the pixel isolation section.

[0009] Note that the electronic equipment may be an independent apparatus or an internal block constituting<sup>55</sup> one apparatus.

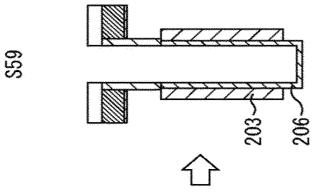

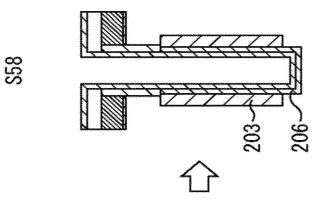

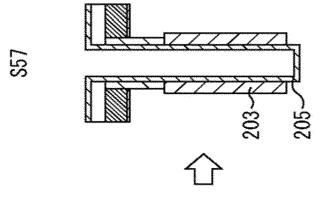

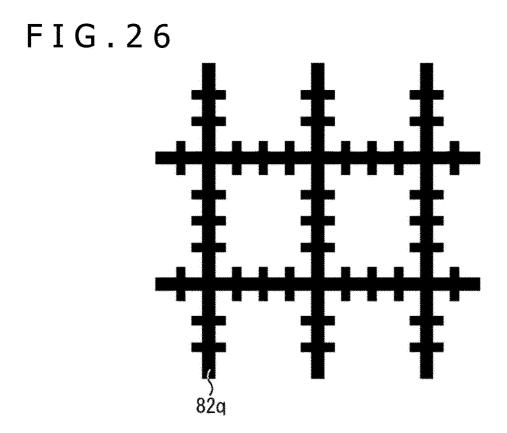

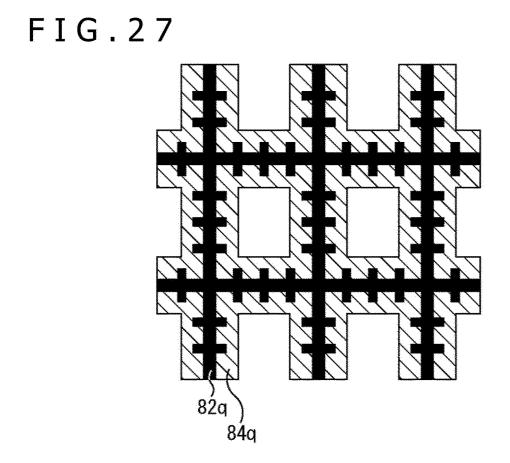

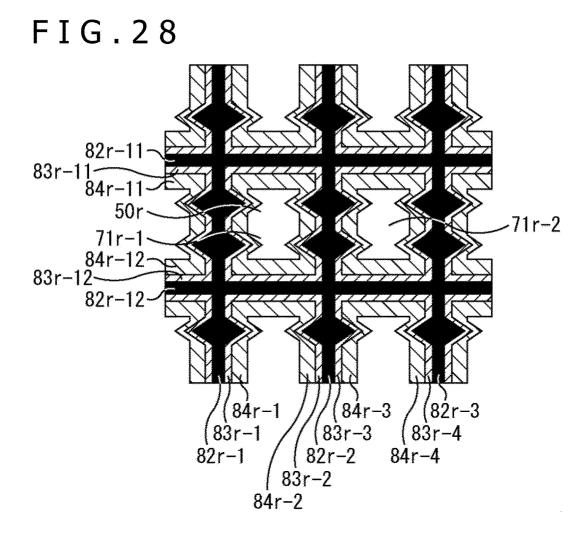

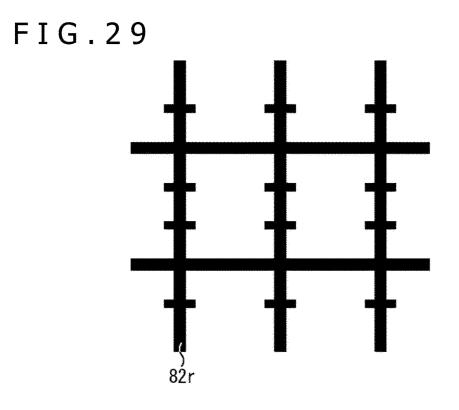

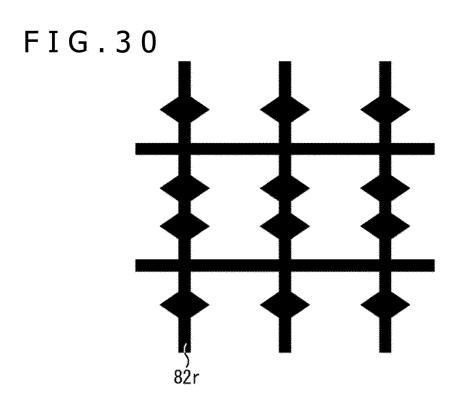

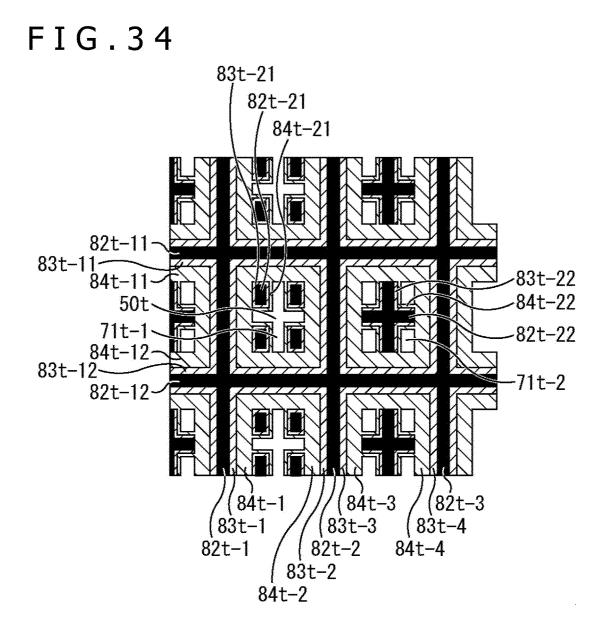

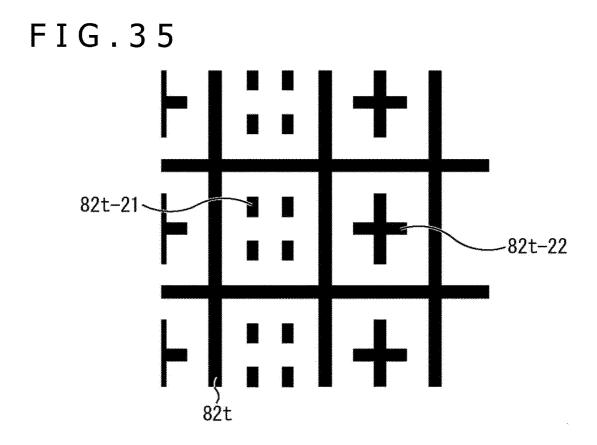

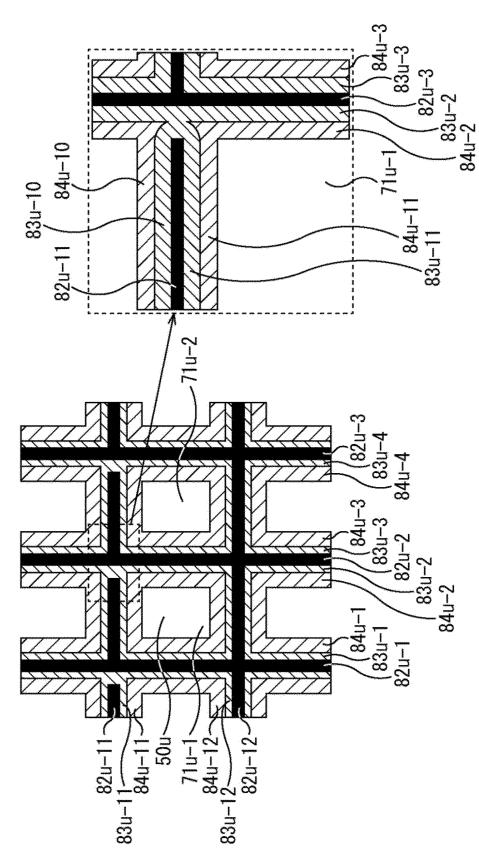

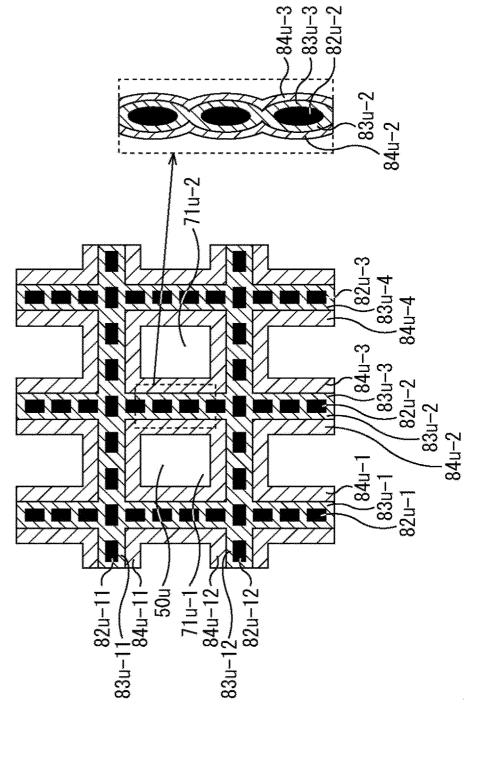

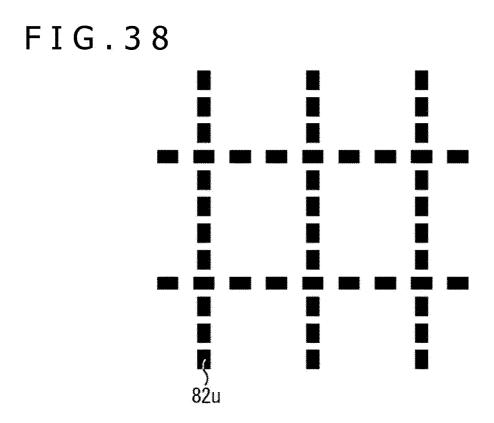

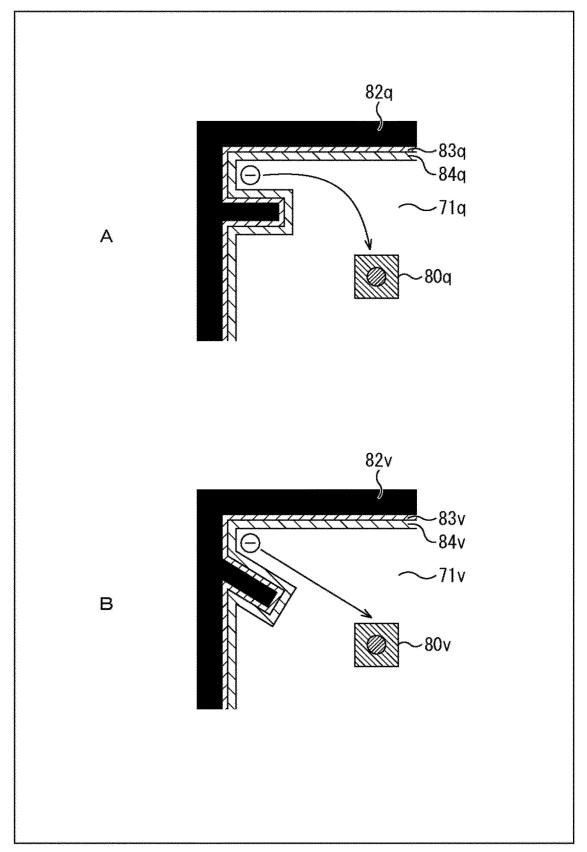

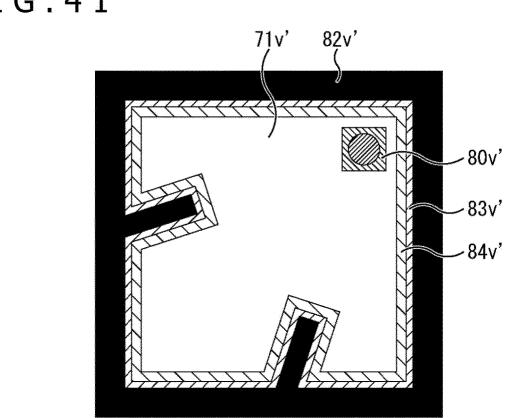

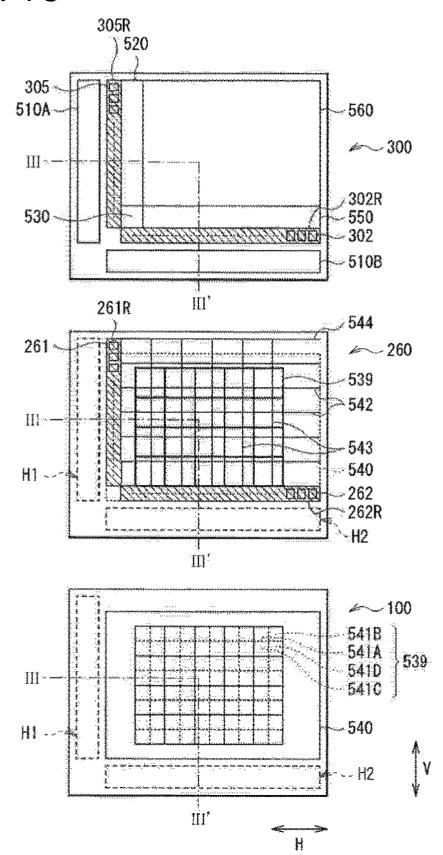

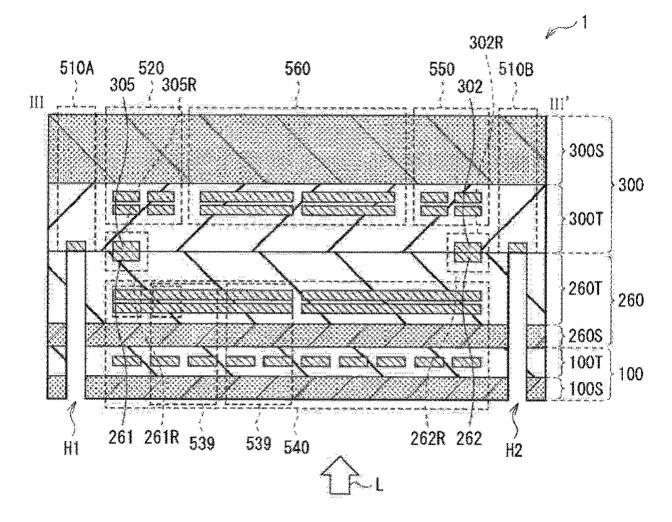

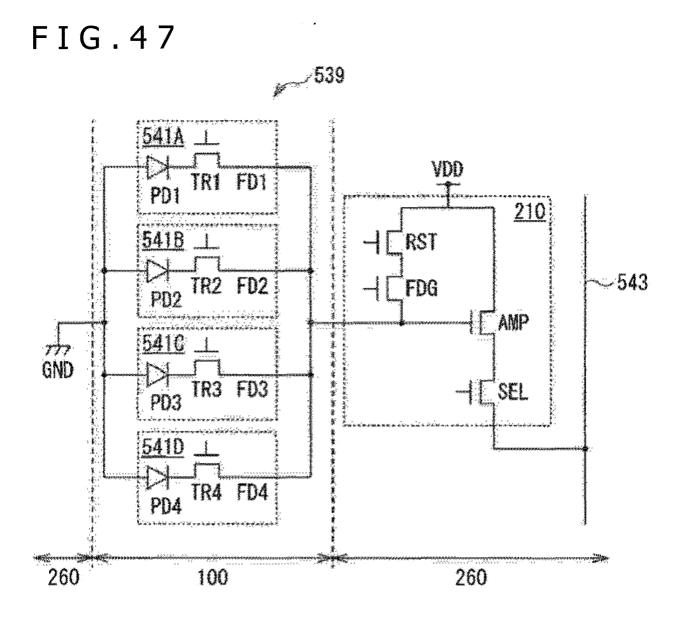

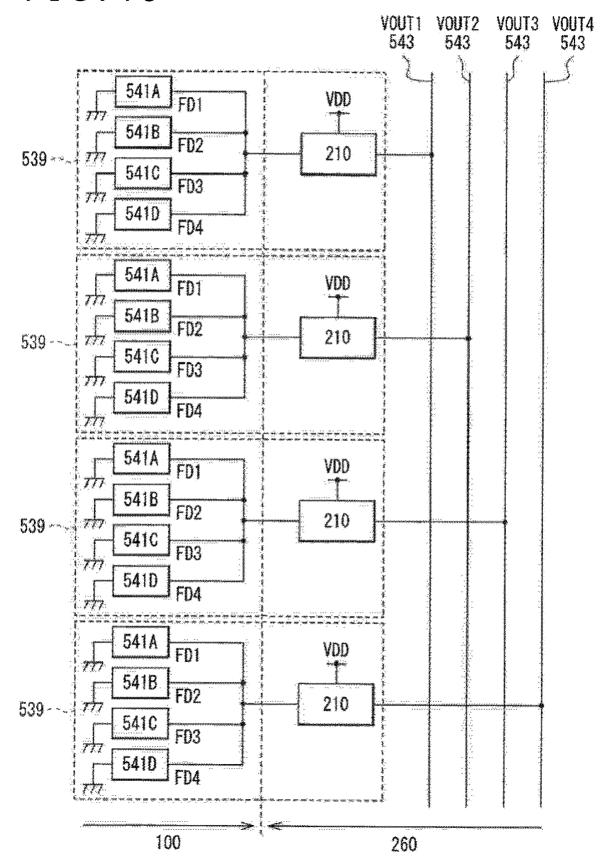

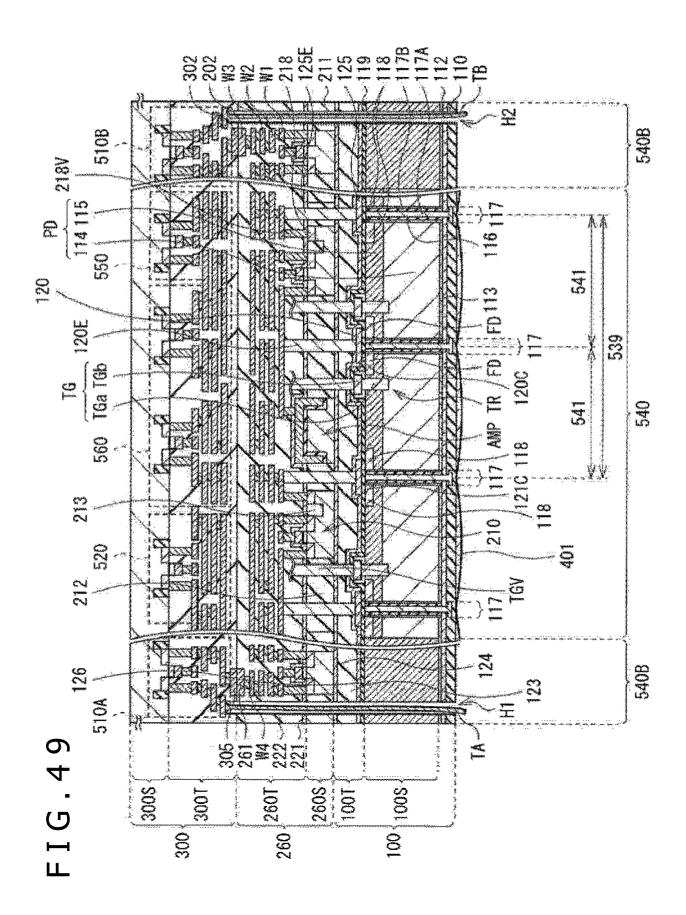

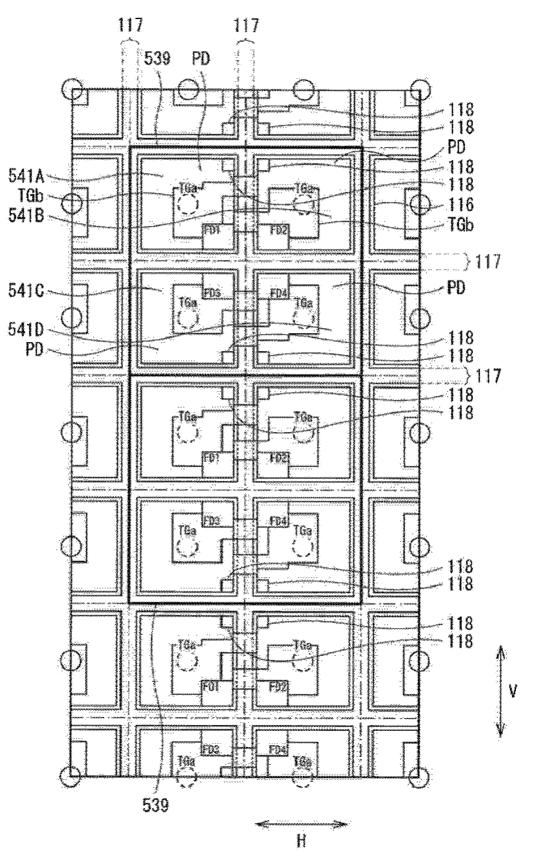

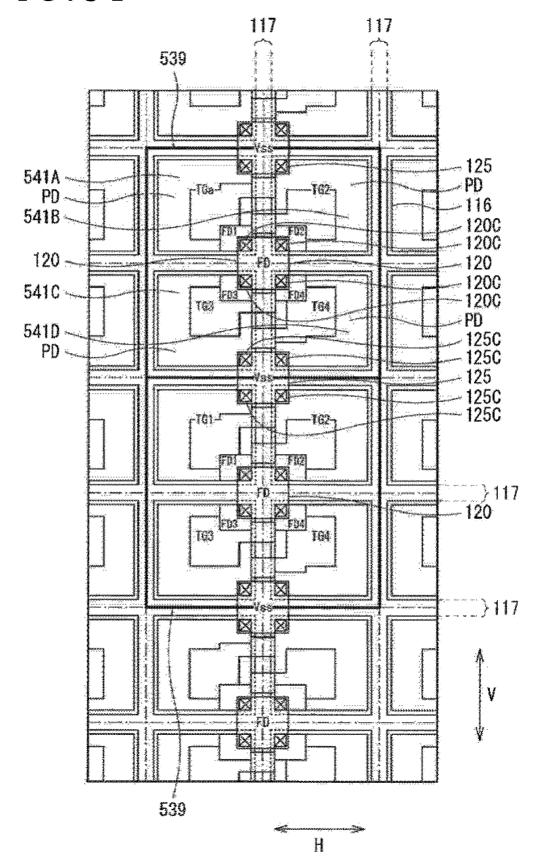

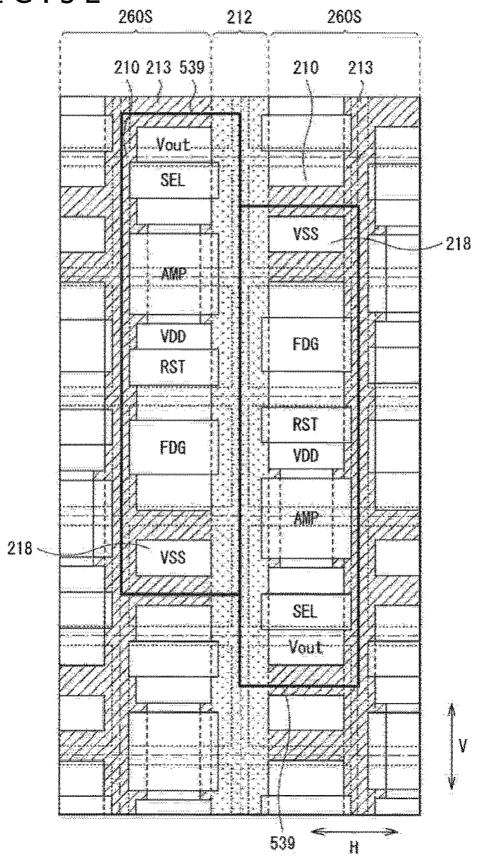

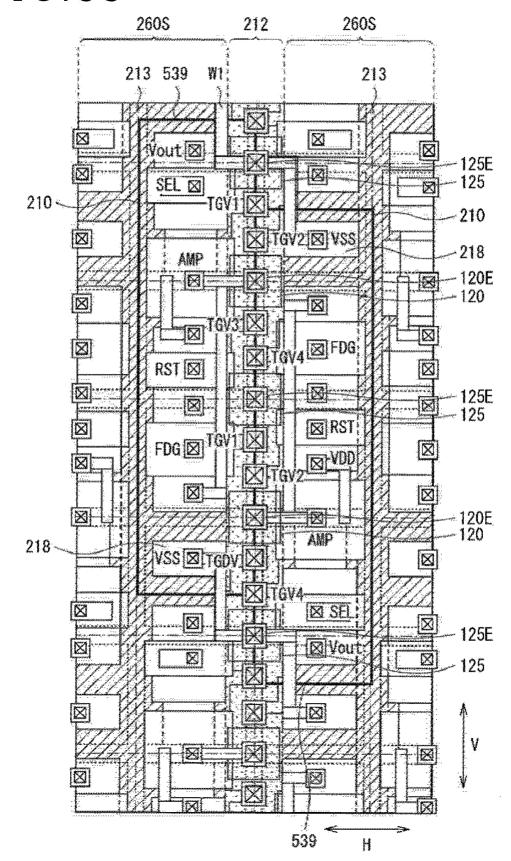

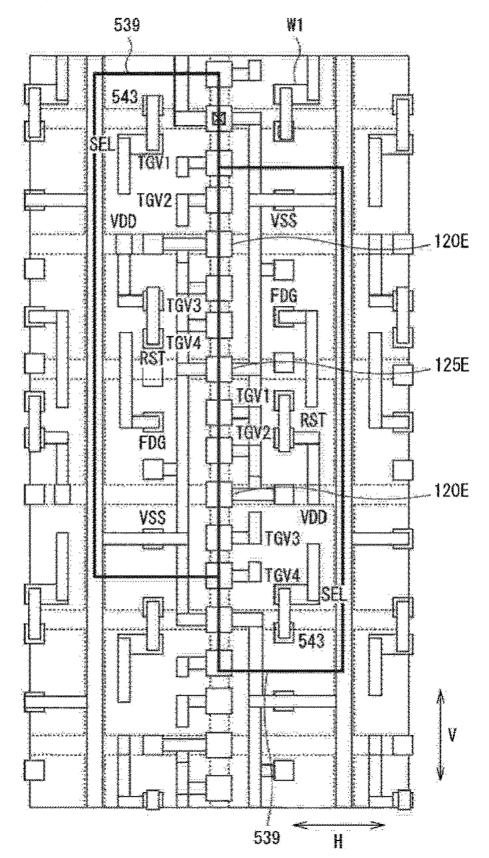

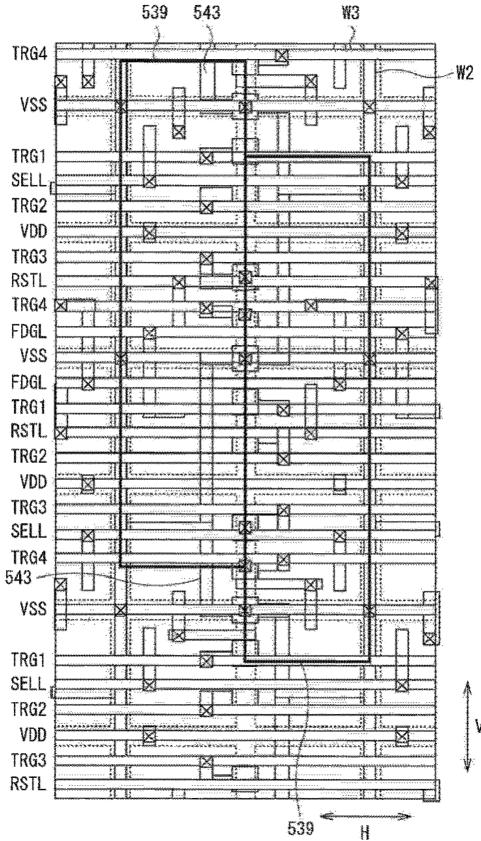

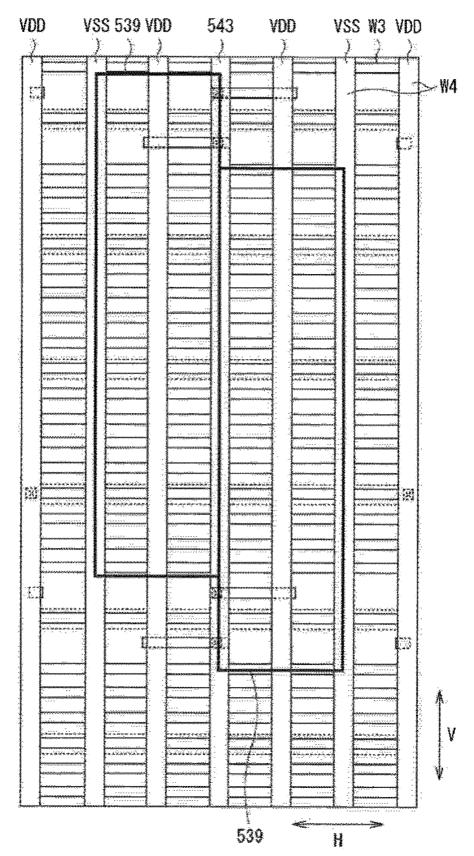

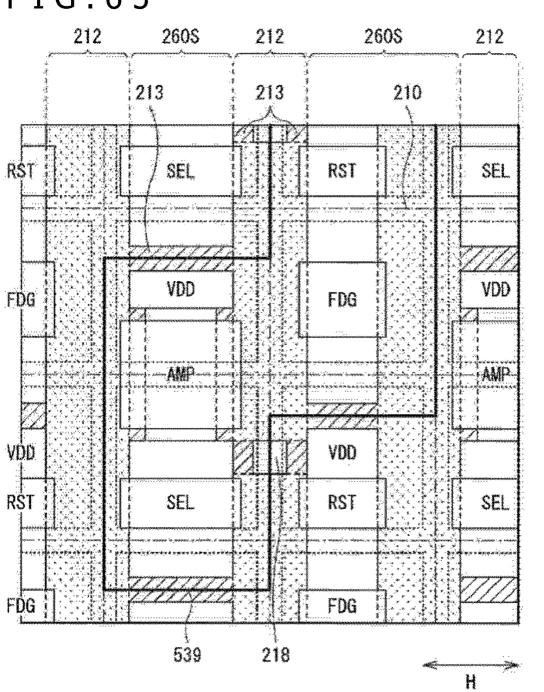

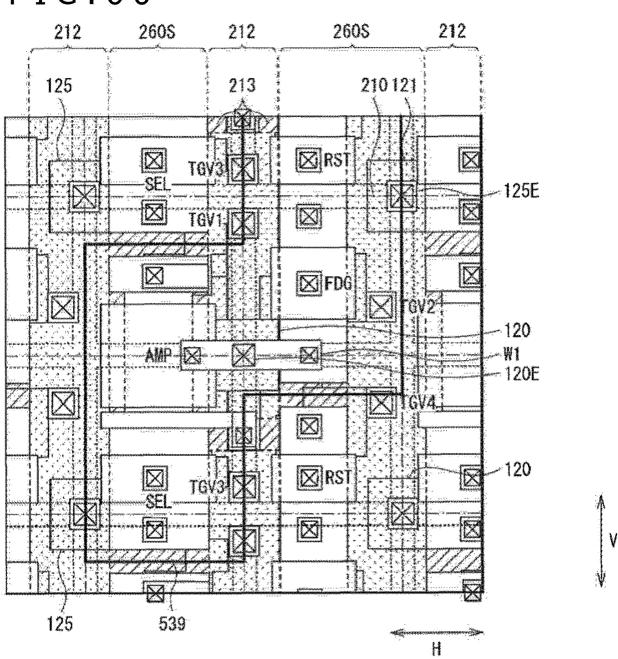

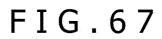

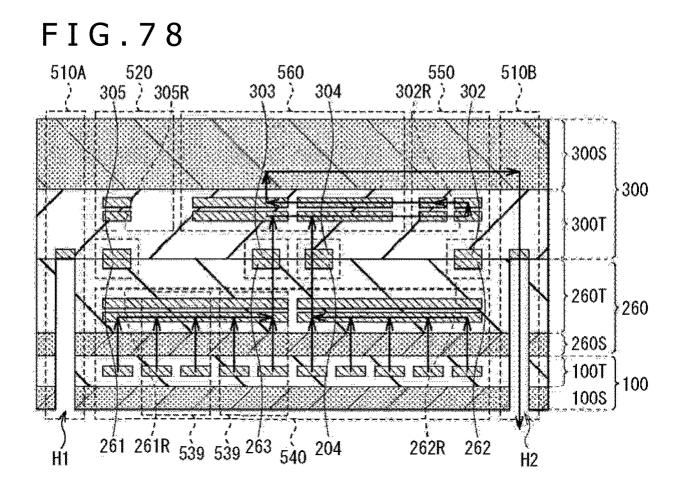

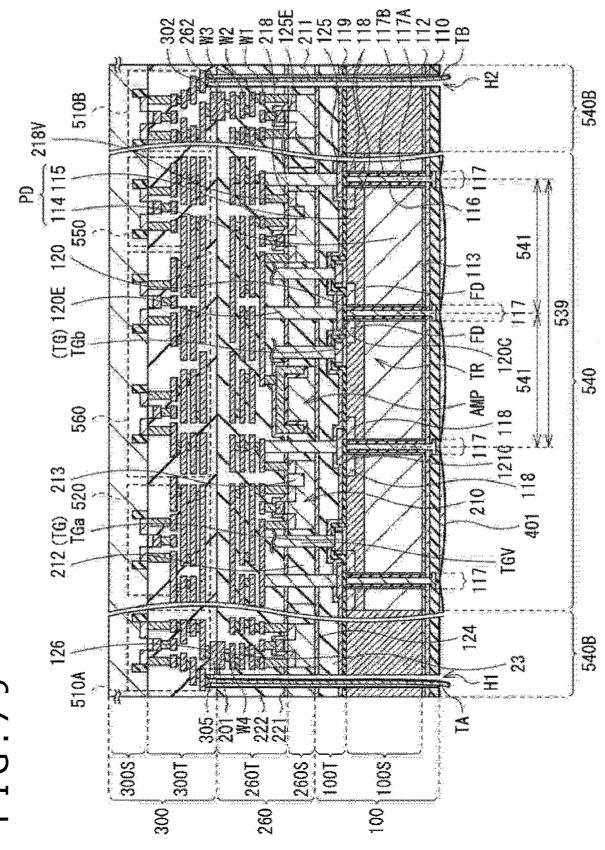

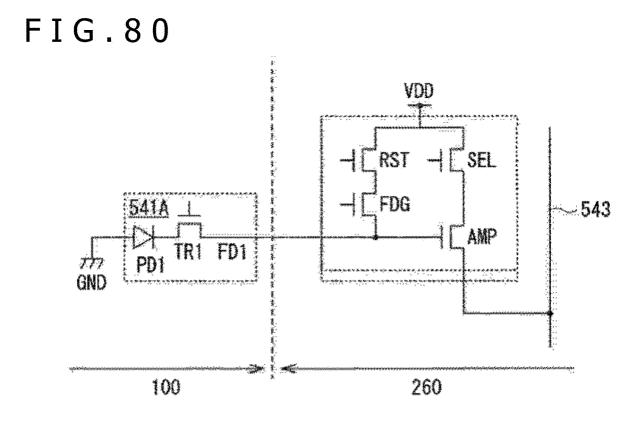

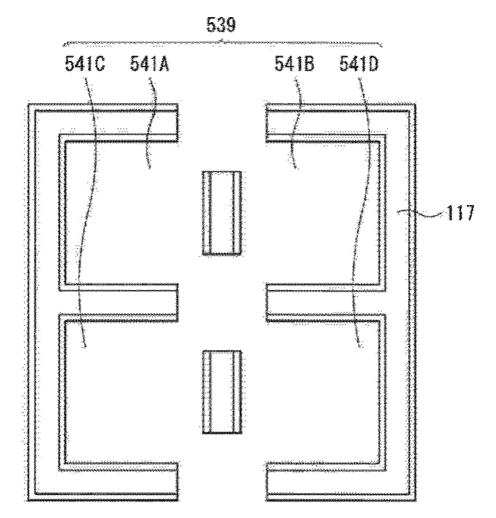

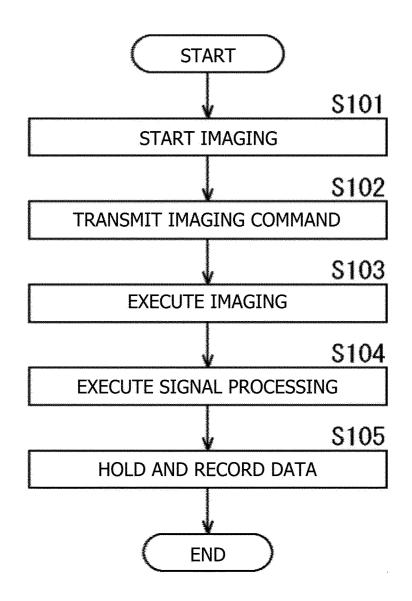

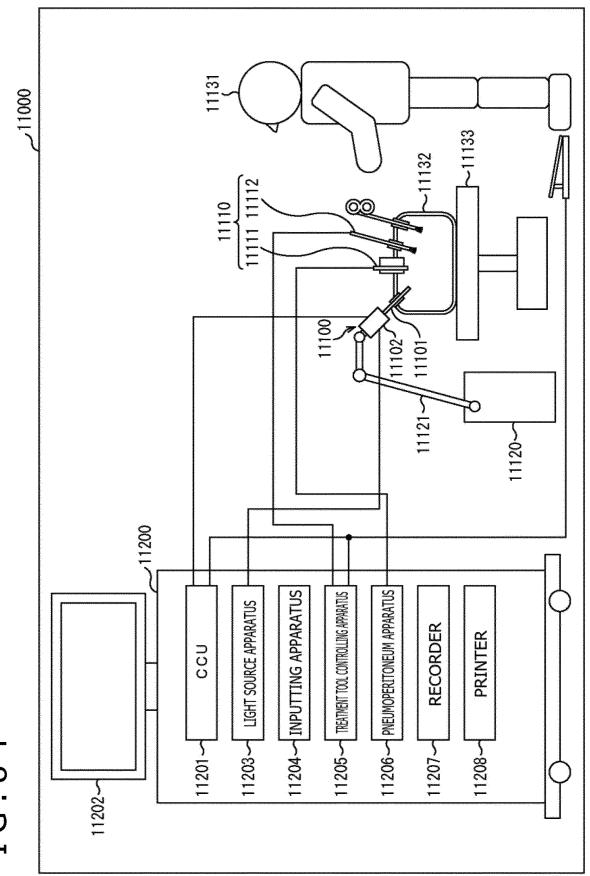

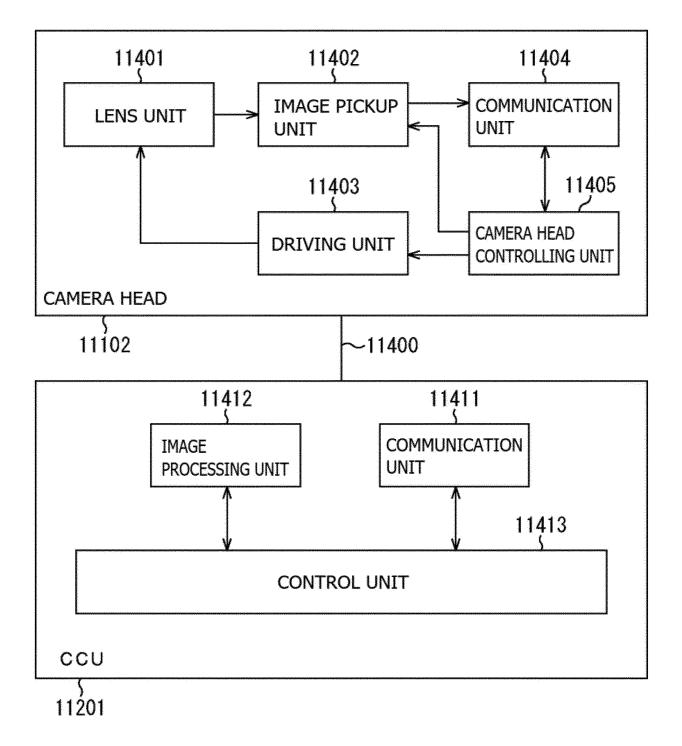

[Brief Description of Drawings] 10th configuration example of the pixel to which the present technology is applied. [0010] [FIG. 16] FIG. 16 depicts a vertical cross-sectional view and 5 [FIG. 1] a plan view illustrating an 11th configuration example FIG. 1 is a diagram depicting a configuration examof the pixel to which the present technology is apple of an imaging element. plied. [FIG. 2] [FIG. 17] FIG. 2 is a diagram depicting a configuration exam-FIG. 17 depicts a vertical cross-sectional view and ple of the imaging element. 10 a plan view illustrating a 12th configuration example of the pixel to which the present technology is ap-[FIG. 3] FIG. 3 is a vertical cross-sectional view of assistance plied. in describing a first configuration example of a pixel [FIG. 18] to which the present technology is applied. FIG. 18 is a vertical cross-sectional view depicting a [FIG. 4] 15 13th configuration example of the pixel to which the FIG. 4 is a plan view of a front side of a first embodpresent technology is applied. iment of pixels to which the present technology is [FIG. 19] applied. FIG. 19 is a vertical cross-sectional view depicting a [FIG. 5] 14th configuration example of the pixel to which the 20 FIG. 5 is a circuit diagram of the pixel. present technology is applied. [FIG. 6] [FIG. 20] FIG. 6 depicts diagrams of assistance in describing FIG. 20 is a plan view depicting a configuration exa method for manufacturing the DTI 82 and periphample of pixels to which the present technology is eral regions. applied. 25 [FIG. 7] [FIG. 21] FIG. 7 is a vertical cross-sectional view depicting a FIG. 21 is a plan view depicting a 15th configuration second configuration example of the pixel to which example of the pixel to which the present technology is applied. the present technology is applied. [FIG. 8] [FIG. 22] FIG. 8 is a vertical cross-sectional view depicting a 30 FIG. 22 is a plan view depicting another 15th configuration example of the pixel to which the present third configuration example of the pixel to which the present technology is applied. technology is applied. [FIG. 9] [FIG. 23] FIG. 9 is a vertical cross-sectional view depicting a FIG. 23 depicts diagrams of assistance in describing fourth configuration example of the pixel to which the the size of a protruding portion. 35 present technology is applied. [FIG. 24] [FIG. 10] FIG. 24 is a diagram of assistance in describing man-FIG. 10 is a vertical cross-sectional view depicting a ufacturing of a pixel to which the present technology fifth configuration example of the pixel to which the is applied. 40 present technology is applied. [FIG. 25] [FIG. 11] FIG. 25 is a diagram of assistance in describing man-FIG. 11 is a vertical cross-sectional view depicting a ufacturing of a pixel to which the present technology sixth configuration example of the pixel to which the is applied. present technology is applied. [FIG. 26] 45 [FIG. 12] FIG. 26 is a diagram of assistance in describing the FIG. 12 is a vertical cross-sectional view depicting a shape of a trench resulting from etching. seventh configuration example of the pixel to which [FIG. 27] the present technology is applied. FIG. 27 is a diagram of assistance in describing the [FIG. 13] shape of an N-type solid phase diffusion layer result-FIG. 13 is a vertical cross-sectional view depicting 50 ing from etching. an eighth configuration example of the pixel to which [FIG. 28] the present technology is applied. FIG. 28 is a plan view depicting a 16th configuration example of pixels to which the present technology [FIG. 14] FIG. 14 is a vertical cross-sectional view depicting a is applied. ninth configuration example of the pixel to which the 55 [FIG. 29] present technology is applied. FIG. 29 is a diagram of assistance in describing the shape of trenches resulting from etching. [FIG. 15] FIG. 15 is a vertical cross-sectional view depicting a [FIG. 30]

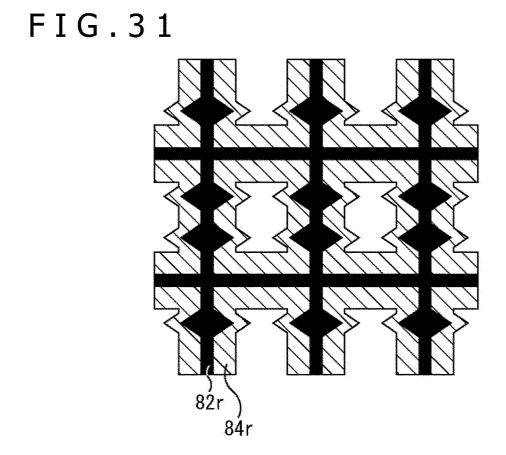

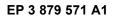

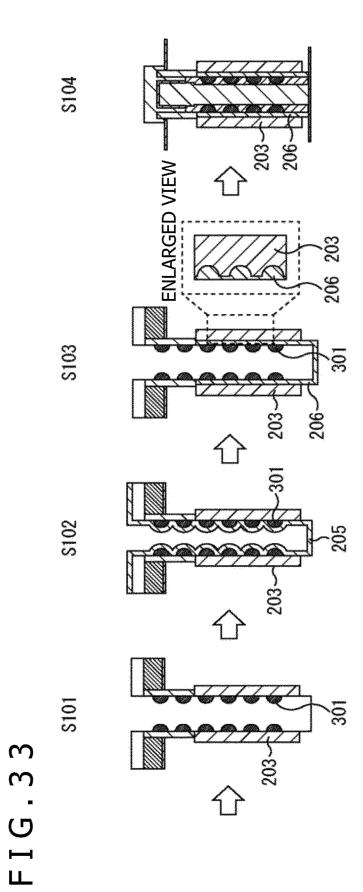

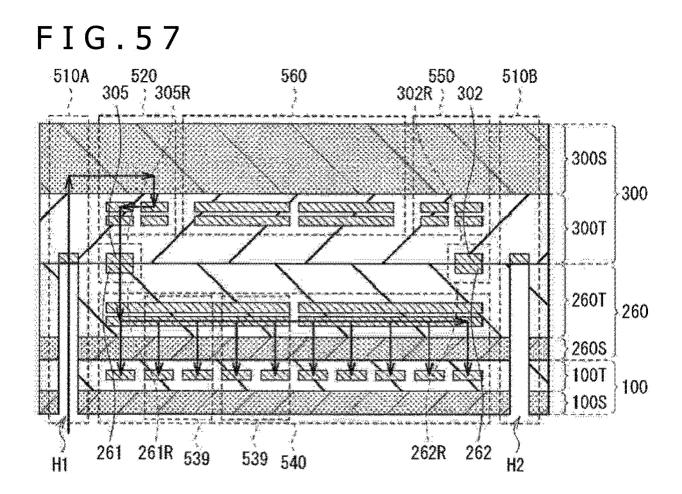

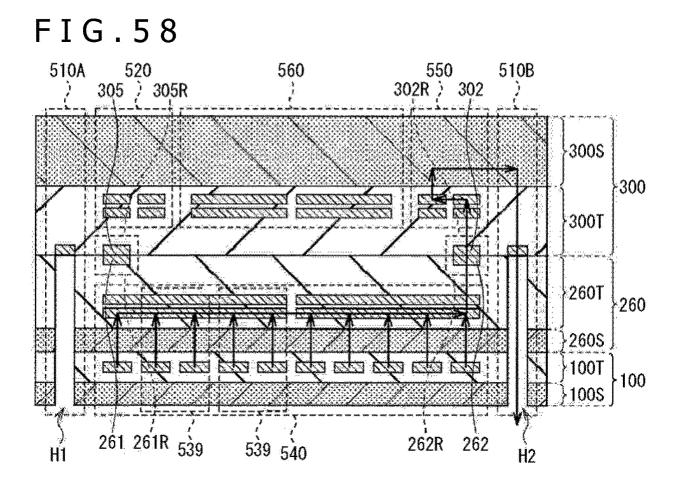

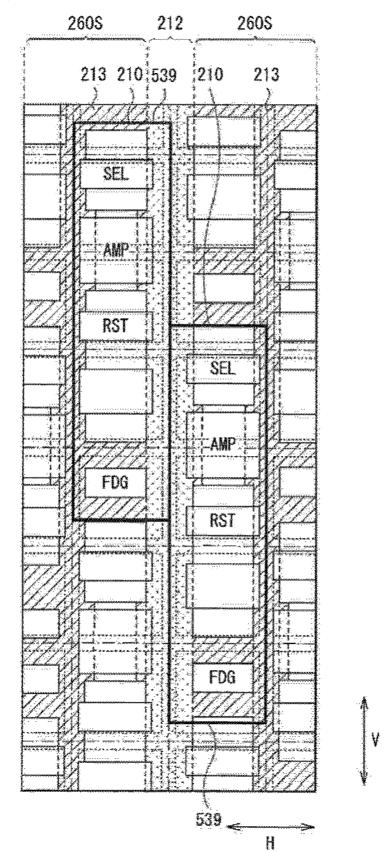

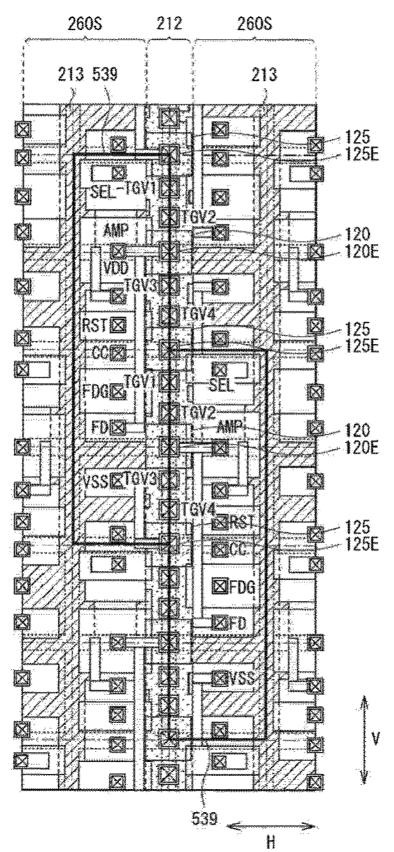

FIG. 30 is a diagram of assistance in describing the describing a general configuration of the imaging apshape of trenches resulting from etching. paratus depicted in FIG. 44. [FIG. 31] [FIG. 46] FIG. 31 is a diagram of assistance in describing the FIG. 46 is a schematic diagram illustrating a crossshape of an N-type solid phase diffusion layer result-5 sectional configuration taken along line III-III' depicting from etching. ed in FIG. 45. [FIG. 32] [FIG. 47] FIG. 32 is a plan view depicting a 17th configuration FIG. 47 is an equivalent circuit diagram of a pixel example of pixels to which the present technology sharing unit depicted in FIG. 44. is applied. 10 [FIG. 48] [FIG. 33] FIG. 48 is a diagram illustrating an example of a con-FIG. 33 is a diagram of assistance in describing mannection aspect of a plurality of pixel sharing units and ufacturing of a pixel to which the present technology a plurality of vertical signal lines. is applied. [FIG. 49] [FIG. 34] 15 FIG. 49 is a schematic cross-sectional view illustrat-FIG. 34 is a plan view depicting an 18th configuration ing an example of a specific configuration of the imexample of pixels to which the present technology aging apparatus depicted in FIG. 46. is applied. [FIG. 50] FIG. 50 is a schematic diagram illustrating an exam-[FIG. 35] ple of a planar configuration of a main part of a first FIG. 35 is a diagram of assistance in describing the 20 shape of trenches resulting from etching. substrate depicted in FIG. 49. [FIG. 36] [FIG. 51] FIG. 36 is a plan view depicting a 19th configuration FIG. 50 is a schematic diagram illustrating a planar example of pixels to which the present technology configuration of a pad portion along with the main 25 part of the first substrate depicted in FIG. 50. is applied. [FIG. 37] [FIG. 52] FIG. 37 is a plan view depicting another 19th config-FIG. 52 is a schematic diagram illustrating an examuration example of pixels to which the present techple of a planar configuration of a second substrate nology is applied. (semiconductor layer) depicted in FIG. 49. [FIG. 38] 30 [FIG. 53] FIG. 38 is a diagram of assistance in describing the FIG. 53 is a schematic diagram illustrating an examshape of trenches resulting from etching. ple of a planar configuration of main parts of pixel [FIG. 39] circuits and a first substrate along with a first inter-FIG. 39 is a plan view depicting a 20th configuration connect layer depicted in FIG. 49. example of pixels to which the present technology 35 [FIG. 54] is applied. FIG. 54 is a schematic diagram illustrating an exam-[FIG. 40] ple of a planar configuration of a first interconnect FIG. 40 depicts diagrams of assistance in describing layer and a second interconnect layer depicted in FIG. 49. effects. [FIG. 41] 40 [FIG. 55] FIG. 41 is a plan view depicting another 20th config-FIG. 55 is a schematic diagram illustrating an examuration example of a pixel to which the present techple of a planar configuration of a second interconnect nology is applied. layer and a third interconnect layer depicted in FIG. [FIG. 42] 49. FIG. 42 is a plan view depicting a 21st configuration 45 [FIG. 56] example of a pixel to which the present technology FIG. 56 is a schematic diagram illustrating an examis applied. ple of a planar configuration of a third interconnect [FIG. 43] layer and a fourth interconnect layer depicted in FIG. FIG. 43 is a cross-sectional view depicting the 21st 49. configuration example of the pixel to which the 50 [FIG. 57] present technology is applied. FIG. 57 is a schematic diagram of assistance in de-[FIG. 44] scribing a path of an input signal to the imaging ap-FIG. 44 is a block diagram of assistance in describing paratus depicted in FIG. 46. a functional configuration of an imaging apparatus [FIG. 58] 55 according to an embodiment of the present disclo-FIG. 58 is a schematic diagram of assistance in desure. scribing a signal path of a pixel signal to the imaging [FIG. 45] apparatus depicted in FIG. 46. FIG. 45 is a schematic plan view of assistance in [FIG. 59]

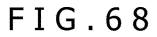

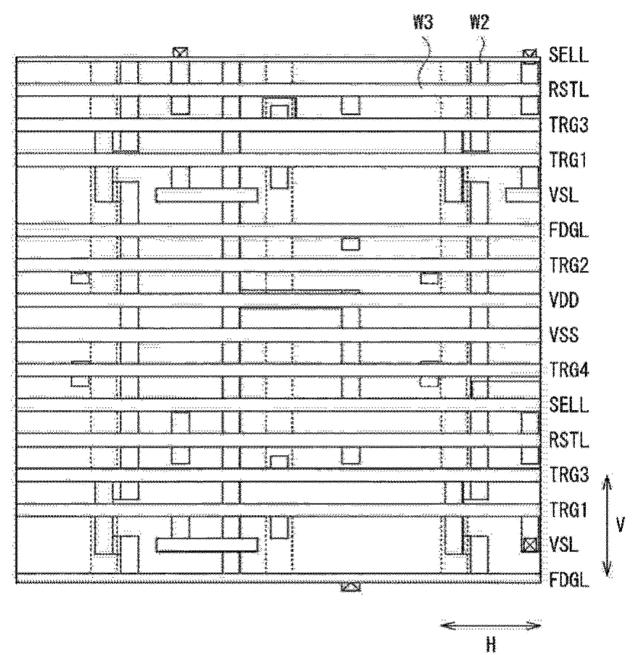

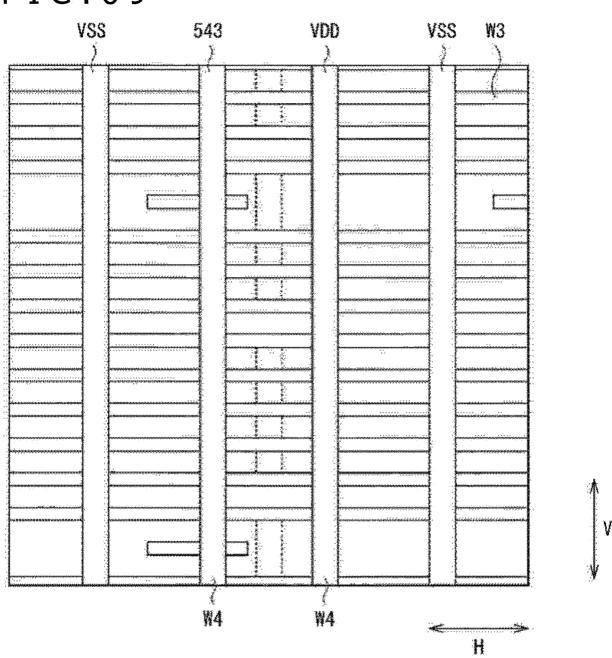

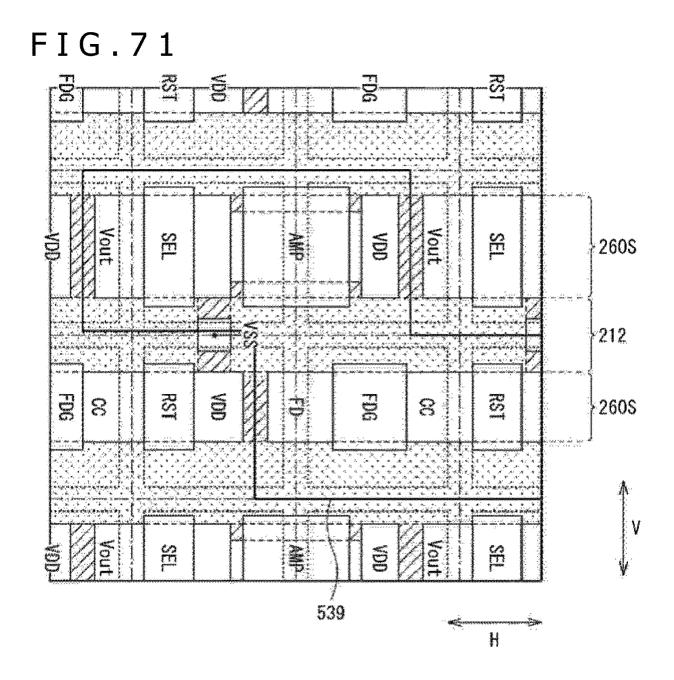

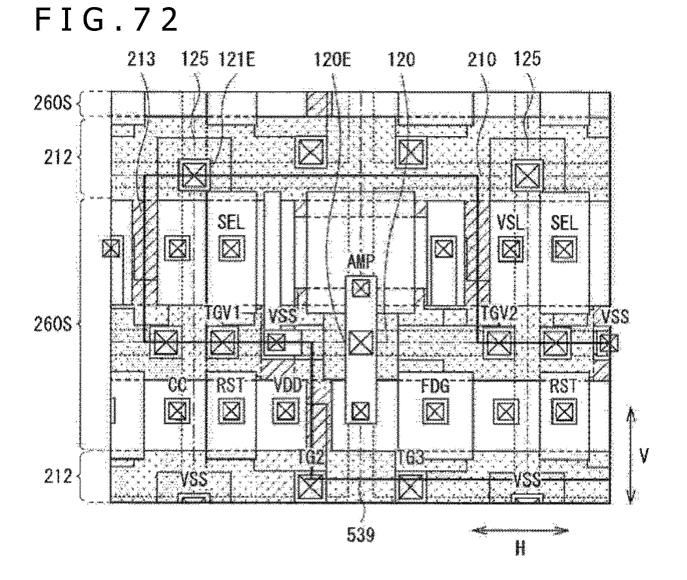

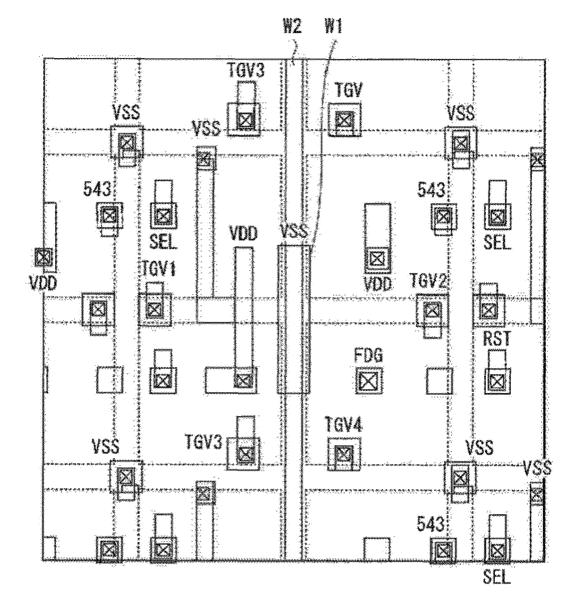

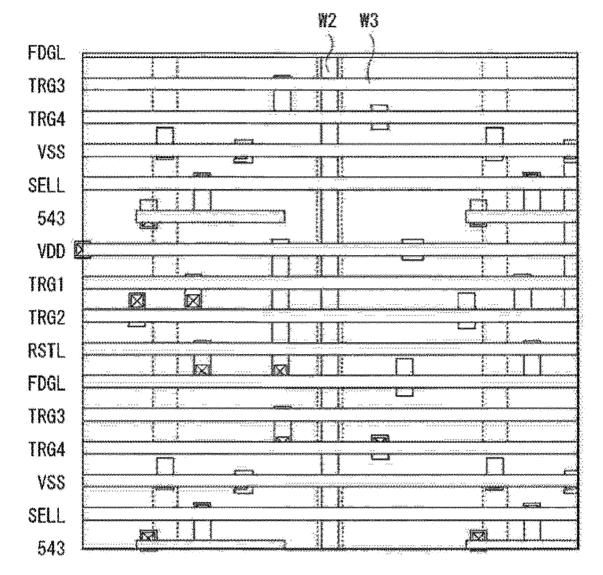

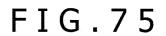

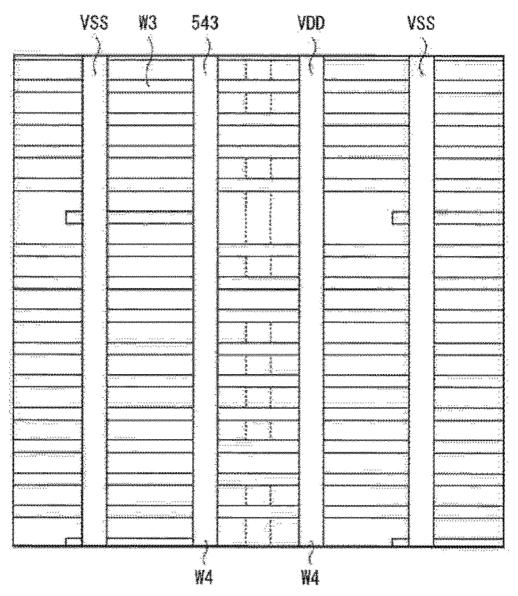

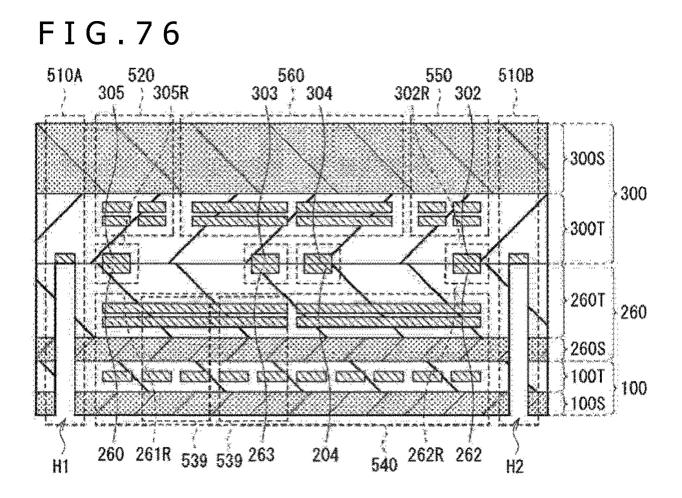

FIG. 59 is a schematic diagram illustrating a modified FIG. 72 is a schematic diagram illustrating an examexample of a planar configuration of a second subple of a planar configuration of a first interconnect strate (semiconductor layer) depicted in FIG. 52. layer along with pixel circuits depicted in FIG. 71. [FIG. 60] [FIG. 73] FIG. 73 is a schematic diagram illustrating an exam-FIG. 60 is a schematic diagram illustrating a planar 5 configuration of main parts of a first interconnect layple of a planar configuration of a second interconnect er and a first substrate along with pixel circuits delayer along with the first interconnect layer depicted picted in FIG. 59. in FIG. 72. [FIG. 61] [FIG. 74] FIG. 61 is a schematic diagram illustrating a planar 10 FIG. 74 is a schematic diagram illustrating an examconfiguration of a second interconnect layer along ple of a planar configuration of a third interconnect with the first interconnect layer depicted in FIG. 60. layer along with the second interconnect layer de-[FIG. 62] picted in FIG. 73. FIG. 62 is a schematic diagram illustrating a planar [FIG. 75] configuration of a third interconnect layer along with 15 FIG. 75 is a schematic diagram illustrating an examthe second interconnect layer depicted in FIG. 61. ple of a planar configuration of a fourth interconnect layer along with the third interconnect layer depicted [FIG. 63] FIG. 63 is a schematic diagram illustrating a planar in FIG. 74. configuration of a fourth interconnect layer along with [FIG. 76] 20 the third interconnect layer depicted in FIG. 62. FIG. 76 is a schematic cross-sectional view illustrat-[FIG. 64] ing another example of the imaging apparatus de-FIG. 64 is a schematic diagram illustrating a modified picted in FIG. 46. example of a planar configuration of the first sub-[FIG. 77] strate depicted in FIG. 50. FIG. 77 is a schematic diagram of assistance in de-25 scribing a path of an input signal to the imaging ap-[FIG. 65] FIG. 65 is a schematic diagram illustrating an examparatus depicted in FIG. 76. ple of a planar configuration of a second substrate [FIG. 78] (semiconductor layer) stacked on the first substrate FIG. 78 is a schematic diagram of assistance in describing a signal path of a pixel signal to the imaging depicted in FIG. 64. [FIG. 66] 30 apparatus depicted in FIG. 76. FIG. 66 is a schematic diagram illustrating an exam-[FIG. 79] FIG. 79 is a schematic cross-sectional view illustratple of a planar configuration of a first interconnect layer along with pixel circuits depicted in FIG. 65. ing another example of the imaging apparatus de-[FIG. 67] picted in FIG. 49. FIG. 67 is a schematic diagram illustrating an exam-35 [FIG. 80] ple of a planar configuration of a second interconnect FIG. 80 is a diagram illustrating another example of layer along with the first interconnect layer depicted an equivalent circuit depicted in FIG. 4. in FIG. 66. [FIG. 81] FIG. 81 is a schematic plan view illustrating another [FIG. 68] FIG. 68 is a schematic diagram illustrating an exam-40 example of a pixel isolation section depicted in FIG. ple of a planar configuration of a third interconnect 50 and the like. layer along with the second interconnect layer de-[FIG. 82] picted in FIG. 67. FIG. 82 is a diagram illustrating an example of a gen-[FIG. 69] eral configuration of an imaging system including an 45 imaging apparatus according to the embodiments FIG. 69 is a schematic diagram illustrating an example of a planar configuration of a fourth interconnect and the modified examples described above. layer along with the third interconnect layer depicted [FIG. 83] in FIG. 68. FIG. 83 is a diagram illustrating an example of an [FIG. 70] imaging procedure of the imaging system depicted FIG. 70 is a schematic diagram illustrating another 50 in FIG. 82. example of the planar configuration of the first sub-[FIG. 84] strate depicted in FIG. 64. FIG. 84 is a view depicting an example of a schematic configuration of an endoscopic surgery system. [FIG. 71] FIG. 71 is a schematic diagram illustrating an exam-[FIG. 85] ple of a planar configuration of a second substrate 55 FIG. 85 is a block diagram depicting an example of (semiconductor layer) stacked on the first substrate a functional configuration of a camera head and a depicted in FIG. 70. camera control unit (CCU). [FIG. 86] [FIG. 72]

30

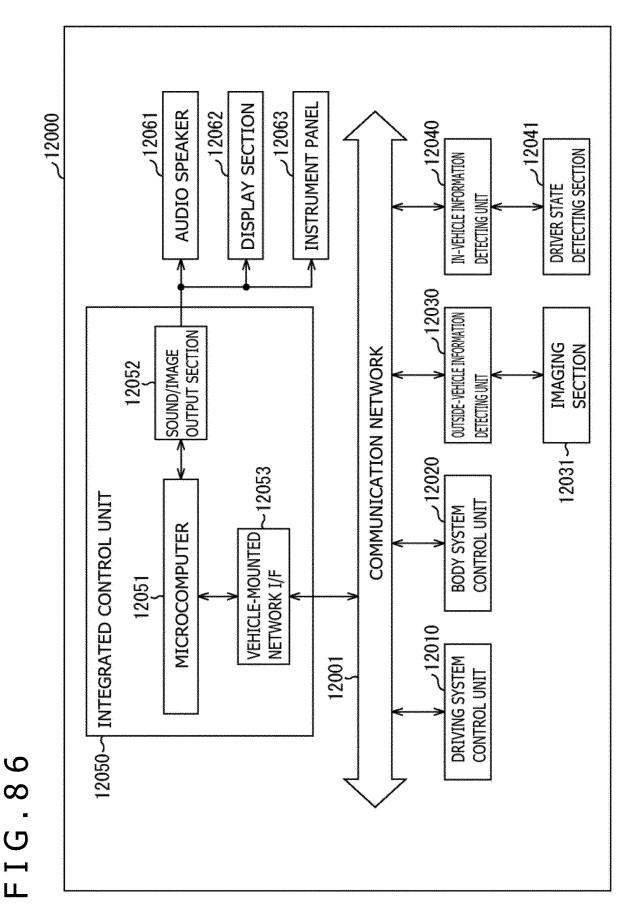

FIG. 86 is a block diagram depicting an example of schematic configuration of a vehicle control system. [FIG. 87]

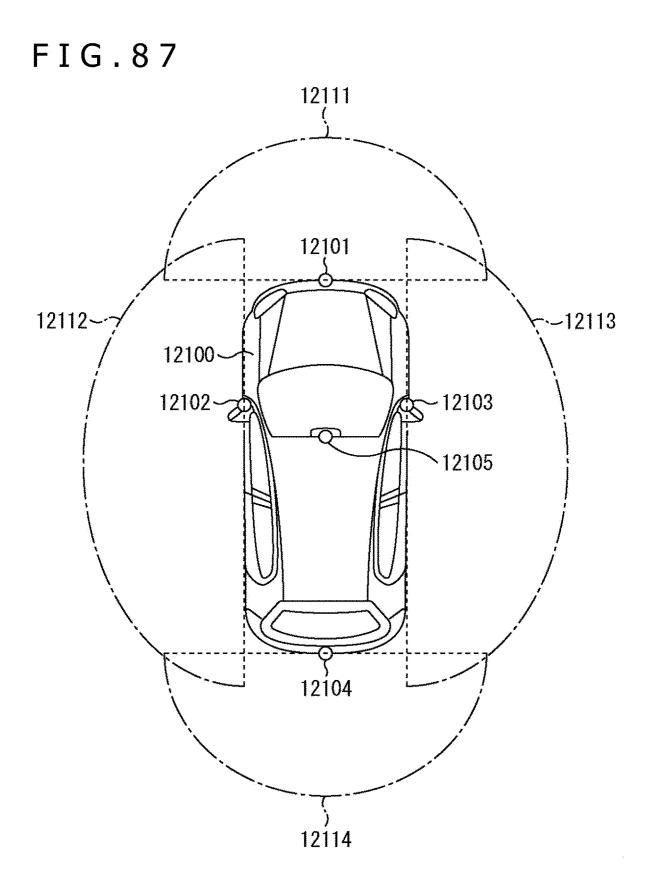

FIG. 87 is a diagram of assistance in explaining an example of installation positions of an outside-vehicle information detecting section and an imaging section.

## [Description of Embodiments]

**[0011]** Embodiments of the present technology (hereinafter referred to as embodiments) will be described below.

[0012] The present technology is applicable to an imaging apparatus, and thus the following description takes, as an example, a case where the present technology is applied to an imaging apparatus. Note that the description will be continued taking the imaging apparatus as an example but the present technology is not limited to the application to the imaging apparatus and is applicable to electronic equipment using an imaging apparatus as an image reading section (photoelectric conversion region) in general, for example, imaging apparatuses such as digital still cameras and video cameras, portable terminal apparatuses, such as cellular phones, which include an imaging function, and copiers using an imaging apparatus as an image reading section. Note that a modular configuration mounted in the electronic equipment, that is, a camera module, may be regarded as an imaging apparatus.

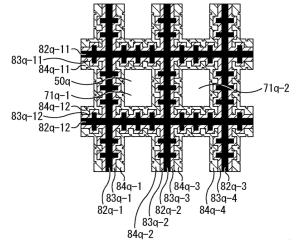

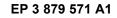

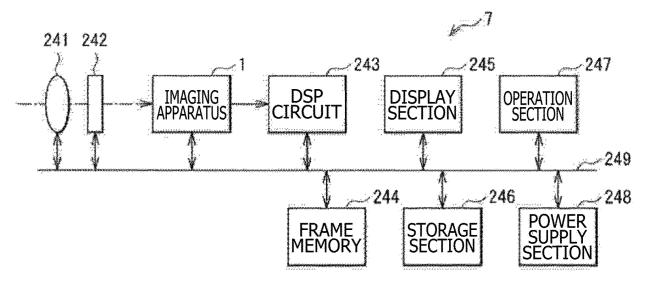

**[0013]** FIG. 1 is a block diagram depicting a configuration example of an imaging apparatus as an example of electronic equipment of the present disclosure. As depicted in FIG. 1, an imaging apparatus 10 includes an optical system including a lens group 11 and the like, an imaging element 12, a DSP circuit 13 corresponding to a camera signal processing section, a frame memory 14, a display section 15, a recording section 16, an operation system 17, a power supply system 18, and the like.

**[0014]** In addition, the imaging apparatus 10 is configured such that the DSP circuit 13, the frame memory 14, the display section 15, the recording section 16, the operation system 17, and the power supply system 18 are connected together via a bus line 19. A CPU 20 controls sections in the imaging apparatus 10.

**[0015]** The lens group 11 captures incident light (image light) from a subject and forms the light into an image on an imaging surface of the imaging element 12. The imaging element 12 converts, into an electric signal in units of pixels, the amount of incident light formed into an image on the imaging surface by the lens group 11, and outputs the electric signal as a pixel signal. As the imaging element 12, an imaging element including pixels described below (image sensor) can be used.

**[0016]** The display section 15 includes a panel display section, such as a liquid crystal display section or an organic EL (electro luminescence) display section, and displays moving images or still images captured by the im-

aging element 12. The recording section 16 records, in a recording medium such as an HDD (Hard Disk Drive) or a memory card, moving images or still images captured by the imaging element 12.

- <sup>5</sup> **[0017]** The operation system 17 provides operation commands for various functions of the imaging apparatus under the operation of a user. The power supply system 18 provides various types of power supplies used as operating power supplies for the DSP circuit 13, the frame

- memory 14, the display section 15, the recording section16, and the operation system 17, to these supply targets as appropriate.

<Configuration of Imaging Element>

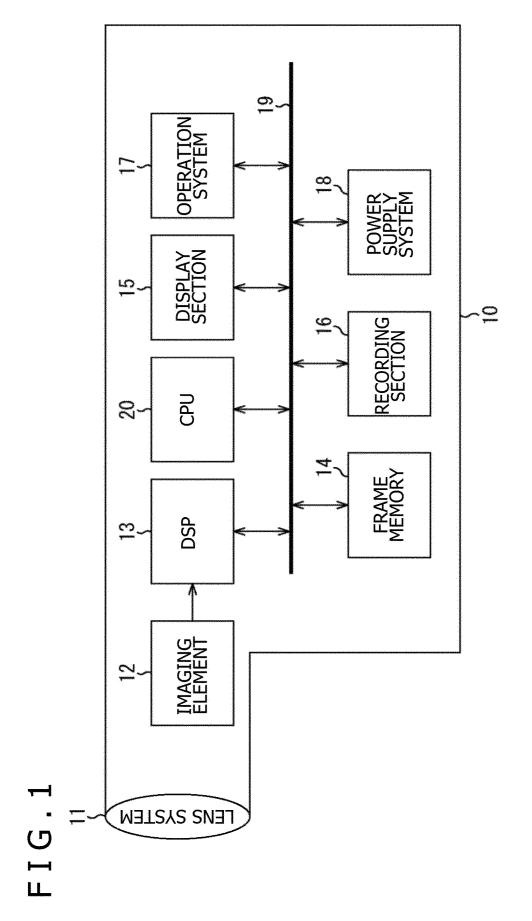

**[0018]** FIG. 2 is a block diagram depicting a configuration example of the imaging element 12. The imaging element 12 may be a CMOS (Complementary Metal Oxide Semiconductor) image sensor.

20 [0019] The imaging element 12 includes a pixel array section 41, a vertical driving section 42, a column processing section 43, a horizontal driving section 44, and a system control section 45. The pixel array section 41, the vertical driving section 42, the column processing

<sup>25</sup> section 43, the horizontal driving section 44, and the system control section 45 are formed in an unillustrated semiconductor substrate (chip).

**[0020]** The pixel array section 41 includes unit pixels (for example, a pixel 50 in FIG. 3) arranged two-dimensionally in a matrix, the unit pixels each including a photoelectric conversion element generating photocharge with an amount of charge corresponding to the amount of incident light and storing the photocharge inside. Note that the photocharge with an amount of charge corresponding to the amount of incident light and storing the photocharge corresponding to the amount of incident light and storing the photocharge inside.

<sup>35</sup> sponding to the amount of incident light is hereinafter simply referred to as a "charge" and that the unit pixel may simply be described as a "pixel."

[0021] The pixel array section 41 further includes pixel driving lines 46 formed for the respective rows of the matrix-like pixel array along the lateral direction of the figure (array direction of the pixels in pixel rows) and vertical signal lines 47 formed for the respective columns of the matrix-like pixel array along the up-down direction of the figure (array direction of the pixels in pixel columns). One

<sup>45</sup> end of each of the pixel driving lines 46 is connected to one of output ends of the vertical driving section 42 that corresponds to the row corresponding to the pixel driving line 46.

[0022] The imaging element 12 further includes a signal processing section 48 and a data storage section 49. The signal processing section 48 and the data storage section 49 may include processing executed by an external signal processing unit, for example, a DSP (Digital Signal Processor) or software, provided in a substrate

<sup>55</sup> different from a substrate in which the imaging element 12 is provided, or may be mounted on the same substrate as that in which the imaging element 12 is provided.

[0023] The vertical driving section 42 includes a shift

register, an address decoder, or the like, and simultaneously drives all the pixels in the pixel array section 41 or drives the pixels in units of rows or the like. Although a specific configuration of the vertical driving section 42 is not illustrated, the vertical driving section 42 includes a readout scanning system, a sweep-out scanning system, or batch sweep-out and batch transfer.

**[0024]** To read out signals from the unit pixels, the readout scanning system selectively scans the unit pixels in the pixel array section 41 sequentially in units of rows. In a case of row driving (rolling shutter operation), for sweep-out, sweep-out scanning is performed, earlier than readout scanning by a time corresponding to a shutter speed, on readout rows on which readout scanning is to be performed by the readout scanning system. Additionally, in a case of global exposure (global shutter operation), batch sweep-out is performed earlier than batch transfer by the time corresponding to the shutter speed.

**[0025]** The sweepout sweeps out unnecessary charge from photoelectric conversion elements in the unit pixels in the readout rows (reset). Then, sweep-out of the unnecessary charge (reset) causes what is called an electronic shutter operation to be performed. Here, the electronic shutter operation refers to an operation discarding photocharge from the photoelectric conversion elements and newly starting exposure (starting storage of photocharge).

**[0026]** Signals read out by the readout operation of the readout scanning system correspond to the amount of light having been incident since the last readout operation or electronic shutter operation. In a case of row driving, a photocharge storage period (exposure period) for the unit pixel corresponds to the period from the timing of readout by the last readout operation or the timing of sweep-out by the last electronic shutter operation. In a case of global exposure, the storage period (exposure period) corresponds to the period from batch sweep-out to batch transfer.

[0027] Pixel signals output from the unit pixels in the pixel row selectively scanned by the vertical driving section 42 are fed to the column processing section 43 through the vertical signal lines 47. The column processing section 43 executes, for each pixel column of the pixel array section 41, predetermined signal processing on the pixel signals output from the unit pixels in the selected row through the vertical signal lines 47, and temporarily holds the pixel signal subjected to the signal processing. **[0028]** Specifically, the column processing section 43 executes, as signal processing, at least noise removal processing, for example, CDS (Correlated Double Sampling). The correlated double sampling by the column processing section 43 removes pixel-specific fixed pattern noise such as reset noise and variation in threshold for amplifying transistors. Note that the column processing section 43 can be provided with, for example, an AD (Analog-Digital) conversion function, besides the noise

removal processing, to output a signal level using a digital signal.

[0029] The horizontal driving section 44 includes a shift register, an address decoder, or the like and sequentially selects unit circuits corresponding to pixel columns in the column processing section 43. The selective scanning by the horizontal driving section 44 causes the pixel signals subjected to the signal processing by the column processing section 43 to be sequentially output to the signal processing section 48.

**[0030]** The system control section 45 includes, for example, a timing generator generating various timing signals, and drives and controls the vertical driving section 42, the column processing section 43, the horizontal driv-

<sup>15</sup> ing section 44, and the like on the basis of the various timing signals generated by the timing generator.[0031] The signal processing section 48 includes at least an addition processing function to execute various

types of signal processing, such as addition processing,

on pixel signals output from the column processing section 43. The data storage section 49 temporarily stores, for signal processing in the signal processing section 48, data required for the processing.

# 25 <Structure of Unit Pixel>

30

35

**[0032]** Now, a specific structure of each of unit pixels 50 arranged in the pixel array section 41 in a matrix will be described. The pixel 50 described below can reduce the possibility that pinning on a light incidence side of an Si (silicon) substrate (in FIG. 3, an Si substrate 70) is weakened to cause charge generated to flow into a photodiode (in FIG. 3, a PD 71) to degrade the Dark property, leading to, for example, occurrence of voids or generation of a dark current.

#### <Configuration Example of Pixel in First Embodiment>

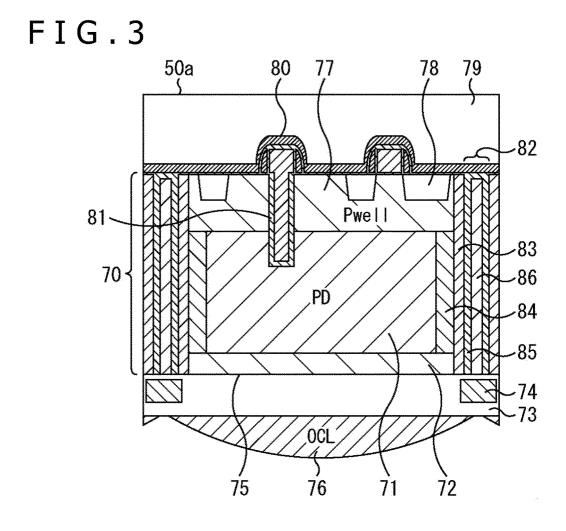

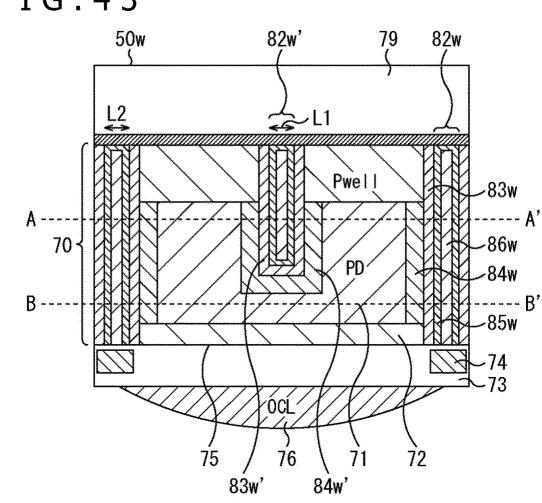

[0033] FIG. 3 is a vertical cross-sectional view of a pixel

50a in a first embodiment of the pixel 50 to which the present technology is applied, and FIG. 4 is a plan view of a front side of the pixel 50a. Note that FIG. 3 corresponds to the position of a segment X-X' in FIG. 4.

[0034] The pixel 50 will be described below taking, as

<sup>45</sup> an example, a configuration in which the pixel 50 is of a back-illuminated type. However, the present technology can also be applied to a front-illuminated type.

**[0035]** The pixel 50 depicted in FIG. 3 includes a PD (photodiode) 71 used as a photoelectric conversion element in each of the pixels formed inside the Si substrate 70. A P-type region 72 is formed on a light incidence side of the PD 71 (in the figure, a lower side corresponding to a back side), and a planarization film 73 is further

formed below the P-type region 72. The boundary between the P-type region 72 and the planarization film 73 corresponds to a back side Si interface 75.

**[0036]** Light shielding films 74 are formed in the planarization film 73. The light shielding films 74 are pro-

vided to prevent light from leaking into adjacent pixels and are formed between the adjacent PDs 71. The light shielding films 74 include a metal material, for example, W (tungsten).

**[0037]** An OCL (On Chip Lens) 76 focusing incident light on the PD 71 is formed on the planarization film 73 and thus on the back side of the Si substrate 70. The OCL 76 may include an inorganic material, and for example, SiN, SiO, or SiOxNy (provided,  $0 < x \le 1$  and  $0 < y \le 1$ ) can be used as the inorganic material.

**[0038]** Although not depicted in FIG. 3, the pixel can be configured such that a transparent plate such as cover glass or resin is bonded onto the OCL 76. Additionally, although not depicted in FIG. 3, the pixel may be configured such that a color filter layer is formed between the OCL 76 and the planarization film 73. In addition, the pixel can be configured such that, in the color filter layer, a plurality of color filters are provided in each pixel and such that the colors of the color filers are, for example, arranged according to a Bayer arrangement.

[0039] An active region (Pwell) 77 is formed opposite to the light incidence side of the PD 71 (in the figure, an upper side corresponding to the front side). Element isolation regions (hereinafter referred to as STI (Shallow Trench Isolation)) 78 isolating pixel transistors and the like from one another are formed in the active region 77. [0040] An interconnect layer 79 is formed on the front side of the Si substrate 70 (in the drawing, the upper side) and thus on the active region 77, and a plurality of transistors are formed in the interconnect layer 79. FIG. 3 depicts an example in which transfer transistors 80 are formed in the interconnect layer 79. The transfer transistors (gates) 80 include vertical transistors. Specifically, for the transfer transistors (gates) 80, a vertical transistor trench 81 is formed, and then a transfer gate (TG) 80 for reading out charge from the PD 71 is formed at the vertical transistor trench 81.

**[0041]** Further, pixel transistors such as an amplifying (AMP) transistor, a select (SEL) transistor, and a reset (RST) transistor are formed on the front side of the Si substrate 70. The arrangement of the transistors will be described with reference to FIG. 4, and operations of the transistors will be described with reference to a circuit diagram in FIG. 5.

**[0042]** A trench is formed between the pixels 50a and is described as DTI (Deep Trench Isolation) 82. The DTI 82 is formed between the adjacent pixels 50a and is shaped to penetrate the Si substrate 70 in a depth direction (in the figure, the vertical direction corresponding to a direction from the front surface to the back surface). Additionally, the DTI 82 also functions as a light shielding wall between the pixels to prevent unnecessary light from leaking to the adjacent pixels 50a.

**[0043]** Between the PD 71 and the DTI 82, a P-type solid phase diffusion layer 83 and an N-type solid phase diffusion layer 84 are formed in this order from the DTI 82 side toward the PD 71. The P-type solid phase diffusion layer 83 is formed to extend along the DTI 82 until

coming into contact with the back side Si interface 75 of the Si substrate 70. The N-type solid phase diffusion layer 84 is formed to extend along the DTI 82 until coming into contact with the P-type region 72 of the Si substrate 70.

<sup>5</sup> [0044] Note that the solid phase diffusion layers refer to layers formed in accordance with a manufacturing method described below and used to form a P-type layer and an N-type layer by impurity doping but the present technology is not limited to the manufacturing method

<sup>10</sup> based on solid phase diffusion and a P type layer and an N type layer generated in accordance with another manufacturing method such as ion injection may each be provided between the DTI 82 and the PD 71. Additionally, the PD 71 in the embodiment includes an N-type region.

<sup>15</sup> Photoelectric conversion is performed in some or all of the N-type regions.

**[0045]** The P-type solid phase diffusion layer 83 is formed to extend until coming into contact with the back side Si interface 75, whereas the N-type solid phase dif-

<sup>20</sup> fusion layer 84 does not contact the back side Si interface 75, with a space provided between the N-type solid phase diffusion layer 84 and the back side Si interface 75.

[0046] In such a configuration, a PN junction region between the P-type solid phase diffusion layer 83 and

the N-type solid phase diffusion layer 84 forms an intense electric field region to hold charge generated by the PD 71. According to such a configuration, the P-type solid phase diffusion layer 83 and the N-type solid phase diffusion layer 84 formed along the DTI 82 can form an

intense electric field region to hold charge generated by the PD 71.

**[0047]** If the N-type solid phase diffusion layer 84 is formed to extend along the DTI 82 until coming into contact with the back side Si interface 75 of the Si substrate 70, pinning of charge is weakened in a portion in which the N-type solid phase diffusion layer 84 contacts the back side Si interface 75 of the Si substrate 70 corre-

sponding to the light incidence surface side, and charge generated flows into the PD 71 to degrade the Dark property, leading to, for example, occurrence of voids and

erty, leading to, for example, occurrence of voids and generation of a dark current.[0048] However, the pixel 50a depicted in FIG. 3 is

configured such that the N-type solid phase diffusion layer 84 does not contact the back side Si interface 75 of

<sup>45</sup> the Si substrate 70 but contacts the P-type region 72 of the Si substrate 70 along the DTI 82. Such a configuration allows prevention of weakening of pinning of charge, enabling prevention of flow of the charge into the PD 71 that would otherwise degrade the Dark property.

50 [0049] Additionally, in the pixel 50a depicted in FIG. 3, a side wall film 85 including SiO2 is formed on an inner wall of the DTI 82, and a filler 86 including polysilicon is embedded inside the side wall film 85.

[0050] The pixel 50a in the first embodiment is configured such that the P-type region 72 is provided on the back side, precluding the PD 71 and the N-type solid phase diffusion layer 84 from being present near the back side Si interface 75. This prevents weakening of pinning

near the back side Si interface 75, allowing generated charge to be inhibited from flowing into the PD 71 to degrade the Dark property.

**[0051]** Note that, instead of SiO2 adopted for the side wall film 85, SiN may be used for the DTI 82. Additionally, instead of polysilicon adopted for the filler 86, doping polysilicon may be used. In a case where the DTI 82 is filled with doping polysilicon or is doped with N-type impurities or P-type impurities after being filled with polysilicon, application of a negative bias to the DTI 82 allows enhancing of the pinning on the side wall of the DTI 82, enabling the Dark property to be further improved.

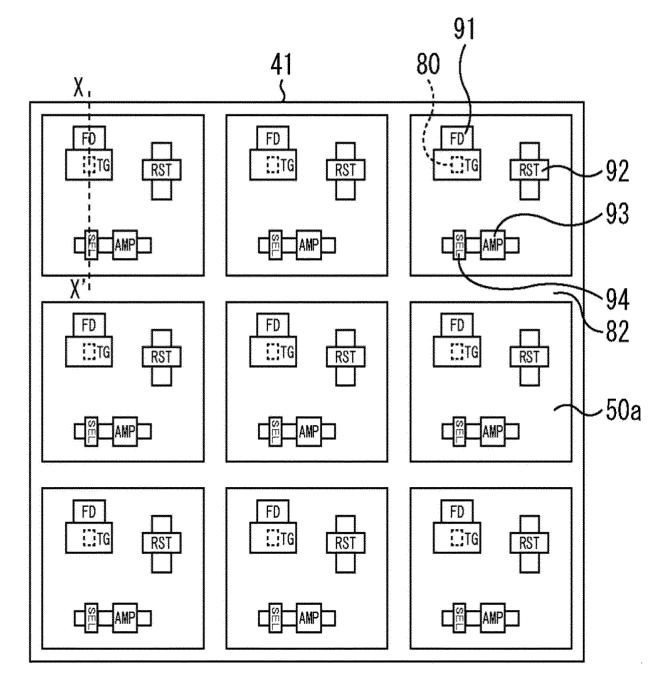

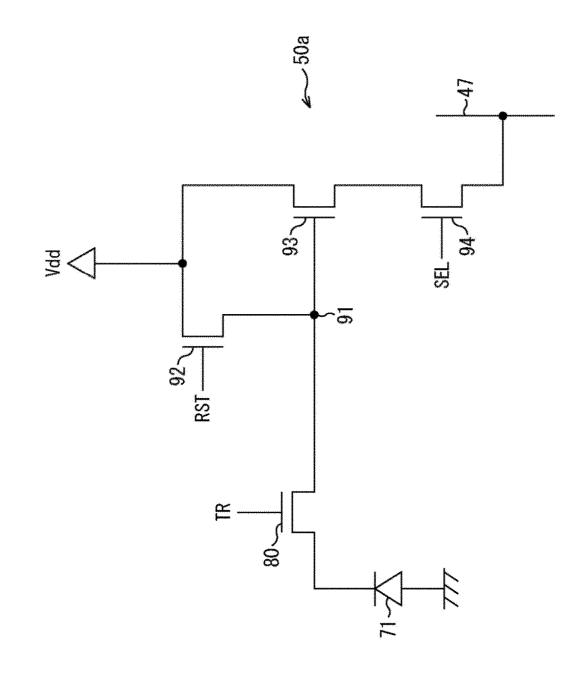

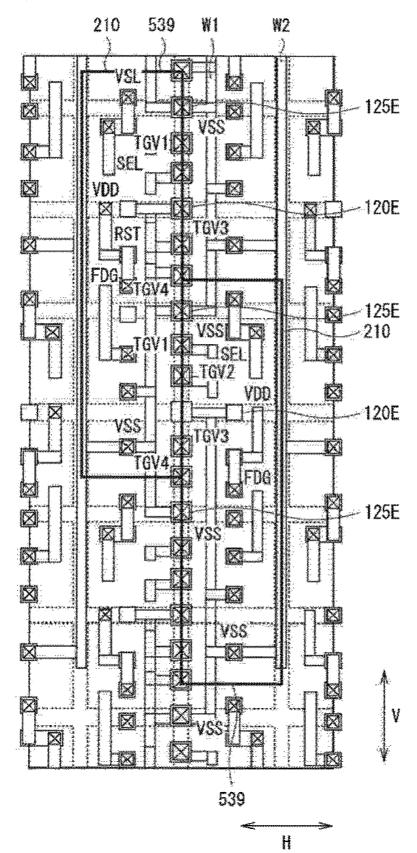

**[0052]** With reference to FIG. 4 and FIG. 5, the arrangement of the transistors formed in the pixel 50a and the operations of the transistors will be described. FIG. 4 is a plan view of  $3 \times 3 = 9$  pixels 50a arranged in the pixel array section 41 (FIG. 2) as viewed from the front side (in FIG. 3, from the upper side). FIG. 5 is a circuit diagram of assistance in describing a connection relation among the transistors depicted in FIG. 4.

**[0053]** In FIG. 4, one rectangle represents one pixel 50a. As depicted in FIG. 4, the DTI 82 is formed to enclose the pixel 50a (PD 71 included in the pixel 50a). Additionally, transfer transistors (gates) 80, FD (floating diffusion) 91, reset transistors 92, amplifying transistors 93, and select transistors 94 are formed on the front side of the pixel 50a.

**[0054]** The PD 71 generates and stores charge (signal charge) corresponding to the amount of light received. The PD 71 includes an anode terminal grounded and a cathode terminal connected to the FD 91 via the transfer transistor (gate) 80.

**[0055]** When turned on by a transfer signal TR, the transfer transistor 80 reads out charge generated by the PD 71 and transfers the charge to the FD 91.

**[0056]** The FD 91 holds the charge read out from the PD 71. When the reset transistor 92 is turned on by a reset signal RST, the charge stored in the FD 91 is discharged to a drain (constant voltage source Vdd) to reset the potential of the FD 91.

**[0057]** The amplifying transistor 93 outputs a pixel signal corresponding to the potential of the FD 91. Specifically, the amplifying transistor 93 constitutes a source follower circuit along with a load MOS (not depicted) connected to the amplifying transistor 93 via a vertical signal line 33 and used as a constant current source. A pixel signal indicating a level corresponding to the charge stored in the FD 91 is output from the amplifying transistor 93 to the column processing section 43 (FIG. 2) via the select transistor 94 and the vertical signal line 47.

**[0058]** The select transistor 94 is turned on when a pixel 31 is selected by a select signal SEL, and outputs a pixel signal from the pixel 31 to the column processing section 43 via the vertical signal line 33. Signal lines through which the transfer signal TR, the select signal SEL, and the reset signal RST are transmitted correspond to the pixel driving lines 46 in FIG. 2.

**[0059]** The pixel 50a can be configured as described

above. However, the pixel 50a is not limited to this configuration, and another configuration can be adopted.

<Method for Manufacturing DTI 82 and Peripheral Regions>

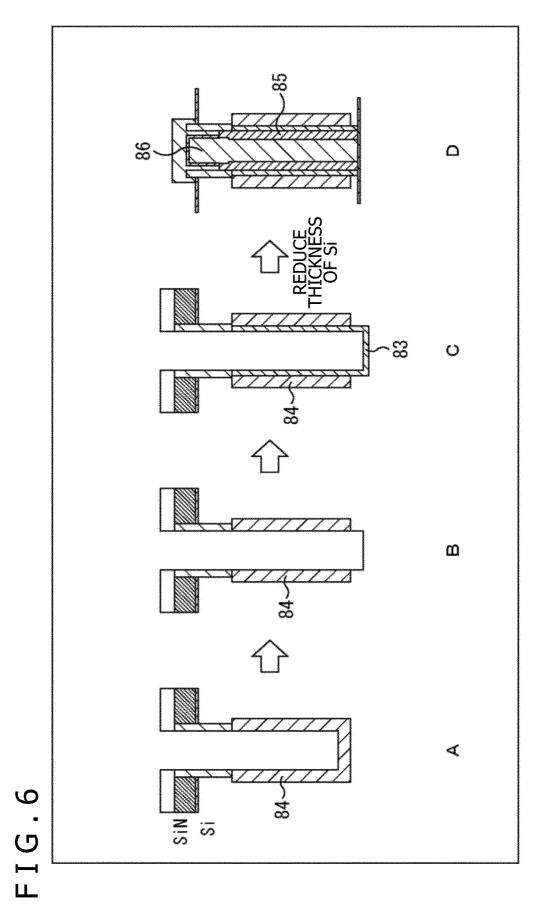

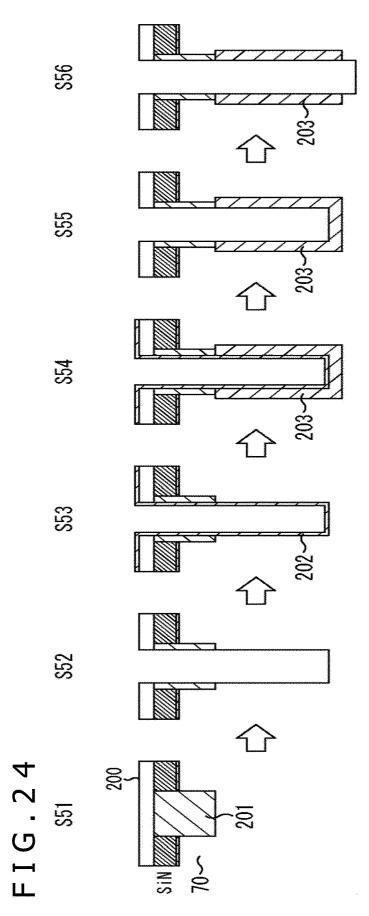

**[0060]** FIG. 6 is a diagram of assistance in describing a method for manufacturing the DTI 82 and peripheral regions.

10 [0061] When the DTI 82 is formed in the Si substrate 70, the entire Si substrate 70 except for the position where the DTI 82 is to be formed is covered with a hard mask including SiN and SiO2, and the portion not covered with the hard mask is dry etched to form a trench extend-

<sup>15</sup> ing through the Si substrate 70 in the vertical direction down to a predetermined depth, as depicted in A of FIG. 6.

[0062] Then, an SiO2 film including P (phosphorous) corresponding to N-type impurities is formed inside the trench formed, and is thermally treated to dope the Si

<sup>20</sup> substrate 70 with P (phosphorous) from the SiO2 film

<sup>20</sup> substrate 70 with P (phosphorous) from the SiO2 film (the doping is hereinafter referred to as solid phase diffusion).

**[0063]** Then, as depicted in B of FIG. 6, the SiO2 film that is formed inside the trench formed and that includes

P is removed, and thermal treatment is executed again to diffuse P (phosphorous) into the Si substrate 70 and thereby form an N-type solid phase diffusion layer 84 self-aligned with the current shape of the trench. Subsequently, a bottom portion of the trench is etched by dry

etching to extend the trench in the depth direction.

**[0064]** Then, as depicted in C of FIG. 6, an SiO2 film including B (boron) corresponding to P-type impurities is formed inside the extended trench and thermally treated to cause solid phase diffusion to diffuse B (boron) from the SiO2 film toward the Si substrate 70 side. According-

<sup>35</sup> the SiO2 film toward the Si substrate 70 side. Accordingly, formed is a P-type solid phase diffusion layer 83 that is self-aligned with the shape of the extended trench. [0065] Subsequently, the SiO2 films that are formed on the inner walls of the trench and that include B (boron)

40 are removed.

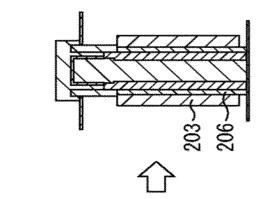

**[0066]** Then, as depicted in D of FIG. 6, a side wall film 85 including SiO2 is formed on the inner wall of the trench formed, and the trench is filled with polysilicon to form DTI 82. Subsequently, pixel transistors and intercon-

<sup>45</sup> nects are formed. Then, the Si substrate 70 is thinned from the back side. During the thinning, including the P-type solid phase diffusion layer 83, the bottom portion of the DTI 82 is simultaneously thinned. The thinning is performed up to a depth not reaching the N-type solid phase

<sup>50</sup> diffusion layer 84.

**[0067]** The above-described process allows an intense electric field region to be formed adjacent to PD 71, the intense electric field region including the N-type solid phase diffusion layer 84 not in contact with the back side Si interface 75 and the P-type solid phase diffusion layer 83 in contact with the back side Si interface 75.

<Second Embodiment>

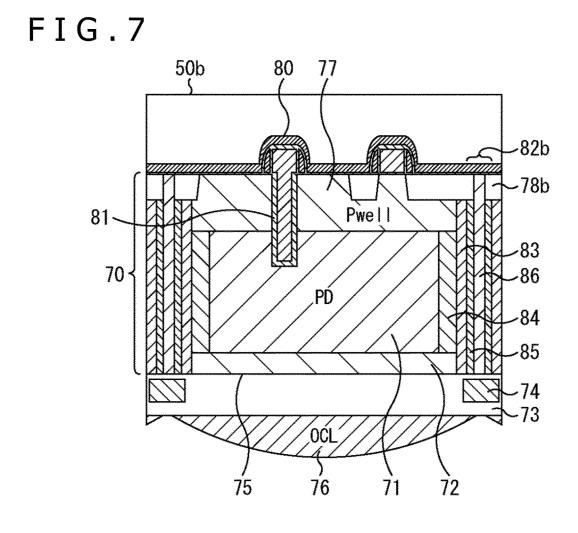

**[0068]** FIG. 7 is a vertical cross-sectional view of a pixel 50b in a second embodiment to which the present technology is applied.

**[0069]** The second embodiment differs from the first embodiment in that the DTI 82 is formed in the STI 78, but is otherwise similar to the first embodiment. Similar components of the embodiments are denoted by the same reference signs, and description of such components is omitted as appropriate. In the description below of the pixel 50, the same components as those of the pixel 50b in the first embodiment are denoted by the same reference signs, and description of the components is omitted as appropriate.

**[0070]** In the pixel 50b depicted in FIG. 7, STI 78b formed in the active region 77 is formed to extend to a portion in which the DTI 82b is formed (extend to an end of the pixel 50b). In addition, the DTI 82b is formed below the STI 78b.

**[0071]** In other words, the STI 78b is formed at the portion in which the DTI 82b is formed, and the STI 78b and the DTI 82b are formed at a position where the STI 78b and the DTI 82b contact each other.

**[0072]** Such formation enables the pixel 50b to be made smaller as compared to the configuration where the STI 78b and the DTI 82b are formed at different positions (for example, the pixel 50a in the first embodiment (FIG. 3)).

**[0073]** Additionally, the pixel 50b in the second embodiment can also produce an effect similar to the effect of the pixel 50a, that is, the effect of enabling prevention of degradation of the Dark property.

<Third Embodiment>

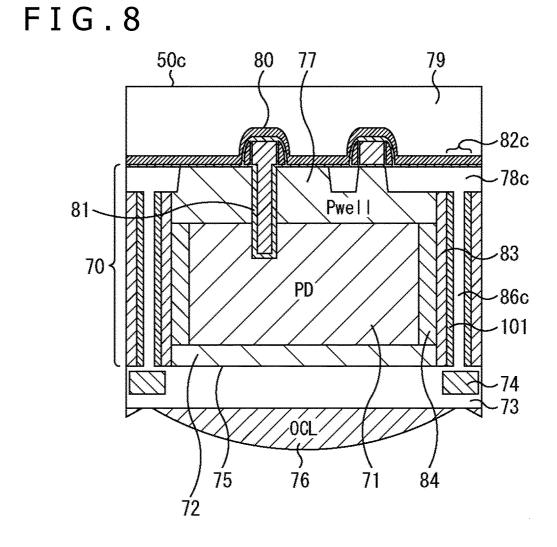

**[0074]** FIG. 8 is a vertical cross-sectional view of a pixel 50c in a third embodiment to which the present technology is applied.

**[0075]** A pixel in the third embodiment differs from the pixel 50a and the pixel 50b in the first and second embodiments in that a film 101 with a negative fixed charge is formed on a side wall of DTI 82c and that the inside of the film 101 is filled with SiO2 as a filler 86c.

**[0076]** The pixel 50a in the first embodiment is configured such that the side wall film 85 of SiO2 is formed on the side wall of the DTI 82 which is filled with polysilicon, whereas, in the pixel 50c in the third embodiment, the film 101 with the negative fixed charge is formed on the side wall of the DTI 82c, with the inside of the film 101 filled with SiO2.

**[0077]** The film 101 that is formed on the side wall of the DTI 82c and that has the negative fixed charge may include, for example, a hafnium oxide (HfO2) film, an aluminum oxide (Al2O3) film, a zirconium oxide (ZrO2) film, a tantalum oxide (Ta2O5) film, or a titanium oxide (TiO2) film. The above-described types of films have successfully been used as gate insulating films in insulated-

gate field effect transistors. Thus, film formation methods have been established, allowing easy film formation.

**[0078]** Examples of the film formation method include chemical vapor deposition, sputtering, and atomic layer

<sup>5</sup> deposition, and the atomic layer deposition is suitably used because this method allows an SiO2 layer reducing an interface state to be simultaneously formed to a thickness of approximately 1 nm during film formation.

[0079] Additionally, materials other than those listed

above include lanthanum oxide (La2O3), praseodymium oxide (Pr2O3), cerium oxide (CeO2), neodymium oxide (Nd2O3), promethium oxide (Pm2O3), samarium oxide (Sm2O3), europium oxide (Eu2O3), gadolinium oxide (Gd2O3), terbium oxide (Tb2O3), dysprosium oxide

<sup>15</sup> (Dy2O3), holmium oxide (Ho2O3), erbium oxide (Er2O3), thulium oxide (Tm2O3), ytterbium oxide (Yb2O3), lutetium oxide (Lu2O3), yttrium oxide (Y2O3), and the like.

**[0080]** Further, the film 101 with the negative fixed charge may include a hafnium nitride film, an aluminum nitride film, a hafnium oxynitride film, or an aluminum oxynitride film.

**[0081]** The film 101 with the negative fixed charge may include silicon (Si) or nitrogen (N) added into the film to the extent that the insulation property is not impaired.

The concentration of silicon or nitrogen is determined as appropriate to the extent that the insulation property is not impaired. However, for prevention of image defects such as voids, additives such as the silicon and nitrogen described above are preferably added to a front surface

of the film 101 with the negative fixed charge, that is, the surface of the film 101 opposite to the PD 71 side. As described above, addition of silicon (Si) or nitrogen (N) enables improvement of heat resistance of the film and <sup>35</sup> the capability of inhibiting ion injection during the process.

the capability of inhibiting ion injection during the process.

[0082] In the third embodiment, pinning of the trench side wall of the DTI 82 can be enhanced. Accordingly, for example, compared to the pixel 50a in the first embodiment, the pixel 50c enables the Dark property to be

reliably prevented from being degraded.

**[0083]** For formation of the DTI 82 in the third embodiment, in a state depicted in D of FIG. 6, the back side may be polished until the polysilicon provided as the filler 86 is exposed. Then, the filler 86 (polysilicon) inside the

<sup>45</sup> trench and the side wall film 85 (SiO2) may be removed using photoresist and wet etching, the film 101 may be formed, and the trench may be filled with SiO2.

$[0084] \qquad \hbox{Note that, instead of SiO2, a metal material such} as W (tungsten) may be used to fill the inside of the trench.$

This reduces the light transmission, through the DTI 82, of incident light traveling in an oblique direction, allowing color mixing to be reduced.

<Fourth Embodiment>

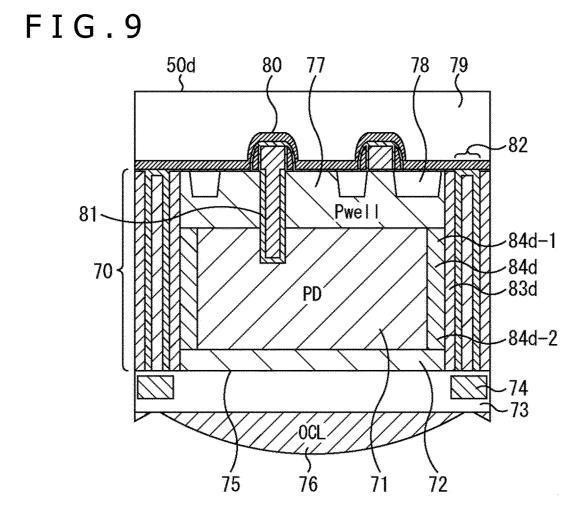

**[0085]** FIG. 9 is a vertical cross-sectional view of a pixel 50d in a fourth embodiment to which the present technology is applied.

50

[0086] The fourth embodiment differs from the first embodiment in that an N-type solid phase diffusion layer 84d formed along the DTI 82 has a concentration gradient in the depth direction of the Si substrate 70, but the pixel in the fourth embodiment is otherwise similar to the pixel 50a in the first embodiment.

[0087] The N-type impurities in the N-type solid phase diffusion layer 84 in the pixel 50a in the first embodiment have a constant concentration regardless of the depth direction, whereas N-type impurities in an N-type solid phase diffusion layer 84d of a pixel 50d in the fourth embodiment have a concentration depending on the depth direction.

[0088] Specifically, an N-type solid phase diffusion layer 84d-1 close to a front side of the N-type solid phase diffusion layer 84d in the pixel 50d has a high concentration of N-type impurities, whereas an N-type solid phase diffusion layer 84d-2 close to a back side of the N-type solid phase diffusion layer 84d has a low concentration of N-type impurities.

[0089] In addition to producing an effect similar to the effect of the pixel 50a in the first embodiment, the pixel 50d in the fourth embodiment can exert a new effect of allowing facilitation of readout of charge as a result of a shallow potential on the back side resulting from the concentration gradient provided in the N-type solid phase diffusion layer 84d.

[0090] The concentration gradient can be provided in the N-type solid phase diffusion layer 84d as follows. For example, when the trench of the DTI 82 is formed, etching damage is caused to the side wall of the trench, and thus a variation in solid phase diffusion doping level depending on the amount of the damage can be used to provide the concentration gradient.

[0091] Note that, instead of the N-type solid phase diffusion layer 84d being provided with the concentration gradient, the P-type solid phase diffusion layer 83d close to the front side may have a reduced concentration of Ptype impurities, whereas the P-type solid phase diffusion layer 83d close to the back side may have an increased concentration of P-type impurities. Even in this case, an effect similar to the effect of providing the concentration gradient in the N-type solid phase diffusion layer 84d can be produced.

[0092] Additionally, both the N-type solid phase diffusion layer 84d and the P-type solid phase diffusion layer 83d may be provided with the respective concentration gradients.

# <Fifth Embodiment>

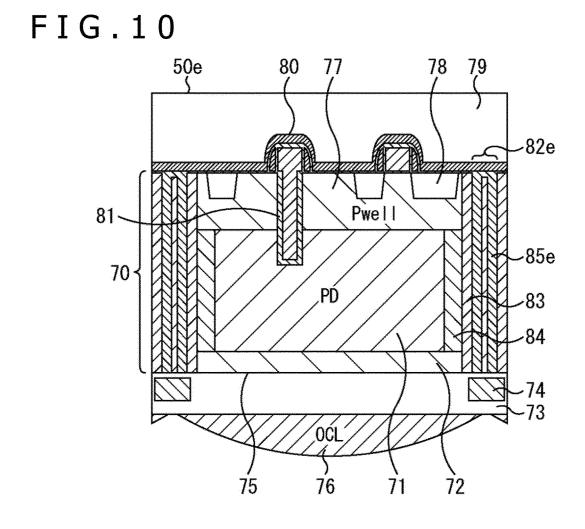

[0093] FIG. 10 is a vertical cross-sectional view of a pixel 50e in a fifth embodiment to which the present technology is applied.

**[0094]** The pixel 50e in the fifth embodiment differs from the pixel 50a in the first embodiment in that a side wall film 85e that is formed on an inner wall of DTI 82e and that includes SiO2 is thicker than the side wall film

85 in the pixel 50e in the first embodiment, but the pixel 50e in the fifth embodiment is otherwise similar to the pixel 50a in the first embodiment.

[0095] SiO2 has a lower refractive index than Si, and 5 thus incident light entering the Si substrate 70 is reflected in accordance with the Snell's law, reducing transmittance of light to the adjacent pixels 50. However, a reduced thickness of the side wall film 85 may prevent the Snell's law from being completely established, leading 10 to an increased amount of transmitted light.

[0096] The increased film thickness of the side wall film 85e formed in the pixel 50e in the fifth embodiment enables a reduction in deviation from the Snell's law, allowing for an increase in reflection of incident light at the side

15 wall film 85e to reduce transmission of the light to the adjacent pixel 50e. Accordingly, in addition to producing an effect similar to the effect of the pixel 50a in the first embodiment, the pixel 50e in the fifth embodiment can exert an effect of allowing inhibition of color mixing into 20 the adjacent pixels 50e caused by oblique incident light.

<Sixth Embodiment>

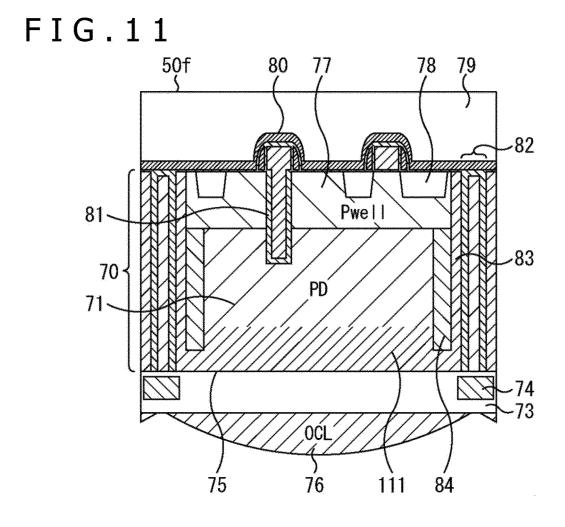

[0097] FIG. 11 is a vertical cross-sectional view of a 25 pixel 50f in a sixth embodiment to which the present technology is applied.

[0098] The pixel 50f in the sixth embodiment differs from the pixel 50a in the first embodiment in that a region 111 between the PD 71 and the back side Si interface

30 75 is doped with P-type impurities to provide a concentration gradient such that the concentration of the P-type impurities in the Si substrate 70 is higher on the front side than on the back side, but the pixel 50f in the sixth embodiment is otherwise similar to the pixel 50a in the first 35 embodiment.

[0099] Referring back to FIG. 3, the pixel 50a of the first embodiment has no concentration gradient in the Si substrate 70 and includes the P-type region 72 between the Si substrate 70 and the back side Si interface 75. In

- 40 the pixel 50f in the sixth embodiment, the Si substrate 70 is provided with a concentration gradient. The concentration gradient is such that the concentration of the Ptype impurities is higher on the back side (P-type region 111 side) than on the front side.

- 45 [0100] In addition to producing an effect similar to the effect of the pixel 50a in the first embodiment, the pixel 50f in the sixth embodiment having the concentration gradient as described above can exert a further effect of allowing charge to be read out more easily as compared to the pixel 50a in the first embodiment.

<Seventh Embodiment>

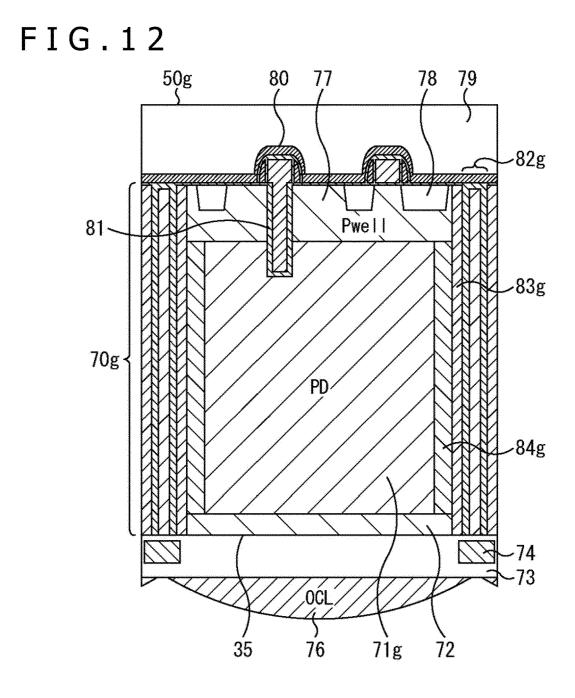

[0101] FIG. 12 is a vertical cross-sectional view of a 55 pixel 50g in a seventh embodiment to which the present technology is applied.

[0102] The pixel 50g in the seventh embodiment differs from the pixel 50a in the first embodiment in that the Si

substrate 70 is thicker in the pixel 50g than in the pixel 50a and that the increased thickness of the Si substrate 70 increases the depths of the DTI 82 and the like formed in the pixel 50g.

**[0103]** An Si substrate 70g formed in the pixel 50g in the seventh embodiment has an increased thickness. The increased thickness of the Si substrate 70g increases the area (volume) of a PD 71g and the depth of DTI 82g. Additionally, formation of the DTI 82g with the increased depth leads to formation of a P-type solid phase diffusion layer 83g and an N-type solid phase diffusion layer 84g both having an increased depth (increased area).

**[0104]** The increased areas of the P-type solid phase diffusion layer 83g and the N-type solid phase diffusion layer 84g increase the area of the PN junction region including the P-type solid phase diffusion layer 83g and the N-type solid phase diffusion layer 84g. Consequently, in addition to producing an effect similar to the effect of the pixel 50a in the first embodiment, the pixel 50g in the seventh embodiment can further increase the amount of saturated charge Qs compared to the pixel 50a in the first embodiment.

## <Eighth Embodiment>

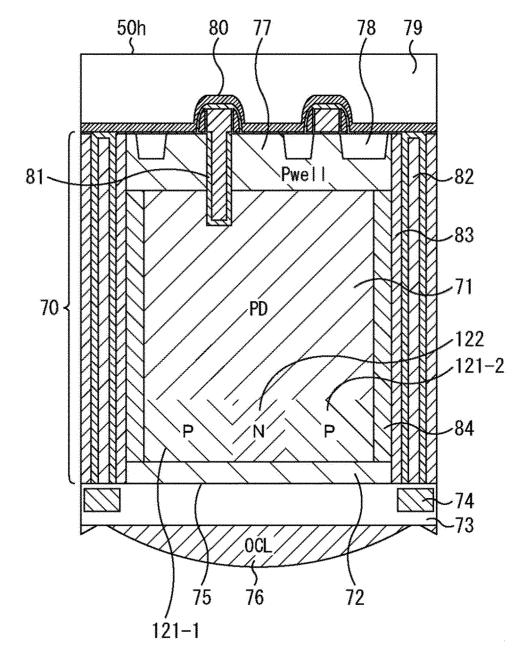

**[0105]** FIG. 13 is a vertical cross-sectional view of a pixel 50h in an eighth embodiment to which the present technology is applied.

**[0106]** In the pixel 50h in the eighth embodiment, as in the pixel 50g in the seventh embodiment depicted in FIG. 12, the Si substrate 70g has an extended length in the depth direction.

**[0107]** Furthermore, in a pixel 50r, a P-type region 121-1, an N-type region 122, and a P-type region 121-2 are formed on the back side of the PD 71 by ion injection. A PN junction portion defined by the P-type region 121-1, the N-type region 122, and the P-type region 122-2 is subjected to an intense electric field and can thus hold charge.

**[0108]** Consequently, in addition to producing an effect similar to the effect of the pixel 50g in the seventh embodiment, the pixel 50h in the eighth embodiment can further increase the amount of saturated charge Qs.

<Ninth Embodiment>

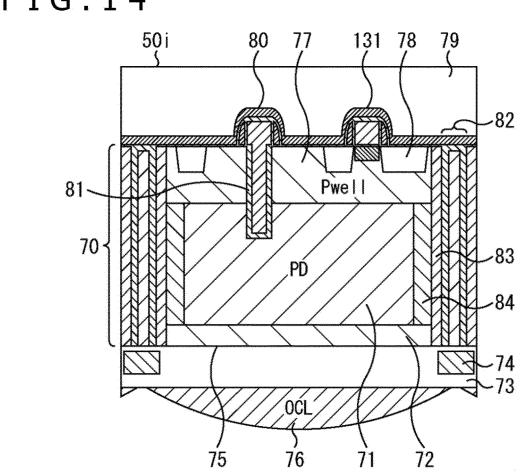

**[0109]** FIG. 14 is a vertical cross-sectional view of a pixel 50i in a ninth embodiment to which the present technology is applied.

**[0110]** The pixel 50i in the ninth embodiment differs from the pixel 50a in the first embodiment in that a MOS capacitor 131 and a pixel transistor (not depicted) are formed on the front side of the Si substrate 70, but the pixel 50i in the ninth embodiment is otherwise similar to the pixel 50a in the first embodiment.

**[0111]** Normally, even with an increased amount of saturated charge Qs of the PD 71, the amplitude limit of vertical signal lines VSL (vertical signal lines 47 depicted in FIG. 2) limits output unless conversion efficiency is reduced, leading to difficulty in making the most of the increased amount of saturated charge Qs.

<sup>5</sup> [0112] Reducing the conversion efficiency of the PD 71 requires addition of a capacity to the FD 91 (FIG. 4). Thus, the pixel 50i in the ninth embodiment is configured such that the MOS capacitor 131 is added as a capacity to be added to the FD 91 (not depicted in FIG. 11).

10 [0113] The pixel 50i in the ninth embodiment can be configured not only to produce an effect similar to the effect of the pixel 50a in the first embodiment but also to enable a reduction in the conversion efficiency of the PD 71 by addition of the MOS capacitor 131 to the FD 91,

<sup>15</sup> allowing the increased amount of saturated charge Qs to be made the most of.

<10th Embodiment>

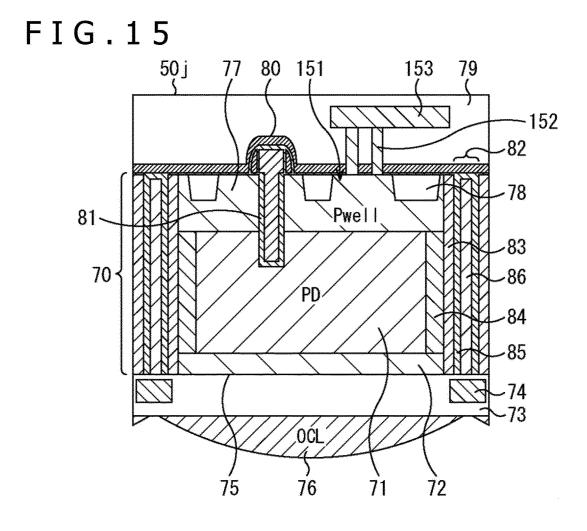

<sup>20</sup> **[0114]** FIG. 15 is a vertical cross-sectional view of a pixel 50j in a 10th embodiment to which the present technology is applied.

**[0115]** The pixel 50j in the 10th embodiment differs from the pixel 50a in the first embodiment in that two

- <sup>25</sup> contacts 152 are formed on a well contact portion 151 formed in the active region 77 and that the contacts 152 are connected to a Cu interconnect 153, but the pixel 50j in the 10th embodiment is otherwise similar to the pixel 50a in the first embodiment.

- 30 [0116] As described above, a configuration including the well contact portion 151 can be provided. Note that FIG. 15 depicts an example in which two contacts 152 are formed but two or more contacts 152 may be formed on the well contact portion 151.

- <sup>35</sup> [0117] In addition to producing an effect similar to the effect of the pixel 50a in the first embodiment, the pixel 50j in the 10th embodiment can improve major defect yield.

- 40 <11th Embodiment>

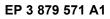

**[0118]** FIG. 16 illustrates a vertical cross-sectional view and a plan view of a pixel 50k in an 11th embodiment to which the present technology is applied.

<sup>45</sup> [0119] The pixel 50k in the 11th embodiment differs from the pixel 50a in the first embodiment in that a vertical transistor trench 81k is formed in the center of the pixel 50k to form a transfer transistor (gate) 80k, but the pixel 50k in the 11th embodiment is otherwise similar to the pixel 50a in the first embodiment.

[0120] The pixel 50k depicted in FIG. 16 is formed such that the transfer transistor (gate) 80k is located at an equal distance from each outer circumference of the PD 71. Accordingly, in addition to producing an effect similar to the effect of the pixel 50a in the first embodiment, the pixel 50k in the 11th embodiment includes the transfer

pixel 50k in the 11th embodiment includes the transfer transistor (gate) present at the equal distance from each outer circumference of the PD 71, allowing transfer of

20

charge to be improved.

<12th Embodiment>

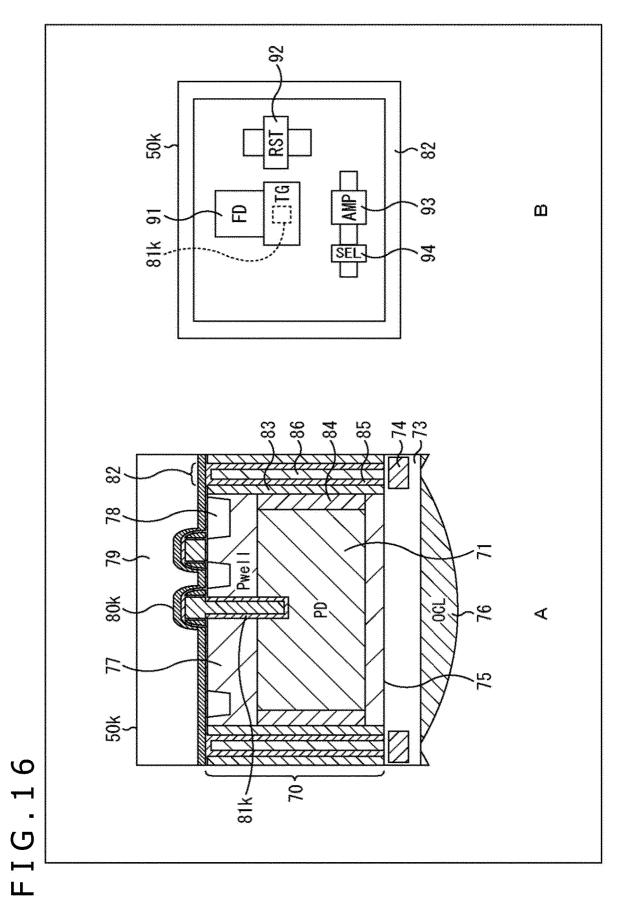

**[0121]** FIG. 17 illustrates a vertical cross-sectional view and a plan view of a pixel 50m in a 12th embodiment to which the present technology is applied.

**[0122]** The pixel 50m in the 12th embodiment differs from the pixel 50a in the first embodiment in that a transfer transistor 80m includes two vertical transistor trenches 81-1 and 81-2, but the pixel 50m in the 12th embodiment is otherwise similar to the pixel 50a in the first embodiment.

**[0123]** The pixel 50a in the first embodiment (FIG. 3) is configured such that the transfer transistor 80 includes the single vertical transistor trench 81, whereas, in the pixel 50m in the 12th embodiment, the transfer transistor 80m includes two vertical transistor trenches 81-1 and 81-2.

**[0124]** The configuration with the two vertical transistor trenches 81-1 and 81-2 as described above improves the followability of the potential of the region sandwiched between the two vertical transistor trenches 81-1 and 81-2 observed when the potential of the transfer transistor 80k is changed. Accordingly, a modulation factor can be increased. As a result, the charge transfer efficiency can be improved.

**[0125]** Additionally, an effect similar to the effect of the pixel 50a in the first embodiment is obtained.

**[0126]** Note that, although the description takes, as an example, the transfer transistor 80k including the two vertical transistor trenches 81-1 and 81-2, two or more vertical transistor trenches 81 may be formed in each pixel region.

**[0127]** Additionally, in the depicted example, the two vertical transistor trenches 81-1 and 81-2 formed are the same in size (length and thickness). However, in a case that a plurality of vertical transistor trenches 81 are formed, the vertical transistor trenches 81 formed may be different from each other in size. For example, the two vertical transistor trenches 81-1 and 81-2 may be formed such that one of the vertical transistor trenches 81-1 and 81-2 is longer or thicker than the other.

<13th Embodiment>

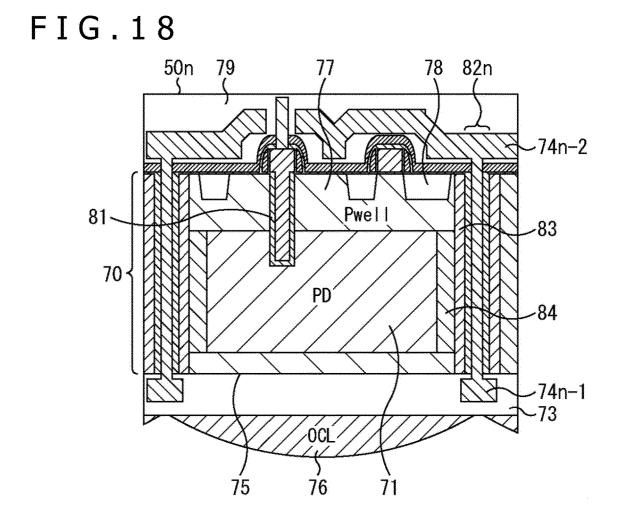

**[0128]** FIG. 18 is a vertical cross-sectional view of a pixel 50n in a 13th embodiment to which the present technology is applied.

**[0129]** The pixel 50n in the 13th embodiment differs from the pixel 50a in the first embodiment in the configuration of the light shielding films 74, but is otherwise similar to the pixel 50a.

**[0130]** In the pixel 50n in the 13th embodiment, a light shielding film 74n-1 and a light shielding film 74n-2 are respectively formed above and below DTI 82n. In the pixel 50a in the first embodiment (FIG. 3), the light shielding film 74 is formed on the back side of the DTI 82 (in

the figure, the lower side) to cover the back side. However, in the pixel 50n (FIG. 18), the inside of the DTI 82n is filled with the same metal material (for example, tungsten) as that of the light shielding film 74, and the front side of the Si substrate 70 (in the figure, the upper side)

is also covered with the metal material. [0131] In other words, the pixel 50n is configured such that each entire pixel region except for the back side (except for the light incidence surface) is enclosed by the

<sup>10</sup> metal material. However, in a case where the pixel 50n is configured such that the entire pixel 50n except for the back side is enclosed by the metal material, an opening portion is formed as appropriate at a required position, for example, the portion of the light shielding film 74n-2

<sup>15</sup> at which the transfer transistor 80n is located is opened and a terminal for connection to the outside is formed in the opening.

**[0132]** Note that a metal material other than tungsten (W) may be used for the light shielding films 74 and the like.

**[0133]** The pixel 50n in the 13th embodiment can prevent incident light from leaking to the adjacent pixel 50n, thus allowing color mixing to be inhibited.

[0134] Additionally, the pixel 50n can be configured

<sup>25</sup> such that light having reached the front side without being photoelectrically converted after being incident from the back side is reflected by the metal material (light shielding film 74n-2) and enters the PD 71 again. Accordingly, in addition to producing an effect similar to the effect of the

<sup>30</sup> pixel 50a in the first embodiment, the pixel 50n in the 13th embodiment can improve the sensitivity of the PD 71.

<14th Embodiment>

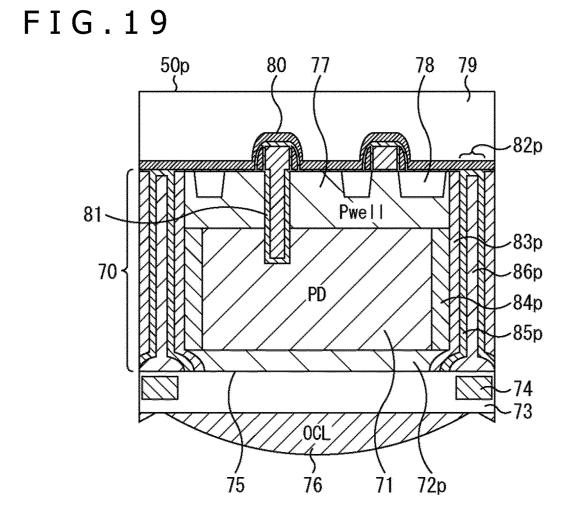

**[0135]** FIG. 19 is a vertical cross-sectional view of a pixel 50p in a 14th embodiment to which the present technology is applied.

[0136] The pixel 50p in the 14th embodiment differs

from the pixel 50a in the first embodiment in the shapes of a P-type solid phase diffusion layer 83p and a side wall film 85p formed on the back side, but is otherwise similar to the pixel 50a in the first embodiment.

[0137] The P-type solid phase diffusion layer 83p on

the back side of the pixel 50p is shaped to project toward an area below the N-type solid phase diffusion layer 84p. The pixel 50p includes the P-type solid phase diffusion layer 83p formed at an end of a P-type region 72p and shaped to project into the P-type region 72p. Additionally,

the side wall film 85p formed in the P-type solid phase

diffusion layer 83p is also shaped to project toward the P-type region 72p. Furthermore, a filler 86p formed in the side wall film 85p is shaped to project toward the P-type region 72p.

<sup>55</sup> **[0138]** Such a shape provides a configuration in which the N-type solid phase diffusion layer 84p is more reliably prevented from contacting the back side Si interface 75 of the Si substrate 70. This allows pinning of charge to

< 35 be prevented from being weakened, enabling prevention of flow of charge into the PD 71 which would otherwise degrade the Dark property.

**[0139]** When the N-type solid phase diffusion layer 84p is formed, the depth or the concentration of the N-type solid phase diffusion layer 84p may vary. For example, a variation may occur such that the N-type solid phase diffusion layer 84 formed in an A pixel 50 is deeper than the N-type solid phase diffusion layer 84 formed in a B pixel 50. In this case, the deeper N-type solid phase diffusion layer 84 may extend through the P-type region 72 or penetrate the P-type region 72 to reach the back side Si interface 75 of the Si substrate 70.

**[0140]** Additionally, a variation may occur such that the N-type impurities in the N-type solid phase diffusion layer 84 formed in the A pixel 50 have higher concentration than the N-type impurities in the N-type solid phase diffusion layer 84 formed in the B pixel 50. In this case, the N-type solid phase diffusion layer 84 with higher concentration may extend through the P-type region 72 or penetrate the P-type region 72 to reach the back side Si interface 75 of the Si substrate 70.

**[0141]** In the pixel 50p, on the back side Si interface 75 side of the N-type solid phase diffusion layer 84p, not only the P-type region 72, but also the P-type solid phase diffusion layer 83p is shaped to project to the area below the N-type solid phase diffusion layer 84p. Thus, given that the depth or concentration of the N-type solid phase diffusion layer 84 varies as described above, the variation can be absorbed, and the P-type solid phase diffusion layer 83p can reliably prevent the N-type solid phase diffusion layer 84p from contacting the back side Si interface 75 of the Si substrate 70.

**[0142]** The pixel 50p in the 14th embodiment can produce an effect similar to the effect of the pixel 50a in the first embodiment.

<Shape of Intense Electric Field Region>

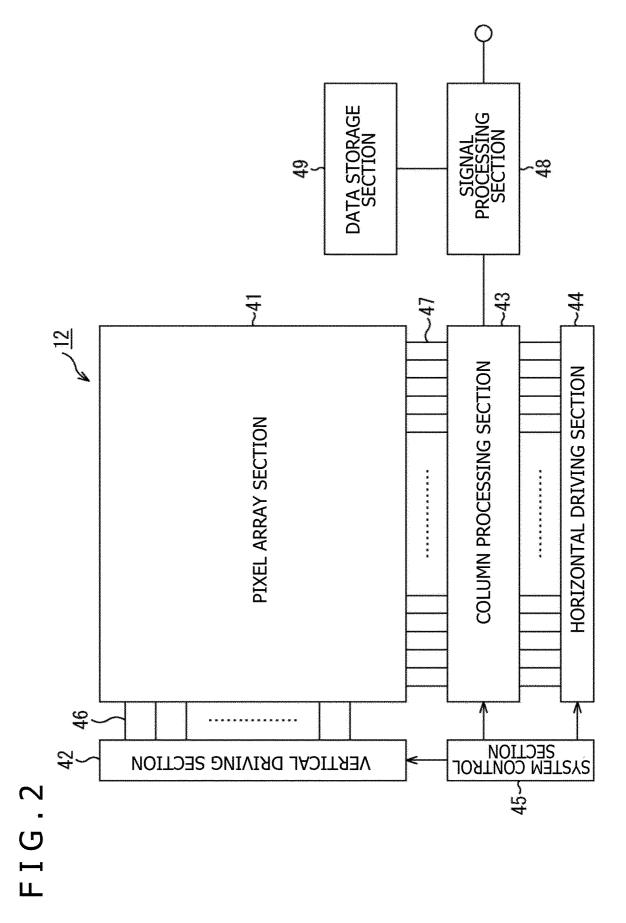

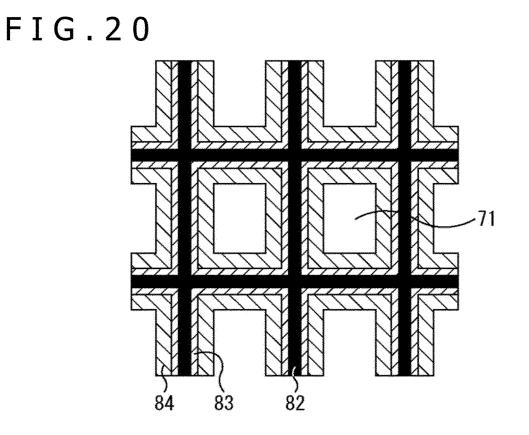

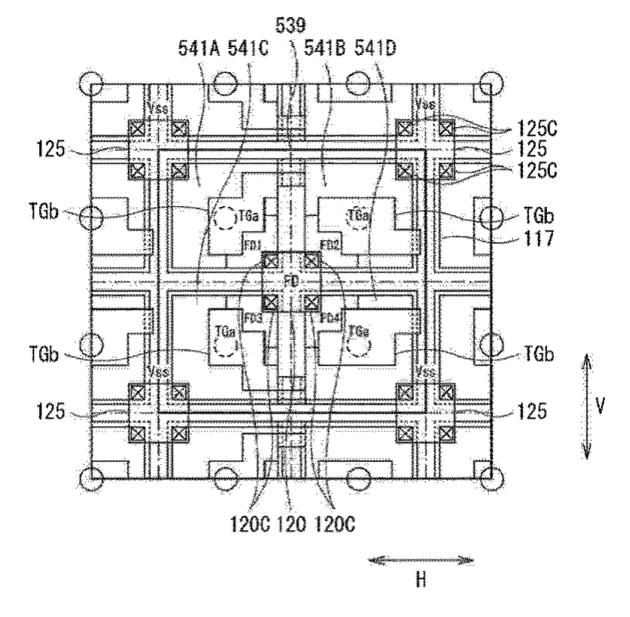

**[0143]** The pixel 50 in the first to 14th embodiments is formed to be enclosed by the DTI 82 in plan view, for example, as depicted in FIG. 20. On the side wall of the DTI 82, a PN junction region including the P-type solid phase diffusion layer 83 and the N-type solid phase diffusion layer 84 is formed to provide an intense electric field region. Note that the above description and the description below include a configuration in which a depletion layer region is present between the P-type solid phase diffusion layer 83 and the N-type solid phase diffusion layer 83 and the N-type solid phase diffusion layer 83 and the N-type solid phase diffusion layer 84, as well as a configuration in which the PN junction region includes only the P-type solid phase diffusion layer 83 and the N-type solid phase diffusion layer 84.

**[0144]** As depicted in FIG. 20, the PD 71 is enclosed by the N-type solid phase diffusion layer 84. The N-type solid phase diffusion layer 84 is enclosed by the P-type solid phase diffusion layer 83. Further, the P-type solid phase diffusion layer 83 is enclosed by the DTI 82.

**[0145]** As described above, the P-type solid phase diffusion layer 83 and the N-type solid phase diffusion layer 84 form the PN junction region, leading to formation of an intense electric field region around the PD 71. This

- <sup>5</sup> enables an increase in the amount of saturated charge. Description will be given below of the shape, in plan view, of a PN junction region further increasing the amount of saturated charge Qs compared to the linearly shaped PN junction region, as depicted in FIG. 20.

- <sup>10</sup> **[0146]** The shape of the intense electric field region will be described below as 15th to 19th embodiments, and any of the 15th to 19th embodiments can be combined with any of the first to 14th embodiments described above.

- <sup>15</sup> [0147] Additionally, the above description and the description below take, as an example, the PN junction region including the P-type solid phase diffusion layer 83 and the N-type solid phase diffusion layer 84 arranged in this order from the DTI 82 side toward the PD 71 side.

- 20 However, depending on the configuration of the PD 71, the PN junction region may include the N-type solid phase diffusion layer 84 and the P-type solid phase diffusion layer 83 arranged in this order from the DTI 82 side toward the PD 71 side. The present technology is applicable in

- <sup>25</sup> a case where the PN junction region provided in the side wall of the DTI 82 includes a first impurity region including first impurities and a second impurity region including second impurities and the first impurities are N-type impurities, whereas the second impurities are P-type impu-

- rities, or the first impurities are P-type impurities, whereas the second impurities are N-type impurities.

[0148] Additionally, the P type and the N type described above and below represent functioning as the P type or the N type with respect to a predetermined material. The description here takes, as an example, the pixels using the Si substrate 70, and thus the description below takes, as an example, a configuration in which

- (silicon) are treated as P-type impurities and impuritiesfunctioning as the N type with respect to Si (silicon) are treated as N-type impurities.

impurities functioning as the P type with respect to Si

<15th Embodiment>

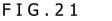

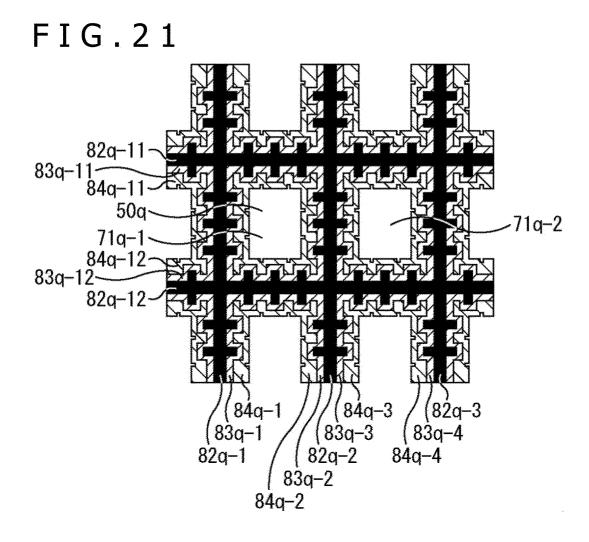

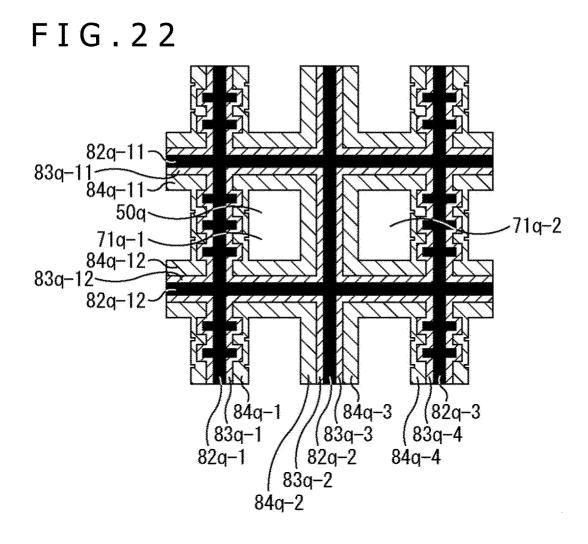

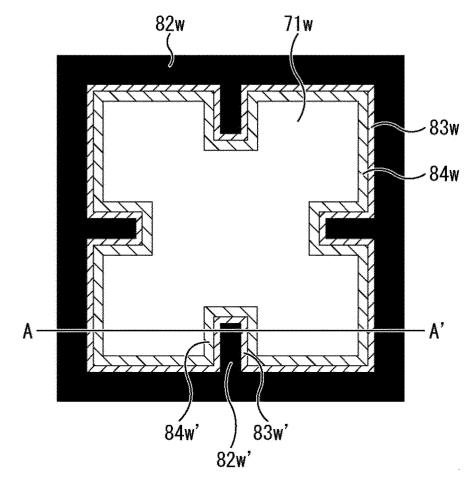

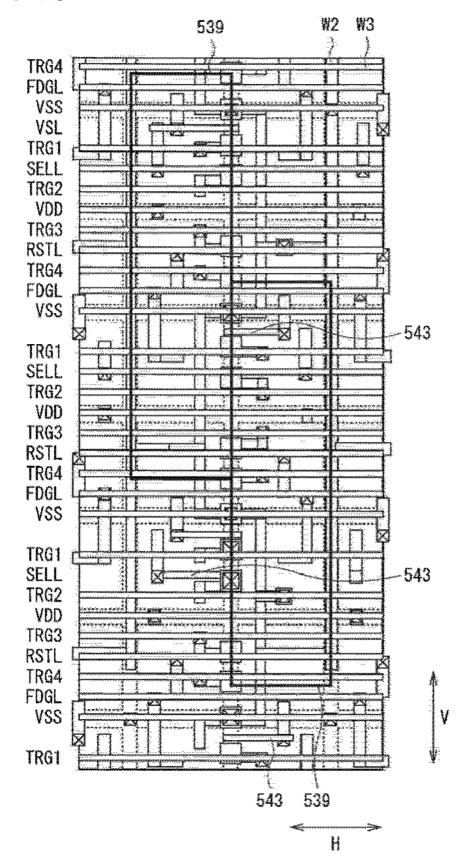

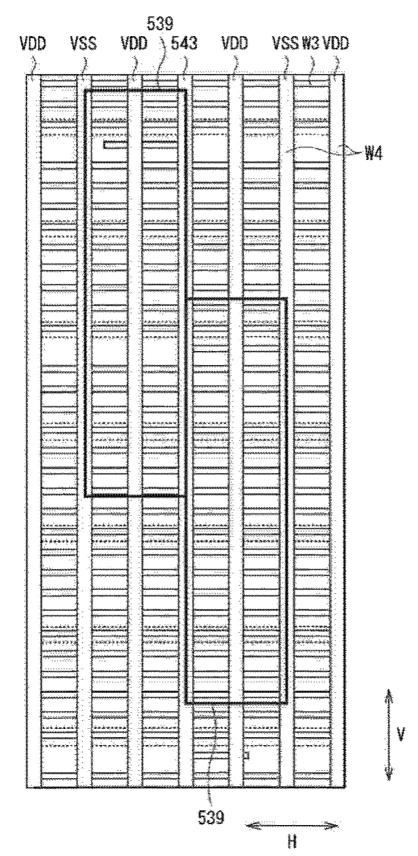

<sup>45</sup> **[0149]** FIG. 21 is a horizontal cross-sectional view (plan view) of a pixel 50q in a 15th embodiment to which the present technology is applied.

**[0150]** The pixel 50q in the 15th embodiment is shaped such that an intense electric field region enclosing a PD

- <sup>50</sup> 71q includes recesses and protrusions. Referring to the pixel 50q depicted in FIG. 21, when focus is placed on a PD 71q-1 included in the pixel 50q, DTI 82q corresponding to sides enclosing the PD 71q-1 is shaped with protruding portions (recessed portions).

- <sup>55</sup> **[0151]** The description will be continued in conjunction with the protruding portions. However, whether the portion protrudes or is recessed with respect to a side used as a reference depends on which of the sides is used as

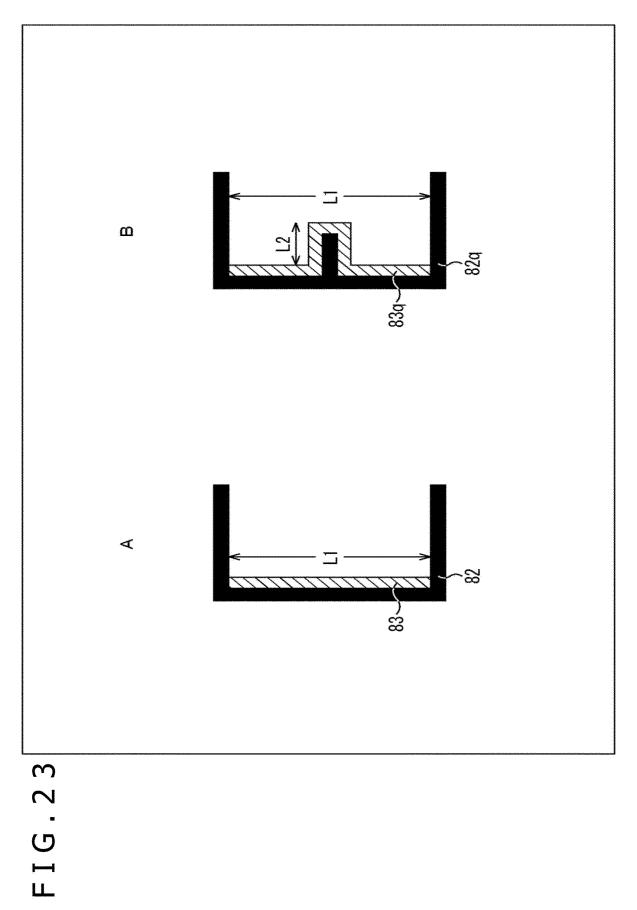

**[0152]** According to the shape of the DTI 82q, the Ptype solid phase diffusion layer 83q is shaped to include protruding portions. Further, according to the shape of the P-type solid phase diffusion layer 83q, the N-type solid phase diffusion layer 84q is also shaped to include protruding portions (the protruding portions of the P-type solid phase diffusion layer 83q correspond to recessed portions of the N-type solid phase diffusion layer 84q).

**[0153]** The P-type solid phase diffusion layer 83q is provided with the protruding portions, enabling an increase in the area where the P-type solid phase diffusion layer 83q contacts the N-type solid phase diffusion layer 84q. This enlarges the PN junction region including the P-type solid phase diffusion layer 83q and the N-type solid phase diffusion layer 84q, enlarging the intense electric field region. The enlarged intense electric field region increases the amount of charge that can be held in the intense electric field region, enabling an increase in the amount of saturated charge.

**[0154]** In the pixel 50q depicted in FIG. 21, for example, a DTI 82q-1 side that is included in four sides enclosing the PD 71q-1 and that is formed to the left of the PD 71q-1 is provided with three protruding portions. The number of the protruding portions is illustrative, and it is sufficient to form one or more protruding portions. Additionally, instead of the rectangle, another shape may be used. The other shape may be a triangle described below as a 16th embodiment.

**[0155]** Additionally, the pixel 50q depicted in FIG. 21 is an example in which each of the four sides enclosing the PD 71q-1 is provided with three protruding portions. However, at least one of the four sides can be provided with protruding portions. For example, as in the pixel 50q depicted in FIG. 22, one of the four sides enclosing the PD 71q can be provided with protruding portions.