# (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2018/0350847 A1 ZHOU et al.

Dec. 6, 2018 (43) **Pub. Date:**

# (54) THIN FILM TRANSISTOR, METHOD FOR FABRICATING THE SAME, ARRAY SUBSTRATE, AND DISPLAY PANEL

# (71) Applicants: BOE TECHNOLOGY GROUP CO., LTD., Beijing (CN); HEFEI XINSHENG OPTOELECTRONICS TECHNOLOGY CO., LTD., Anhui (CN)

(72) Inventors: Qiang ZHOU, Beijing (CN); Chaofan ZHU, Beijing (CN); Xingfeng REN, Beijing (CN)

(21) Appl. No.: 15/778,719

PCT Filed: Oct. 17, 2017

(86) PCT No.: PCT/CN2017/106504

§ 371 (c)(1),

(2) Date: May 24, 2018

#### (30)Foreign Application Priority Data

Oct. 31, 2016 (CN) ...... 201610943113.4

#### **Publication Classification**

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

|      | H01L 27/12  | (2006.01) |

|      | H01L 21/768 | (2006.01) |

|      | H01L 29/786 | (2006.01) |

|      | H01L 29/66  | (2006.01) |

(52) U.S. Cl.

CPC .... H01L 27/1225 (2013.01); H01L 21/76829 (2013.01); H01L 29/7869 (2013.01); H01L 27/127 (2013.01); H01L 27/1288 (2013.01); H01L 27/1262 (2013.01); H01L 29/66765 (2013.01)

#### (57)**ABSTRACT**

A thin film transistor, a method for fabricating the same, an array substrate, and a display panel are disclosed. The method includes: forming a semiconductor film comprising metallic elements, an etching stop film, and a source and drain film on a substrate in this order; and forming a pattern comprising an active layer, an etching stop layer, and a source and drain on the active layer by using a same mask plate, wherein the etching stop layer electrically connects the source and drain with the active layer. Since an etching stop film is formed on a semiconductor film comprising metallic elements, during etching the metal layer, the etching stop film can protect the semiconductor film comprising metallic elements from being etched, and this ensures the performance of the resultant active layer.

220

forming a semiconductor film comprising metallic elements, an etching stop film, and a source and drain film on a substrate in this order

forming a pattern comprising an active layer, an etching stop layer, and a source and drain on the active layer by using a same mask plate, wherein the etching stop layer electrically connects the source and drain with the active layer

Fig. 4c

## THIN FILM TRANSISTOR, METHOD FOR FABRICATING THE SAME, ARRAY SUBSTRATE, AND DISPLAY PANEL

#### RELATED APPLICATIONS

[0001] The present application is the U.S. national phase entry of PCT/CN2017/106504, with an international filing date of Oct. 17, 2017, which claims the benefit of Chinese Patent Application No. 201610943113.4, filed on Oct. 31, 2016, the entire disclosures of which are incorporated herein by reference.

#### TECHNICAL FIELD

[0002] The present disclosure relates to the field of display technologies, and particularly to a thin film transistor, a method for fabricating the same, an array substrate, and a display panel.

### BACKGROUND

[0003] A thin film transistor (TFT) plays a key role in a display device. As a non-linear switching element, the thin film transistor has been widely applied to a large size LCD display and AM-OLED display.

[0004] An active layer of the thin film transistor may be a semiconductor material comprising metallic elements, for example a metal oxide semiconductor material, or a metal-doped semiconductor material. In this case, during etching a metal layer to form a source and a drain, since the active layer comprises metallic elements, this etching will damage the active layer region between the source and the drain. This results in that the design requirements cannot be met, the mobility is reduced, and the performance of thin film transistor is affected.

### **SUMMARY**

[0005] Embodiments of the present disclosure provides a thin film transistor, a method for fabricating the same, an array substrate, and a display panel, which alleviates or overcomes one or more of the above defects.

**[0006]** In a first aspect, the present disclosure provides a method for fabricating a thin film transistor, comprising:

[0007] forming a semiconductor film comprising metallic elements, an etching stop film, and a source and drain film on a substrate in this order; and

[0008] forming a pattern comprising an active layer, an etching stop layer, and a source and drain on the active layer by using a same mask plate, wherein the etching stop layer electrically connects the source and drain with the active layer

[0009] For example, forming the pattern comprising the active layer, the etching stop layer, and the source and drain on the active layer by using a same mask plate comprises: [0010] coating a photoresist layer on the source and drain film;

[0011] exposing and developing the photoresist layer by using a gray tone mask plate, to form a first photoresist completely retained region in a region corresponding to a pattern of source to be formed, forming a second photoresist completely retained region in a region corresponding to a pattern of drain to be formed, forming a photoresist partially retained region in a region between the region corresponding to the pattern of source to be formed and the region corresponding to the pattern of drain to be formed, and

forming a photoresist completely removed region surrounding the region corresponding to a pattern of active layer to be formed; and

[0012] etching the source and drain film, the etching stop film, and the semiconductor film comprising metallic elements by using the photoresist layer, to form a pattern comprising the source, the drain, and the active layer.

[0013] For example, etching the source and drain film, the etching stop film, and the semiconductor film comprising metallic elements by using the photoresist layer to form the pattern comprising the source, the drain and the active layer comprises:

[0014] wet etching the source and drain film for a first time, to retain the source and drain film in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained;

[0015] dry etching the etching stop film for a first time, to retain the etching stop film in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained;

[0016] ashing the photoresist layer in the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained region, to completely remove the photoresist layer in the photoresist partially retained region, and thin the photoresist layer in the first photoresist completely retained region and the second photoresist completely retained region;

[0017] wet etching the source and drain film for a second time, to retain the source and drain film in a region corresponding to the first photoresist completely retained region and the second photoresist completely retained region, so as to form a pattern comprising source and drain;

[0018] wet etching the semiconductor film comprising metallic elements, to retain the semiconductor film comprising metallic elements in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained region, so as to form a pattern comprising active layer;

[0019] dry etching the etching stop film for a second time, to remove the etching stop film in a region corresponding to the photoresist partially retained region; and

[0020] removing the photoresist layer in the first photoresist completely retained region and the second photoresist completely retained region.

[0021] For example, prior to forming the semiconductor film comprising metallic elements, the etching stop film, and the source and drain film on the substrate in this order, the method further comprises: forming a pattern comprising gate and a gate insulating layer covering the pattern comprising gate on the substrate, and

[0022] wherein forming the semiconductor film comprising metallic elements, the etching stop film, and the source and drain film on the substrate in this order, comprises: forming the semiconductor film comprising metallic elements, the etching stop film, and the source and drain film on the substrate on which the pattern comprising gate and the gate insulating layer have been formed.

[0023] For example, the semiconductor film comprising metallic elements comprises a metal oxide semiconductor material or a metal-doped semiconductor material.

[0024] For example, the etching stop film comprises graphite, graphene, or a carbon nanomaterial. For example, the etching stop film comprises a mixture of a non-metal oxide and at least one of graphite, graphene, and a carbon nanomaterial. For example, the etching stop film comprises a non-metal dopant.

[0025] For example, the etching stop film has a thickness of about 800 Å $\sim$ 3000 Å.

[0026] In a second aspect, the present disclosure provides a thin film transistor, comprising a substrate, a semiconductor active layer comprising metallic elements on the substrate, a source and drain on the active layer, and an etching stop layer between the source and the active layer and between the drain and the active layer, wherein the etching stop layer electrically connects the source and drain with the active layer.

[0027] In a third aspect, the present disclosure provides an array substrate, comprising the thin film transistor as described above.

[0028] In fourth aspect, the present disclosure provides a display device, comprising the array substrate as described above.

### BRIEF DESCRIPTION OF THE DRAWINGS

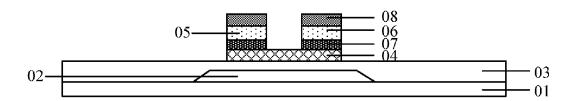

[0029] FIG. 1 is a structural view for illustrating a thin film transistor;

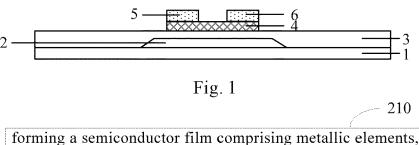

[0030] FIG. 2 is a flow chart for illustrating a method for fabricating a thin film transistor in an embodiment of the present disclosure;

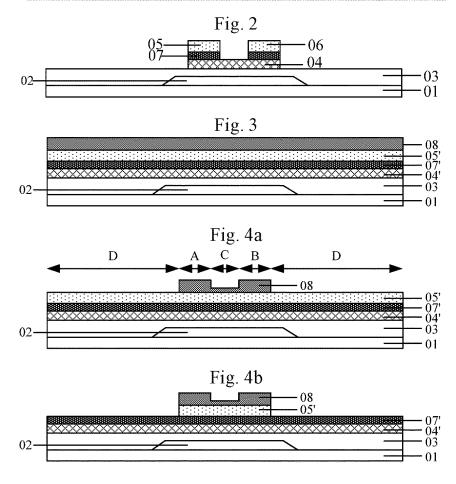

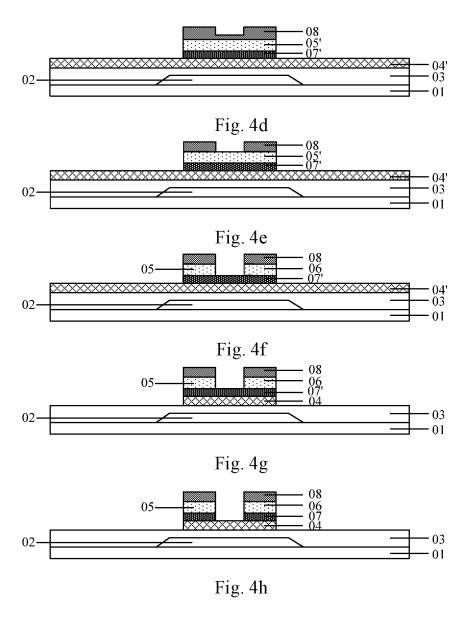

[0031] FIG. 3 is a structural view for illustrating a thin film transistor in an embodiment of the present disclosure; and [0032] FIGS. 4a, 4b, 4c, 4d, 4e, 4f, 4g and 4h are structural views for illustrating a thin film transistor during fabricating process in an embodiment of the present disclosure.

### DETAILED DESCRIPTION OF EMBODIMENTS

[0033] A thin film transistor, a method for fabricating the same, an array substrate, and a display panel in embodiments of the present disclosure will be described in detail hereinafter with reference to the accompanying drawings and specific implementations.

[0034] Currently, as shown in FIG. 1, a conventional thin film transistor of a bottom gate type comprises a substrate 1, a gate 2 on the substrate 1, an active layer 4 insulated from the gate 2 by an insulating layer 3, a source 5 and a drain 6 which are electrically connected with the active layer 4. As for the thin film transistor in which the active layer 4 is formed by a semiconductor material comprising metallic elements, during etching a metal layer to form the source 5 and the drain 6, since the active layer 4 also comprises metallic elements, such an etching will damage the active layer region between the source 5 and the drain 6. This results in that the design requirements cannot be met, the mobility is reduced, and the performance of thin film transistor is affected.

[0035] In an embodiment of the present disclosure, a method for fabricating a thin film transistor is provided. As shown in FIG. 2, the method comprises the following steps: [0036] step 210, forming a semiconductor film comprising metallic elements, an etching stop film, and a source and drain film on a substrate in this order; and

[0037] step 220, forming a pattern comprising an active layer, an etching stop layer, and a source and drain on the

active layer by using a same mask plate, wherein the etching stop layer electrically connects the source and drain with the active layer.

[0038] The etching stop film can protect the semiconductor film comprising metallic elements during etching the metal layer. Since the etching stop film is formed on the semiconductor film comprising metallic elements, during a patterning process, the etching stop film protects the semiconductor film comprising metallic elements from being etched, thus ensuring the performance of the resultant active layer.

[0039] Besides, the method for etching the etching stop film is different from the method for etching the semiconductor film comprising metallic elements, so that there is no damage to the semiconductor film comprising metallic elements

[0040] Furthermore, in the present method, the pattern comprising the source, the drain, the etching stop layer and the active layer is formed by etching only by using a same mask plate. This decreases the masking times, simplifies the process, and reduces the cost.

[0041] In implementations, for example, the step 220 comprises the following steps:

[0042] coating a photoresist layer on the source and drain film:

[0043] exposing and developing the photoresist layer by using a gray tone mask plate, to form a first photoresist completely retained region in a region corresponding to a pattern of source to be formed, forming a second photoresist completely retained region in a region corresponding to a pattern of drain to be formed, forming a photoresist partially retained region in a region between the region corresponding to the pattern of source to be formed and the region corresponding to the pattern of drain to be formed, and forming a photoresist completely removed region surrounding the region corresponding to a pattern of active layer to be formed; and

[0044] etching the source and drain film, the etching stop film, and the semiconductor film comprising metallic elements by using the photoresist layer, to form a pattern comprising the source, the drain, and the active layer.

[0045] In this embodiment, a gray tone mask plate is used to form a mask. In implementations, a half tone mask plate can be used to form a mask.

[0046] In implementations, for example, etching the source and drain film, the etching stop film, and the semi-conductor film comprising metallic elements by using the photoresist layer to form the pattern comprising the source, the drain and the active layer comprises:

[0047] wet etching the source and drain film for a first time, to retain the source and drain film in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained;

[0048] dry etching the etching stop film for a first time, to retain the etching stop film in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained; ashing the photoresist layer in the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained region, to completely remove the photoresist layer in the photoresist partially retained region, and thin the

photoresist layer in the first photoresist completely retained region and the second photoresist completely retained region;

[0049] wet etching the source and drain film for a second time, to retain the source and drain film in a region corresponding to the first photoresist completely retained region and the second photoresist completely retained region, so as to form a pattern comprising source and drain;

[0050] wet etching the semiconductor film comprising metallic elements, to retain the semiconductor film comprising metallic elements in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained region, so as to form a pattern comprising active layer;

[0051] dry etching the etching stop film for a second time, to remove the etching stop film in a region corresponding to the photoresist partially retained region; and

[0052] removing the photoresist layer in the first photoresist completely retained region and the second photoresist completely retained region.

[0053] In this embodiment, during etching the source and drain film by wet etching, the etching stop film can protect the semiconductor film comprising metallic elements from being etched. The etching stop film is etched by dry etching. Generally the dry etching will not damage to the semiconductor film comprising metallic elements. This further ensures the performance of the resultant active layer.

[0054] In the above embodiments, the photoresist can be a positive photoresist, or a negative photoresist.

[0055] On basis of any one of the above embodiments, for example, prior to forming the semiconductor film comprising metallic elements, the etching stop film, and the source and drain film on the substrate in this order, the method further comprises: forming a pattern comprising gate and a gate insulating layer covering the pattern comprising gate on the substrate.

[0056] Forming the semiconductor film comprising metallic elements, the etching stop film, and the source and drain film on the substrate in this order, comprises: forming the semiconductor film comprising metallic elements, the etching stop film, and the source and drain film on the substrate on which the pattern comprising gate and the gate insulating layer have been formed.

[0057] On basis of any one of the above embodiments, for example, the semiconductor film comprising metallic elements can comprise, but not limited to, a metal oxide semiconductor material or a metal-doped semiconductor material.

[0058] The metal oxide semiconductor material can be, but not limited to, IGZO.

[0059] metal-doped semiconductor material can be, but not limited to, zinc sulfide (ZnS), cadmium telluride (CdTe), copper gallium selenide (CuGaSe<sub>2</sub>), silver indium telluride (AgInTe<sub>2</sub>), silver thallium telluride (AgTITe<sub>2</sub>), or copper iron tin sulphide (Cu<sub>2</sub>FeSnS<sub>4</sub>).

[0060] On basis of any one of the above embodiments, for example, the etching stop film can comprise, but not limited to, graphite, graphene, a carbon nanomaterial; a mixture of a non-metal oxide and at least one of graphite, graphene, and a carbon nanomaterial; or a non-metal dopant. These materials are only some examples for the etching stop film, and the etching stop film can also be made from other materials, provided that it can protect the semiconductor film compris-

ing metallic elements from being etched, and etching of the etching stop film will not damage the semiconductor film. The etching stop film is made from an electrically conductive material, so that the resulting etching stop layer electrically connects the source and drain with the active layer, respectively.

[0061] The non-metal dopant can be silicon which is doped with one of boron, nitrogen, phosphorus and arsenic, germanium which is doped with one of boron, nitrogen, phosphorus and arsenic, or other suitable materials.

[0062] The non-metal oxide can be, but not limited to, silicon oxide or silicon oxynitride.

[0063] The etching stop film has a thickness of about 800 Å-3000 Å. For example, the etching stop film has a thickness of 1000 Å.

[0064] On basis of the same inventive concept, an embodiment of the present disclosure further provides a thin film transistor. The thin film transistor is fabricated by the method of any one of the above embodiments. The thin film transistor comprises a substrate, a semiconductor active layer comprising metallic elements on the substrate, a source and drain on the active layer, and an etching stop layer between the source and the active layer and between the drain and the active layer, wherein the etching stop layer electrically connects the source and drain with the active layer.

[0065] A thin film transistor and a method for fabricating the same in embodiments of the present disclosure will be described hereinafter in detail, with reference to a specific structure of the thin film transistor.

[0066] In this embodiment, the thin film transistor has a structure shown in FIG. 3. The thin film transistor comprises a substrate 01, a gate 02 on the substrate 01, a gate insulating layer 03 covering the gate 02, a pattern comprising active layer 04 of a metal oxide semiconductor material on the gate insulating layer 03, a pattern comprising source 05 and a pattern comprising drain 06 on the pattern comprising active layer 04, and an etching stop layer 07 between the pattern comprising source 05 and the pattern comprising active layer 04 and between the pattern comprising drain 06 and the pattern comprising active layer 04. A method for fabricating this thin film transistor structure for example comprises the following step 1–step 9.

[0067] Step 1, the gate 02, the gate insulating layer 03, a metal oxide semiconductor film 04', an etching stop film 07', a source and drain film 05' and a photoresist layer 08 are formed on the substrate 01 in this order, as shown in FIG. 4a. [0068] In this embodiment, the etching stop film is a graphite, and the metal oxide semiconductor film comprises Indium Gallium Zinc Oxide (IGZO).

[0069] Step 2, the photoresist layer 08 is exposed and developed. In the photoresist layer 08, a first photoresist completely retained region A is formed in a region corresponding to a pattern of source to be formed, a second photoresist completely retained region B is formed in a region corresponding to the pattern of drain to be formed, a photoresist partially retained region C is formed in a region between the region corresponding to the pattern of source to be formed and the region corresponding to the pattern of drain to be formed, and a photoresist completely removed region D is formed to surround the region corresponding to the pattern of active layer to be formed, as shown in FIG. 4b. [0070] Step 3, the source and drain film 05' is etched for a first time by wet etching, and the source and drain film 05'

in regions corresponding to the first photoresist completely retained region A, the second photoresist completely retained region B, and the photoresist partially retained region C is retained, as shown in FIG. 4c.

[0071] Step 4, the etching stop film 07' is etched for a first time by dry etching, and the etching stop film 07' in regions corresponding to the first photoresist completely retained region A, the second photoresist completely retained region B, and the photoresist partially retained region C is retained, as shown in FIG. 4d.

[0072] Step 5, the photoresist layer 08 in the first photoresist completely retained region A, the second photoresist completely retained region B, and the photoresist partially retained region C is ashed, to completely remove the photoresist layer 08 the photoresist partially retained region C, and at the same time, to thin the photoresist layer 08 in the first photoresist completely retained region A and the second photoresist completely retained region B, as shown in FIG.

[0073] Step 6, the source and drain film 05' is etched for a second time by wet etching, to remove the source and drain film 05' in a region corresponding to the photoresist partially retained region C, and to retain the source and drain film 05' in regions corresponding to the first photoresist completely retained region A and the second photoresist completely retained region B, so as to at least form the pattern comprising source 05 and the pattern comprising drain 06, as shown in FIG. 4f.

[0074] Step 7, the metal oxide semiconductor film 04' is etched by wet etching, to retain the metal oxide semiconductor film 04' in regions corresponding to the first photoresist completely retained region A, the second photoresist completely retained region B and photoresist partially retained region C, so as to at least form the pattern comprising active layer 04, as shown in FIG. 4g.

[0075] Step 8, the etching stop film 07' is etched for a second time by dry etching, to remove the etching stop film 07' in a region corresponding to the photoresist partially retained region C, as shown in FIG. 4h.

[0076] In this step, the etching of the etching stop film 07' is completed, forming the etching stop layer 07 shown in FIG. 3.

[0077] Step 9, the photoresist layer 08 in the first photoresist completely retained region A and the second photoresist completely retained region B is removed.

[0078] After this step, the thin film transistor with the structure shown in FIG. 3 is obtained.

[0079] On basis of the same inventive concept, an embodiment of the present disclosure further provides an array substrate, which comprises the thin film transistor in any one of the above embodiments.

[0080] On basis of the same inventive concept, an embodiment of the present disclosure further provides a display device, which comprises the array substrate in any one of the above embodiments. It is noted that the display device can be any product or component with a display function, such as a liquid crystal display panel, electronic paper, an OLED panel, a mobile phone, a tablet computer, a TV set, a monitor, a notebook computer, a digital photo frame, a navigator.

[0081] In the thin film transistor, the method for fabricating the same, the array substrate, and the display panel of embodiments of the present disclosure, since an etching stop film is formed on a semiconductor film comprising metallic

elements, during etching the metal layer, the etching stop film can protect the semiconductor film comprising metallic elements from being etched, and this ensures the performance of the resultant active layer.

[0082] Apparently, the person with ordinary skill in the art can make various modifications and variations to the present disclosure without departing from the spirit and the scope of the present disclosure. In this way, provided that these modifications and variations of the present disclosure belong to the scopes of the claims of the present disclosure and the equivalent technologies thereof, the present disclosure also intends to encompass these modifications and variations.

1. A method for fabricating a thin film transistor, comprising:

forming a semiconductor film comprising metallic elements, an etching stop film, and a source and drain film on a substrate in this order; and

forming a pattern comprising an active layer, an etching stop layer, and a source and a drain on the active layer by using a same mask plate, wherein the etching stop layer electrically connects the source and drain with the active layer.

2. The method of claim 1, wherein the step of forming the pattern comprising the active layer, the etching stop layer, and the source and the drain on the active layer by using a same mask plate comprises:

coating a photoresist layer on the source and drain film; exposing and developing the photoresist layer by using a gray tone mask plate, to form a first photoresist completely retained region in a region corresponding to a pattern of source to be formed, forming a second photoresist completely retained region in a region corresponding to a pattern of drain to be formed, forming a photoresist partially retained region in a region between the region corresponding to the pattern of source to be formed and the region corresponding to the pattern of drain to be formed, and forming a photoresist completely removed region surrounding the region corresponding to a pattern of active layer to be formed; and

etching the source and drain film, the etching stop film, and the semiconductor film comprising metallic elements by using the photoresist layer, to form a pattern comprising the source, the drain, and the active layer.

3. The method of claim 2, wherein the step of etching the source and drain film, the etching stop film, and the semi-conductor film comprising metallic elements by using the photoresist layer to form the pattern comprising the source, the drain and the active layer comprises:

wet etching the source and drain film for a first time, to retain the source and drain film in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained;

dry etching the etching stop film for a first time, to retain the etching stop film in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained;

ashing the photoresist layer in the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained region, to completely remove the photoresist layer in the photoresist partially retained region, and thin the photoresist layer in the first photoresist completely retained region and the second photoresist completely retained region;

- wet etching the source and drain film for a second time, to retain the source and drain film in a region corresponding to the first photoresist completely retained region and the second photoresist completely retained region, so as to form a pattern comprising source and drain:

- wet etching the semiconductor film comprising metallic elements, to retain the semiconductor film comprising metallic elements in a region corresponding to the first photoresist completely retained region, the second photoresist completely retained region, and the photoresist partially retained region, so as to form a pattern comprising active layer:

- dry etching the etching stop film for a second time, to remove the etching stop film in a region corresponding to the photoresist partially retained region; and

- removing the photoresist layer in the first photoresist completely retained region and the second photoresist completely retained region.

- 4. The method of claim 1, wherein prior to forming the semiconductor film comprising metallic elements, the etching stop film, and the source and drain film on the substrate in this order, the method further comprises: forming a pattern comprising gate and a gate insulating layer covering the pattern comprising gate on the substrate, and

- wherein the step of forming the semiconductor film comprising metallic elements, the etching stop film, and the source and drain film on the substrate in this order, comprises: forming the semiconductor film comprising metallic elements, the etching stop film, and the

- source and drain film on the substrate on which the pattern comprising gate and the gate insulating layer have been formed.

- 5. The method of claim 1, wherein the semiconductor film comprising metallic elements comprises a metal oxide semiconductor material or a metal-doped semiconductor material.

- **6**. The method of claim **1**, wherein the etching stop film comprises graphite, graphene, or a carbon nanomaterial.

- 7. The method of claim 1, wherein the etching stop film comprises a mixture of a non-metal oxide and at least one of graphite, graphene, and a carbon nanomaterial.

- 8. The method of claim 1, wherein the etching stop film comprises a non-metal dopant.

- 9. The method of claim 8, wherein the non-metal dopant is silicon which is doped with one of boron, nitrogen, phosphorus and arsenic, or germanium which is doped with one of boron, nitrogen, phosphorus and arsenic.

- 10. The method of claim 1, wherein the etching stop film has a thickness of about 800 Å~3000 Å.

- 11. A thin film transistor, comprising a substrate, a semiconductor active layer comprising metallic elements on the substrate, a source and drain on the active layer, and an etching stop layer between the source and the active layer and between the drain and the active layer, wherein the etching stop layer electrically connects the source and the drain with the active layer.

- 12. An array substrate, comprising the thin film transistor of claim 11.

- 13. A display device, comprising the array substrate of claim 12.

\* \* \* \* \*