# (19) United States

## (12) Patent Application Publication (10) Pub. No.: US 2024/0194140 A1 **MORITA**

Jun. 13, 2024 (43) **Pub. Date:**

## (54) DISPLAY DEVICE AND METHOD FOR DRIVING DISPLAY DEVICE

(71) Applicant: Japan Display Inc., Tokyo (JP)

(72) Inventor: Tetsuo MORITA, Tokyo (JP)

(73) Assignee: Japan Display Inc., Tokyo (JP)

(21) Appl. No.: 18/524,291

(22)Filed: Nov. 30, 2023

#### (30)Foreign Application Priority Data

(JP) ...... 2022-198098

### **Publication Classification**

(51) Int. Cl. G09G 3/3233 (2006.01)

<u>180</u>

(52) U.S. Cl.

CPC ... G09G 3/3233 (2013.01); G09G 2300/0426 (2013.01); G09G 2300/0819 (2013.01); G09G 2300/0861 (2013.01); G09G 2330/021 (2013.01); G09G 2330/045 (2013.01)

#### (57)ABSTRACT

A display device includes a first transistor controlled using a second control signal obtained by shifting a first control signal and electrically connected a first node, a second transistor electrically connected between the first node and a second node, a third transistor controlled using the first control signal to which a third control signal has been shifted, and electrically connected between the second node and a gate electrode of the second transistor, and a fourth transistor electrically connected to the second node is controlled to supply a reset voltage to the second node and the gate electrode of the second transistor using the third control signal.

FIG. 1

FIG. 2

FIG. 3

180

S C C

FIG. 16

180

FIG. 30

<u>40</u>

FIG. 31

FIG. 32

FIG. 33

FIG. 34

FIG. 35

FIG. 36

FIG. 37

FIG. 38

FIG. 39

FIG. 40

FIG. 41

FIG. 42

# DISPLAY DEVICE AND METHOD FOR DRIVING DISPLAY DEVICE

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of priority to Japanese Patent Application No. 2022-198098 filed on Dec. 12, 2022, the entire contents of which are incorporated herein by reference.

#### **FIELD**

[0002] An embodiment of the present invention relates to a display device and a method for driving the display device.

# BACKGROUND

[0003] In recent years, self-luminous display devices have been mounted on televisions, smart phones, digital signages (electronic signboards, electronic advertising boards, and the like), and the like and are becoming popular. The self-luminous display device includes, for example, a plurality of pixels and a driver for driving the plurality of pixels. Each of the plurality of pixels includes, for example, a plurality of transistors, a capacitive element, and a light emitting element. The light emitting element is, for example, a light emitting diode (Light Emitting Diode: LED), a micro light emitting diode (micro LED), or an organic electroluminescent (Electro Luminescence: EL) element. In the selfluminous display device, the driver supplies a voltage to each of the plurality of pixels, so that a current corresponding to the supplied voltage value flows to the light emitting element included in each of the plurality of pixels. Each of the light emitting elements emits light with a luminance corresponding to the current flowing through the light emitting element, and the pixel including the light emitting element can display an image with a gradation corresponding to the luminance. On the other hand, there is an increasing demand for reducing power consumption of the selfluminous display device.

[0004] For example, U.S. Patent Application Publication No. 2016/0284276 discloses a pixel including six transistors, one capacitive element, and one light emitting element, and a self-luminous display device including the pixel. Power consumption of the self-luminous display device described in Patent Literature 1 can be reduced, for example, by adjusting a power supply voltage electrically connected to the light emitting element.

#### **SUMMARY**

[0005] A display device according to an embodiment of the present invention includes: a first transistor controlled using a second control signal in which a first control signal is shifted and electrically connected to a first node; a second transistor electrically connected between the first node and a second node; a third transistor controlled using the first control signal in which a third control signal is shifted and electrically connected between the second node and a gate electrode of the second transistor; and a fourth transistor controlled using the third control signal to supply a reset voltage to the second node and the gate electrode of the second transistor and electrically connected to the second node

[0006] A method for driving a display device according to an embodiment of the present invention is a method for

driving a self-luminous display device including a first transistor controlled using a second control signal obtained by shifting a first control signal and electrically connected to a first node, a second transistor electrically connected between the first node and a second node, and a third transistor controlled using the first control signal obtained by shifting a third control signal and electrically connected between the second node and a gate electrode of the second transistor, and a fourth transistor controlled using the third control signal and electrically connected to the second node, wherein the fourth transistor is turned on using the third control signal and the third transistor is turned on using the first control signal, a reset voltage is supplied to the second node and the gate electrode of the second transistor, and after the reset voltage is supplied, the fourth transistor is turned off using the third control signal, the first transistor is turned on using the second control signal, and a data voltage is supplied to the second node and the first node.

#### BRIEF DESCRIPTION OF DRAWINGS

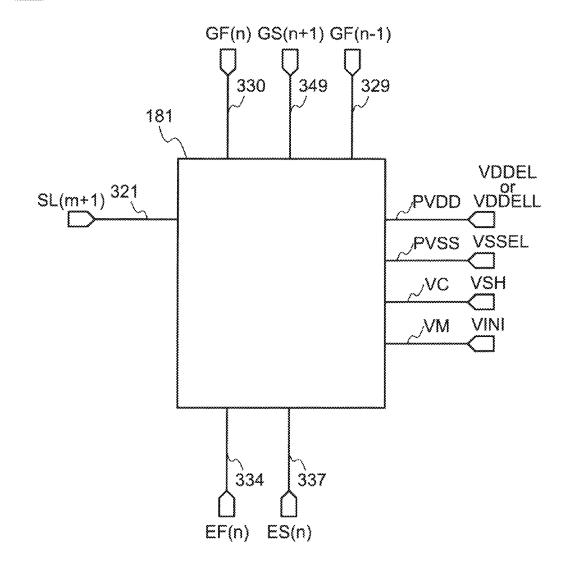

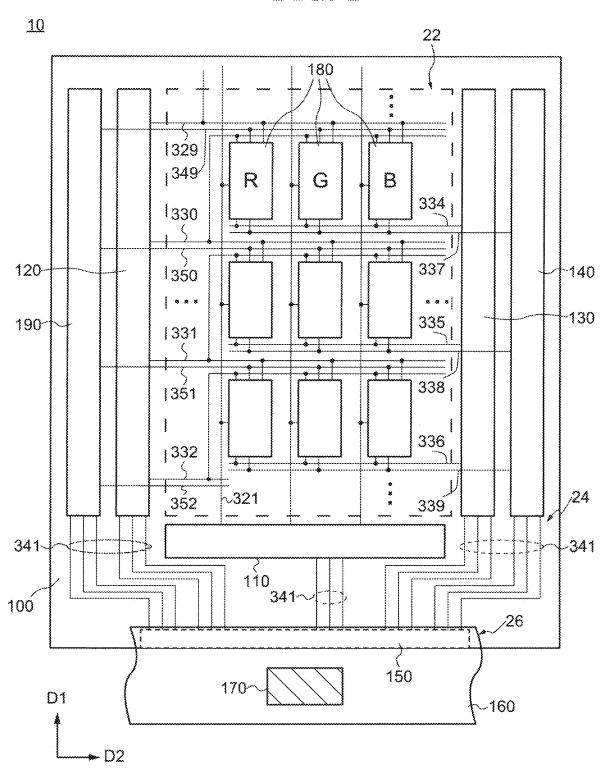

[0007] FIG. 1 is a schematic diagram showing a configuration of a self-luminous display device according to a first embodiment of the present invention.

[0008] FIG. 2 is a schematic diagram showing the configuration of the self-luminous display device according to the first embodiment of the present invention.

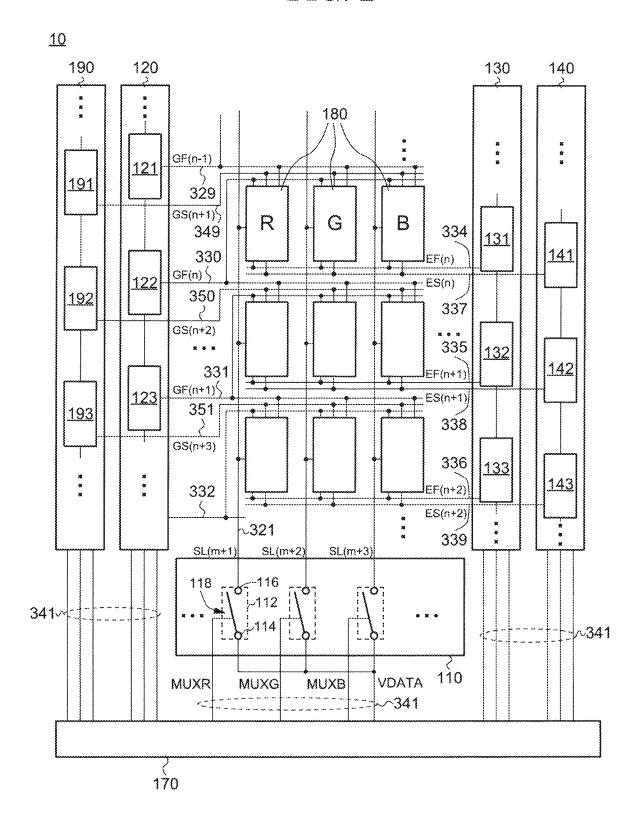

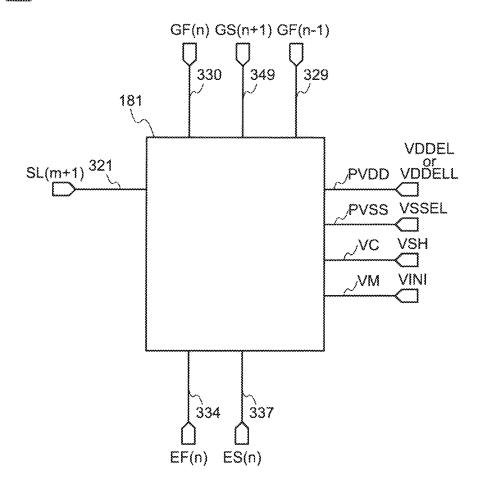

[0009] FIG. 3 is a schematic diagram showing an input signal to a pixel circuit according to the first embodiment of the present invention.

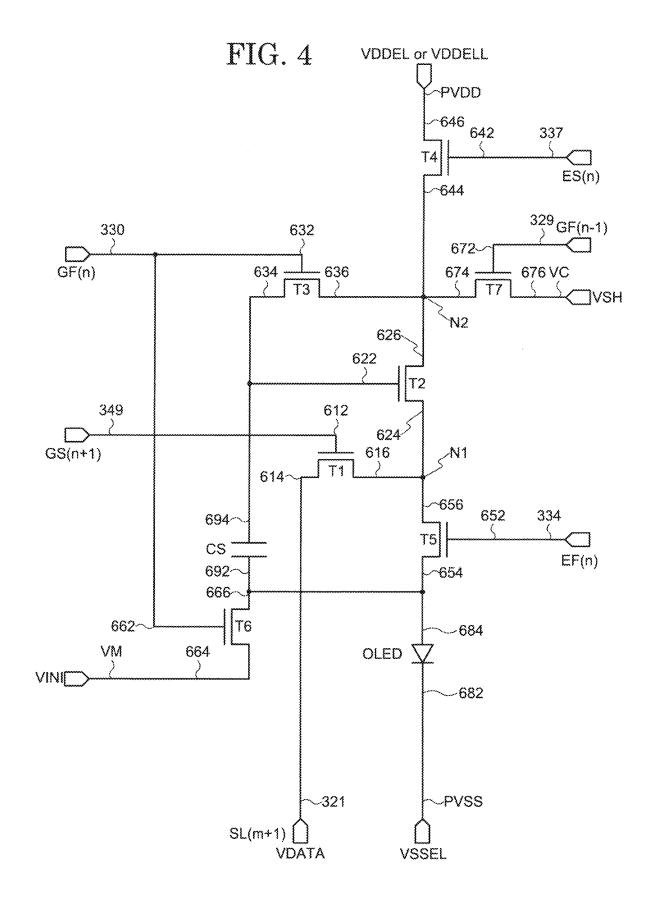

[0010] FIG. 4 is a circuit diagram showing a configuration of the pixel circuit according to the first embodiment of the present invention.

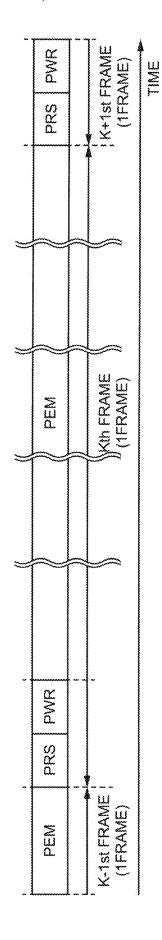

[0011] FIG. 5A is a diagram showing the configuration of the self-luminous display device according to the first embodiment of the present invention.

[0012] FIG. 5B is a diagram showing the configuration of the self-luminous display device according to the first embodiment of the present invention.

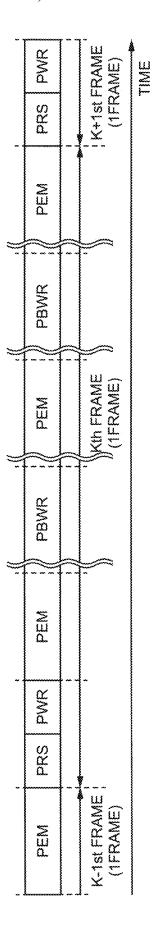

[0013] FIG. 6 is a schematic diagram showing a timing chart of the self-luminous display device according to the first embodiment of the present invention.

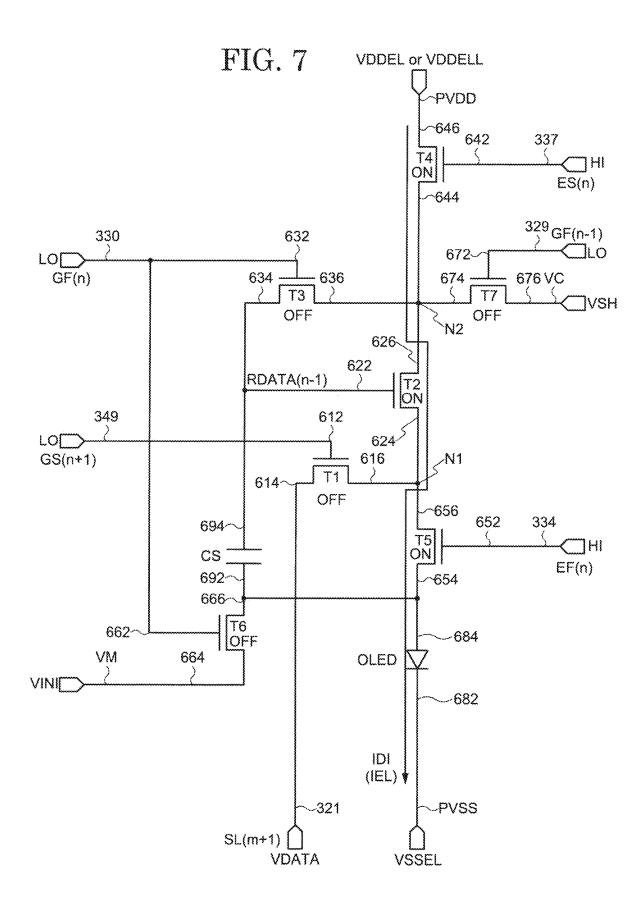

[0014] FIG. 7 is a schematic diagram showing an operation state of a pixel at the timing shown in FIG. 6.

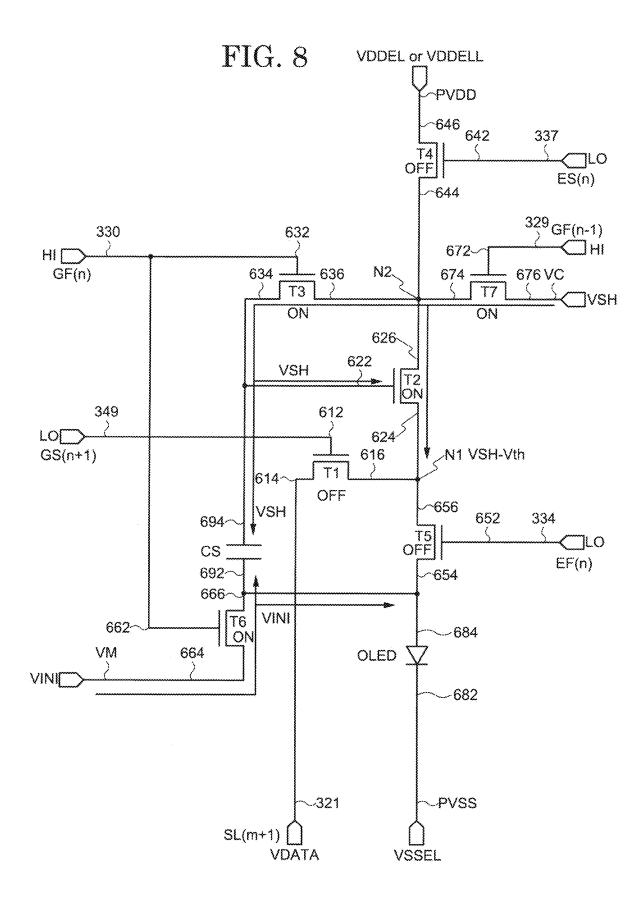

[0015] FIG.  $\hat{8}$  is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 6.

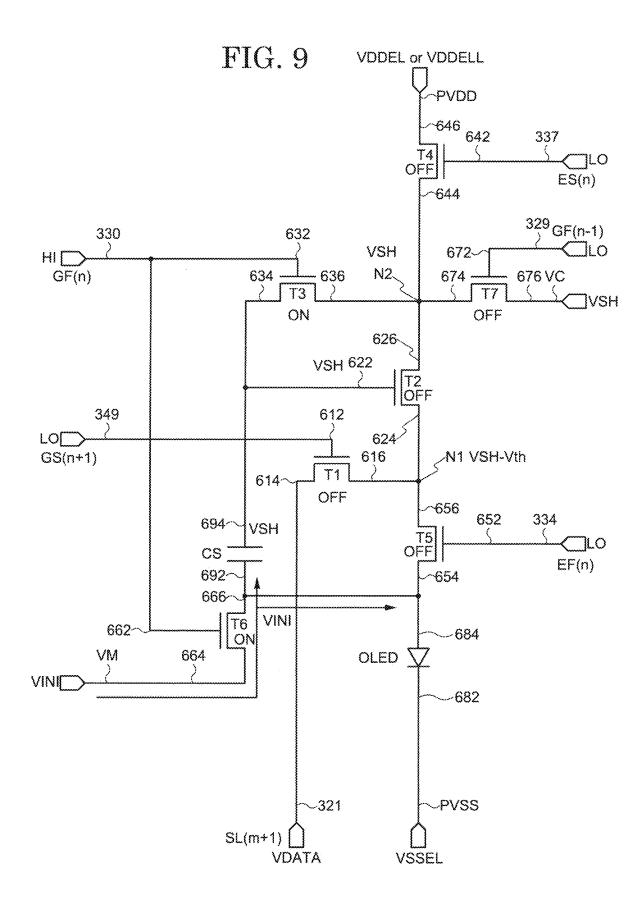

[0016] FIG. 9 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 6.

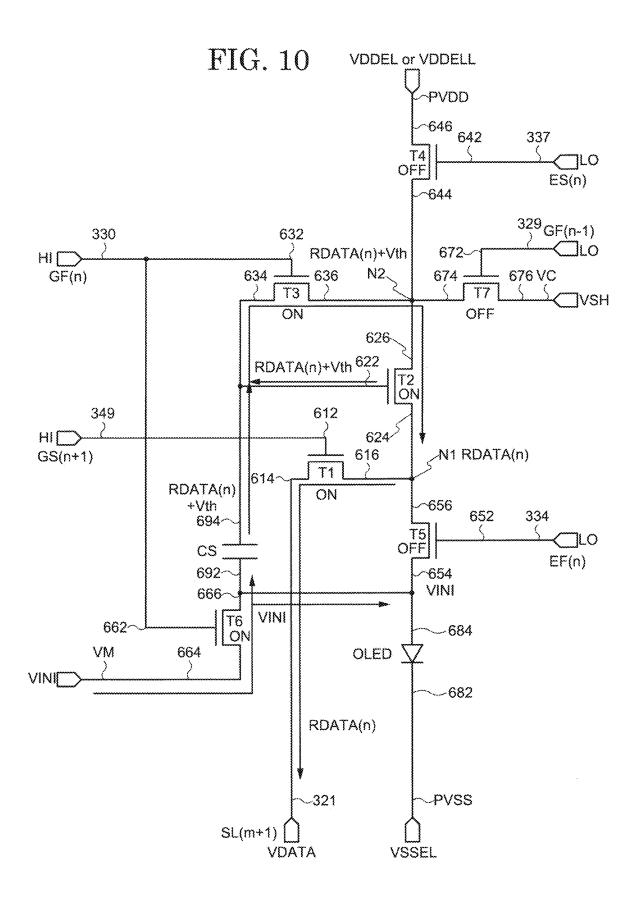

[0017] FIG. 10 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 6.

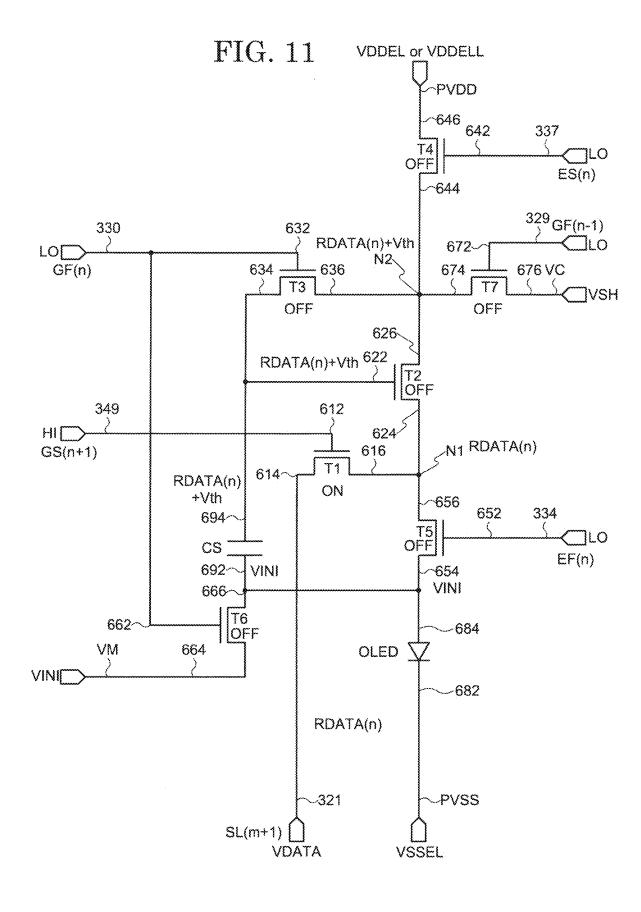

[0018] FIG. 11 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 6.

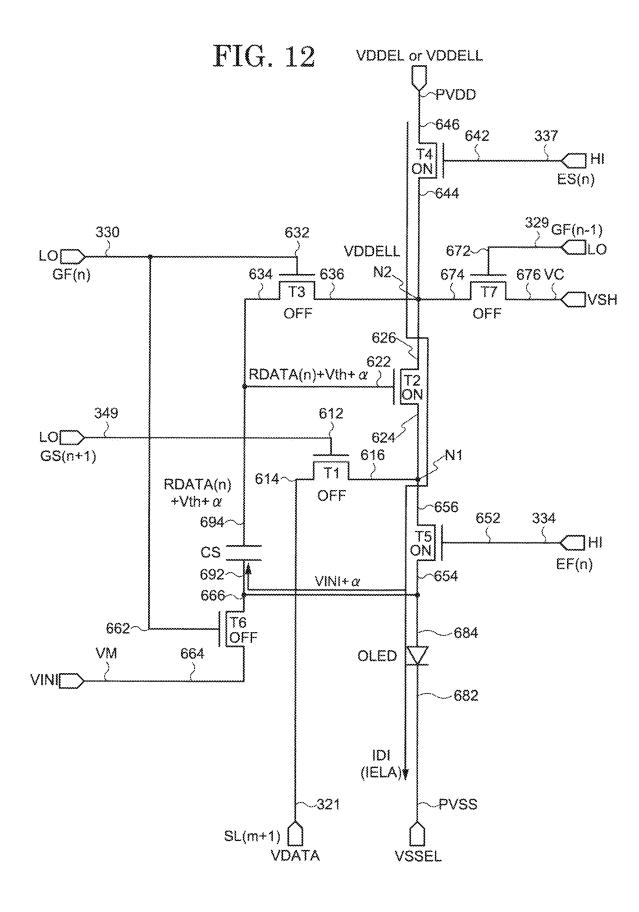

[0019] FIG. 12 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 6.

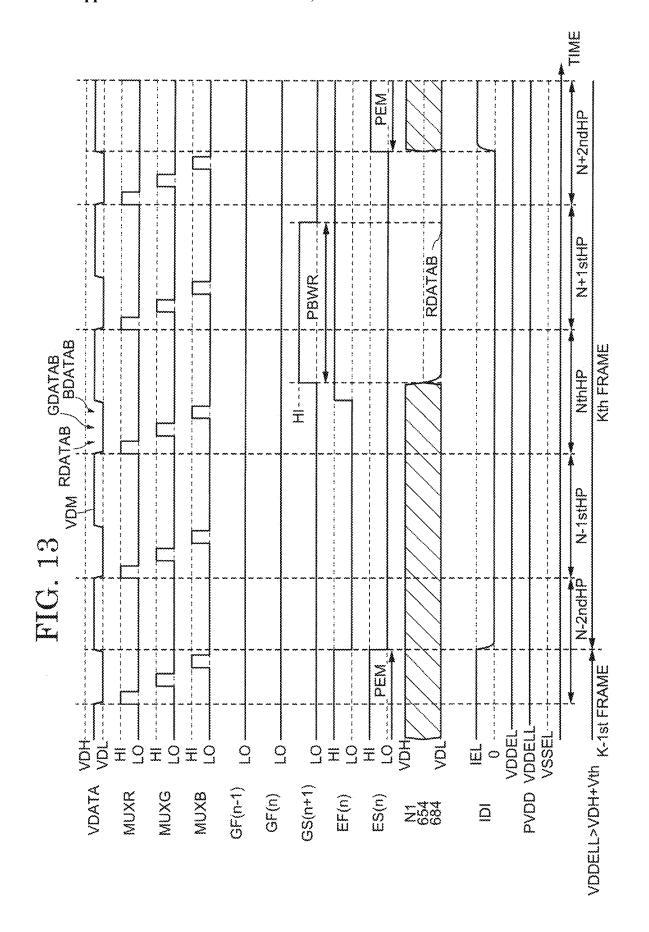

[0020] FIG. 13 is a schematic diagram showing a timing chart of the self-luminous display device according to the first embodiment of the present invention.

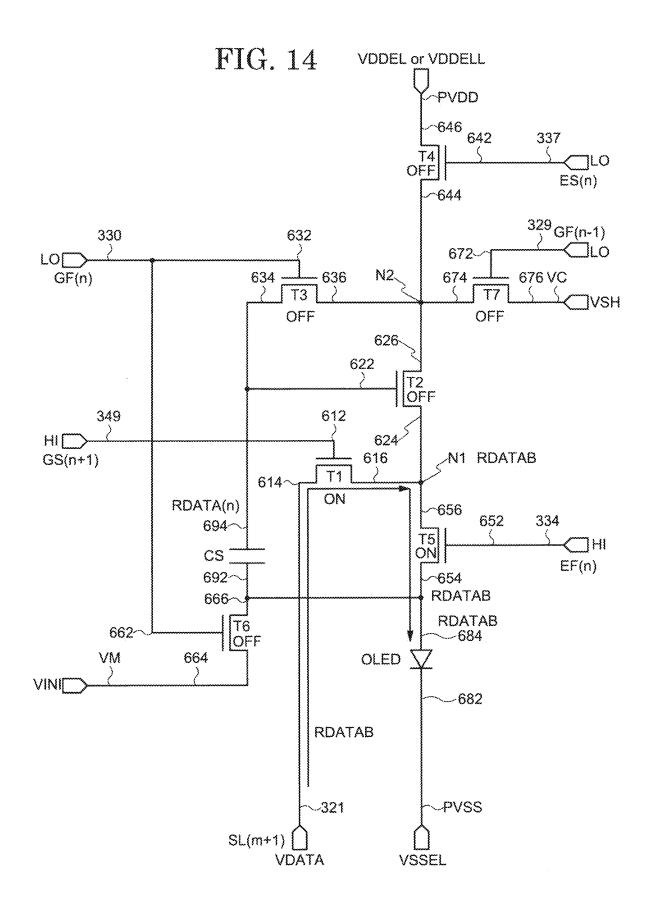

[0021] FIG. 14 is a schematic diagram showing an operation state of a pixel at the timing shown in FIG. 13.

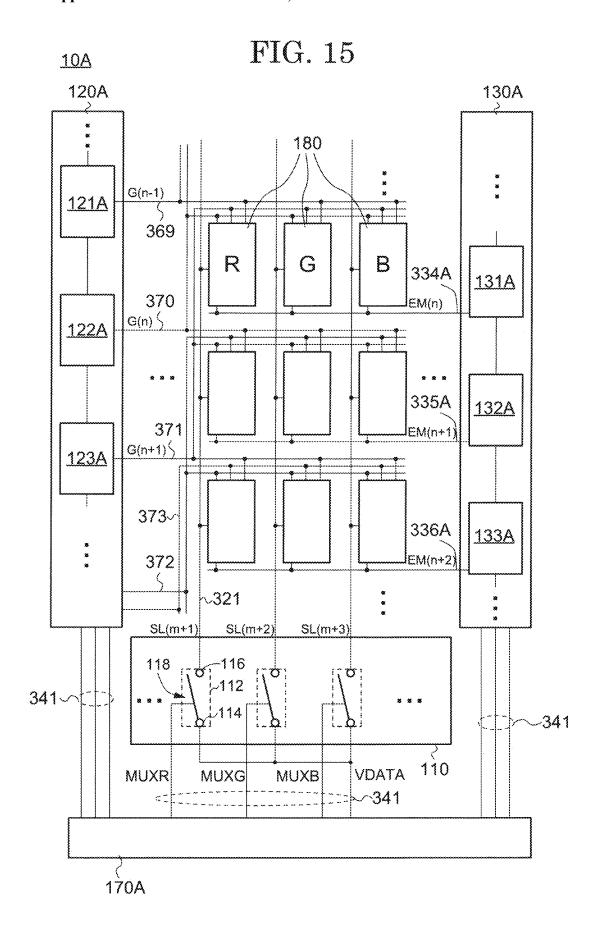

[0022] FIG. 15 is a schematic diagram showing a configuration of a self-luminous display device according to a second embodiment of the present invention.

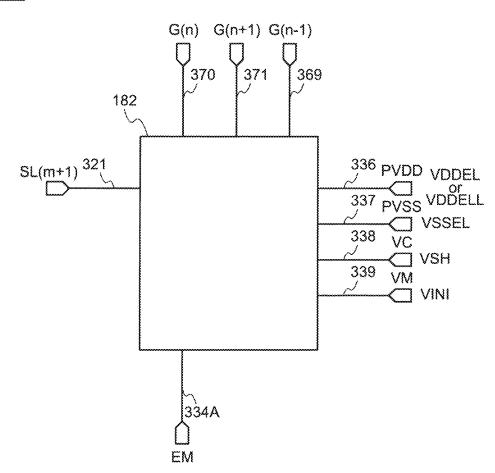

[0023] FIG. 16 is a schematic diagram showing an input signal to a pixel circuit according to the second embodiment of the present invention.

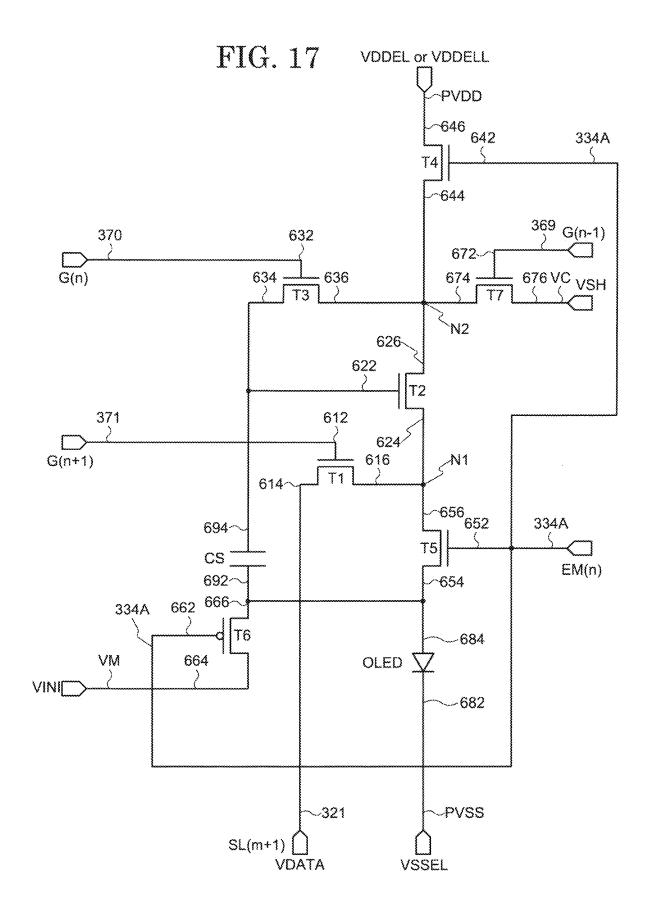

[0024] FIG. 17 is a circuit diagram showing a configuration of the pixel circuit according to the second embodiment of the present invention.

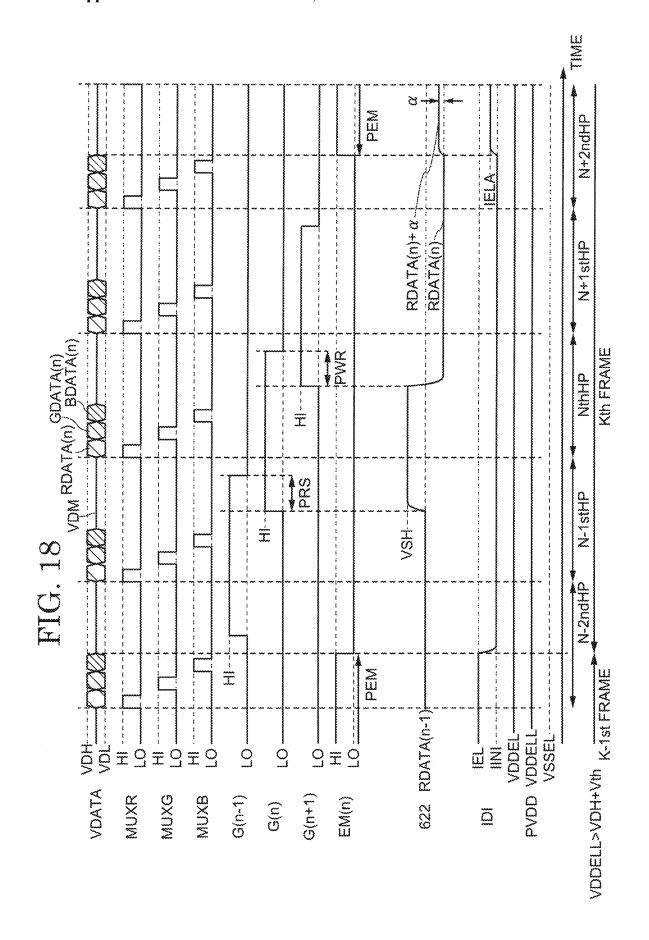

[0025] FIG. 18 is a schematic diagram showing a timing chart of the self-luminous display device according to the second embodiment of the present invention.

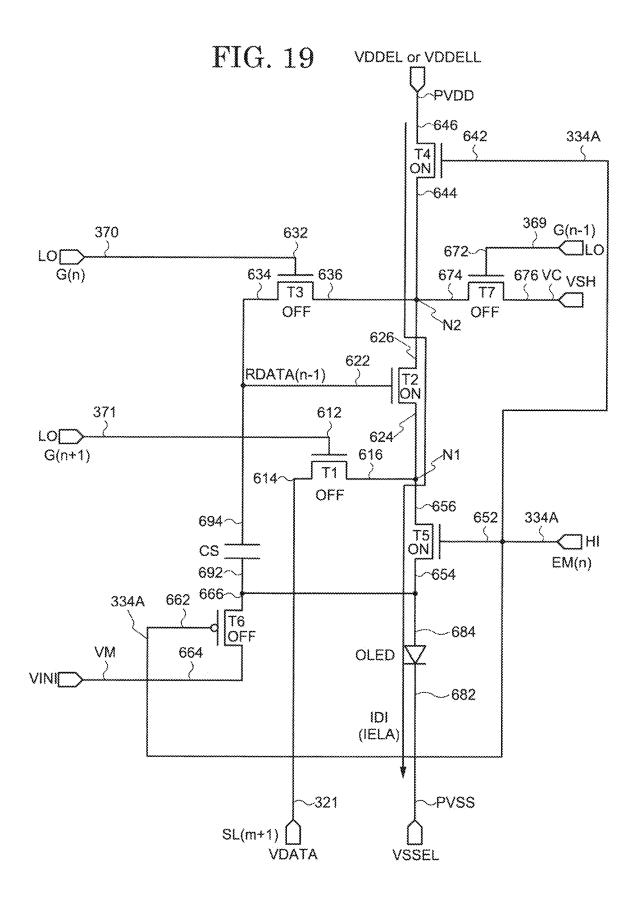

[0026] FIG. 19 is a schematic diagram showing an operation state of a pixel at the timing shown in FIG. 18.

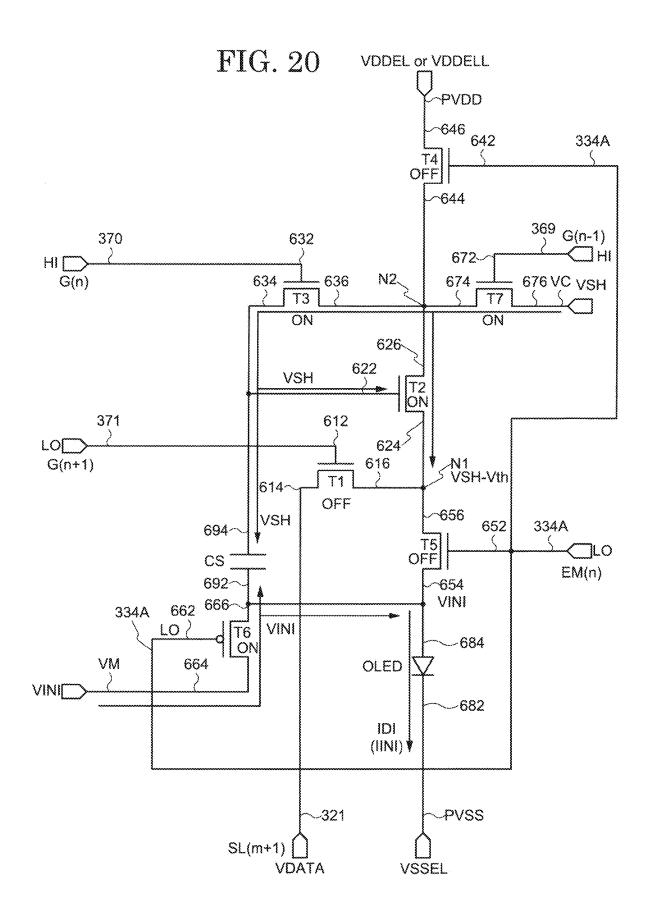

[0027] FIG. 20 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 18.

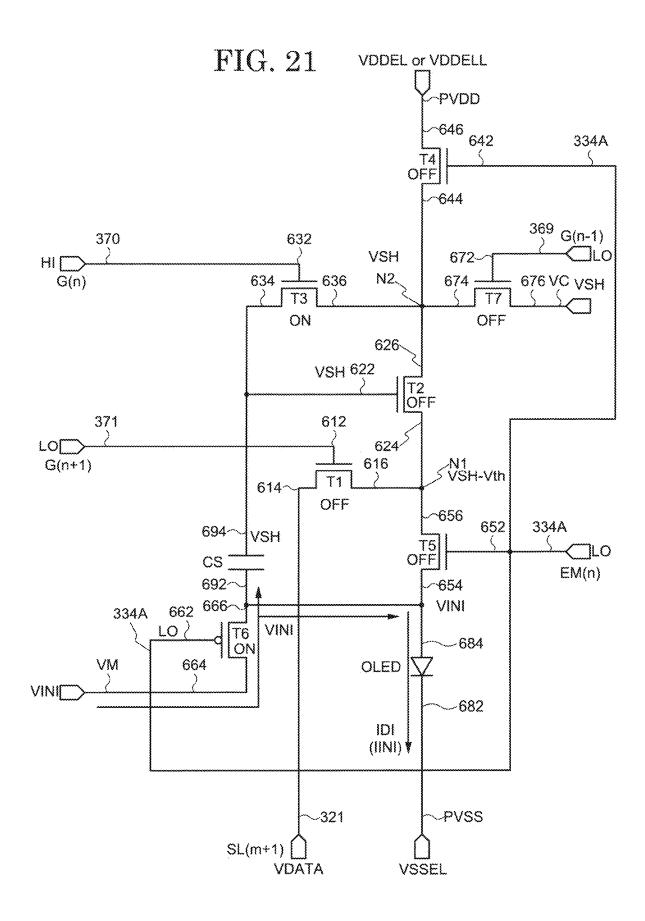

[0028] FIG. 21 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 18.

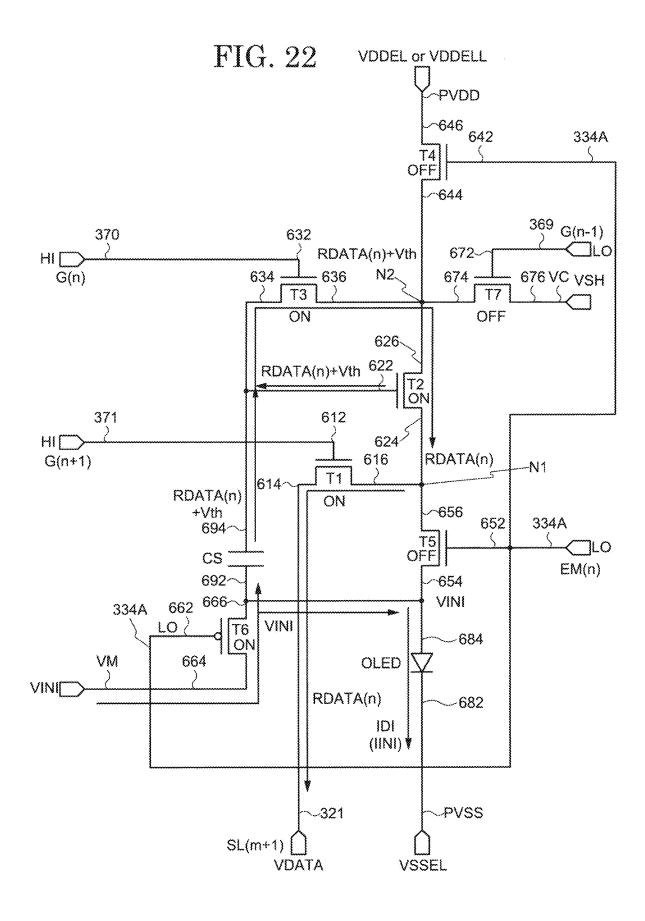

[0029] FIG. 22 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 18.

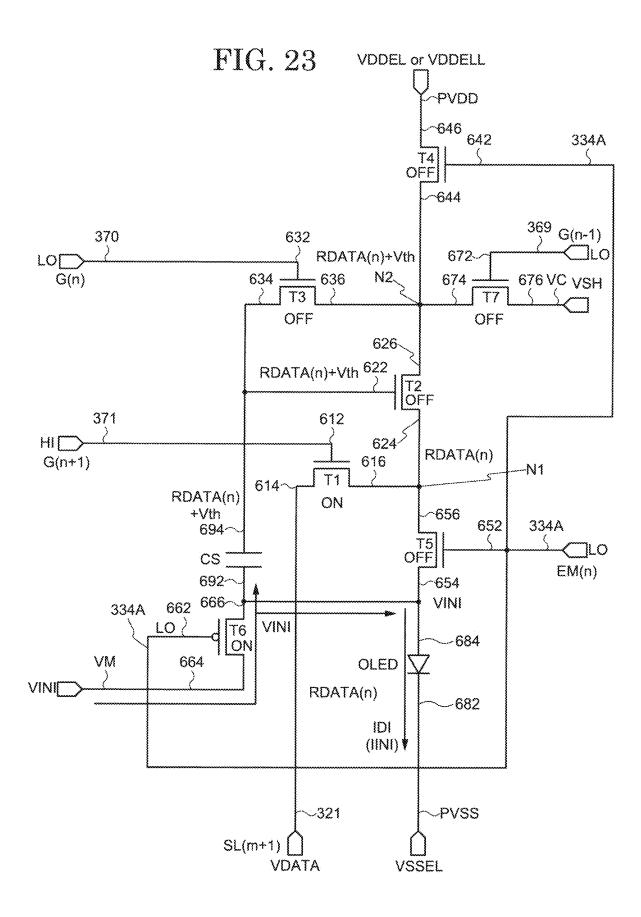

[0030] FIG. 23 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 18.

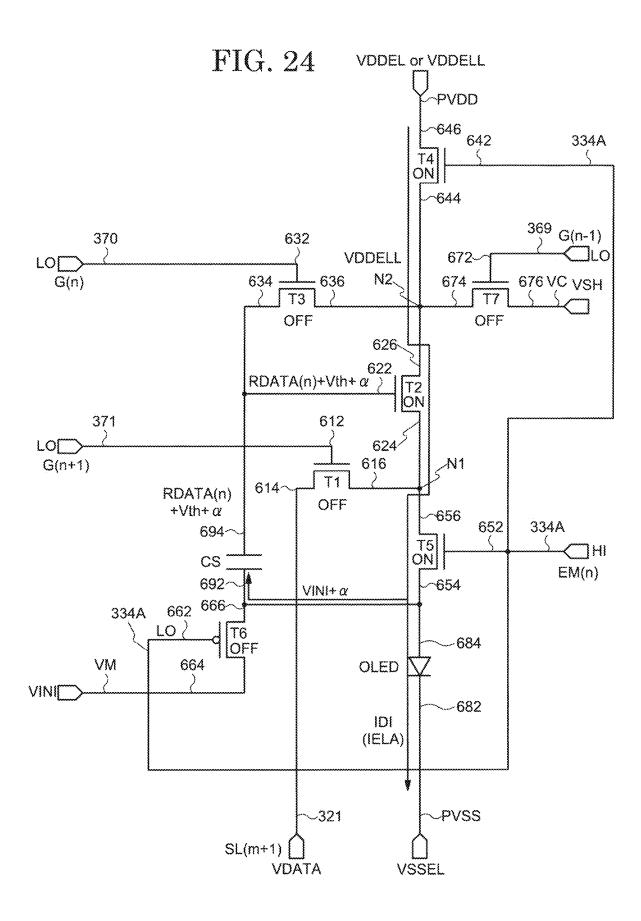

[0031] FIG. 24 is a schematic diagram showing an operation state of the pixel at the timing shown in FIG. 18.

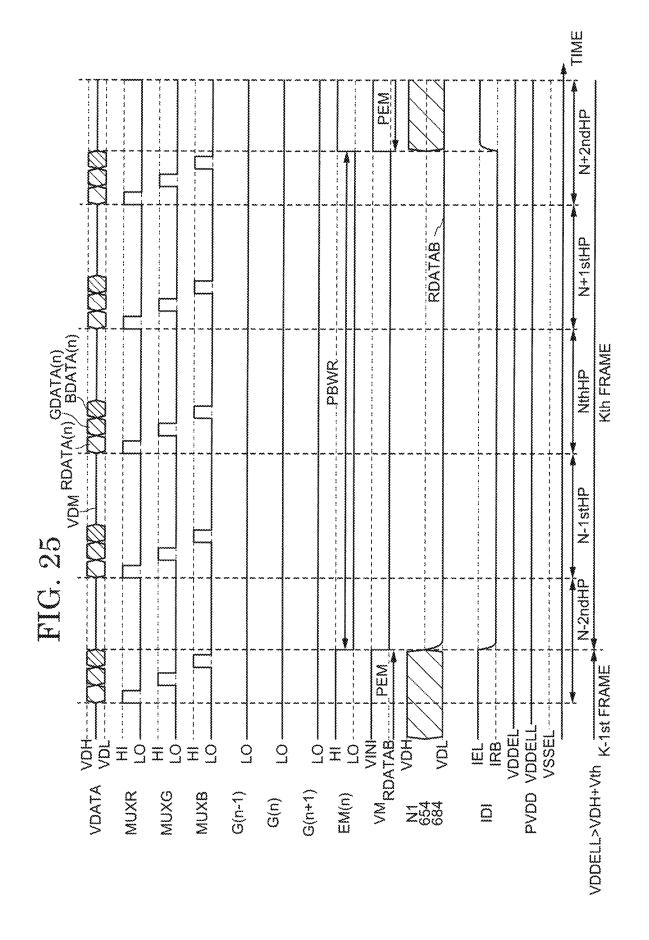

[0032] FIG. 25 is a schematic diagram showing a timing chart of the self-luminous display device according to the second embodiment of the present invention.

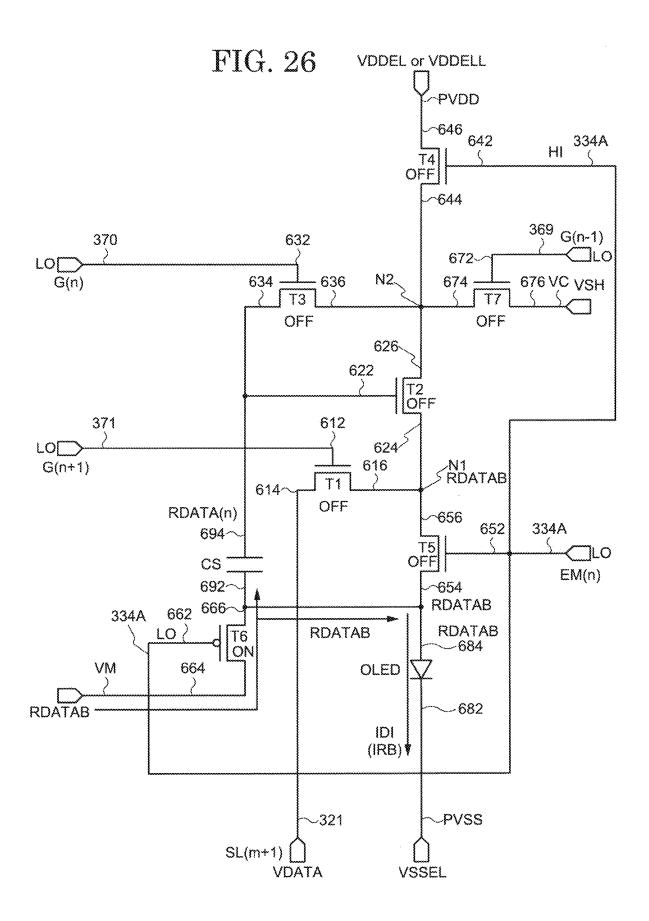

[0033] FIG. 26 is a schematic diagram showing an operation state of a pixel at the timing shown in FIG. 25.

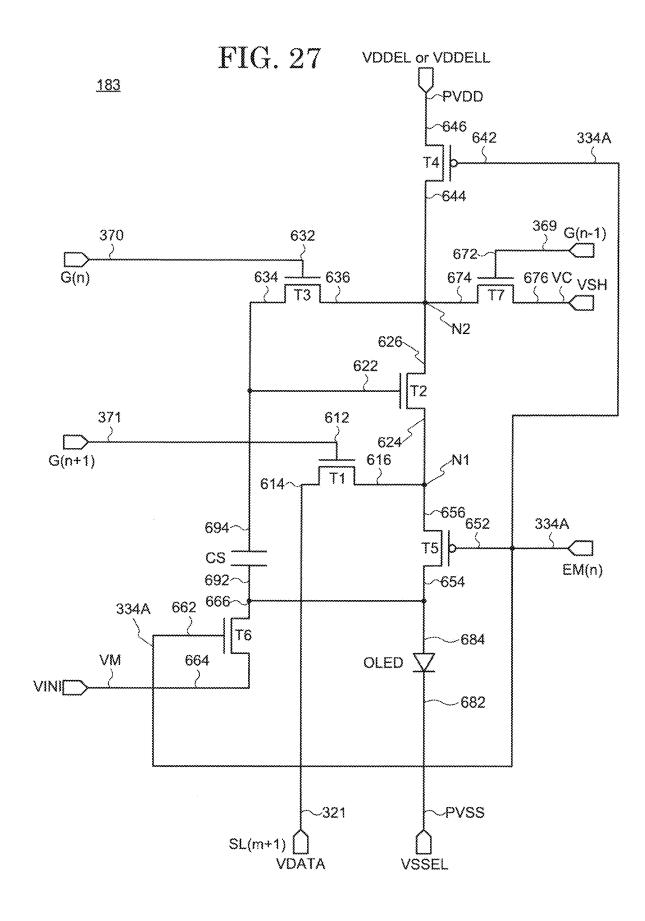

[0034] FIG. 27 is a circuit diagram showing a configuration of a pixel circuit according to a third embodiment of the present invention.

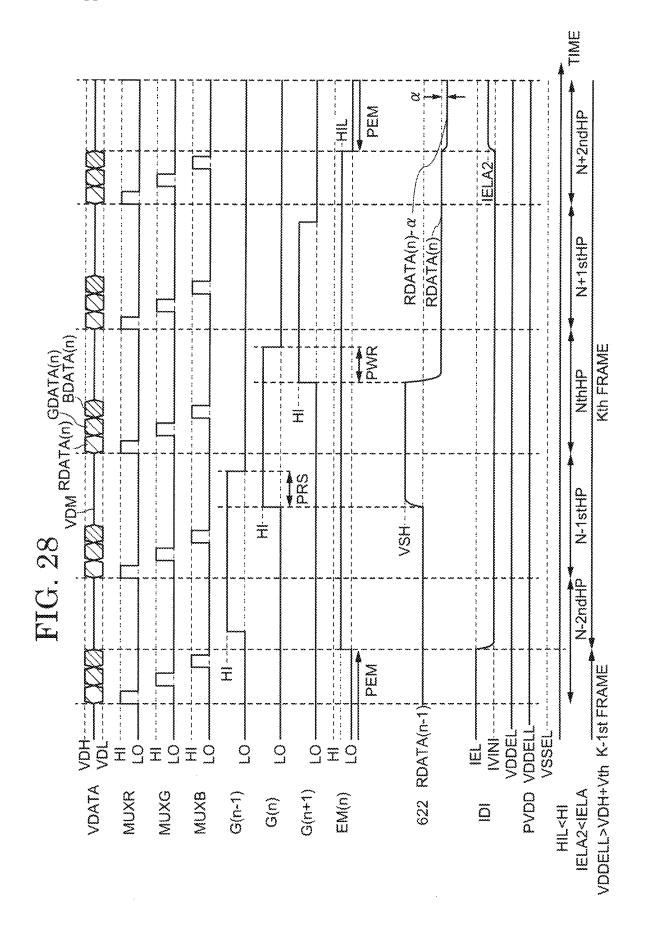

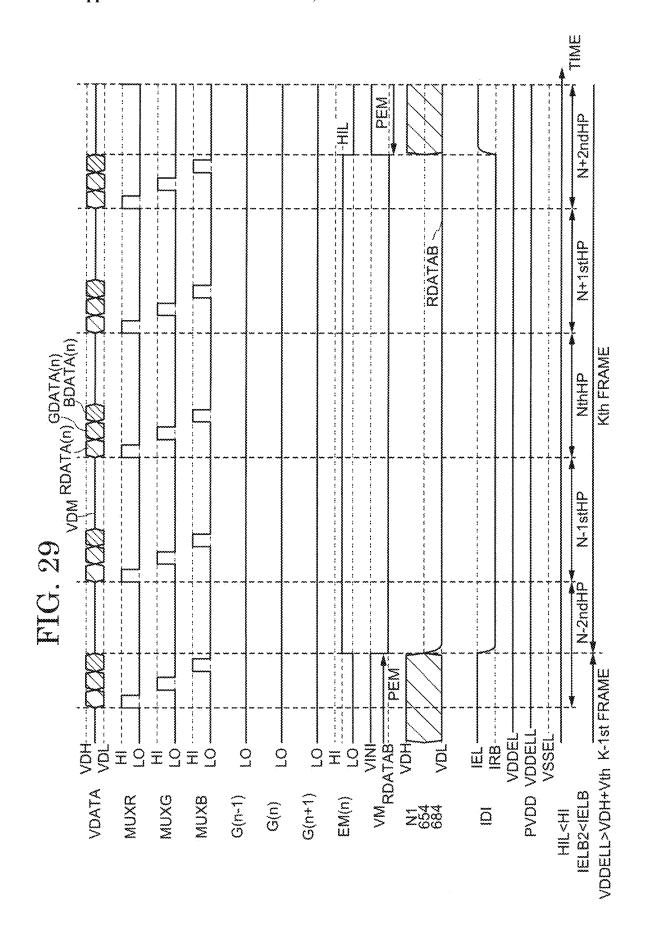

[0035] FIG. 28 is a schematic diagram showing a timing chart of a self-luminous display device according to the third embodiment of the present invention.

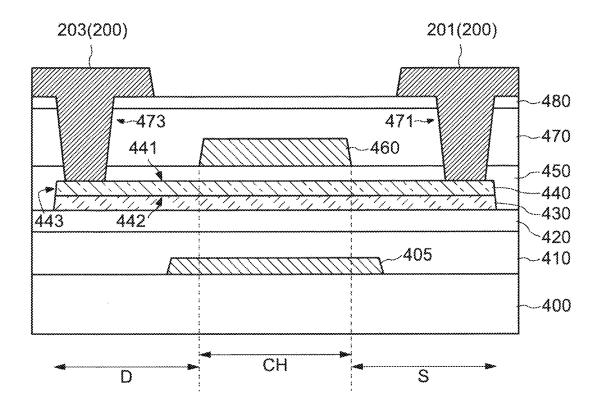

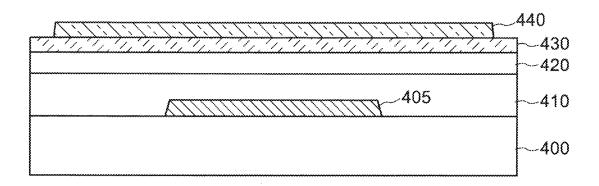

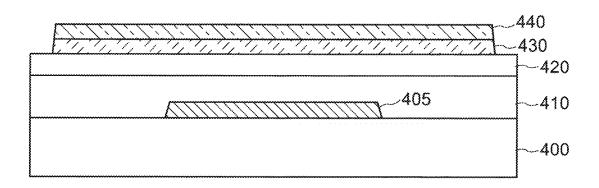

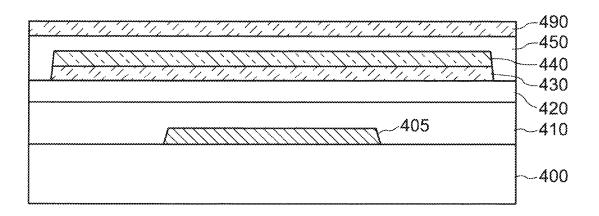

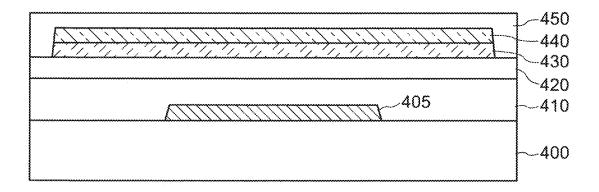

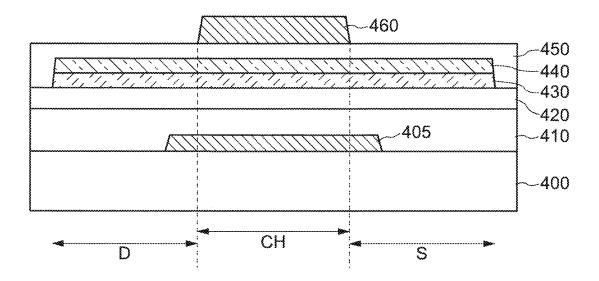

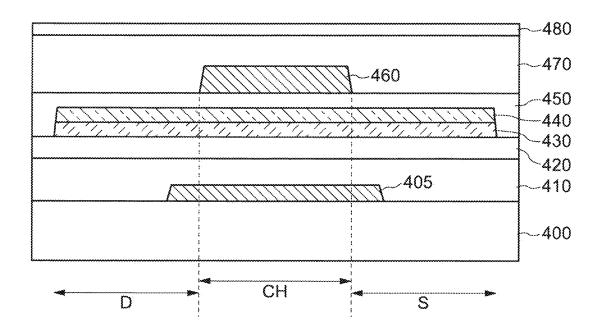

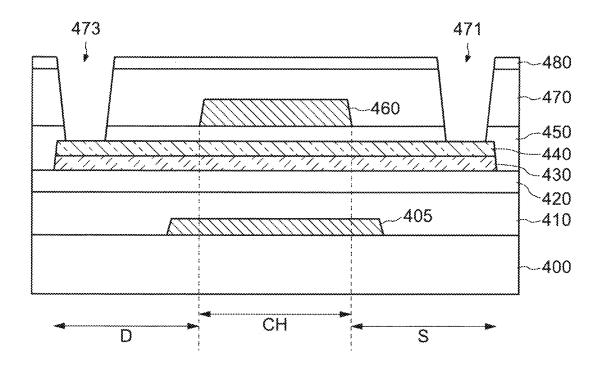

[0036] FIG. 30 is a cross-sectional view showing an overview of a semiconductor device according to a fourth embodiment of the present invention.

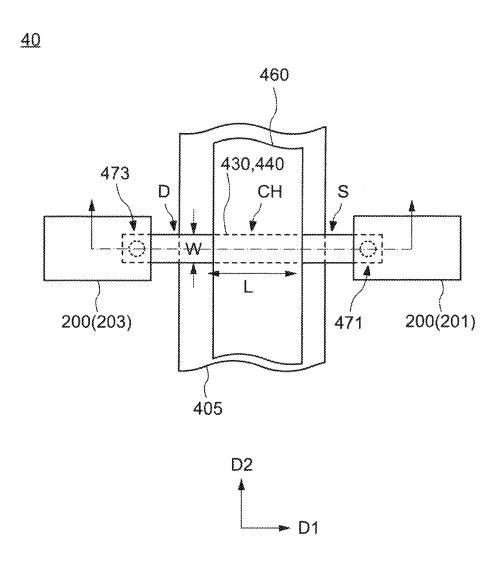

[0037] FIG. 31 is a plan view showing an overview of the semiconductor device according to the fourth embodiment of the present invention.

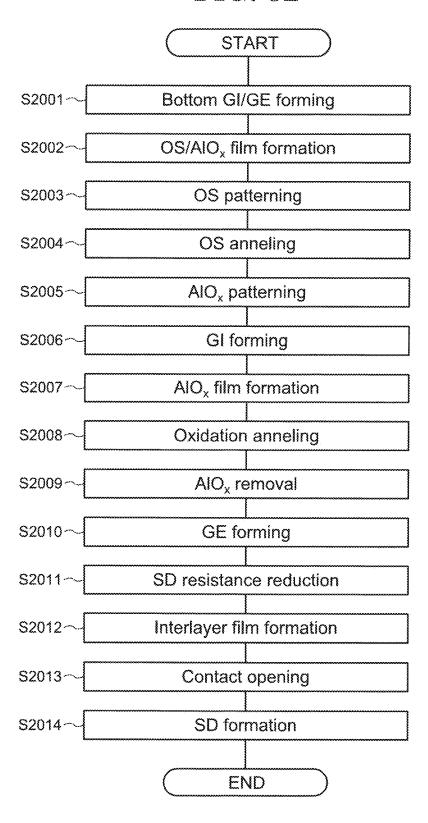

[0038] FIG. 32 is a sequence diagram showing a method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

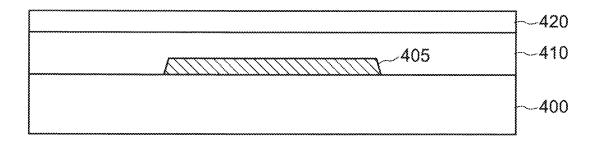

[0039] FIG. 33 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

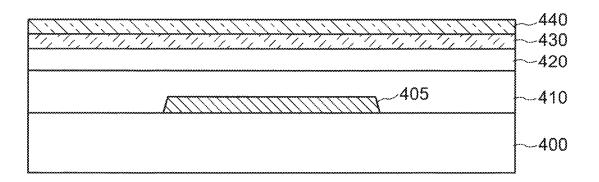

[0040] FIG. 34 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

[0041] FIG. 35 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

[0042] FIG. 36 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

[0043] FIG. 37 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

[0044] FIG. 38 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

[0045] FIG. 39 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

[0046] FIG. 40 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

[0047] FIG. 41 is a cross-sectional view showing the method for manufacturing the semiconductor device according to the fourth embodiment of the present invention.

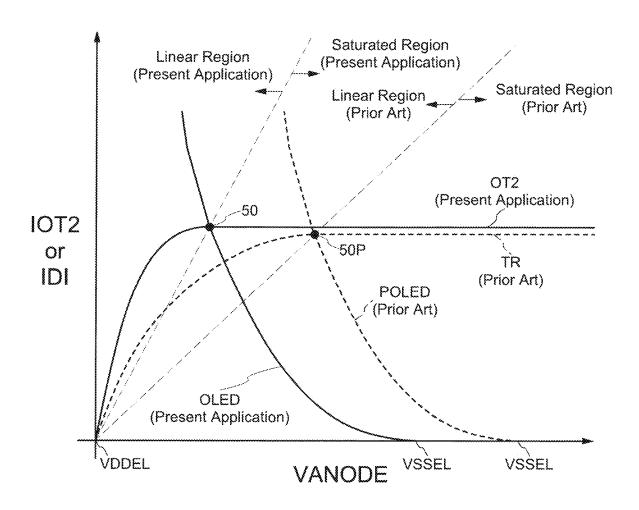

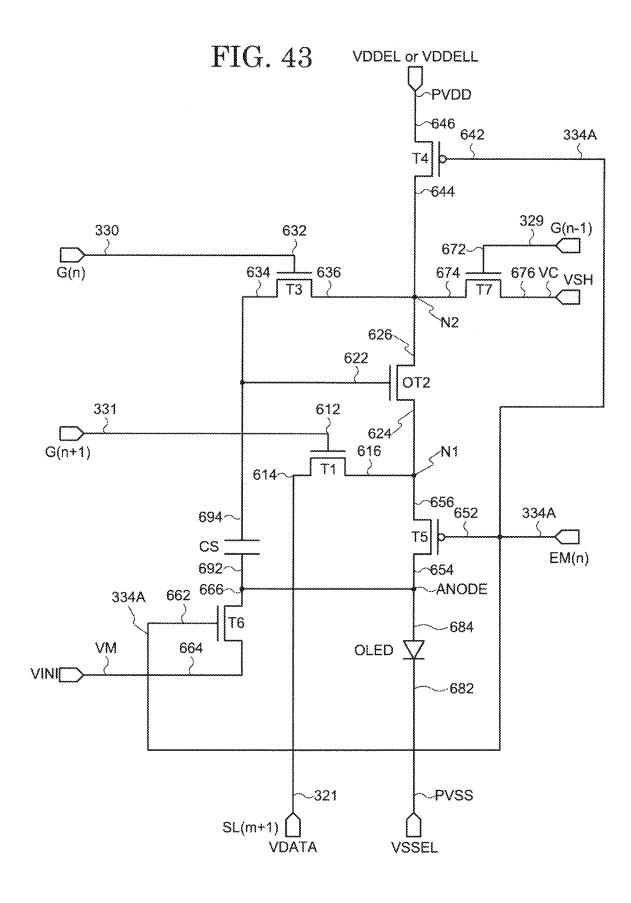

[0048] FIG. 42 is a graph showing an example of the electrical characteristics of the semiconductor device according to the fourth embodiment of the present invention and shows an example of the electrical characteristics of a semiconductor device according to a comparative example. [0049] FIG. 43 is a schematic diagram showing a configuration of a pixel circuit according to the fourth embodiment

## DESCRIPTION OF EMBODIMENTS

of the present invention.

[0050] Hereinafter, embodiments of the present invention will be described with reference to the drawings and the like. However, the present invention can be implemented in many different aspects, and should not be construed as being limited to the description of the embodiments exemplified below. Further, in order to make the description clearer, although the drawings may be schematically represented with respect to the width, thickness, shape, configuration, and the like of each part as compared with the actual embodiment, they are merely examples, and do not limit the interpretation of the present invention. It should be noted that the terms "first" and "second" for each element are convenient labels used to distinguish each element, and do not have any further meaning unless otherwise described.

[0051] Also, in the present specification, the expression "a includes A, B, or C," "a includes any of A, B or C," "a includes one selected from the group consisting of A, B and C," and the like does not exclude cases where a includes a plurality of combinations of A to C unless otherwise specified. Furthermore, these expressions do not exclude the case where a includes other elements.

[0052] In a self-luminous display device described in U.S. Patent Application Publication No. 2016/0284276, in the case where power consumption is reduced by adjusting a power supply voltage electrically connected to a light emitting element, the luminance of the light emitting element (self-luminous display device) may decrease.

[0053] In view of such problems, an object of an embodiment of the present invention is to provide a display device capable of reducing power consumption while suppressing a decrease in luminance of a light emitting element (self-luminous display device) and a method for driving the display device.

[0054] A display device according to an embodiment of the present invention is, for example, a self-luminous display device, and is a light emitting device using an EL element as a light emitting element.

# 1. First Embodiment

# [1-1. Overview of Self-Luminous Display Device 10]

[0055] An overview of a self-luminous display device 10 according to a first embodiment will be described with reference to FIG. 1 and FIG. 2. FIG. 1 and FIG. 2 are schematic diagrams showing a configuration of the self-luminous display device 10 according to the first embodiment. The configuration of the self-luminous display device 10 shown in FIG. 1 and FIG. 2 is an example, and the configuration of the self-luminous display device 10 is not limited to the configuration shown in FIG. 1 and FIG. 2.

[0056] As shown in FIG. 1 or FIG. 2, the self-luminous display device 10 includes an array substrate 100, a flexible printed circuit board 160 (FPC 160), and an IC chip 170. The self-luminous display device 10 includes a display region 22 arranged on the array substrate 100, a peripheral region 24 surrounding the display region 22, and a terminal region 26. [0057] A plurality of pixels 180 in the display region 22 are arranged in a matrix. The pixel 180 is the smallest unit constituting a part of an image to be displayed in the display region 22. For example, each of the plurality of pixels 180 may correspond to a sub-pixel R, a sub-pixel G, and a sub-pixel B. One pixel may be formed by three sub-pixels. An array of the pixels 180 is not limited. For example, the array of the plurality of pixels 180 is a stripe array. The array of the self-luminous display device 10 may be a delta array, a pentyle array, or the like.

[0058] The sub-pixel R, the sub-pixel G, and the sub-pixel B are configured to display images of different colors. For example, each of the sub-pixel R, the sub-pixel G, and the sub-pixel B may include a light emitting element including a light emitting layer that emits three primary colors of red, green, and blue. An arbitrary voltage or current is supplied to each of the three sub-pixels, and the self-luminous display device 10 can display an image.

[0059] A source driver circuit 110, a first gate driver circuit 120, a first light emission control circuit 130, and a second light emission control circuit 140 are arranged in the peripheral region 24. Each of the source driver circuit 110, the first gate driver circuit 120, the first light emission control circuit 130, and the second light emission control circuit 140 is connected to a terminal portion 150 using a connection wiring 341. The peripheral region 24 may be referred to as a frame region. The connection wiring 341 may be referred to as the connection wirings 341 may be referred to as the connection wirings 341 may be referred to as the connection wirings 341.

[0060] The terminal portion 150 and the FPC 160 electrically connected to the terminal portion 150 are arranged in the terminal region 26. The terminal region 26 is a region opposed to a first direction D1 with respect to a region in which the display region 22 is arranged with respect to the peripheral region 24.

[0061] The FPC 160 is connected to an external device (not shown) on an outer side of the self-luminous device 10. The self-luminous display device 10 is connected to the external device via the FPC 160 and the terminal portion 150 connected to the FPC. A control signal and a voltage are transmitted from the external device to the self-luminous display device 10 via the FPC 160 and the terminal portion 150 connected to the FPC. The self-luminous display device 10 drives each of the pixels 180 arranged in the self-luminous display device 10 by using the received control signal and voltage from the external device. As a result, the self-luminous display device 10 can display an image in the display region 22.

[0062] For example, the IC chip 170 is arranged on the FPC 160. The IC chip 170 supplies signals, voltages, and the like for driving each of the pixels 180 to the source driver circuit 110, the first gate driver circuit 120, the first light emission control circuit 130, the second light emission control circuit 140, and a pixel circuit via the FPC 160, the terminal portion 150, and the connecting wiring 341.

[0063] In the first embodiment, each of the source driver circuit 110, the first gate driver circuit 120, the first light

emission control circuit 130, the second light emission control circuit 140, and the IC chip 170 may be referred to as a control circuit alone, and a circuit group including a part or all of the source driver circuit 110, the first gate driver circuit 120, the first light emission control circuit 130, the second light emission control circuit 140, and the IC chip 170 may be referred to as a control circuit.

# [1-2. Configuration of Source Driver Circuit 110]

[0064] Referring to FIG. 1 and FIG. 2, an overview of the source driver circuit 110 will be described. As shown in FIG. 1 or FIG. 2, the source driver circuit 110 is arranged at a position adjoining the display region 22 in a first direction D1 (column direction). An image data signal line 321 extends from the source driver circuit 110 in the first direction D1 and is connected to the plurality of pixels 180 arranged in the first direction D1.

[0065] As shown in FIG. 2, for example, the source driver circuit 110 includes a plurality of selection circuits 112. Each of the plurality of selection circuits 112 is controlled based on, for example, an on signal and an off signal supplied to a selection signal MUXR, a selection signal MUXG, and a selection signal MUXB. The selection circuit 112 is selected by an on signal arranged to a selection signal (for example, the selection signal MUXR). The pixel 180 is electrically connected to the image data signal line 321, a first scanning signal line 330, and the like. In addition, the selection circuit 112 supplies the pixel 180 with the image data signal SL (m+1) including a data signal VDATA supplied to an input terminal 114. The data signal VDATA includes, for example, a voltage RDATA (n), a voltage GDATA (n), or a voltage BDATA (n).

[0066] For example, the selection circuit 112 is a switch 118 including the input terminal 114 and an output terminal 116. For example, the input terminal 114 and the output terminal 116 are conductive (connected) by an on signal supplied from the IC chip 170 to the selection signal MUXR, and the input terminal 114 and the output terminal 116 are cut off (disconnected) by an off signal supplied from the IC chip 170 to the selection signal MUXR. The on signal is a signal including a voltage that conducts between the input terminal 114 and the output terminal 116, and the off signal is a signal including a voltage that blocks the input terminal 114 and the output terminal 116.

[0067] In the present invention, the on signal may be high level (High, HI), the off signal may be low level (Low, LO), the on signal may be low level (Low, LO), and the off signal may be high level (High, HI).

[1-3. Configurations of First Gate Driver Circuit 120 and Second Gate Driver Circuit 190]

[0068] An overview of the first gate driver circuit 120 will be described with reference to FIG. 1 and FIG. 2. As shown in FIG. 1 or FIG. 2, the first gate driver circuit 120 is arranged at a position adjoining the display region 22 in a second direction D2 (row direction). First scanning signal lines 329, 330, 331, 332, and 333 extend from the first gate driver circuit 120 in the second direction D2 and are connected to the plurality of pixels 180 arranged in the second direction D2.

[0069] As shown in FIG. 2, the first gate driver circuit 120 includes a plurality of shift registers (for example, shift registers 121, 122, and 123). For example, the shift registers

121, 122, and 123 sequentially supply different scanning signals of timing (for example, a scanning signal GF (n-1), a scanning signal GF (n), and a scanning signal GF (n+1)) respectively to the first scanning signal lines 329, 330, and 331 based on control signals such as a clock signal and a start pulse supplied from the IC chip 170, and have a role of driving the pixels 180 (pixel circuit) electrically connected to each of the first scanning signal lines.

[0070] For example, the shift register 121 is electrically connected to the shift register 122 and the shift register 122 is electrically connected to the shift register 123. For example, the shift register 121 is electrically connected to the first scanning signal line 329 and supplies the scanning signal GF (n-1) to the first scanning signal line 329. For example, similar to the shift register 121, the shift register 122 is electrically connected to the first scanning signal line 330 and supplies the scanning signal GF (n) to the first scanning signal line 330, and the shift register 123 is electrically connected to the first scanning signal line 331 and supplies the scanning signal GF (n+1) to the first scanning signal line 331. Although not shown, a shift register of a next stage electrically connected to the shift register 123 is electrically connected to the first scanning signal line 332. The scanning signal GF (n) includes a pulse-width equivalent to the scanning signal GF (n-1), and is a signal obtained by shifting the scanning signal GF(n-1). The scanning signal GF (n+1) includes a pulse-width equivalent to the scanning signal GF (n), and is a signal obtained by shifting the scanning signal GF (n). Similar to the scanning signal GF (n+1), the scanning signal GF (n+2)includes the same pulse-width as the scanning signal GF (n+1), and is a signal obtained by shifting the scanning signal GF (n+1).

[0071] An overview of a second gate driver circuit 190 will be described with reference to FIG. 1 and FIG. 2. The second gate driver circuit 190 in the embodiment shown in FIG. 1 or FIG. 2 is arranged at a position adjoining the first gate driver circuit 120 in the second direction D2 (row direction). The position of the second gate driver circuit 190 is not limited to the position shown in FIG. 1 or FIG. 2. The second gate driver circuit 190 may be arranged between the first gate driver circuit 120 and the display region 22. Second scanning signal lines 349, 350, 351, and 352 extend from the second gate driver circuit 190 in the second direction D2 and are connected to the plurality of pixels 180 arranged in the second direction D2.

[0072] As shown in FIG. 2, the second gate driver circuit 190 includes a plurality of shift registers (for example, shift registers 191, 192, and 193). The shift registers 191, 192, and 193 have the same configuration and function as the shift registers 121, 122, and 123. For example, the shift registers 191, 192, and 193 sequentially supply different scanning signals of timing (for example, a scanning signal GS (n+1), a scanning signal GS (n+2), and a scanning signal GS (n+3)) respectively to the second scanning signal lines 349, 350, 351, and 352 based on control signals such as a clock signal and a start pulse supplied from the IC chip 170. That is, the shift registers 191, 192, and 193 have a function of driving the pixels 180 (pixel circuits) electrically connected to each of the second scanning signal lines. Here, the control signals such as the clock signal and the start pulse supplied to the shift registers 191, 192, and 193 are synchronized with the control signals such as the clock signal and the start pulse supplied to the shift registers 121, 122,

and 123. The control signals such as the clock signal and the start pulse supplied to shift registers 191, 192, and 193 may be the same as the control signals such as the clock signal and the start pulse supplied to shift registers 121, 122, and 123. That is, the second gate driver circuit 190 is synchronized with the first gate driver circuit 120.

[0073] For example, the shift register 191 is electrically connected to the shift register 192 and the shift register 192 is electrically connected to the shift register 193. For example, the shift register 191 is electrically connected to the second scanning signal line 349 and supplies the scanning signal GS (n+1) to the second scanning signal line 349. For example, similarly to the shift register 191, the shift register 192 is electrically connected to the second scanning signal line 350 and supplies the scanning signal GS (n+2) to the second scanning signal line 350, and the shift register 193 is electrically connected to the second scanning signal line 351 and supplies the scanning signal GS (n+3) to the second scanning signal line 351. The second scanning signal GS (n+2) includes a pulse-width equivalent to the scanning signal GS (n+1), and is a signal obtained by shifting the scanning signal GS (n+1). The scanning signal GS (n+3) includes a pulse-width equivalent to the scanning signal GS (n+2), and is a signal obtained by shifting the scanning signal GS(n+2).

[0074] As described above, the first gate driver circuit 120 and the second gate driver circuit 190 are synchronized. The pulse-width of each of the scanning signals supplied to each of the scanning signal lines by the first gate driver circuit 120 and the second gate driver circuit 190 are equal to each other. Further, since the first gate driver circuit 120 and the second gate driver circuit 190 are synchronized, the scanning signal GF (n) becomes the signal obtained by shifting the scanning signal GF (n-1), the scanning signal GS (n+1) becomes a signal corresponding to the signal obtained by shifting the scanning signal GF (n), the scanning signal GF (n+1) becomes a signal corresponding to the signal obtained by shifting the scanning signal GS (n+1), and GS (n+2) becomes a signal corresponding to the signal obtained by shifting the scanning signal GF (n+1). That is, the shift register 121, the shift register 122, the shift register 191, the shift register 123, the shift register 192, and a shift register included in the first gate driver circuit 120 and connected to the shift register 123, and the shift register 193 are sequentially output with the shifted scanning signals. Thereafter, the shift register included in the first gate driver circuit 120 and a shift register included in the second gate driver circuit 190 alternately output the sequentially shifted scanning signals. The scanning signal GF (n) may be referred to as a first control signal, the scanning signal GS (n+1) may be referred to as a second control signal, and the scanning signal GF (n-1) may be referred to as a third control signal.

[1-4. Configurations of First Light Emission Control Circuit 130 and Second Light Emission Control Circuit 140]

[0075] Referring to FIG. 1 and FIG. 2, overviews of the first light emission control circuit 130 and the second light emission control circuit 140 will be described. As shown in FIG. 1 or FIG. 2, the first light emission control circuit 130 is arranged adjacent to the display region 22 in the second direction D2 (row direction) and opposite to a position where the first gate driver circuit 120 is disposed with respect to the display region 22. First light emission control lines 334, 335, and 336 extend from the first light emission

control circuit 130 in the second direction D2 and are connected to the plurality of pixels 180 (pixel circuits) arranged in the second direction D2.

[0076] As shown in FIG. 2, the first light emission control circuit 130 includes a plurality of shift registers (for example, shift registers 131, 132, and 133). The shift registers 131, 132, and 133 sequentially supply different first light emission control signals of timing (for example, a first light emission control signal EF (n), a first light emission control signal EF (n+1), and a first light emission control signal EF (n+2)) respectively to the first light emission control signals such as a clock signal and a start pulse supplied from the IC chip 170. That is, the shift registers 131, 132, and 133 have a function of driving the pixels 180 (pixel circuits) electrically connected to the first light emission control signal lines.

[0077] For example, the shift register 131 is electrically connected to the shift register 132 and the shift register 132 is electrically connected to the shift register 133. For example, the shift register 131 is electrically connected to the first light emission control signal line 334 and supplies the first light emission control signal EF (n) to the first light emission control signal line 334. For example, similar to the shift register 131, the shift register 132 is electrically connected to the first light emission control signal line 335 and supplies the first light emission control signal EF (n+1) to the first light emission control signal line 335, and the shift register 133 is electrically connected to the first light emission control signal line 336 and supplies the first light emission control signal EF (n+2) to the first light emission control signal line 336. A pulse-width of the first light emission control signal EF (n+1) is the same as the first light emission control signal EF (n), and the first light emission control signal EF (n+1) is a signal obtained by shifting the first light emission control signal EF (n). Similarly, a pulsewidth of the first light emission control signal EF(n+2) is the same as the first light emission control signal EF (n+1), and the first light emission control signal EF (n+2) is a signal obtained by shifting the first light emission control signal EF (n+1). The first light emission control signal EF may be referred to as a fourth control signal.

[0078] As shown in FIG. 2, the second light emission control circuit 140 is arranged adjacent to the first light emission control circuit 130 in the second direction D2 (row direction) and opposite to the position where the first gate driver circuit 120 is disposed with respect to the display region 22. The second light emission control lines 337, 338, and 339 extend from the second light emission control circuit 140 in the second direction D2 and are connected to the plurality of pixels 180 (pixel circuit) arranged in the second direction D2.

[0079] The second light emission control circuit 140 includes a plurality of shift registers (for example, shift registers 141, 142, and 143). For example, the shift registers 141, 142, and 143 sequentially supply different second light emission control signals of timing (for example, a second light emission control signal ES (n), a second light emission control signal ES (n+1), and a second light emission control signal ES (n+2)) respectively to the second light emission control signal lines 337, 338, and 339 based on the control signals such as a clock signal and a start pulse supplied from the IC chip 170. That is, the shift registers 141, 142, and 143 have a function of driving the pixels 180 (pixel circuit)

electrically connected to the second light emission control signal lines. The second light emission control signal ES may be referred to as a fifth control signal.

[0080] For example, the shift register 141 is electrically connected to the shift register 142 and the shift register 142 is electrically connected to the shift register 143. For example, the shift register 141 is electrically connected to the second light emission control signal line 337 and supplies the second light emission control signal ES (n) to the second light emission control signal line 337. For example, similar to the shift register 141, the shift register 142 is electrically connected to the second light emission control signal line 338 and supplies the second light emission control signal ES (n+1) to the second light emission control signal line 338, and the shift register 143 is electrically connected to the second light emission control signal line 339 and supplies the second light emission control signal ES (n+2) to the second light emission control signal line 339. A pulse-width of the second light emission control signal ES (n+1) is the same as a pulse-width of the second light emission control signal ES (n), and the second light emission control signal ES (n+1) is a signal obtained by shifting the second light emission control signal ES (n). Similarly, a pulse-width of the second light emission control signal ES (n+2) is the same as a pulse-width of the second light emission control signal ES (n+1), and the second light emission control signal ES (n+2) is a signal obtained by shifting the second light emission control signal ES (n+1). [0081] In addition, a position of the first light emission control circuit 130 and a position of the second light emission control circuit 140 may be interchanged with respect to the second direction D2 (row direction).

## [1-5. Configuration of Pixel 180]

[0082] Referring to FIG. 3 and FIG. 4, an overview of the pixel 180 will be described. FIG. 3 is a schematic diagram showing an input signal to a pixel circuit 181 included in the pixel 180. FIG. 4 is a circuit diagram showing a configuration of the pixel circuit 181. For example, FIG. 3 and FIG. 4 show the configuration of the pixel circuit 181 of the pixel 180 shown in FIG. 1 and FIG. 2. Configurations of the pixel 180 and the pixel circuit 181 are not limited to the configurations shown in FIG. 3 and FIG. 4. The same or similar configurations as those in FIG. 1 and FIG. 2 will not be described here.

[0083] The pixel circuit 181 is a circuit for driving the pixel 180. Pixel circuits of the sub-pixel R, the sub-pixel G, and the sub-pixel B included in the pixel 180 are the same as the pixel circuit 181, and differ in colors emitted by light emitting elements OLED. A light emitting element OLED that emits red will be mainly described in the following explanation.

[0084] As shown in FIG. 3, the pixel circuit 181 is supplied with the scanning signal GF (n-1), the scanning signal GF (n), the scanning signal GS (n+1), the image data signal SL (m+1), the first light emission control signal EF (n), the second light emission control signal ES (n), a reset voltage VSH, and an initialization voltage VINI. Further, a driving voltage VDDEL or a driving voltage VDDELL and a reference voltage VSSEL are supplied to the pixel circuit 181 as a power source for driving the pixel 180.

[0085] The reset voltage VSH is supplied to a reset voltage line VC, the initialization voltage VINI is supplied to an initialization voltage line VM, the driving voltage VDDEL

and the driving voltage VDDELL are supplied to a drive power supply line PVDD, and the reference voltage VSSEL is supplied to a reference voltage line PVSS. Each of the reset voltage line VC, the initialization voltage line VM, the drive power supply line PVDD, and the reference voltage line PVSS may be electrically connected to, for example, a different connection line 341 or may be a different connection line 341. The reset voltage VSH, the initialization voltage VINI, the driving voltage VDDEL, the driving voltage VDDELL, and the reference voltage VSSEL may be supplied from an external circuit to the plurality of pixels 180 (the pixel circuit 181) via the FPC 160, the terminal portion 150, the reset voltage line VC, the initialization voltage line VM, the drive power supply line PVDD, and the reference voltage line VSSEL. In addition, the reset voltage VSH, the initialization voltage VINI, the driving voltage VDDEL, the driving voltage VDDELL, and the reference voltage VSSEL may be supplied from the IC chip 170 to the plurality of pixels 180 (the pixel circuits 181) via the FPC 160, the terminal portion 150, the reset voltage line VC, the initialization voltage line VM, the drive power supply line PVDD, and the reference voltage line PVSS. The reset voltage VSH and the initialization voltage VINI are smaller than the driving voltage VDDEL and the driving voltage VDDELL. The driving voltage VDDELL is smaller than the driving voltage VDDEL. The reference voltage VSSEL is smaller than the driving voltage VDDELL. The reset voltage VSH is, for example, bigger than the voltage included in the data signal VDATA (for example, the voltage RDATA (n), the voltage GDATA (n) or the voltage BDATA (n)).

[0086] As shown in FIG. 4, the pixel circuit 181 includes a transistor T1, a transistor T2, a transistor T3, a transistor T4, a transistor T6, a transistor T7, a capacitive element CS and a light emitting element OLED. Each of these transistors includes a gate electrode and a pair of electrodes including a first electrode and a second electrode (a source electrode and a drain electrode). Each of the capacitive element CS and the light emitting element OLED has a pair of electrodes including a first electrode and a second electrode.

[0087] For example, the transistor T1 is a selection transistor. The transistor T1 has a function of supplying an image data signal SL (m+1) to the transistor T2.

[0088] For example, the transistor T2 is a driving transistor. The transistor T2 has a function of causing the light emitting element OLED to emit light by supplying a current to the light emitting element OLED using the input image data signal SL (m+1).

[0089] The transistor T3 has a function of conducting a second node N2 and a gate electrode 622 of the transistor T2 (and a second electrode 694 of the capacitive element CS), supplying the reset voltage VSH to the gate electrode 622 of the transistor T2, and resetting the gate electrode 622 of the transistor T2. The transistor T3 has a function of accumulating a charge corresponding to a threshold voltage Vth of the transistor T2 in the gate electrode 622 of the transistor T2 and the second electrode 694 of the capacitive element CS.

[0090] The transistor T4 controls connection and disconnection between the drive power supply line PVDD and the transistor T2. That is, the transistor T4 has a function of supplying the driving voltage VDDEL to the transistor T2. [0091] The transistor T5 controls connection and disconnection

[0091] The transistor T5 controls connection and disconnection between the transistor T2 and the light emitting element OLED. In other words, the transistor T5 has a

function of controlling connection and disconnection between the transistor T2 and the light emitting element OLED, and supplying a current to the light emitting element OLED to control light emission and non-light emission of the light emitting element OLED.

[0092] The transistor T6 has a function of initializing a first electrode 654 of the transistor T5, a second electrode 684 of the light emitting element OLED, and a first electrode 692 of the capacitive element CS by supplying the initialization voltage VINI to the first electrode 654 of the transistor T5, the second electrode 684 of the light emitting element OLED, and the first electrode 692 of the capacitive element CS.

[0093] The transistor T7 has a function of supplying the reset voltage VSH to a first electrode 644 of the transistor T4, a second electrode 626 of the transistor T2, a second electrode 636 of the transistor T3, and the like, and resetting the first electrode 644 of the transistor T4, the second electrode 626 of the transistor T2, and the second electrode 636 of the transistor T3.

[0094] For example, the capacitive element CS has a function of holding the charge (first charge) corresponding to the threshold voltage Vth of the transistor T2. The capacitive element CS has a function of holding a charge (second charge) corresponding to a data voltage (for example, RDATA (n) (see FIG. 6)) included in the image data signal SL (m+1) input to the gate electrode 622 of the transistor T2.

[0095] The light emitting element OLED has a diode characteristic and has a function of emitting light based on a current flowing through the light emitting element OLED (that is, a drain current of the transistor T2).

[0096] The transistor T1 includes a gate electrode 612, a first electrode 614, and a second electrode 616. The gate electrode 612 is electrically connected to the second scanning signal line 349. The first electrode 614 is electrically connected to the image data signal line 321. The second electrode **616** is electrically connected to a first node N1, a first electrode 624 of the transistor T2, and a second electrode **656** of the transistor T5. The scanning signal GS (n+1) is supplied to the second scanning signal line 349. A conduction state (on state) and a non-conduction state (off state) are controlled by the scanning signal GS (n+1) in the transistor T1. The first transistor T1 becomes non-conductive in the case where the signal supplied to the scanning signal GS (n+1) is low level (LO). The first transistor T1 becomes conductive in the case where the signal supplied to the scanning signal GS (n+1) is high level (HI).

[0097] The transistor T2 includes the gate electrode 622, the first electrode 624, and the second electrode 626. The gate electrode 622 is electrically connected to a first electrode 634 of the transistor T3 and the second electrode 694 of the capacitive element CS. The second electrode 626 is electrically connected to the second node N2, the second electrode 636 of the transistor T3, a first electrode 674 of the transistor T7, and the first electrode 644 of the transistor T4. [0098] The transistor T3 includes a gate electrode 632, the first electrode 634, and the second electrode 636. The gate electrode 632 is electrically connected to the first scanning

electrode **634**, and the second electrode **636**. The gate electrode **632** is electrically connected to the first scanning signal line **330**. The scanning signal GF (n) is supplied to the first scanning signal line **330**. The conduction state (on state) and the non-conduction state (off state) are controlled by the scanning signal GF (n) in the transistor T3. The transistor T3 becomes non-conductive in the case where the signal sup-

plied to the scanning signal GF(n) is low level (LO). The transistor T3 becomes conductive in the case where the signal supplied to the scanning signal GF(n) is high level (HD).

[0099] The transistor T4 includes a gate electrode 642, the first electrode 644, and a second electrode 646. The gate electrode 642 is electrically connected to the second light emission control signal line 337. The second electrode 646 is electrically connected to the drive power supply line PVDD. The drive power supply line PVDD is supplied with the driving voltage VDDEL. The second light emission control signal ES (n) is supplied to the second light emission control signal line 337. The conduction state (on state) and the non-conduction state (off state) are controlled by the second light emission control signal ES (n) in the transistor T4. The transistor T4 becomes non-conductive in the case where the signal supplied to the second light emission control signal ES (n) is low level (LO). The transistor T4 becomes conductive in the case where the signal supplied to the second light emission control signal ES (n) is high level (HI).

[0100] The transistor T5 includes a gate electrode 652, the first electrode 654, and the second electrode 656. The gate electrode 652 is electrically connected to the first light emission control signal line 334. The first electrode 654 is electrically connected to a second electrode 666 of the transistor T6, the first electrode 692 of the capacitive element CS, and the second electrode 684 of the light emitting element OLED. The first light emission control signal EF (n) is supplied to the first light emission control signal line 334. The conductive state (on state) and the non-conductive state (off state) are controlled by the first light emission control signal EF (n) in the transistor T5. The transistor T5 becomes non-conductive in the case where the signal supplied to the first light emission control signal EF (n) is low level (LO). The transistor T5 becomes conductive in the case where the signal supplied to the first light emission control signal EF (n) is high level (HI).

[0101] The transistor T6 includes a gate electrode 662, a first electrode 664, and the second electrode 666. The gate electrode 662 is electrically connected to the first scanning signal line 330. The first electrode 664 is electrically connected to the initialization voltage line VM. As described above, the scanning signal GF (n) is supplied to the first scanning signal line 330, and the initialization voltage VINI is supplied to the initialization voltage line VM. Similar to the transistor T3, the conductive state (on state) and the non-conductive state (off state) are controlled by the scanning signal GF (n) in the transistor T6. The transistor T6 becomes non-conductive in the case where the signal supplied to the scanning signal GF (n) is low level (LO). The transistor T6 becomes conductive in the case where the signal supplied to the scanning signal GF (n) is high level (HI).

[0102] The transistor T7 includes a gate electrode 672, the first electrode 674, and a second electrode 676. The gate electrode 672 is electrically connected to the first scanning signal line 329. The scanning signal GF (n-1) is supplied to the first scanning signal line 329. The second electrode 676 is electrically connected to the reset voltage line VC. As described above, the reset voltage line VC is supplied with the reset voltage VSH. The conductive state (on state) or the non-conductive state (off state) are controlled by the scanning signal GF (n-1) in the transistor T7. The transistor T7

becomes non-conductive in the case where the signal supplied to the scanning signal GF(n-1) is low level (LO). The transistor T7 becomes conductive in the case where the signal supplied to the scanning signal GF(n-1) is high level (HI).

[0103] A first electrode 682 of the light emitting element OLED is electrically connected to the reference voltage line PVSS. As described above, the reference voltage line PVSS is supplied with the reference voltage VSSEL. For example, the first electrode 682 of the light emitting element OLED is a cathode electrode, and the second electrode 684 of the light emitting element OLED is an anode electrode.

[0104] For example, a conduction state of a transistor in the self-luminous display device 10 is assumed to indicate a state in which a source electrode and a drain electrode of the transistor are in conduction and the transistor is in an on (ON) state, and the non-conduction state of the transistor in the self-luminous display device 10 is assumed to indicate a state in which the source electrode and the drain electrode of the transistor are in non-conduction and the transistor is in an off (OFF) state. In addition, the source electrode and the drain electrode may be interchanged depending on a voltage or a potential supplied to each electrode in each transistor. In addition, it can be easily understood by a person skilled in the art that a slight current flows, such as a leakage current, even when the transistor is in an off state.

[0105] Each transistor shown in FIG. 4 may have a Group 14 element, such as silicon or germanium, or an oxide exhibiting semiconductor characteristics in a channel region. For example, the channel region of each of the transistors has low-temperature polysilicon (LTPS). The transistors in the self-luminous display device 10 are formed using thin film transistors (TFT) and include n-channel field effect transistors. Each of the transistors In the self-luminous display device 10 may have either an n-channel field effect transistor or a p-channel field effect transistor. A configuration of the transistor, a connection of the storage capacitor, a power supply voltage, and the like may be appropriately adapted according to the application and specifications in the self-luminous display device 10.

[1-6. Method for Driving Self-Luminous Display Device 10]

[0106] Referring to FIG. 5A to FIG. 14, methods for driving the self-luminous displays 10 will be described. FIG. 5A, FIG. 5B, FIG. 6 and FIG. 13 are schematic diagrams showing timing charts of the self-luminous display device 10. FIG. 7 to FIG. 12 are schematic diagrams showing operation states of the pixel 180 (the pixel circuit 181) at the timing shown in FIG. 6. FIG. 14 is a schematic diagram showing an operation state of the pixel 180 (the pixel circuit 181) at the timing shown in FIG. 13. The method for driving the self-luminous display device 10 is not limited to the driving methods shown in FIG. 5A to FIG. 14. Descriptions of the same or similar configurations as those in FIG. 1 to FIG. 4 will be omitted. The horizontal axis of the timing charts indicates times (TIME).

[0107] FIG. 5A is a diagram showing a timing chart of the method for driving the self-luminous display device 10 in the case where the self-luminous display device 10 is driven at a higher frequency. For example, the higher frequency is 60 Hz and is the frequency at which one frame (1 FRAME) is driven by 60 Hz. For example, a part of the current frame (Kth FRAME), a part of a previous frame of the current frame (K-1st FRAME), and a part of a subsequent frame of

the current frame (K+1st FRAME) are shown in FIG. 5A. The driving method shown in FIG. 5A is referred to as high-frequency driving.

[0108] As shown in FIG. 5A, the method for driving the self-luminous display device 10 includes at least a reset period PRS, a sampling period PWR, and a light emission period PEM in one frame. The sampling period PWR is executed after the reset period PRS, and the emission period PEM is executed after the sampling period PWR in the pixel 180 (the pixel circuit 181) included in the self-luminous display device 10. Further, after a light emission period PEM of the previous frame of the current frame, a reset period PRS of the current frame is executed, and after a light emission period PEM of the current frame, a reset period PRS and a sampling period PWR of the subsequent frame of the current frame are executed.

[0109] FIG. 5B shows a timing chart of the method for driving a self-luminous display device 10 in the case where the self-luminous display device 10 is driven at a lower frequency. For example, the lower frequency is 1 Hz and is a frequency at which one frame (1 FRAME) is driven by 1 Hz. The driving methods shown in FIG. 5B are referred to as low-frequency driving. The low-frequency driving is a driving method in which a period (black period PBWR) for displaying black is executed a plurality of times in the light emission period PEM as compared with the high-frequency driving. The driving other than the black period PBWR in the low-frequency driving is the same as the high-frequency driving.

[0110] FIG. 6 is a diagram for describing a reset period PRS, a sampling period PWR, and an emission period PEM of a method for driving the pixels 180 (the pixel circuits 181) of the self-luminous display device 10. FIG. 6 shows the light emission period PEM of the previous frame of the current frame (K-1st FRAME), the reset period PRS, a sampling period PWR, and a light emission period PEM of the current frame (Kth FRAME). Further, FIG. 6 shows a plurality of one horizontal periods (horizontal period N-2nd HP, horizontal period N-1st HP, horizontal period Nth HP, horizontal period N+1st HP, horizontal period N+2nd HP). For example, one horizontal period is a period in which the image data signal SL (m+1) including the data signal VDATA is input to a pixel (pixel circuit) electrically connected to one second scanning signal line, the image data signal SL (m+1) including the data signal VDATA is input to a pixel (pixel circuit) electrically connected to all the second scanning signal lines, and an image of the current frame corresponding to 1 FRAME is displayed.

[0111] Referring to FIG. 6 to FIG. 12, an example of a driving method for the pixel 180 (pixel circuit 181) to display an image based on the voltage RDATA (n) included in the data signal VDATA input to the one horizontal period Nth HP will be described. In addition, the driving voltage VDDEL or the driving voltage VDDELL is supplied to the drive power line PVDD, and the reference voltage VSSEL is supplied to the reference voltage line PVSS as an example in the description of the driving method according to the first embodiment.

[0112] First, the data signal VDATA, the selection signal MUXR, the selection signal MUXG, and the selection signal MUXB will be described. The image data signal SL (m+1) including the data signal VDATA is input to each pixel 180 (pixel circuit 181) in accordance with each horizontal period. The data signal VDATA is, for example, analog data

including a voltage between a voltage VDH and a voltage VDL that is lower than the voltage VDH. A voltage VDM is a voltage between the voltage VDH and the voltage VDL that is lower than the voltage VDH. For example in each of the horizontal periods, the voltage RDATA is selected using the selection signal MUXR and supplied to an image data signal line, the voltage GDATA is selected using the selection signal MUXG and supplied to the image data signal line, and the voltage BDATA is selected using the selection signal MUXB and supplied to the image data signal line. For example, the data signal VDATA is kept at the voltage VDM during a time period in which data is not selected using the selection signal MUXG.

[0113] Next, referring to FIG. 6 and FIG. 7, a method for driving the pixel 180 (the pixel circuit 181) in the light emission period PEM of the previous frame of the current frame (K-1st FRAME) will be described. The light emission period PEM of the previous frame of the current frame (K-1st FRAME) is a period in which the pixel 180 (pixel circuit 181) emits light in accordance with a voltage RDATA (n-1).

[0114] The gate electrode 622 of the transistor T2 is supplied with the voltage RDATA (n-1). The scanning signal GF (n-1), the scanning signal GF (n) and the scanning signal GS (n+1) are supplied with a low level (LO) and the transistor T1, transistor T3, transistor T6 and transistor T7 are in an off state. Further, the second light emission control signal ES (n) supplies a high level (HI) to the transistor T4, the first light emission control signal EF (n) supplies a high level (HI) to the transistor T5, and the transistor T4 and the transistor T5 are in an on state.

[0115] The transistor T2 is in an on state based on the voltage RDATA (n-1). Consequently, the transistor T2 can supply a current IEL based on a gate/source voltage Vgs and a source/drain voltage Vds according to the voltage RDATA (n-1).

[0116] The transistor T4, the transistor T2, and the transistor T5 are in an on state, and the current IEL flows from the drive power supply line PVDD to the reference voltage line PVSS. Consequently, the current IEL flows to the light emitting element OLED, and the light emitting element OLED emits light.

[0117] Next, referring to FIG. 6, a method for driving the pixel 180 (pixel circuit 181) in a period between the light emission period PEM of the previous frame of the current frame (K-1st FRAME) and the reset period PRS of the current frame will be described. The period between the emission period PEM of the previous frame of the current frame (K-1st FRAME) and the reset period PRS of the current frame is a period overlapping a part of the single horizontal period N-2nd HP and a part of the single horizontal period N-1st HP. In this period, the second light emission control signal ES (n) and the first light emission control signal EF (n) are supplied from a high level (HI) to a low level (LO), and the transistor T5 and the transistor T4 are in an off state. The scanning signal GF (n-1) is supplied from a low level (LO) to a high level (HI), and the transistor T7 is in an on state. The transistor T1, the transistor T3, and the transistor T6 remain in an off state. The transistor T4 and the transistor T5 are in an off state, no current flows from the drive power supply line PVDD to the reference voltage line PVSS, and the light emitting element OLED becomes nonlight emitting (does not emit light).

[0118] Next, referring to FIG. 6 and FIG. 8, a method for driving the pixel 180 (pixel circuit 181) in the reset period PRS of the current frame will be described. The reset period PRS is a period in which the reset voltage VSH and the initialization voltage VINI are written to the pixel 180 (the pixel circuit 181) and is a period initializing the pixel 180 (the pixel circuit 181). The reset period PRS of the current frame is a period overlapping a part of the one horizontal period N-1st HP.

**[0119]** In the reset period PRS, the scanning signal GF (n) is supplied from a low level (LO) to a high level (HI), and the transistor T3 and the transistor T6 are in an on state. Further, the transistor T7 remains in an on state, and the transistor T1, the transistor T4, and the transistor T5 remain in an off state.

[0120] The reset voltage VSH is supplied to the first node N1, the second node N2, each electrode electrically connected to the first node N1, each electrode electrically connected to the second node N2, the gate electrode 622 of the transistor T2, and the second electrode 694 of the capacitive element CS, based on the transistor T7 and the transistor T3 being in an on state. In addition, the initialization voltage VINI is supplied to the first electrode 692 of the capacitive element CS, each electrode electrically connected to the first electrode 692, and the second electrode 684 of the light emitting element OLED based on the transistor T6 being in an on state. Consequently, the first node N1, the second node N2, each electrode electrically connected to the first node N1, each electrode electrically connected to the second node N2, the gate electrode 622 of the transistor T2, and the second electrode 694 of the capacitive element CS are reset, and the first electrode 692 of the capacitive element CS, each electrode electrically connected to the first electrode 692, and the second electrode 684 of the light emitting element OLED are initialized. Further, since the transistor T4 and the transistor T5 remain in an off state, no current flows from the drive power supply line PVDD to the reference voltage line PVSS, and the light emitting element OLED is non-light emitting (does not emit light).

[0121] Next, referring to FIG. 6 and FIG. 9, a method for driving the pixel 180 (pixel circuit 181) in a period between the reset period PRS and the sampling period PWR of the current frame will be described. The period between the reset period PRS and the sampling period PWR of the current frame is a period that overlaps a part of the one horizontal period N-1st HP and a part of the one horizontal period Nth HP.

[0122] The scanning signal GF (n-1) is supplied from a high level (HI) to a low level (LO), and the transistor T7 is in an off state in the period between the reset period PRS and the sampling period PWR of the current frame. Also, the transistor T3 and transistor T6 remain in an on state, and the transistor T1, transistor T2, transistor T4, and transistor T5 remain in an off state.

[0123] Further, the reset voltage VSH is held in the second node N2, each electrode electrically connected to the second node N2, the gate electrode 622 of the transistor T2, and the second electrode 694 of the capacitive element CS in the period between the reset period PRS and the sampling period PWR of the current frame. Further, since the transistor T6 remains in an on state, the initialization voltage VINI is supplied to the first electrode 692 of the capacitive element CS, each electrode electrically connected to the first

electrode **692**, and the second electrode **684** of the light emitting element OLED. Further, since the transistor T**4** and the transistor T**5** remain in an off state, no current flows from the drive power supply line PVDD to the reference voltage line PVSS, and the light emitting element OLED is non-light emitting (does not emit light).

[0124] The voltage RDATA (n) is selected based on an on signal being supplied to the selection signal MUXR in the period between the reset period PRS and the sampling period PWR of the current frame. Therefore, the image data signal SL (m+1) includes the voltage RDATA (n). Further, the image data signal SL (m+1) including the voltage RDATA (n) is supplied to the image data signal line 321. The image data signal line 321 holds the voltage RDATA (n) based on the off signal being supplied to the selection signal MUXR.

[0125] Next, referring to FIG. 6 and FIG. 10, a method for driving the pixel 180 (pixel circuit 181) in the sampling period PWR of the current frame will be described. The sampling period PWR is a period in which the pixel 180 (the pixel circuit 181) writes a voltage corresponding to the image data to the pixel 180 (the pixel circuit 181). The sampling period PWR of the current frame is a period overlapping a part of the one horizontal period Nth HP.

[0126] The scanning signal GS (n+1) is supplied from a low level (LO) to a high level (HI), and the transistor T1 is in an on state in the sampling period PWR of the current frame. Further, the transistor T3 and the transistor T6 remain in an on state, and the transistor T4, the transistor T5, and the transistor T7 remain in an off state.

[0127] The voltage RDATA (n) is supplied to the first node N1 and each electrode electrically connected to the first node N1 based on the transistor T1 being in an on state. Further, if the voltage RDATA (n) is supplied to the first node N1, the voltage between the gate and the source of the transistor T2 also changes, and the transistor T2 is in an on state. Consequently, voltages of the second node N2, each electrode electrically connected to the second node N2, the gate electrode 622 of the transistor T2, and the second electrode 694 of the capacitive element CS drop from the voltage VSH, and become the voltage RDATA (n)+a threshold voltage Vth (RDATA (n)+Vth). In this way, a potential difference between the gate electrode 622 and the first electrode 624 of the transistor T2 becomes the same as the threshold voltage Vth of the transistor T2, the dop in voltage of the second node N2 or the like are finished, and the transistor T2 is in an off state. Further, since the transistor T6 remains in an on state, the initialization voltage VINI is supplied to each electrode electrically connected to the first electrode 692 of the capacitive element CS and the second electrode 684 of the light emitting element OLED. Further, since the transistor T4 and the transistor T5 remain in an off state, no current flows from the drive power supply line PVDD to the reference voltage line PVSS, and the light emitting element OLED is non-light emitting (does not emit

[0128] Although a detailed illustration is omitted, since the transistor T1 remains in an on state in this case, the voltages of the first node N1 and each electrode electrically connected to the first node N1 are fixed to the voltage RDATA (n). The charge corresponding to the threshold voltage Vth is held between the gate electrode 622 and the first electrode 624 of the transistor T2. Therefore, the sampling period PWR of the current frame is a period in

which the voltage corresponding to the image data displayed by the pixel 180 (the pixel circuit 181) is written to the pixel 180 (the pixel circuit 181), and is also a period (threshold correction period) in which the charge corresponding to the threshold voltage Vth is held between the gate electrode 622 and the first electrode 624 of the transistor T2 and a period in which the threshold value of the transistor T2 is corrected. [0129] Next, referring to FIG. 6 and FIG. 11, a method for driving the pixel 180 (pixel circuit 181) after the sampling period PWR of the current frame will be described. A period after the sampling period PWR of the current frame is a period overlapping a part of the one horizontal period Nth HP and the one horizontal period N+1st HP.

[0130] The scanning signal GF (n) is supplied from a high level (HI) to a low level (LO), and the transistor T3 is in an off state in the period after the sampling period PWR of the current frame. The transistor T1 remains in an on state, and the transistor T2, transistor T4, transistor T5, transistor T6 and transistor T7 remain in an off state. A high level (HI) is supplied to the scanning signal GS (n+1), and the transistor T1 is in an on state. Therefore, since a potential difference between a voltage of the first electrode 614 and a voltage of the second electrode 616 of the transistor T1 is 0, no current flows through the transistor T1.

[0131] Since the transistor T2, transistor T3, transistor T6 and transistor T7 are in an off state, the voltage RDATA (n)+the threshold voltage Vth (RDATA (n)+Vth) is held in the second node N2, each electrode electrically connected to the second node N2, the gate electrode 622 of the transistor T2 and the second electrode 694 of the capacitive element CS, and the initialization voltage VINI is held in the first electrode 692 of the capacitive element CS, each electrode electrically connected to the first electrode 692, and the second electrode 684 of the luminescent element OLED. Further, since the transistor T4 and the transistor T5 are in an off state, no current flows from the drive power supply line PVDD to the reference voltage line PVSS, and the light emitting element OLED is non-light emitting (does not emit light).

[0132] As shown in FIG. 6, the scanning signal GF (n) is supplied from a high level (HI) to a low level (LO), the transistor T3 is in an off state, the scanning signal GS (n+1) is supplied from a high level (HI) to a low level (LO), and the transistor T1 is in an off state.

[0133] Since the transistor T1 is in an off state in this case, the voltage RDATA (n) is held in each electrode electrically connected to the first node N1 and the first node N1. Further, since the transistor T2, the transistor T3, the transistor T6 and the transistor T7 are in an off state, the voltage RDATA (n)+threshold voltage Vth (RDATA (n)+Vth) is held the second node N2, each electrode electrically connected to the second node N2, the gate electrode 622 of the transistor T2, and the second electrode 694 of the capacitive element CS, and the initialization voltage VINI is held the first electrode 692 of the capacitive element CS, each electrode electrically connected to the first electrode 692, and the second electrode 684 of the light emitting element OLED. Further, since the transistor T4 and the transistor T5 are in an off state, no current flows from the drive power supply line PVDD to the reference voltage line PVSS, and the light emitting element OLED is non-light emitting (not emitting light).

[0134] Next, referring to FIG. 6, FIG. 11, and FIG. 12, a method for driving the pixel 180 (pixel circuit 181) in the light emission period PEM of the current frame will be

described. The light emission period PEM of the current frame is a period in which the pixel 180 (the pixel circuit 181) emits light in accordance with the voltage RDATA (n). The emission period PEM of the current frame is a period overlapping the one horizontal period N+2nd HP.

[0135] As shown in FIG. 6 and FIG. 12, the scanning signal GF (n-1), the scanning signal G (n) and the scanning signal GS (n+1) are supplied with a low lever (LO), and the transistor T1, transistor T2, transistor T3, transistor T6 and transistor T7 are in an off state. Further, the transistor T4 is supplied with a high level (HI) from the second light emission control signal ES (n), the transistor T5 is supplied with a high level (HI) from the first light emission control signal EF (n), and the transistor T4 and the transistor T5 are in an on state.

[0136] As shown in FIG. 11, a voltage held by the second electrode 656 of the transistor T5 is RDATA (n), and a voltage held by the first electrode 654 of the transistor T5 is the initialization voltage *VINI*.

[0137] In the case where the transistor T5 shown in FIG. 6 and FIG. 12 is in an on state from a state in which a voltage of the second electrode 656 and the voltage of the first electrode 654 of the transistor T5 are the voltage RDATA (n) and the initialization voltage VINI, a current flows from the second electrode 656 to the first electrode 654 of the transistor T5, a redistribution of charges occurs, and the voltage of the second electrode 656 and the voltage of the first electrode 654 become the initialization voltage VINI In this case, the gate electrode 622 of the transistor T2 and the second electrode 694 of the capacitive element CS become the voltage RDATA (n)+the threshold voltage Vth-the initialization voltage VINI (RDATA (n)+Vth-VINI). Depending on a value of the voltage RDATA (n), the transistor T2 may be in an on state or an off state.

[0138] Further, for example, as shown in FIG. 6 and FIG. 12, a current flows from the second electrode 656 to the first electrode 654 of the transistor T5 based on the transistor T5 being in an on state, and if the voltages of the second electrode 656 and each of the electrodes electrically connected to the second electrode (the second electrode 684 of the light emitting element OLED, the second electrode 666 of the transistor T6, and the first electrode 692 of the capacitive element CS) increase from the voltage VINI to a voltage VINI+ $\alpha$ , a voltage held by the first node N1 (the second electrode 656 of the transistor T5 and the first electrode 624 of the transistor T2) decreases from RDATA (n). As the first electrode 692 of the capacitive element CS increases to the voltage VINI+α, a voltage of the gate electrode 622 of the transistor T2 and a voltage of the second electrode 694 of the capacitive element CS increase from the voltage RDATA (n)+the threshold voltage Vth (RDATA (n)+Vth) to the voltage RDATA (n)+the threshold voltage Vth+a voltage  $\alpha$  (RDATA (n)+Vth+ $\alpha$ ). Consequently, since a gate/source voltage between the gate electrode 622 and the first electrode 624 of the transistor T2 is higher than the threshold voltage Vth of the transistor T2, the transistor T2 is in an on state.

[0139] The transistor T4, the transistor T2, and the transistor T5 are in an on state, and a current IELA flows from the drive power supply line PVDD to the reference voltage line PVSS. Consequently, the current IELA flows to the light emitting element OLED, and the light emitting element OLED emits light. The current IELA is, for example, a current based on the voltage RDATA (n)+the threshold

voltage Vth+the voltage  $\alpha$  (RDATA (n)+Vth+ $\alpha$ ) written in the transistor T2. Here, for example, the voltage  $\alpha$  is a positive value, and is a voltage value that changes in accordance with the voltage RDATA (n). For example, if the voltage RDATA (n) increases, the voltage a increases, and if the voltage RDATA (n) decreases, the voltage  $\alpha$  decreases. For example, the voltage a is determined such that a current value that the transistor T2 supplies in accordance with the gate electrode 622, the first electrode 624, and the second electrode 626 is the same as a current value that the light emitting element OLED supplies.

[0140] The self-luminous display device 10 is driven as described above, and image data corresponding to each pixel 180 (the pixel circuit 181) is supplied to each pixel 180 (the pixel circuit 181), a current corresponding to the image data is supplied to the light emitting element OLED included in each pixel 180 (the pixel circuit 181), and each light emitting element OLED emits light with a brightness corresponding to the image data. As a result, the self-luminous display device 10 can display a desired image.

[0141] For example, in the conventional methods for driving the self-luminous display device, the driving voltage VDDEL is used as a reset voltage during a reset period. In other words, in the conventional driving methods, the driving voltage VDDEL is supplied from the driving power supply line PVDD to the second node N2 and the gate electrode 622 of the pixel 180. For example, power consumption of the self-luminous display device is reduced in the case where a low-gradation image is displayed. For example, the power supply voltage VDDEL is reduced to the driving voltage VDDELL lower than the driving voltage VDDEL in this case. However, in the conventional driving methods, if the driving voltage VDDEL is reduced to the driving voltage VDDELL, the reset voltage is also lowered, so that a brightness of the self-luminous display device is lowered.

[0142] On the other hand, the self-luminous device 10 of the present invention includes the transistor T7. The self-luminous display device 10 of the present invention can use the transistor T7 to supply the reset voltage VSH independent of the driving voltage VDDEL to the second node N2 and the gate electrode 622 based on the fact that the self-luminous display device 10 includes the transistor T7. Further, the self-luminous display device 10 of the present invention is capable of supplying the driving voltage VDDEL to the driving power supply line PVDD independent of the reset voltage VSH. Consequently, as shown in FIG. 6, for example, the reset voltage VSH supplied to the gate electrode 622 (second node N2) does not decrease even if the driving voltage VDDELL lower than the driving voltage VDDEL is supplied to the drive power supply line PVDD.

[0143] Therefore, in the self-luminous display device 10 of the present invention, there is no decrease in brightness due to a decrease in the reset voltage VSH. In the case where a low-gradation image is displayed in the self-luminous display device 10, since the power supply voltage VDDELL lower than the power supply voltage VDDEL is supplied to the pixel 180 (the pixel circuit 181), the power consumption can be reduced without the decrease in brightness.

[0144] Next, referring to FIG. 5B, FIG. 13, and FIG. 14, an example of driving methods in which the pixel 180 (the pixel circuit 181) displays black will be described. The pixel 180 (the pixel circuit 181) in the example of the driving

methods for displaying black displays black based on a voltage RDATAB included in the data signal VDATA that is input to the black one horizontal period Nth HP.

[0145] As described above, driving other than the black period PBWR in the low-frequency driving is the same as the high-frequency driving. Thus, driving of the pixel 180 (the pixel circuit 181) in the black period PBWR will mainly be described here. The same or similar configurations as those in FIG. 1 to FIG. 5A and FIG. 6 to FIG. 12 will not be described here. The horizontal axis of the timing charts indicates times (TIME).

[0146] First, the data signal VDATA, the selection signal MUXR, the selection signal MUXG, and the selection signal MUXB will be described. The image data signal SL (m+1) including the data signal VDATA is input to each pixel 180 (pixel circuit 181) in accordance with each horizontal period. For example, the data signal VDATA is analog data including the voltage VDL for displaying black. The voltage VDM is the voltage between the voltage VDH and the voltage VDL that is lower than the voltage VDH. In each of the horizontally periods, for example, the voltage VDL is selected using the selection signal MUXR and is supplied to the image data signal line, the voltage VDL is selected using the selection signal MUXG and is supplied to the image data signal line, and the voltage VDL is selected using the selection signal MUXB and is supplied to the image data signal line. During periods in which no data is selected using the select signal MUXG, the data signal VDATA is kept, for example, at the voltage VDM.

[0147] A method for driving the pixel 180 (pixel circuit 181) in the emission period PEM of the previous frame of the current frame (K-1st FRAME) is the same as the driving method described with reference to FIG. 1 to FIG. 5A and FIG. 6 to FIG. 12. Therefore, a description thereof will be omitted. The voltages of the first node N1, the first electrode 654 of the transistor T5, and the second electrode 684 of the light emitting element OLED from the light emission period PEM to the black period PBWR of the previous frame of the current frame (K-1st FRAME) are voltages between the voltage VDL and the voltage VDH.

[0148] Next, a method for driving the pixel 180 (the pixel circuit 181) in a period between the emission period PEM and the black period PBWR of the previous frame of the current frame (K-1st FRAME) will be described. The period between the emission period PEM and the black period PBWR of the previous frame of the current frame (K-1st FRAME) is a period overlapping a part of the one horizontal period N-2nd HP, a part of the one horizontal period N-1st HP, and a part of the one horizontal period Nth HP.