(19)

## (11) **EP 4 020 878 B1**

(12)

## **EUROPEAN PATENT SPECIFICATION**

- (45) Date of publication and mention of the grant of the patent:03.07.2024 Bulletin 2024/27

- (21) Application number: 21198718.5

- (22) Date of filing: 24.09.2021

- (51) International Patent Classification (IPC): H04L 9/08 <sup>(2006.01)</sup> G06F 9/30 <sup>(2018.01)</sup> G06F 21/73 <sup>(2013.01)</sup> H04L 9/32 <sup>(2006.01)</sup> G06F 21/60 <sup>(2013.01)</sup>

- (52) Cooperative Patent Classification (CPC): H04L 9/0866; G06F 9/30007; G06F 21/602; G06F 21/73; H04L 9/3278; G06F 2221/2107

## (54) ISA ACCESSIBLE PHYSICAL UNCLONABLE FUNCTION

ISA-ZUGÄNGLICHE PHYSIKALISCHE UNKLONBARE FUNKTION

FONCTION PHYSIQUE NON CLONABLE ACCESSIBLE ISA

- (84) Designated Contracting States: AL AT BE BG CH CY CZ DE DK EE ES FI FR GB GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO PL PT RO RS SE SI SK SM TR

- (30) Priority: 26.12.2020 US 202017134365

- (43) Date of publication of application: 29.06.2022 Bulletin 2022/26

- (73) Proprietor: INTEL Corporation Santa Clara, CA 95054 (US)

- (72) Inventors:

- CHHABRA, Siddhartha Portland, 97229 (US)

- DEWAN, Prashant Portland, 97229 (US)

- PATEL, Baiju

Portland, 97229 (US)

- SHANBHOGUE, Vedvyas Austin, 78738 (US)

- (74) Representative: Goddar, Heinz J. Boehmert & Boehmert Anwaltspartnerschaft mbB Pettenkoferstrasse 22 80336 München (DE)

- (56) References cited: US-A1- 2017 093 567

- PATIL VINAY C ET AL: "Preventing integrated circuit piracy via custom encoding of hardware instruction set", 2016 17TH INTERNATIONAL SYMPOSIUM ON QUALITY ELECTRONIC DESIGN (ISQED), IEEE, 15 March 2016 (2016-03-15), pages 234-241, XP032905050, ISSN: 1948-3295, DOI: 10.1109/ISQED.2016.7479206 [retrieved on 2016-05-25]

Note: Within nine months of the publication of the mention of the grant of the European patent in the European Patent Bulletin, any person may give notice to the European Patent Office of opposition to that patent, in accordance with the Implementing Regulations. Notice of opposition shall not be deemed to have been filed until the opposition fee has been paid. (Art. 99(1) European Patent Convention).

#### Description

#### BACKGROUND

- <sup>5</sup> **[0001]** A physical unclonable function (PUF) is a physical object that, for a given input and conditions (challenge), provides a physically-defined output (response) that serves as a unique identifier for a semiconductor device (e.g., a processor). An example PUF is an array of transistor devices, the response of which is based on unique physical variations that occur naturally during semiconductor manufacturing. Because of this unique response, PUFs provide platform-unique entropy, which can be used to generate unclonable cryptographic keys. For example, on a (same value

- <sup>10</sup> generated across boots). Because the PUF-generated entropy is unique to the platform (e.g., a desktop computer, a laptop computer, a tablet computer, etc.), the same PUF circuit used on a different platform will generate different entropy, which makes the cryptographic keys generated by the PUF unclonable. [0002] US 2017/093567 A1 discloses embodiments for hardware enforced one-way cryptography. In one embodiment

- of this document, a processor includes a processor key location, instruction hardware, and execution hardware. The processor key location is to hold a processor key. The instruction hardware is to receive a first instruction in an instruction set of the processor. The first instruction is to encrypt input data with the processor key and return a handle. The instruction set lacks a second instruction corresponding to the first instruction to decrypt the handle with the processor key to return the input data. The execution hardware is to perform, in response to receipt of the first instruction by the instruction hardware, encryption of the input data with the processor key and to return the handle.

## 20

#### SUMMARY

**[0003]** The invention is defined by the independent claims. Advantageous embodiments are described by the dependent claims.

#### 25

#### BRIEF DESCRIPTION OF DRAWINGS

**[0004]** Various embodiments in accordance with the present disclosure will be described with reference to the drawings, in which:

30

35

FIG. 1 is a schematic block diagram of a computing system that provides isolation in virtualized systems using TDs, according to an implementation of the disclosure.

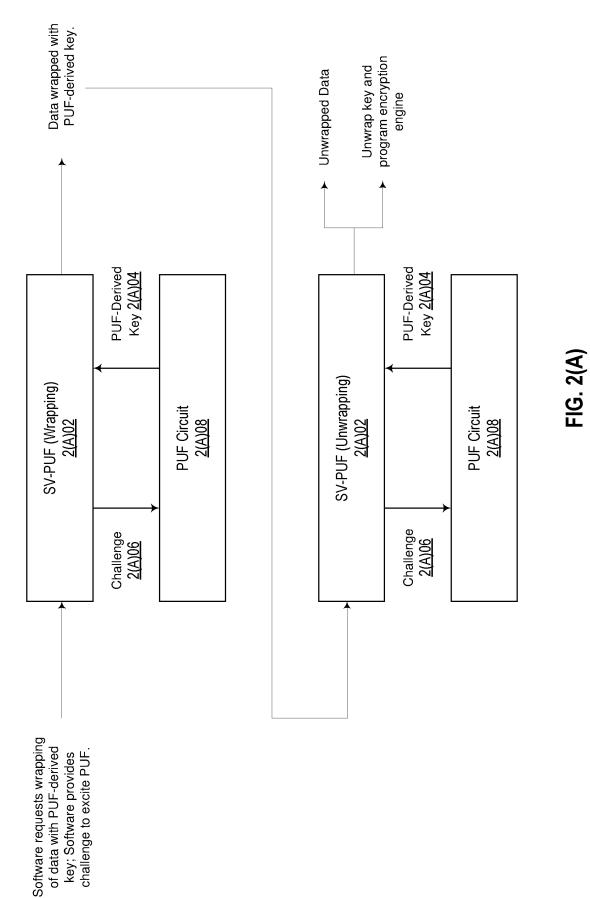

FIG. 2(A) illustrates an example of using a PUF to generate and use a key for wrapping and unwrapping data according to the present embodiments.

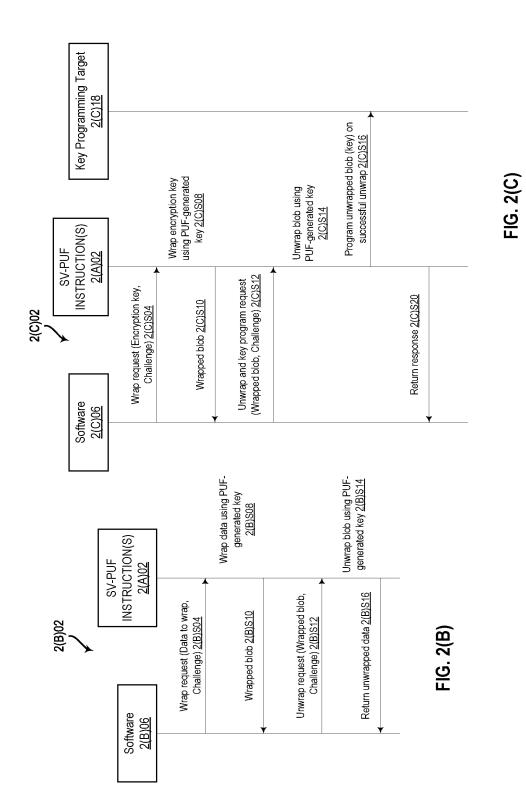

FIG. 2(B) illustrates an example process for wrapping and unwrapping a secret according to the present embodiments.

<sup>40</sup> FIG. 2(C) illustrates another example process for wrapping and unwrapping a secret according to the present embodiments.

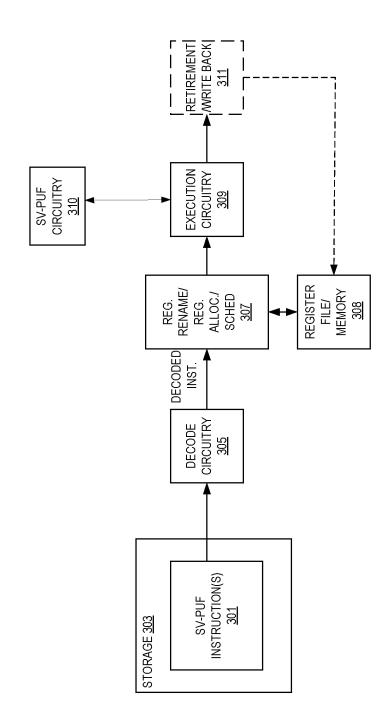

FIG. 3 illustrates embodiments of hardware to process an instruction, such as a SV-PUF instruction.

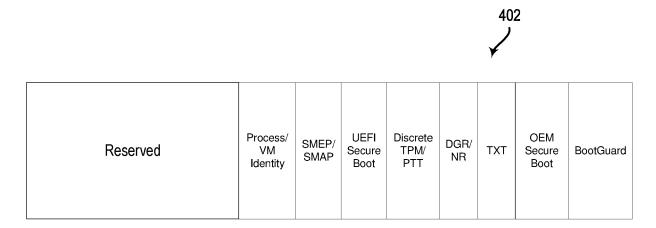

<sup>45</sup> FIG. 4 is a functional block diagram illustrating a bitvector representing a platform/processor configuration to which the wrapped data is to be bound.

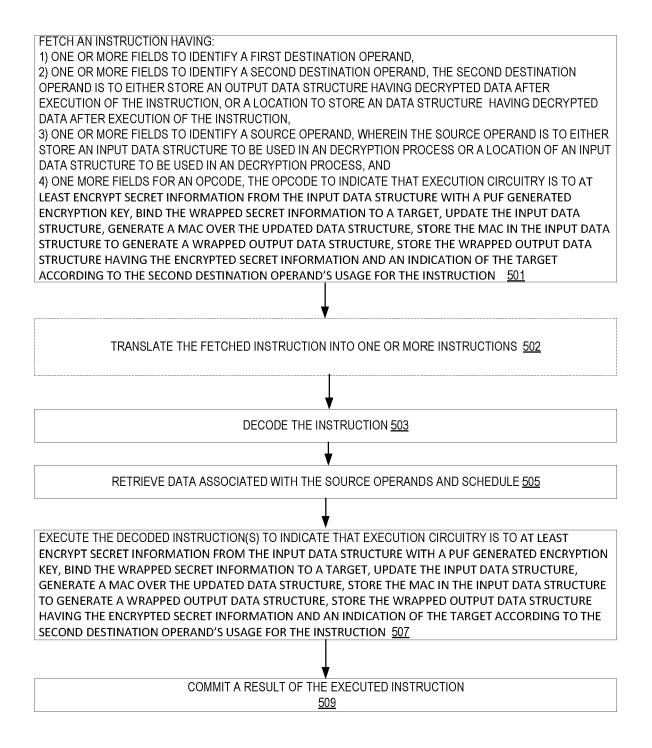

FIG. 5 illustrates an embodiment of method performed by a processor to process a WRP instruction.

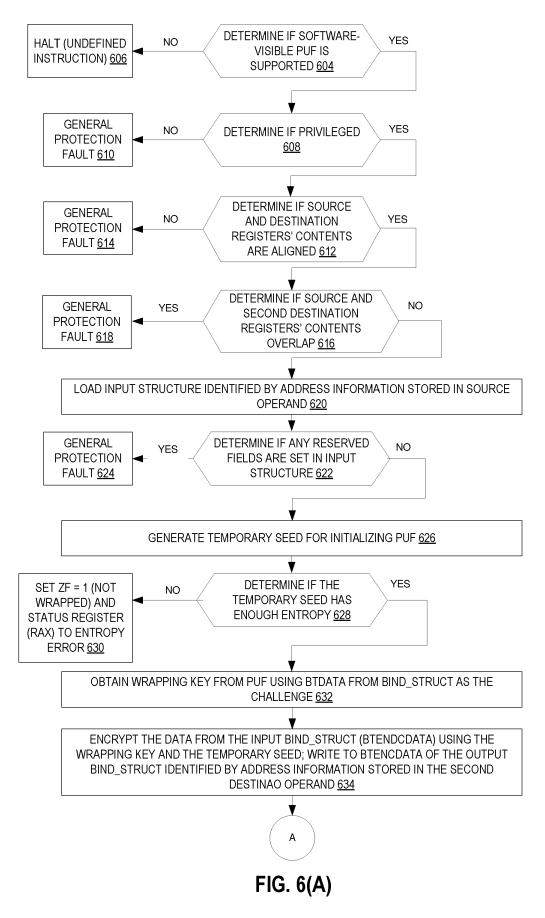

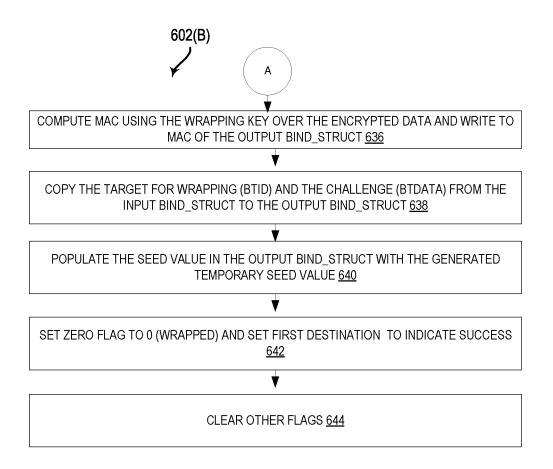

<sup>50</sup> FIGS. 6(A)-(B) illustrate a method for the execution of a wrap (WRP) instruction according to the present embodiments.

FIG. 7 illustrates embodiments of pseudocode for the execution of the WRP instruction.

<sup>55</sup> FIG. 8 illustrates embodiments of processing an UNWRP instruction.

FIGS. 9(A)-(B) illustrate a method performed by a processor to execute an unwrap (UNWRP) instruction according to the present embodiments.

FIG. 10 illustrates embodiments of pseudocode for the execution of the UNWRP instruction.

FIG. 11 illustrates embodiments of a signature data structure used to define which signing algorithm is to be used during the execution of UNWRPMAC.

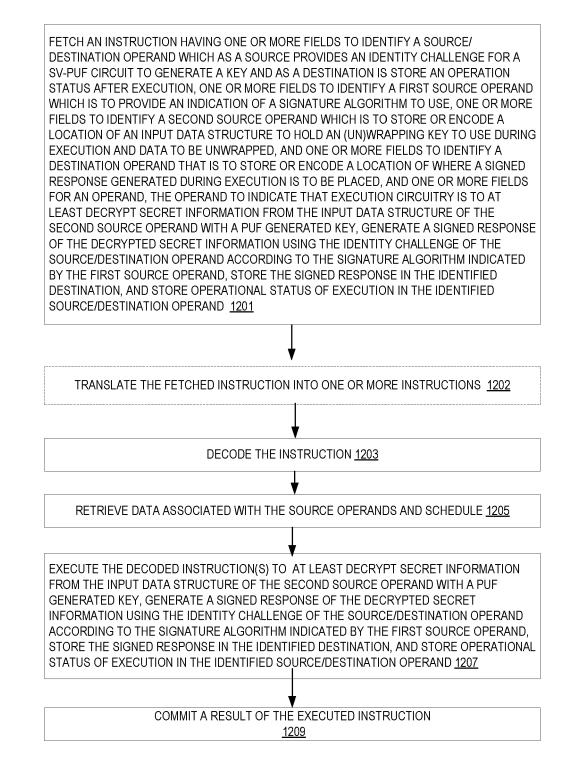

FIG. 12 illustrates embodiments of processing an UNWRPMAC instruction.

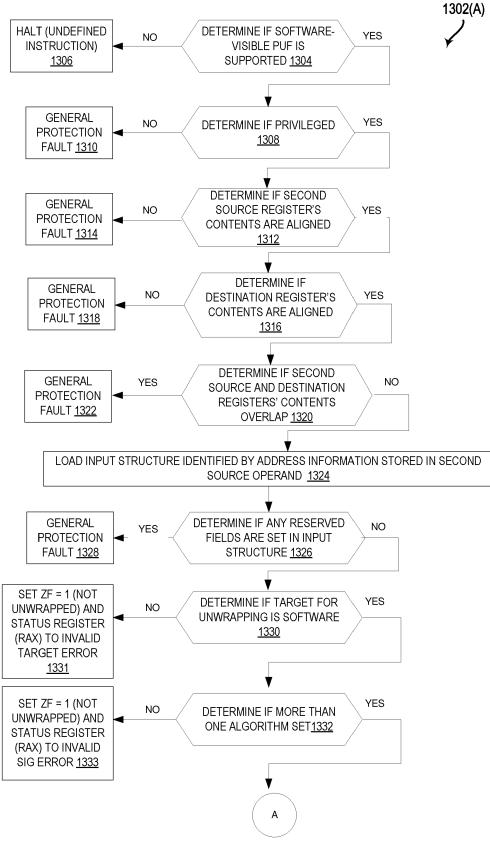

FIGS. 13(A)-(B) illustrate a method 1302 performed by a processor to process an UNWRPMAC instruction according to the present embodiments.

10

20

5

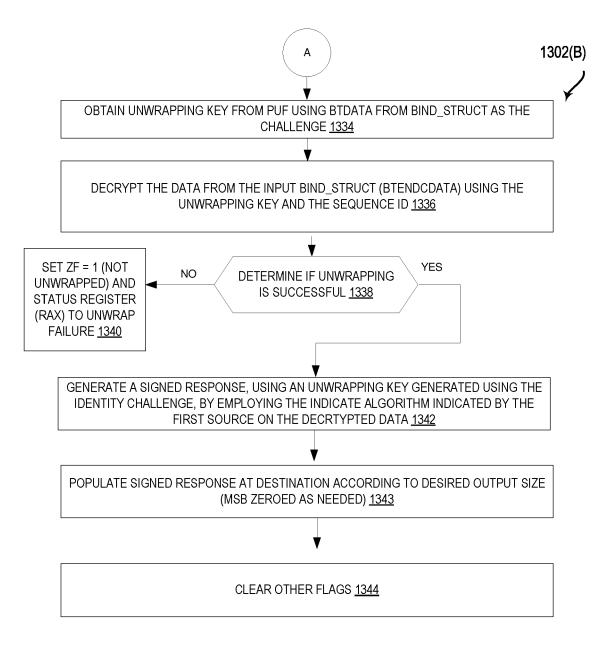

FIG. 14 illustrates embodiments of pseudocode for the execution of an UNWRPMAC instruction.

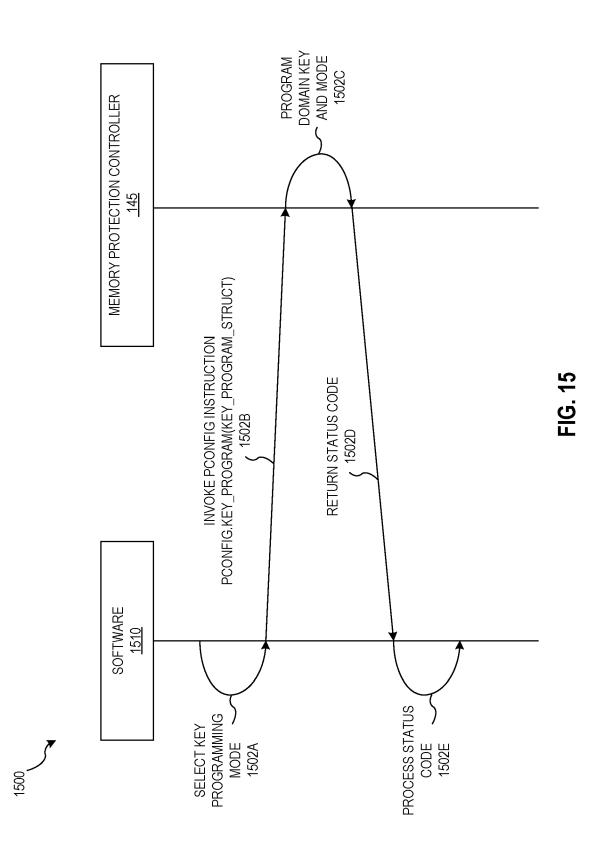

FIG. 15 illustrates an example of configuring a protected domain using a configuration instruction.

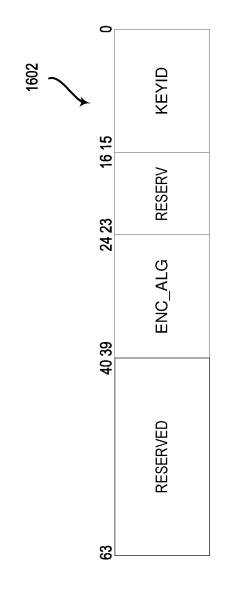

<sup>15</sup> FIG. 16 illustrates an example configuration for KEYID\_CTRL to be stored in one of the "other" registers.

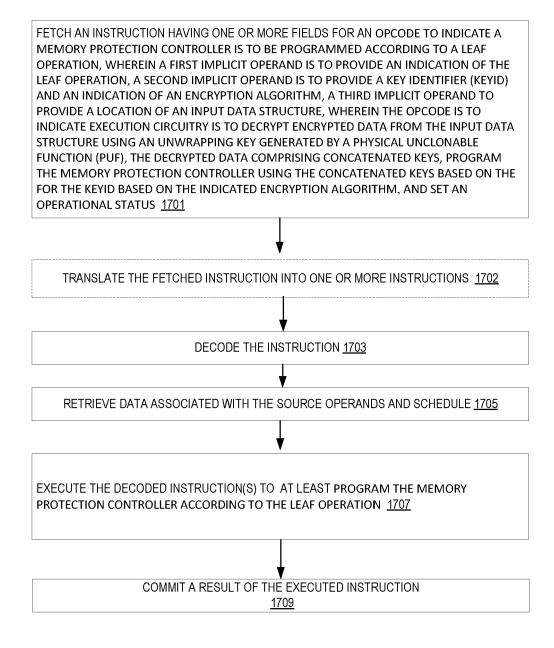

FIG. 17 illustrates embodiments of processing an PCONFIG instruction.

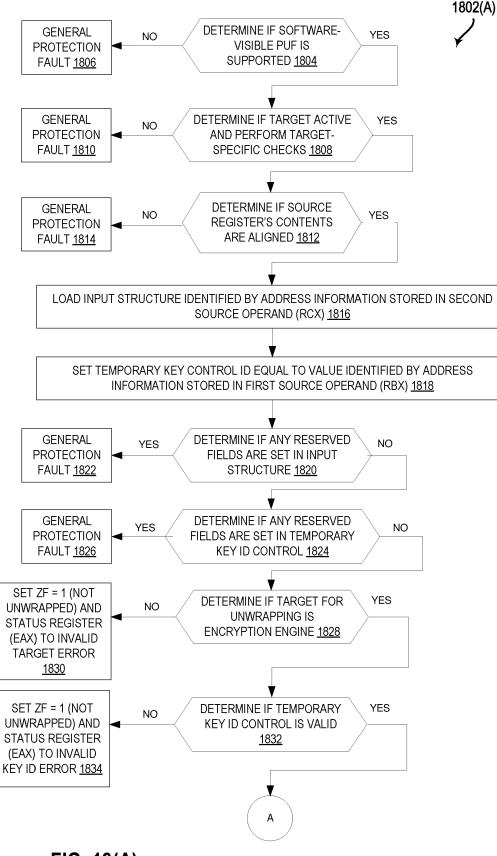

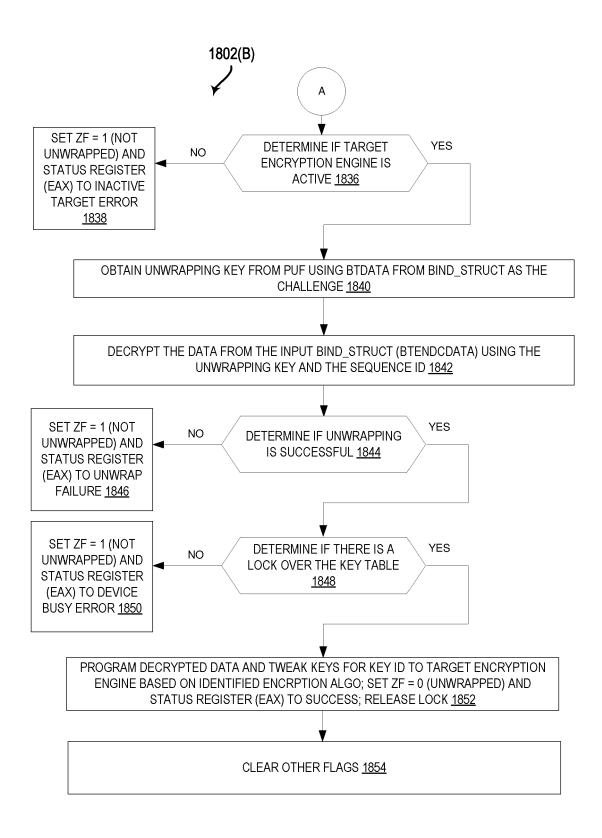

FIGS. 18(A)-(B) illustrates a method performed by a processor to execute an encryption key programming instruction to program a target according to the present embodiments.

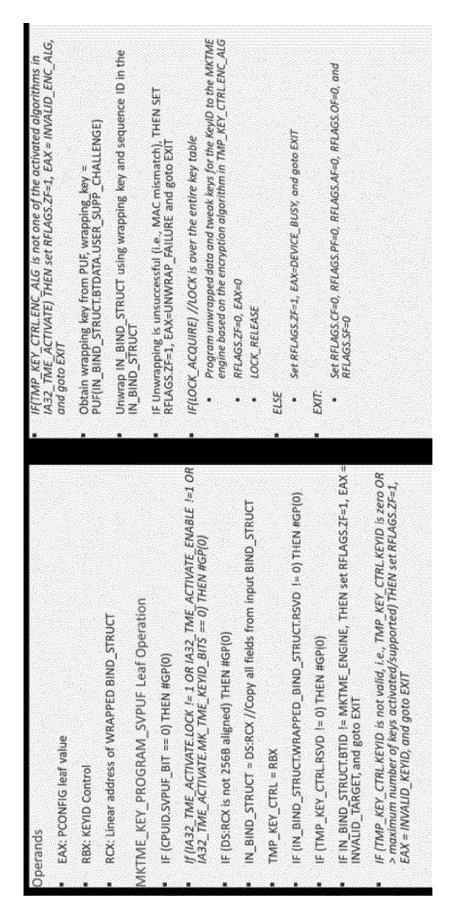

FIG. 19 illustrates embodiments of pseudocode for the execution of an PCONFIG instruction.

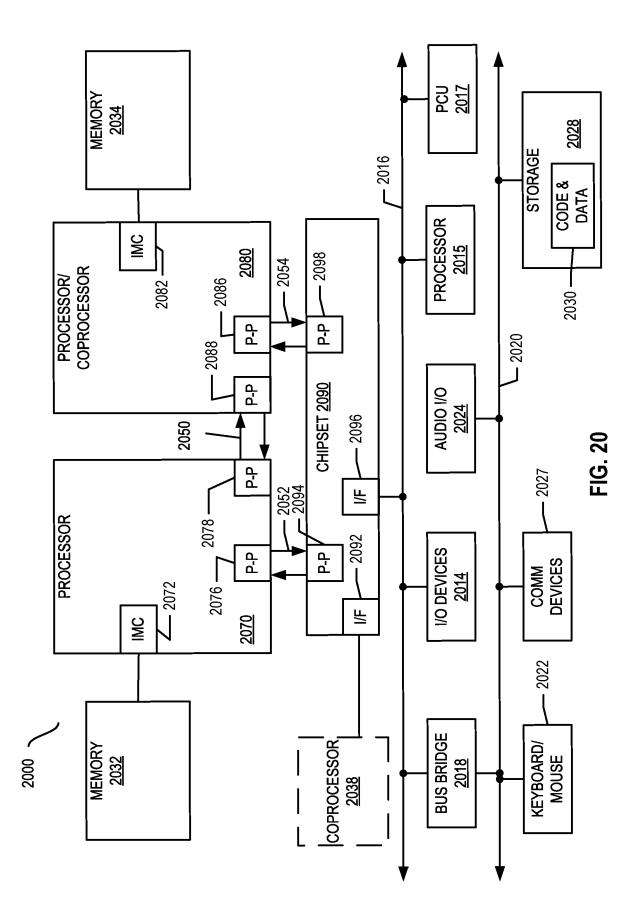

FIG. 20 is a functional block diagram illustrating hardware of an example system for processing instructions according

to the present embodiments;

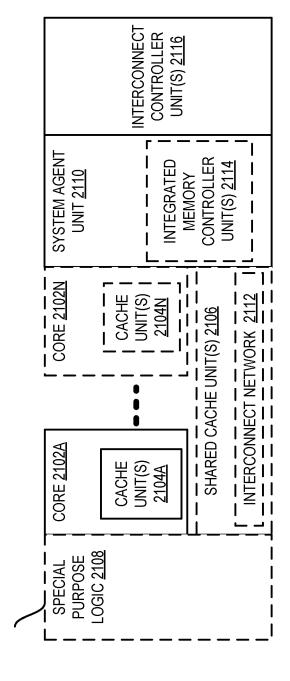

FIG. 21 is a functional block diagram illustrating a processor according to the present embodiments;

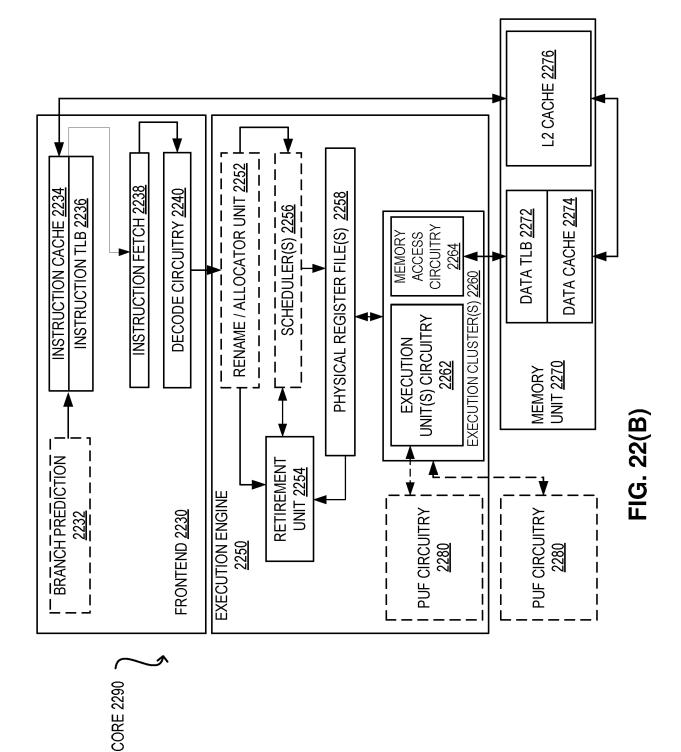

FIG. 22(A) is a functional block diagram illustrating both an example in-order pipeline and an example register renaming, out-of-order issue/execution pipeline according to the present embodiments;

FIG. 22(B) is a functional block diagram illustrating both an example in-order architecture core and an example register renaming, out-of-order issue/execution architecture core to be included in a processor according to the present embodiments;

35

50

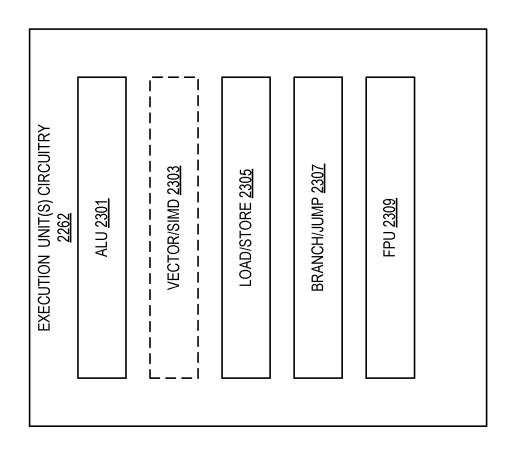

FIG. 23 is a functional block diagram illustrating execution unit(s) circuitry according to the present embodiments;

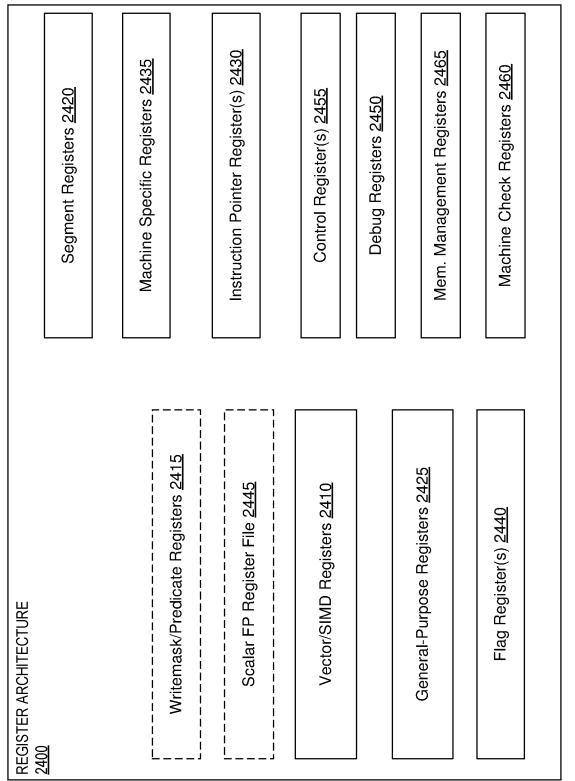

FIG. 24 is a functional block diagram illustrating register architecture according to the present embodiments;

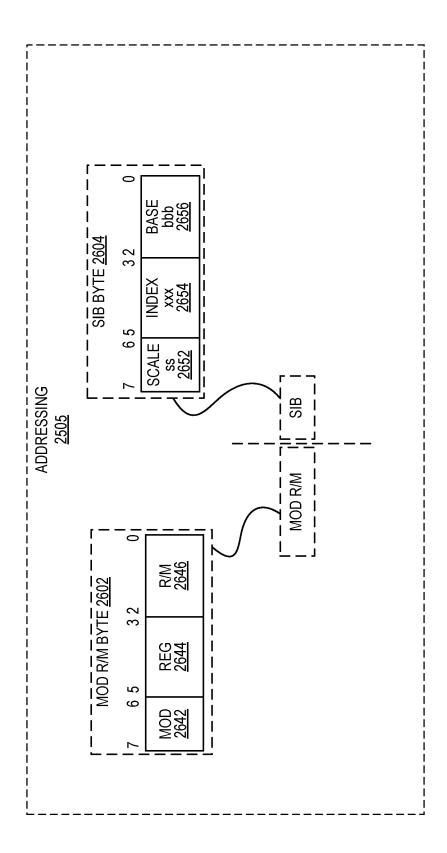

<sup>40</sup> FIG. 25 is a functional block diagram illustrating an instruction format according to the present embodiments;

FIG. 26 is a functional block diagram illustrating details of the addressing field of the instruction format of FIG. 25 according to the present embodiments;

<sup>45</sup> FIG. 27 is a functional block diagram illustrating details of a first example prefix of the instruction format of FIG. 25 according to the present embodiments;

FIGS. 28(A)-(D) are functional block diagrams illustrating how the R, X, and B fields of the first example prefix of FIG. 27 are used according to the present embodiments;

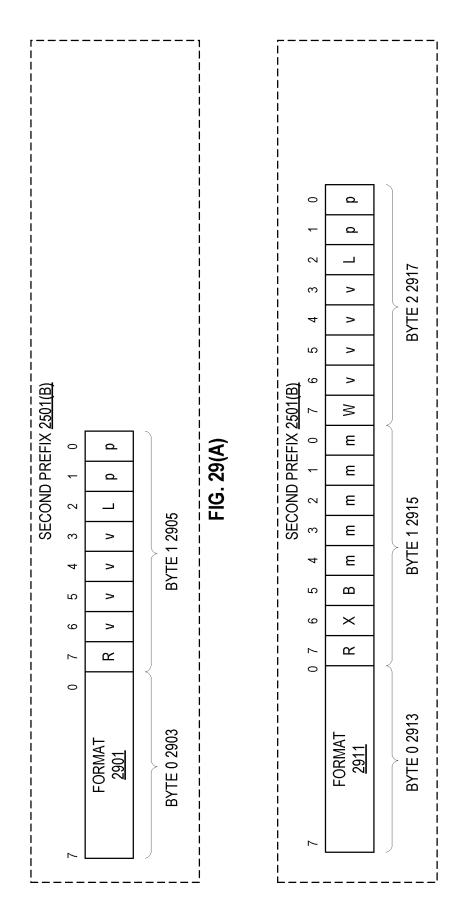

FIGS. 29(A)-(B) are functional block diagrams illustrating details of a second example prefix of the instruction format of FIG. 25 according to the present embodiments;

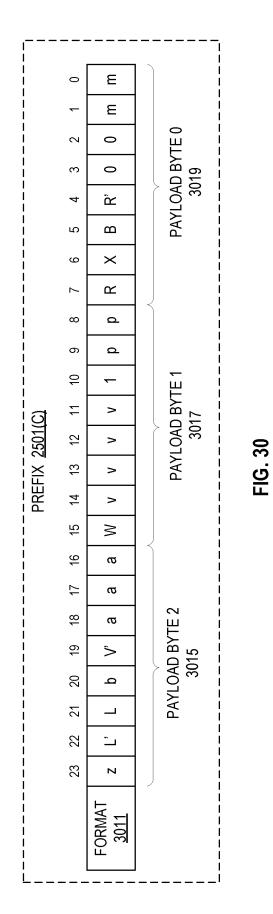

FIG. 30 is a functional block diagram illustrating details of a third example prefix of the instruction format of FIG. 25 according to the present embodiments; and

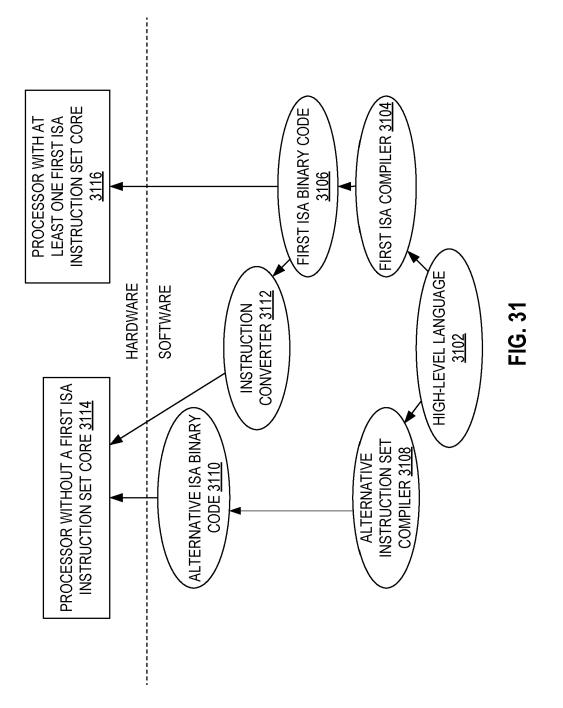

FIG. 31 is a functional block diagram contrasting the use of a software instruction converter to convert binary instructions in a source instruction set to binary instructions in a target instruction set according to the present

embodiments.

#### DETAILED DESCRIPTION

- <sup>5</sup> **[0005]** The present disclosure relates to methods, apparatus, systems, and non-transitory computer-readable storage media storing instructions for encrypting data using a key generated by a physical unclonable function (PUF). Encryption is the process of encoding information, and is a tool used to protect the security or privacy of sensitive information (e.g., passwords) stored on a computer. The encryption process converts the original representation of the information, known as plaintext, into an alternative form known as ciphertext. An encryption scheme usually uses a pseudo-random encryption

- 10 key generated by an algorithm. Authorized parties who possess the key can easily decrypt the encoded information. It is possible to decrypt the encoded information without possessing the key, but, for a well-designed encryption scheme, considerable computational resources and skills are required.

10 To maintain the encoded information without possessing the key but, for a well-designed encryption scheme, considerable computational resources and skills are required.

**[0006]** To maintain the secrecy of the encoded information, it is thus important to prevent access to the encryption key by unauthorized parties. One way to protect an encryption key (or any secret information, such as a password) when

- <sup>15</sup> stored on a computer is to store the secret information using electronic fuses. Fuses had long been considered to be secure, but recent studies have shown that determined hardware attackers can scan the fuses and recover the secret information. The present embodiments solve this problem by protecting the secret information with a PUF-generated encryption key. PUFs advantageously protect against scanning, and the PUF circuit is also resistant to side-channel attacks (e.g., attacks using EM radiation).

- 20 [0007] According to some embodiments, a software-visible PUF (SV-PUF) exposes the PUF functionality to software through instruction. One or more of these instructions comprise a SV-PUF ISA or ISA extension (throughout the description SV-PUF ISA will be the term used, but the text below applies to an ISA extension). The present embodiments disclose the use of a SV-PUF for wrapping secrets and tying them to a platform using PUF-derived keys. This wrapping (encryption and integrity protection) can protect secrets such as passwords, keys, cookies, etc. while they are not in use, and

- <sup>25</sup> unwrap/retrieve the secrets in plaintext at the point of use. The secrets protected using PUF-derived keys can then either be returned back to software, or can be used to program encryption engine(s) (e.g., Multi-Key Total Memory Encryption (MKTME) available from Intel Corporation of Santa Clara, California) on the platform. In the case of programming encryption engine(s), the secrets are advantageously never revealed in plaintext after initial provisioning through the lifetime of the platform, and are instead programmed directly to the desired encryption engine(s) over an interface using

<sup>30</sup> the instructions of the present embodiments.

- [0008] The present embodiments advantageously enable binding secrets to the platform using PUF-derived keys for protecting them. In addition, the secrets can be tied to a configuration of the platform (e.g., whether a platform firmware verification program, such as Intel Boot Guard, is enabled) and the processor (e.g., the secrets are wrapped inside an enclave or a trust domain). Furthermore, the secrets are retained across boots, because the same key is generated by the PUF each time the system reboots.

**[0009]** As contemplated in the present disclosure, embodiments include a processor security capability called Trusted Domain Extensions (TDX) to meet increased security objectives via the use of memory encryption and integrity via memory controller engines. As used in TDX, a Trusted Domain (TD) is a protected VM.

- [0010] Embodiments comprise an additional extended page table (EPT) structure called a Secure Extended Page Table (SEPT) that is used by a processor for TD private page walks. The SEPT is a per-TD EPT (i.e., each TD has its own SEPT) that is managed by a Trusted Domain Resource Manager (TDRM) only via special instructions newly added to the instruction set architecture (ISA) of the processor. The TDRM cannot alter SEPT without using these instructions otherwise an integrity failure will be reported by the processor. In other embodiments, all or parts of the SEPT may be access-controlled using processor range-register protection.

- In typical VM implementations, the processor supports one EPT pointer (EPTP) per virtual memory control structure (VMCS). The VMCS is a data structure in memory that exists once per VM, while the VM is managed by the VMM. With every change of the execution context between different VMs, the VMCS is restored for the current VM, thereby defining the state of the VM's virtual processor. The VMM manages the EPT referenced by the EPTP. In embodiments, the VMs may be encapsulated by TDs, and the VMCS may be replaced by an analogous control structure called the Trusted Domain Control Structure (TDCS) that manages the guest state of TDs.

- [0012] An architecture to provide isolation in virtualized systems using trust domains (TDs) is described. A current trend in computing is the placement of data and enterprise workloads in the cloud by utilizing hosting services provided by cloud service providers (CSPs). As a result of the hosting of the data and enterprise workloads in the cloud, customers (referred to as tenants herein) of the CSPs are requesting better security and isolation solutions for their workloads. In

- <sup>55</sup> particular, customers are seeking out solutions that enable the operation of CSP-provided software outside of a TCB of the tenant's software. The TCB of a system refers to a set of hardware, firmware, and/or software components that have an ability to influence the trust for the overall operation of the system.

[0013] In implementations of the disclosure, a TD architecture and instruction set architecture (ISA) extensions (referred

to herein as TD extensions (TDX)) for the TD architecture is provided to provide confidentiality (and integrity) for customer (tenant) software executing in an untrusted CSP infrastructure. The TD architecture, which can be a System-on-Chip (SoC) capability, provides isolation between TD workloads and CSP software, such as a virtual machine manager (VMM) of the CSP. Components of the TD architecture can include 1) memory encryption via a MK-Total Memory Encryption

<sup>5</sup> (MKTME) engine, 2) a resource management capability referred to herein as the trust domain resource manager (TDRM) (a TDRM may be a software extension of the Virtual Machine Monitor (VMM)), and 3) execution state and memory isolation capabilities in the processor provided via a CPU-managed Memory Ownership Table (MOT) and via CPU access-controlled TD control structures. The TD architecture provides an ability of the processor to deploy TDs that leverage the MK-TME engine, the MOT, and the access-controlled TD control structures for secure operation of TD workloads.

**[0014]** In one implementation, the tenant's software is executed in an architectural concept known as a TD. A TD (also referred to as a tenant TD) refers to a tenant workload (which can comprise an operating system (OS) alone along with other ring-3 applications running on top of the OS, or a virtual machine (VM) running on top of a VMM along with other ring-3 applications, for example). Each TD operates independently of other TDs in the system and uses logical proces-

<sup>15</sup> sor(s), memory, and I/O assigned by the TDRM on the platform. Each TD is cryptographically isolated in memory using at least one exclusive encryption key of the MK-TME engine for encrypting the memory (holding code and/or data) associated with the trust domain.

**[0015]** In implementations of the disclosure, the TDRM in the TD architecture acts as a host for the TDs and has full control of the cores and other platform hardware. A TDRM assigns software in a TD with logical processor(s). The TDRM,

20 however, cannot access a TD's execution state on the assigned logical processor(s). Similarly, a TDRM assigns physical memory and I/O resources to the TDs, but is not privy to access the memory state of a TD due to the use of separate encryption keys enforced by the processors per TD, and other integrity and replay controls on memory. Software executing in a TD operates with reduced privileges so that the TDRM can retain control of platform resources. However, the TDRM cannot affect the confidentiality or integrity of the TD state in memory or in the CPU structures under defined circum-

25 stances.

40

50

**[0016]** Conventional systems for providing isolation in virtualized systems do not extract the CSP software out of the tenant's TCB completely. Furthermore, conventional systems may increase the TCB significantly using separate chipset subsystems that implementations of the disclosure avoid. The TD architecture of implementations of the disclosure provides isolation between customer (tenant) workloads and CSP software by explicitly reducing the TCB by removing

- the CSP software from the TCB. Implementations provide a technical improvement over conventional systems by providing secure isolation for CSP customer workloads (tenant TDs) and allow for the removal of CSP software from a customer's TCB while meeting security and functionality requirements of the CSP. In addition, the TD architecture is scalable to multiple TDs, which can support multiple tenant workloads. Furthermore, the TD architecture described herein is generic and can be applied to any dynamic random-access memory (DRAM), or storage class memory

- 35 (SCM)-based memory, such as Non-Volatile Dual In-line Memory Module (NVDIMM). As such, implementations of the disclosure allow software to take advantage of performance benefits, such as NVDIMM direct access storage (DAS) mode for SCM, without compromising platform security requirements.

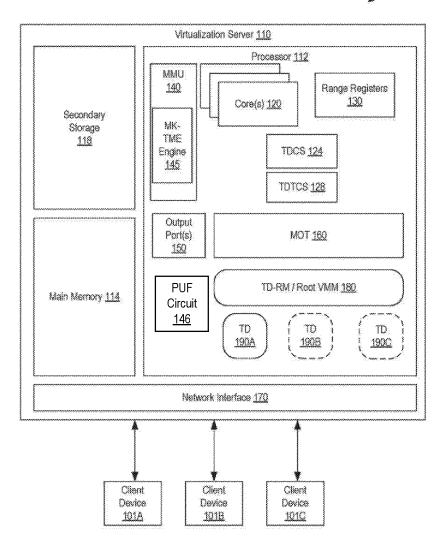

**[0017]** FIG. 1 is a schematic block diagram of a computing system 100 that provides isolation in virtualized systems using TDs, according to an implementation of the disclosure. The virtualization system 100 includes a virtualization server 110 that supports a number of client devices 10IA-101 C. The virtualization server 110 includes at least one processor 112 (also referred to as a processing device) that executes a TDRM 180. The TDRM 180 may include a VMM (may also be referred to as hypervisor) that may instantiate one or more TDs 190A-190C accessible by the client devices

101A-101C via a network interface 170. The client devices 10IA-101 C may include, but is not limited to, a desktop computer, a tablet computer, a laptop computer, a netbook, a notebook computer, a personal digital assistant (PDA), a

server, a workstation, a cellular telephone, a mobile computing device, a smart phone, an Internet appliance or any other type of computing device.

**[0018]** A TD may refer to a tenant (e.g., customer) workload. The tenant workload can include an OS alone along with other ring-3 applications running on top of the OS, or can include a VM running on top of a VMM along with other ring-3 applications, for example. In implementations of the disclosure, each TD may be cryptographically isolated in memory using a separate exclusive key for encrypting the memory (holding code and data) associated with the TD.

- **[0019]** Processor 112 may include one or more cores 120 (also referred to as processing cores 120), range registers 130, a memory management unit (MMU) 140, and output port(s) 150. Processor 112 may be used in a system that includes, but is not limited to, a desktop computer, a tablet computer, a laptop computer, a netbook, a notebook computer, a PDA, a server, a workstation, a cellular telephone, a mobile computing device, a smart phone, an Internet appliance

- or any other type of computing device. In another implementation, processor 112 may be used in a SoC system. [0020] The computing system 100 is representative of processing systems based on micro-processing devices available from Intel Corporation of Santa Clara, Calif., although other systems (including PCs having other micro-processing devices, engineering workstations, set-top boxes and the like) may also be used. In one implementation, sample system

100 executes a version of the WINDOWS<sup>™</sup> operating system available from Microsoft Corporation of Redmond, Wash., although other operating systems (UNIX and Linux for example), embedded software, and/or graphical user interfaces, may also be used. Thus, implementations of the disclosure are not limited to any specific combination of hardware circuitry and software.

- <sup>5</sup> **[0021]** The one or more processing cores 120 execute instructions of the system. The processing core 120 includes, but is not limited to, pre-fetch logic to fetch instructions, decode logic to decode the instructions, execution logic to execute instructions and the like. In an implementation, the computing system 100 includes a component, such as the processor 112 to employ execution units including logic to perform algorithms for processing data.

- [0022] The virtualization server 110 includes a main memory 114 and a secondary storage 118 to store program binaries and OS driver events. Data in the secondary storage 118 may be stored in blocks referred to as pages, and each page may correspond to a set of physical memory addresses. The virtualization server 110 may employ virtual memory management in which applications run by the core(s) 120, such as the TDs 190A-190C, use virtual memory addresses that are mapped to guest physical memory addresses, and guest physical memory addresses are mapped to host/system physical addresses by MMU 140.

- 15 [0023] The core 120 may execute the MMU 140 to load pages from the secondary storage 118 into the main memory 114 (which includes a volatile memory and/or a nonvolatile memory) for faster access by software running on the processor 112 (e.g., on the core). When one of the TDs 190A-190C attempts to access a virtual memory address that corresponds to a physical memory address of a page loaded into the main memory 114, the MMU 140 returns the requested data. The core 120 may execute the VMM portion of TDRM 180 to translate guest physical addresses to host

- <sup>20</sup> physical addresses of main memory and provide parameters for a protocol that allows the core 120 to read, walk and interpret these mappings.

[0024] In one implementation, processor 112 implements a TD architecture and ISA extensions (TDX) for the TD architecture. The TD architecture provides isolation between TD workloads 190A-190C and from CSP software (e.g.,

- TDRM 180 and/or a CSP VMM (e.g., root VMM 180)) executing on the processor 112). Components of the TD architecture

can include 1) memory encryption via MK-ME engine (memory encryption engine (MEE) or memory protection controller)

145 or other encryption engine, 2) a resource management capability referred to herein as the TDRM 180, and 3)

execution state and memory isolation capabilities in the processor 112 provided via a MOT 160 and via access-controlled

TD control structures (i.e., TDCS 124 and TDTCS 128). The TDX architecture provides an ability of the processor 112

to deploy TDs 190A-190C that leverage the MK-TME engine 145, the MOT 160, and the access-controlled TD control

- 30 structures (i.e., TDCS 124 and TDTCS 128) for secure operation of TD workloads 190A-190C.

[0025] A physically unclonable function (PUF) circuit 146 responds to a challenge to provide a unique value. Note that while illustrated as a part of a processor 112, the PUF circuit 146 may be external to the processor 112. In some embodiments, it is a part of the MMU 140. In some embodiments, it is a part of the core(s) 120.

[0026] In implementations of the disclosure, the TDRM 180 acts as a host and has full control of the cores 120 and

- other platform hardware. A TDRM 180 assigns software in a TD 190A-190C with logical processor(s). The TDRM 180, however, cannot access a TD's 190A-190C execution state on the assigned logical processor(s). Similarly, a TDRM 180 assigns physical memory and I/O resources to the TDs 190A-190C, but is not privy to access the memory state of a TD 190A due to separate encryption keys, and other integrity and replay controls on memory.

- [0027] With respect to the separate encryption keys, the processor may utilize the MK-TME engine 145 to encrypt (and decrypt) memory used during execution. With total memory encryption (TME), any memory accesses by software executing on the core 120 can be encrypted in memory with an encryption key. MK-TME is an enhancement to TME that allows use of multiple encryption keys (the number of supported keys is implementation dependent). The processor 112 may utilize the MKTME engine 145 to cause different pages to be encrypted using different MK-TME keys. The MK-TME engine 145 may be utilized in the TD architecture described herein to support one or more encryption keys per

- <sup>45</sup> each TD 190A-190C to help achieve the cryptographic isolation between different CSP customer workloads. For example, when MK-TME engine 145 is used in the TD architecture, the CPU enforces by default that TD (all pages) are to be encrypted using a TD-specific key. Furthermore, a TD may further choose specific TD pages to be plain text or encrypted using different ephemeral keys that are opaque to CSP software. The MK-TME engine 145 may include storage for the one or more keys. In some embodiments, there is at least one fuse keys on die.

- 50 [0028] Each TD 190A-190C is a software environment that supports a software stack consisting of VMMs (e.g., using virtual machine extensions (VMX)), OSes, and/or application software (hosted by the OS). Each TD 190A-190C operates independently of other TDs 190A-190C and uses logical processor(s), memory, and I/O assigned by the TDRM 180 on the platform. Software executing in a TD 190A-190C operates with reduced privileges so that the TDRM 180 can retain control of platform resources; however, the TDRM cannot affect the confidentiality or integrity of the TD 190A-190C

- **[0029]** Implementations of the disclosure are not limited to computer systems. Alternative implementations of the disclosure can be used in other devices such as handheld devices and embedded applications. Some examples of handheld devices include cellular phones, Internet Protocol devices, digital cameras, personal digital assistants (PDAs),

and handheld PCs. Embedded applications can include a micro controller, a digital signal processing device (DSP), system on a chip, network computers (NetPC), set-top boxes, network hubs, wide area network (WAN) switches, or any other system that can perform one or more instructions in accordance with at least one implementation.

- [0030] One implementation may be described in the context of a single processing device desktop or server system, <sup>5</sup> but alternative implementations may be included in a multiprocessing device system. Computing system 100 may be an example of a 'hub' system architecture. The computing system 100 includes a processor 112 to process data signals. The processor 112, as one illustrative example, includes a complex instruction set computer (CISC) micro-processing device, a reduced instruction set computing (RISC) micro-processing device, a very long instruction word (VLIW) microprocessing device, a processing device implementing a combination of instruction sets, or any other processing device,

- <sup>10</sup> such as a digital signal processing device, for example. The processor 112 is coupled to a processing device bus that transmits data signals between the processor 112 and other components in the computing system 100, such as main memory 114 and/or secondary storage 118, storing instruction, data, or any combination thereof. The other components of the computing system 100 may include a graphics accelerator, a memory controller hub, an I/O controller hub, a wireless transceiver, a Flash BIOS, a network controller, an audio controller, a serial expansion port, an I/O controller,

- etc. These elements perform their conventional functions that are well known to those familiar with the art.

[0031] In one implementation, processor 112 includes a Level 1 (L1) internal cache memory. Depending on the architecture, the processor 112 may have a single internal cache or multiple levels of internal caches. Other implementations include a combination of both internal and external caches depending on the particular implementation and needs. A register file is to store different types of data in various registers including integer registers, floating point registers, vector

- 20 registers, banked registers, shadow registers, checkpoint registers, status registers, configuration registers, and instruction pointer register.

25

**[0032]** It should be noted that the execution unit may or may not have a floating-point unit. The processor 112, in one implementation, includes a microcode (ucode) ROM to store microcode, which when executed, is to perform algorithms for certain macroinstructions or handle complex scenarios. Here, microcode is potentially updateable to handle logic bugs/fixes for processor 112.

**[0033]** Alternate implementations of an execution unit may also be used in micro controllers, embedded processing devices, graphics devices, DSPs, and other types of logic circuits. System 100 includes a main memory 114 (may also be referred to as memory 114). Main memory 114 includes a DRAM device, a static random-access memory (SRAM) device, flash memory device, or other memory device. Main memory 114 stores instructions and/or data represented

- <sup>30</sup> by data signals that are to be executed by the processor 112. The processor 112 is coupled to the main memory 114 via a processing device bus. A system logic chip, such as a memory controller hub (MCH) may be coupled to the processing device bus and main memory 114. An MCH can provide a high bandwidth memory path to main memory 114 for instruction and data storage and for storage of graphics commands, data and textures. The MCH can be used to direct data signals between the processor 112, main memory 114, and other components in the system 100 and to

- <sup>35</sup> bridge the data signals between processing device bus, memory 114, and system 1/0, for example. The MCH may be coupled to memory 114 through a memory interface. In some implementations, the system logic chip can provide a graphics port for coupling to a graphics controller through an Accelerated Graphics Port (AGP) interconnect. [0034] The computing system 100 may also include an I/O controller hub (ICH). The ICH can provide direct connections to some I/O devices via a local I/O bus. The local I/O bus is a highspeed I/O bus for connecting peripherals to the memory

- 40 114, chipset, and processor 112. Some examples are the audio controller, firmware hub (flash BIOS), wireless transceiver, data storage, legacy I/O controller containing user input and keyboard interfaces, a serial expansion port such as Universal Serial Bus (USB), and a network controller. The data storage device can comprise a hard disk drive, a floppy disk drive, a CD-ROM device, a flash memory device, or other mass storage device.

- [0035] For another implementation of a system, the instructions executed by the processing device core 120 described above can be used with a system on a chip. One implementation of a system on a chip comprises of a processing device and a memory. The memory for one such system is a flash memory. The flash memory can be located on the same die as the processing device and other system components. Additionally, other logic blocks such as a memory controller or graphics controller can also be located on a system on a chip.

- **[0036]** FIG. 2(A) illustrates an example of using a PUF to generate and use a key for wrapping and unwrapping data according to the present embodiments. Generally, an execution of a wrapping instruction according to the present embodiments receives data that is to be kept secure (may be referred to herein as a "secret"). The secret may be any information, for example, and without limitation, a password, an encryption key, etc. The wrapping instruction receives the secret as a part of an input and encrypts it using a PUF derived key. The input is updated and wrapped (e.g., encrypts and integrity-protects). In some embodiments, the output of the secret wrapping process (may be referred to herein as

- <sup>55</sup> a "blob" or a "wrapped blob") is tied to a particular use. For example, a blob may be generated to protect a secret that software intends to retrieve at a later point in time. In another example, a blob can be generated to protect keys for programming to a cryptographic engine. As an example of this use, MKTME keys for persistent memory can be protected using the present ISA.

**[0037]** To use the secrets available in wrapped blobs, the present embodiments further provide for execution of an unwrapping instruction that receives, from software, the wrapped blob as an input operand and unwraps the blob (e.g., decrypts and verifies the integrity) and decrypts the secret using a PUF derived key. The retrieved secret is then returned to the software or programmed to a cryptographic engine, depending on the intended use, which is indicated by software

- to the instruction at the time of wrapping. In some embodiments, the wrapping instruction allows platform and processor configuration to be included in the wrapping, such that the unwrapping instruction will allow a blob to be unwrapped only if the platform and processor configuration desired at the time of wrapping is active at the time of unwrapping.

[0038] With further reference to FIG. 2(A), software requests, of a SV-PUF wrapping instruction of the SV-PUF ISA 2(A)02 according to the present embodiments, a encryption of a secret using a PUF-derived key 2(A)04. In addition to

- <sup>10</sup> providing the secret to encrypt, the software also provides a challenge 2(A)06, which is used to generate the PUFderived key 2(A)04 from the root PUF key (described below. As described in further detail below, in some embodiments the challenge 2(A)06 is a 256-bit random value chosen by the software, and it must be provided for both wrapping the secret and unwrapping the secret. Execution circuitry executing the wrapping instruction (described below in greater detail) of the SV-PUF ISA takes the input provided by the software in a memory structure and, using the challenge 2(A)06

- <sup>15</sup> provided by the software, excites a PUF circuit 2(A)08 to get the PUF-derived key 2(A)04 to be used to encrypt the secret. After retrieving the key 2(A)04 from the PUF circuit 2(A)08, the execution of the wrapping instruction uses the key 2(A)04 to encrypt the secret and integrity-protect a data structure containing encrypted secret to generate a wrapped blob. The wrapped blob is then returned to the software in a memory location provided by the software.

[0039] Later, when the software needs to use the secret, the software requests, an unwrapping instruction of the SV-

- PUF ISA 2(A)02, an unwrapping of the secret contained within the blob. The SV-PUF ISA 2(A)02 has multiple instructions for unwrapping in some embodiments, and the particular instruction invoked for a given unwrapping request from the software depends upon the use of the secret in that instance. In a first example where the software needs to retrieve the secret, a first unwrapping instruction of the SV-PUF ISA 2(A)02 receives the wrapped blob as an input operand and unwraps the secret by checking the integrity of the blob and decrypting it. The retrieved secret is then returned back to find the blob.

- the software. In addition to providing the blob to unwrap, the software also provides the challenge 2(A)06, which is used to generate the PUF-derived key 2(A)04 from the root PUF key (described below) for unwrapping the blob.

[0040] In a second example, where the secret is to be used for programming to a cryptographic engine, such as where a persistent memory key is programmed to the MKTME engine using a wrapped blob, a second unwrapping instruction of the SV-PUF ISA 2(A)02 receives the wrapped blob as an input operand and unwraps data structure by checking the

- <sup>30</sup> integrity of the blob and decrypting the secret data, but does not return the retrieved key(s) to the software. Instead, the key is programmed directly to the target cryptographic engine over an interface, thereby never exposing the key(s) in plaintext in memory. In addition to providing the blob to unwrap, the software also provides the challenge 2(A)06, which is used to generate the PUF-derived key 2(A)04 from the root PUF key (described below) for unwrapping the blob. [0041] FIG. 2(B) illustrates an example process 2(B)02 for wrapping and unwrapping a secret according to the present

- <sup>35</sup> embodiments. At 2(B)S04, software 2(B)06 requiring to protect a secret invokes an instruction, wrap (WRP described below), passing the data to wrap as an input operand to the SV-PUF instructions 2(A)02 along with the challenge 2(A)06. At 2(B)S08, the WRP instruction of the SV-PUF instructions 2(A)02 uses the challenge 2(A)06 as an input to the PUF circuit 2(A)08 to generate the unique PUF-derived key 2(A)04. In some embodiments, the PUF root key is mixed with the challenge 2(A)06 using a standard key derivation function (KDF). Further, in some embodiments, the PUF circuit

- 2(A)08 itself can provide multiple root keys for different uses. As an example, there can be one root key derived for standard platform uses (e.g., protecting fuses) and another root key for SV-PUF uses. The WRP instruction of the SV-PUF ISA 2(A)02 uses the challenge 2(A)06 to get the PUF-derived key 2(A)04, and uses the PUF-derived key 2(A)04 to encrypt and integrity-protect the secret at 2(B)S08. At 2(B)S10, the SV-PUF instructions 2(A)02 provides the wrapped blob as an output of the WRP instruction in a memory location specified by the software 2(B)06 and provided as an input

- <sup>45</sup> to the WRP instruction. The software 2(B)06 retains the blob in memory when the secret it protects is not in use. [0042] With further reference to FIG. 2(B), at 2(B)S12, when the software 2(B)06 needs access to the secret contained within the blob, the software 2(B)06 invokes another instruction, unwrap (UNWRP) (described below), passing the wrapped blob as an input operand to the SV-PUF instructions 2(A)02 along with the challenge 2(A)06. At 2(B)S14, the UNWRP instruction of the SV-PUF instructions 2(A)02 uses the challenge 2(A)06 along with the blob as an input to the

- <sup>50</sup> PUF circuit 2(A)08 to retrieve the unique PUF-derived key 2(A)04 that was used to wrap the blob. The UNWRP instruction of the SV-PUF ISA 2(A)02 then uses the PUF-derived key 2(A)04 to decrypt the wrapped blob and verify its integrity at 2(B)S14. The integrity verification will only be successful if the wrapped blob passed by the software 2(B)06 at 2(B)S12 is unmodified as compared to the wrapped blob that the SV-PUF instructions 2(A)02 provided to the software 2(B)06 at 2(B)S10. If the integrity verification is successful, the unwrapped data is returned back to the software at 2(B)S16.

- <sup>55</sup> **[0043]** FIG. 2(C) illustrates another example process for wrapping and unwrapping a secret according to the present embodiments. In the embodiment of FIG. 2(C), the software 2(B)06 programs an encryption key to a hardware block on the platform. One non-limiting example of such a use is programming keys for persistent memory to the MKTME engine. In this use, during a provisioning phase, which can happen when a user receives his or her employer-issued computer

at the IT center in an enterprise environment, the key to be used for persistent memory encryption is encrypted using a PUF-derived key similar to the embodiment described above with reference to FIG. 2(B). Acts 2(C)S04, 2(C)S08, and 2(C)S10, use the WRP instruction as previously described above with reference to steps 2(B)S04, 2(B)S08, and 2(B)S10, respectively.

- <sup>5</sup> **[0044]** With further reference to FIG. 2(C), at 2(C)S12, when the software 2(C)06 wants to program the key (e.g., on each reboot to set up the persistent memory key), the software 2(C)06 invokes another instruction, PCONFIG (described below), passing the wrapped blob as an input operand to the SV-PUF ISA 2(A)02 along with the challenge 2(A)06. At 2(C)S14, the PCONFIG instruction of the SV-PUF instructions 2(A)02 unwraps and verifies the integrity of the blob, as described above at 2(B)S14. However, in this embodiment, instead of returning the decrypted secret back to the software

- 2(C)06, at 2(C)S16 the key is programmed to the key programming target 2(C)18 (e.g., an encryption engine) over an interface. In this way, the key is advantageously never exposed in memory beyond the provisioning phase, which typically happens only once during the lifetime of the platform. At 2(B)S20, the SV-PUF instructions 2(A)02 returns a response of successful/failed programming to the requesting software 2(C)06.

- [0045] In some embodiments, the ISA (e.g., WRP, UNWRP, UNWRPMAC, PCONFIG) is executed by the execution cluster(s) 2260 of the execution engine 2250 of the processor core 2290 (FIG. 22(B)). For example, the execution units circuitry 2262 may execute the present ISA to communicate with the PUF circuitry 2280, passing the challenge 2(A)06 to the PUF circuitry 2280 and receiving the PUF-derived key 2(A)04 from the PUF circuitry 2280. In some embodiments, the PUF circuitry 2280 may be part of the execution engine 2250, while in other embodiments the PUF circuitry 2280 may be part of the execution engine 2250.

- [0046] FIG. 3 illustrates embodiments of hardware to process an instruction, such as a SV-PUF instruction. As illustrated, storage 303 stores a SV-PUF instruction 301 to be executed.

[0047] The instruction 301 is received by decode circuitry 305. For example, the decode circuitry 305 receives this instruction from fetch logic/circuitry. The instruction includes fields for an opcode, first and second sources, and a destination. In some embodiments, the sources and destination are registers, and in other embodiments one or more

- <sup>25</sup> are memory locations. In some embodiments, the opcode details which arithmetic operation(s) is/are to be performed. [0048] More detailed embodiments of at least one instruction format will be detailed later. The decode circuitry 305 decodes the instruction into one or more operations. In some embodiments, this decoding includes generating a plurality of micro-operations to be performed by execution circuitry (such as execution circuitry 309). The decode circuitry 305 also decodes instruction prefixes.

- 30 [0049] In some embodiments, register renaming, register allocation, and/or scheduling circuitry 307 provides functionality for one or more of: 1) renaming logical operand values to physical operand values (e.g., a register alias table in some embodiments), 2) allocating status bits and flags to the decoded instruction, and 3) scheduling the decoded instruction for execution on execution circuitry out of an instruction pool (e.g., using a reservation station in some embodiments).

- 35 [0050] Registers (register file) and/or memory 308 store data as operands of the instruction to be operated on by execution circuitry 309. Example register types include packed data registers, general purpose registers, and floatingpoint registers.

**[0051]** Execution circuitry 309 executes the decoded instruction (e.g., a SV-PUF instruction). Example detailed execution circuitry is shown in other figures, including at least FIG. 22. The execution of the decoded SV-PUF instruction

40 causes the execution circuitry to perform the act(s) indicated by the opcode of the instruction. For some of the instructions, the execution circuitry 309 interacts with SV-PUF circuitry 310 (if that circuitry is not included in the execution circuitry 309. In some embodiments, the SV-PUF circuitry 310 is a part of a core. In some embodiments, the SV-PUF circuitry 310 is external to a core.

**[0052]** In some embodiments, retirement/write back circuitry 311 architecturally commits the destination register into the registers or memory 308 and retires the instruction.

**[0053]** A first instruction of the SV-PUF ISA is a wrapping instruction (WRP). An execution of a WRP instruction causes data to be encrypted using a key generated by a SV-PUF. In some embodiments, the WRP instruction is associated with a most-privileged protection ring (e.g., ring-0). Therefore, when the software invokes the WRP instruction, a confirmation may be needed to determine that the software has the necessary privileges before completing the wrapping

45

- <sup>50</sup> process. To invoke the WRP instruction, the software passes, to the SV-PUF WRP instruction, an input memory buffer location, an output memory buffer location, and the challenge to be provided to the PUF to generate the wrapping key. The WRP instruction operates using BIND\_STRUCT (described below) as an input and output structure, which allows specification of target-specific data. In some embodiments, the WRP instruction identifies three operands. A source operand is to store a location of a source (input) BIND\_STRUCT. A first destination operand is to store an operation

- 55 status of the execution of the WRP instruction. A second destination operand is to store a location of a destination (output) BIND\_STRUCT.

**[0054]** In some embodiments, one or more of the identified operands are registers (e.g., RAX, RBC, RCX, etc.). In some embodiments, one or more of the identified operands are memory locations. The location of the structs is provided

by an address in some embodiments. For example, the first source operand stores an address for the input struct, etc. The WRP instruction affects the following flags or condition codes in some embodiments, a zero flag, a carry flag, a parity flag, an overflow flag, an adjust flag, and/or a sign flag. The zero flag (ZF) is cleared on a successful wrap, and set to 1 otherwise whereas CF, PF, AF, OF, and SF are always cleared.

5 [0055] The WRP instruction includes one or more fields to be used to encode an opcode. The opcode is to indicate that execution circuitry is to encryptat least encrypt secret information from the input data structure with a PUF generated wrapping key, bind the wrapped secret information to a target, update the input data structure, generate a MAC over the updated data structure, store the MAC in the input data structure to generate an output data structure, store an output data structure having the wrapped secret information and an indication of the target according to the second destination operand's usage for the instruction. An operational stats may be updated too.

[0056] The table below shows the structure of BIND\_STRUCT, and the fields of BIND\_STRUCT are described just below the table.

|    |           |                   |                 |                  | -                                                    |                         |                               |

|----|-----------|-------------------|-----------------|------------------|------------------------------------------------------|-------------------------|-------------------------------|

| 15 | Field     | Offset<br>(Bytes) | Size<br>(Bytes) | Input/<br>Output | Description                                          | Integrity<br>Protected? | Confidentiality<br>Protected? |

|    | MAC       | 0                 | 16              | Output           | MAC on BIND_<br>STRUCT                               | N/A                     | N/A                           |

| 20 | BTID      | 16                | 4               | Input            | Target for wrapping (e.g., MKTME engine)             | Y                       | N                             |

|    | RSVD      | 20                | 4               | Input            | RSVD, must be zero                                   | Y                       | N                             |

| 25 | SEQID     | 24                | 8               | Output           | Seed for generating<br>initialization vector<br>(IV) | Y                       | N                             |

|    | RSVD      | 32                | 32              | Input            | RSVD, must be zero                                   | Y                       | N                             |

| 30 | BTENCDATA | 64                | 64              | Input/<br>Output | Target-specific<br>encrypted data                    | Y                       | Y                             |

|    | BTDATA    | 128               | 128             | Input            | Target-specific data<br>(challenge)                  | Y                       | N                             |

BIND STRUCT

- [0057] Note that the MAC is generated on a data structure having generated SEQID, encrypted BTENCDATA (or a portion of that data), BTDATA, and reserved fields which is what it is not integrity protected (it provides that protection). In some embodiments, the MAC is generated using a GHASH function.

[0058] MAC: This field is a Message Authentication Code over the data structure generated by the WRP instruction.

- The software does not populate this field. Therefore, on the input side this field may be empty.

[0059] A message authentication code (MAC) is a cryptographic checksum on data that uses a session key to detect both accidental and intentional modifications of the data. A MAC requires two inputs: a message and a secret key known only to the originator of the message and its intended recipient(s). This allows the recipient of the message to verify the integrity of the message and authenticate that the message's sender has the shared secret key. If a sender does not know the secret key, the hash value would then be different, which would tell the recipient that the message was not from the original sender.

**[0060]** BTID: This field is a target for wrapping, and is populated by the software. There may be one or more targets for the uses according to the present embodiments. Examples include a CPU (or core), a memory encryption engine, etc. Tying the wrapped data to a particular use enhances the security of the data wrapping process, as further described below.

- <sup>50</sup> **[0061]** FIG. 4 is a functional block diagram illustrating a bitvector representing a platform/processor configuration to which the wrapped data is to be bound. The fields in the bitvector 402 indicate whether the corresponding program is active or inactive, and the state of the bit positions collectively indicates a platform/processor configuration. In some embodiments, the WRP instruction microcode uses this bitvector 402 during the wrapping process and binds the blob to the configuration indicated by the bitvector 402 by including it in the MAC generated on the output BIND STRUCT

- (Table 1). In some embodiments, the execution of the WRP instruction does not do any checks, but the unwrapping instructions (e.g., UNWRP, UNWRPMAC, and/or PCONFIG) check for platform/processor configurations and only allow unwrapping if the configuration that the software provided (as part of BTDATA (detailed below) in BIND\_STRUCT) is active at the time of unwrapping. Therefore, the software checks the current platform/processor configuration before

requesting binding to ensure that it doesn't bind secrets to a configuration that is not active on the platform. Binding done for an inactive configuration will result in a blob that cannot be unwrapped to retrieve the secret(s). For example, if a platform firmware verification program (e.g., Intel Boot Guard) was not enabled at the time of wrapping, and the software requested binding without first verifying that Boot Guard was enabled, then the UNWRP instruction will disallow unwrapping the blob if Boot Guard is not enabled at unwrapping time.

- [0062] As another example embodiment, the WRP instruction allows wrapping to the software identity (e.g., process identity, enclave measurement, virtual machine/trust domain measurement). The execution of the WRP instruction, if requested to bind to the identity of the software, picks the identity from hardware and includes it in the MAC generated. On unwrapping, the execution of the unwrapping instruction uses the identity from hardware to verify the MAC. If the 10 software unwrapping a blob does not own the blob, the unwrapping will fail.

- **[0063]** SEQID: This field is an initialization vector used for authenticated encryption performed by the WRP instruction. In some embodiments, microcode randomly generates this vector and uses it for encryption and MAC generation. This field is later used during the unwrapping process to decrypt and verify the MAC.

- [0064] BTENCDATA: This field carries the data (secret) that the software is requesting to be wrapped. As an example, 15 for MKTME key programming, this field carries two keys: A data encryption key, and a tweak key to be used for encryption using Advanced Encryption Standard (AES) in XTS mode (XEX-based tweaked-codebook mode with ciphertext stealing). In some embodiments, each key can be up to 256b in size. Advantageously, the software can cryptographically protect any amount of data using a key, and then use the present SV-PUF ISA to protect the key, thereby allowing arbitrarily large amounts of data to be protected with the SV-PUF.

- 20 [0065] BTDATA: This field carries information such as the challenge to be used by the PUF circuit to generate the key, and a configuration vector to indicate, to the WRP instruction, the platform and processor configuration to be included with the data wrapping. In some embodiments, this field may include one or more sub-fields that control the data wrapping using the PUF-derived key. For example, and as shown the table below, there may be two sub-fields: 1) The challenge used to generate the PUF-derived key, and 2) A bit vector to carry the platform/processor configuration to which the

| 25 | wrapped data is to be bound. |

|----|------------------------------|

|----|------------------------------|

5

40

|    | DIDAIA                  |                   |              |                                                                         |  |

|----|-------------------------|-------------------|--------------|-------------------------------------------------------------------------|--|

| 30 | Field                   | Offset<br>(Bytes) | Size (Bytes) | Description                                                             |  |

|    | USER_SUP_<br>CHALLENGE  | 0                 | 32           | User-supplied challenge used to obtain wrapping key from PUF            |  |

| 25 | PLATFORM_CPU_<br>CONFIG | 32                | 8            | Bit vector to identify platform and processor configurations to bind to |  |

| 35 | RSVD                    | 40                | 24           | RSVD, must be zero                                                      |  |

BTDATA

[0066] FIG. 5 illustrates an embodiment of method performed by a processor to process a WRP instruction. For example, a processor core as shown in FIG. 22(B), a pipeline as detailed, etc. performs this method. At 501, a single WRP instruction is fetched. For example, a WRP instruction is fetched. The WRP instruction includes fields for an opcode, a first destination operand which is to store an operation status of the execution of the WRP instruction, a source operand

- which is to store or encode a location (e.g., address) of an input/source BIND\_STRUCT, and a destination operand which is to store or encode a location (e.g., address) of an output/destination location. Note that in some embodiments, one or more of the BIND STRUCTS are stored in one or more registers and in some embodiments one or more of the

- 45 BIND\_STRUCTS are stored in one or more registers. In some embodiments, the WRP instruction further includes a field for a writemask. In some embodiments, the WRP instruction is fetched from an instruction cache. The opcode is to indicate that execution circuitry is to encrypt at least encrypt secret information from the input data structure with a PUF generated encryption key, bind the wrapped secret information to a target, update the input data structure, generate a MAC over the updated data structure, store the MAC in the input data structure to generate a wrapped output data

- 50 structure, store the wrapped output data structure having the encrypted secret information and an indication of the target according to the second destination operand's usage for the instruction. Additionally, the operational status of execution is stored in the identified first destination operand.

- [0067] In some embodiments, the execution circuitry is to encrypt data from the input data structure using a key generated by a PUF and store the encrypted data in an output data structure, wherein a challenge to excite the PUF is 55 found in the input data structure, and store an operation status in the identified first destination operand. In some embodiments, the encryption is performed by using the generated key and a temporary value used as an initial vector for a cryptography engine. In some embodiments, a MAC is computed using the PUF generated key over the entire

input data structure (including updates to SEQID and encrypted data) and stored in an output data structure (which is the updated input data structure). Note that in some embodiments, the entire input data structure is copied into the output data structure prior to other operations (however, some fields may be overwritten).

- [0068] In some embodiments, the fetched single instruction is translated into one or more instructions of a different instruction set architecture prior to decoding at 502. Executing of the one or more instructions of the different instruction set architecture is to be functionally equivalent as the executing according to the opcode of the single instruction

- **[0069]** The fetched single instruction (or translated instruction(s)) is/are decoded at 503. For example, the fetched WRP instruction is decoded by decode circuitry such as that detailed herein.

- [0070] Data values associated with the source operand of the decoded instruction is retrieved at 505. For example, when one or more of the source operands are memory operands, the data from the indicated memory location is retrieved. [0071] At 507, the decoded instruction (or translated instruction(s)) is/are executed by execution circuitry (hardware) such as that detailed herein. For the WRP instruction, the execution will cause execution circuitry to execute the decoded instruction according to the opcode to at least encrypt secret information from the input data structure with a PUF generated encryption key, bind the wrapped secret information to a target, update the input data structure, generate a

- <sup>15</sup> MAC over the updated data structure, store the MAC in the input data structure to generate a wrapped output data structure, store the wrapped output data structure having the encrypted secret information and an indication of the target according to the second destination operand's usage for the instructionencrypt.

[0072] In some embodiments, the execution circuitry is to encrypt data from the input data structure using a key

- generated by a PUF and store the encrypted data in the input data structure (which will be made to be the output data structure), wherein a challenge to excite the PUF is found in the input data structure, and store an operation status in the identified first destination operand. In some embodiments, the encryption is performed by using the generated key and a temporary value used as an initial vector as input to a cryptography engine. The initial vector is stored as the SEQID in the output data structure. In some embodiments, a MAC is computed using the PUF generated key over the entire data structure and is stored in the output data structure. Note that in some embodiments, the entire input data

- <sup>25</sup> structure is copied into the output data structure prior to other operations (however, some fields may be overwritten such as the SEQID, MAC, BTENCDATA).

[0073] In some embodiments, the instruction is committed or retired at 509.

30

**[0074]** FIG. 6 illustrates a method for the execution of a wrap (WRP) instruction according to the present embodiments. Note the execution may be performed by execution circuitry and/or SV-PUF circuitry. A determination of whether the SV-PUF is supported is made at 604. In some embodiments, this aspect is set in a model specific register (MSR). If it is determined that the SV-PUF is not supported, then the execution halts at 606 due to an undefined instruction. If, however, it is determined that the SV-PUF is supported, then the execution advances to 608 where it is determined

- whether the software requesting wrapping is privileged (e.g., ring-0). If it is determined that the software requesting wrapping is not privileged, then the execution exits at 610 due to a general protection fault. If, however, it is determined that the software requesting wrapping is privileged, then the execution advances to 612, where it is determined whether

- the contents of the source and destination registers are aligned. If it is determined that the contents of the source and destination registers are not aligned, then the process exits at 614 due to a general protection fault. If, however, it is determined that the contents of the source and second destination registers are aligned, then the process advances to 616, where it is determined whether the contents of the source and destination registers overlap. If it is determined that

- 40 the contents of the source and destination registers overlap, then the process exits at 618 due to a general protection fault. If, however, it is determined that the contents of the source and destination registers do not overlap, then the process advances to 620, where the input structure identified by the address information stored in the source operand (e.g., RBX) is loaded into memory. The process 602 then advances to 622.

- **[0075]** At 622, it is determined whether any reserved fields are set in the input structure identified by the address information stored in the source operand. If it is determined that there are reserved fields set in the input structure identified by the address information stored in the source operand, then the process exits at 624 due to a general protection fault. If, however, it is determined that there are no reserved fields set in the input structure identified by the address information stored in the source operand, then the process advances to 626, where a temporary seed for encryption is generated (forexample, using a hardware number generator). The process 602 then advances to 628.

- 50 [0076] At 628, it is determined whether the temporary seed has enough entropy (randomness). If it is determined that the temporary seed does not have enough entropy, then the process advances to 630 where the zero flag is set to 1, to indicate that the data was not wrapped, and the status register (e.g., RAX) is set to indicate an entropy error. If, however, it is determined that the temporary seed has enough entropy, then the process advances to 632, where the wrapping key is obtained from the PUF using the challenge stored in the BTDATA field of BIND\_STRUCT. The process 602 then advances to 634.

- **[0077]** At 634, the data from the BTENDCDATA field of the input BIND\_STRUCT is encrypted using the wrapping key and the temporary seed from the SEQID field of the input BIND\_STRUCT. The encrypted data is then written to the BTENDCDATA field of the output BIND\_STRUCT identified by address information stored in the second destination

operand (e.g., RCX).

5

**[0078]** At 636, the MAC is computed using the wrapping key over the encrypted data, and the MAC is then written to the MAC field of the output BIND\_STRUCT.

**[0079]** At 638, the target for wrapping (BTID) and the challenge (BTDATA) are copied from their respective fields in the input BIND\_STRUCT to their respective fields in the output BIND\_STRUCT.

[0080] At 640, the seed value in the output BIND\_STRUCT is populated with the generated temporary seed value.

**[0081]** At 642, the zero flag is set to 0, indicating that the data was successfully wrapped, and the destination register (e.g., RAX) is set to indicate success.

[0082] At 644, all other flags are cleared.

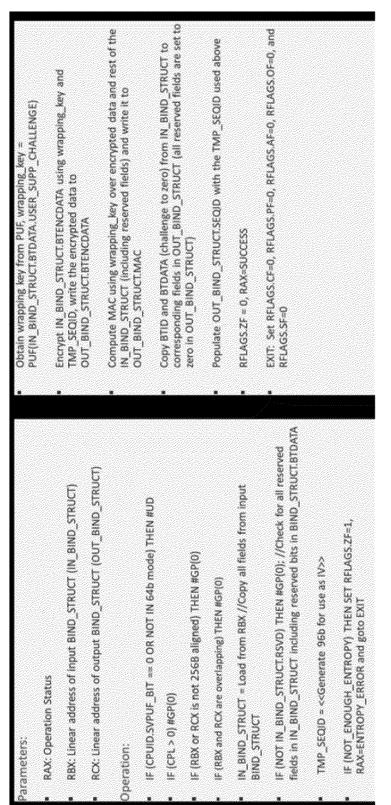

<sup>10</sup> **[0083]** FIG. 7 illustrates embodiments of pseudocode for the execution of the WRP instruction.

**[0084]** Generally, the UNWRP instruction allows for the decryption of the data contained within wrapped blobs generated by the WRP instruction. The UNWRP instruction takes the wrapped blob, unwraps the blob (confirms the MAC is correct, for example), and returns the decrypted secret. If the software passes a different unwrapping target (indicated by BTID in BIND\_STRUCT) to the UNWRP instruction, the unwrapping process will fail. Advantageously, at wrapping

<sup>15</sup> time the BTID is included as a part of the MAC. Therefore, untrusted software cannot change the BTID to use a blob for a purpose different from the one specified at wrapping time. In other words, the WRP instruction ensures the wrapped data is bound to the target.

[0085] In some embodiments, the UNWRP instruction is associated with a most-privileged protection ring (e.g., ring-0). Therefore, when the software invokes the UNWRP instruction, the SV-PUF ISA may confirm that the software has

- 20 the necessary privileges before completing the wrapping process. To invoke the UNWRP instruction, the software passes the wrapped blob that was generated using the WRP instruction, a pointer to an output buffer that will receive the unwrapped data, and the challenge to be provided to the PUF to generate the unwrapping key. The UNWRP instruction operates using BIND\_STRUCT (described above) as the input structure, which allows specification of target-specific data. [0086] The UNWRP instruction operates using BIND\_STRUCT (described below) as an input and output structure,

- <sup>25</sup> which allows specification of target-specific data. In some embodiments, the UNWRP instruction identifies three operands. A source operand is to store a location of a source (input) wrapped BIND\_STRUCT. A second destination operand is to store a location of a destination (output) unwrapped BIND\_STRUCT. A first destination operand is to store an operation status of the execution of the UNWRP instruction. The UNWRP instruction affects the following flags: ZF is cleared on a successful unwrap, and set to 1 otherwise; CF, PF, AF, OF, and SF are always cleared.

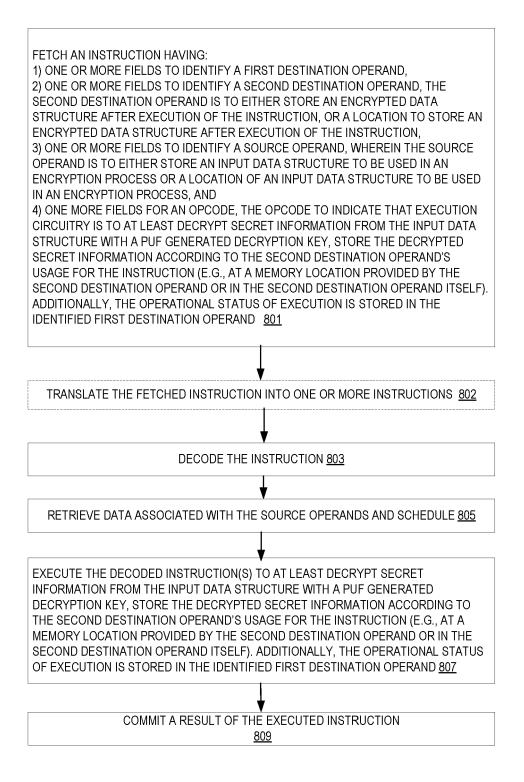

- [0087] FIG. 8 illustrates embodiments of processing an UNWRP instruction. The processing utilizes one or more of execution circuitry, PUF circuitry, encryption circuitry, and/or MAC circuitry.

[0088] At 801, a single UNWRP instruction is fetched. For example, a UNWRP instruction is fetched. The UNWRP instruction includes fields for an opcode, a first destination operand which is to store an operation status of the execution of the UNWRP instruction, a source operand which is to store or encode a location (e.g., address) of an input/source

- <sup>35</sup> BIND\_STRUCT, and a destination operand which is to store or encode a location (e.g., address) of an output/destination location. Note that in some embodiments, one or more of the BIND\_STRUCTS are stored in one or more registers and in some embodiments one or more of the BIND\_STRUCTS are stored in one or more registers. In some embodiments, the UNWRP instruction further includes a field for a writemask. In some embodiments, the UNWRP instruction is fetched from an instruction cache. The opcode is to indicate that execution circuitry is to at least decrypt secret information from

- 40 the input data structure with a puf generated decryption key, store the decrypted secret information according to the second destination operand's usage for the instruction (e.g., at a memory location provided by the second destination operand or in the second destination operand itself). additionally, the operational status of execution is stored in the identified first destination operand. Additionally, the operational status of execution is stored in the identified first destination operand.

- <sup>45</sup> **[0089]** In some embodiments, the execution circuitry is to decrypt data from the input data structure using a key generated by a PUF and store the decrypted data in the output data structure, wherein a challenge to excite the PUF is found in the input data structure, and store an operation status in the identified first destination operand. In some embodiments, the decryption is performed by providing the generated key and a sequence ID from the input data structure to a cryptography engine. In some embodiments, the input data structure is first verified using a MAC comparison. For

- 50 example, a MAC is computed by removing the MAC from the input data structure and then generating a MAC on the remaining data. The MAC of the input data structure and generated MAC are then compared to determine if any data of the wrapped blob has changed. Note that in some embodiments, the entire input data structure is copied into the output data structure prior to other operations.

- [0090] In some embodiments, the fetched single instruction is translated into one or more instructions of a different instruction set architecture prior to decoding at 802. Executing of the one or more instructions of the different instruction set architecture is to be functionally equivalent as the executing according to the opcode of the single instruction

[0091] The fetched single instruction (or translated instruction(s)) is/are decoded at 803. For example, the fetched

**[0091]** The fetched single instruction (or translated instruction(s)) is/are decoded at 803. For example, the fetched UNWRP instruction is decoded by decode circuitry such as that detailed herein.

[0092] Data values associated with the source operand of the decoded instruction is retrieved at 805. For example, when one or more of the source operands are memory operands, the data from the indicated memory location is retrieved.

[0093] At 807, the decoded instruction (or translated instruction(s)) is/are executed by execution circuitry (hardware) such as that detailed herein. For the UNWRP instruction, the execution will cause execution circuitry to execute the

- <sup>5</sup> decoded instruction according to the opcode to at least decrypt secret information from the input data structure with a puf generated decryption key, store the decrypted secret information according to the second destination operand's usage for the instruction (e.g., at a memory location provided by the second destination operand or in the second destination operand itself). additionally, the operational status of execution is stored in the identified first destination operand.

- <sup>10</sup> **[0094]** In some embodiments, the execution circuitry is to decrypt data from the input data structure using a key generated by a PUF and store the decrypted data in the output data structure, wherein a challenge to excite the PUF is found in the input data structure, and store an operation status in the identified first destination operand. In some embodiments, the decryption is performed by providing the generated key and a sequence ID from the input data structure to a cryptography engine. In some embodiments, the input data structure is first verified using a MAC comparison. For

- <sup>15</sup> example, a MAC is computed by removing the MAC from the input data structure and then generating a MAC on the remaining data. The MAC of the input data structure and generated MAC are then compared to determine if any data of the wrapped blob has changed. Note that in some embodiments, the entire input data structure is copied into the output data structure prior to other operations.

- **[0095]** In some embodiments, the instruction is committed or retired at 809.

35

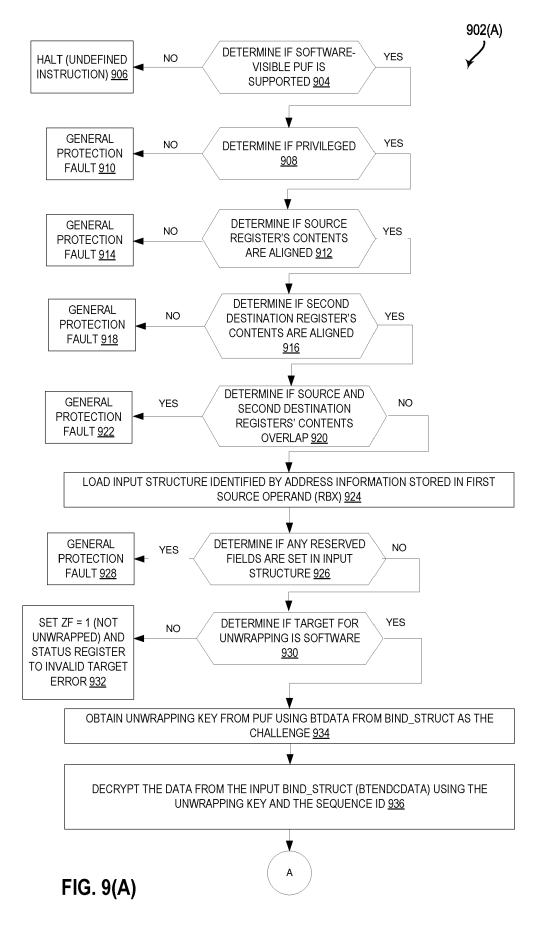

- 20 [0096] FIG. 9 illustrates a method 902 performed by a processor to execute an unwrap (UNWRP) instruction according to the present embodiments. Note that an SV-PUF circuit is also involved for the generation of the key. At 904 it is determined whether the SV-PUF is supported. In some embodiments, this aspect is set in a model specific register (MSR). If it is determined that the SV-PUF is not supported, then the process halts at 906 due to an undefined instruction. If, however, it is determined that the SV-PUF is supported, then the process advances to 908, where it is determined

- <sup>25</sup> whether the software requesting wrapping is privileged (e.g., ring-0). If it is determined that the software requesting wrapping is not privileged, then the process exits at 910 due to a general protection fault. If, however, it is determined that the software requesting wrapping is privileged, then the process advances to 912, where it is determined whether the contents of the source register are aligned. If it is determined that the contents of the source register are not aligned, then the process exits at 914 due to a general protection fault. If, however, it is determined that the contents of the source register are not aligned.

- <sup>30</sup> register are aligned, then the process advances to 916, where it is determined whether the contents of the second destination register are aligned.

**[0097]** If it is determined that the contents of the source register are not aligned, then the process exits at 918 due to a general protection fault. If, however, it is determined that the contents of the destination register are aligned, then the process advances to 920, where it is determined whether the contents of the source and second destination registers overlap.

**[0098]** If it is determined that the contents of the source and destination registers overlap, then the process exits at 922 due to a general protection fault. If, however, it is determined that the contents of the source and destination registers do not overlap, then the process advances to 924, where the input structure identified by the address information stored in the first source operand (e.g., RBX) is loaded into memory. The process 902 then advances to 926.

- <sup>40</sup> **[0099]** At 926, it is determined whether any reserved fields are set in the input structure identified by the address information stored in the first source operand. If it is determined that there are reserved fields set in the input structure identified by the address information stored in the first source operand, then the process exits at 928 due to a general protection fault. If, however, it is determined that there are no reserved fields set in the input structure identified by the address information stored in the first source operand, then the process advances to 930, where it is determined whether

- the unwrapping target (e.g., indicated by BTID in BIND\_STRUCT) is the software. If it is determined that the unwrapping target is not the software, then the process advances to 932 where the zero flag is set to 1, to indicate that the data was not unwrapped, and the status register (first destination such as RAX) is set to indicate an invalid target error. If, however, it is determined that the unwrapping target is the software, then the process advances to 934, where the unwrapping key is obtained from the PUF using the challenge stored in the BTDATA field of BIND\_STRUCT. The process 902 then advances to 936.

**[0100]** At 936, the data from the BTENDCDATA field of the input BIND\_STRUCT is decrypted using the unwrapping key and the SEQID field of the input BIND\_STRUCT. The process 902 then advances to 938.

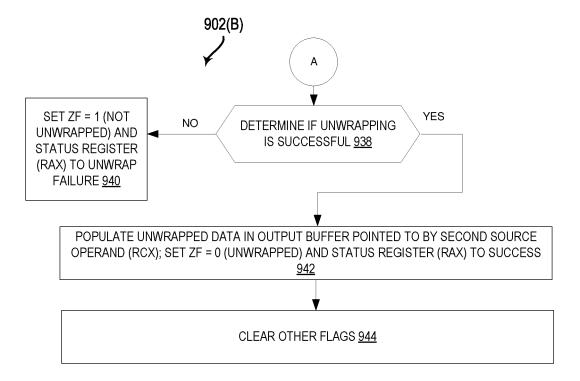

[0101] At 938, it is determined whether the unwrapping is successful. If it is determined that the unwrapping is not successful (e.g., because of a MAC mismatch), then the process advances to 940 where the zero flag is set to 1, to indicate that the data was not unwrapped, and the status register (e.g., RAX) is set to indicate an unwrap failure. If, however, it is determined that the unwrapping is successful (e.g., because of a MAC match), then the process advances to 942, where the unwrapped data is written to the output buffer identified by address information stored in the second source operand (e.g., RCX), the zero flag is set to 0, indicating that the data was successfully unwrapped, and the

destination register (e.g., RAX) is set to indicate success. The process 902 then advances to 944, where all other flags are cleared.

[0102] FIG. 10 illustrates embodiments of pseudocode for the execution of the UNWRP instruction.

5

10