### UK Patent Application (19) GB (11) 2625583

26.06.2024

2219375.9 (21) Application No:

(22) Date of Filing: 21.12.2022

(71) Applicant(s):

**Imagination Technologies Limited** (Incorporated in the United Kingdom) Imagination House, Home Park Estate, KINGS LANGLEY, Hertfordshire, WD4 8LZ, **United Kingdom**

(72) Inventor(s): Szabolcs Cséfalvay

(74) Agent and/or Address for Service:

Slingsby Partners LLP 1 Kingsway, LONDON, WC2B 6AN, United Kingdom (51) INT CL:

G06F 9/54 (2006.01)

G06F 17/14 (2006.01)

(56) Documents Cited:

US 7836116 B

US 7584342 B

(58) Field of Search:

INT CL G06F

Other: WPI, EPODOC

- (54) Title of the Invention: Performing an operation on an array of values at a processing unit Abstract Title: Performing an operation on an array of values using a plurality of threads

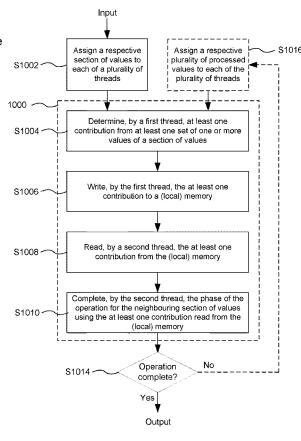

- (57) Disclosed is a computer-implemented method of performing an operation on an array of values by a processing unit. The method starts by performing a phase of the operation 1000, for each of the one-dimensional sequences of values of the array of values, assigning a respective section of values of the 1-D sequence of values to each of a plurality of threads S1002. The first thread of the plurality of threads, then determines one contribution, from the section of values assigned to the first thread S1004, to the phase of the operation that is to be completed by a second thread of the plurality of threads for a neighbouring section of values of the 1-D sequence of values, and writing the contribution to a memory \$1006. Next, the second thread reads the contribution from the memory S1008 and completes the phase of the operation for the neighbouring section of values assigned to the second thread S1010 in dependence on the contribution read from the memory in order to generate a section of processed values. The operation may be a 2-D Gaussian filter.

FIGURE 10

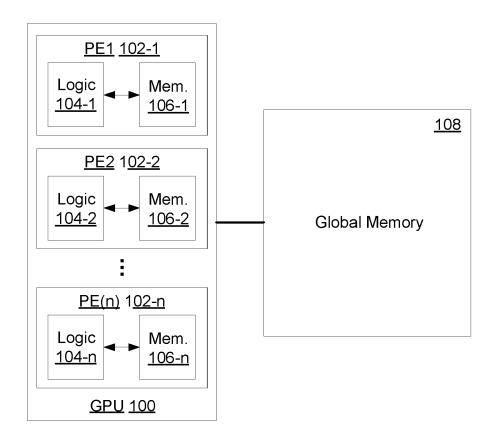

FIGURE 1A

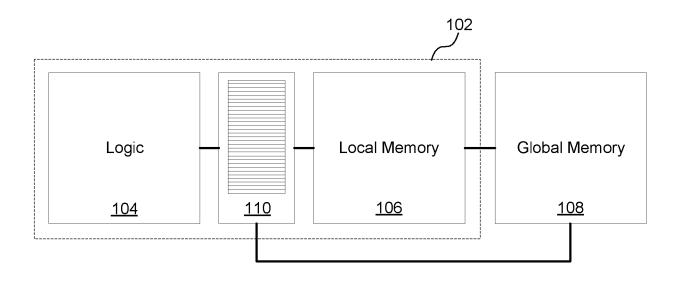

FIGURE 1B

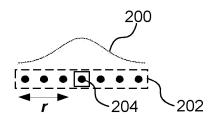

FIGURE 2

FIGURE 3

3 of 15

| T1   | Т9   | T17  | T25  |

|------|------|------|------|

| T2   | T10  | T18  | T26  |

| T3   | T11  | T19  | T27  |

| T4   | T12  | T20  | T28  |

| T5   | T13  | T21  | T29  |

| T6   | T14  | T22  | T30  |

| T7   | T15  | T23  | T31  |

| T8   | T16  | T24  | T32  |

| T33  | T41  | T49  | T57  |

| T34  | T42  | T50  | T58  |

| T35  | T43  | T51  | T59  |

| T36  | T44  | T52  | T60  |

| T37  | T45  | T53  | T61  |

| T38  | T46  | T54  | T62  |

| T39  | T47  | T55  | T63  |

| T40  | T48  | T56  | T64  |

| T65  | T73  | T81  | T89  |

| T66  | T74  | T82  | T90  |

| T67  | T75  | T83  | T91  |

| T68  | T76  | T84  | T92  |

| T69  | T77  | T85  | T93  |

| T70  | T78  | T86  | T94  |

| T71  | T79  | T87  | T95  |

| T72  | T80  | T88  | T96  |

| T97  | T105 | T113 | T121 |

| T98  | T106 | T114 | T122 |

| T99  | T107 | T115 | T123 |

| T100 | T108 | T116 | T124 |

| T101 | T109 | T117 | T125 |

| T102 | T110 | T118 | T126 |

| T103 | T111 | T119 | T127 |

| T104 | T112 | T120 | T128 |

| 1104 | 1112 | 1120 | 1120 |

400

FIGURE 5

FIGURE 6

FIGURE 7a

FIGURE 7b

FIGURE 7c

| $\infty$     |           |

|--------------|-----------|

| Ш            |           |

| $\mathbf{C}$ | 0         |

| $\supset$    | $\approx$ |

| <u>ত</u>     |           |

| 正            |           |

| <b>₽</b> 01T | ていて               | T120            | 1128            |

|--------------|-------------------|-----------------|-----------------|

| £01T         | ŀŀŀ⊥              | 6llT            | 721十            |

| Z01T         | OllT              | 811T            | 11Se            |

| IOIT         | 601⊤              | ∠レレ⊥            | 1125<br>1       |

| 001T         | 801T              | 911T            | <b>₽2</b> I⊥    |

| 66⊥          | 701T              | SIIT            | F21T            |

| 86T          | 901⊤              | <b>⊅</b>   ↓    | 7122            |

| 79T          | 901T              | EIIT            | 121丁            |

| STT          | 08T               | 88T             | 96⊥             |

| VZI          | 6 <b>/</b> 1      | <u> </u>        | 96T             |

| 0ZT          | 87T               | 98T             | <del>7</del> 6⊥ |

| 69⊥          | 221               | 98⊥             | £6T             |

| 89T          | 977               | <i>1</i> ∕8T    | Z6T             |

| Z9T          | 9ZT               | £8T             | l6T             |

| 99 <b>T</b>  | ₽ZI               | <u>28</u> T     | 06L             |

| <b>9</b> 9⊥  | £ζŢ               | <b>18</b> Τ     | 68⊥             |

| 0⊅⊥          | 84T               | 99⊥             | <b>≯</b> 9⊥     |

| 6ET          | 747               | 99L             | £9T             |

| 8£T          | 9 <del>1</del> 71 | <del>7</del> 9⊥ | Z9T             |

| 7.E.T        | S <del>1</del> 1  | £9T             | 19 <b>T</b>     |

| 9ET          | <del>bb</del> 1   | Z9T             | 09L             |

| GET          | £ <del>1</del> 1  | lθT             | 69T             |

| 134<br>T34   | <u> 2</u> 41      | 09L             | 85T             |

| EET          | Γ <del>Þ</del> Τ  | 6 <b>7</b> L    | <u> </u>        |

| 8T           | 91⊥               | <b>≯</b> Z⊥     | T32             |

| <u> </u>     | 91T               | EZT             | ۲ST             |

| 9 <b>T</b>   | ⊅↓⊥               | 727             | 0£T             |

| SΤ           | ειΤ               | ΓZ1             | 42T             |

| Þ⊥           | ζŀΤ               | T20             | 82T             |

| £Τ           | ΙΙL               | 6∤⊥             | 727             |

| ΣŢ           | 0[1               | 81T             | T26             |

| lΤ           | 6L                | <b>∠\</b> ⊥     | 725             |

FIGURE 10

FIGURE 11

106

|    |              |            |            |            |    |          | Γ          |          |     |      |          |

|----|--------------|------------|------------|------------|----|----------|------------|----------|-----|------|----------|

| 16 | 12           | <b>P</b> 8 | 74         | д<br>8     | 16 | <u>С</u> | 18         | <u>Б</u> |     | T128 | 82       |

| 15 | 12           | Ь7         | 74         | Р7         | 91 | P7       | 18         | Ъ7       |     | 1128 | Р7       |

| 14 | 12           | P6         | 74         | P6         | 91 | P6       | 18         | 9d       |     | 1128 | P6       |

| 13 | T2           | P5         | 74         | P5         | 16 | ಕ್ಷ      | 18         | P5       |     | T128 | P5       |

| 12 | T2           | ď.         | 74         | <b>7</b>   | T6 | ğ        | T8         | ф.<br>7  |     | T128 | ъд.      |

| 11 | 12           | 23         | 14         | P3         | 91 | 23       | 18         | E3       |     | T128 | 23       |

| 10 | 12           | P2         | 74         | 2          | 16 | P2       | <u>T8</u>  | 2        |     | T128 | <u>7</u> |

| 6  | 12           | ₫.         | 74         | ģ.         | 91 | ₫.       | 18         | ğ        |     | T128 | ğ        |

| œ  | 1            | P8         | 13         | P8         | 51 | g.<br>80 | 11         | P8       | *** | T127 | P8       |

| 7  | <u>-</u>     | Ъ7         | T3         | Ld         | 51 | Ъ4       | <i>£</i> 1 | Źd       |     | T127 | Ъ2       |

| 9  | <del>-</del> | P6         | T3         | P6         | 15 | P6       | 17         | 9d       |     | T127 | P6       |

| 5  | T1           | P5         | T3         | P5         | TS | ದ್ದ      | <u> </u>   | P5       |     | T127 | P5       |

| 4  | 11           | ₽.         | <b>1</b> 3 | <b>P</b> 4 | 75 | g.       | 11         | P4       |     | T127 | ď        |

| က  | <del>-</del> | <u>5</u>   | T3         | P3         | 15 | £        | 11         | БЗ       |     | 1127 | ЪЗ       |

| 7  | -            | P2         | <u>T3</u>  | 2          | 15 | P2       | 4          | 2        |     | 1127 | P2       |

|    | 11           | <u>7</u>   | T3         | ᄑ          | T5 | Ţ        | 17         | <u>7</u> |     | T127 | <u>7</u> |

# **FIGURE 12A**

| generate | *****       | *****      |              | *****    | *****        | ****       | **** | *****    | ****       | *****      | ***** | ***** | annana.    |

|----------|-------------|------------|--------------|----------|--------------|------------|------|----------|------------|------------|-------|-------|------------|

| 16       | 78          | ã          | 18           | ğ.       | <u>1</u> 8   | g.         | 8    | &<br>C.  | 718        | ã          |       | 1128  | œ          |

| 15       | 17          | 2          | 21           | <u>7</u> | 2            | 9 <u>6</u> | 17   | д<br>80  | 115        | P2         |       | T127  | <u>۾</u>   |

| 14       | 16          | P2         | T6           | 75       | T6           | 9<br>0     | T6   | 8        | 114        | <b>P</b> 2 |       | T126  | <u>ი</u>   |

| 13       | TS          | <b>P</b> 2 | 15           | ъф.      | 15           | 9<br>0     | 75   | 8        | 713        | P2         |       | T125  | Д<br>8     |

| 12       | 4           | 22         | 14           | <u>7</u> | 74           | P6         | 7.4  | 8        | T12        | P2         |       | 1124  | 80         |

| 7.       | 13          | 2          | E            | 72       | £3           | 9<br>0     | E    | 8        | 17.7       | 2          |       | 7123  | 82         |

| 10       | 12          | P2         | 12           | P4       | 72           | 9<br>9     | 12   | 82       | 110        | P2         |       | 1122  | 9<br>8     |

| 6        | <del></del> | ã          | <del> </del> | ф.       | <del> </del> | 9d         | 77   | œ<br>60  | <u>1</u>   | 2          |       | T121  | <u>0</u>   |

| ဆ        | T8          | <u>~</u>   | 138          | £        | 18           | 2          | T8   | ă        | 716        | Ď.         | :001  | 7128  | b2         |

| 7        | 11          | <u>7.</u>  | 4            | P3       | 7            | <b>P</b> 5 | 1    | P.7      | 115        | ă          |       | T127  | <u>1</u>   |

| 9        | T6          | ă.         | T6           | ೭        | 16           | 8          | T6   | <u>p</u> | 714        | ğ          |       | T126  | Ь7         |

| 2        | 13          | ŗ.         | TS           | E.       | 13           | P5         | TS   | P.7      | T13        | <u>o</u>   |       | T125  | 5          |

| 4        | 7.4         | <u>v</u>   | 74           | £        | 74           | 5          | 74   | à        | 112        | ă          |       | T124  | P.7        |

| 3        | 13          | ă          | 13           | 2        | 13           | g.         | T3   | <u>p</u> | 713        | ă          |       | 1123  | р <u>т</u> |

| 2        | 12          | ă          | 12           | <u>g</u> | 12           | P.5        | 12   | P.7      | T10        | ž          |       | T122  | P7         |

| 7        | <b></b>     | 2          | ļ            | a        | <b>}</b>     | P5         | ļ    | P7       | <u>T</u> 3 | ğ.         |       | T121  | 72         |

# FIGURE 12B

FIGURE 13

FIGURE 14

| ,          | ,              |              |    |          | ,  |             | ····· |          | ,        |            | ·   |          |     |            | ,   |          |     |            | ,          |          |     | ·    |          |

|------------|----------------|--------------|----|----------|----|-------------|-------|----------|----------|------------|-----|----------|-----|------------|-----|----------|-----|------------|------------|----------|-----|------|----------|

| 16         | <b>T</b> 2     | Ь2           | 14 | PS       | T6 | <b>6</b>    | 13    | ģ.       | <u>T</u> | <b>9</b> 8 | 111 | P6       | 113 | ъ <u>ф</u> | 715 | P2       | ×   |            | <b>₹18</b> | Ъ2       |     | ×    |          |

| 'n         | 7.2            | <del>р</del> | 74 | P4       | T6 | P2          | ×     |          | <u>5</u> | <u>6</u>   | 111 | P5       | T13 | 23         | 7.5 | 2        | T16 | о<br>89    | T18        | 9<br>0   |     | T128 | 9<br>8   |

| 4          | 12             | P5           | 14 | P3       | 16 | 2           | 17    | <u>Б</u> | 13       | P6         | 111 | P4       | T13 | P2         | ×   |          | 716 | Ь7         | T18        | PS       |     | T128 | р7       |

| ç          | 12             | P4           | 74 | P2       | ×  | •••••       | 11    | 2d       | 13       | g.         | 113 | P3       | T13 | ž          | T14 | D8       | 118 | 9<br>0     | 718        | P4       |     | T128 | <u>6</u> |

| <b>2</b> 2 | 12             | D3           | 74 | ā        | 75 | P8          | 1     | 9d       | 6        | <u>ā</u>   | 111 | 2        | ×   | *****      | T14 | b7       | T16 | PS         | T18        | ъз.      |     | T128 | P5       |

| Ат.<br>Ат. | 12             | 23           | ×  | •••••    | 13 | P7          | 11    | D        | 13       | <u>ج</u>   | 131 | <u>7</u> | 112 | 98<br>8    | 114 | 9<br>6   | 716 | <b>P</b> 4 | 118        | 22       |     | T128 | ъд.      |

| 0          | 12             | Ę.           | T3 | ъ<br>8   | 13 | P6          | 17    | <u>7</u> | 13       | <u>م</u>   | ×   |          | T12 | <u>p</u>   | T14 | P5       | 7.6 | ಬ್         | T18        | Ę.       |     | T128 | <u>6</u> |

| ø          | ×              |              | 13 | b2       | 15 | <b>D</b> 2  | 11    | 8        | 13       | 2          | 110 | 8        | 112 | က္ဆ        | T14 | <u>q</u> | 120 | 22         | ×          |          |     | T128 | 2        |

| 60         | 11             | P8           | 13 | P6       | 15 | P4          | 1     | 2        | ×        |            | T10 | P7       | T12 | PS         | T14 | ದ್       | T16 | ã          | 117        | <b>D</b> | ŸEA | T128 | ģ.       |

| ~          | 13             | Ъ7           | T3 | g<br>IS  | 15 | 23          | 11    | Ž.       | T8       | ۵.<br>8    | 710 | P6       | T12 | ğ          | 114 | 2        | ×   |            | 117        | р.<br>Д  |     | ×    |          |

| Ø          | 11             | P6           | T3 | D.A.     | 15 | P2          | ×     |          | 18       | <u>7</u> d | 110 | ದ್       | 112 | ಕ್ಷ        | 114 | ā        | 7.5 | 8          | 117        | P6       |     | 1127 | ф<br>С   |

| ĸ          | 11             | g.           | 13 | 23       | 75 | <u>~</u>    | 16    | 8        | 18       | ದ್ದಿ       | T10 | g.<br>24 | 112 | 2          | ×   | •••••    | 113 | b2         | 117        | 75       |     | T127 | ď        |

| 4          | <del> </del> - | g.<br>24     | T3 | <b>5</b> | ×  |             | T6    | ď        | 18       | ŭ.         | 110 | ದ್ದ      | 132 | ă          | 113 | 80       | 7.5 | 9<br>0     | 117        | g.<br>2  |     | 1127 | Д<br>9   |

| e)         | 1,             | P3           | T3 | 2        | 44 | 9<br>8<br>8 | 76    | - DG     | 138      | 24         | 110 | P2       | ×   |            | 113 | 2        | £   | ಕ್ಕ        | 117        | <u>و</u> |     | T127 | D.       |

| N          | Į.             | P2           | ×  |          | 74 | P7          | T6    | g<br>S   | 18       | ೮          | 110 | ğ        |     | 9<br>8     | T13 | 9d       | 7.5 | ă.         | 117        | 22       |     | T127 | ď.       |

| <b>/</b>   | 11             | ğ            | 12 | 82       | T4 | ည်          | T6    | g<br>2   | T8       | 2          | ×   |          | 131 | <u>7</u>   | T13 | g.       | 115 | L          | 117        | ₽.       |     | T127 | 2        |

**FIGURE 15A**

### 12 of 15

|            |              |          |           |            |           |          | ۲          |                | ·····     |            |            |            |            |            | ۲   |          |            |          |    |   |      |            |

|------------|--------------|----------|-----------|------------|-----------|----------|------------|----------------|-----------|------------|------------|------------|------------|------------|-----|----------|------------|----------|----|---|------|------------|

| 16         | 72           | <u>Б</u> | 74        | P7         | T6        | P6       | 80         | PS             | 110       | P4         | T12        | <u>p</u>   | 114        | P2         | T16 | 2        | 117        | 82       |    |   | ×    |            |

| ñ          | 72           | Ъ        | 74        | 9<br>9     | <u>1</u>  | <b>P</b> | <u>T</u> 8 | <b>Q</b>       | T10       | 23         | T12        | 2          | T14        | ă          | T15 | 82       | 117        | Р7       |    |   | T128 | <u>8</u>   |

| 14         | 72           | P6       | 14        | £          | TG        | Q.       | <u></u>    | £              | T10       | P2         | T12        | ă          | T13        | 9<br>8     | T15 | P.7      | 117        | P6       |    |   | T128 | Ъ7         |

| 5          | 12           | ದ್ದ      | 14        | P4         | <u>16</u> | 23       | 138        | P2             | T10       | ₹.         | T11        | P8         | 133        | þ7         | 713 | 9d       | 117        | P5       |    |   | T128 | P6         |

| 12         | T2           | ã        | 74        | P3         | T6        | 22       | 18         | 2              | <u>T3</u> | 80         | <b>T11</b> | <u>7</u> d | <b>T13</b> | 9 <u>d</u> | T15 | <b>B</b> | 117        | P.       |    |   | 1128 | P5         |

| d<br>d     | 22           | g.       | 74        | 22         | <u>16</u> | 7        | <u></u>    | 82             | £         | <u>2</u>   |            | 9<br>9     | T13        | P5         | 115 | ъд<br>Ф  | 117        | ೭        |    |   | T128 | <b>P</b>   |

| 30<br>20   | 12           | 22       | 74        | ã.         | 13        | 80.      | 17         | 2              | 13        | 9 <u>c</u> | 111        | 5          | 733        | ã.         | T15 | ã        | 117        | 2        |    |   | T128 | E          |

| on.        | 12           | ₫.       | 73        | <u>С</u>   | TS        | <u>6</u> | 17         | P6             | <u>T9</u> | 2          | T11        | <b>P</b> 4 | T13        | g.         | T15 | 22       | 117        | ŗ.       |    |   | T128 | P2         |

| <b>~</b>   | -            | 8        | T3        | <u>7</u> d | 73        | 9<br>9   | 17         | 75             | <u></u>   | <u>a</u>   | 111        | 2          | T13        | 2          | 115 | ž        | ×          |          | ** | • | T128 | <u>o</u> . |

| <b>!</b> ~ | <u>-</u>     | Ъ,       | <u>T3</u> | 9 <u>6</u> | TS        | P5       | 17         | D4             | T9        | 8          | Lii        | P2         | T13        | <u>5</u>   | ×   |          | T.16       | <b>9</b> |    |   | T127 | 8          |

| ယ          | F-           | 9<br>9   | 73        | £          | 15        | ď.       | 17         | £              | 13        | 2          | 111        | ā          | ×          | •••••      | 114 | а<br>8   | 116        | Ъ        |    |   | T127 | Ъ          |

| ယ          | 1            | P        | 13        | 7<br>7     | T5        | 2        | 77         | 22             | T9        | ă          | ×          |            | T12        | 80         | T14 | p7       | T16        | P6       |    |   | 1127 | P6         |

| খ          | 7            | ሿ        | 13        | ಬ್         | 75        | S.       | 21         | 2              | ×         |            | 110        | 8          | 112        | P.7        | 114 | 9<br>9   | <b>116</b> | P5       |    |   | T127 | 75<br>25   |

| က          | F            | <u>B</u> | ೭         | P2         | 13        | Ž.       | ×          |                | <u>T8</u> | 8<br>8     | T10        | P7         | T12        | P6         | T14 | ğ        | T16        | Ž        |    |   | T127 | ₽          |

| 7          | <u>-</u>     | P2       | 73        | £          | ×         |          | <u>T6</u>  | <u>п</u><br>80 | T8        | 2          | T10        | 8          | 112        | 25         | 114 | 4        | 116        | 23       |    |   | T127 | £3         |

| ****       | <del>-</del> | Ţ        | ×         |            | 7.4       | 82       | <u>T</u>   | Ъ2             | T8        | 9          | 110        | P5         | 112        | 2          | T14 | 23       | 716        | 2        |    |   | 1127 | P2         |

## FIGURE 15B

### **-IGURE 15**0

| ,      | ,            |             |                                        | ,        |            |            |          |            | ,                |          | ,              |          | ,   |          | ,       |                |          |            |      |             |     |            | ,          |                          | ,           |          |     | ,      |     | ,          | ·   |          | ·   |                | ,     | ·          |

|--------|--------------|-------------|----------------------------------------|----------|------------|------------|----------|------------|------------------|----------|----------------|----------|-----|----------|---------|----------------|----------|------------|------|-------------|-----|------------|------------|--------------------------|-------------|----------|-----|--------|-----|------------|-----|----------|-----|----------------|-------|------------|

| 38     | 12           | 98<br>8     | 7                                      | 80<br>80 | <u>1</u> 9 | Įd         | <u>8</u> | 74         | T10              | g.<br>G  | 112            | 9<br>9   | 17  | Š        | T16     | క్షిద          | T18      | ğ          | T20  | т<br>Д      | T22 | £          | <b>T24</b> | a                        | <b>T</b> 26 | g<br>2   | T28 | 2      | 130 | <u>a</u> . | T32 | ά        | T33 | ස              |       | ×          |

| ž.     | Ŋ            | Ъ7          | 7                                      | Ъ7       | 16         | යි         | æ        | 9<br>9     | 710              | g.       | 112            | P5       | 114 | <u>4</u> | 7.50    | <b>1</b> 2     | ۳.<br>30 | 8          | 120  | ದ್ದ         | 122 | 2          | 124        | 22                       | 126         | ã.       | 128 | ŭ      | 129 | РВ         | 131 | g.<br>80 | T33 | ρğ             |       | T128       |

| 14     | 12           | ьв          | 7                                      | 9d       | 9          | D          | <u></u>  | ದ್ವ        | 7.<br>0.<br>1.0. | ğ        | 712            | ď.       | 114 | E        | 716     | ೭              | T18      | 8          | T20  | ಜ           | T22 | ž          | 124        | ğ                        | 125         | ص<br>80  | 127 | С<br>8 | 129 | Ъ7         | T31 | ь2       | 133 | 9<br>9         |       | 1128<br>P7 |

| 13     | 72           | PS          | 74                                     | P5       | 3          | Žď.        | 82       | g.         | 110              | £        | 112            | P3       | 114 | ã        | ₩<br>16 | 2              | <br>8    | ž          | 120  | <u></u>     | 121 | 80         | 123        | <br>20<br>20<br>30<br>30 | 125         | Ъ2       | 127 | Ъ2     | 129 | ЬВ         | 131 | <br>9d.  | 133 | بر<br>و        |       | T128       |

| 42     | 12           | ğ.          | 7                                      | g.       | 91         | 23         | 82       | 8          | 1.0              | ã        | 112            | 2        | 7.7 | ã.       | 716     | ğ.             | 117      | 80         | 119  | 80          | 121 | <u>5</u>   | 123        | Ľď                       | 125         | g<br>9   | 127 | ထို    | 129 | g<br>S     | 131 | బ్       | 133 | ã.             |       | 7128<br>P5 |

| #<br># | 12           | 23          | ###################################### | £        | <u>L</u>   | 22         | <u>χ</u> | <b>5</b> 2 | 110              | ã        | 112            | ŭ        | 113 | 80       | £       | <u>с</u>       | 111      | <u>6</u>   | 119  | <u>5</u>    | 121 | 9          | 123        | <u>Б</u>                 | 125         | £        | 127 | ಜ್ಞ    | 129 | p4         | 131 | 24       | 133 | 23             |       | T128       |

| 10     | 12           | 22          | ₩.<br>4                                | ã        | 38         | ũ          | 8        | ž          | <u>13</u>        | 82       | =              | 80       | 113 | ă        | 715     | ā              | 147      | විය        | 713  | 9d          | 121 | ದ್ದ        | 123        | g<br>ಬ                   | 725         | ğ        | 127 | ₫      | 129 | ь3         | T31 | ಜ್ಞ      | T33 | 22             |       | 7128<br>P3 |

| ආ      | 12           | ğ           | 77                                     | <u>ç</u> | 5          | С<br>Ж     | 13       | 80         | <u> </u>         | ь<br>Б   | }<br>\$<br>\$  | P7       | 113 | 9d       | 72      | 9d<br>9d       | 117      | ದ್         | 119  | 8           | 121 | <u>4</u>   | 123        | <u>P</u>                 | T25         | <u>E</u> | 127 | ည      | 129 | P2         | 131 | ಜ        | 133 | ã              |       | T128       |

| 80     | <u>-</u>     | 9<br>8<br>8 | T3                                     | 8d       | 5          | ₽2         | 2        | <u>24</u>  | <u>5</u>         | å        | 111            | 9<br>d.  | T13 | g.       | 733     | <u>г</u>       | T17      | <u>g</u>   | T13  | ъд.         | Ę   | ä          | T23        | E                        | T25         | 2        | T27 | ಜ      | T29 | <u>g</u>   | T31 | ₹        | ×   | ••••           | . ••• | T128       |

| 7      | <del>-</del> | р7          | 2                                      | Ъ7       | T2         | ъ<br>В     | <u></u>  | <br>9<br>4 | <u> 13</u>       |          |                | ಕ        | 113 | ã        | 115     | ã              | 117      | <u></u>    | 119  | 23          | 123 | 22         | 123        | 22                       | 125         | <u>g</u> | 127 | ă      | ×   |            | 130 | <br>8    | 132 | <u>т</u><br>82 |       | 7727<br>P8 |

| G      | <u></u>      | 9d          | E                                      | G        | 75         | g.         | 17       | g.         | <u>13</u>        | <u>v</u> | 111            | <u>g</u> | 113 | ã        | 775     | ద్ద            | 117      | ã          | T18  | 2<br>2<br>2 | 121 | ă          | 123        | ã                        | ×           |          | 126 | 80     | 128 | g.<br>&    | 130 | ä        | T32 | à              |       | T127       |

| \$     | <b>}</b>     | p5          | <u></u>                                | PS       | 55         | ъ <u>т</u> | 13       | ă          | 2                | e<br>E   | 7.             | E<br>E   | 113 | 2        | 115     | 2<br>2         | 117      | ã          | 119  | ŭ           | ×   |            | 122        | <u>с</u>                 | 124         | д.<br>89 | 126 | ρģ     | 128 | p3         | 130 | က္       | 132 | <br>80         |       | 7127<br>P6 |

| *4     | ķ            | ğ.          | Œ                                      | đ        | 32         | g.         | ££       | £          | <u> </u>         | ď        | <del>***</del> | 2        | 113 | ã        | T 55    | <u>v</u>       | ×        |            | 7.18 | Д<br>8      | 120 | œ<br>6     | 122        | à                        | 124         | <br>2d   | 126 | g.     | 128 | 9d         | 130 | ದ್ದ      | 132 | Š.             |       | 7127<br>P5 |

| 8      | <del></del>  | ಜ್ಞ         | T3                                     | 23       | 13         | 22         | 13       | D2         | 25               | <u>g</u> | 14.            | ž        | ×   |          | T14     | 80<br>20<br>20 | T.16     | <u>с</u>   | T:18 | P3          | T20 | <i>b</i> 3 | 122        | 9<br>9                   | 124         | က္ဆ      | T26 | PS     | T28 | D<br>S     | T30 | ğ        | T32 | ğ              |       | T127       |

| ~      | <del> </del> | P2          | m                                      | 2        | ಸ್ತ        | ā          | 1        | ā          | ×                | 77777    | 110            | ф<br>80  | 112 | 80       | 7.74    | <u>2</u>       | 716      | ă          | T18  | 9<br>0      | T20 | 9<br>6     | T22        | ದ್ದಿ                     | T24         | ಜ್ಞ      | T26 | ğ      | 128 | 74         | T30 | £        | T32 | ద              |       | T127<br>P3 |

| d      | Ξ.           | ā           | ೭                                      | ŭ        | ×          |            | Ē        | 8          | <u> </u>         | 80       | 730            | Ь7       | 112 | ă        | 734     | 9<br>d.        | 716      | 9 <u>d</u> | 738  | ట్          | T20 | g<br>ಟ     | 122        | ğ                        | T24         | ğ        | T26 | £      | T28 | g          | T30 | P2       | T32 | 2              |       | T123       |

|                | ,        |    |          |          | ,         |              |       |          | ,            |          |             |          | ,        |              | ,             |                |              |          |       |                                         |      |          |

|----------------|----------|----|----------|----------|-----------|--------------|-------|----------|--------------|----------|-------------|----------|----------|--------------|---------------|----------------|--------------|----------|-------|-----------------------------------------|------|----------|

| <del>1</del> 6 | <u></u>  | P2 | 1        | 4        | <u>16</u> | P6           | 5     | <u>0</u> | 112          | P2       | ₩<br>₩<br>₩ | <u>4</u> | T10      | <del>р</del> | <u>6</u>      | <u>0</u>       | <b>T24</b>   | ã        |       |                                         | ×    |          |

| £              | 2        | 22 | 10       | <u>a</u> | 75        | <br>90<br>0. | 7     | 82       | }<br>4<br>*  | 2        | 110         | ã        | 13       | <u>a</u>     | 138           | 6              | 123          | ğ        |       |                                         | 1128 | 82       |

| 7              | 3        | ğ  | £        | ₫.       | 7         | 9<br>9       | ೭     | 80       | T10          | 22       | <u>B</u>    | g.       | 716      | ಕ್ಷ          | T15           | ğ              | 122          | <u>v</u> |       | *************************************** | 1127 | 80       |

| <u> </u>       | ಜ        | 2  | F.       | \$       | Ω         | Pg           | 72    | 80       | <u>m</u>     | P2       | 736         | 2        | 135      | స్ట          | # 14<br>44    | Ъ2             | Ž            | ã        |       | *************************************** | 1126 | 82       |

| 42             | 7        | 22 | 2        | <u>g</u> | 72        | 9 <u>d</u>   | ;     | 80       | 116          | 2        | 7.13        | 23       | 114      | ద్ద          | 713           | <u>7</u> d     | 120          | ğ        |       | £                                       | 1125 | 80       |

| ж<br>4         | ೭        | 2  | C        | <u>4</u> | <b>}</b>  | 9 <u>0</u>   | 8     | Zd.      | <u>الم</u>   | ã        | 7.4         | ద        | 713      | 22           | 112           | à              | 119          | g.       |       |                                         | 124  | 80       |

| 40             | 12       | 23 | ļ        | <u>Q</u> | <u></u>   | g<br>S       | 17    | P.7      | 114          | ã        | 13          | ಜ        | 112      | g<br>in      | ***           | 2              | 118          | <u>o</u> |       |                                         | 1123 | 80       |

| တ              | *<br>    | 2  | 80       | ద        | 2         | 75           | 16    | 22       | 733          | 2        | 42          | 23       | <u>,</u> | ట్ట          | 110           | ă              | 7            | ğ        |       |                                         | 1322 | 80       |

| ထ              | <u></u>  | 2  | 2        | ದ್       | <u>16</u> | g<br>S       | 5     | à        | ゴン           | <u>o</u> | <del></del> | ñ        | T10      | g.           | 62            | 77             | ×            |          | 191   |                                         | Ž.   | 8        |

| 7              | 1        | ã  | 9        | g.       | 72        | g.           | 74    | Zd.      | }<br>\$<br>* | ã        | 710         | ã        | <u>5</u> | ğ            | ×             |                | T16          | g.<br>80 |       |                                         | - C  | <u>7</u> |

| 9              | 6        | ã  | 2        | ಜ        | 7         | ద్ద          | 13    | 2        | 110          | ă        | <u>B</u>    | 2        | ×        |              | 116           | ထို            | 7,52         | 80       |       | *************************************** | 1127 | ã        |

| ın             | 유        | ā  | F        | ద        | 73        | ದ್ದ          | T2    | 2        | T.9          | 2        | ×           |          | 7.6      | ã            | <u>ا</u><br>ت | g<br>9         | F<br>4       | 80       |       | *************************************** | 1126 | à        |

| **             | Z        | 2  | 2        | g.       | 2         | ಜ್ಞ          | ;<br> | à        | ×            |          | 716         | ã        | 115      | ğ            | #             | g<br>S         | 113          | 82       |       |                                         | 1125 | à        |

| w              | ೯        | ž  | 2        | ೮        | <u>}</u>  | ಜ್ಞ          | ×     |          | 20           | <u>ф</u> | 7.5         | 2        | 114      | <u>a</u>     | 73            | က္ဆ            | 112          | g<br>8   |       |                                         | 1124 | 2        |

| ~              | 72       | ã  | <u>-</u> | ೭        | ×         |              | 82    | 8        | 11           | g.<br>89 | 114         | 2        | 733      | g.           | 112           | င္ထ            | <del> </del> | 8<br>8   |       |                                         | 1123 | 7d       |

| 4m             | <b>*</b> | ā  | ×        |          | 80        | p4           | 11    | D<br>0   | 91           | ъ<br>В   | £           | 2        | 712      | ğ            | }<br>4<br>4   | <del>D</del> 6 | 110          | <u>Б</u> |       |                                         | 1122 | <u>5</u> |

| <br>1          |          |    |          |          |           |              | ••••• |          |              |          |             |          |          |              | ******        |                | •••••        |          | ••••• |                                         |      |          |

FIGURE 15D

FIGURE 16

FIGURE 17

### PERFORMING AN OPERATION ON AN ARRAY OF VALUES AT A PROCESSING UNIT

**FIELD**

15

20

25

30

35

**[0001]** The present disclosure is directed to performing an operation on an array of values at a processing unit.

### **BACKGROUND**

**[0002]** Figure 1A shows an example graphics processing unit (GPU) 100 and global memory 108. Work to be performed by a GPU can be arranged into "workgroups", "warps" and "threads". A workgroup may comprise one or more warps. A warp may comprise a plurality of threads, where that plurality of threads can be processed in parallel at a single core 102 of the GPU 100.

**[0003]** GPU 100 can perform operations on arrays of values. Figure 2 shows an example operation. In Figure 2, the operation is a one-dimensional Gaussian filter operation, in which a value 204 is filtered in dependence on a one-dimensional kernel 202 of values including the value 204 to be filtered and three values on either side of that value 204. A filtered output for the value 204 is determined by performing a weighted sum of the values in the kernel 202. The respective weight for each value in the kernel 202 is determined in dependence on a Gaussian function 200 centred on the value 204 to be filtered.

**[0004]** A separable two-dimensional Gaussian filter operation can be implemented by performing an initial phase in which a one-dimensional Gaussian filter operation is performed horizontally across each row of a two-dimensional array of values, followed by performing a subsequent phase in which the same one-dimensional Gaussian filter operation is performed vertically along each column of the horizontally filtered two-dimensional array of values – or vice versa (i.e. vertically, followed by horizontally).

[0005] In a simple approach, a phase of a separable two-dimensional Gaussian filter operation can be performed on an array of values by assigning each value of the array of values to be filtered to a thread for processing. As an illustrative example, consider a separable two-dimensional Gaussian filter operation to be performed on a two-dimensional array of values comprising 1024 values (e.g. arranged as a 32x32 array of values). In this example, in order to perform the initial (e.g. horizontal) phase of said operation, each of said 1024 values could be assigned to a respective one of 1024 threads. In order to filter each value, each thread can read all of the values included in the one-dimensional filter kernel used to filter that value (e.g. the value to be filtered and the three values on either side of that value) from global memory 108. Each thread can then generate a filtered value for its value by performing a weighted sum of the values in the kernel, and write that filtered value back to global memory 108, such that the global memory 108 stores a once-filtered (e.g. horizontally filtered) value for each value of the two-dimensional array of values. In order to perform the subsequent (e.g. vertical) phase of said operation, each of said 1024 once-filtered values could be

assigned to a respective one of 1024 threads. In order to further filter each once-filtered value, each thread can read all of the once-filtered values included in the one-dimensional filter kernel used to further filter that once-filtered value (e.g. the once-filtered value to be further filtered and the three once-filtered values on either side of that value) from global memory 108. The one-dimensional filter kernels used in the subsequent (e.g. vertical) phase are perpendicular to the one-dimensional filter kernels used in the initial (e.g. horizontal) phase. Each thread can then generate a further filtered value for its once-filtered value by performing a weighted sum of the once-filtered values in the kernel, and write that further filtered value back to global memory 108, such that the global memory 108 stores a further filtered (e.g. horizontally and vertically filtered) value for each value of the two-dimensional array of values.

**[0006]** Performing a separable two-dimensional Gaussian filter operation on a graphics processing unit 100 in this way is relatively slow, as it involves performing two sets of reads and two sets of writes to global memory 108. Further, in each phase of the separable filter operation, each value is read from memory many times (e.g. seven times in the example given above). This is because, in each phase, each value is read from memory (e.g. global memory 108) by the thread that is assigned to filter that value, and also read from memory (e.g. a cache memory into which it is written after being read from global memory 108) by each of the threads that are assigned to filter other values using a filter kernel that includes that value.

### SUMMARY

10

15

20

25

35

**[0007]** This Summary is provided to introduce a selection of concepts in a simplified form that are further described below in the Detailed Description. This Summary is not intended to identify key features or essential features of the claimed subject matter, nor is it intended to be used to limit the scope of the claimed subject matter.

**[0008]** According to a first aspect of the present invention there is provided a computer-implemented method of performing an operation on an array of values at a processing unit, the method comprising: so as to perform a phase of the operation: for each of one or more one-dimensional sequences of values of the array of values: assigning a respective section of values of the one-dimensional sequence of values to each of a plurality of threads; and a first thread of the plurality of threads: determining at least one contribution, from the section of values assigned to the first thread, to the phase of the operation that is to be completed by a second thread of the plurality of threads for a neighbouring section of values of the one-dimensional sequence of values; and writing the at least one contribution to a memory; and the second thread of the plurality of threads: reading the at least one contribution from the memory; and completing the phase of the operation for the neighbouring section of values assigned to the second thread in dependence on the at least one contribution read from the memory in order to generate a section of processed values.

**[0009]** The first thread of the plurality of threads may perform at least one part of the phase of the operation on at least one set of one or more values of the section of values assigned to the first thread in order to determine the at least one contribution, from said at least one set of one or more

values, to the phase of the operation that is to be completed by the second thread of the plurality of threads for the neighbouring section of values of the one-dimensional sequence of values.

[0010] The second thread of the plurality of threads may: perform at least one part of the phase of the operation on at least one set of one or more values of the neighbouring section of values assigned to the second thread in order to determine at least one contribution, from said at least one set of one or more values of the neighbouring section of values, to the phase of the operation that is to be completed by the first thread for the section of values assigned to the first thread; and write the at least one contribution determined by the second thread to the memory; and the first thread of the plurality of threads may: read the at least one contribution determined by the second thread from the memory; and complete the phase of the operation for the section of values assigned to the first thread in dependence on the at least one contribution determined by the second thread read from the memory in order to generate a section of processed values.

10

15

20

30

35

**[0011]** Completing the phase of the operation for the neighbouring section of values may comprise: the second thread performing at least one part of the phase of the operation on at least one set of one or more values of the neighbouring section of values assigned to the second thread in order to determine at least one contribution from each of said one or more values of the neighbouring section of values to the phase of the operation; and combining said at least one contribution determined by the second thread for the neighbouring section of values with the at least one contribution read from the memory by the second thread.

[0012] The first thread of the plurality of threads may determine one or more values of the section of values assigned to the first thread as the at least one contribution, from the section of values assigned to the first thread, to the phase of the operation that is to be completed by the second thread of the plurality of threads for the neighbouring section of values of the one-dimensional sequence of values.

**[0013]** The second thread of the plurality of threads may: determine one or more values of the neighbouring section of values assigned to the second thread as at least one contribution, from the neighbouring section of values assigned to the second thread, to the phase of the operation that is to be completed by the first thread for the section of values assigned to the first thread; and write the at least one contribution determined by the second thread to the memory; and the first thread of the plurality of threads may: read the at least one contribution determined by the second thread from the memory; and complete the phase of the operation for the section of values assigned to the first thread in dependence on the at least one contribution determined by the second thread read from the memory in order to generate a section of processed values.

**[0014]** Completing the phase of the operation for the neighbouring section of values may comprise: the second thread performing the phase of the operation on the values of the neighbouring section of values assigned to the second thread using the values of the neighbouring section of values assigned to the second thread and the at least one contribution read from the memory in order to generate a section of processed values.

**[0015]** The plurality of threads may be processed by processing logic comprised by a core of the processing unit, the processing logic may be implemented on a chip and the memory being physically located on the same chip as the processing logic.

**[0016]** Each of the plurality of threads may read the values of the section of values assigned to that thread from a further memory that is not physically located on the same chip as the core.

**[0017]** The array of values may be an array of pixel values, an array of audio samples of an audio signal, or an array of signal samples of a transmitted signal.

**[0018]** The array of values may be a two-dimensional array of pixel values, and the operation may be a separable filter operation.

[0019] During the phase of the separable filter operation, values of the one-dimensional sequence of values may be filtered in dependence on a one-dimensional filter kernel including the value to be filtered and one or more values of the sequence of values positioned on one or both sides of that value. The radius of the filter kernel may be less than or equal to half of the number of values in each section of values.

15 **[0020]** The separable filter operation may be a separable Gaussian filter operation or a separable box filter operation.

**[0021]** The one-dimensional sequence of values of the array of values may be a row of values of the array of values; or the one-dimensional sequence of values of the array of values may be a column of values of the array of values.

**[0022]** The sections of processed values generated by the plurality of threads may be written to the memory such that a processed value is written to memory corresponding to each value of the array of values.

20

25

30

35

[0023] Said phase of the operation may be an initial phase of the operation, the array of values may be a two-dimensional array of values, the operation may be a separable operation, and the method may further comprise: so as to perform a subsequent phase of the operation: for each of one or more perpendicular one-dimensional sequences of values of the two-dimensional array of values: assigning, to each of the plurality of threads, a respective plurality of processed values from the memory, said plurality of processed values corresponding to a one-dimensional section of values of the perpendicular one-dimensional sequence of values of the two-dimensional array of values; and a first thread of the plurality of threads: determining at least one contribution, from the plurality of processed values assigned to the first thread, to the subsequent phase of the operation that is to be completed by a second thread of the plurality of threads for a plurality of processed values that correspond with a one-dimensional section of values of the perpendicular one-dimensional sequence of values of the two-dimensional array of values that neighbour the one-dimensional section of values of the perpendicular one-dimensional sequence of values that correspond to the plurality of processed values assigned to the first thread; and writing the at least one contribution determined by the first thread to the memory; and the second thread of the plurality of threads: reading the at

least one contribution determined by the first thread from the memory; and completing the subsequent phase of the separable operation for the plurality of processed values assigned to the second thread in dependence on the at least one contribution determined by the first thread in order to generate a section of output values.

[0024] The first thread of the plurality of threads may perform at least one part of the subsequent phase of the separable operation on at least one set of one or more values of the plurality of processed values assigned to the first thread in order to determine at least one contribution, from said at least one set of one or more values, to the subsequent phase of the operation that is to be completed by the second thread of the plurality of threads for the plurality of processed values that correspond with the one-dimensional section of values of the perpendicular one-dimensional sequence of values of the perpendicular one-dimensional section of values of the perpendicular one-dimensional sequence of values that correspond to the plurality of processed values assigned to the first thread.

10

15

20

25

30

**[0025]** The first thread of the plurality of threads may determine one or more values of the plurality of processed values assigned to the first thread as the at least one contribution, from the plurality of processed values assigned to the first thread, to the subsequent phase of the operation that is to be completed by the second thread of the plurality of threads for the plurality of processed values that correspond with the one-dimensional section of values of the perpendicular one-dimensional sequence of values of the two-dimensional array of values that neighbour the one-dimensional section of values of the perpendicular one-dimensional sequence of values that correspond to the plurality of processed values assigned to the first thread.

[0026] The one-dimensional sequence of values of the two-dimensional array of values is a row of values of the two-dimensional array of values and the perpendicular one-dimensional sequence of values of the two-dimensional array of values is a column of values of the two-dimensional array of values; or the one-dimensional sequence of values of the two-dimensional array of values and the perpendicular one-dimensional sequence of values of the two-dimensional array of values is a row of values of the two-dimensional array of values.

**[0027]** The method may further comprise: receiving a two-dimensional image; dividing the two-dimensional image into a plurality of overlapping tiles, each tile comprising a two-dimensional array of pixel values; and performing the method described herein on the two-dimensional array of pixel values of each tile.

**[0028]** The operation may be performed on the two-dimensional array of pixel values of each tile of the plurality of overlapping tiles by a different core of the processing unit.

[0029] According to a second aspect of the present invention there is provided a processing unit for performing an operation on an array of values, the processing unit comprising processing logic and a memory, the processing logic being configured to so as to perform a phase of the operation: for each of one or more one-dimensional sequences of values of the array of values: assign a

respective section of values of the one-dimensional sequence of values to each of a plurality of threads; and by a first thread of the plurality of threads: determine at least one contribution, from the section of values assigned to the first thread, to the phase of the operation that is to be completed by a second thread of the plurality of threads for a neighbouring section of values of the one-dimensional sequence of values; and write the at least one contribution to the memory; and by the second thread of the plurality of threads: read the at least one contribution from the memory; and complete the phase of the operation for the neighbouring section of values assigned to the second thread in dependence on the at least one contribution read from the memory in order to generate a section of processed values.

**[0030]** The processing logic may be comprised by a core of the processing unit, the processing logic may be implemented on a chip and the memory being physically located on the same chip as the processing logic.

10

15

20

25

30

35

40

[0031] There may also be provided a computer-implemented method of performing a separable operation on a two-dimensional array of values at a processing unit comprising a memory, the memory comprising a plurality of memory banks, wherein in each writing or reading step each memory bank can be written into or read from by only one respective thread, the method comprising: dividing the two-dimensional array of values into a plurality of two-dimensional sub-arrays of values; for each of the plurality of sub-arrays: performing, using a plurality of threads, an initial phase of the separable operation for said sub-array of values in order to generate a respective processed value for each value of said sub-array of values; each of the plurality of threads writing a respective first plurality of processed values to the memory over a plurality of writing steps, said first plurality of processed values corresponding to a one-dimensional sequence of values of said sub-array of values; each of the plurality of threads reading a respective second plurality of processed values from the memory over a plurality of reading steps, said second plurality of processed values corresponding to a perpendicular one-dimensional sequence of values of a sub-array of values in a transposed position within the array of values relative to said sub-array of values; and performing, using the plurality of threads, a subsequent phase of the separable operation for the plurality of processed values read by the plurality of threads in order to generate a respective output value for each value of the sub-array of values in the transposed position; wherein a respective processed value is written into each of the memory banks of the memory in at least one of the plurality of writing steps, and a respective processed value is read from each of the memory banks of the memory in at least one of the plurality of reading steps.

**[0032]** There may also be provided a processing unit for performing a separable operation on a two-dimensional array of values, the processing unit comprising: a memory comprising a plurality of memory banks, wherein the memory is configured so that in each writing or reading step each memory bank can be written into or read from by only one respective thread; and processing logic configured to: divide the two-dimensional array of values into a plurality of two-dimensional subarrays of values; for each of the plurality of sub-arrays: perform, using a plurality of threads, an initial phase of the separable operation for said sub-array of values in order to generate a respective processed value for each value of said sub-array of values; using each of the plurality of threads,

write a respective first plurality of processed values to the memory over a plurality of writing steps, said first plurality of processed values corresponding to a one-dimensional sequence of values of said sub-array of values; using each of the plurality of threads, read a respective second plurality of processed values from the memory over a plurality of reading steps, said second plurality of processed values corresponding to a perpendicular one-dimensional sequence of values of a sub-array of values in a transposed position within the array of values relative to said sub-array of values; and perform, using the plurality of threads, a subsequent phase of the separable operation for the plurality of processed values read by the plurality of threads in order to generate a respective output value for each value of the sub-array of values in the transposed position; wherein a respective processed value is written into each of the memory banks of the memory in at least one of the plurality of writing steps, and a respective processed value is read from each of the memory banks of the memory in at least one of the plurality of reading steps.

[0033] A processing unit as described in any of the examples herein may be embodied in hardware on an integrated circuit. There may be provided a method of manufacturing, at an integrated circuit manufacturing system, a processing unit as described in any of the examples herein. There may be provided an integrated circuit definition dataset that, when processed in an integrated circuit manufacturing system, configures the system to manufacture a processing unit as described in any of the examples herein. There may be provided a non-transitory computer readable storage medium having stored thereon a computer readable description of a processing unit as described in any of the examples herein that, when processed in an integrated circuit manufacturing system, causes the integrated circuit manufacturing system to manufacture an integrated circuit embodying the processing unit.

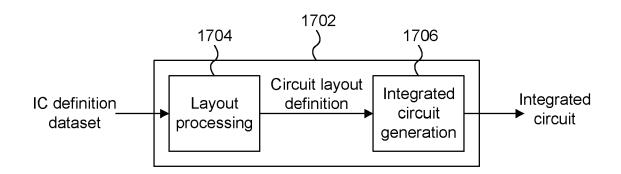

**[0034]** There may be provided an integrated circuit manufacturing system comprising: a non-transitory computer readable storage medium having stored thereon a computer readable description of a processing unit as described in any of the examples herein; a layout processing system configured to process the computer readable description so as to generate a circuit layout description of an integrated circuit embodying the processing unit; and an integrated circuit generation system configured to manufacture the processing unit according to the circuit layout description.

**[0035]** There may be provided computer program code for performing any of the methods described herein. There may be provided non-transitory computer readable storage medium having stored thereon computer readable instructions that, when executed at a computer system, cause the computer system to perform any of the methods described herein.

**[0036]** The above features may be combined as appropriate, as would be apparent to a skilled person, and may be combined with any of the aspects of the examples described herein.

### 35 BRIEF DESCRIPTION OF THE DRAWINGS

10

15

20

25

30

[0037] Examples will now be described in detail with reference to the accompanying drawings in which:

Figure 1A shows an example graphics processing unit (GPU) and memory.

Figure 1B shows an example memory hierarchy accessible by processing logic.

Figure 2 shows an example operation.

5

10

15

20

25

30

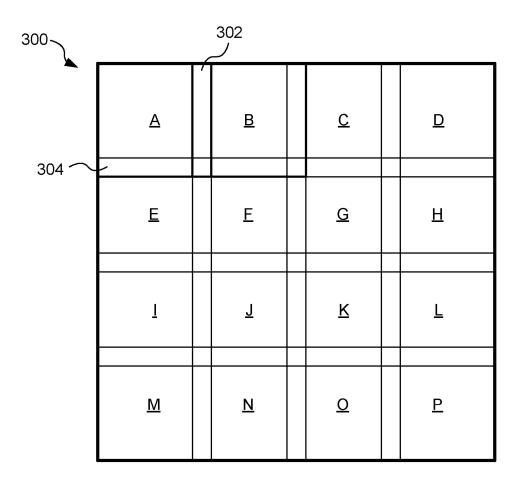

Figure 3 shows an example image divided into a plurality of overlapping tiles.

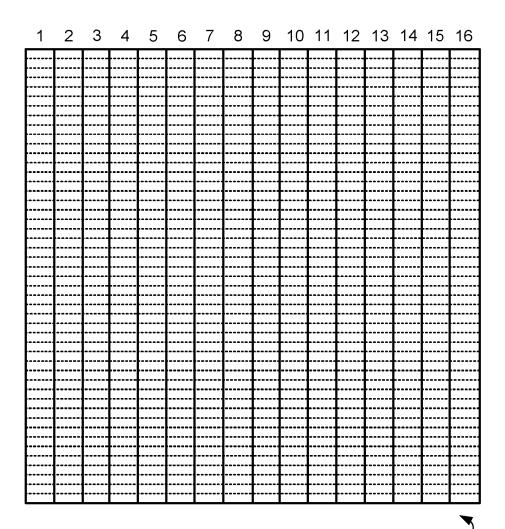

Figure 4 shows an example assignment of sections of values to a plurality of threads.

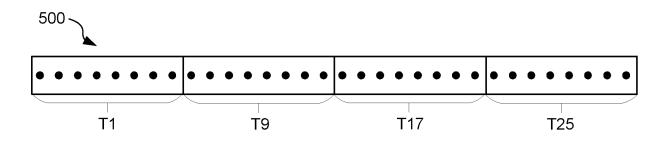

Figure 5 shows a one-dimensional sequence of values.

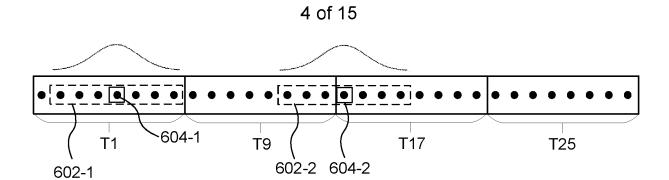

Figure 6 shows example filter kernels overlayed on a one-dimensional sequence of values.

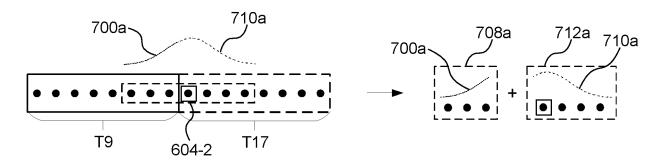

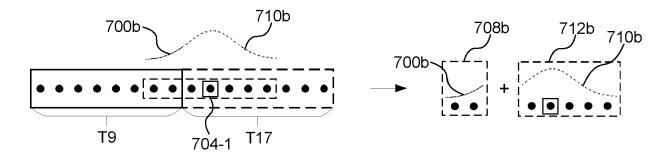

Figures 7a to 7c show example contributions from values of a section of values to a phase of an operation to be completed for a neighbouring a section of values.

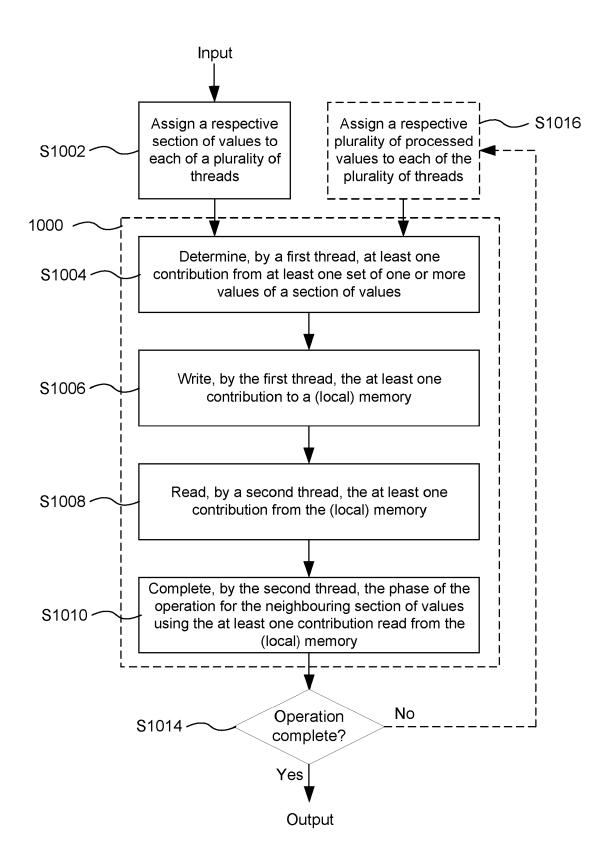

Figure 8 shows, in an example, the sections of values to which the plurality of processed values assigned in the subsequent phase of the operation correspond.

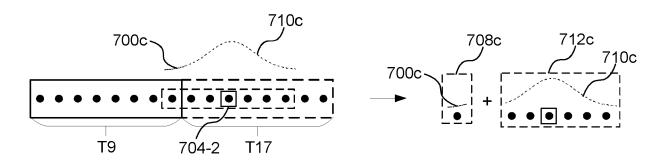

Figure 9 shows a perpendicular one-dimensional sequence of values.

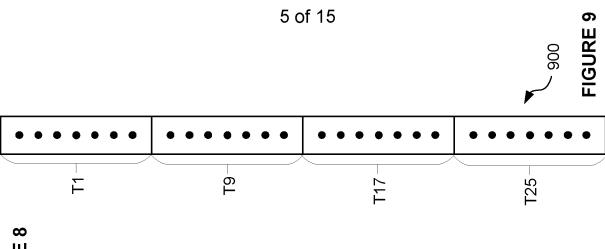

Figure 10 shows a method of performing an operation on an array of values at a processing unit according to the principles described herein.

Figure 11 shows an example memory comprising a plurality of memory banks.

Figures 12A and 12B illustrate processed values in memory.

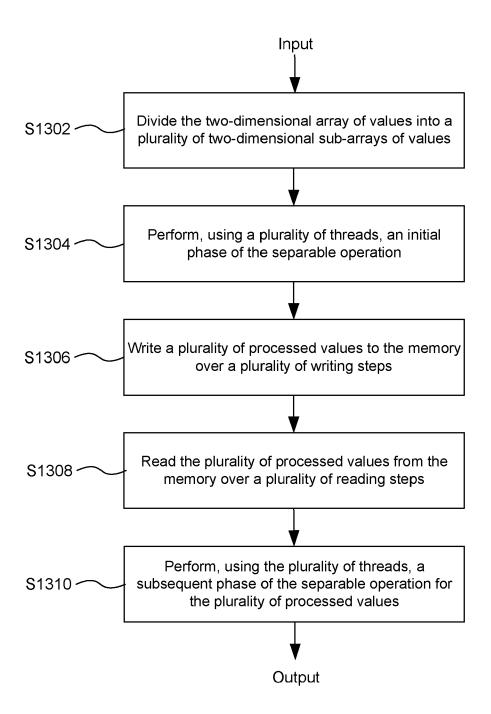

Figure 13 shows a method of performing a separable operation on a two-dimensional array of values at a processing unit comprising a memory according to the principles described herein.

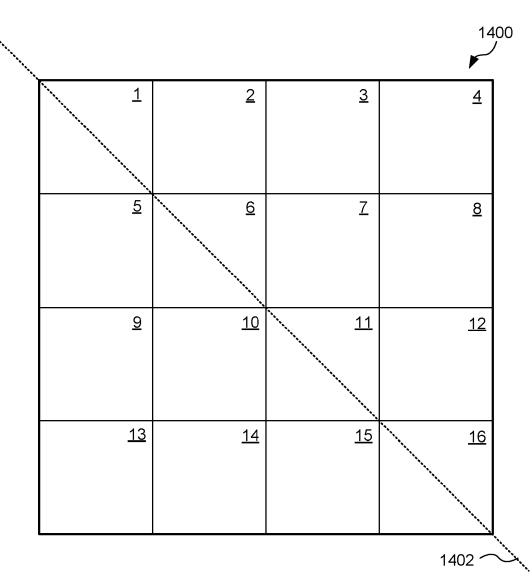

Figure 14 shows an array of values divided into a plurality of sub-arrays of values.

Figures 15A to 15D illustrate processed values and padding in memory.

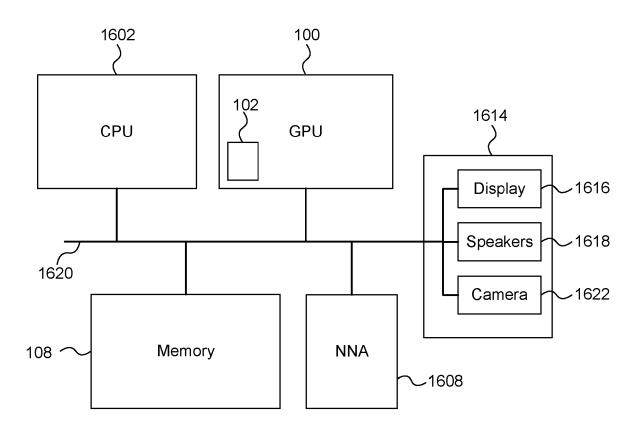

Figure 16 shows a computer system in which a processing unit is implemented; and Figure 17 shows an integrated circuit manufacturing system for generating an integrated circuit embodying a processing unit.

**[0038]** The accompanying drawings illustrate various examples. The skilled person will appreciate that the illustrated element boundaries (e.g., boxes, groups of boxes, or other shapes) in the drawings represent one example of the boundaries. It may be that in some examples, one element may be designed as multiple elements or that multiple elements may be designed as one element. Common reference numerals are used throughout the figures, where appropriate, to indicate similar features.

### **DETAILED DESCRIPTION**

**[0039]** The following description is presented by way of example to enable a person skilled in the art to make and use the invention. The present invention is not limited to the embodiments described herein and various modifications to the disclosed embodiments will be apparent to those skilled in the art.

[0040] Embodiments will now be described by way of example only.

**[0041]** Figure 1A shows an example graphics processing unit (GPU) 100 and memory 108. Graphics processing unit 100 is described herein as an example of a processing unit capable of (e.g. configured to perform) parallel processing. It is to be understood that the principles described herein could also be applied to any other suitable type of processing unit that is capable of (e.g. configured

to perform) parallel processing – such as a digital signal processing unit (e.g. DSP), or a suitable type of central processing unit (CPU) that is capable of parallel processing.

**[0042]** Graphics processing unit 100 may have any suitable architecture. Graphics processing unit 100 may be operable to perform any kind of graphics, image or video processing, general processing and/or any other type of data processing – such as the processing of general computing tasks, particularly those which can be readily parallelised. Examples of general computing tasks include signal processing, audio processing, computer vision, physical simulations, statistical calculations, neural networks and cryptography.

**[0043]** A graphics processing unit typically comprises one or more processing elements. In Figure 1A, the graphics processing unit 100 is shown comprising three processing elements – labelled as 102-1, 102-2 and 102-n. It is to be understood that a processing unit configured in accordance with the principles described herein could comprise any suitable number of processing elements.

10

15

20

25

30

35

[0044] Each processing element 102 may be a different core of the graphics processing unit 100. Each processing element 102 comprises processing logic 104 and a memory 106. That is, in Figure 1A: processing element 102-1 comprises processing logic 104-1 and memory 106-1; processing element 102-2 comprises processing logic 104-2 and memory 106-2; and processing element 102-n comprises processing logic 104-n and memory 106-n. Each memory 106 may be available for the storage of data exclusively by / for the processing logic 104 of the processing element 102 that it is comprised by. Each memory 106 may be physically located on the same chip (e.g. on the same semiconductor die and/or in the same integrated circuit package) as the processing logic 104 of the processing element 102 that it is comprised by. As such, each memory 106 may be referred to as "local memory", "on-chip memory" or "internal memory". The processing logic 104 of each processing element 102 may be able to access its local memory 106 without consuming memory bandwidth to the memory 108. That said, relative to the storage capacity of memory 108, each local memory 106 may have a small storage capacity, e.g. 60 kB (kilobytes).

[0045] Memory 108 may also be accessible to the processing logic 104 of each processing element 102, e.g. over a system bus. Graphics processing unit 100 may be implemented on a chip (e.g. semiconductor die and/or integrated circuit package) and memory 108 may not be physically located on the same chip (e.g. semiconductor die and/or integrated circuit package) as the graphics processing unit 100. As such, memory 108 may be referred to as "off-chip memory" and/or "external memory". Memory 108 may also be used to store data for other processing units of the system at which the graphics processing unit is implemented, e.g. a central processing unit (CPU – not shown in Figure 1A), and so may also be referred to as "system memory" and/or "global memory". Memory 108 may be a dynamic random access memory (e.g. DRAM). Relative to the storage capacity of each local memory 106, global memory 108 may have a large storage capacity, e.g. 10 GB (gigabytes). That said, the latency associated with processing logic 104 reading from / writing to global memory 108 may be greater (e.g. significantly greater) than with the latency associated with processing logic 104 reading from / writing to its local memory 106.

**[0046]** As described in further detail herein, other types of memory (e.g. caches, registers or any other suitable type of memory – not shown in Figure 1A for ease of illustration) may also be accessible to the processing logic 104 of each processing element 102.

[0047] Work to be performed by a processing unit that is capable of (e.g. configured to perform) parallel processing can be arranged into so called "workgroups", "warps" and "threads". A workgroup may comprise one or more warps. A warp may comprise a plurality of threads, where that plurality of threads can be processed in parallel (e.g. at a single core of a graphics processing unit). In examples where a workgroup comprises more than one warp, each of those warps can be processed in series at a single core of a graphics processing unit. Workgroups may be processed independently of each other (e.g. at different cores of a graphics processing unit, or in series at a single core of a graphics processing unit). Threads within the same workgroup (e.g. threads within the same warp of a workgroup, and threads within different warps of the same workgroup) may be able to share access during their processing to memory dedicated to the processing element (e.g. core) of the processing unit processing those threads (e.g. local memory 106 dedicated to the processing logic 104 processing those threads). That is, threads within the same warp may be able to share access during their processing to memory dedicated to the processing element (e.g. core) of the processing unit processing those threads (e.g. local memory 106 dedicated to the processing logic 104 processing those threads). Further, warps within the same workgroup may be able to share access during their processing to memory dedicated to the processing element (e.g. core) of the processing unit processing those threads (e.g. local memory 106 dedicated to the processing logic 104 processing those warps). By contrast, different workgroups may not be able to share access during their processing to memory dedicated to a certain processing element (e.g. core) of the processing unit.

10

15

20

25

30

35

[0048] A warp may be arranged as an array of threads (e.g. a one-dimensional, two-dimensional or three-dimensional array of threads). The number of threads comprised by a warp may be limited. The limit on the number of threads comprised by a warp may be caused by a hardware restriction (e.g. a limit on how many threads can be processed in parallel on the available processing hardware). In an example, a warp may comprise up to 128 threads. In this example, if more than 128 threads are to be perform the same operation, then more than one warp will be associated with that operation. For example, if 2048 threads are to perform the same operation, then sixteen warps may be associated with that operation. Said sixteen warps may be comprised by the same workgroup, or may be divided between a plurality of workgroups (e.g. up to sixteen different workgroups). It is to be understood that the "workgroup", "warp" and "thread" terminology used herein is not intended to be limiting, and that other terminology could be used to describe the same concepts. For example, a "thread" as described herein could alternatively be referred to as an "invocation" or a "work-item", whilst a "workgroup" as described herein could alternatively be referred to as a "thread block" or a "threadgroup".

**[0049]** Figure 1B shows an example memory hierarchy accessible by the processing logic 104 of a processing element 102. In Figure 1B, for ease of illustration, the memory hierarchy associated with a single processing element 102 of a processing unit (e.g. processing unit 100 of Figure 1A) is

shown. It is to be understood that each processing element 102 of a processing unit (e.g. processing unit 100 of Figure 1A) may be associated with an equivalent memory hierarchy to that shown in Figure 1B.

[0050] In Figure 1B, processing logic 104, local memory 106 and global memory 108 have the same properties as the processing logic 104, local memory 106 and global memory 108 described with reference to Figure 1A. Also shown in Figure 1B is a register bank 110 comprised by the processing element 102. Register bank 110 comprises a plurality of registers (e.g. register memories). Relative to the storage capacity of local memory 106, each register of the register bank 108 has a small storage capacity, e.g. 32 bits. That said, the latency associated with processing logic 104 reading from / writing to the register bank 110 may be less than with the latency associated with processing logic 104 reading from / writing to local memory 106. The register bank 110 may be physically located on the same chip (e.g. on the same semiconductor die and/or in the same integrated circuit package) as the processing logic 104 of the processing element 102 that it is comprised by. The register bank 110 may be physically located on the same chip (e.g. on the same semiconductor die and/or in the same integrated circuit package) as the local memory 106 of the processing element 102 that it is comprised by.

10

15

20

25

30

35

40

**[0051]** When processing logic 104 is processing a warp comprising a plurality of threads, a respective one or more registers of the register bank 110 may be dedicated to (e.g. accessible exclusively by) each thread of that warp. That is, values to be processed in accordance with (e.g. "by") a thread may be stored in the one or more registers accessible by that thread. Other threads within the same warp may not be able to access those values within the one or more registers accessible by that thread.

[0052] For example, a warp comprising a plurality of threads (e.g. 128 threads) can be processed at processing element 102 (e.g. a core of a processing unit) so as to perform an operation on an array of values (e.g. 1024 values). With reference to Figure 1B, the array of values may initially be stored in global memory 108. Each thread of the warp may be configured to perform the operation on a group of values (e.g. 8 values) of the array of values (e.g. 1024 values). The limit on the number of values that can be processed by a thread may be caused by the amount of register memory in register bank 110 accessible by (e.g. dedicated to) each thread. In order to perform the operation, the processing logic 104 may cause, for each thread of the warp, a respective group of values (e.g. 8 values) to be processed by that thread to be read from global memory 108 into the one or more registers dedicated to that thread. The values written into the one or more registers dedicated to a thread can be processed by the processing logic 104 in accordance with that thread. Thereafter, the processed values can be output from the processing element 102 by writing those processed values from the respective one or more registers dedicated to each thread into global memory 108. Alternatively, if further processing is to be performed on those processed values at the processing element 102, those values can be written from the respective one or more registers dedicated to each thread into local memory 106. The plurality of threads within the warp can share access to local memory 106. That is, the plurality of threads within the warp can access the processed values written into local memory 106. As such, the processing logic 104 may cause, for each thread of the warp, a

respective group of processed values (e.g. 8 processed values) to be further processed by that thread to be read from local memory 106 into the one or more registers dedicated to that thread. The processed values written into the one or more registers dedicated to a thread can be further processed by the processing logic 104 in accordance with that thread. Thereafter, the further processed values can be output from the processing element 102 by writing those further processed values from the respective one or more registers dedicated to each thread into global memory 108. Alternatively, yet further processing iterations can be performed at the processing element 102 in the same manner.

**[0053]** Processing units, such as graphics processing unit 100, can perform operations on arrays of values (e.g. one-dimensional or multi-dimensional arrays of values). In examples, the values of said arrays of values can be pixels values, audio samples of an audio signal, signal samples of a transmitted signal, or any other suitable type of values.

[0054] Figure 2 shows an example operation. In Figure 2, the operation is a one-dimensional Gaussian filter operation, in which a value 204 is filtered in dependence on a one-dimensional kernel 202 of values including the value 204 to be filtered and one or more values on one or both sides of that value 204. A one-dimensional Gaussian filter operation can use a filter kernel 202 including an odd number of values, the centre value 204 being the value to be filtered. In Figure 2, the filter kernel 202 is symmetrical. In the specific example shown in Figure 2, the filter kernel 202 comprises seven values, including the value 204 to be filtered, and three values on either side of that value 204. In this example, the filter kernel 202 can be said to have a radius r of three values. That is, for a symmetrical filter kernel, the radius r of the filter kernel 202 can be said to be the number of values on either side of the central value to be filtered. It is to be understood that, in other examples, the filter kernel need not be symmetrical. That is, the filter kernel may include more values on one side of the value to be filtered than on the other side).

15

20

25

30

[0055] In a one-dimensional Gaussian filter operation, a filtered output for the centre value 204 may be determined by performing a weighted sum of the values in the kernel 202. The respective weight for each value in the kernel 202 can be determined in dependence on a Gaussian function 200 centred on the value 204 to be filtered. That is, as would be understood by the skilled person, in dependence on the Gaussian function 200, a value further from the value 204 to be filtered will be weighted lower (e.g. with a value closer to 0) in the weighted sum than a value closer to the value 204 to be filtered.

[0056] The one-dimensional Gaussian filter operation shown in Figure 2 may be performed for each value of a one-dimensional sequence of values. That is, each value in a one-dimensional sequence of values may be filtered in dependence on a one-dimensional kernel 202 of values in which it is the value to be filtered. As an aside, the skilled person would be aware of numerous different techniques for operating on the values at the start and end of a sequence of values – such as when the value to be filtered is the first value in the sequence of values. In one example, this edge case may be addressed by duplicating the first value in the sequence of values such that the filter kernel includes the value to be filtered, a number of values from the sequence of values on one side

of the value to be filtered, and a number of copies of the value to be filtered on the other side of the value to be filtered. Typically, the number of values at the start and end of a sequence of values to which an "edge case technique" is applied during filtering is equal to the radius r of the filter kernel. The skilled person would be aware of various other techniques for addressing edge cases such as this, and so these techniques will not be discussed further herein for conciseness.