US 20030197535A1

# (19) United States (12) Patent Application Publication Peng (10) Pub. No.: US 2003/0197535 A1 (43) Pub. Date: Oct. 23, 2003

#### (54) METHOD AND APPARATUS FOR CHANGE PUMP CIRCUIT

(76) Inventor: Yung-Chow Peng, (US)

Correspondence Address: Finnegan, Henderson, Farabow, Garrett & Dunner, L.L.P. 1300 I Street, N. W. Washington, DC 20005-3315 (US)

- (21) Appl. No.: 10/127,732

- (22) Filed: Apr. 23, 2002

## **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |         |

|------|-----------------------|---------|

| (52) | U.S. Cl.              | 327/157 |

### (57) ABSTRACT

Charge-pumps consistent with this invention comprise a first transistor for sinking a current from an output node; a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off; and a current source to provide a turn-off current to a common node between the first transistor and the second transistor when the second transistor interrupts the sinking current. Charge-pump circuits consistent with this invention comprise a first transistor for sinking a current from an output node; a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off; and a clamping circuit to clamp a common node between the first transistor and the second transistor below a clamping voltage.

140

130

120

/110

Phase Detector

ລົ

ć

$\cup_2$

<u>200</u>

Fig. 2 PRIOR ART

300

#### METHOD AND APPARATUS FOR CHANGE PUMP CIRCUIT

#### DESCRIPTION OF THE INVENTION

[0001] 1. Field of the Invention

**[0002]** This invention relates to charge pump circuits, such as charge pump circuits that may be used, for example, in phase-locked loops (PLLs).

[0003] 2. Background of the Invention

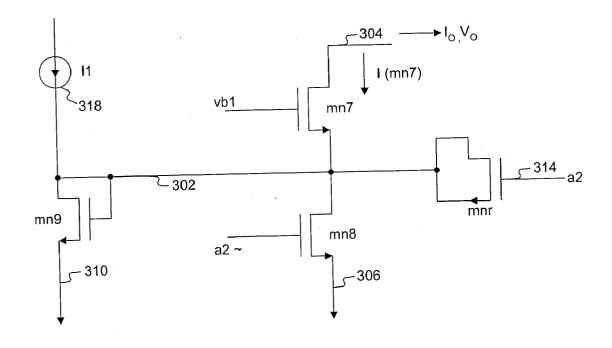

[0004] FIG. 1 is a block diagram of a conventional PLL 100. Conventional PLL 100 includes a phase detector 110, a charge pump 120, a loop filter 130, and a voltage controlled oscillator (VCO) 140. Phase detector 110 compares the relative phase of two signals, such as signal  $U_1$  and signal U<sub>2</sub>, and outputs a signal that is a measure of their phase difference. Charge pump 120 outputs positive or negative charge to loop filter 130, based in part on the output of phase detector 110. Typically, charge pump 120 varies the output charge by varying the duration of a current applied to loop filter 130. Based on the output signal of charge pump 120, which is filtered by loop filter 130, VCO 140 deviates the frequency of its output signal U<sub>2</sub> toward the frequency of signal U1. The output signal U2 quickly "locks" to the input U<sub>1</sub>, maintaining a fixed phase relationship between input signal  $U_1$  and output signal  $U_2$ .

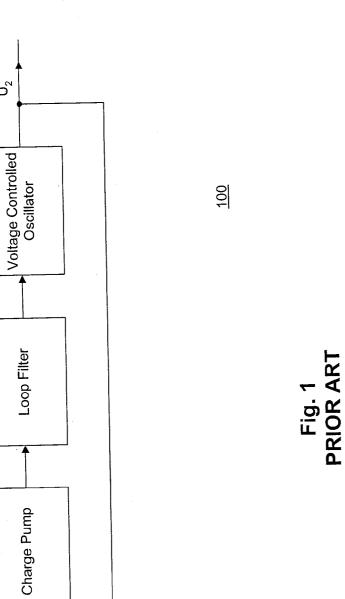

[0005] FIG. 2 is a circuit diagram of a sinking path circuit 200 of a conventional charge pump 120, that may be used in PLL 100 of FIG. 1, for example. Sinking path circuit 200 includes four metal-oxide-semiconductor (MOS) transistors mn7, mn8, 230, and 240. A reference current  $I_{REF}$ , is applied to transistor 230 by a current source 250. Reference current  $I_{REF}$  is mirrored to transistor mn7. A gate-to-source voltage  $V_{G}$  is applied to transistor 240 so that transistor 230 has a conductive electrical path coupling its source to ground. Transistor 240 may be matched to transistor mn8 so that when a voltage level equal to  $V_{\rm G}$  is applied to a gate 212 of transistor mn8, transistor mn8 couples the source of transistor mn7 to ground. Due to the mirroring effect of transistors 230 and mn7, a current  $I_{OUT}$  appears through transistor mn7 that substantially matches current I<sub>REF</sub>. Current I may be provided to loop filter 130 as illustrated in FIG. 1, for example.

**[0006]** Alternatively, instead of applying a voltage equal to  $V_G$  to gate **212** of transistor mn8, gate **212** may be grounded, thus removing the substantially conductive path to ground from source **222** of transistor mn7. In this case, substantially no current appears (i.e.,  $I_{OUT}$  is substantially zero) through transistor mn7. One of ordinary skill in the art recognizes how similar principles are used for the driving path of charge pump **120**.

[0007] In a variety of applications, it is desirable for charge pump 120 to switch at high speeds. Typically, high speed charge pump circuits require large output currents. Large output currents, however, are not desirable in PLLs because they generate noise that degrades performance. Furthermore, large currents require larger, more costly circuit components. Therefore, there is a need for a charge pump circuit that operates at high switching speeds while reducing charge-pump current.

#### SUMMARY OF THE INVENTION

**[0008]** Charge-pumps consistent with this invention comprise a first transistor for sinking a current from an output node; a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off; and a current source to provide a turn-off current to a common node between the first transistor and the second transistor when the second transistor interrupts the sinking current.

**[0009]** Charge-pump circuits consistent with this invention comprise a first transistor for sinking a current from an output node; a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off; and a clamping circuit to clamp a common node between the first transistor and the second transistor below a clamping voltage.

**[0010]** Charge-pumps consistent with this invention comprise a first transistor to drive a current to an output node; a second transistor coupled between the first transistor and a power supply, wherein the second transistor interrupts the driving current when the second transistor is turned off; and a current source to provide a turn-off current to a common node between the first transistor and the second transistor when the second transistor and the second transistor when the second transistor and the second transistor when the second transistor interrupts the driving current.

**[0011]** Charge-pump circuits consistent with this invention comprise a first transistor for driving a current to an output node; a second transistor coupled between the first transistor and a power supply, wherein the second transistor interrupts the driving current when the second transistor is turned off; and a clamping circuit to clamp a common node between the first transistor and the second transistor above a clamping voltage.

**[0012]** Additional objects and advantages of the invention will be set forth in part in the description which follows, and in part will be obvious from the description, or may be learned by practice of the invention. The objects and advantages of the invention will be realized and attained by means of the elements and combinations particularly pointed out in the appended claims.

**[0013]** It is understood that both the foregoing general description and the following detailed description are exemplary and explanatory only and are not restrictive of the invention, as claimed.

**[0014]** The accompanying drawings, which are incorporated in and constitute a part of this specification, illustrate several embodiments of the invention and together with the description, serve to explain the principles of the invention.

## BRIEF DESCRIPTION OF THE DRAWINGS

[0015] FIG. 1 is a block diagram of a conventional PLL;

[0016] FIG. 2 is a circuit diagram of a sinking path circuit of a conventional charge pump that may be used in the PLL of FIG. 1;

**[0017]** FIG. **3** is a circuit diagram of a sinking path of a charge pump circuit consistent with this invention;

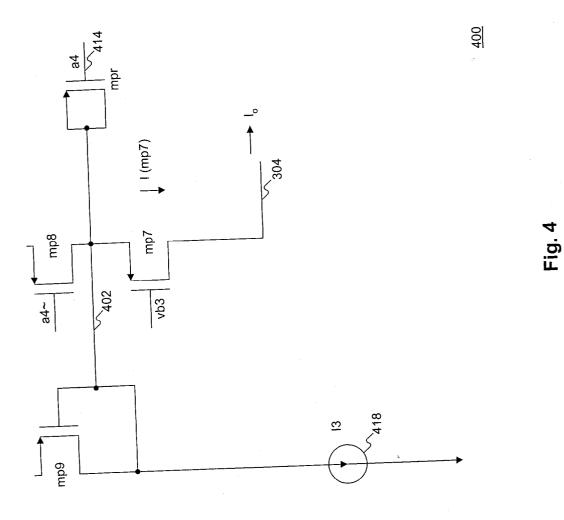

**[0018]** FIG. 4 is a circuit diagram of a driving path of a charge pump circuit consistent with this invention;

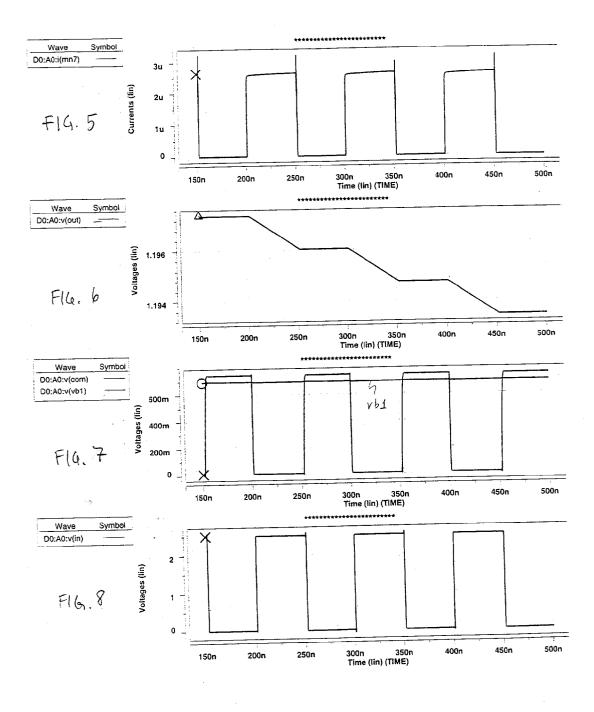

**[0019]** FIG. 5 is a signal diagram of current through transistor mn7 of FIG. 3 from a SPICE simulation;

[0020] FIG. 6 is a signal diagram of an output voltage  $V_{\odot}$  in FIG. 3 from a SPICE simulation;

**[0021]** FIG. 7 is a signal diagram of voltage bias signal vb1 and a voltage at a common node from a SPICE simulation;

**[0022]** FIG. 8 is a signal diagram of control signal a2~ at a gate voltage of transistor mn8 from a SPICE simulation; and

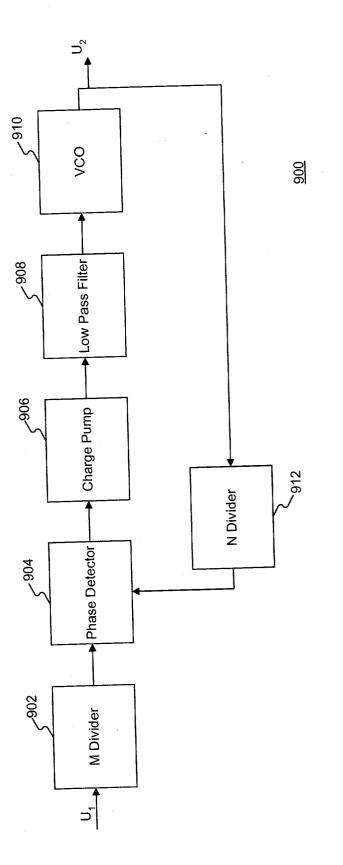

**[0023]** FIG. 9 is a block diagram of a PLL using a charge pump circuit consistent with this invention.

#### DESCRIPTION OF THE EMBODIMENTS

**[0024]** Reference is made below in detail to the present exemplary embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference characters or numbers are used throughout the drawings to refer to the same or like parts.

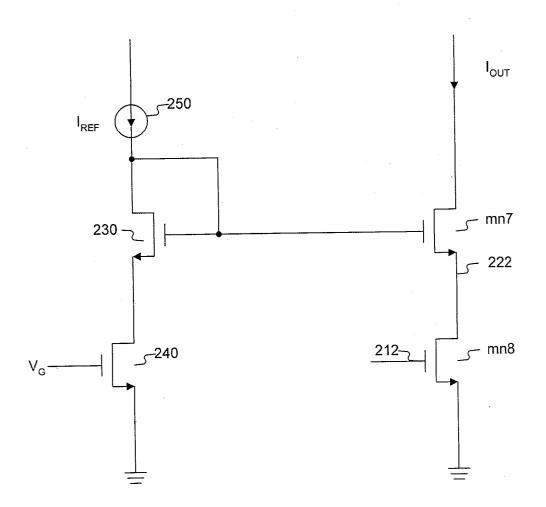

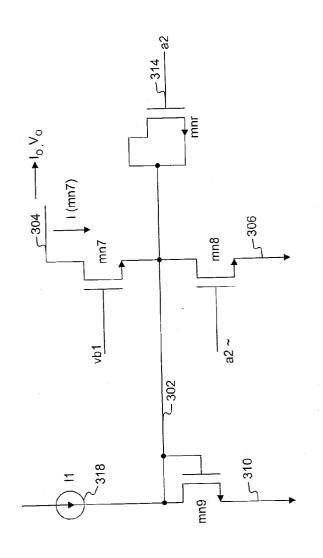

[0025] FIG. 3 is a circuit diagram of a sinking path 300 of a charge pump circuit consistent with this invention. The embodiment shown in FIG. 3 comprises four MOS transistors mn7, mn8, mn9, and mnr. Transistor mn7 acts as a current sinking device and comprises a gate connected to a voltage bias signal vb1; a drain that sinks a current I(mn7) from an output node 304; and a source connected to the drain of transistor mn8 at a common node 302. Voltage vb1 is a bias voltage that controls the magnitude of sinking current I(mn7) to output node 304. A current mirror circuit similar to that discussed with respect to charge-pump circuit 200 of FIG. 2 may supply bias voltage vb1.

[0026] Transistor mn8 acts as a current control device and comprises a source connected to ground; a drain connected to the source of transistor mn7 at common node 302; and a gate connected to an input signal a2~. When the voltage of signal a2~ is sufficiently high, transistor mn8 turns on and couples the source of transistor mn7 to ground and current I(mn7) passes through transistors mn7 and mn8. Alternatively, when the voltage of signal a2~ is sufficiently low, transistor mn8 turns off and the source of transistor mn7 does not have a substantially conductive path to ground. Thus, when mn8 turns off, transistor mn7 or transistor mn8, i.e., I(mn7) is substantially zero. Current I(mn7) may form part of output current I<sub>0</sub>.

[0027] In the embodiment of FIG. 3, a current source 318 provides current I1 to common node 302. Current source 318 assists turning off transistor mn7 by allowing transistor mn7 to turn off more quickly after transistor mn8 turns off. With current I1, transistor mn7 turns off more quickly because when transistor mn8 turns off, the current through transistor mn7 declines more quickly. Transistor mn7 turns off more quickly because current I1 helps pull up the source node voltage of transistor mn7 when transistor mn8 is turned off until it is clamped by transistor mn9. This may be referred to as "current to turn off transistor mn7. Without current I1, the current through transistor mn7 is not as sufficient to pull up the source node voltage of transistor mn7 turns form 7 is not as sufficient to pull up the source node voltage of transistor mn7 to turn off.

[0028] In the embodiment of FIG. 3, transistor mn9 acts as a clamping device and comprises a source connected to ground; and a gate and a drain connected to the source of transistor mn7 and the drain of transistor mn8 at common node 302. Transistor mn9 clamps the source voltage of transistor mn7 to below a clamped voltage when transistor mn8 is turned off. The clamped voltage is the voltage drop across transistor mn9. Clamping provides the advantage of reducing switching noise because the voltage change of common node 302 (the source node of transistor mn7) is minimized. In the embodiment of FIG. 3, transistor mn9 turns off when transistor mn8 turns on. Thus, a part of current I1 goes through transistor mn8 when transistor mn8 is turned on. When transistor mn8 turns off (and transistor mn7 turns off), transistor mn9 turns on and a part of current I1 flows through transistor mn9 to ground.

[0029] Current source 318 may be implemented as a simple current mirror current source, as is evident to one of ordinary skill in the art. Alternatively, current source 318 may be a resistor or any other well-known device that achieves the same purposes.

[0030] Transistor mnr acts as a "dummy device" and comprises a gate with a control signal  $a^2$ ; and a source and a drain connected together and to common node 302. Control signal  $a^2$  of transistor mnr is the inverse of control signal  $a^2\sim$  of transistor mn8. Because control signals  $a^2$  and  $a^2\sim$  are inverted, channel charge between transistor mn7 and transistor mn8 are complementary, thus reducing switching noise. In other words, transistor mnr may minimize switching noise due to charge rejection from transistor mn7 and transistor mn8.

[0031] Below is a truth table of the different states of transistors mn7, mn8, mn9, and mnr.

TABLE I

| transistor         | mn7       | mn8       | mn9       | mnr       |  |  |  |

|--------------------|-----------|-----------|-----------|-----------|--|--|--|

| state 1<br>state 2 | on<br>off | on<br>off | off<br>on | off<br>on |  |  |  |

[0032] FIG. 4 is a circuit diagram of a driving path 400 of a charge pump circuit consistent with this invention. The operation of the embodiment of FIG. 4 is similar to the operation of the embodiment of FIG. 3. The embodiment shown in FIG. 4 comprises four MOS transistors mp7, mp8, mp9, and mpr. Transistor mp7 acts as a current driving device and comprises a gate connected to a voltage bias signal vb3; a drain that drives a current I(mp7) to output node 304; and a source connected to the drain of transistor mp8 at a common node 402. Voltage vb3 is a bias voltage that controls the magnitude of driving current I(mp7) to output node 304. A current mirror circuit similar to that discussed with respect to charge-pump circuit 200 of FIG. 2 may supply bias voltage vb3.

[0033] Transistor mp8 acts as a current control device and comprises a source connected to voltage supply  $V_{DD}$ ; a drain connected to the source of transistor mp7 at common node 402; and a gate connected to an input signal a4~. When the voltage of signal a4~ is sufficiently low, transistor mp8 turns on and couples the source of transistor mp7 to voltage supply  $V_{DD}$  and current I(mp7) passes through transistors

mp7 and mp8 to output node 304. Alternatively, when the voltage of signal a4~ is high, i.e., approximately  $V_{DD}$ , transistor mp8 turns off and the source of transistor mp7 does not have a substantially conductive path to voltage supply  $V_{DD}$ . Thus, when mp8 turns off, transistor mp7 subsequently turns off as well. When transistor mp8 is off, substantially no current passes through transistor mn7 or transistor mn8, i.e., I(mp7) is substantially zero. Current I(mp7) may form part of output current I<sub>Q</sub>.

[0034] In the embodiment of FIG. 4, a current source 418 provides current I3 to common node 402. Current source 418 assists turning off transistor mp7 by allowing transistor mp7 to turn off more quickly after transistor mp8 turns off. With current I3, transistor mp7 turns off more quickly because when transistor mn8 turns off, the current through transistor mp7 declines more quickly. Transistor mp7 turns off more quickly because current I3 helps pull down the source node voltage of transistor mp7 when transistor mp8 is turned off until it is clamped by transistor mp7. Without current I3, the current to turn off transistor mp7. Without current I3, the current to turn off transistor mp7 is less sufficient (i.e., has less charge) to pull down the source node voltage of transistor mp7 to turn off.

[0035] In the embodiment of FIG. 4, transistor mp9 acts as a clamping device and comprises a source connected to voltage supply  $V_{DD}$ ; and a gate and a drain connected to the source of transistor mp7 and the drain of transistor mp8 at common node 402. Transistor mp9 clamps the source voltage of transistor mp7 to above a voltage when transistor mp8 is turned off. The clamped voltage is  $V_{DD}$  minus the voltage drop across transistor mp9. Clamping provides the advantage of reducing switching noise because the voltage change of common node 402 (the source node of transistor mp7) is minimized. In the embodiment of FIG. 4, transistor mp9 turns off when transistor mp8 turns on. Thus, a part of current I3 goes through transistor mp8 when transistor mp8 is turned on. When transistor mp8 turns off (and transistor mp7 turns off), transistor mp9 turns on and a part of current I3 flows through transistor mp9 to ground.

[0036] Current source 418 may be implemented as a simple current mirror current source, as evident to one of ordinary skill in the art. Alternatively, current source 418 may be a resistor or any other well-known device that achieves the same purposes.

[0037] Transistor mpr acts as a "dummy device" and comprises a gate with a control signal a4; and a source and a drain connected together and to common node 402. Control signal a4 of transistor mpr is the inverse of control signal a4- of transistor mp8. Because control signals a4 and a4- are inverted, channel charge between transistor mp7 and transistor mp8 are complementary, thus reducing switching noise. Thus, transistor mpr minimizes switching noise due to charge rejection from transistor mp7 and transistor mp8.

[0038] Below is a truth table of the different states of transistors mp7, mp8, mp9, and mpr.

TABLE II

| transistor         | mp7       | mp8       | mp9       | mpr       |  |  |  |  |

|--------------------|-----------|-----------|-----------|-----------|--|--|--|--|

| state 1<br>state 2 | on<br>off | on<br>off | off<br>on | off<br>on |  |  |  |  |

[0039] FIGS. 5, 6, 7, and 8 are signal diagrams of a SPICE simulation of a low voltage, 200 MHz sinking path charge pump circuit shown in FIG. 3. In the simulation,  $V_{\rm DD}$  is 2.5 volts. FIG. 5 is a signal diagram of current I(mn7) through transistor mn7 of FIG. 3 from a SPICE simulation. The vertical axis of FIG. 5 represents the current in microamps, and the horizontal axis represents time in nanoseconds. As shown in FIG. 5, there is little spiking current when transistor mn7 turns on after being off, resulting in greater accuracy and higher switching speeds for sinking current control. FIG. 6 is a signal diagram of an output voltage  $V_{\rm O}$  in FIG. 3 from a SPICE simulation. The vertical axis of FIG. 6 represents voltage in volts, and the horizontal axis represents time in nanoseconds.

[0040] FIG. 7 is a signal diagram of voltage bias signal vb1 and a voltage v(com) at common node 302 from a SPICE simulation. The value of voltage bias signal vb1 is constant at approximately 700 mV. FIG. 8 is a signal diagram of control signal  $a^2$ ~ at the gate voltage of transistor mn8 from a SPICE simulation. Control signal  $a^2$ ~ is periodic with a period of 100 nanoseconds as shown in FIG. 8. The value of a voltage v(com) at common node 302 shown in FIG. 7 is periodic and may follow the control signal  $a^2$ ~ of FIG. 8 very closely.

[0041] FIG. 9 is a block diagram of a PLL 900 using a charge pump 906 consistent with this invention. Charge pump 906 may comprise sinking path 300 and driving path 400 as shown in FIGS. 3 and 4. PLL 900 consists of an M divider 902, a phase detector 904, a charge pump 906, a low pass filter 908, a voltage controlled oscillator 910, and an N divider 912. M divider 902 divides input signal  $U_1$  frequency by the factor M. N divider divides output signal  $U_2$  frequency by N.

[0042] Other embodiments of the invention are apparent to those skilled in the art from consideration of the specification and practice of the invention disclosed herein. For example, one of ordinary skill in the art realizes that methods and systems consistent with this invention may be used in a delay-locked loop (DLL) as well as a PLL. Further, clamping device mn9 may be replaced by a diode or a series of diodes. Still further, bipolar junction transistors (BJTs) may be used instead of MOS transistors. It is intended that the specification and examples be considered as exemplary only, with a true scope and spirit of the invention being indicated by the following claims.

What is claimed is:

- 1. A charge-pump circuit comprising:

- a first transistor for sinking a current from an output node;

- a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off; and

a current source to provide a turn-off current to a common node between the first transistor and the second transistor when the second transistor interrupts the sinking current.

2. The charge-pump circuit of claim 1, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source node of the first transistor.

3. The charge-pump circuit of claim 1, further comprising a clamping circuit to clamp the common node below a clamping voltage.

4. The charge-pump circuit of claim 3, wherein the clamping circuit comprises a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

5. The charge-pump circuit of claim 3, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source node of the first transistor.

6. A charge-pump circuit comprising:

a first transistor for sinking a current from an output node;

- a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off; and

- a clamping circuit to clamp a common node between the first transistor and the second transistor below a clamping voltage.

7. The charge-pump circuit of claim 6, wherein the clamping circuit comprises a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

8. A method for operating a charge-pump circuit, wherein the charge-pump circuit comprises a first transistor for sinking a current from an output node and a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off, wherein the method comprises:

providing a turn-off current to a common node between the first transistor and the second transistor when the second transistor interrupts the sinking current.

9. The method of claim 8, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turnoff current is provided to a source node of the first transistor. 10. The method of claim 8, further comprising

clamping the common node below a clamping voltage.

11. The method of claim 10, wherein clamping uses a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

12. The method of claim 10, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turnoff current is provided to a source node of the first transistor.

13. A method for operating a charge-pump circuit having a first transistor for sinking a current from an output node and a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off, wherein the method comprises:

14. The method of claim 13, wherein clamping uses a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

**15**. A charge-pump circuit comprising:

a first transistor to drive a current to an output node;

- a second transistor coupled between the first transistor and a power supply, wherein the second transistor interrupts the driving current when the second transistor is turned off: and

- a current source to provide a turn-off current to a common node between the first transistor and the second transistor when the second transistor interrupts the driving current

16. The charge-pump circuit of claim 15, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source of the MOS transistor.

17. The charge-pump circuit of claim 15, further comprising

a clamping circuit to clamp the common node above a clamping voltage.

18. The charge-pump circuit of claim 17, wherein the clamping circuit comprises a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

19. The charge-pump circuit of claim 17, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source of the MOS transistor.

**20**. A charge-pump circuit comprising:

a first transistor for driving a current to an output node;

- a second transistor coupled between the first transistor and a power supply, wherein the second transistor interrupts the driving current when the second transistor is turned off; and

- a clamping circuit to clamp a common node between the first transistor and the second transistor a clamping voltage.

21. The charge-pump circuit of claim 20, wherein the clamping circuit comprises a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

22. A method for operating a charge-pump circuit, wherein the charge-pump circuit comprises a first transistor for driving a current from an output node and a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the driving current when the second transistor is turned off, wherein the method comprises:

providing a turn-off current to a common node between the first transistor and the second transistor when the second transistor interrupts the driving current.

23. The method of claim 22, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turnoff current is provided to a source node of the first transistor.

## 24. The method of claim 22, further comprising

clamping the common node to above a clamping voltage. **25**. The method of claim 24, wherein clamping uses a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

**26**. The method of claim 24, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source node of the first transistor.

27. A method for operating a charge-pump circuit having a first transistor for driving a current from an output node and a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the driving current when the second transistor is turned off, wherein the method comprises:

clamping a common node between the first transistor and the second transistor above a clamping voltage.

**28**. The method of claim 27, wherein clamping uses a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

**29.** An apparatus for operating a charge-pump circuit, wherein the charge-pump circuit comprises a first transistor for sinking a current from an output node and a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off, wherein the apparatus comprises:

means for providing a turn-off current to a common node between the first transistor and the second transistor when the second transistor interrupts the sinking current.

**30**. The apparatus of claim 29, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source node of the first transistor.

**31**. The apparatus of claim 29, further comprising

means for clamping the common node below a clamping voltage.

**32**. The apparatus of claim 31, wherein the means for clamping uses a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

**33.** The apparatus of claim 31, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source node of the first transistor.

**34**. An apparatus for operating a charge-pump circuit having a first transistor for sinking a current from an output node and a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off, wherein the apparatus comprises:

means for clamping a common node between the first transistor and the second transistor below a clamping voltage.

**35**. The apparatus of claim 34, wherein the means for clamping uses a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

**36**. A phase-locked loop having a phase detector, a low pass filter, a voltage controlled oscillator, and a charge-pump circuit, wherein the charge pump circuit comprises:

a first transistor for sinking a current from an output node;

- a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off; and

- a current source to provide a turn-off current to a common node between the first transistor and the second transistor when the second transistor interrupts the sinking current.

**37**. The phase-locked loop of claim 36, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source node of the first transistor.

**38**. The phase-locked loop of claim 36, wherein the charge-pump circuit further comprises a clamping circuit to clamp the common node below a clamping voltage.

**39**. The phase-locked loop of claim 38, wherein the clamping circuit comprises a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

**40**. The phase-locked loop of claim 38, wherein the first transistor is a metal-oxide-semiconductor (MOS) transistor and the turn-off current is provided to a source node of the first transistor.

**41**. The phase-locked loop of claim 40, further including a divider circuit.

**42**. A phase-locked loop having a phase detector, a low pass filter, a voltage controlled oscillator, and a charge-pump circuit, wherein the charge pump circuit comprises:

a first transistor for sinking a current from an output node;

- a second transistor coupled between the first transistor and a ground node, wherein the second transistor interrupts the sinking current when the second transistor is turned off; and

- a clamping circuit to clamp a common node between the first transistor and the second transistor below a clamping voltage.

**43**. The phase-locked loop of claim 42, wherein the clamping circuit comprises a metal-oxide-semiconductor (MOS) transistor with a source coupled to ground, a drain coupled to the common node, and a gate coupled to the common node.

**44**. The phase-locked loop of claim **43**, further including a divider circuit.

\* \* \* \* \*