US010644650B2

### (12) United States Patent

### Chamas

### (54) AMPLIFIER CONFIGURATION FOR LOAD-LINE ENHANCEMENT

- (71) Applicant: Qualcomm Incorporated, San Diego, CA (US)

- (72) Inventor: **Ibrahim Ramez Chamas**, Carlsbad, CA (US)

- (73) Assignee: **QUALCOMM Incorporated**, San Diego, CA (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 16/138,811

- (22) Filed: Sep. 21, 2018

### (65) **Prior Publication Data**

US 2019/0097583 A1 Mar. 28, 2019

### **Related U.S. Application Data**

- (60) Provisional application No. 62/562,343, filed on Sep. 22, 2017.

- (51) Int. Cl.

| H03F 3/45  | (2006.01) |

|------------|-----------|

| H03F 1/02  | (2006.01) |

| H03F 3/213 | (2006.01) |

- (52) U.S. Cl.

## (10) Patent No.: US 10,644,650 B2

### (45) **Date of Patent:** May 5, 2020

(56) **References Cited**

U.S. PATENT DOCUMENTS

6,100,717 A 8/2000 May 7,449,950 B2 11/2008 Ivanov (Continued)

### OTHER PUBLICATIONS

Yuan-Hung Chung et al. "Dual-Band Integrated Wi-Fi PAs with Load-Line Adjustment and Phase Compensated Power Detector", MediaTek Inc., Hsinchu, Taiwan, 30078. R.O.C., 2015 pp. 223-228.

Primary Examiner — Steven J Mottola

(74) Attorney, Agent, or Firm — Holland & Hart LLP/Qualcomm Incorporated

### (57) **ABSTRACT**

Amplifier configuration for load-line enhancement is described herein. In some implementations, an apparatus includes an amplifier. The amplifier includes at least one plus transistor stack, at least one minus transistor stack, and at least one inductor. The at least one plus transistor stack is coupled to a plus amplifier node and a plus input node. The at least one minus transistor stack is coupled to a minus amplifier node and a minus input node. The at least one inductor is coupled between the plus amplifier node and the minus amplifier node, with the at least one inductor including an inter-inductor node. The amplifier also includes a minus power switch coupled between the minus amplifier node and one or more supply voltages and an inductor power switch coupled between the inter-inductor node and at least one supply voltage.

### 29 Claims, 15 Drawing Sheets

#### (56) **References** Cited

### U.S. PATENT DOCUMENTS

| 7,978,009    | B2   | 7/2011  | Mu                 |

|--------------|------|---------|--------------------|

| 8,570,106    | B2 * | 10/2013 | Kim H03F 1/223     |

|              |      |         | 330/260            |

| 9,584,076    | B2   | 2/2017  | Ortiz              |

| 10,141,891   | B2 * | 11/2018 | Gomez H03G 3/3042  |

| 2015/0357977 | A1*  | 12/2015 | Bonaccio H03B 5/10 |

|              |      |         | 331/117 FE         |

| 2017/0012653 | A1   | 1/2017  | Fong et al.        |

\* cited by examiner

200 Single-Ended Output 222 216 -1 VDD <u>228</u> - 218 220 -1 <u>236</u>  $I_{m}$ ٧+ V-~VDD 230 -VDD LVDD ٧-V+ VDD <u>232</u> <u>234</u> 210 -212 214 206 208  $2 \cdot I_m$  $2 \cdot I_m$ Vc ( $\langle \hat{\uparrow} \rangle$ Ŋ. <u>226</u> <u>224</u> Input B Input A 202 204 1 FIG. 2

600 -

Provide, with a voltage supply, a voltage supply signal to a differential amplifier, the differential amplifier including a first pair of transistors designed for a load line having a first impedance in a first amplifier configuration 1202

Configure, with amplifier configuration circuitry, the differential amplifier in a second amplifier configuration corresponding to the load line having a second impedance, the second impedance lower than the first impedance <u>1204</u>

> Disable, with the amplifier configuration circuitry, one transistor of the first pair of transistors 1206

Enable, with the amplifier configuration circuitry, at least one transistor of a second pair of transistors of the differential amplifier, the second pair of transistors being a complementary transistor type to the first pair of transistors, an enabled transistor of the second pair of transistors having a first terminal coupled to the voltage supply signal and a second terminal coupled to a first terminal of an additional transistor of the first pair of transistors

<u>1208</u>

Amplify, with the with the differential amplifier, an input signal with the differential amplifier in the second amplifier configuration with the load line having the first impedance 1210

FIG. 12

## FIG. 14

# FIG. 15

### AMPLIFIER CONFIGURATION FOR LOAD-LINE ENHANCEMENT

### CROSS-REFERENCE TO RELATED APPLICATION

This application claims the benefit of U.S. Provisional Application No. 62/562,343, filed 22 Sep. 2017, the disclosure of which is hereby incorporated by reference in its entirety herein.

### TECHNICAL FIELD

The present disclosure relates to signal usage with electronic devices and, more specifically, to managing the power consumption of an amplifier that can amplify a signal (e.g., for transmission from an electronic device) using amplifier reconfiguration.

### BACKGROUND

Electronic devices include traditional computing devices such as desktop computers, notebook computers, smartphones, wearable devices like a smartwatch, internet serv-25 ers, and so forth. However, electronic devices also include other types of computing devices such as personal voice assistants, thermostats, automotive electronics, robotics, devices embedded in other machines like refrigerators and industrial tools, medical devices, Internet of Things (IoT) 30 devices, and so forth. These various electronic devices provide services relating to productivity, remote communication, social interaction, security, health and safety, entertainment, transportation, and information dissemination. Thus, electronic devices play crucial roles in many aspects 35 of modern society.

Many of the services provided by electronic devices in today's interconnected world depend at least partly on electronic communications. Electronic communications include, for example, those exchanged between or among 40 different electronic devices using wireless or wired signals that are transmitted over one or more networks, such as the Internet or a cellular network. Electronic communications therefore include both wireless and wired transmissions and receptions. With wireless electronic communications, 45 mobile services can be enjoyed by users of electronic devices. With a smart phone, for example, mobile services can include voice and video calls, social media interactions, messaging, watching movies, sharing videos, performing searches, acquiring map information or navigational instruc- 50 tions, locating friends, transferring money, making reservations or purchasing tickets, obtaining another service like a car ride, monitoring health data, and so forth.

To participate in a wireless electronic communication, an electronic device uses a wireless communication compo-55 nent, such as a wireless transceiver. Electronic communications can therefore be realized by propagating signals between two wireless transceivers at two different electronic devices. For example, using a wireless transmitter, a smart phone can transmit a wireless signal to a base station over an 60 air medium as part of an uplink communication to support mobile services. Using a wireless receiver, the smart phone can receive a wireless signal from the base station via the air medium as part of a downlink communication to enable mobile services. Wireless transceivers, however, consume 65 power, which is limited with a portable or other batterypowered device. 2

Battery-powered talk-time represents how long a device can, on average, engage in a voice conversation before a battery's energy reserves are depleted. Thus, a longer talktime is better than a shorter talk-time, and many device manufacturers advertise the rated talk-time of each electronic device. One aspect of a wireless transceiver that consumes power during operation—for both voice calls and other wireless communications—is the amplifier. Amplifiers are used to increase a signal's strength, or amplitude, in many electronic devices. For instance, transmitters in mobile phones may include driver amplifiers and power amplifiers that supply a signal to an antenna during transmission operations and may include low-noise amplifiers (LNAs) that accept a received signal from the antenna during reception operations.

During times of wireless transceiver activity, amplifiers draw an appreciable level of power. This power draw can more quickly deplete the energy contained in a battery of a portable or other battery-powered device. Consequently, 20 electrical engineers and other designers of electronic devices strive to develop amplifiers for wireless transceivers that use less power and that can therefore extend talk-time usage, as well as battery life in general.

### SUMMARY

This summary is provided to introduce a selection of concepts in a simplified form that are further described below in the detailed description. This summary is not intended to identify key features or essential features of the claimed subject matter.

Various aspects of amplifier configuration for load-line enhancement are disclosed herein. In example aspects, an apparatus including an amplifier is described. The amplifier includes at least one plus transistor stack, at least one minus transistor stack, and at least one inductor. The at least one plus transistor stack is coupled to a plus amplifier node and a plus input node. The at least one minus transistor stack is coupled to a minus amplifier node and a minus input node. The at least one inductor is coupled between the plus amplifier node and the minus amplifier node, with the at least one inductor including an inter-inductor node. The amplifier also includes a minus power switch coupled between the minus amplifier node and one or more supply voltages and an inductor power switch coupled between the inter-inductor node and at least one supply voltage.

In example aspects, a system for load-line enhancement using amplifier reconfiguration is described. The system includes an amplifier, and the amplifier includes a plus array of transistors, a minus array of transistors, and at least one inductor. The plus array of transistors is coupled to a plus amplifier node and a plus input node, with the plus array of transistors including multiple plus transistor stacks. The minus array of transistors is coupled to a minus amplifier node and a minus input node, with the minus array of transistors including multiple minus transistor stacks. The at least one inductor is coupled between the plus amplifier node and the minus amplifier node, with the at least one inductor including an inter-inductor node. The amplifier also includes configuration means for configuring the amplifier into different amplifier configurations. The system also includes control means for controlling the configuration means to adjust an effective impedance of a load line of the amplifier, the control means coupled to the configuration means.

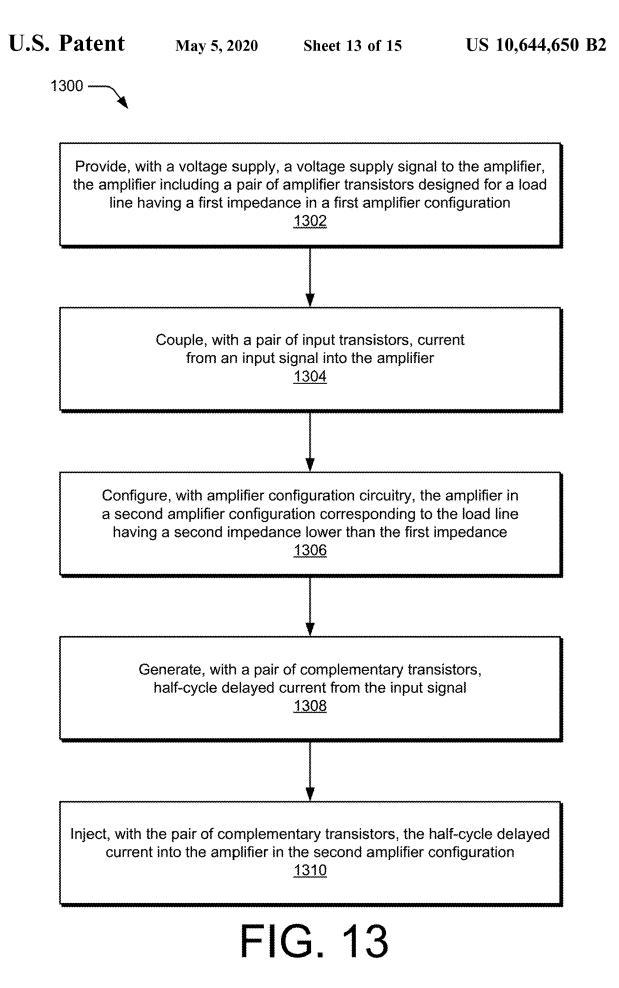

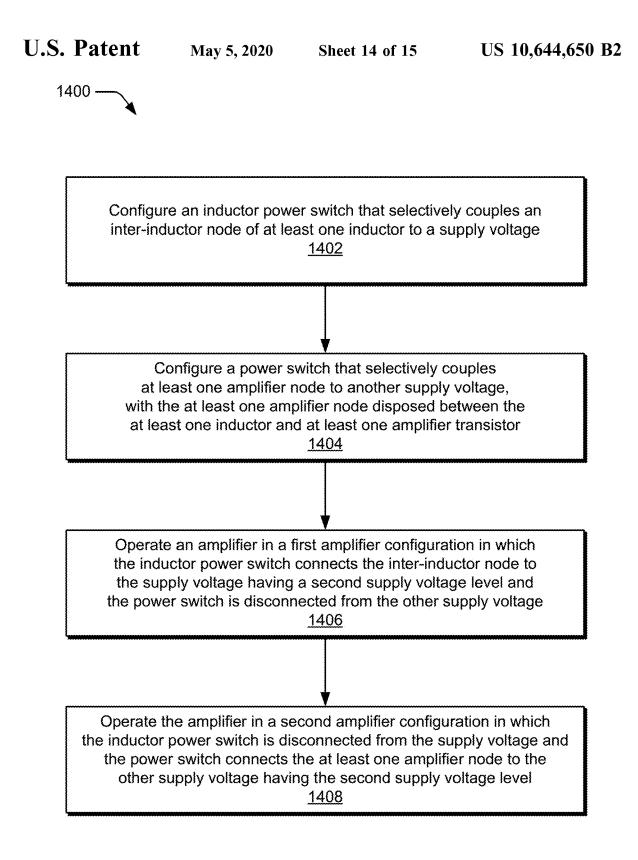

In example aspects, a method is described for amplifier configuration for load-line enhancement. The method

includes configuring an inductor power switch that selectively couples an inter-inductor node of at least one inductor to a supply voltage. The method also includes configuring a power switch that selectively couples at least one amplifier node to another supply voltage, with the at least one ampli-5 fier node disposed between the at least one inductor and at least one amplifier transistor. The method additionally includes operating an amplifier in a first amplifier configuration in which the inductor power switch connects the inter-inductor node to the supply voltage having a second 10 supply voltage level and the power switch is disconnected from the other supply voltage. The method further includes operating the amplifier in a second amplifier configuration in which the inductor power switch is disconnected from the supply voltage and the power switch connects the at least 15 one amplifier node to the other supply voltage having the second supply voltage level.

In example aspects, an apparatus including a differential amplifier is described. The differential amplifier includes a pair of input transistors and a pair of amplifier transistors. 20 The pair of input transistors is coupled to an equipotential node, with the pair of input transistors configured to receive a differential input signal. The pair of amplifier transistors is respectively coupled in series with the pair of input transistors. The pair of amplifier transistors is configured to 25 amplify the differential input signal. The pair of amplifier transistors have a load line with a first impedance in conjunction with the pair of input transistors in accordance with a first amplifier configuration. The differential amplifier also includes amplifier configuration circuitry coupled to the pair 30 of amplifier transistors. The differential amplifier further includes amplifier configuration control circuitry coupled to the amplifier configuration circuitry. The amplifier configuration control circuitry is configured to use the amplifier configuration circuitry to institute one or more other ampli- 35 fier configurations that respectively correspond to the load line of the pair of amplifier transistors having one or more other impedances by reconfiguring current flow in the differential amplifier.

In other example aspects, a method of operating a differ- 40 ential amplifier is described. The method includes providing a voltage supply signal to the differential amplifier, the differential amplifier including a first pair of transistors designed for a load line having a first impedance in a first amplifier configuration. The method also includes configur- 45 ing the differential amplifier in a second amplifier configuration corresponding to the load line having a second impedance that is less than the first impedance. Here, the configuring includes at least one of: disabling one transistor of the first pair of transistors or enabling at least one 50 transistor of a second pair of transistors of the differential amplifier, with the second pair of transistors of a complementary transistor type to the first pair of transistors. An enabled transistor of the second pair of transistors has a first terminal connected to the voltage supply signal and a second 55 terminal connected to a first terminal of an additional transistor of the first pair of transistors. The method further includes amplifying an input signal with the differential amplifier in the second amplifier configuration with the load line having the first impedance.

In other example aspects, an amplifier configured in a second amplifier configuration is described. The amplifier includes a first pair of transistors with a load line having a first impedance in a first amplifier configuration, with the first impedance being greater than a second impedance of 65 the load line corresponding to the second amplifier configuration. Each transistor of the first pair of transistors has

4

respective first terminals coupled to each other through at least one resistor. The amplifier also includes a second pair of transistors of a complementary transistor type to a first transistor type of the first pair of transistors, with the second pair of transistors deactivated in the first amplifier configuration. Each transistor of the second pair of transistors has a respective first terminal coupled to a voltage supply signal. a respective second terminal coupled to a respective third terminal of a respective transistor of the first pair of transistors, and a respective third terminal coupled to a respective component of a differential input signal to the amplifier. The amplifier further includes a third pair of transistors, with the third pair of transistors of the first transistor type. Each transistor of the third pair of transistors has a respective first terminal coupled to a respective second terminal of a respective transistor of the first pair of transistors, a respective second terminal coupled to a ground, and a respective third terminal coupled to a respective component of the differential input signal for the amplifier. Here, the first amplifier configuration includes the first pair of transistors and the third pair of transistors.

In other example aspects, a system for configuring an amplifier is described. The system includes a voltage supply for providing a voltage supply signal to the amplifier. The amplifier includes a pair of amplifier transistors designed for a load line having a first impedance in a first amplifier configuration. The system also includes one or more input transistors for coupling current from an input signal into the amplifier. The system also includes means for configuring the amplifier in a second amplifier configuration corresponding to the load line having a second impedance that is lower than the first impedance. The system further includes means for generating half-cycle delayed current from the input signal. Additionally, the system includes means for injecting the half-cycle delayed current into the amplifier in the second amplifier configuration.

The foregoing is a summary and thus contains, by necessity, simplifications, generalizations and omissions of detail; consequently, those skilled in the art will appreciate that the summary is illustrative only and does not purport to be limiting in any way. Other aspects, inventive features, and advantages of the devices and/or processes described herein, as defined solely by the claims, will become apparent in the non-limiting detailed description set forth herein.

### BRIEF DESCRIPTION OF DRAWINGS

The detailed description references the accompanying figures. In the figures, the left-most digit(s) of a reference number identifies the figure in which the reference number first appears. The use of the same reference numbers in different instances in the description and the figures may indicate similar or identical items.

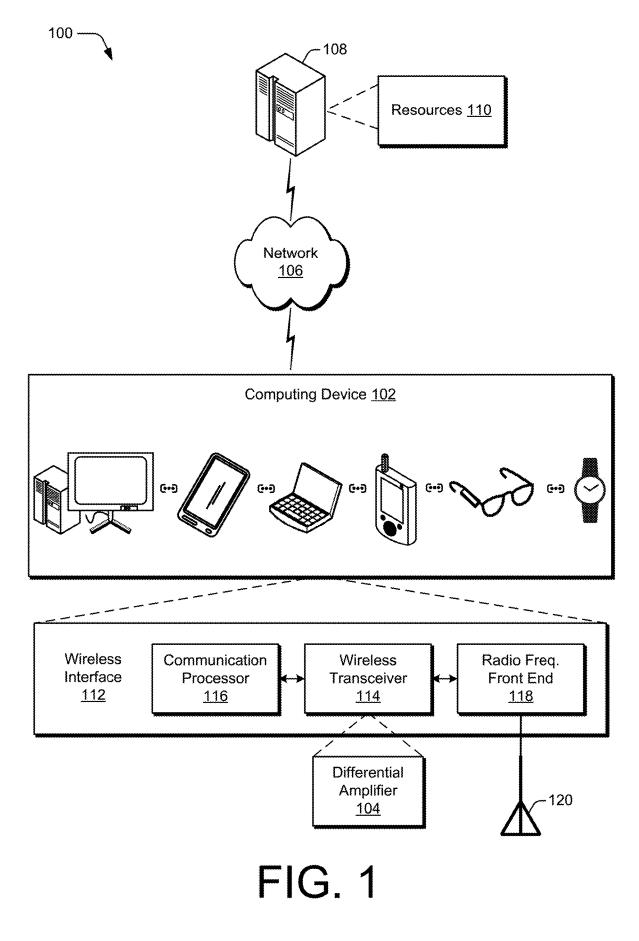

FIG. 1 illustrates an example environment that may include an amplifier in accordance with one or more aspects of the disclosure.

FIG. 2 illustrates, from a voltage and current perspective, 60 an example amplifier in a first circuit configuration in accordance with one or more aspects of the disclosure.

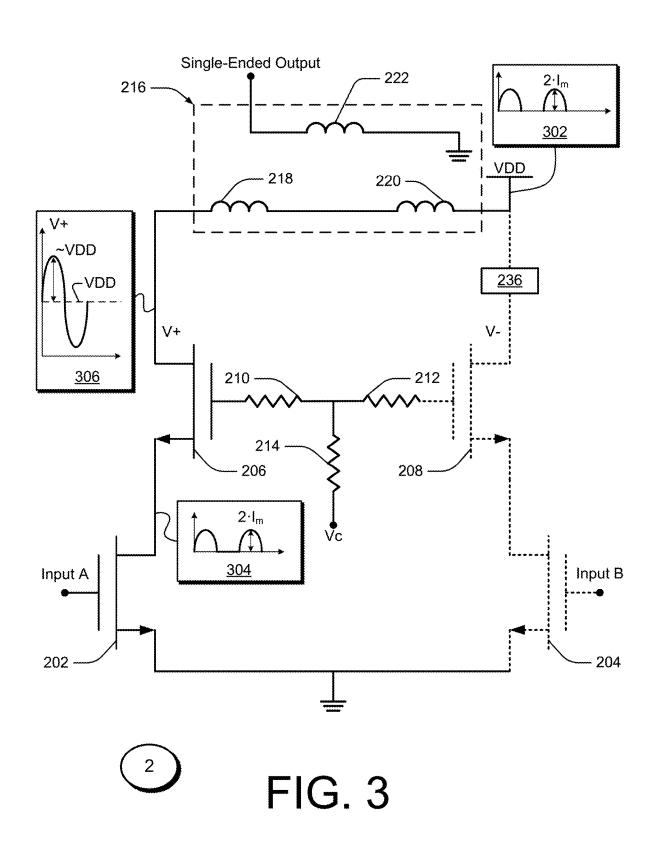

FIG. **3** illustrates, from a voltage and current perspective, an example amplifier in a second circuit configuration in accordance with one or more aspects of the disclosure.

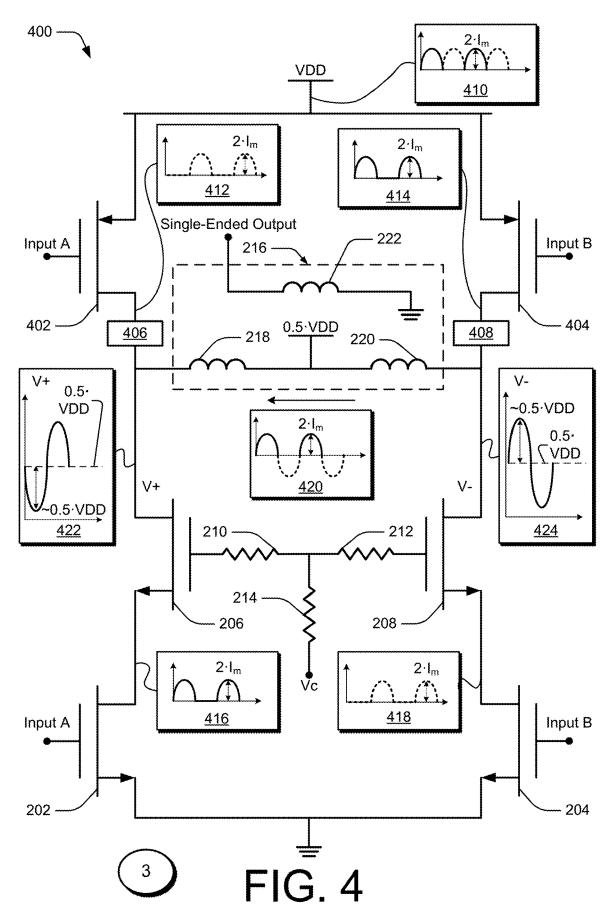

FIG. 4 illustrates, from a voltage and current perspective, an example amplifier in a third circuit configuration in accordance with one or more aspects of the disclosure.

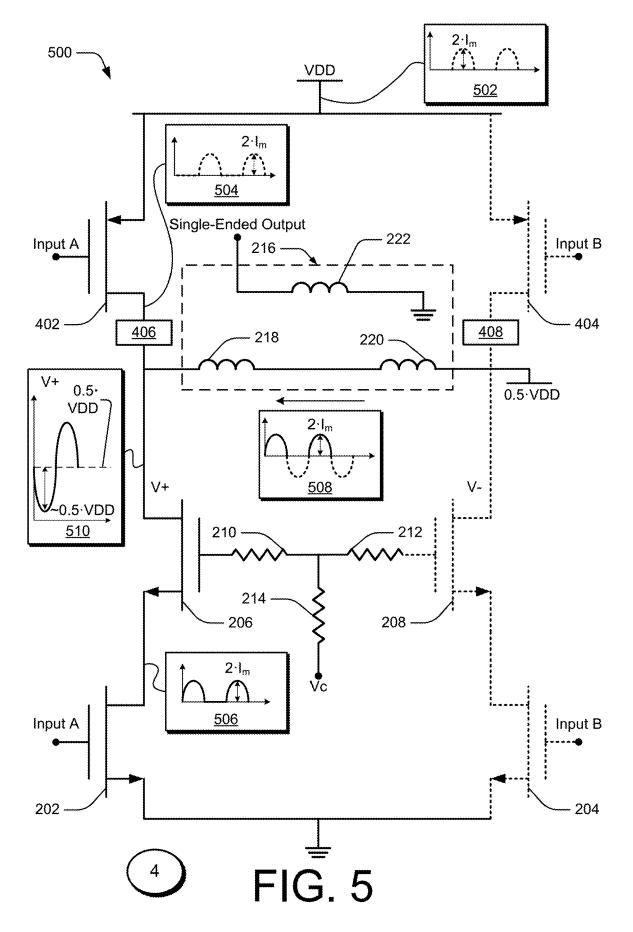

FIG. 5 illustrates, from a voltage and current perspective, an example amplifier in a fourth circuit configuration in accordance with one or more aspects of the disclosure.

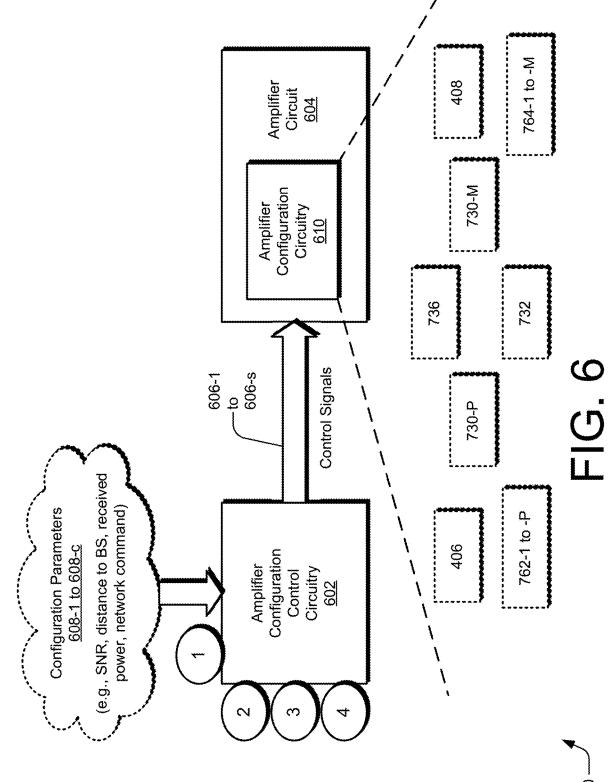

FIG. 6 illustrates an example system in which an amplifier can be operated in different configurations responsive to one 5 or more control signals in accordance with one or more aspects of the disclosure.

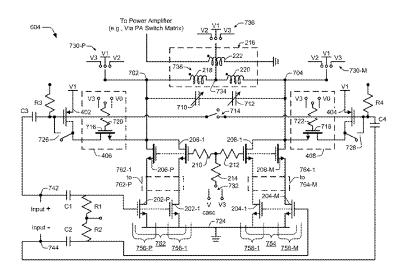

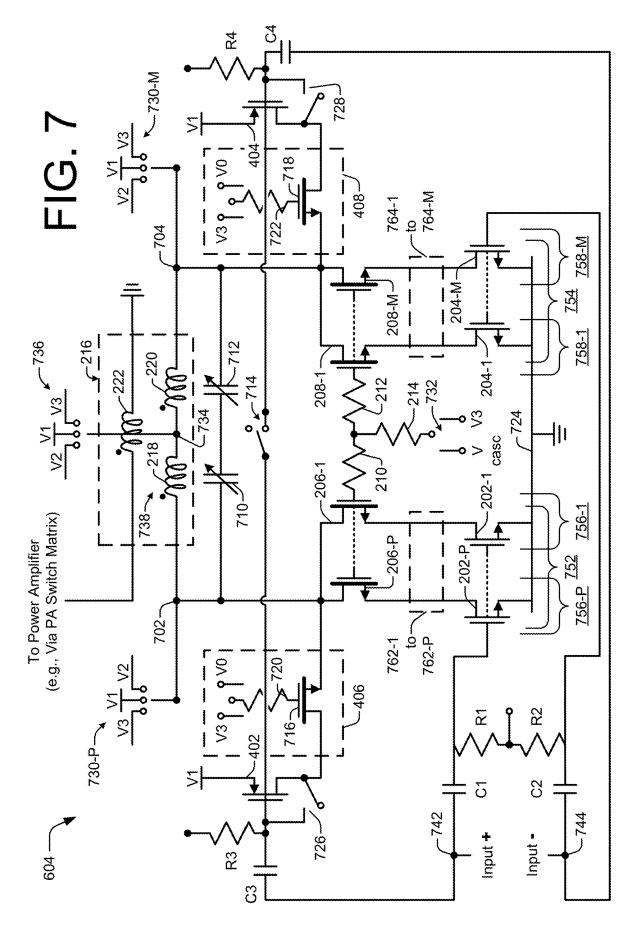

FIG. 7 illustrates, from a circuit perspective, an example amplifier circuit that can be activated into different configurations using one or more switches in accordance with one 10 or more aspects of the disclosure.

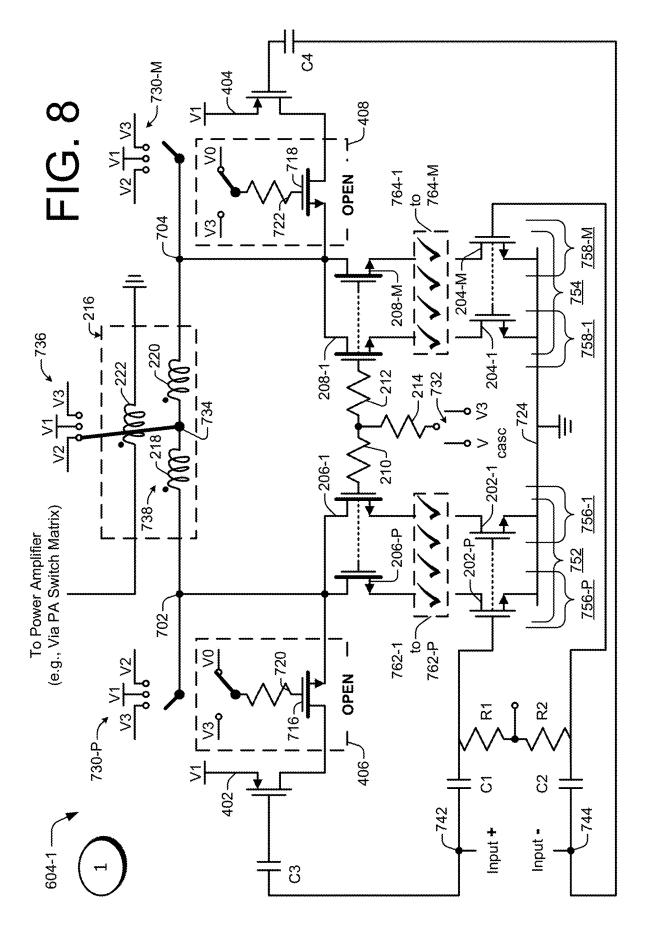

FIG. 8 illustrates, from a circuit control perspective, an example amplifier circuit in the first amplifier configuration in accordance with one or more aspects of the disclosure.

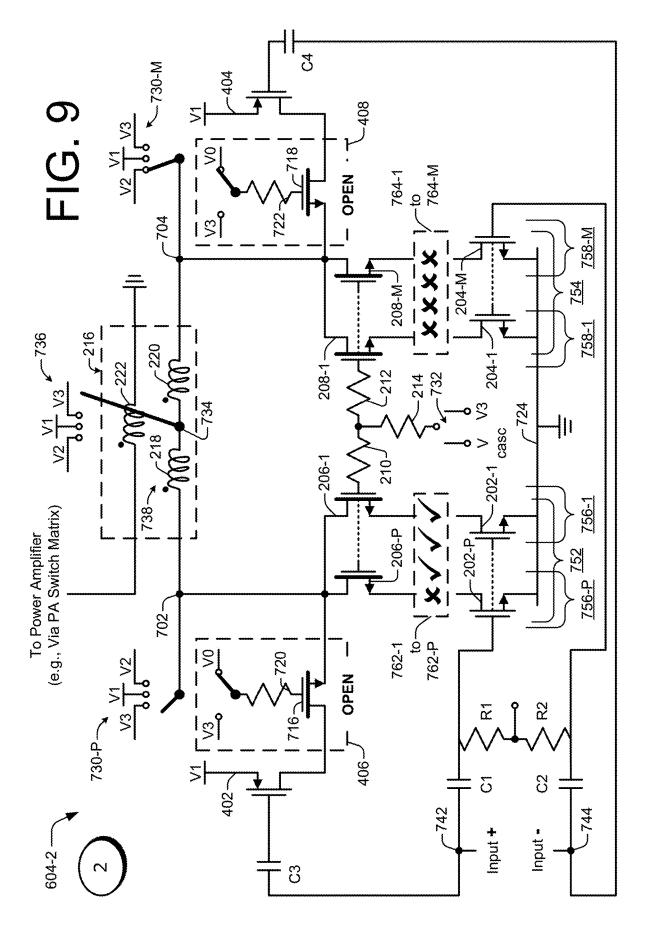

FIG. 9 illustrates, from a circuit control perspective, an 15 example amplifier circuit in the second amplifier configuration in accordance with one or more aspects of the disclosure.

FIG. 10 illustrates, from a circuit control perspective, an example amplifier circuit in the third amplifier configuration 20 in accordance with one or more aspects of the disclosure.

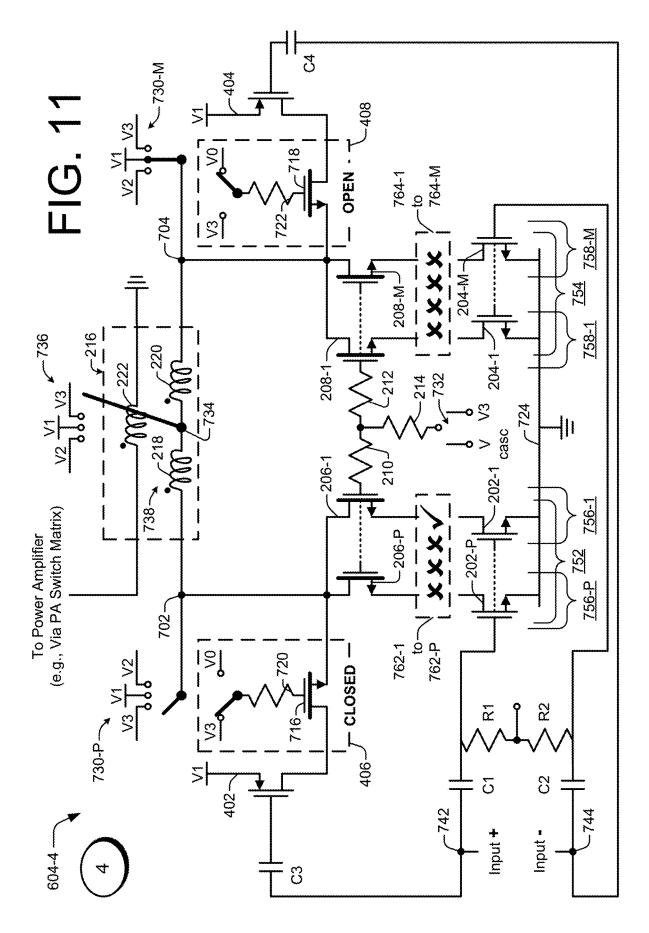

FIG. 11 illustrates, from a circuit control perspective, an example amplifier circuit in the fourth amplifier configuration in accordance with one or more aspects of the disclosure

FIG. 12 is a flow diagram depicting an example procedure in accordance with one or more aspects of the disclosure.

FIG. 13 is a flow diagram depicting an example procedure in accordance with one or more aspects of the disclosure.

FIG. 14 is a flow diagram depicting an example procedure 30 in accordance with one or more aspects of the disclosure.

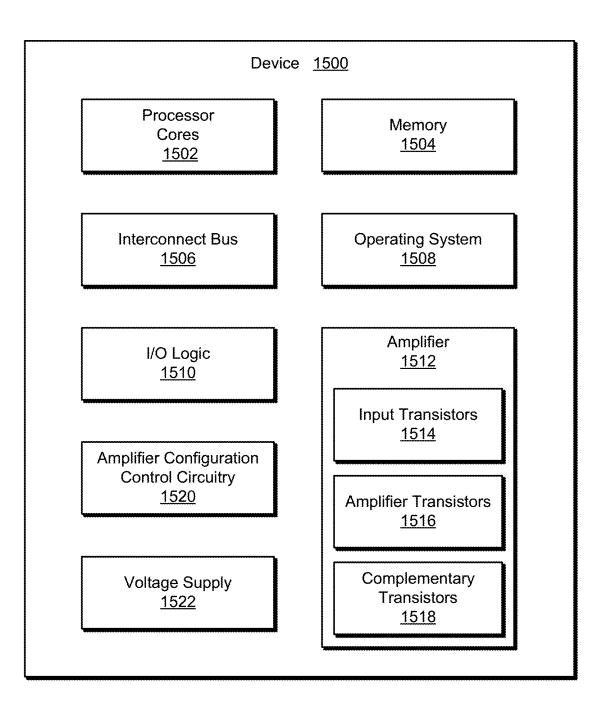

FIG. 15 illustrates an example electronic device that can be employed for one or more implementations described herein.

### DETAILED DESCRIPTION

A common performance metric of a transmitter in a smart phone or other portable wireless electronic device is talktime current consumption of a battery at a prescribed 40 antenna power, which is usually indicative of an average antenna power. This antenna power translates to an operating power for a transceiver supplying a signal to an antenna of the smart phone. The load line of an amplifier in the transceiver, however, is usually designed for maximum 45 transceiver power, and this maximum transceiver power is greater than the operating power at which battery talk-time current consumption is measured for the transceiver. Consequently, an impedance of the load line of the amplifier is generally lower than desired when battery talk-time current 50 consumption is measured.

Several approaches can be adopted to improve the talktime current consumption. First, a quantity of amplifier units (e.g., transistors) that are enabled in an amplifier during signal transmission can be reduced. Second, a voltage sup- 55 ply that is provided to the enabled amplifier units when the mobile device is transmitting can be reduced. Although these approaches can help to reduce the current consumed by the amplifiers that are part of a signal transmission uplink chain, further current reduction is usually desired to extend 60 battery life for all-day use or with heavy-duty signal transmission demands.

Thus, it is desirable to adopt another approach to further reduce power consumption during signal transmission. One such approach is the modulation of the load line of an 65 amplifier when a portable electronic device is transmitting. Power is proportional to the square of the current flowing

6

through the load line and directly proportional to the impedance of the load line. Consequently, if the effective impedance of the load line can be increased, the current can be decreased while achieving the same power. For example, if the effective impedance of the load line can be increased by a factor of four during transmission, then the current can be halved with no change in the power delivered by the amplifier.

Accordingly, approaches to load line modulation attempt to increase the effective impedance of the load line of an amplifier. For example, switches can be used to switch output matching networks into the amplifier circuitry to increase the impedance of the load line. Such output matching networks include inductors and capacitors. Unfortunately, inductors and capacitors do not scale in size proportionally to process dimension (e.g., they do not follow Moore's law). As a result, in circuits built using modern process technologies, it is not uncommon for an inductor to comprise half the area of an integrated circuit. Furthermore, switches connected to inductors degrade the quality of the inductors due to leakage currents and losses of the switches that occur during interaction with the inductors.

A few other approaches can be utilized to change the effective impedance of a load line, but each is associated with one or more drawbacks. For example, multiple devices, such as transformers, that are selectively enabled to achieve a desired impedance of the load line can be used. However, multiple transformers consume too much area to be practical, and they usually need to be spatially separated on the integrated circuit, which exacerbates the area problem. Furthermore, disabling a transformer usually involves shorting the primary inductance of the transformer, which allows current to flow and reduces the effective impedance of the load line. Still other approaches add a significant amount of 35 hardware, such as auxiliary amplifiers to modulate the impedance of the load line, phase shifters, quarter-wave transmission lines, and so forth. Besides adding cost, these other approaches are impractical for implementations in portable electronic devices that place a premium on small size and low power consumption.

In contrast, this disclosure describes methods and circuits for configuring an amplifier in at least one amplifier configuration in which the expected load line impedance is less than what is actually implemented by reconfiguring current flows within the amplifier using one or more switches. Consequently, current can be reduced for a given amount of power that is to be delivered by the amplifier. The use of expensive inductors and capacitors for impedance matching can be avoided.

In some implementations, an amplifier, such as a differential amplifier, can be reconfigured into multiple configurations-e.g., a first amplifier configuration, a second amplifier configuration, a third amplifier configuration, and a fourth amplifier configuration. The differential amplifier includes a pair of amplifier transistors designed for and implemented with a given load line impedance in the first amplifier configuration is reconfigured to the third amplifier configuration that enables a pair of complementary transistors (e.g., transistors that are of a complementary transistor type to the amplifier transistors) to operate as part of the differential amplifier in the third amplifier configuration. Differential inputs are provided to both the complementary transistors and a pair of input transistors of the differential amplifier. Thusly configured, the complementary transistors inject half-cycle-delayed current into the amplifier to reconfigure and increase the current in the amplifier. Because the current in the amplifier is increased in the third amplifier

Example Environment

configuration (as compared to the first amplifier configuration), the corresponding impedance of the load line for the amplifier in the third amplifier configuration is less than the impedance of the load line as actually implemented. Accordingly, because the amplifier is operated in a configuration 5 that has a greater impedance than what the amplifier "expects" to see, the current drawn from the supply voltage by the amplifier can be reduced for the same amount of power delivered by the amplifier across the first and third amplifier configurations. Talk-time current consumption can 10 therefore be decreased.

Additionally or alternatively, a differential amplifier is configured in the second amplifier configuration (e.g., that is different from the first amplifier configuration for which the load line of the amplifier was designed) by disabling transistors on one of the differential sides of the amplifier. The reconfigured amplifier changes the expected impedance of the amplifier by reconfiguring current within the amplifier. For the fourth amplifier configuration, a differential amplifier that includes a pair of complementary transistors (e.g., 20 like the third amplifier configuration) can be reconfigured by disabling transistors on one of the differential sides of the amplifier.

In aspects as described herein, a reconfigurable amplifier can be converted between two or more different amplifier 25 configurations by changing states of one or more switches (e.g., by opening or closing switches). Under the control of amplifier configuration control circuitry, at least one of these switches can selectively couple different parts of a differential amplifier to different supply voltages. Additionally or 30 alternatively, at least one of these switches can selectively couple a transistor of a pair of complementary transistors to enable the complementary transistor to operate as part of the differential amplifier. In these manners, a differential amplifier can be reconfigured by changing current flows to adjust 35 an apparent impedance from a voltage and current perspective, which can enable decreased power usage.

Accordingly, the disclosed methods and circuits can avoid adopting approaches that add output matching networks or other expensive hardware (e.g., transformers, inductors, 40 capacitors, phase shifters, quarter-wave transmission lines, and so forth) to modulate the impedance of a load line in an amplifier. Instead, in accordance with certain aspects, lowpower complementary transistors and amplifier configuration circuitry (e.g., switches) are included with a reconfigu- 45 rable amplifier without changing the implemented impedance of the load line (e.g., without swapping electromagnetic (EM) components of the amplifier output). Furthermore, the low-power complementary transistors and amplifier configuration circuitry scale with semiconductor 50 geometry (e.g., they follow Moore's Law), and they therefore consume relatively little chip area. Consequently, the methods and circuits described herein are well-suited for implementations in mobile devices that place a premium on small size and low power consumption.

In the following discussion, example systems including amplifiers and amplifier configuration circuitry are described. Techniques that components of the example system may implement, and a computing device on which elements of the example system may be included, are also 60 described. Consequently, performance of the example procedures is not limited to the example system, and the example system is not limited to performance of the example procedures. Any reference made with respect to the example system, or components thereof, is by way of 65 example only and is not intended to limit any of the aspects described herein. 8

FIG. 1 illustrates an example environment 100 in accordance with one or more aspects of the disclosure. The example environment 100 includes a computing device 102. The computing device 102 may be configured as any suitable type of computing device (e.g., a mobile device, a fixed device, or a wireless electronic device). For example, the computing device 102 may be configured as a server, a server farm, a desktop computer, a laptop computer, a workstation, a mobile device, a tablet, a mobile phone (e.g., a smart phone), a personal digital assistant, a router, a modem, a gateway, a camera, a gaming station, a wearable device (e.g., a smart wristwatch or smart eyeglasses), smart appliance, medical device, vehicle-based communication system, Internet-of-Things (IoT) device, smart-home or security device, wireless power device, and so forth. Thus, the computing device 102 may range from a full-resource device with substantial memory and processor resources (e.g., servers and personal computers) to a low-resource device with limited memory or processing resources (e.g., wearable devices). Additionally, the computing device 102 may be representative of a plurality of different devices, such as multiple devices in a server farm of a service provider, or a single computing device, such as an end-user device.

The computing device **102** is illustrated as including a differential amplifier **104** as part of a wireless transceiver **114**. The wireless transceiver **114** can be part of a wireless interface **112**. The wireless interface **112** can include a communication processor **116** and a radio-frequency front end **118** (RFFE **118**), in addition to the wireless transceiver **114**. However, the computing device **102** can also include a variety of other components, which are not shown in FIG. **1** for simplicity. For example, the computing device **102** can include one or more processing devices, one or more computer-readable storage media, and various applications (e.g., a web browser which is operable to access various kinds of web-based resources from cloud servers) embodied on the computer-readable storage media and operable via a processing system.

In some implementations, the wireless interface 112 of the computing device 102 provides connectivity to respective networks and peer devices via a wireless link. Alternatively or additionally, the computing device 102 may include a wired interface, such as an Ethernet or fiber optic transceiver for communicating over a wired local network, an intranet, or the Internet. The wireless interface 112 may facilitate communication over any suitable type of wireless network, such as a wireless local area network (LAN) (WLAN), peer-to-peer (P2P) network, mesh network, cellular network, wireless wide-area-network (WWAN), and/or wireless personal-area-network (WPAN). In the context of the example environment 100, the computing device 102 communicates various data and control information via the 55 wireless interface 120 to a remote device, which may be part of a base station (not explicitly shown) or an internet server, for example. The computing device 102 may also communicate directly with peer devices and the like.

As shown, the wireless interface **112** includes the communication processor **116**, the wireless transceiver **114**, and the RFFE **118** to process data and signals associated with communicating data of the computing device **102** over one or more antennas **120**. The communication processor **116** may generally be realized as a modem (e.g., a baseband modem), as a digital signal processor (DSP), or as a communications-oriented processing unit that is configured to perform signal processing to support communication via one or more networks. The communication processor **116** may be implemented as a system on-chip (SoC) that provides a digital communication interface for data, voice, messaging, and other applications of the computing device **102**. The communication processor **112** may also include baseband 5 circuitry to perform high-rate sampling processes that can include analog-to-digital conversion (ADC), digital-to-analog conversion (DAC), gain correction, skew correction, frequency translation, and so forth.

Further, the communication processor **112** may include 10 logic to perform in-phase/quadrature (I/Q) operations, such as synthesis, encoding, modulation, demodulation, and decoding. Alternatively, ADC or DAC operations may be performed by a separate component or another illustrated component, such as the wireless transceiver **114**. Addition-15 ally, the communication processor **116** may also manage (e.g., control or configure) aspects or operation of the transceiver **114**, the RFFE **118**, or other components of the wireless interface **112** to implement various communication processor **116** can control reconfiguration of the differential amplifier **104** as described herein.

The wireless transceiver **114** includes circuitry and logic for filtering, amplification, channelization, and frequency translation, which may be an up-conversion or down-con-25 version of frequency, which is performed in a single conversion or through multiple conversion steps. The wireless transceiver **114** can also include a digital-to-analog converter (DAC) that converts digital values to an analog signal for amplification and filtering by circuitry of the wireless 30 transceiver **114** or an analog-to-digital converter (ADC) to convert analog signals to digital values for communication processing.

The components or circuitry of the wireless transceiver **114** can be implemented in any suitable fashion, such as 35 combined transceiver logic or separately as respective receiver and transmitter entities. In some cases, the wireless transceiver **114** is implemented with multiple or different sections to implement respective receiving and transmitting operations (e.g., separate receive and transmit chains). The 40 wireless transceiver **114** may also include logic to perform in-phase/quadrature (I/Q) operations, such as synthesis, phase correction, modulation, demodulation, and the like.

The RFFE **118** can include filters, switches, and amplifiers for conditioning signals received via the antenna **120** or 45 signals to be transmitted via the antenna **120**. The RFFE **118** may also include other RF sensors and components, such as a peak detector, power meter, gain control block, antenna tuning circuit, diplexer, balun, and the like. Configurable components of the RFFE **118** may be controlled by the 50 communication processor **116** to implement communications in different modes or frequency bands or in accordance with different wireless standards.

The wireless transceiver **114** may include one or more amplifiers. Examples of amplifiers include low-noise ampli-55 fiers (LNAs) (e.g., for a receive chain) and driver or power amplifiers (e.g., for a transmit chain). Any one or more of these or other types of amplifiers, that are part of a wireless transceiver **114** or that are included elsewhere in a computing device **102**, may be implemented as a differential ampli-60 fier, such as the differential amplifier **104**. Thus, the differential amplifier **104** can be implemented as any suitable type of differential amplifier and can be implemented for any suitable purpose in the computing device **102**. In one example, the differential amplifier **104** comprises a driver 65 amplifier for a power amplifier that supplies a signal to the antenna **120** during transmission, such as during a telephone

call on a mobile phone. The differential amplifier **104** can provide an amplified signal (e.g., a pre-amplified signal) to a switch matrix that selects an appropriate power amplifier from multiple power amplifiers, such as power amplifiers for different bandwidths, operating frequencies, and communications protocols. Additionally or alternatively, the differential amplifier **104** can comprise a low-noise amplifier that accepts a signal received by the computing device **102** via the antenna **120**.

The example environment 100 also includes a network 106 and one or more devices 108 that are communicatively coupled to the computing device 102 via the network 106. The one or more devices 108 can operate as, for instance, one or more service providers configured to make various resources 110 available over the network 106 to one or more clients (e.g., the computing device 102). In some scenarios, users may sign up for accounts that are employed to access corresponding resources from a provider. The provider may authenticate credentials of a user (e.g., a username and password) before granting access to an account and corresponding resources. Resources 110 may be licensed, purchased, or made freely available (e.g., without authentication, license, or account-based access). Resources 110 can include any suitable combination of services and content made available over the network 106, such as a videoediting service, a photo-editing service, a web development and management service, a collaboration service, a social networking service, a messaging service, an advertisement service, a conferencing service, a telephone service, and so forth. Content may include various combinations of assets, including videos, ads, audio, multi-media streams, animations, images, web documents, web pages, applications, device applications, text documents, text messages, drawings, presentations, files (e.g., configuration files and device driver files), maps, and the like.

In one example, the one or more devices **108** comprise one or more cell phones, and the network **106** comprises a cellular network that enables a user of the computing device **102** to participate in a conversation (e.g., sharing audio, video, text, data, or combinations thereof) with one or more respective users of the one or more devices **108**. The network **106**, however, may include a variety of networks, including the Internet, an intranet, a local area network (LAN), a wide area network (WAN), a personal area network (PAN), a body area network (BAN), one or more cellular networks, one or more terrestrial networks, a satellite network, combinations of networks, and the like, and as such may be wired, wireless, or a combination thereof.

Although the network 106 and the one or more devices 108 are illustrated in FIG. 1 separately from the computing device 102, the computing device 102 may form a part of the network 106 or the one or more devices 108. Further, the one or more devices 108 may also include one or more differential amplifiers that are similar or analogous to the differential amplifier 104. Consequently, the techniques and circuits described herein may be practiced with any suitable differential amplifier, such as a differential amplifier 104 that can be part of the one or more devices 108 or a component of the network 106.

Having considered an example environment **100**, consider now a discussion of example amplifier circuits.

Example Amplifier Circuits from a Voltage and Current Perspective

Example aspects of the disclosure use a differential amplifier, such as in a class-B fashion with half-wave rectified signals, that is designed for a first impedance load line in a first amplifier configuration. Aspects of the disclosure reconfigure the differential amplifier in other amplifier configurations corresponding to the load line having different impedances that are less than the first impedance from a voltage and current perspective. By operating the amplifier 5 in the other configurations with the load line having the first impedance rather than the other, lower impedances, the impedance of the load line "seen" by the amplifier is greater than what is "expected" by the amplifier. Thus, for a given transmit power level, lower current levels can be used such 10 that less power is consumed.

In some implementations, the amplifier is configured in a second amplifier configuration by disabling transistors on one of the differential sides of the amplifier. In a third amplifier configuration, the amplifier is configured by acti- 15 vating a pair of complementary transistors that are included as part of, or are coupled to, the differential amplifier. In a fourth amplifier configuration, the amplifier is configured by both activating a pair of complementary transistors of the differential amplifier and disabling transistors on one of the 20 differential sides of the differential amplifier. The reconfigured amplifier changes the effective impedance of the amplifier (e.g., the impedance of the load line that the amplifier expects to see in a respective amplifier configuration) by reconfiguring current within the amplifier, as is explained 25 below.

In accordance with some implementations, four different load line impedances can exist, or be created, for a differential amplifier. In general,  $2^N$  different load line impedances can be realized, where "N" is the number of signal phases, 30 and N=2 corresponds to a differential signal. By way of example, differential amplifiers are described herein with two signal phases. However, amplifiers with any suitable number of signal phases can be constructed using aspects of reconfiguring amplifiers for load-line enhancement as 35 described herein. Accordingly, although differential amplifiers are described herein by way of example, amplifiers implementing aspects of the disclosure are not limited to differential amplifiers, for they can be implemented using any suitable number of phases, such as 2, 4, or 8. 40

Consider next a discussion of examples of each of four amplifier configurations for an example differential amplifier from a voltage and current perspective. The first amplifier configuration includes a pair of amplifier transistors and a pair of input transistors (e.g., coupled together in a cascode 45 arrangement). In a second amplifier configuration, two individual transistors (one transistor from each pair of transistors) are disabled during some operations, such as during talk time. A third amplifier configuration includes a pair of complementary transistors respectively coupled to each pair 50 of the cascode-arranged transistors. A fourth amplifier configuration includes the complementary transistors but disables three individual transistors (one transistor from each of the three pairs of transistors). Although some of the description in this paragraph (e.g., the precise quantities of transis- 55 tors) pertains to differential amplifier implementations with two amplifier transistors and two input transistors, the principles are applicable to other implementations having banks of amplifier and input transistors as described below. First Amplifier Configuration from a Voltage and Current 60 Perspective

FIG. 2 illustrates an example first amplifier configuration 200 in accordance with one or more aspects of the disclosure. The example first amplifier configuration 200 is an example implementation of the differential amplifier 104 in 65 FIG. 1. The circuit of the first example amplifier configuration 200 includes a pair of input transistors 202 and 204

and a pair of amplifier transistors 206 and 208. The amplifier transistors 206 and 208 are respectively coupled in series with the input transistors 202 and 204-e.g., in a cascode arrangement. The input transistors 202 and 204 and the amplifier transistors 206 and 208 can be implemented as any suitable type of transistor, such as a metal-oxide-semiconductor field-effect transistor (MOSFET), a junction fieldeffect transistor (JFET), metal-semiconductor field-effect transistor (MESFET), a bipolar junction transistor (BJT), and so forth. These four transistors can operate in any suitable type of mode, such as depletion mode or enhancement mode, and can be constructed as n-channel or p-channel. The input transistors 202 and 204 and the amplifier transistors 206 and 208 are illustrated in FIG. 2 as n-channel metal-oxide-semiconductor (NMOS) FET transistors for example purposes.

A differential input signal applied to the example amplifier circuit of the first amplifier configuration 200 includes two components, Input A and Input B, that are supplied to respective terminals of the input transistors 202 and 204 (e.g., respective gates of the input transistors 202 and 204). For instance, Input A can represent a positive or plus input, and Input B can represent a negative or minus input. The input transistors 202 and 204 have respective other terminals (e.g., sources) coupled to ground (e.g., any suitable equipotential node). The input transistors 202 and 204 also have respective additional terminals (e.g., drains) coupled to respective terminals (e.g., sources) of the amplifier transistors 206 and 208, respectively.

Other respective terminals (e.g., gates) of the amplifier transistors 206 and 208 are resistively coupled through a resistor network including resistor 210, resistor 212, and resistor 214. The resistors 210, 212, and 214 can have any suitable resistor values. In one example, the resistor 210 and the resistor 212 are a same nominal resistance, such as 12 ohms, and the resistor 214 is a larger resistance, such as 14.7 kilo-ohms. A control voltage  $V_c$  is supplied, such as from a voltage supply circuit (not shown), to one terminal of the resistor 214 to suitably bias the amplifier transistors 206 and 40 208. The control voltage  $V_c$  can be set to any suitable voltage. In one example, the control voltage  $V_c$  is set to 1.8 volts. In another example, the control voltage  $V_c$  is set to 1.0 volts. The control voltage  $V_c$  can be set to different voltages using, for instance, at least one switch (e.g., as shown in FIG. 7). The amplifier transistors 206 and 208 amplify the differential signals coupled via the input transistors 202 and 204 according to a supply voltage  $V_{DD}$  to form differential outputs V<sup>+</sup> and V<sup>-</sup>. Respective additional terminals (e.g., drains) of the amplifier transistors 206 and 208 couple the differential outputs V<sup>+</sup> and V<sup>-</sup> to differential inputs of a differential-to-single-ended converter 216.

The differential-to-single-ended converter **216** receives the differential outputs V<sup>+</sup> and V<sup>-</sup> and converts them to a single-ended output with inductors **218**, **220**, and **222**. The inductors **218** and **220** are coupled together in series between respective terminals (e.g., drains) of the amplifier transistors **206** and **208**. The supply voltage  $V_{DD}$  is provided, such as from a voltage supply circuit of the illustrated amplifier circuit, between the inductor **218** and the inductor **220**. The inductors **218** and **220** are electromagnetically coupled to the inductor **222**. The single-ended output of the differential-to-single-ended converter **216** is provided on one end of the inductor **222**, and the other end of the inductor **222** is grounded.

In example operation, the signals in the first amplifier configuration **200** are half-wave rectified (e.g., in a class-B fashion), and the two phases of the current in the first

amplifier configuration 200 are shown in solid and dashed lines, respectively, in the inlays 224, 226, 228, and 230. For instance, current represented by dashed lines is half-cycle delayed relative to current represented by solid lines. Inlays **224** and **226** illustrate currents on the respective drains of the input transistors 202 and 204, and inlay 228 illustrates current provided by the supply voltage  $V_{DD}$ . The peak value of the current (e.g., the swing) in these inlays has a value of  $2 \cdot I_m$  current units (for any suitable unit of current, such as milli-amps (mA)). For the half-rectified current having a 10 peak of  $2 \cdot I_m$  current units, a differential current flowing through the amplifier transistors 206 and 208 (e.g., the difference between a current flowing through the amplifier transistor 206 and a current flowing through the amplifier transistor 208) has a peak value (or swing) of  $I_m$  current units (e.g., the fundamental component of the Fourier transform of the current has a value of  $I_m$ ), as illustrated in inlay 230.

The differential output voltages V<sup>+</sup> and V<sup>-</sup> of the amplifier transistors **206** and **208** are illustrated in inlays **232** and **234**, respectively. The differential output voltages V<sup>+</sup> and V<sup>-</sup> are 20 centered at approximately the supply voltage V<sub>DD</sub>. Furthermore, neglecting the saturation voltage of the amplifier transistors **206** and **208**, each of the differential output voltages V<sup>+</sup> and V<sup>-</sup> has a peak voltage of approximately the supply voltage V<sub>DD</sub>. The peak of the differential voltage, 25 defined as the peak of V<sup>+</sup>-V<sup>-</sup>, is therefore:

### $V_{diff,pk} = 2 \cdot V_{DD}$ .

The impedance of the load line can be represented by the ratio of the peak of the differential voltage  $V_{diff,pk}$  to the differential current flowing through the amplifier transistors **206** and **208**. Accordingly, the impedance of the load line for the first amplifier configuration **200** (which is defined as R) is given by:

$$\frac{2 \cdot V_{DD}}{I_m} = R.$$

The amplifier transistors 206 and 208 are designed and 40 built to provide this load line impedance, at a specified power level. If the amount of current flowing through the amplifier transistors 206 and 208 can be increased in a modified version of the amplifier circuit depicted in FIG. 2, the desired impedance of the load line in that modified 45 configuration will be reduced. Switch 236 is an example of amplifier configuration circuitry that can be used to reconfigure the example amplifier circuit of FIG. 2 and modulate the load line, as discussed in more detail below. By using one or more of the amplifier transistors 206 and 208 in a 50 modified amplifier configuration that "expects" to see a load line having a lower impedance than R but that is actually implemented with a load line having the impedance of R, the actual impedance of the load line "seen" by the amplifier transistors 206 and 208 in the modified configuration of the 55 amplifier is greater than what is expected in that configuration. Accordingly, for the same output power, the current provided by the supply voltage  $V_{DD}$  to the amplifier can be reduced by an amount equal to the square root of the reduction in impedance, thus improving talk-time current 60 consumption.

In one example, the impedance R is based on the voltage supply signal  $V_{DD}$ , as described above. Additionally or alternatively, the impedance R can be based on (e.g., designed for) a voltage other than the voltage supply signal  $65 V_{DD}$ , such as a higher voltage than the voltage supply signal  $V_{DD}$ .

Having considered a discussion of the example first amplifier configuration **200**, consider now another example amplifier circuit representing a second amplifier configuration.

Second Amplifier Configuration from a Voltage and Current Perspective

FIG. 3 illustrates an example second amplifier configuration 300 in accordance with one or more aspects of the disclosure. The example second amplifier configuration 300 is another example configuration of the differential amplifier 104 in FIG. 1. The circuit of the example second amplifier configuration 300 includes the input transistor 202 and the amplifier transistor 206 in an active mode or enabled state as described with respect to FIG. 2. However, unlike with the circuit of FIG. 2, the example second amplifier configuration 300 in FIG. 3 disables one side of the differential amplifier by disabling one transistor of each pair of transistors (e.g., one input transistor and one amplifier transistor as shown). For instance, the input transistor 204 and the amplifier transistor 208 are illustrated in FIG. 3 with dashed lines to denote that the input transistor 204 and the amplifier transistor 208 are disabled to operationally decouple them from the amplifier circuit in the second amplifier configuration 300. The input transistor 204 and the amplifier transistor 208 can be disabled in any suitable way, such as with amplifier configuration circuitry containing switches that disconnect the input transistor 204 or the amplifier transistor 208 from the illustrated circuit. This disconnection can be accomplished, for example, by setting appropriate bias voltages, by using control voltages (such as  $V_c$ ), or combinations thereof. Switch 236 is an example of a switch that can be included in the amplifier configuration circuitry to disable the input transistor 204 and the amplifier transistor 208.

Further, although the minus side of the example second amplifier configuration **300** is illustrated in FIG. **3** as being disabled, the plus side can alternatively be disabled. The plus side can be disabled by, for example, disabling the input transistor **202** or the amplifier transistor **206** with respect to the remainder of the example amplifier circuit instead of disabling the input transistor **204** and the amplifier transistor **208**.

In FIG. 3, the supply voltage  $V_{DD}$  is connected to a different end of the inductor 220—e.g., at an external node of the differential-to-single-ended converter 216, instead of at an internal node between the inductor 220 and the inductor 218 as shown in FIG. 2. Further, the current provided by the supply voltage  $V_{DD}$  is illustrated in inlay 302. As illustrated by inlay 302, because one side of the differential amplifier is disabled, the half-cycle delayed current is omitted. For instance, inlay 304 shows the current at the drain of the input transistor 202. Inlay 304 shows the same current flow as inlay 224 in FIG. 2. However, because the input transistor 204 is disabled, there is no appreciable current in FIG. 3, for the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is substantially zero at the drain of the input transistor 204 (e.g., the current is current is the right or minus amplifier branch being disabled).

Similarly, because the amplifier transistor **208** is disabled, the component of the output voltage V<sup>-</sup> generated by the amplifier transistor **208** is substantially zero, and FIG. **3** therefore has no inlay for the output voltage V<sup>-</sup>. The component of the output voltage V<sup>+</sup> generated by the amplifier transistor **206**, however, is determined at least partially by the supply voltage V<sub>DD</sub> and is illustrated in the inlay **306**. The component of the output voltage V<sup>+</sup> is centered at approximately the supply voltage V<sub>DD</sub>, and, neglecting the saturation voltage of the amplifier transistor 206, has a peak voltage of approximately the supply voltage  $V_{DD}$ .

The peak of the differential voltage  $V^+-V^-$  for the example second amplifier configuration 300 is therefore  $V_{diff,pk} = V_{DD}$ . The differential current flowing through the amplifier transistor 206 retains a value of  $I_m$  current units (e.g., the fundamental component of the Fourier transform of the current has a value of I<sub>m</sub>). Hence, the "desired" impedance of the load line for the second amplifier configu-10 ration 300 is:

$$\frac{V_{DD}}{I_m} = R/2.$$

This R/2 impedance is the desired impedance because it is the ratio of the peak of the differential voltage to the differential current flowing in the example amplifier circuit 20 for the second amplifier configuration 300.

Although the desired impedance of the load line is R/2 for the second amplifier configuration 300, the amplifier transistors 206 and 208 are designed and built to provide a load line impedance of R. Accordingly, the example second 25 amplifier configuration 300 "sees" an impedance of the load line that is twice what is "expected." Consequently, the current supplied to the amplifier by the voltage supply  $V_{DD}$ for the example second amplifier configuration 300 in FIG. 3 can be reduced by  $\sqrt{2}$  for the same power delivered by the 30 amplifier as compared to the example first amplifier configuration 200 in FIG. 2.

Having considered a discussion of the example second amplifier configuration 300, consider now another amplifier circuit representing an example third amplifier configura- 35 tion.

Third Amplifier Configuration from a Voltage and Current Perspective

FIG. 4 illustrates an example third amplifier configuration **400** in accordance with one or more aspects of the disclo- 40 sure. The example third amplifier configuration 400 can be implemented with the differential amplifier 104 in FIG. 1. The example third amplifier configuration 400 can reconfigure current in the amplifier circuit by injecting half-cycle delayed current into the amplifier to achieve an "expected" 45 impedance of the load line corresponding to R/4.

The circuit of the example third amplifier configuration 400 includes the input transistors 202 and 204 and the amplifier transistors 206 and 208 in an active mode or enabled state as described with reference to FIG. 2. How- 50 ever, unlike the example first amplifier configuration 200 of FIG. 2, the example third amplifier configuration 400 in FIG. 4 additionally includes complementary transistors 402 and 404. The complementary transistors 402 and 404 are respectively coupled in series with the amplifier transistors 206 and 55 208 via respective switches 406 and 408. The pair of complementary transistors 402 and 404 are disposed between the amplifier transistors 206 and 208 and the supply voltage signal  $V_{DD}$ . The complementary transistors 402 and 404 are of a complementary transistor type with respect to 60 the amplifier transistors 206 and 208 and the input transistors 202 and 204.

For instance, the amplifier transistors 206 and 208 and the input transistors 202 and 204 in FIG. 4 are illustrated as n-channel metal-oxide-semiconductor (NMOS) devices, and the complementary transistors 402 and 404 are illustrated as PMOS devices. The complementary transistors 402 and 404

can be any suitable type of complementary transistor to the amplifier transistors 206 and 208 and the input transistors 202 and 204, such as a MOSFET, JFET, MESFET, BJT, and the like. Further, the complementary transistors 402 and 404 can operate in any suitable type of mode, such as depletion mode or enhancement mode, and can be n-channel or p-channel.

The complementary transistors 402 and 404 have respective terminals (e.g., gates) supplied with the same differential components of the input signal (e.g., Input A and Input B, respectively) as the respective gates of the input transistors 202 and 204. The complementary transistors 402 and 404 have respective other terminals (e.g., sources) coupled  $_{15}\,$  to the supply voltage  $V_{DD}.$  The complementary transistors 402 and 404 are selectively coupled to the amplifier transistors 206 and 208, respectively, by way of additional terminals (e.g., drains) of the complementary transistors 402 and 404 being coupled to the switches 406 and 408.

Because the complementary transistors 402 and 404 are of a complementary transistor type as the input transistors 202 and 204, the complementary transistors 402 and 404 inject current that is a half-cycle delayed relative to the current provided from the input transistors 202 and 204, respectively. For instance, an inlay 410 shows the current supplied by the supply voltage  $V_{DD}$ . The current injected from the complementary transistors 402 and 404 is illustrated in inlays 412 and 414, respectively. The current from the input transistors 202 and 204 is illustrated in inlays 416 and 418, respectively. Inlays 416 and 418 show the same current flows as inlays 224 and 226 in FIG. 2, respectively. In the inlays showing current in FIG. 4, the two phases of the current in the example third amplifier configuration 400 are shown in solid and dashed lines. For instance, current represented by dashed lines is half-cycle delayed relative to current represented by solid lines.

The current injected by the complementary transistor 402 illustrated in inlay 412 is half-cycle delayed compared to the current from the input transistor 202 illustrated in inlay 416. On the other side of the amplifier, the current injected by the complementary transistor 404 illustrated in inlay 414 is half-cycle delayed compared to the current from the input transistor 204 illustrated in inlay 418. Consequently, the differential current flowing through the amplifier transistors 206 and 208 is doubled relative to the amplifier configuration in FIG. 2, so the differential current has a peak value of  $2 \cdot I_m$  rather than  $I_m$ , as illustrated in inlay 420.

Moreover, the amplifier transistors 206 and 208 in the example third amplifier configuration 400 are coupled to  $0.5 \cdot V_{DD}$  via the internal node (which is also referred to herein as an inter-inductor node) of the differential-tosingle-ended converter 216, with the internal node being located between the inductor 218 and the inductor 220. As shown, the drain terminals of the amplifier transistors 206 and  $\mathbf{208}$  are coupled to  $0.5 \cdot \mathrm{V}_{DD}$  via the inductors  $\mathbf{218}$  and 220, respectively. By coupling the transistors to the supply voltage  $0.5 \cdot V_{DD}$  in this manner, the NMOS and PMOS transistors are symmetric, and no appreciable current flows through the internal node between the inductors 218 and 220. As a result of this supply-voltage coupling (e.g., at  $0.5 \cdot V_{DD}$ ) at the drains of the amplifier transistors 206 and 208, the differential output voltages  $V^+$  and  $V^-$  are centered at approximately half the supply voltage,  $0.5 \cdot V_{DD}$ . Further, neglecting the saturation voltage of the amplifier transistors 206 and 208, each of the differential output voltages V<sup>+</sup> and V<sup>-</sup> has a peak voltage (e.g., voltage swing) of approximately

50

half the supply voltage, or  $0.5 \cdot V_{DD}$ , as illustrated in inlays 422 and 424. The peak of the differential voltage,  $V^+-V^-$ , is therefore:

$V_{diff,pk} = V_{DD}$ .

The "desired" impedance of the load line for the example third amplifier configuration 400 is thus:

$$\frac{V_{DD}}{2 \cdot I_m} = R/4.$$

This impedance of R/4 is the desired impedance because it is the ratio of the peak of the differential voltage to the differential current flowing in the circuit of the example third 15 amplifier configuration 400.

Although the desired impedance of the load line is R/4 for this third amplifier configuration, the amplifier transistors 206 and 208 are designed and built to provide a load line impedance of R. Accordingly, the amplifier circuit config- 20 ured according to FIG. 4 "sees" an impedance of the load line that is quadruple what is "expected." Accordingly, the current can be reduced by  $\sqrt{4}$ , or a factor of two, for the same power as compared to the example first amplifier configuration 200 in FIG. 2.

Furthermore, the complementary transistors 402 and 404 can be selectively activated to create the example third amplifier configuration 400, such as during uplink transmission with a receiving entity that is closer, using the switches 406 and 408. The switches 406 and 408 can isolate the 30 amplifier transistors 206 and 208 from voltage supply signals of a semiconductor chip on which the amplifier circuit is disposed. The switches 406 and 408 can be any suitable type of switch. In one example, the switches 406 and 408 include transistor switches, such as a switch constructed 35 from a PMOS transistor. A gate of the transistor switch can be appropriately biased to enable and disable the transistor switch, such as by setting the gate to 0 volts and 1.8 volts, respectively. The bias voltage applied to the transistor switch can be resistively coupled (e.g., applied with a series resis- 40 tor) to the gate of the transistor switch. Moreover, the complementary transistors 402 and 404 can be implemented as low power transistors, so the additional power drawn by the complementary transistors 402 and 404 is small relative to the current reduction achieved by utilizing the example 45 third amplifier configuration 400.

Having considered a discussion of the example third amplifier configuration 400, consider now another amplifier circuit representing an example fourth amplifier configuration.

Fourth Amplifier Configuration from a Voltage and Current Perspective

FIG. 5 illustrates an example fourth amplifier configuration 500 in accordance with one or more aspects of the disclosure. The example fourth amplifier configuration 500 55 is an example configuration of the differential amplifier 104 in FIG. 1. A circuit for the example fourth amplifier configuration 500 includes the input transistor 202, the amplifier transistor 206, and the complementary transistor 402 in an active mode or enabled state as described with respect to 60 FIG. 4. However, unlike the configuration depicted in FIG. 4, the example fourth amplifier configuration 500 in FIG. 5 disables one side of the differential amplifier by disabling one transistor of each pair of transistors in a manner analogous to that described for the second amplifier configuration 65 300 of FIG. 3. For instance, the input transistor 204, the amplifier transistor 208, and the complementary transistor

404 are illustrated in FIG. 5 with dashed lines to denote that amplifier configuration circuitry disables the input transistor 204, the amplifier transistor 208, and the complementary transistor 404 to operationally decouple them from the example amplifier circuit. The amplifier configuration circuitry includes the switches 406 and 408 that selectively connect and disconnect the complementary transistors 402 and 404 from the amplifier and input transistors. The amplifier configuration circuitry may also include other like 10 switches (not shown) and control signals or control voltages (e.g., the control voltage  $V_c$ ) for setting appropriate bias voltages in the example fourth amplifier configuration 500.

Further, although the negative or minus side of the example fourth amplifier configuration 500 is illustrated in FIG. 5 as being disabled, the positive or plus side can alternatively be disabled. The plus side can be disabled by, for example, operationally disconnecting the input transistor 202, the amplifier transistor 206, and the complementary transistor 402 from the example amplifier circuit, instead of the input transistor 204, the amplifier transistor 208, and the complementary transistor 404.

The current provided by the supply voltage  $V_{DD}$  is illustrated in an inlay 502. As illustrated by inlay 502, because one side of the differential amplifier is disabled, one phase of the current is omitted, while the other phase remains. Inlays 504 and 506 show the current at the drains of the complementary transistor 402 and the input transistor 202, respectively. However, because the transistors on the minus side of the example fourth amplifier configuration 500 are disabled, their current is substantially zero and thus no inlays are shown in FIG. 5 for the minus side of the example amplifier circuit. The differential current flowing through the amplifier transistor 206 retains a value of  $2 \cdot I_m$  current units as indicated in inlay 508 (e.g., the fundamental component of the Fourier transform of the current has a value of  $2 \cdot I_m$ ).

Moreover, the supply voltage  $0.5 \cdot V_{DD}$  in the example fourth amplifier configuration 500 in FIG. 5 is connected to a different end of the inductor 220-e.g., at an external node of the differential-to-single-ended converter 216 (which is also referred to herein as the minus amplifier node), instead of at an internal node between the inductor 220 and the inductor 218, as shown in FIG. 4. Based on the supply voltage being set this way, the component of the output voltage V<sup>+</sup> is centered at approximately half the supply voltage, or  $0.5 \cdot V_{DD}$ . Neglecting the saturation voltage of the amplifier transistor 206, the output voltage  $V^+$  has a peak voltage (e.g., voltage swing) of approximately half the supply voltage, or  $0.5 V_{DD}$ , as illustrated in inlay 510. The peak of the differential voltage,  $V^+-V^-$ , is therefore:

$$V_{diff,pk} = 0.5 \cdot V_{DD}$$

.

Consequently, the "desired" impedance of the load line for the fourth amplifier configuration 500 is:

$$\frac{0.5 \cdot V_{DD}}{2 \cdot I_m} = R/8.$$

This R/8 impedance is the desired impedance because it is the ratio of the peak of the differential voltage to the differential current flowing in the example amplifier circuit for the fourth amplifier configuration 500.

Although the desired impedance of the load line is R/8 for this fourth amplifier configuration, the amplifier transistors 206 and 208 are designed and built to provide a load line impedance of R. Accordingly, the amplifier circuit configured according to FIG. 5 "sees" an impedance of the load

line that is eight times what is "expected." Thus, the current can be reduced by  $\sqrt{8}$  for the same power as compared to the example first amplifier configuration **200** in FIG. **2**.

Accordingly, the example circuits described can avoid including output matching networks or other hardware (e.g., 5 transformers, inductors, capacitors, phase shifters, or quarter-wave transmission lines) to modulate the impedance of a load line in an amplifier. Instead, complementary transistors and amplifier configuration circuitry (e.g., switches) are added to an amplifier circuit to enable reconfigurability, and these components consume relatively low power and do not need to change the implemented impedance of the load line. Rather, the amplifiers and amplifier configurations described herein operate to modulate the effective impedance of the load line by reconfiguring current so that the "expected" load line impedance in the modified amplifier configuration is less than the actual load line impedance implemented in the amplifier. No inductors, capacitors, matching networks, or transformers need to be added to the amplifier circuit to modulate the effective impedance of the load line by recon- 20 figuring current, unlike with existing approaches. Thus, in some aspects, the example circuits described herein modulate the effective impedance of the load line without modifying the amplifier transistors 206 and 208. Furthermore, the low-power complementary transistors and the devices of the 25 amplifier configuration circuitry can scale with semiconductor geometry (e.g., they follow Moore's Law), and they therefore consume relatively little chip area as compared to EM components. Consequently, the example circuits described herein are well-suited for implementations in 30 mobile devices that place a premium on small size and low power consumption. Hence, the example circuits described herein can save power without relying on output matching networks or other costly hardware to modulate the impedance of a load line in an amplifier.

Configurable Amplifier from a Circuit Perspective

FIG. 6 illustrates an example system 600 in which an amplifier can be operated in accordance with one or more aspects of the disclosure. As shown, the system 600 includes amplifier configuration control circuitry 602 and an ampli-40 fier circuit 604, which can realize the differential amplifier 104 of FIG. 1. The amplifier circuit 604 includes amplifier configuration circuitry 610. In example implementations, the amplifier configuration switches. Such configuration switches 45 can include the switches 406 and 408 (as well as the switch 236) that are described above. Further, such configuration switches of the amplifier configuration circuitry 610 can include switches 730, 732, 736, 762, and/or 764. These configuration switches are described below starting with 50 FIG. 7.

In operation, the amplifier configuration control circuitry 602 controls the amplifier circuit 604 to enter or activate an amplifier configuration of multiple different amplifier configurations (e.g., the encircled 1, 2, 3, and 4 for the first, 55 second, third, and fourth amplifier configurations, respectively). To cause the amplifier circuit 604 to activate a particular amplifier configuration, the amplifier configuration control circuitry 602 provides one or more control signals 606-1 to 606-s to the amplifier configuration cir- 60 cuitry 610 of the amplifier circuit 604, with "s" representing a positive integer. The one or more control signals 606-1 to 606-s can cause, for example, configuration switches to operate such that the switches are opened, closed, etc. so that currents are prevented from flowing or permitted to flow, 65 respectively. Thus, a control signal 606 can be coupled, for instance, to a gate terminal of an FET that is configured as

a switch. The control signal **606** can cause the FET switch to have an open state or a closed state by turning the FET off or on, respectively. Examples of configuration switches of the amplifier configuration circuitry **610** are shown in the lower portion of FIG. **6** and correspond to, for instance, switches depicted in FIGS. **7-11**.

The amplifier configuration control circuitry 602 can generate the multiple control signals 606-1 to 606-s based on one or more of multiple configuration parameters 608-1 to 608-c, with "c" representing a positive integer. Examples of a configuration parameter 608 include a signal-to-noise ratio (SNR), a distance to a base station (or other wireless device party to a wireless communication), a received power, a bit error rate (BER), beamforming usage, a present bandwidth versus a targeted bandwidth, a network command, and combinations thereof. For instance, responsive to a distance to a base station, the amplifier configuration control circuitry 602 can generate at least one control signal 606 to establish states of the configuration switches of the amplifier configuration circuitry 610. Accordingly, power usage can be reduced as the distance to the base station decreases-e.g., by progressing through the first to the fourth example amplifier configurations as a computing device approaches a base station.

The amplifier configuration control circuitry **602** can include at least one processor and computer-readable storage media (CRSM), which stores computer-executable instructions. The processor and the CRSM can be localized at one module or one integrated circuit chip or can be distributed across multiple modules or chips of an electronic device. Together, a processor and associated instructions can be realized in separate circuitry, fixed logic circuitry, hard-coded logic, and so forth. The amplifier configuration control circuitry **602** can be implemented as part of the wireless interface **112**, the communication processor **116**, logic of the wireless transceiver **114**, a general-purpose processor, some combination thereof, and so forth.