US012048221B2

# (12) United States Patent Kim et al.

## (54) DISPLAY DEVICE AND MANUFACTURING METHOD THEREOF

(71) Applicant: **Samsung Display Co., LTD.**, Yongin-si

(72) Inventors: Young Gu Kim, Yongin-si (KR); Chang Hee Lee, Yongin-si (KR); Yun Hee Park, Yongin-si (KR); Ji Yun Park, Yongin-si (KR); Bong Sung Seo,

Yongin-si (KR); Baek Kyun Jeon, Yongin-si (KR); Kyung Seon Tak,

Yongin-si (KR)

(73) Assignee: SAMSUNG DISPLAY CO., LTD.,

Yongin-si (KR)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35 U.S.C. 154(b) by 391 days.

(21) Appl. No.: 17/567,368

(22) Filed: Jan. 3, 2022

(65) **Prior Publication Data**

US 2022/0375996 A1 Nov. 24, 2022

(30) Foreign Application Priority Data

May 18, 2021 (KR) ...... 10-2021-0064382

(51) **Int. Cl.** *H10K 59/38 H10K 50/858*(2

(2023.01) (2023.01)

(Continued)

(Continued)

## (10) Patent No.: US 12,048,221 B2

(45) **Date of Patent:**

Jul. 23, 2024

### (58) Field of Classification Search

CPC .... H10K 59/38; H10K 50/858; H10K 59/121; H10K 59/122; H10K 50/865;

(Continued)

## (56) References Cited

## U.S. PATENT DOCUMENTS

8,405,063 B2 3/2013 Kazlas et al. 10,923,538 B2 2/2021 Lee et al. (Continued)

### FOREIGN PATENT DOCUMENTS

KR 10-2020-0003209 1/2020 KR 10-2020-0121430 10/2020

Primary Examiner — Bac H Au

(74) Attorney, Agent, or Firm — KILE PARK REED & HOUTTEMAN PLLC

## (57) ABSTRACT

A display device may include a substrate including a display area and a non-display area; and a plurality of pixels disposed in the display area, the plurality of pixels each including an emission area and a non-emission area. Each of the plurality of pixels may include at least one light emitting element in the emission area; a first pixel electrode and a second pixel electrode electrically connected to the at least one light emitting element; a bank including a first opening corresponding to the emission area; a color conversion layer disposed in the emission area to correspond to the at least one light emitting element; a barrier layer disposed on the bank and the color conversion layer; and a low refractive layer disposed on the barrier layer. The barrier layer may include silicon oxide (SiO<sub>x</sub>) having cured polysilazane.

### 20 Claims, 26 Drawing Sheets

| (51) | Int. Cl.    |                                          |

|------|-------------|------------------------------------------|

|      | H10K 59/121 | (2023.01)                                |

|      | H10K 59/122 | (2023.01)                                |

|      | H10K 71/00  | (2023.01)                                |

|      | H10K 59/12  | (2023.01)                                |

| (52) | U.S. Cl.    |                                          |

| ` ′  | CPC         | H10K 59/122 (2023.02); H10K 71/00        |

|      |             | (2023.02); <i>H10K 59/1201</i> (2023.02) |

|      |             |                                          |

(58) Field of Classification Search

CPC .. H10K 59/124; H10K 59/126; H10K 50/844;

H01L 33/504; H01L 2933/0025; H01L

33/44; H01L 2933/005

See application file for complete search history.

#### (56) **References Cited**

## U.S. PATENT DOCUMENTS

| 11,626,575   | B2 *          | 4/2023  | Baek H10K 50/844 257/40 |

|--------------|---------------|---------|-------------------------|

| 2020/0407627 | A1            | 12/2020 | Zhou et al.             |

| 2021/0011342 | $\mathbf{A}1$ | 1/2021  | Chen et al.             |

| 2023/0041748 | A1*           | 2/2023  | Tak H01L 33/24          |

| 2023/0121816 | A1*           | 4/2023  | Kim H01L 33/505         |

|              |               |         | 257/419                 |

| 2023/0155077 | A1*           | 5/2023  | Park H01L 25/167        |

|              |               |         | 257/318                 |

| 2023/0187583 | A1*           | 6/2023  | Baek H01L 27/156        |

|              |               |         | 257/79                  |

| 2023/0255083 | A1*           | 8/2023  | Jeon H10K 59/38         |

|              |               |         | 257/40                  |

| 2023/0335575 | A1*           | 10/2023 | Lee H01L 33/24          |

|              |               |         |                         |

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

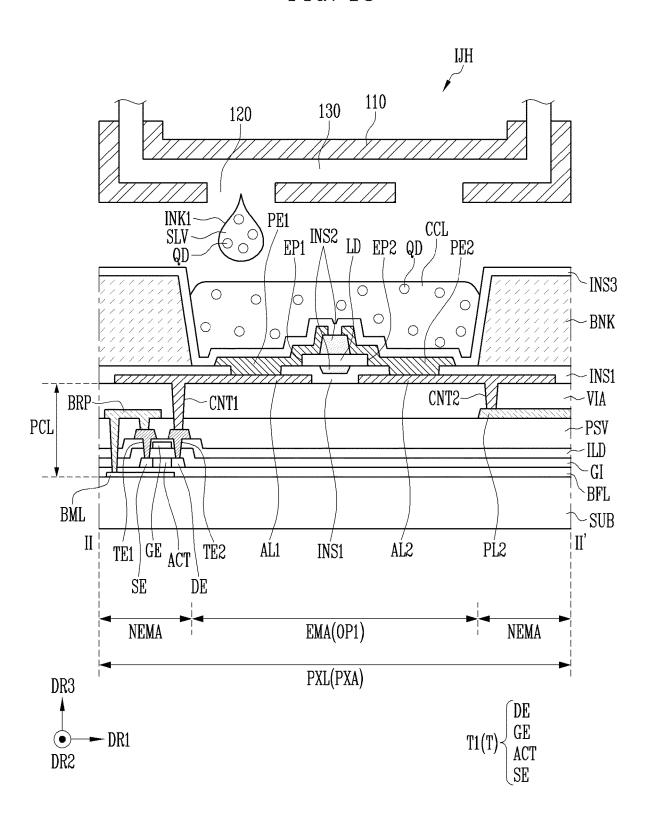

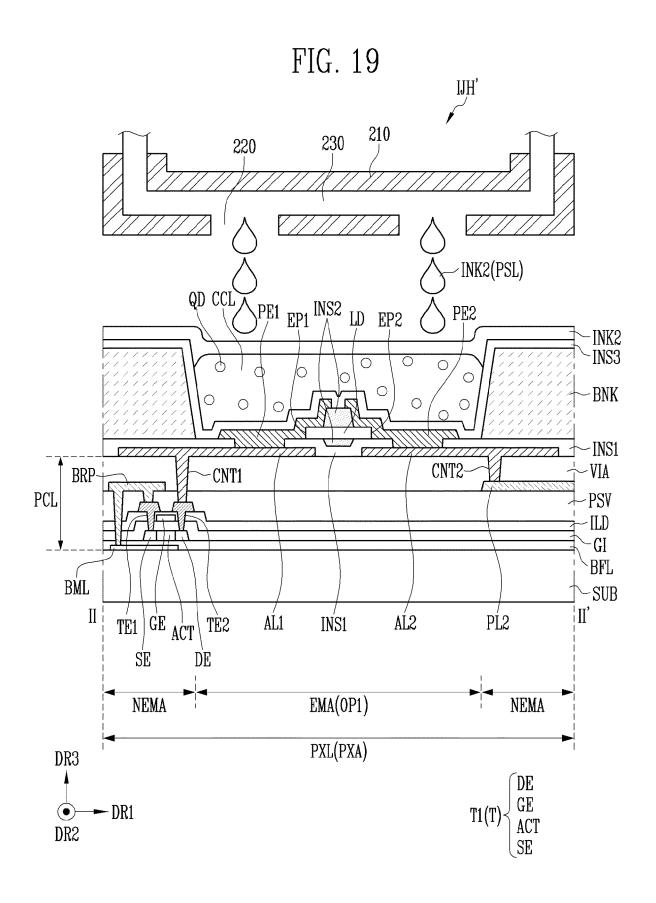

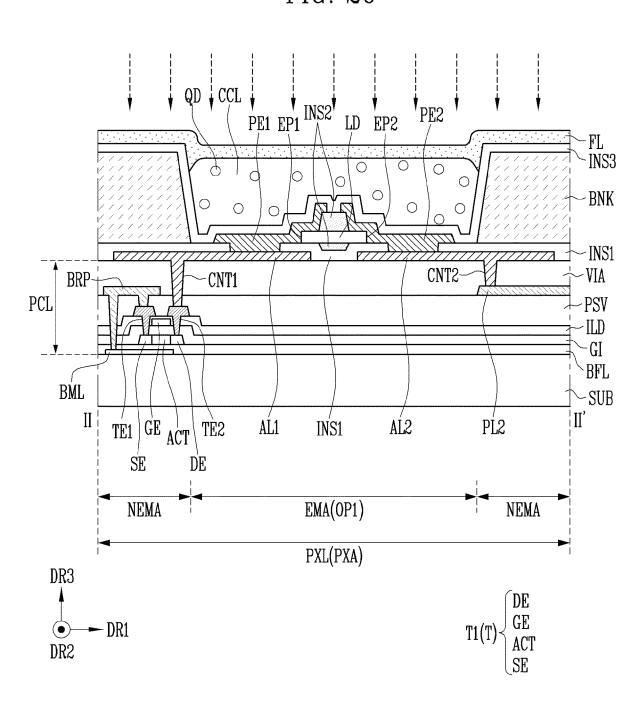

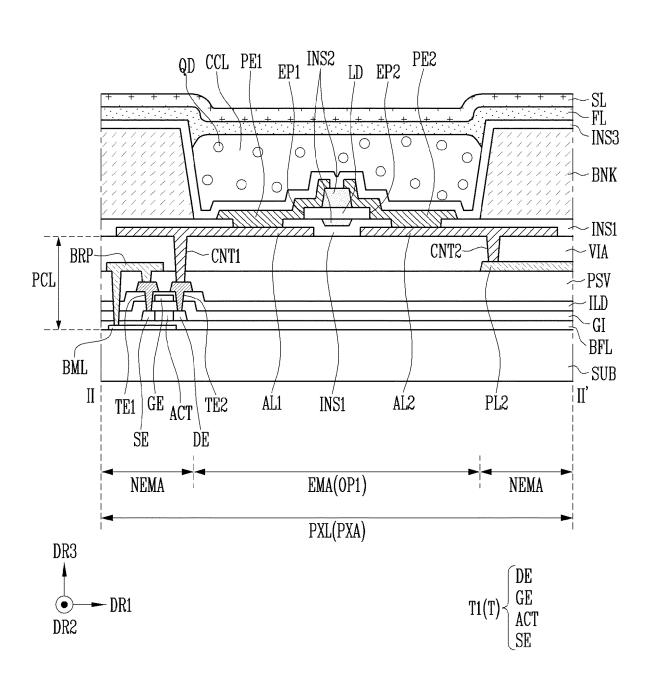

FIG. 18

FIG. 20

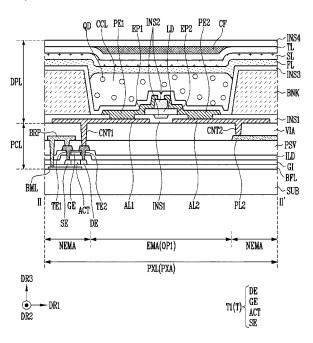

FIG. 21 IJĦ" 310 330 320 QD CCL PE1 EP1 INS2 LD EP2 PE2 INK3 -INK3 FL INS3 BNK -INS1 CNT2 -VIA BRP-CNT1 PSV PCL - ILD -GI BFL BML -SUB AL1 **∏**' II TE1 GE ACT INS1 AĹ2 PĹ2 TÈ2 SE ĎΕ NEMA EMA(OP1) NEMA PXL(PXA) DR3 DE GE ACT SE DR1 DR2

FIG. 22

FIG. 23

FIG. 24

FIG. 25

FIG. 26

FIG. 27

## DISPLAY DEVICE AND MANUFACTURING METHOD THEREOF

## CROSS-REFERENCE TO RELATED APPLICATION(S)

The application claims priority to and the benefit of Korean patent application 10-2021-0064382 under 35 U.S.C. § 119(a), filed on May 18, 2021, in the Korean Intellectual Property Office (KIPO), the entire contents of which are incorporated herein by reference.

## BACKGROUND

### 1. Technical Field

The disclosure generally relates to a display device and a manufacturing method thereof.

#### 2. Related Art

As interest in information displays and demand for portable information media increase, research and commercialization has focused on display devices.

## **SUMMARY**

Embodiments provide a display device capable of improving display quality by improving the reliability of a 30 color conversion layer, and a manufacturing method of the display device.

In accordance with an aspect of the disclosure, there is provided a display device including a substrate including a display area and a non-display area; and a plurality of pixels 35 disposed in the display area, the plurality of pixels each including an emission area and a non-emission area, wherein each of the plurality of pixels may include at least one light emitting element located in the emission area; a first pixel electrode and a second pixel electrode located in at least the emission area, the first pixel electrode and the second pixel electrode being electrically connected to the light emitting element; a bank disposed in the non-emission area, the bank including a first opening corresponding to the emission area; 45 a color conversion layer located above the at least one light emitting element, the color conversion layer being disposed in the emission area to correspond to the at least one light emitting element, the color conversion layer including color conversion particles; a barrier layer disposed on the bank 50 and the color conversion layer; and a low refractive layer disposed on the barrier layer. The barrier layer may include silicon oxide (SiO<sub>x</sub>) having cured polysilazane.

The barrier layer may be located directly on the color conversion layer in the emission area. The low refractive 55 layer may be located directly on the barrier layer on the color conversion layer in the emission area. The color conversion layer, the barrier layer, and the low refractive layer may be sequentially disposed in the emission area.

The low refractive layer may be disposed on an entire side 60 of the barrier layer in the emission area and the non-emission area.

The low refractive layer may be disposed on the barrier layer of the emission area to correspond to the color conversion layer.

The low refractive layer may compensate for a height difference between the bank and the color conversion layer. 2

Each of the plurality of pixels may further include a capping layer disposed on an entire side of the low refractive layer. The capping layer and the barrier layer may include a same material.

The capping layer may overlap the low refractive layer and may protect the low refractive layer.

Each of the plurality of pixels may further include a color filter disposed on the capping layer in the emission area to correspond to the color conversion layer.

Each of the barrier layer, the low refractive layer, and the capping layer may be a common layer disposed in the plurality of pixels.

Each of the plurality of pixels may further include a pixel circuit layer located between the substrate and the at least one light emitting element, the pixel circuit layer including at least one transistor and at least one power line, wherein the at least one transistor and the at least one power line are electrically connected to the at least one light emitting element; a first electrode disposed on the pixel circuit layer, the first electrode being electrically connected to the at least one transistor; a second electrode disposed on the pixel circuit layer and spaced from the first electrode, the second electrode being electrically connected to the at least one power line; and an insulating layer disposed on the first and second electrodes, the insulating layer including at least one opened portion.

The first electrode may be electrically connected to the first pixel electrode through an opened portion of the insulating layer, and the second electrode may be electrically connected to the second pixel electrode through another opened portion of the insulating layer.

The bank may include a second opening spaced from the first opening. At least one of the first and second electrodes may include an opened portion in the second opening.

The opened portion of the insulating layer and the another opened portion of the insulating layer may be located in the second opening.

In accordance with another aspect of the disclosure, there is provided a display device including a substrate including a display area and a non-display area; and a plurality of pixels disposed in the display area, the plurality of pixels each including an emission area and a non-emission area, wherein each of the plurality of pixels may include at least one light emitting element located in the emission area, a first pixel electrode and a second pixel electrode, located in at least the emission area, the first pixel electrode and the second pixel electrode being electrically connected to the at least one light emitting element; a bank disposed in the non-emission area, the bank including an opening corresponding to the emission area; a base layer located above the bank and the at least one light emitting element such that a surface of the base layer faces the substrate; a color filter disposed on the surface of the base layer to correspond to the emission area; a first light blocking pattern disposed on the surface of the base layer to correspond to the non-emission area; a low refractive layer provided entirely on the first light blocking pattern and the color filter; a capping layer disposed on the low refractive layer; a second light blocking pattern provided on the capping layer to correspond to the first light blocking pattern; a color conversion layer surrounded by the second light blocking pattern, the color conversion layer being provided on the capping layer to correspond to the at least one light emitting element; and a barrier layer disposed entirely on the color conversion layer and the second light blocking pattern, and wherein the barrier layer includes silicon oxide (SiO<sub>x</sub>) having cured polysilazane.

3

The first and second light blocking patterns may correspond to the bank.

In accordance with still another aspect of the disclosure, there is provided a method of manufacturing a display device, the method including providing a substrate having at least one light emitting element disposed in an emission area and a bank including an opening corresponding to the emission area, the bank being disposed in a non-emission area; forming a color conversion layer including color conversion particles above the at least one light emitting element; forming a polysilazane layer on the color conversion layer and the bank; forming a barrier layer by curing the polysilazane layer; forming a low refractive layer on the barrier layer; and forming a capping layer on the low refractive layer.

The color conversion layer, the barrier layer, and the low refractive layer may be formed by continuous inkjet printing.

The barrier layer may include silicon oxide (SiO<sub>x</sub>).

The method may further include forming a color filter on the capping layer to correspond to the color conversion layer.

The curing of the polysilazane layer may be performed by heat-curing.

## BRIEF DESCRIPTION OF THE DRAWINGS

Example embodiments will now be described more fully hereinafter with reference to the accompanying drawings; 30 however, they may be embodied in different forms and should not be construed as being limited to the embodiments set forth herein. Rather, these embodiments are provided so that this disclosure will be thorough and complete, and will convey the scope of the example embodiments to those 35 skilled in the art.

In the drawing figures, dimensions may be exaggerated for clarity of illustration. It will be understood that when an element is referred to as being "between" two elements, it can be the only element between the two elements, or one or 40 more intervening elements may also be present. Like reference numerals refer to like elements throughout.

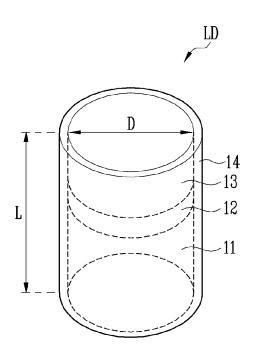

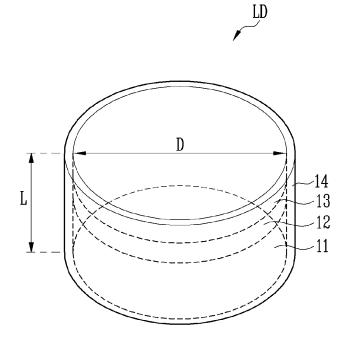

FIGS. 1 and 2 are perspective views schematically illustrating a light emitting element in accordance with an embodiment of the disclosure.

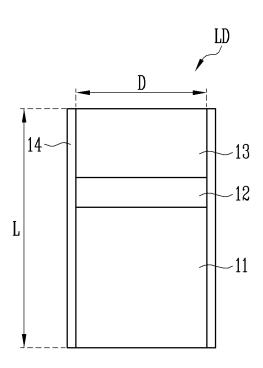

FIG. 3 is a schematic cross-sectional view of the light emitting element shown in FIG. 1.

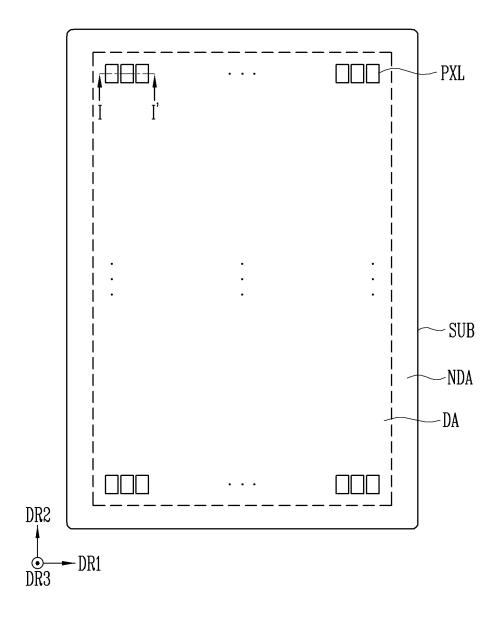

FIG. 4 is a plan view schematically illustrating a display device in accordance with an embodiment of the disclosure.

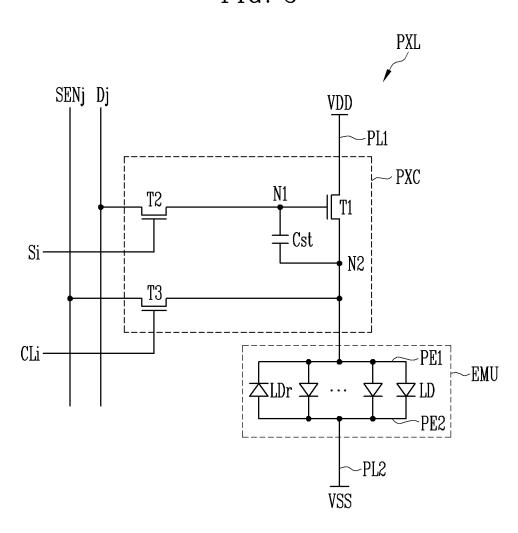

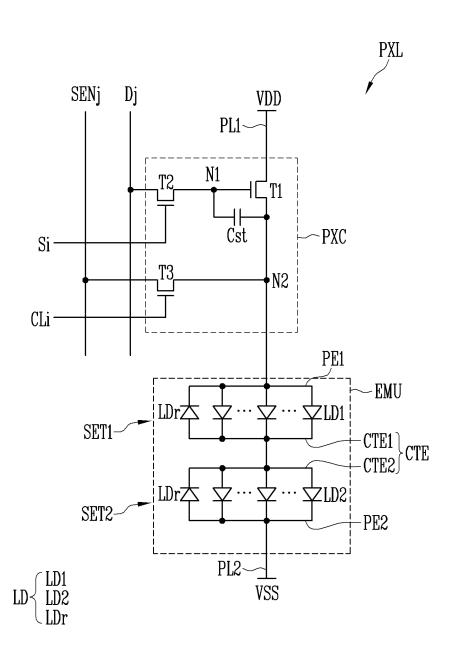

FIGS. 5 and 6 are schematic diagram of an equivalent 50 circuit illustrating various embodiments of an electrical connection relationship between components included in a pixel shown in FIG. 4.

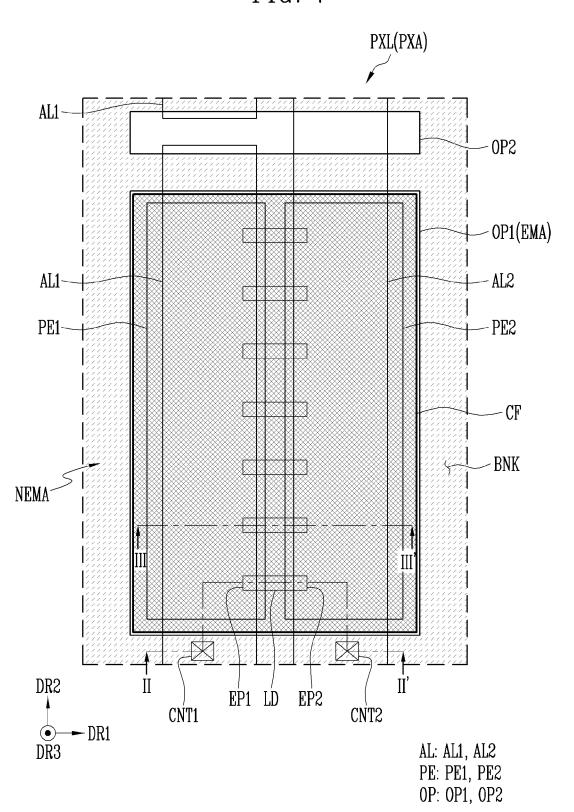

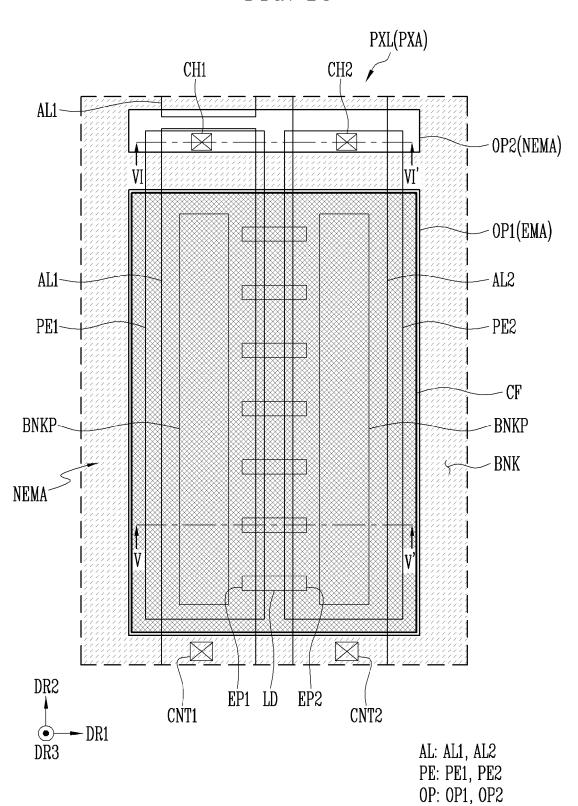

FIG. 7 is a plan view schematically illustrating the pixel shown in FIG. 4.

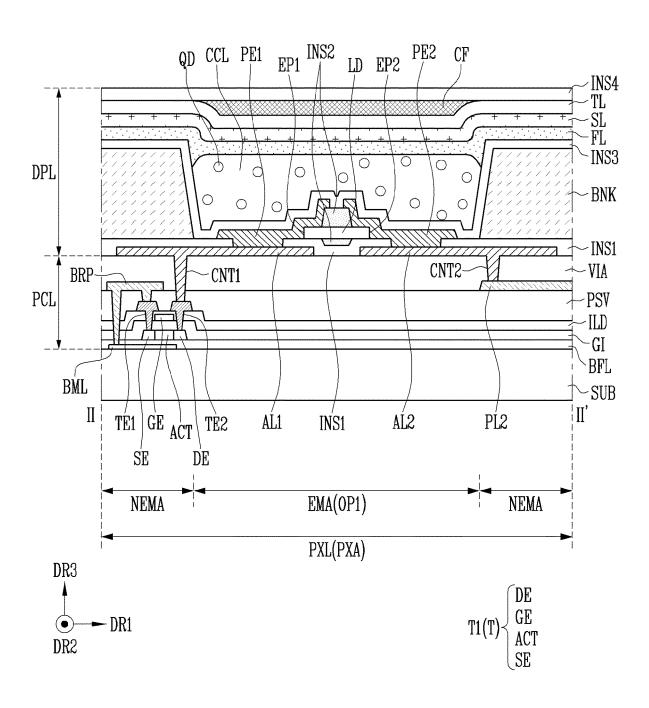

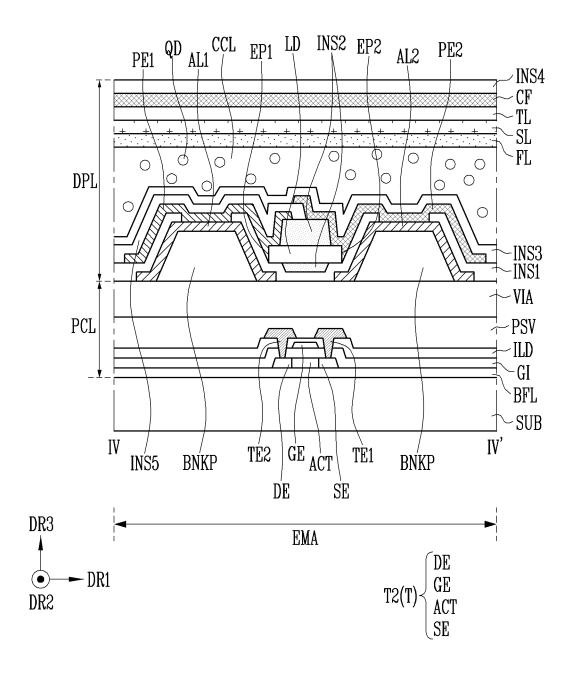

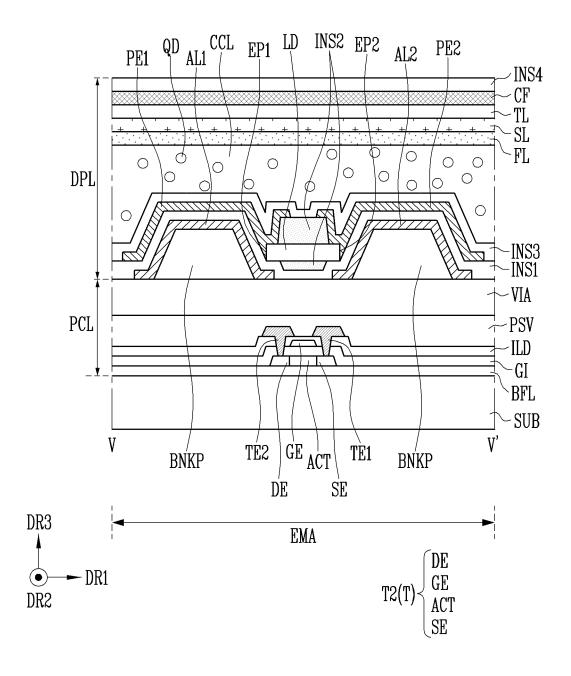

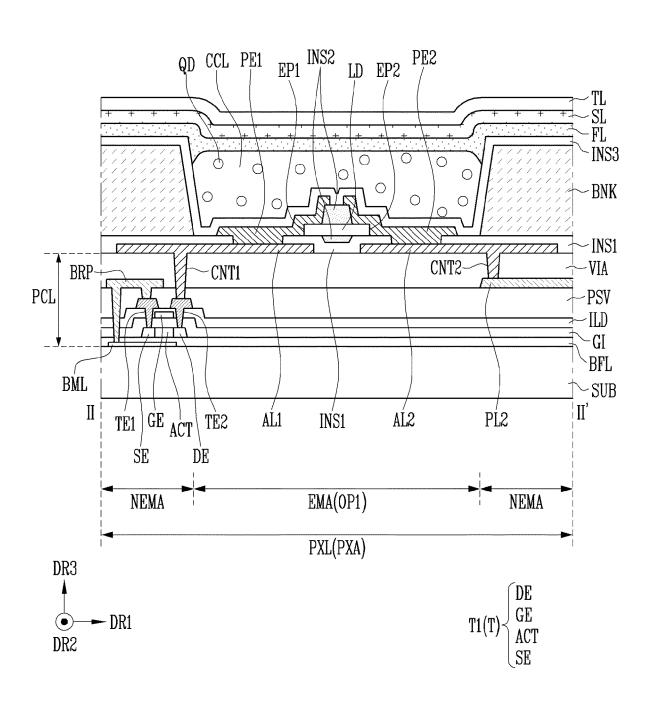

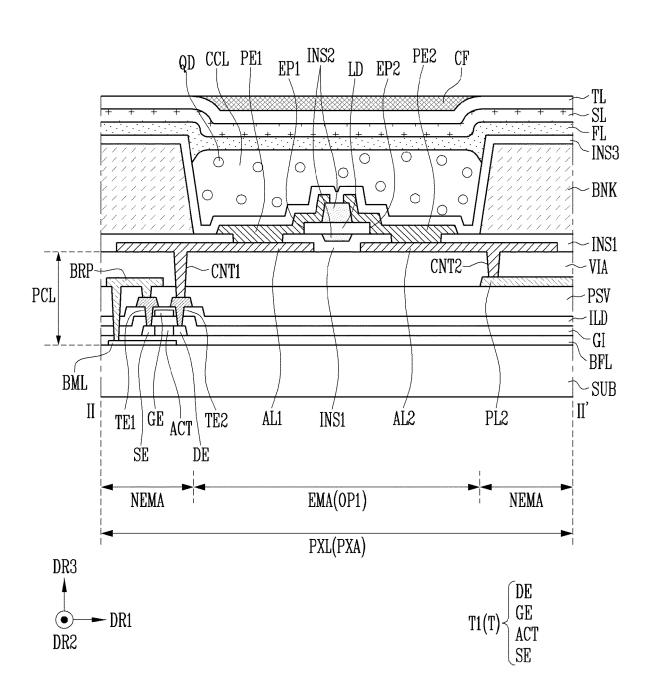

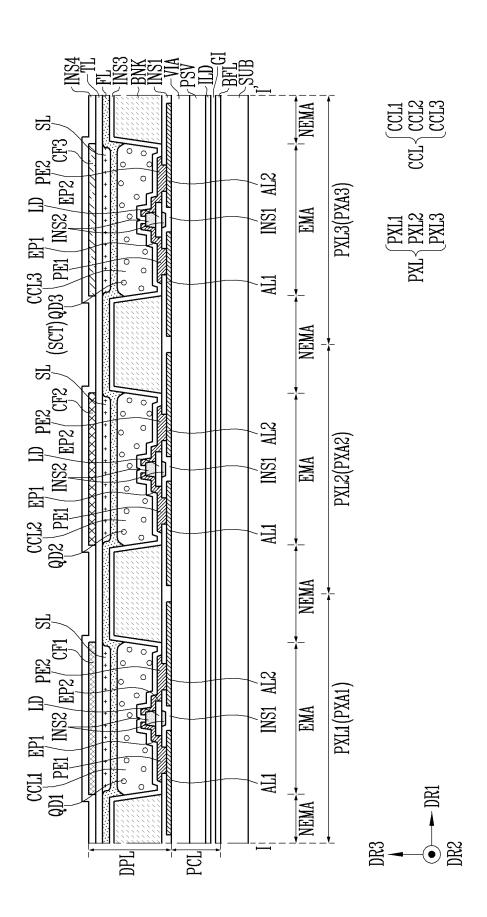

FIG. 8 is a schematic cross-sectional view taken along line II-II' shown in FIG. 7.

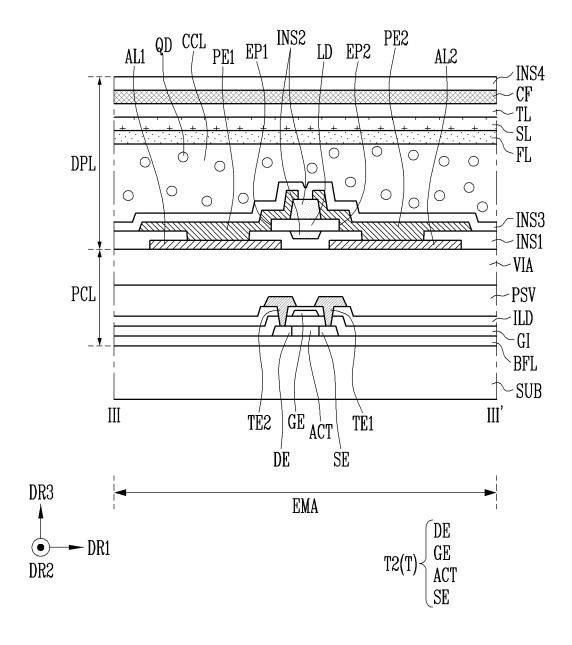

FIG. 9 is a schematic cross-sectional view taken along line III-III' shown in FIG. 7.

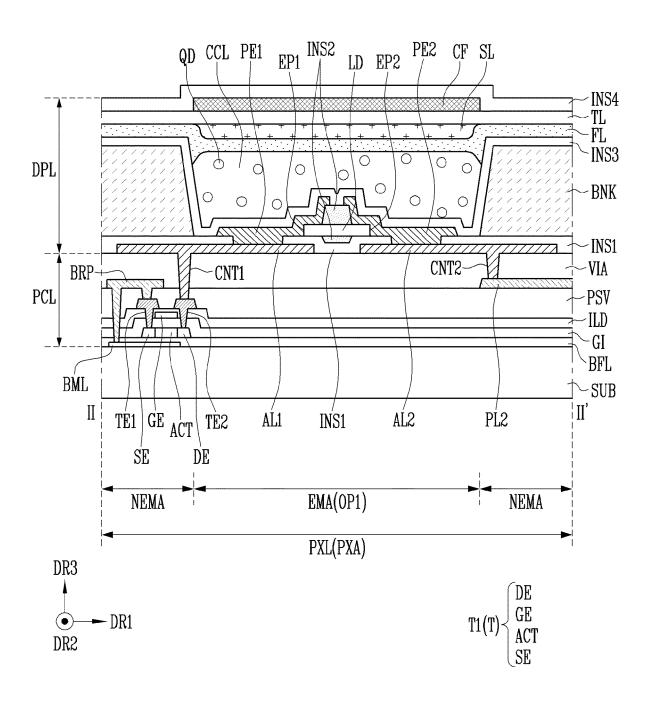

FIG. 10 schematically illustrates another embodiment of 60 a low refractive layer shown in FIG. 8, and is a cross-sectional view corresponding to the line II-II' shown in FIG. 7

FIG. 11 is a plan view schematically illustrating a pixel in accordance with another embodiment of the disclosure.

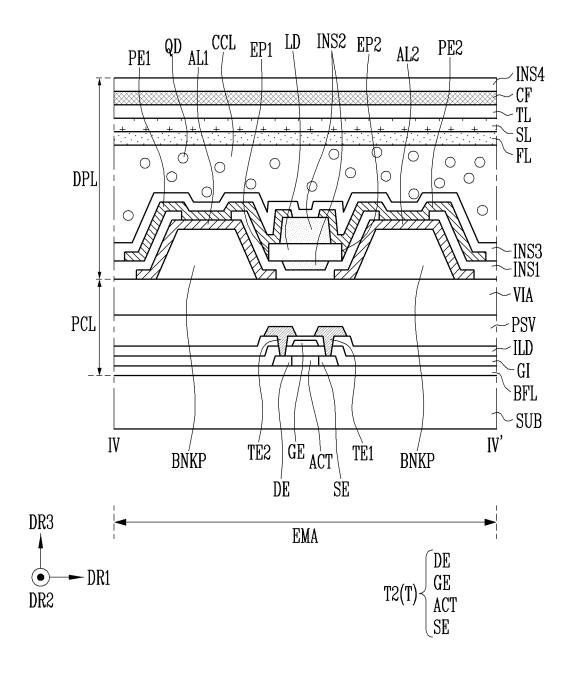

FIGS. 12 to 14 are schematic cross-sectional views taken along line IV-IV' shown in FIG. 11.

4

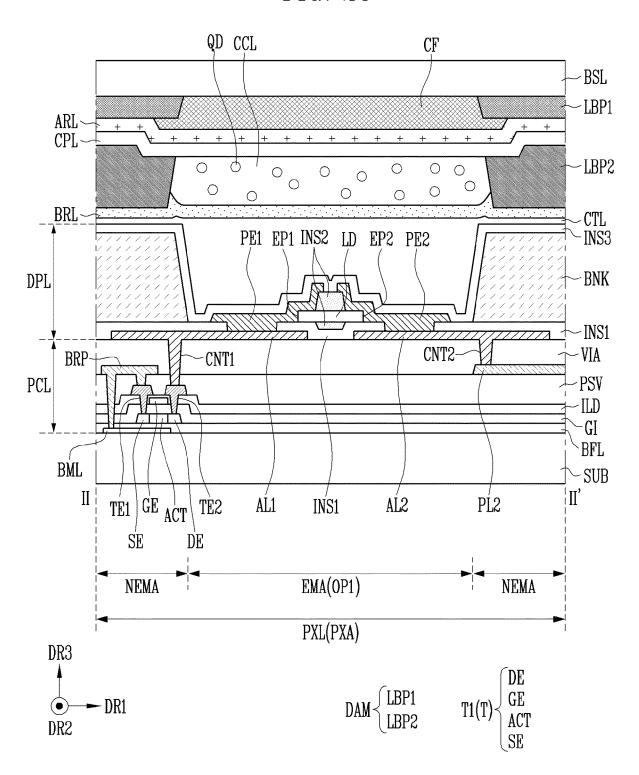

FIG. 15 is a plan view schematically illustrating a pixel in accordance with still another embodiment of the disclosure.

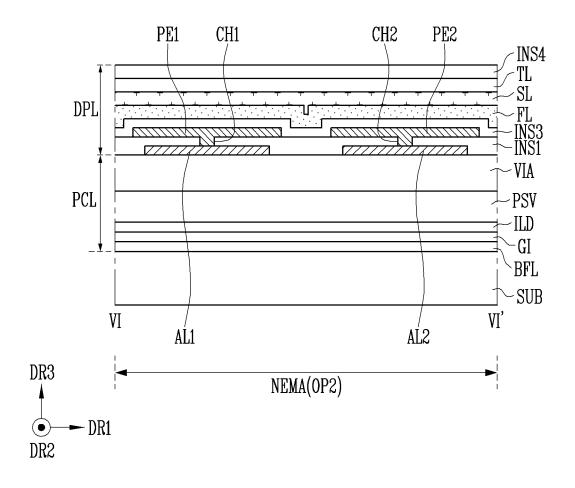

FIG. 16 is a schematic cross-sectional view taken along line V-V' shown in FIG. 15.

FIG. 17 is a schematic cross-sectional view taken along line VI-VI' shown in FIG. 15.

FIGS. **18** to **24** are cross-sectional views schematically illustrating a manufacturing method of a display device in accordance with an embodiment of the disclosure.

FIG. 25 schematically illustrates a pixel in accordance with an embodiment of the disclosure, and is a cross-sectional view corresponding to the line II-II' shown in FIG. 7

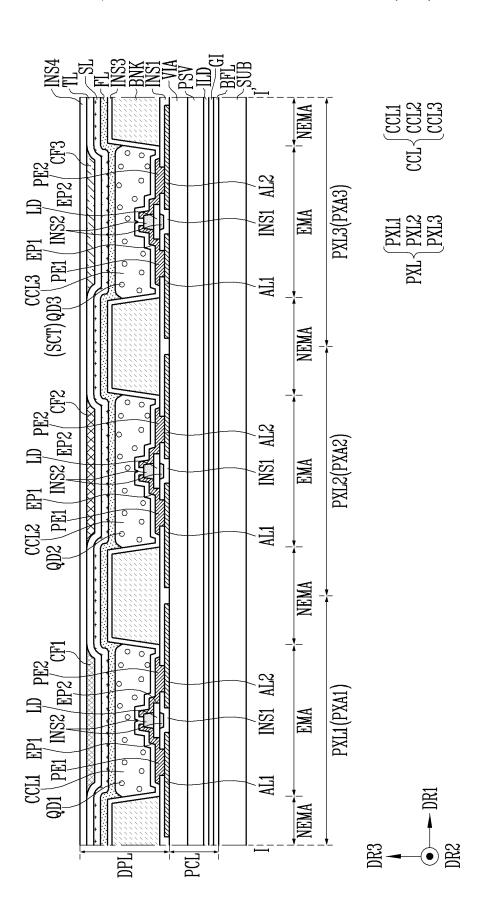

FIGS. **26** and **27** are schematic cross-sectional views taken along line I-I' shown in FIG. **4**.

## DETAILED DESCRIPTION OF THE EMBODIMENTS

The disclosure may apply various changes and different shape, therefore only illustrate in detail with particular examples. However, the examples do not limit to certain shapes but apply to all the change and equivalent material and replacement. The drawings included are illustrated a fashion where the figures are expanded for the better understanding.

Like numbers refer to like elements throughout. In the drawings, the thickness of certain lines, layers, components, elements or features may be exaggerated for clarity. It will be understood that, although the terms "first," "second," and the like may be used herein to describe various elements, these elements should not be limited by these terms. These terms are only used to distinguish one element from another element. Thus, a "first" element discussed below could also be termed a "second" element without departing from the teachings of the disclosure. As used herein, the singular forms are intended to include the plural forms as well, unless the context clearly indicates otherwise.

It will be further understood that the terms "includes" and/or "including", when used in this specification, specify the presence of stated features, integers, steps, operations, elements, and/or components, but do not preclude the presence and/or addition of one or more other features, integers, steps, operations, elements, components, and/or groups thereof. Further, an expression that an element such as a layer, region, substrate or plate is placed "on" or "above" another element indicates not only a case where the element is placed "directly on" or "just above" the other element but also a case where a further element is interposed between the element and the other element. On the contrary, an expression that an element such as a layer, region, substrate or plate is placed "beneath" or "below" another element indicates not only a case where the element is placed "directly beneath" or "just below" the other element but also a case where a further element is interposed between the element and the other element.

In this specification, it will be understood that, when an element (for example, a first element) is "(operatively or communicatively) coupled with/to" or "connected to" another element (for example, a second element), the element may be directly coupled with/to another element, and there may be an intervening element (for example, a third element) between the element and another element. Also, in this specification, the term "connection" or "coupling" may inclusively mean connection or physical and/or electrical coupling.

0.2 12,0 10,221 2

The terms "about" or "approximately" as used herein is inclusive of the stated value and means within an acceptable range of deviation for the particular value as determined by one of ordinary skill in the art, considering the measurement in question and the error associated with measurement of the particular quantity (i.e., the limitations of the measurement system). For example, "about" may mean within one or more standard deviations, or within ±30%, 20%, 10%, 5% of the stated value.

5

The phrase "at least one of" is intended to include the 10 meaning of "at least one selected from the group of" for the purpose of its meaning and interpretation. For example, "at least one of A and B" may be understood to mean "A, B, or A and B."

Unless otherwise defined or implied herein, all terms 15 (including technical and scientific terms) used herein have the same meaning as commonly understood by those skilled in the art to which this disclosure pertains. It will be further understood that terms, such as those defined in commonly used dictionaries, should be interpreted as having a meaning 20 that is consistent with their meaning in the context of the relevant art and the disclosure, and should not be interpreted in an ideal or excessively formal sense unless clearly so defined herein.

Hereinafter, embodiments of the disclosure and items 25 required for those skilled in the art to easily understand the content of the disclosure will be described in detail with reference to the accompanying drawings. In the following description, singular forms in the disclosure are intended to include the plural meanings as well, unless the context 30 clearly indicates otherwise.

FIGS. 1 and 2 are perspective views schematically illustrating a light emitting element LD in accordance with an embodiment. FIG. 3 is a schematic cross-sectional view of the light emitting element LD shown in FIG. 1.

In an embodiment, the kind (or type) and/or shape of the light emitting element LD is not limited to the embodiment shown in FIGS. 1 to 3.

Referring to FIGS. 1 to 3, the light emitting element LD may include a first semiconductor layer 11, a second semiconductor layer 13, and an active layer 12 interposed (or disposed) between the first and second semiconductor layers 11 and 13. In an example, the light emitting element LD may be implemented with (or implemented as) a light emitting stack structure (or a light emitting stack pattern) in which the 45 first semiconductor layer 11, the active layer 12, and the second semiconductor layer 13 are sequentially stacked.

The light emitting element LD may extend in a direction. When assuming that an extending direction of the light emitting element LD is a length direction, the light emitting 50 element LD may include one end portion (or lower end portion or first end portion) and the other end portion (or upper end portion or second end) in the length direction. One of the first and second semiconductor layers 11 and 13 may be disposed at the one end portion of the light emitting 55 element LD, and the other of the first and second semiconductor layers 11 and 13 may be disposed at the other end portion of the light emitting element LD. In an example, the first semiconductor layer 11 may be disposed at the one end portion of the light emitting element LD, and the second 60 semiconductor layer 13 may be disposed at the other end portion of the light emitting element LD.

The light emitting element LD may be provided in various shapes. In an example, the light emitting element LD may have a rod-like shape, a bar-like shape, a pillar-like shape (or 65 cylinder-like shape), or the like, which is long in its length direction (or extending direction) (i.e., its aspect ratio is

6

greater than 1) as shown in FIG. 1. In an embodiment, a length L of the light emitting element LD in the length direction may be larger than a diameter D (or a width of a cross-section) of the light emitting element LD. However, the disclosure is not limited thereto. In some embodiments, the light emitting element LD may have a rod-like shape, a bar-like shape, a pillar-like shape, or the like, which is short in its length direction (i.e., its aspect ratio is smaller than 1) as shown in FIG. 2. In some embodiments, the light emitting element LD may have a rod-like shape, a bar-like shape, a pillar-like shape, or the like, of which a length L and a diameter D are the same.

The light emitting element LD may include, for example, a light emitting diode (LED) manufactured small enough to have a diameter D and/or a length L to a degree of nanometer scale to micrometer scale.

In case that the light emitting element LD is long in its length direction (i.e., its aspect ratio is greater than 1), the diameter D of the light emitting element LD may be about 0.5  $\mu m$  to about 6  $\mu m$ , and the length L of the light emitting element LD may be about 1  $\mu m$  to about 10  $\mu m$ . However, the diameter D and length L of the light emitting element LD are not limited thereto, and the size of the light emitting element LD may be changed according to requirement conditions (or design conditions) of a lighting device or a self-luminous display device, to which the light emitting element LD is applied.

The first semiconductor layer 11 may include, for example, at least one n-type semiconductor layer. For example, the first semiconductor layer 11 may include any semiconductor material among InAlGaN, GaN, AlGaN, InGaN, AlN, and InN, and include an n-type semiconductor layer doped with a first conductive dopant (or n-type dopant) such as Si, Ge, or Sn. However, the material forming (or 35 constituting) the first semiconductor layer 11 is not limited thereto. The first semiconductor layer 11 may be configured with various materials. The first semiconductor layer 11 may include an upper surface contacting (or in contact with) the active layer 12 and a lower surface exposed to the outside in the length direction of the light emitting element LD. The lower surface of the first semiconductor layer 11 may be the one end portion (or lower end portion) of the light emitting element LD.

be implemented with (or implemented as) a light emitting stack structure (or a light emitting stack pattern) in which the second semiconductor layer 11, the active layer 12, and the second semiconductor layer 13 are sequentially stacked.

The light emitting element LD may extend in a direction. When assuming that an extending direction of the light emitting element LD is a length direction, the light emitting element LD may include one end portion (or lower end portion or first end portion) and the other end portion (or upper end portion or second end) in the length direction. One of the first and second semiconductor layer 12 is formed in the first semiconductor layer 12 in an example, in case that the active layer 12 is formed in the multiple quantum well structure, a barrier layer (not shown), a strain reinforcing layer, which constitute a unit, may be periodically and repeatedly stacked in the active layer 12. The strain reinforcing layer may have a lattice constant smaller than that of the barrier layer to further reinforce strain, e.g., compressive strain applied to the well layer. However, the structure of the active layer 12 is formed on the first semiconductor layer 12 and may be formed in a single or multiple quantum well structure. In an example, in case that the active layer (not shown), a strain reinforcing layer, which constitute a unit, may be periodically and repeatedly stacked in the active layer 12. The strain reinforcing layer may have a lattice constant smaller than that of the barrier layer to further reinforce strain, e.g., compressive strain applied to the well layer. However, the structure of the active layer 12 is formed in the multiple quantum well structure. In an example, in case that the active layer 12 is formed in the multiple quantum well structure. In an example, in case that the active layer 12 is formed in the multiple quantum well structure.

The active layer 12 may emit light having a wavelength of about 400 nm to about 900 nm and use a double heterostructure. In an embodiment, a clad layer (not shown) doped with a conductive dopant may be formed on the top and/or bottom of the active layer 12 in the length direction of the light emitting element LD. In an example, the clad layer may be formed as an AlGaN layer or InAlGaN layer. In some embodiments, a material such as AlGaN or AlInGaN may be used to form the active layer 12. The active layer 12 may be configured with various materials. The active layer 12 may include a first surface contacting the first semiconductor layer 11 and a second surface contacting the second semiconductor layer 13.

In case that an electric field having a predetermined voltage or more is applied to both end portions of the light emitting element LD, the light emitting element LD emits light as electron-hole pairs are combined in the active layer 12. The light emission of the light emitting element LD is 5 controlled by using such a principle, so that the light emitting element LD may be used as a light source (or light emitting source) for various light emitting devices, including a pixel of a display device.

The second semiconductor layer 13 is formed on the 10 second surface of the active layer 12 and may include a semiconductor layer having a type different from that of the first semiconductor layer 11. In an example, the second semiconductor layer 13 may include at least one p-type semiconductor material. For example, the second semiconductor layer 13 may include at least one semiconductor material among InAlGaN, GaN, AlGaN, InGaN, AlN, and InN and include a p-type semiconductor layer doped with a second conductive dopant (or p-type dopant) such as Mg, Zn, Ca, Sr, or Ba. However, the material forming the second 20 semiconductor layer 13 is not limited thereto. The second semiconductor layer 13 may be configured with various materials. The second semiconductor layer 13 may include a lower surface contacting the second surface of the active layer 12 and an upper surface exposed to the outside in the 25 length direction of the light emitting element LD. The upper surface of the second semiconductor layer 13 may be the second end portion (or upper end portion) of the light emitting element LD.

In an embodiment, the first semiconductor layer 11 and 30 the second semiconductor layer 13 may have different thicknesses in the length direction of the light emitting element LD. In an example, the first semiconductor layer 11 may have a thickness relatively thicker or greater than that of the second semiconductor layer 13 in the length direction 35 of the light emitting element LD. Accordingly, the active layer 12 of the light emitting element LD may be located more adjacent to the upper surface of the second semiconductor layer 13 than the lower surface of the first semiconductor layer 11.

Although FIGS. 1 to 3 illustrate that each of the first semiconductor layer 11 and the second semiconductor layer 13 is configured with a layer, the disclosure is not limited thereto. In an embodiment, each of the first semiconductor layer 11 and the second semiconductor layer 13 may further 45 include at least one layer, e.g., a clad layer and/or a tensile strain barrier reducing (TSBR) layer according to the material of the active layer 12. The TSBR layer may be a strain reducing layer disposed between semiconductor layers having different lattice structures to perform a buffering function for reducing a lattice constant difference. The TSBR may be configured with a p-type semiconductor layer such as p-GAInP, p-AIInP, or p-AIGaInP, but the disclosure is not limited thereto.

In some embodiments, the light emitting element LD may 55 further include a contact electrode (not shown) (hereinafter referred to as a "first contact electrode") disposed on the top of the second semiconductor layer 13, in addition to the first semiconductor layer 11, the active layer 12, and the second semiconductor layer 13, which are described above. In some 60 embodiments, the light emitting element LD may further include another contact electrode (not shown) (hereinafter referred to as a "second contact electrode") disposed at one end of the first semiconductor layer 11.

Each of the first and second contact electrodes may be an 65 ohmic contact electrode, but the disclosure is not limited thereto. In some embodiments, each of the first and second

8

contact electrodes may be a Schottky contact electrode. The first and second contact electrodes may include a conductive material. For example, the first and second contact electrodes may include an opaque metal using, one or mixture of chromium (Cr), titanium (Ti), aluminum (Al), gold (Au), nickel (Ni), and an oxide or alloy thereof, but the disclosure is not limited thereto. In some embodiments, the first and second contact electrodes may include a transparent conductive oxide such as indium tin oxide (ITO), indium zinc oxide (IZO), zinc oxide (ZnO), indium gallium zinc oxide (IGZO), or indium tin zinc oxide (ITZO).

Materials respectively included in the first and second contact electrodes may be identical to or different from each other. The first and second contact electrodes may be substantially transparent or translucent. Accordingly, light generated from the light emitting element LD may be emitted to the outside of the light emitting element LD by passing through the first and second contact electrodes. In some embodiments, in case that light generated from the light emitting element LD does not pass through the first and second contact electrodes and is emitted to the outside of the light emitting element LD through an area except both the end portions of the light emitting element LD, the first and second contact electrodes may include an opaque metal.

In an embodiment, the light emitting element LD may further include an insulating film 14 (or insulating film). However, in some embodiments, the insulating film 14 may be omitted and may also be provided to cover only portions of the first semiconductor layer 11, the active layer 12, and the second semiconductor layer 13.

The insulating film 14 may prevent an electrical short circuit which may occur in case that the active layer 12 contacts a conductive material in addition to the first semi-conductor layer 11 and the second semiconductor layer 13. The insulating film 14 minimizes a surface defect of the light emitting element LD, thereby improving the lifespan and light emission efficiency of the light emitting element LD. In case that light emitting elements LD are densely disposed, the insulating film 14 may prevent an unwanted short circuit which may occur between the light emitting elements LD. Whether the insulating film 14 is provided is not limited as long as the active layer 12 may be prevented from being short-circuited with an external conductive material.

The insulating film 14 may be provided in a shape entirely surround the outer circumference of a light emitting stack structure including the first semiconductor layer 11, the active layer 12, and the second semiconductor layer 13.

Although a case where the insulating film 14 is provided in a shape entirely surrounding the outer circumference of each of the first semiconductor layer 11, the active layer 12, and the second semiconductor layer 13 in the above-described embodiment, the disclosure is not limited thereto. In some embodiments, in case that the light emitting element LD includes the first contact electrode, the insulating film 14 may entirely surround the outer circumference of each of the first semiconductor layer 11, the active layer 12, the second semiconductor layer 13, and the first contact electrode. In some embodiments, the insulating film 14 may not entirely surround the outer circumference of the first contact electrode, or may surround only a portion of the outer circumference of the first contact electrode and may not surround the other of the outer circumference of the first contact electrode. In some embodiments, in case that the first contact electrode is disposed at the other end portion (e.g., upper end portion) of the light emitting element LD, and the second contact electrode is disposed at one end portion (e.g., lower

end portion) of the light emitting element LD, the insulating film **14** may expose at least one area of each of the first and second contact electrodes.

The insulating film 14 may include a transparent insulating material. For example, the insulating film 14 may include at least one insulating material selected from the group consisting of silicon oxide (SiO<sub>x</sub>), silicon nitride  $(SiN_x)$ , silicon oxynitride  $(SiO_xN_y)$ , aluminum oxide  $(AlO_x)$ , titanium dioxide (TiO<sub>2</sub>), hafnium oxide (HfO<sub>r</sub>), titanium strontium oxide (SrTiO<sub>x</sub>), cobalt oxide (CoxO<sub>v</sub>), magnesium 10 oxide (MgO), zinc oxide (ZnO), ruthenium oxide (RuO<sub>x</sub>), nickel oxide (NiO), tungsten oxide (WO<sub>x</sub>), tantalum oxide  $(TaO_x)$ , gadolinium oxide  $(GdO_x)$ , zirconium oxide  $(ZrO_x)$ , gallium oxide (GaO<sub>x</sub>), vanadium oxide (VxO<sub>y</sub>), ZnO:Al, ZnO:B, InxOy:H, niobium oxide (Nb<sub>x</sub>O<sub>v</sub>), magnesium fluo- 15 ride (MgF<sub>x</sub>), aluminum fluoride (AIF<sub>x</sub>), Alucone polymer film, titanium nitride (TiN), tantalum nitride (TaN), aluminum nitride (AlN<sub>x</sub>), gallium nitride (GaN), tungsten nitride (WN), hafnium nitride (HfN), niobium nitride (NbN), gadolinium nitride (GdN), zirconium nitride (ZrN), vanadium 20 nitride (VN), and the like. However, the disclosure is not limited thereto, and various materials having insulating properties may be used as the material of the insulating film

The insulating film 14 may be provided in the form of a 25 single layer or be provided in the form of a multi-layer including at least two layers. In an example, in case that the insulating film 14 is formed as a double layer including a first layer and a second layer, which are sequentially stacked, the first layer and the second layer may be made of (or 30 include) different materials (or ingredients) and be formed by different processes. In some embodiments, the first layer and the second layers may be formed of the same material and may be formed by a continuous process.

In some embodiments, the light emitting element LD may 35 be implemented with a light emitting pattern having a core-shell structure. The first semiconductor layer 11 may be located at a core, e.g., in the middle (or center) of the light emitting element LD, the active layer 12 may be provided and/or formed in a shape surrounding the outer circumfer- 40 ence of the first semiconductor layer 11, and the second semiconductor layer 13 may be provided and/or formed in a shape surrounding the active layer 12. The light emitting element LD may further include a contact electrode (not shown) surrounding at least one side of the second semi- 45 conductor layer 13. In some embodiments, the light emitting element LD may further include an insulating film 14 which is provided on the outer circumference of the light emitting pattern having the core-shell structure and includes a transparent insulating material. The light emitting element LD 50 implemented in the light emitting pattern having the coreshell structure may be manufactured by a growth process.

The above-described light emitting element LD may be used as a light emitting source (or light source) for various display devices. The light emitting element LD may be 55 manufactured through a surface treatment process. For example, in case that light emitting elements LD are mixed in a liquid solution (or solvent) to be supplied to each pixel area (e.g., an emission area of each pixel or an emission area of each sub-pixel), each light emitting element LD may be 60 surface-treated such that the light emitting elements LD are not unequally condensed in the solution but may be equally dispersed in the solution.

A light emitting unit (or light emitting part) (or light emitting device) including the above-described light emitting element LD may be used in various types of devices that require a light source, including a display device. In case that

10

light emitting elements LD are disposed in an emission area of each pixel of a display panel, the light emitting elements LD may be used as a light source of the pixel. However, the application field of the light emitting element LD is not limited to the above-described example. For example, the light emitting element LD may be used for other types of devices that require a light source, such as a lighting device.

FIG. 4 is a plan view schematically illustrating a display device in accordance with an embodiment.

For convenience, FIG. 4 illustrates a structure of the display device based on a display area DA in which an image is displayed.

The disclosure may be applied as long as the display device is an electronic device in which a display surface is applied to at least one surface thereof, such as a smartphone, a television, a tablet personal computer (PC), a mobile phone, a video phone, an electronic book reader, a desktop PC, a laptop PC, a netbook computer, a workstation, a server, a personal digital assistant (PDA), a portable multimedia player (PMP), an MP3 player, a medical device, a camera, or a wearable device.

Referring to FIGS. 1 to 4, the display device may include a substrate SUB, pixels PXL which are provided on the substrate SUB and each include at least one light emitting element LD, a driving unit (or driving part) which is provided on the substrate SUB and drives the pixels PXL, and a line unit (or line part)\_ which electrically connects the pixels PXL and the driving part.

The display device may be classified into a passive-matrix type display device and an active-matrix type display device according to a method of driving the light emitting element LD. In an example, in case that the display device is implemented as the active-matrix type display device, each of the pixels PXL may include a driving transistor for controlling an amount of current supplied to the light emitting element LD, a switching transistor for transferring a data signal to the driving transistor, and the like.

The display device may be provided in various shapes. In an example, the display device may be provided in a rectangular plate shape having two pairs of sides parallel to each other, but the disclosure is not limited thereto. In case that the display device is provided in the rectangular plate shape, any pair of sides among the two pairs of sides may be longer than the other pair of sides. For convenience, a case where the display device is provided in a rectangular shape having a pair of long sides and a pair of short sides is illustrated. An extending direction of the long sides is represented as a second direction DR2, an extending direction of the short sides is represented as a first direction DR1, and a direction perpendicular to the extending directions of the long sides and the short sides is represented as a third direction DR3. In the display device provided in the rectangular plate shape, a corner portion at which a long side and a short side contact (or meet) each other may have a round

The substrate SUB may include the display area DA and a non-display area NDA.

The display area DA may be an area in which the pixels PXL for displaying an image are provided. The non-display area NDA may be an area in which the driving part for driving the pixels PXL and a portion of the line part which electrically connects the pixels PXL and the driving part are provided.

The non-display area DA may be located adjacent to the display area DA. The non-display area NDA may be provided at at least one side of the display area DA. For example, the non-display area NDA may surround the

circumference (or edge) of the display area DA. The nondisplay area NDA may be provided with the line part electrically connected to the pixels PXL and the driving part which is electrically connected to the line part and drives the pixels PXL.

The line part may electrically connect the driving part and the pixels PXL. The line part may include a fan-out line which provides a signal to each pixel PXL and is electrically connected to signal lines, e.g., a scan line, a data line, an emission control line, and the like, which are electrically 10 connected to each pixel PXL. In some embodiments, the line part may include a fan-out line electrically connected to signal lines, e.g., a control line, a sensing line, and the like, which are electrically connected to each pixel PXL so as to compensate for a change in an electrical characteristic of 15 each pixel PXL in real time. Additionally, the line part may include a fan-output line which provides a predetermined voltage to each pixel PXL and is electrically connected to power lines electrically connected to each pixel PXL.

The substrate SUB may include a transparent insulating 20 material to enable light to be transmitted therethrough. The substrate SUB may be a rigid substrate or a flexible substrate

An area on the substrate SUB may be provided as the display area DA such that the pixels PXL are disposed 25 therein, and the other area on the substrate SUB may be provided as the non-display area NDA. In an example, the substrate SUB may include the display area DA including pixel areas in which the respective pixels PXL are disposed, and the non-display area NDA disposed at the periphery of 30 the display area DA (or adjacent to the display area DA).

Each of the pixels PXL may be provided in the display area DA on the substrate SUB. In an embodiment, the pixels PXL may be arranged in a stripe arrangement structure in the display area DA, but the disclosure is not limited thereto. 35

Each pixel PXL may include at least one light emitting element LD driven by a corresponding scan signal and a corresponding data signal. The light emitting element LD may have a size small to a degree of micrometer scale or nanometer scale and be electrically connected in parallel to 40 light emitting elements disposed adjacent thereto. However, the disclosure is not limited thereto. The light emitting element LD may form a light source of each pixel PXL.

Each pixel PXL may include at least one light source, e.g., the light emitting element LD shown in FIGS. 1 to 3, which 45 is driven by a signal (e.g., a scan signal, a data signal, and the like) and/or a power source (e.g., a first driving power source a second driving power source, and the like). However, in the embodiment of the disclosure, the kind of the light emitting element LD which may be used as the light source of the pixel PXL is not limited thereto. In an example, each pixel PXL may include a light emitting element configured as an organic light emitting diode. The organic light emitting diode may have a form in which an anode, a hole transport layer, an organic emitting layer, an electron transport layer, and a cathode are sequentially stacked, but the disclosure is not limited thereto.

The driving part provides a signal and a power source to each pixel PXL through the line part. Accordingly, the driving part may control the driving of the pixel PXL.

FIGS. 5 and 6 are schematic diagrams of equivalent circuits illustrating various embodiments of an electrical connection relationship between components included in the pixel PXL shown in FIG. 4.

For example, FIGS. **5** and **6** illustrate various embodiments of an electrical connection relationship between components included in the pixel PXL applicable to an active-

matrix type display device. However, the kinds of the components included in the pixel PXL applicable to embodiments of the disclosure are not limited thereto.

12

In FIGS. 5 and 6, the pixel PXL comprehensively includes not only components included in the pixel PXL shown in FIG. 4 but also an area in which the components are provided (or located).

Referring to FIGS. 1 to 6, the pixel PXL may include a light emitting part EMU which generates light with a luminance corresponding to a data signal. The pixel PXL may selectively further include a pixel circuit PXC for driving the light emitting part EMU.

In some embodiments, the light emitting part EMU may include light emitting elements LD electrically connected in parallel between a first power line PL1 electrically connected to a first driving power source VDD to be applied with a voltage of the first driving power source VDD, and a second power line PL2 electrically connected to a second driving power source VSS to be applied with a voltage of the second driving power source VSS. For example, the light emitting part EMU may include a first pixel electrode PE1 electrically connected to the first driving power source VDD via the pixel circuit PXC and the first power line PL1, a second pixel electrode PE2 electrically connected to the second driving power source VSS through the second power line PL2, and light emitting elements LD electrically connected in parallel in the same direction between the first and second pixel electrodes PE1 and PE2. In an embodiment, the first pixel electrode PE1 may be an anode, and the second pixel electrode PE2 may be a cathode.

Each of the light emitting elements LD included in the light emitting part EMU may include one end portion (or first end portion) electrically connected to the first driving power source VDD through the first pixel electrode PE1 and the other end portion (or second end) electrically connected to the second driving power source VSS through the second pixel electrode PE2. The first driving power source VDD and the second driving power source VSS may have different potentials. In an example, the first driving power source VDD may be set as a high-potential power source, and the second driving power source VSS may be set as a lowpotential power source. A potential difference between the first and second driving power sources VDD and VSS may be set to be equal to or higher than a threshold voltage of the light emitting elements LD during an emission period of the pixel PXL.

As described above, the light emitting elements LD electrically connected in parallel in the same direction (e.g., a forward direction) between the first pixel electrode PE1 and the second pixel electrode PE2, to which voltages having difference potentials are supplied, may form effective light sources, respectively.

Each of the light emitting elements LD of the light emitting part EMU may emit light with a luminance corresponding to a driving current supplied through a corresponding pixel circuit PXC. For example, the pixel circuit PXC may supply, to the light emitting part EMU, a driving current corresponding to a grayscale value of corresponding frame data during each frame period. The driving current supplied to the light emitting part EMU may be divided and flow through each of the light emitting elements LD. Accordingly, the light emitting unit EMU may emit light with a luminance corresponding to the driving current while each light emitting element LD is emitting light with a luminance corresponding to a current flowing therethrough.

An embodiment in which both the end portions of the light emitting elements LD are electrically connected to each

other in the same direction between the first and second driving power sources VDD and VSS has been described, but the disclosure is not limited thereto. In some embodiments, the light emitting part EMU may further include at least one ineffective light source, e.g., a reverse light emitting element LDr, in addition to the light emitting elements LD forming the respective effective light sources. The reverse light emitting element LDr is electrically connected in parallel together with the light emitting elements LD forming the effective light sources between the first and 10 second pixel electrodes PE1 and PE2, and may be electrically connected between the first and second pixel electrodes PE1 and PE2 in a direction opposite to that in which the light emitting elements LD are connected. Although a predetermined driving voltage (e.g., a forward driving voltage) is 15 applied between the first and second pixel electrodes PE1 and PE2, the reverse light emitting element LDr maintains an inactivated state, and accordingly, no current substantially flows through the reverse light emitting element LDr.

The pixel circuit PXC may be electrically connected to a 20 scan line Si and a data line Dj of the pixel PXL. The pixel circuit PXC may be electrically connected to a control line CLi and a sensing line SENj of the pixel PXL. In an example, in case that the pixel PXL may be disposed on an i-th row and a j-th column of the display area DA, the pixel 25 circuit PXC of the pixel PXL may be electrically connected to an i-th scan line Si, a j-th data line Dj, an i-th control line CLi, and a j-th sensing line SENj of the display area DA.

The pixel circuit PXC may include first to third transistors  $T\mathbf{1}$  to  $T\mathbf{3}$  and a storage capacitor Cst.

The first transistor T1 is a driving transistor for controlling a driving current applied to the light emitting part EMU, and may be electrically connected between the first driving power source VDD and the light emitting part EMU. A first terminal of the first transistor T1 may be electrically con- 35 nected (or coupled) to the first driving power source VDD through the first power line PL1, a second terminal of the first transistor T1 may be electrically connected to a second node N2, and a gate electrode of the first transistor T1 may be electrically connected to a first node N1. The first 40 transistor T1 may control an amount of driving current applied to the light emitting part EMU through the second node N2 from the first driving power source VDD according to a voltage applied to the first node N1. In an embodiment, the first terminal of the first transistor T1 may be a drain 45 electrode, and the second terminal of the first transistor T1 may be a source electrode. However, the disclosure is not limited thereto. In some embodiments, the first terminal may be the source electrode, and the second terminal may be the drain electrode.

The second transistor T2 is a switching transistor which selects a pixel PXL in response to a scan signal and activates the pixel PXL, and may be electrically connected between the data line Dj and the first node N1. A first terminal of the second transistor T2 may be electrically connected to the 55 data line Dj, a second terminal of the second transistor T2 may be electrically connected to the first node N1, and a gate electrode of the second transistor T2 may be electrically connected to the scan line Si. The first terminal and the second terminal of the second transistor T2 are different 60 terminals. For example, in case that the first terminal is a drain electrode, the second terminal may be a source electrode.

In case that a scan having a gate-on voltage (e.g., a high-level voltage) is supplied from the scan line Si, the 65 second transistor T2 may be turned on to electrically connect the data line Dj and the first node N1 to each other. The first

node N1 is a point at which the second terminal of the second transistor T2 and the gate electrode of the first transistor T1 are electrically connected to each other, and the second transistor T2 may transfer a data signal to the gate electrode of the first transistor T1.

The third transistor T3 may electrically connect the first transistor T1 to the sensing line SEN<sub>1</sub> to acquire a sensing signal through the sensing line SENj and may detect a characteristic of the pixel PXL, including a threshold voltage of the first transistor T1, or the like, by using the sensing signal. Information on the characteristic of the pixel PXL may be used to convert image data such that a characteristic deviation between pixels PXL may be compensated for. A second terminal of the third transistor T3 may be electrically connected to the second terminal of the first transistor T1, a first terminal of the third transistor T3 may be electrically connected to the sensing line SENj, and a gate electrode of the third transistor T3 may be electrically connected to the control line CLi. The first terminal of the third transistor T3 may be electrically connected to an initialization power source. The third transistor T3 is an initialization transistor capable of initializing the second node N2. In case that a sensing control signal is supplied from the control line CLi, the third transistor T3 may be turned on to transfer a voltage of the initialization power source to the second node N2. Accordingly, a second storage electrode of the storage capacitor Cst, which is electrically connected to the second node N2, may be initialized.

A first storage electrode of the storage capacitor Cst may be electrically connected to the first node N1, and the second storage electrode of the storage capacitor Cst may be electrically connected to the second node N2. The storage capacitor Cst charges a data voltage corresponding to the data signal supplied to the first node N1 during a frame period. Accordingly, the storage capacitor Cst may store a voltage corresponding to the difference between a voltage of the gate electrode of the first transistor T1 and a voltage of the second node N2.

Although an embodiment in which the light emitting elements LD constituting the light emitting part EMU are all electrically connected in parallel has been illustrated in FIG. 5, the disclosure is not limited thereto. In some embodiments, the light emitting part EMU may be configured to include at least one serial stage (or stage) including light emitting elements LD electrically connected in parallel to each other. For example, the light emitting part EMU may be configured in a series-parallel hybrid structure as shown in FIG. 6.

Referring to FIG. 6, the light emitting part EMU may include first and second serial stages SET1 and SET2 sequentially electrically connected between the first and second driving power sources VDD and VSS. Each of the first and second serial stages SET1 and SET2 may include two electrodes PE1 and CTE1 or CTE2 and PE2 constituting an electrode pair of the corresponding serial stage, and light emitting elements LD electrically connected in parallel in the same direction between the two electrodes PE1 and CTE1 or CTE2 and PE2.

The first serial stage SET1 (or first stage) includes the first pixel electrode PE1 and a first intermediate electrode CTE1, and may include at least one first light emitting element LD1 electrically connected between the first pixel electrode PE1 and the first intermediate electrode CTE1. The first serial stage SET1 may include a reverse light emitting element LDr electrically connected in a direction opposite to that in

which the first light emitting element LD1 is connected between the first pixel electrode PE1 and the first intermediate electrode CTE1.

15

The second serial stage SET2 (or second stage) includes a second intermediate electrode CTE2 and the second pixel 5 electrode PE2, and may include at least one second light emitting element LD2 electrically connected between the second intermediate electrode CTE2 and the second pixel electrode PE2. The second serial stage SET2 may include a reverse light emitting element LDr electrically connected in 10 a direction opposite to that in which the second light emitting element LD2 is connected between the second intermediate electrode CTE2 and the second pixel electrode PE2.

The first intermediate electrode CTE1 and the second 15 intermediate electrode CTE2 may be electrically and/or physically connected to each other. The first intermediate electrode CTE1 and the second intermediate electrode CTE2 may constitute an intermediate electrode CTE which electrically connects the first serial stage SET1 and the second 20 serial stage SET2, which are consecutive.

In the above-described embodiment, the first pixel electrode PE1 of the first serial stage SET1 may be an anode of each pixel PXL, and the second pixel electrode PE2 of the second serial stage SET2 may be a cathode of the corresponding pixel PXL.

As described above, the light emitting part EMU of the pixel PXL, which includes the serial stages (or first and second serial stages) SET1 and SET2 (or the light emitting elements LD) electrically connected in the series-parallel 30 hybrid structure, may easily control driving current/voltage conditions to be suitable for specifications of a product to which the light emitting part EMU is applied.

The light emitting part EMU of the pixel PXL, which includes the first and second serial stages SET1 and SET2 35 (or the light emitting elements LD) electrically connected in the series-parallel hybrid structure, may decrease a driving current, as compared with a light emitting part having a structure in which light emitting elements LD are electrically connected only in parallel. The light emitting part 40 EMU of the pixel PXL, which includes the first and second serial stages SET1 and SET2 electrically connected in the series-parallel hybrid structure, may decrease a driving voltage applied to both ends of the light emitting part EMU, as compared with a light emitting part having a structure in 45 which the same number of light emitting elements LD are electrically connected only in series. Further, the light emitting part EMU of the pixel PXL, which includes the first and second serial stages SET1 and SET2 (or the light emitting elements LD) electrically connected in the series-parallel 50 hybrid structure, may include a larger number of light emitting elements LD between the same numbers of electrodes PE, CTE1, CTE2, and PE2, as compared with a light emitting part having a structure in which serial stages (or stages) are electrically connected in series. Thus, the light 55 emission efficiency of the light emitting element LD may be improved, and the ratio of light emitting elements LD which do not emit light because of a failure may be relatively decreased even in case that the failure occurs in a specific serial stage (or stage). Accordingly, the deterioration of the 60 light emission efficiency of light emitting elements LD may be reduced.

Although an embodiment in which the first to third transistors T1, T2, and T3 included in the pixel circuit PXC are N-type transistors is illustrated in FIGS. 5 and 6, the 65 disclosure is not limited thereto. For example, at least one of the first to third transistors T1, T2, and T3 may be replaced

with a P-type transistor. Although an embodiment in which the light emitting part EMU is electrically connected between the pixel circuit PXC and the second driving power source VSS is illustrated in FIGS. 5 and 6, the light emitting

16

part EMU may be electrically connected between the first driving power source VDD and the pixel circuit PXC.

The structure of the pixel circuit PXC may be variously modified and embodied. In an example, the pixel circuit PXC may additionally further include at least one transistor element such as a transistor element for initializing the first node N1 and/or a transistor element for controlling an emission time of the light emitting elements LD, or other circuit elements such as a boosting capacitor for boosting the voltage of the first node N1.

The structure of a pixel PXL applicable to the disclosure is not limited to the embodiments shown in FIGS. 5 and 6, and the corresponding pixel PXL may have various structures. For example, each pixel PXL may be configured in a passive type light emitting display device, etc. In this case, the pixel circuit PXC may be omitted, and both end portions of the light emitting element LD included in the light emitting part EMU may be directly electrically connected to the scan line Si, the data line Dj, the first power line PL1 to which the first driving power source VDD is applied, the second power line PL2 to which the second driving power source VSS is applied, and/or a control line.

FIGS. 5 and 6 illustrate that the light emitting element LD forming the light source of the pixel PXL includes micro inorganic light emitting diodes which are small to a degree of micrometer scale or nanometer scale and are manufactured in a structure in which a nitride-based semiconductor is grown. However, the disclosure is not limited thereto. In some embodiments, the light emitting element LD of the pixel PXL may include an organic light emitting diode.

FIG. 7 is a plan view schematically illustrating the pixel PXL shown in FIG. 4.

In FIG. 7, illustration of transistors electrically connected to light emitting elements LD and signal lines electrically connected to the transistors will be omitted for convenience.

In an embodiment, for convenience of description, a lateral direction (or horizontal direction) on a plane (or in a plan view) is represented as a first direction DR1, a longitudinal direction (or vertical direction) on a plane is represented as a second direction DR2, and a thickness direction of a substrate SUB on a section (or a cross-sectional view) is represented as a third direction DR3. The first to third directions DR1, DR2, and DR3 may mean directions respectively indicated by the first to third directions DR1, DR2, and DR3.

Referring to FIGS. 4 to 7, the pixel PXL may be located in a pixel area PXA arranged (or provided) on the substrate SUB. The pixel area PXA may include an emission area EMA and a non-emission area NEMA.

The pixel PXL may include a bank BNK located in the non-emission period NEMA and a color filter CF located in the emission area EMA.

The bank BNK is structure which defines (or partitions) a pixel area PXA (or emission area EMA) of each of the pixel PXL and adjacent pixels PXL adjacent thereto, and may be, for example, a pixel defining layer.

In an embodiment, the bank BNK may be a pixel defining layer or a dam structure, which defines each emission area EMA to which light emitting elements LD are to be supplied, in a process of supplying (or inputting) the light emitting elements LD to the pixel PXL. In an example, the emission area EMA of the pixel PXL is partitioned by the bank BNK, so that a mixed liquor (e.g., ink) including a

desired amount and/or a desired kind of light emitting elements LD may be supplied (or input) to the emission area EMA. The bank BNK may be a pixel defining layer which finally defines each emission area EMA to which a color conversion layer (not shown) is to be supplied, in a process of supplying the color conversion layer to the pixel PXL.

The bank BNK includes at least one light blocking material and/or at least one reflective material (or scattering material) to prevent a light leakage defect in which light (or beam) is leaked between the pixel PXL and pixels PXL 10 adjacent thereto. In some embodiments, the bank BNK may include a transparent material (or substance). In an example, the transparent material may include polyamides resin, polyimides resin, etc., but the disclosure is not limited thereto. In an embodiment, a reflective material layer may be separately 15 provided and/or formed on the bank BNK so as to further improve the efficiency of light emitted from the pixel PXL.

The bank BNK may include at least one opening OP exposing components located thereunder in the pixel area PXA. In an example, the bank BNK may include a first 20 opening OP1 and a second OP2, which expose the components located under the bank BNK. In an embodiment, the emission area EMA of the pixel PXL and the first opening OP1 of the bank BNK may correspond to each other.

In the pixel area PXA, the second opening OP2 is located 25 to be spaced from the first opening OP1 and may be located adjacent to a side, e.g., an upper side of the pixel area PXA. In an embodiment, the second opening OP2 may be an electrode separation area in which at least one alignment electrode AL (or electrode) is separated from at least one 30 alignment electrode AL provided in pixels PXL adjacent to the pixel PXL in the second direction DR2.

The color filter CF may be located above light emitting elements LD to correspond to the emission area EMA of the pixel PXL. The color filter CF may allow light advancing 35 toward the color filter CF to be selectively transmitted therethrough. The color filter CF may include a red color filter, a green color filter, or a blue color filter. In an example, in case that the pixel PXL shown in FIG. 7 is a red pixel, the color filter CF may include the red color filter. In case that 40 the pixel PXL is a green pixel, the color filter CF may include the green color filter. In case that the pixel PXL is a blue pixel, the color filter CF may include the blue color filter. The color filter CF may be located in the emission area EMA of the pixel PXL, corresponding to the first opening 45 CP1

The pixel PXL may include pixel electrodes PE provided in at least the emission area EMA, light emitting elements LD electrically connected to the pixel electrodes PE, and alignment electrodes AL provided at positions corresponding to the pixel electrodes PE. In an example, the pixel PXL may include first and second pixel electrodes PE1 and PE2, light emitting elements LD, and first and second alignment electrodes AL1 and AL2. The number, shape, size, and arrangement structure of each of the pixel electrodes PE 55 and/or the alignment electrodes AL may be variously changed according to the structure of the pixel PXL (particularly, the light emitting part EMU).

In an embodiment, the alignment electrodes AL, the light emitting elements LD, and the pixel electrodes PE may be 60 sequentially provided with respect to a surface of the substrate SUB on which the pixel PXL is provided, but the disclosure is not limited thereto. In some embodiments, the positions and formation order of electrode patterns constituting the pixel PXL (or the light emitting part) may be 65 variously changed. A stacking structure of the pixel PXL will be described below with reference to FIGS. 8 to 10.

The alignment electrodes AL may include the first alignment electrode AL1 (or first electrode) and the second alignment electrode AL2 (or second electrode), which are arranged to be spaced from each other in the first direction

18

At least one of the first and second alignment electrodes AL1 and AL2 may be separated from another electrode (e.g., an alignment electrode AL provided in each of adjacent pixels PXL adjacent to each other in the second direction DR2) in the second opening OP2 (or the electrode separation area) after the light emitting elements LD are supplied and aligned in the pixel area PXA in a manufacturing process of the display device. In an example, one end (or first end) of the first alignment electrode AL1 may be separated from a first alignment electrode AL1 of a pixel PXL located at an upper side of the corresponding pixel PXL in the second direction DR2 in the second opening OP2.

The first alignment electrode AL1 may be electrically connected to the first transistor T1 described with reference to FIGS. 5 and 6 through a first contact part CNT1, and the second alignment electrode AL2 may be electrically connected to the second driving power source VSS (or the second power line PL2) described with reference to FIGS. 5 and 6 through a second contact part CNT2.

The first contact part CNT1 may be formed by removing a portion of at least one insulating layer located between the first alignment electrode AL1 and the first transistor T1, and the second contact part CNT2 may be formed by removing a portion of at least one insulating layer located between the second alignment electrode AL2 and the second power line PL2. The first contact part CNT1 and the second contact part CNT2 may be located in the non-emission area NEMA to overlap the bank BNK. However, the disclosure is not limited thereto. In some embodiments, the first and second contact parts CNT1 and CNT2 may be located in the second opening OP2 as the electrode separation area or be located in the emission area EMA.

Each of the first alignment electrode AL1 and the second alignment electrode AL2 may receive a signal (or an alignment signal) transferred from an alignment pad (not shown) located in the non-display area NDA in a process of aligning the light emitting elements LD. For example, the first alignment electrode AL1 may receive a first alignment signal (or first alignment voltage) transferred from a first alignment pad, and the second alignment electrode AL2 may receive a second alignment signal (or second alignment voltage) transferred from a second alignment pad. The above-described first and second alignment signals may be signals having a voltage difference and/or a phase difference to a degree to which the light emitting elements LD may be aligned between the first and second alignment electrodes AL1 and AL2. At least one of the first and second alignment signals may be an AC signal, but the disclosure is not limited thereto.

Each alignment electrode AL may be provided in a bar-like shape having a constant width in the second direction DR2, but the disclosure is not limited thereto. In some embodiments, each alignment electrode AL may have or may not have a bending part in the non-emission area NEMA and/or the second opening OP2 as the electrode separation area. The shape and/or the size of each alignment electrode AL in the other area except the emission area EMA is not particularly limited, and may be variously changed.

At least two to a few tens of light emitting elements LD may be aligned and/or provided in the pixel area PXA, but the number of the light emitting elements LD is not limited thereto. In some embodiments, the number of light emitting

elements LD aligned and/or provided in the emission area EMA (or the pixel area PXA) may be variously changed.

The light emitting elements LD may be disposed between the first alignment electrode AL1 and the second alignment electrode AL2. Each of the light emitting elements LD may 5 be the light emitting element LD described with reference to FIGS. 1 and 3. Each of the light emitting elements LD may include a first end portion EP1 (or one end portion) and a second end portion EP2 (or the other end portion), which are located at both ends of the light emitting element LD in a length direction thereof. In an embodiment, the second semiconductor layer 13 including a p-type semiconductor layer may be located at the first end portion EP1, and the first semiconductor layer 11 including an n-type semiconductor layer may be located at the second end portion EP2. The 15 light emitting elements LD may be electrically connected in parallel to each other between the first alignment electrode AL1 and the second alignment electrode AL2.

Each of the light emitting elements LD may emit any of colored light and/or white light. Each of the light emitting 20 elements LD may be aligned between the first alignment electrode AL1 and the second alignment electrode AL2 such that the length direction thereof is parallel to the first direction DR1. In some embodiments, at least some of the light emitting elements may be aligned between the first 25 alignment electrode AL1 and the second alignment electrode AL2 not to be completely parallel to the first direction DR1. In an example, some light emitting elements LD may be aligned between the first alignment electrode AL1 and the second alignment electrode AL2 to be inclined with respect 30 to the first direction DR1. The light emitting elements LD may be provided in a form in which the light emitting elements LD are sprayed or dispersed in a solution, to be input (or supplied) to the pixel area PXA (or the emission area EMA).

The light emitting elements LD may be input (or supplied) to the pixel area PXA (or the emission area EMA) by an inkjet printing process, a slit coating process, or various processes. In an example, the light emitting elements LD may be mixed with a volatile solvent, to be input (or 40 supplied) to the pixel area PXA by an inkjet printing process or a slit coating process. In case that a corresponding alignment signal is applied to each of the first alignment electrode AL1 and the second alignment electrode AL2, an electric field may be formed between the first alignment 45 electrode AL1 and the second alignment electrode AL2. Therefore, the light emitting elements LD may be aligned between the first alignment electrode AL1 and the second alignment electrode AL2. After the light emitting elements LD are aligned, the solvent may be volatilized or be 50 removed by another process, so that the light emitting elements LD may be stably aligned between the first alignment electrode AL1 and the second alignment electrode AL2.

The pixel electrodes PE may be provided in at least the 55 emission area EMA, and each of the pixel electrodes PE may be provided at a position corresponding to at least one alignment electrode AL and at least one light emitting element LD. For example, each pixel electrode PE may be formed on each alignment electrode AL and corresponding 60 light emitting elements LD to overlap the alignment electrode AL and the corresponding light emitting element LD. Therefore, the pixel electrode PE may be electrically connected to at least the light emitting elements LD.

The first pixel electrode PE1 may be formed on the first 65 alignment electrode AL1 and the first end portion EP1 of each of the light emitting elements LD to be electrically

connected to the first end portion EP1 of each of the light emitting elements LD. The first pixel electrode PE1 may be electrically and/or physically connected to the first alignment electrode AL1 exposed by removing a portion of at least one insulating layer located between the first pixel electrode PE1 and the first alignment electrode AL1 in at least the emission area EMA, while directly contacting the first alignment electrode AL1. Although it has been described that a connection point (or contact point) of the first pixel electrode PE1 and the first alignment electrode AL1 is located in the emission area EMA, the disclosure is not limited thereto. In some embodiments, the connection point (or contact point) of the first pixel electrode PE1 and the first alignment electrode AL1 may be located in the non-emission area NEMA, e.g., the second opening OP2 as the electrode separation area. An embodiment in which the connection point (or contact point) of the first pixel electrode PE1 and the first alignment electrode AL1 is located in the

20

The first pixel electrode PE1 may have a bar-like shape extending in the second direction DR2, but the disclosure is not limited thereto. In some embodiments, the shape of the first pixel electrode PE1 may be variously changed within a range in which the first pixel electrode PE1 is electrically and/or physically stably connected to the first end portion EP1 of each of the light emitting elements LD. The shape of the first pixel electrode PE1 may be variously changed by considering a connection relationship between the first pixel electrode PE1 and the first alignment electrode AL1 disposed on the bottom thereof.

second opening OP2 will be described below with reference

to FIGS. 15 to 17.

The second pixel electrode PE2 may be formed on the second alignment electrode AL2 and the second end portion EP2 of each of the light emitting elements LD to be electrically connected to the second end portion EP2 of each of the light emitting elements LD. The second pixel electrode PE2 may be electrically and/or physically connected to the second alignment electrode AL2 exposed by removing a portion of at least one insulating layer located between the second pixel electrode PE2 and the second alignment electrode AL2 in at least the light emitting area EMA, while contacting the second alignment electrode AL2. A connection point (or contact point) of the second pixel electrode PE2 and the second alignment electrode AL2 may be located in the emission area EMA or the non-emission area NEMA.