US 20210090902A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2021/0090902 A1 CHO et al.

## Mar. 25, 2021 (43) **Pub. Date:**

### (54) PRINTED CIRCUIT BOARD

- (71) Applicant: LG INNOTEK CO., LTD., Seoul (KR)

- (72) Inventors: Sung Oh CHO, Seoul (KR); Yoon Tai KIM, Seoul (KR)

- (21) Appl. No.: 16/952,782

- (22) Filed: Nov. 19, 2020

#### **Related U.S. Application Data**

(63) Continuation of application No. 16/910,959, filed on Jun. 24, 2020, now Pat. No. 10,872,786, which is a continuation of application No. 16/662,583, filed on Oct. 24, 2019, now Pat. No. 10,734,248, which is a continuation of application No. 16/393,323, filed on Apr. 24, 2019, now Pat. No. 10,490,421, which is a continuation of application No. 16/146,104, filed on Sep. 28, 2018, now Pat. No. 10,347,507.

#### (30)**Foreign Application Priority Data**

| Sep. 29, 2017 | (KR) | 10-2017-0127395 |

|---------------|------|-----------------|

| Jun. 1, 2018  | (KR) | 10-2018-0063237 |

#### **Publication Classification**

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

|      | H01L 21/48  | (2006.01) |

|      | H01L 23/498 | (2006.01) |

(52)U.S. Cl. CPC .... H01L 21/4853 (2013.01); H01L 23/49866 (2013.01); H01L 23/49822 (2013.01); H01L 23/49816 (2013.01); H01L 2924/15311 (2013.01); H01L 2924/181 (2013.01); H01L 2224/48091 (2013.01); H01L 2224/48227 (2013.01); H01L 23/49811 (2013.01)

#### (57)ABSTRACT

A printed circuit board according to an embodiment includes: an insulating layer; a first pad disposed on a first surface of the insulating layer; a first conductive layer disposed on the first pad and including gold (Au); a second pad disposed on a second surface of the insulating layer; and a second conductive layer disposed on the second pad and including gold (Au), wherein the first conductive layer is a conductive layer connected to a wire, the second conductive layer is a conductive layer connected to a solder, and the first conductive layer is thicker than the second conductive layer.

FIG. 2

FIG. 3

FIG. 6

FIG. 8

#### PRINTED CIRCUIT BOARD

#### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application is a continuation of U.S. application Ser. No. 16/910,959, filed Jun. 24, 2020; which is a continuation of U.S. application Ser. No. 16/662,583, filed Oct. 24, 2019, now U.S. Pat. No. 10,734,248, issued Aug. 4, 2020; which is a continuation of U.S. application Ser. No. 16/393,323, filed Apr. 24, 2019, now U.S. Pat. No. 10,490, 421, issued Nov. 26, 2019; which is a continuation of U.S. application Ser. No. 16/146,104, filed Sep. 28, 2018, now U.S. Pat. No. 10,347,507, issued Jul. 9, 2019; which claims the benefit under 35 U.S.C. §119 to Korean Patent Application Nos. 10-2017-0127395, filed Sep. 29, 2017; and 10-2018-0063237, filed Jun. 1, 2018, all of which are hereby incorporated in their entirety.

#### TECHNICAL FIELD

**[0002]** The present invention relates to a printed circuit board, and more particularly, to a printed circuit board including an upper conductive layer and a lower conductive layer having different thicknesses at upper and lower portions, and a method of manufacturing the same.

### BACKGROUND

**[0003]** A printed circuit board (PCB) is formed by printing a circuit line pattern at an electrical insulating substrate with a conductive material such as copper, and thus the PCB refers to a board just before electronic components are mounted thereon. That is, in order to densely mount various types of electronic components on a planar surface, the PCB refers to a circuit board having a planar surface on which a mounting position of each component is fixed and a circuit pattern connecting the components is fixedly printed.

**[0004]** In general, a surface processing method for a circuit pattern included in the above-described PCB uses an organic solderability preservative (OSP) method, an electrolytic nickel/gold method, an electrolytic nickel/gold-cobalt alloy method, an electroless nickel/palladium/gold method, etc.

**[0005]** Here, the above-described surface processing methods vary depending on a use thereof, and the use includes, for example, soldering, wire bonding, and a connector.

**[0006]** FIG. **1** is a view illustrating a printed circuit board according to the related art.

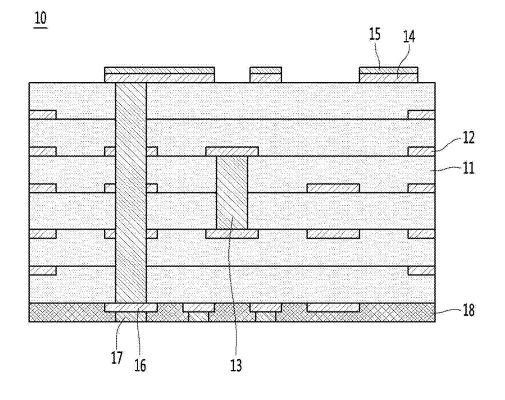

[0007] Referring to FIG. 1, a printed circuit board 10 includes a plurality of insulating layers 11, a circuit pattern 12 disposed at a surface of the plurality of insulating layers 11, and a via 13 configured to pass through at least one among the plurality of insulating layers 11 and electrically connect circuit patterns disposed at different layers.

**[0008]** In addition, a first pad **14** is disposed on an insulating layer disposed at an uppermost layer among the plurality of insulating layers **11**, and an upper conductive layer **15** is disposed on the first pad **14**.

**[0009]** Further, a second pad **16** is disposed under an insulating layer disposed at a lowermost layer among the plurality of insulating layers **11**, and a lower conductive layer **17** is disposed under the second pad **16**.

**[0010]** Furthermore, a protective layer **18** having an opening, through which at least a part of a surface of the lower conductive layer **17** is exposed, is disposed under the insulating layer disposed at the lowermost layer.

**[0011]** In the above-described printed circuit board **10**, pads having different functions are disposed at the uppermost and lowermost portions of the plurality of insulating layers **11**, respectively. That is, the first pad **14** may be a pad for wire bonding, which is electrically connected to an electronic component (not shown) via a wire. In addition, the second pad **16** may be a pad for soldering, which is electrically connected to an external substrate via an adhesive member (not shown).

**[0012]** The upper conductive layer **15** and the lower conductive layer **17** are disposed at surfaces of the first pad **14** and the second pad **16**, respectively. The upper conductive layer **15** and the lower conductive layer **17** are disposed to perform wire bonding or soldering together with a purpose of inhibiting oxidation of the pad.

[0013] However, although thicknesses of the upper conductive layer and the lower conductive layer are different depending on the use of the pad, the upper conductive layer 15 and the lower conductive layer 17 are formed to have the same thickness in the related art. At this point, the upper conductive layer 15 and the lower conductive layer 17 generally include gold (Au). Therefore, in the related art, the thickness of the lower conductive layer 17 is formed based on the thickness required for the upper conductive layer 15, so that there is a problem that a manufacturing cost due to unnecessary consumption of gold is increased. Further, in the related art, in order to reduce a plating thickness of the upper conductive layer or the lower conductive layer including gold, copper/nickel is mainly formed as an underlying layer, so that there is a problem that a product thickness increases due to an increase in the layer.

#### SUMMARY

**[0014]** In an embodiment according to the present invention, there is provided a printed circuit board having a new structure and a method of manufacturing the same.

**[0015]** In addition, in an embodiment according to the present invention, there is provided a printed circuit board capable of electrolytic-plating an upper conductive layer and a lower conductive layer using a plating seed layer used at the time of forming a pad, and a method of manufacturing the same.

**[0016]** Further, in an embodiment according to the present invention, there is provided a printed circuit board capable of forming an upper conductive layer and a lower conductive layer having different thicknesses depending on a use of a pad, and a method of manufacturing the same.

**[0017]** Furthermore, in an embodiment according to the present invention, there is provided a printed circuit board capable of directly forming an upper conductive layer and a lower conductive layer including gold on a pad including copper, and a method of manufacturing the same.

**[0018]** In addition, in an embodiment according to the present invention, there is provided a printed circuit board having a pad including a first pattern having at least a part of an upper surface having a curvature and a second pattern filling the curvature portion of the first pattern, and a method of manufacturing the same.

**[0019]** Further, in the present invention, there is provided a printed circuit board including an upper conductive layer and a lower conductive layer having a portion on a pad, which protrudes from a side surface of the pad to an outside thereof and at least a part of which is not in contact with the pad, and a method of manufacturing the same.

**[0020]** Furthermore, the objectives of the present invention are not limited to the above, and other objectives will be clearly understood to those skilled in the art from the following descriptions.

**[0021]** A printed circuit board according to an embodiment includes: an insulating layer; a first pad disposed on a first surface of the insulating layer; a first conductive layer disposed on the first pad and including gold (Au); a second pad disposed on a second surface of the insulating layer; and a second conductive layer disposed on the second pad and including gold (Au), wherein the first conductive layer is a conductive layer connected to a wire, the second conductive layer is a conductive layer connected to a solder, and the first conductive layer is thicker than the second conductive layer.

**[0022]** In addition, the insulating layer includes a plurality of insulating layers, the first pad is disposed on an upper surface of an insulating layer disposed at an uppermost portion of the plurality of insulating layers, and the second pad is disposed under a lower surface of an insulating layer disposed at a lowermost portion of the plurality of insulating layers.

**[0023]** Further, the first pad has a narrower width than the second pad.

**[0024]** Furthermore, the first conductive layer has a thickness in a range of 0.2 to 0.8  $\mu$ m, and the second conductive layer has a thickness in a range of 0.05 to 0.3  $\mu$ m.

**[0025]** In addition, each of the first pad and the second pad includes a plating seed layer disposed at a surface of the uppermost insulating layer or the lowermost insulating layer and including copper, a first pattern disposed on the plating seed layer and including copper, and a second pattern disposed on the first pattern and including copper.

**[0026]** Further, the first pattern is thicker than the second pattern.

**[0027]** Furthermore, a central portion of an upper surface of the first pattern is located lower than an outer side portion thereof.

**[0028]** In addition, a part of a lower surface of the second pattern is located lower than a part of the upper surface of the first pattern.

**[0029]** Further, each of the first and second conductive layers includes a first region in contact with the second pattern, and a second region extending from the first region and spaced apart from the plating seed layer, the first pattern and the second pattern, and the second region is not in contact with the plating seed layer, the first pattern, and the second pattern.

**[0030]** Furthermore, the second region includes a first portion in direct contact with an upper surface of the second pattern and a second portion in direct contact with a side surface of the second pattern.

**[0031]** In addition, the first conductive layer is disposed in plural on the first surface of the insulating layer, and the second conductive layer is disposed in plural under the second surface of the insulating layer.

**[0032]** Further, a printed circuit board according to an embodiment includes: an insulating layer; a pad disposed on the insulating layer; and a conductive layer disposed on the pad, wherein the conductive layer includes a first region in direct contact with an upper surface of the pad, a second region extending from the first region and in direct contact

with a side surface of the pad, and a third region extending from the second region and spaced apart from the pad.

[0033] Furthermore, a width of the upper surface of the pad is larger than that of a lower surface thereof.

**[0034]** In addition, the pad includes a first pad disposed on a first surface of the insulating layer, and a second pad disposed on a second surface of the insulating layer opposite to the first surface, and the conductive layer includes a first conductive layer disposed on the first pad and including gold (Au), and a second conductive layer disposed on the second pad and including gold (Au), and each of the first and second conductive layers includes the first to third regions.

**[0035]** Further, a thickness of the first region in a longitudinal direction of the first conductive layer is larger than that of the first region in a longitudinal direction of the second conductive layer.

**[0036]** Furthermore, a thickness of the second region in a lateral direction of the first conductive layer is larger than that of the second region in a lateral direction of the second conductive layer.

**[0037]** In addition, each of the first pad and the second pad includes a plating seed layer disposed on the first surface or the second surface of the insulating layer and including copper, a first pattern disposed on the plating seed layer and including copper, and a second pattern disposed on the first pattern and including copper.

**[0038]** Further, an end portion of the third region of the first conductive layer is located higher than an outer side region of an upper surface of the first pattern constituting the first pad, and an end portion of the third region of the second conductive layer is located lower than an outer side region of a lower surface of the first pattern constituting the second pad.

**[0039]** Furthermore, a thickness of the third region in a longitudinal direction of the first conductive layer is different from that of the third region in a longitudinal direction of the second conductive layer.

[0040] Meanwhile, a method of manufacturing a printed circuit board according to an embodiment includes: stacking a plurality of insulating layers and forming a circuit pattern at a surface of the plurality of insulating layers; forming first and second plating seed layers at an insulating layer disposed at an uppermost portion and an insulating layer disposed at a lowermost portion of the plurality of insulating layers, respectively; forming a first pad and a second pad on the first and second plating seed layers, respectively; and proceeding electrolytic plating in a plating tank in which plating spaces on the surface on which the first pad is formed and on the surface on which the second pad is formed are separated to form a first conductive layer on the first pad and a second conductive layer on the second pad, wherein the first conductive layer is formed to have a thickness greater than that of the second conductive layer in the same plating tank in which the second conductive layer is formed.

**[0041]** In addition, the forming of the first conductive layer and the second conductive layer includes differently applying a plating condition in which the first conductive layer is formed and a plating condition in which the second conductive layer is formed to simultaneously form the first conductive layer and the second conductive layer having different thicknesses.

**[0042]** Further, each of the first and second conductive layers is formed of a metal including gold.

**[0043]** Furthermore, the forming of the first pad and the second pad includes forming a first pattern, formed of a metal including copper, on the first and second plating seed layers, respectively, preprocessing an upper surface of the formed first pattern to have a curvature, and forming a second pattern, formed of a metal including copper, having a thickness thinner than the first pattern on the preprocessed first pattern.

**[0044]** In addition, a part of a lower surface of the second pattern is located lower than that of the upper surface of the first pattern.

**[0045]** Further, each of the first and second conductive layers includes a first region in contact with the second pattern, and a second region extending from the first region and spaced apart from the plating seed layer, the first pattern and the second pattern, wherein the second region is not in contact with the plating seed layer, the first pattern, and the second pattern.

#### ADVANTAGEOUS EFFECTS

**[0046]** According to an embodiment of the present invention, since a second pattern filling an edge region of a first pattern is formed on the first pattern, and an upper conductive layer and a lower conductive layer are formed on the formed second pattern, it is possible to solve a reliability problem that occurs when the upper conductive layer or the lower conductive layer permeates between a mask.

**[0047]** In addition, according to an embodiment of the present invention, an upper conductive layer and a lower conductive layer are formed after the second pattern is formed, so that a portion, protruding from a side surface of a pad to an outside thereof, of the upper conductive layer and the lower conductive layer may be minimized, and thus structural reliability (stability) of the upper conductive layer and the lower conductive layer can be secured.

[0048] Further, according to an embodiment of the present invention, an upper conductive layer and a lower conductive layer are formed after the second pattern is formed, so that a portion of a lower surface of the second pattern is disposed to be lower than an upper surface of the first pattern, and a thickness of the second pattern is thinner than that of the first pattern, and thus overspreading itself of the upper conductive layer and the lower conductive layer can be inhibited. [0049] Furthermore, according to an embodiment of the present invention, an upper conductive layer and a lower conductive layer including gold (Au) are formed by using a plating seed layer used at the time of forming the first pattern

and the second pattern, so that a nickel (Ni) seed layer which has served as a seed layer of a gold (Au) conductive layer in the related art may be removed, and thus, not only a thickness of a printed circuit board product can be reduced, but also economic efficiency of a product can be improved by technical effect due to efficiency of a process.

**[0050]** In addition, according to an embodiment of the present invention, a nickel layer may be removed from a pattern structure, and thus not only electrical conductivity of a pattern can be improved, but also a problem of interface property occurring between copper and nickel constituting the pattern can be solved.

**[0051]** Further, according to an embodiment of the present invention, a thickness of an upper conductive layer disposed on a pad for wire bonding and a thickness of a lower conductive layer disposed on a pad for soldering are differently applied, so that a consumption cost of gold used for the

upper conductive layer and the lower conductive layer may be reduced, and thus a thickness can be reduced.

**[0052]** Furthermore, according to an embodiment of the present invention, an upper conductive layer and a lower conductive layer having different thicknesses may be formed by one simultaneous process, and thus efficiency in a manufacturing process can be improved.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0053]** FIG. 1 is a view illustrating a printed circuit board according to the related art.

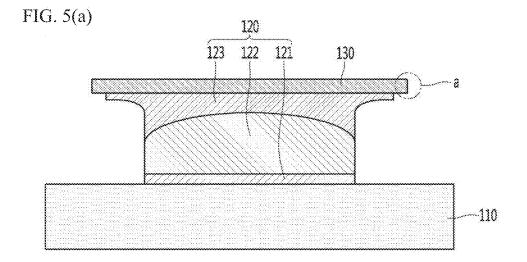

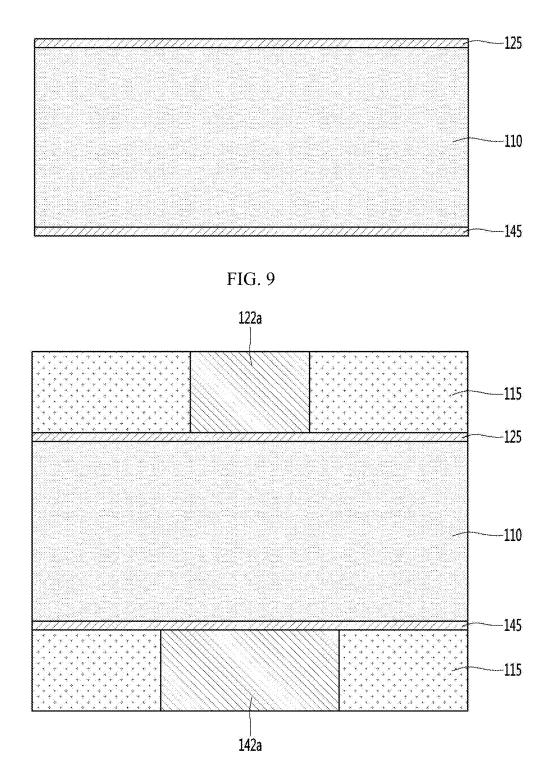

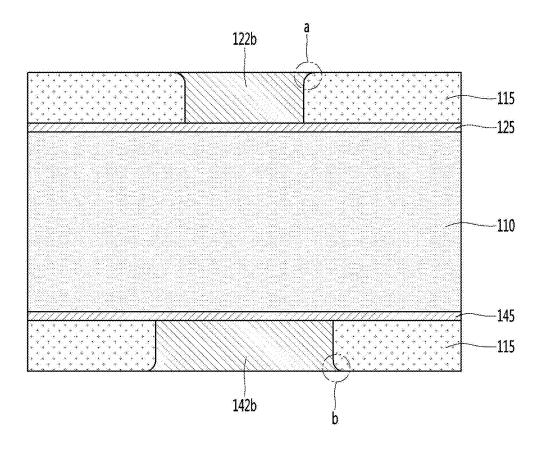

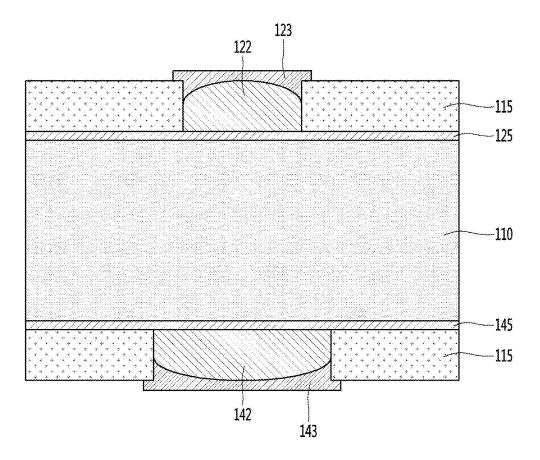

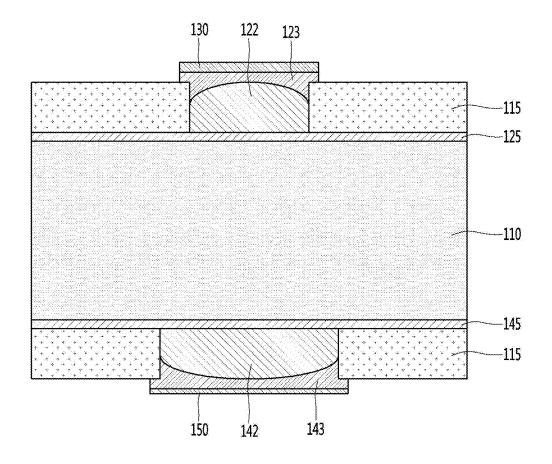

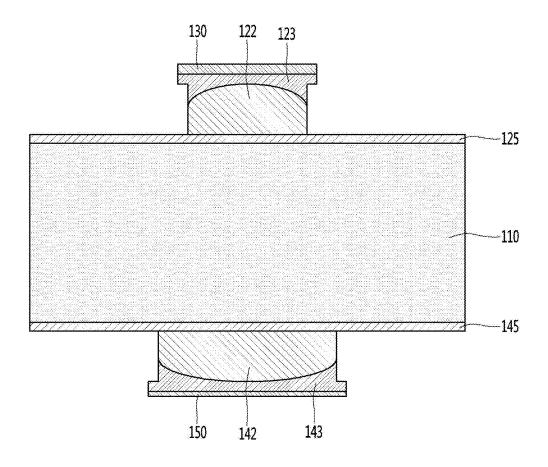

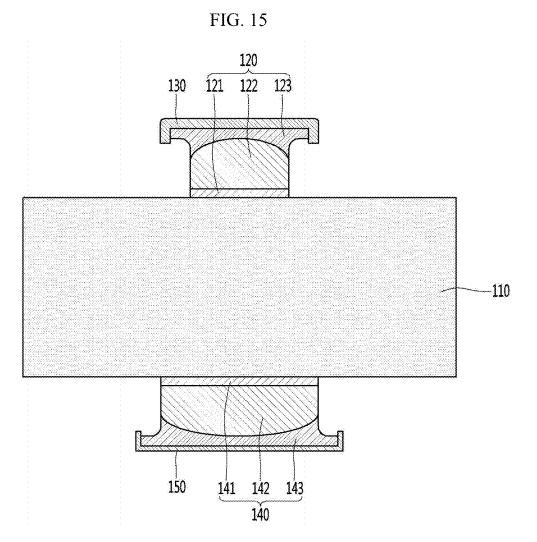

[0054] FIG. 2 is a view illustrating a printed circuit board 100 according to an embodiment of the present invention. [0055] FIG. 3 is a view specifically illustrating a first pad 120 and an upper conductive layer 130 shown in FIG. 2

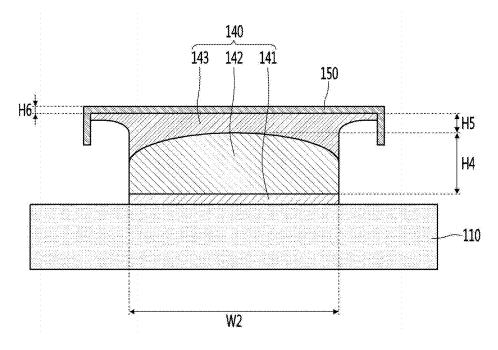

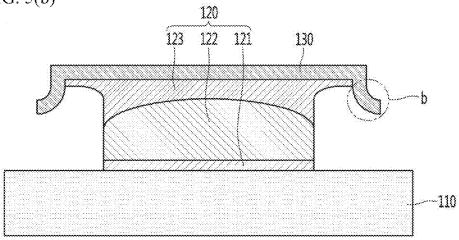

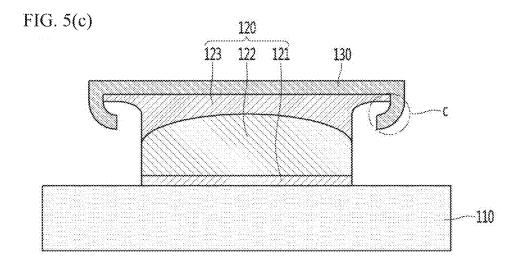

[0056] FIG. 4 is a view specifically illustrating a second pad 140 and a lower conductive layer 150 shown in FIG. 2. [0057] FIGS. 5(a)-5(c) are views illustrating a modified example of an overhang structure shown in FIGS. 3 and 4. [0058] FIG. 6 is a view illustrating a plating apparatus according to an embodiment of the present invention, and FIG. 7 is a view illustrating a detailed structure of a substrate support of the plating apparatus shown in FIG. 6.

**[0059]** FIGS. 8 to 15 are views for explaining a process sequence of a method of manufacturing a printed circuit board according to an embodiment of the present invention.

#### DETAILED DESCRIPTION OF THE EMBODIMENTS

**[0060]** Hereinafter, embodiments of the present invention will be described in detail with reference to the accompanying drawings so that a person skilled in the art to which the present invention belongs can easily carry out. However, the present invention may be embodied in many different forms and is not limited to the embodiments described herein.

**[0061]** Throughout the specification, when a part is referred to as "including" an element, it means that the part may include other elements as well without excluding the other elements unless specifically stated otherwise.

**[0062]** Further, structures and elements which do not relate to the detail description are not shown in the drawings to clearly describe the present invention, thicknesses may be exaggerated to clearly explain various layers and regions, and similar elements in the following description are designated by similar reference numerals.

**[0063]** It will be understood that when a portion such as a layer, a film, a region, a plate or the like is referred to as being "on" another portion, it can be "directly formed on" another portion, or a third portion can be interposed between the portions. Otherwise, when a portion is "directly formed on" another portion, it means that there is no third portion between the portions.

**[0064]** In the present invention, there is provided a new printed circuit board (PCB) on which a surface processing process may be performed after filling corner portions of a pattern, etched by a preprocessing process, based on a flash process and a method of manufacturing the same.

**[0065]** In addition, in the present invention, there is provided a printed circuit board in which an upper conductive layer and a lower conductive layer are simultaneously formed at a pad for wire bonding disposed at an upper portion of a board and a pad for soldering disposed at a lower

portion of the board and have different thicknesses, and a method for manufacturing the same.

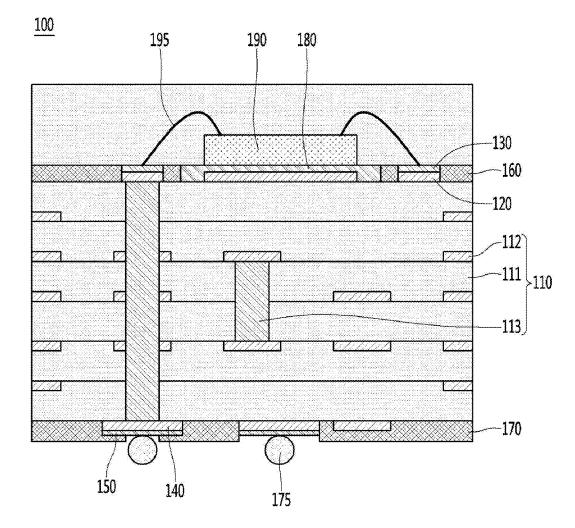

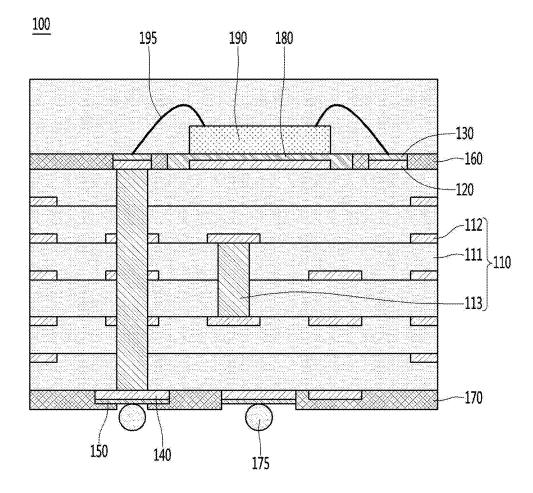

[0066] FIG. 2 is a view illustrating a printed circuit board 100 according to an embodiment of the present invention. [0067] Referring to FIG. 2, the printed circuit board 100 includes an insulating substrate 110, a first pad 120, an upper conductive layer 130, a second pad 140, a lower conductive layer 150, a first passivation layer 160, a second passivation layer 170, an adhesive member 175, a solder paste 180, an electronic component 190, and a wire 195. Here, the upper conductive layer 130 may be referred to as a first conductive layer, and the lower conductive layer 150 may be referred to as a second conductive layer. However, hereinafter, the upper conductive layer and the lower conductive layer will be referred to as an upper conductive layer and a lower conductive layer, respectively, depending on positions in which each of conductive layers is disposed centering on the insulating substrate 110, in order to differentiate each of the conductive layers.

**[0068]** Referring to FIG. 2, the insulating substrate 110 may have a flat plate structure. The insulating substrate 110 may be a printed circuit board (PCB). Here, the insulating substrate 110 may be implemented as a single substrate, and alternatively, may be implemented as a multilayer substrate in which a plurality of insulating layers are sequentially stacked.

**[0069]** Accordingly, the insulating substrate **110** includes a plurality of insulating layers **111**. As shown in FIG. **2**, the plurality of insulating layers **111** may include a first insulating layer, a second insulating layer, a third insulating layer, a fourth insulating layer, a fifth insulating layer, and a sixth insulating layer from an uppermost portion. In addition, a circuit pattern **112** may be disposed at each of surfaces of the first to sixth insulating layers.

**[0070]** That is, the plurality of insulating layers **111** is a substrate on which an electrical circuit capable of changing wirings is disposed and may include all of printing, a wiring plate, and an insulating substrate which are formed of an insulating material which is able to form a circuit pattern **112** at a surface of the insulating layer.

**[0071]** The plurality of insulating layers **111** may be rigid or flexible. For example, the insulating layer **111** may include glass or plastic. Specifically, the insulating layer **111** may include a chemically tempered/semi-tempered glass, such as soda lime glass, aluminosilicate glass, etc., a tempered or flexible plastic such as polyimide (PI), polyethylene terephthalate (PET), propylene glycol (PPG), polycarbonate (PC), etc., or sapphire.

**[0072]** Further, the insulating layer **111** may include an optically isotropic film. For example, the insulating layer **111** may include cyclic olefin copolymer (COC), cyclic olefin polymer (COP), optically isotropic PC, optically isotropic polymethylmethacrylate (PMMA), etc.

**[0073]** Furthermore, the insulating layer **111** may be partially bent while having a curved surface. That is, the insulating layer **111** may partially have a plane and may partially be bent while having a curved surface. Specifically, an end portion of the insulating layer **111** may be bent while having a curved surface, or bent or crooked while having a surface with a random curvature.

**[0074]** In addition, the insulating layer **111** may be a flexible substrate having flexibility. Further, the insulating layer **111** may be a curved or bent substrate. At this point, the insulating layer **111** may form a wiring layout for electrical

wirings which connect circuit components based on a circuit design, and electrical conductors may be disposed on an insulating material. Furthermore, electrical components may be mounted on the insulating layer **111**, and the insulating layer **111** may form wirings configured to connect the electrical components to make a circuit, and may mechanically fix the components besides functioning to electrically connect the components.

[0075] Each of the circuit patterns 112 is disposed at the surface of the insulating layer 111. The circuit pattern 112 may be a wiring for transmitting an electrical signal, and may be formed of a metal material having high electrical conductivity. For this, the circuit pattern 112 may be formed of at least one metal material selected from among gold (Au), silver (Ag), platinum (Pt), titanium (Ti), tin (Sn), copper (Cu), and zinc (Zn). In addition, the circuit pattern 112 may be formed of paste or solder paste including at least one metal material selected from among gold (Au), silver (Ag), platinum (Ti), tin (Sn), copper (Cu), and zinc (Zn). In addition, the circuit pattern 112 may be formed of paste or solder paste including at least one metal material selected from among gold (Au), silver (Ag), platinum (Pt), titanium (Ti), tin (Sn), copper (Cu), and zinc (Zn), which are excellent in bonding strength. Preferably, the circuit pattern 112 may be formed of copper (Cu) having high electrical conductivity and a relatively low cost.

**[0076]** The circuit pattern **112** may be formed by a general process of manufacturing a PCB, such as an additive process, a subtractive process, a modified semi additive process (MSAP), a semi additive process (SAP), etc., and detailed descriptions thereof will be omitted herein.

[0077] At least one via 113 is formed in the insulating layer 111. The via 113 is disposed to be passing through at least one of the plurality of insulating layers 111. The via 113 may pass through only one of the plurality of insulating layers 111, and alternatively, may be formed to commonly pass through at least two insulating layers of the plurality of insulating layers 111. Accordingly, the via 113 electrically connects circuit patterns disposed at surfaces of different insulating layers to each other.

**[0078]** The via **113** may be formed by filling, with a conductive material, a through hole (not shown) passing through at least one of the plurality of insulating layers **111**. **[0079]** The through hole may be formed by any one of mechanical, laser, and chemical processing. When the through hole is formed by mechanical processing, a method such as milling, drilling and routing may be used. When the through hole is formed by laser processing, a method of UV or CO<sub>2</sub> laser may be used. And when the through hole is formed by chemical processing, the insulating layer **111** may be opened by using a chemical including aminosilane, ketone, or the like.

**[0080]** Meanwhile, the laser processing is a cutting method in which a part of a material is melted and evaporated by concentrating optical energy at a surface to take a desired shape. Complex formation by a computer program may be easily processed, and composite materials which are difficult to cut by other methods may be processed.

**[0081]** In addition, the processing by the laser may have a cutting diameter of at least 0.005 mm, and has a wide range of thickness that may be processed.

**[0082]** It is preferable to use an yttrium aluminum garnet (YAG) laser or  $CO_2$  laser or ultraviolet (UV) laser as the laser processing drill. The YAG laser is a laser capable of processing both a copper foil layer and an insulating layer, and the  $CO_2$  laser is a laser capable of processing only an insulating layer.

**[0083]** When the through hole is formed, the via **113** is formed by filling the inside of the through hole with a conductive material. The metal material forming the via **113** may be anyone selected from among copper (Cu), silver (Ag), tin (Sn), gold (Au), nickel (Ni), and palladium (Pd). The conductive material may be filled by any one of electroless plating, electrolytic plating, screen printing, sputtering, evaporation, ink jetting, and dispensing, or a combination thereof.

**[0084]** The first pad **120** is disposed on the insulating layer disposed at the uppermost portion of the plurality of insulating layers **111** and the second pad **140** is disposed under the insulating layer disposed at the lowermost portion of the plurality of insulating layers **111**.

[0085] In other words, the first pad 120 is disposed on the uppermost insulating layer 111 in which the electronic component 190 is to be formed, among the plurality of insulating layers 111. The first pad 120 may be formed in plural on the uppermost insulating layer. In addition, a part of the first pad 120 may serve as a pattern for signal transmission and the other part thereof may serve as an inner lead electrically connected to the electronic component 190 through the wire 195. In other words, the first pad 120 includes a wire-bonding pad for wire bonding.

[0086] In addition, the second pad 140 is disposed under the lowermost insulating layer to which an external substrate (not shown) is to be attached, among the plurality of insulating layers 111. Like the first pad 120, a part of the second pad 140 also serves as a pattern for signal transmission, and the other part thereof may serve as an outer lead in which the adhesive member 175 is disposed for attachment of the external substrate. In other words, the second pad 140 includes a soldering pad for soldering.

[0087] In addition, the upper conductive layer 130 is disposed on the first pad 120 and the lower conductive layer 150 is disposed under the second pad 140. The upper conductive layer 130 and the lower conductive layer 150 are formed of the same material and increase characteristics of the wire bonding or soldering while protecting the first pad 120 and the second pad 140, respectively.

**[0088]** For this, the upper conductive layer **130** and the lower conductive layer **150** are formed of a metal including gold (Au). Preferably, the upper conductive layer **130** and the lower conductive layer **150** may include pure gold (purity of 99% or more) only, or may be formed of an alloy including gold (Au). When the upper conductive layer **130** and the lower conductive layer **150** are formed of an alloy including gold, the alloy may be formed of a gold alloy including cobalt.

**[0089]** The solder paste **180** is disposed at the uppermost insulating layer among the plurality of insulating layers. The solder paste is an adhesive for fixing the electronic component **190** attached to the insulating substrate **110**. Accordingly, the solder paste **180** may be referred to as an adhesive. The adhesive may be a conductive adhesive, or alternatively, the adhesive may be a non-conductive adhesive. That is, the printed circuit board **100** may be a substrate to which the electronic component **190** is attached in a wire-bonding manner, so that a terminal (not shown) of the electronic component **190** is not disposed on the adhesive. In addition, the adhesive is not electrically connected to the electronic component **190**. Therefore, a non-conductive adhesive may be used as the adhesive, or alternatively, a conductive adhesive may be used as the adhesive.

**[0090]** The conductive adhesive is largely classified into an anisotropic conductive adhesive and an isotropic conductive adhesive, and is basically composed of conductive particles such as Ni, Au/polymer, or Ag, and thermosetting and thermoplastic resins, or a blend type insulating resin mixing characteristics of the two resins.

**[0091]** In addition, the non-conductive adhesive may also be a polymeric adhesive and may preferably be a non-conductive polymer adhesive including a thermosetting resin, a thermoplastic resin, a filler, a curing agent, and a curing accelerator.

**[0092]** Further, the first passivation layer **160**, through which at least a part of a surface of the upper conductive layer **130** is exposed, is disposed on the uppermost insulating layer. The first passivation layer **160** is disposed to protect the surface of the uppermost insulating layer, and, for example, may be a solder resist.

[0093] In addition, the wire 195 is bonded to the upper conductive layer 130 so that the first pad 120 and the electronic component 190 may be electrically connected to each other.

**[0094]** Here, the electronic component **190** may include both a device and a chip. The device may be classified into an active device and a passive device. The active device refers to a device that positively uses non-linear characteristics. The passive device refers to a device that does not use non-linear characteristics even though both linear and nonlinear characteristics are present. In addition, the passive device may include a transistor, an IC semiconductor chip, and the like and the passive device may include a condenser, a resistor, an inductor, and the like. The passive device is mounted on a substrate together with an ordinary semiconductor package in order to increase a signal processing speed of a semiconductor chip which is an active device, perform a filtering function, or the like.

**[0095]** As a result, the electronic component **190** may include all of a semiconductor chip, a light emitting diode chip, and other driving chips.

[0096] In addition, a resin molding part is formed on the uppermost insulating layer, so that the electronic component 190, the wire 195, and the wire-bonded upper conductive layer 130 may be protected by the resin molding part.

[0097] Meanwhile, the second passivation layer 170 is disposed under the lowermost insulating layer among the plurality of insulating layers. The second passivation layer 170 has an opening exposing an surface of the lower conductive layer 150 on which the adhesive member 175 is to be disposed. The second passivation layer 170 may be formed of a solder resist.

**[0098]** The adhesive member **175** is disposed under the lower conductive layer **150** exposed through the opening of the second passivation layer **170**. The adhesive member **175** is a member for soldering.

**[0099]** The adhesive member **175** provides an adhesive force between the printed circuit board **100** and the external substrate. The adhesive member **175** may be formed of a solder ball, or alternatively may be formed by using an adhesive paste or a copper core solder ball.

**[0100]** In addition, the adhesive paste may be formed of a conductive material for electrical conduction, and at this point, when the adhesive paste is formed of the conductive material, the adhesive paste may preferably be formed of a

conductive material selected from the group consisting of copper, silver, gold, aluminum, carbon nanotubes, and combinations thereof.

[0101] Hereinafter, the first pad 120, the second pad 140, the upper conductive layer 130, and the lower conductive layer 150 will be described in more detail.

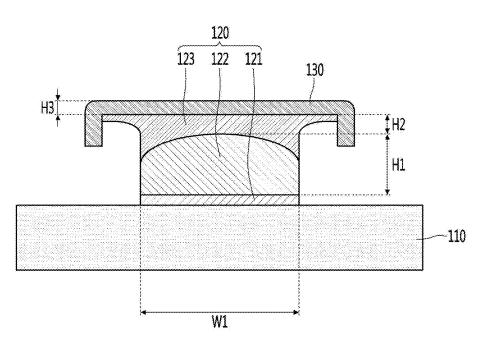

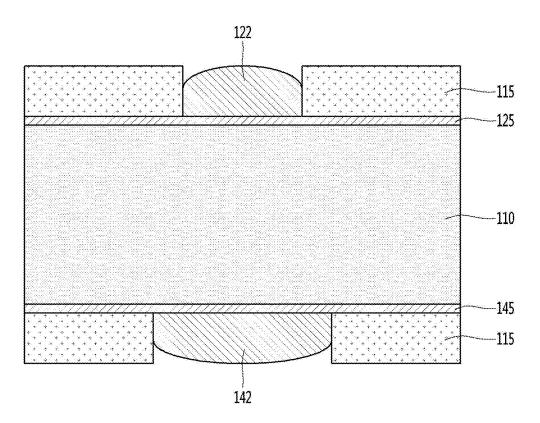

**[0102]** FIG. **3** is a view specifically illustrating the first pad **120** and the upper conductive layer **130** shown in FIG. **2**, and FIG. **4** is a view specifically illustrating the second pad **140** and the lower conductive layer **150** shown in FIG. **2**.

[0103] Referring to FIGS. 3 and 4, the upper conductive layer 130 and the lower conductive layer 150 have an overhang structure with respect to the first pad 120 and the second pad 140, respectively.

**[0104]** First, referring to FIG. **3**, the first pad **120** is disposed on the insulating layer disposed at the uppermost portion of the plurality of insulating layers.

[0105] The first pad 120 includes a plating seed layer 121 disposed on the uppermost insulating layer, a first-first pattern 122 disposed on the plating seed layer 121, and a first-second pattern 123 disposed on the first-first pattern 122. In addition, the upper conductive layer 130 is disposed on the first-second pattern 123.

**[0106]** The plating seed layer **121** is disposed on the uppermost insulating layer. Preferably, a lower surface of the plating seed layer **121** is in direct contact with an upper surface of the uppermost insulating layer. The upper and lower surfaces of the plating seed layer **121** has the same width.

**[0107]** In other words, a width of the upper surface of the plating seed layer **121** refers to an actual length from one end of the upper surface of the plating seed layer **121** to the other end thereof, and a width of the lower surface of the plating seed layer **121** refers to an actual length from one end of the lower surface of the plating seed layer **121** to the other end thereof. Accordingly, a width described below may be defined as an actual length from one end to the other end as described above.

**[0108]** In addition, a horizontal cross section of the plating seed layer **121** may have any one of various shapes such as a circular shape, a square shape, a triangle shape, an ellipse shape, a fan shape, and a star shape.

**[0109]** The plating seed layer **121** may be a seed layer for electrolytic plating of the first-first pattern **122** and the first-second pattern **123** and may be also a seed layer for electrolytic plating of the upper conductive layer **130**. In other words, the upper conductive layer **130** as well as the first-first pattern **122** and the first-second pattern **123** may be formed by electrolytic-plating the plating seed layer **121** as a seed layer.

**[0110]** A circuit pattern part is disposed on the plating seed layer **121**. The circuit pattern part includes a first-first pattern **122** and a first-second pattern **123**. The first-first pattern **122** and the first-second pattern **123** are formed of the same metal material. Preferably, the first-first pattern **122** and the first-second pattern **123** may be formed of copper (Cu), or may further include a conductive metal material while including the copper (Cu).

**[0111]** The first-first pattern **122** is formed on the plating seed layer **121**. An upper surface of the first-first pattern **122** has a curvature. Accordingly, a width of a lower surface of the first-first pattern **122** is different from that of the upper surface of the first-first pattern **122**. Here, the width refers to the actual length from one end to the other end as described

above, and since the upper surface of the first-first pattern **122** has a curvature, the width (actual length) of the upper surface of the first-first pattern **122** is larger than that (actual length) of the lower surface of the first-first pattern **122**. At this point, a straight line distance from one end to the other end of the upper surface of the first-first pattern **122** is the same as a straight line distance from one end to the other end of the lower surface of the first-first pattern **122**.

**[0112]** The first-second pattern **123** is disposed on the first-first pattern **122**. The first-second pattern **123** is disposed to cover the upper surface of the first-first pattern **122**. Accordingly, a lower surface of the first-second pattern **123** has a curvature corresponding to the upper surface of the first-first pattern **122**. In other words, the upper surface of the first-first pattern **122** may have a convex shape that protrudes upward. In addition, the lower surface of the first-second pattern **123** may have a concave shape that is recessed inward to cover the upper surface of the convex first-first pattern **122**.

**[0113]** The first-second pattern **123** is disposed to fill a removed edge region of the first-first pattern **122**. Therefore, at least a part of the lower surface of the first-second pattern **123** is located to be lower than at least a part of the upper surface of the first-first pattern **122**. At this point, the first-second pattern **123** covers the entire upper surface of the first-first pattern **122**. Therefore, the lower surface of the first-second pattern **123** is formed such that at least a part of a portion in contact with the upper surface of the first-first pattern **122** is located to be lower than at least a part of the upper surface of the first-first pattern **122** is located to be lower than at least a part of the upper surface of the first-first pattern **122**.

**[0114]** Accordingly, an outer side portion of the lower surface of the first-second pattern **123** is located to be lower than a remaining central portion of the upper surface of the first-first pattern **122** except for an outer side portion thereof. That is, an outermost side portion of the lower surface of the first-second pattern **123** is located to be lower than the remaining central portion of the upper surface of the first-first pattern **122** except for the outer side portion thereof

**[0115]** Further, the outermost side portion of the lower surface of the first-second pattern **123** and an outermost side portion of the upper surface of the first-first pattern **122** are located to be lower than the remaining central portion of the upper surface of the first-first pattern **122** except for the outer side portion thereof.

**[0116]** Furthermore, the outermost side portion of the lower surface of the first-second pattern **123** and the outermost side portion of the upper surface of the first-first pattern **122** are located to be lower than both the remaining central portion of the upper surface of the first-first pattern **122** except for the outer side portion thereof and a remaining central portion of the lower surface of the first-second pattern **123** except for the outer side portion thereof.

**[0117]** In addition, a thickness of the outer side portion of the first-second pattern **123** is larger than that of the central portion of the first-second pattern **123**.

**[0118]** Accordingly, a distance from the outer side portion of the lower surface of the first-second pattern **123** to the uppermost insulating layer in a first direction perpendicular to the upper surface of the uppermost insulating layer is smaller than that from the central portion except for the outer side portion of the lower surface of the first-second pattern **123** to the uppermost insulating layer.

[0119] In addition, a thickness of the first-second pattern 123 gradually increases toward the outer side portion of the

first-second pattern **123** from the central portion thereof. On the contrary, a thickness of the first-first pattern **122** gradually decreases toward the outer side portion of the first-first pattern **122** from the central portion thereof.

**[0120]** In addition, a width of the first-second pattern **123** may gradually increase toward an upper portion thereof. In other words, at least a part of a side surface of the first-second pattern **123** protrudes in a longitudinal direction than a side surface of the first-first pattern **122**. In other words, at least a part of a left-side surface of the first-second pattern **123** includes a portion that further protrudes in a left-side longitudinal direction than a left-side surface of the first-first pattern **122**. Further, at least a part of a right-side surface of the first-second pattern **123** includes a portion that further protrudes in a left-side surface of the first-second pattern **123** includes a portion that further second pattern **123** includes a portion that further protrudes in a right-side longitudinal direction than a right-side surface of the first-first pattern **122**.

[0121] Meanwhile, the first-first pattern 122 may have a first height H1 and the first-second pattern 123 may have a second height H2. Here, the height may refer to a thickness of each of the plating seed layer 121, the first-first pattern 122, and the first-second pattern 123 in a vertical direction. [0122] The height of the plating seed layer 121 is lower than the first height H1 of the first-first pattern 122. That is, the thickness of the plating seed layer 121 is thinner than that of the first-first pattern 122.

[0123] Furthermore, the first height H1 of the first-first pattern 122 may be higher than the second height H2 of the first-second pattern 123. In other words, the thickness of the first-first pattern 122 is thicker than that of the first-second pattern 123.

**[0124]** At this point, the thickness of the first-second pattern **123** may be in a range of 1 to 13  $\mu$ m. Preferably, the thickness of the first-second pattern **123** may be in a range of 3 to 10  $\mu$ m. More preferably, the thickness of the first-second pattern **123** may be in a range of 3 to 6  $\mu$ m.

[0125] That is, when the thickness of the first-second pattern 123 is more than 1 µm, an overspreading phenomenon of the upper conductive layer according to the present invention may be inhibited, and when the height of the first-second pattern 123 is in a range from 3 to 6 µm, an overhang portion of the upper conductive layer 130 may be minimized and the overspreading phenomenon of the upper conductive layer 130 may be inhibited completely. Here, the overspreading phenomenon may include a phenomenon in which the metal of the upper conductive layer 130 spreads into the first-second pattern 123 of the underlying layer in the plating process of the upper conductive layer 130. In addition, the overspreading phenomenon may include a phenomenon in which a metal material constituting the upper conductive layer 130 penetrates into a space between a mask and the first-second pattern 123 in the plating process of the upper conductive layer 130.

[0126] The upper conductive layer 130 is disposed on the first-second pattern 123. At this point, the upper conductive layer 130 includes a non-contact region not in contact with the first pad 120 and a contact region in contact with the first pad 120.

[0127] In other words, the upper conductive layer 130 includes a contact region in which the upper conductive layer 130 is in contact with at least one of the plating seed layer 121, the first-first pattern 122, and the first-second pattern 123. At this point, the contact region of the upper conductive layer 130 may be in contact with the first-second pattern 123. In other words, a lower surface of the upper

conductive layer 130 includes a contact portion in which the lower surface of the upper conductive layer 130 is in contact with an upper surface of the first-second pattern 123 and the side surface of the first-second pattern 123.

[0128] In addition, the upper conductive layer 130 is spaced apart from the plating seed layer 121, the first-first pattern 122 and the first-second pattern 123, and includes a non-contact region in which the upper conductive layer 130 is not in contact with all of the plating seed layer 121, the first-first pattern 122, and the first-second pattern 123. In other words, the lower surface of the upper conductive layer 130 includes a non-contact portion which is floating in air as the lower surface of the upper conductive layer 130 is not in contact with the plating seed layer 121, the first-first pattern 122, and the first-second pattern 123. At this point, the non-contact portion of the lower surface of the upper conductive layer 130 may be an outer side portion of the lower surface of the upper conductive layer 130. Further, the contact portion of the lower surface of the upper conductive layer 130 may be a remaining central portion of the lower surface of the upper conductive layer 130 except for the outer side portion of the lower surface thereof.

**[0129]** As described above, the upper conductive layer **130** is not disposed only at the upper surface of the first-second pattern **123**, but is bent at least once and disposed also at the side surface of the first-second pattern **123**. In addition, an end portion of a portion of the upper conductive layer **130** which is disposed at the side surface of the first-second pattern **123**. As a result, the upper conductive layer **130** has an overhang structure and is disposed on the first pad **120**, more specifically, on the first-second pattern **123**.

**[0130]** Meanwhile, a width of the non-contact portion of the upper conductive layer **130** may be in a range of 3 to 7  $\mu$ m. Preferably, the width of the non-contact portion of the upper conductive layer **130** may be in a range of 3 to 4  $\mu$ m. Here, the width of the non-contact portion may refer to a thickness (or length, height, or width) in a longitudinal direction of the non-contact portion in the drawing.

[0131] Meanwhile, a height H3 of the upper conductive layer 130 may be determined by characteristics required in the upper conductive layer 130. In other words, a thickness of the upper conductive layer 130 is determined by a function of the first pad 120 disposed under the upper conductive layer 130.

[0132] Here, the first pad 120 is formed for wire bonding in which the wire 195 electrically connected to the electronic component 190 is bonded. Therefore, the upper conductive layer 130 should have a thickness sufficient to satisfy the wire-bonding characteristics. Accordingly, the upper conductive layer 130 may have a thickness that satisfies a range of 0.2 to 0.8 µm. At this point, when the upper conductive layer 130 has a thickness of less than 0.2 µm, it may not meet criteria required for BPT (BPT specification 5 g or more) after wire bonding. In addition, when the upper conductive layer 130 has a thickness of more than 0.8 µm, there is a problem that a material cost due to excessive use of gold (Au) forming the upper conductive layer 130 is increased. Therefore, in the present invention, the upper conductive layer 130 has a thickness that satisfies the range of 0.2 to 0.8 μm. Here, the thickness of the upper conductive layer 130 may refer to a thickness of the upper conductive layer 130 in a lateral direction.

[0133] Meanwhile, as described above, the upper conductive layer 130 of the present invention includes only a layer including gold (Au). In other words, the upper conductive layer 130 including gold is directly disposed on the firstsecond pattern 123 formed of a metal including the copper. [0134] That is, in the present invention, a nickel layer disposed between a copper layer and gold (Au) of a typical conventional upper conductive layer is removed. This is because, as the first-second pattern 123 is formed on the first-first pattern 122, the overspreading phenomenon of the upper conductive layer 130 (which is clearly described above) may be solved, and the upper conductive layer 130 is formed of the plating seed layer 121 as a seed layer, which is used at the time of forming the first-first pattern 122 and the first-second pattern 123.

[0135] At this point, typical copper has so high electrical conductivity as compared with nickel. That is, the electrical conductivity of the nickel is only about 14.9% of the electrical conductivity of the copper. Therefore, in the present invention, since the first-second pattern 123 instead of the nickel layer is formed, a gold (Au) layer may be directly formed on a copper layer, and thus all of reliability problems caused by the formation of the nickel can be solved. In other words, in the related art, there was a problem in the interface characteristics between the first-first pattern 122 and the nickel layer due to the difference in characteristics between metals occurring between copper and nickel, and there was a problem that the electrical conductivity due to the nickel layer was lowered. However, in the present invention, an upper conductive layer including gold (Au) is formed by using a plating seed layer used at the time of forming the first-first pattern and the first-second pattern, so that a nickel (Ni) seed layer which has served as a seed layer of a gold (Au) conductive layer in the related art may be removed, and thus, not only a thickness of a printed circuit board product can be reduced, but also economic efficiency of a product can be improved by technical effect due to efficiency of a process. Further, according to an embodiment of the present invention, a nickel layer may be removed from a pattern structure, and thus not only electrical conductivity of a pattern can be improved, but also a problem of interface property occurring between copper and nickel constituting the pattern can be solved.

[0136] Meanwhile, referring to FIG. 4, the second pad 140 is disposed under the insulating layer disposed at the lowermost portion of the plurality of insulating layers. At this point, as shown in FIG. 4, the lower conductive layer 150 is disposed on the second pad 140, but FIG. 4 substantially illustrates a state in which an actual product is turned upside down. Hereinafter, for convenience of explanation, it is assumed that the second pad 140 is formed on the lowermost insulating layer among the plurality of insulating layers. But, in reality, the second pad 140 is disposed under a lower surface of the lowermost insulating layer, and the lower conductive layer 150 is disposed under the second pad 140. [0137] The second pad 140 includes a plating seed layer 141 disposed on the lowermost insulating layer, a secondfirst pattern 142 disposed on the plating seed layer 141, and a second-second pattern 143 disposed on the second-first pattern 142. In addition, the lower conductive layer 150 is disposed on the second-second pattern 143.

**[0138]** The plating seed layer **141** is disposed on the lowermost insulating layer. Preferably, a lower surface of the plating seed layer **141** is in direct contact with an upper

surface of the lowermost insulating layer. The upper and lower surfaces of the plating seed layer **141** has the same width.

**[0139]** The plating seed layer **141** may be a seed layer for electrolytic plating of the second-first pattern **142** and the second-second pattern **143** and may be also a seed layer for electrolytic plating of the lower conductive layer **150**. In other words, the lower conductive layer **150** as well as the second-first pattern **142** and the second-second pattern **143** may be formed by electrolytic-plating the plating seed layer **141** as a seed layer.

**[0140]** A circuit pattern part of the second pad **140** is disposed on the plating seed layer **141**. The circuit pattern part includes a second-first pattern **142** and a second-second pattern **143**. The second-first pattern **142** and the second-second pattern **143** are formed of the same metal material. Preferably, the second-first pattern **142** and the second-second pattern **143** may be formed of copper (Cu), or may further include a conductive metal material while including the copper (Cu).

[0141] The second-first pattern 142 is formed on the plating seed layer 141. An upper surface of the second-first pattern 142 has a curvature. Accordingly, a width of a lower surface of the second-first pattern 142 is different from that of the upper surface of the second-first pattern 142. Here, the width refers to the actual length from one end to the other end as described above, and since the upper surface of the second-first pattern 142 is larger than that (actual length) of the lower surface of the second-first pattern 142 is larger than that (actual length) of the lower surface of the second-first pattern 142 is larger than that (actual length) of the upper surface of the second-first pattern 142. At this point, a straight line distance from one end to the other end of the upper surface of the second-first pattern 142 is the same as a straight line distance from one end to the other end of the lower surface of the second-first pattern 142.

[0142] The second-second pattern 143 is disposed on the second-first pattern 142. The second-second pattern 143 is disposed to cover the upper surface of the second-first pattern 142. Accordingly, a lower surface of the second-second pattern 143 has a curvature corresponding to the upper surface of the second-first pattern 142. In other words, the upper surface of the second-first pattern 142 may have a convex shape that protrudes upward. In addition, the lower surface of the second-second pattern 143 may have a concave shape that is recessed inward to cover the upper surface of the convex second-first pattern 142.

**[0143]** The second-second pattern **143** is disposed to fill a removed edge region of the second-first pattern **142**. Therefore, at least a part of the lower surface of the second-second pattern **143** is located to be lower than at least a part of the upper surface of the second-first pattern **142**. At this point, the second-second pattern **143** covers the entire upper surface of the second-first pattern **142**. Therefore, the lower surface of the second-second pattern **143** is formed such that at least a part of a portion in contact with the upper surface of the second-first pattern **142** is located to be lower than at least a part of the upper surface of the second-first pattern **142** is located to be lower than at least a part of the upper surface of the second-first pattern **142** is located to be lower than at least a part of the upper surface of the second-first pattern **142**.

**[0144]** Accordingly, an outer side portion of the lower surface of the second-second pattern **143** is located to be lower than a remaining central portion of the upper surface of the second-first pattern **142** except for an outer side portion thereof. That is, an outermost side portion of the lower surface of the second-second pattern **143** is located to

be lower than the remaining central portion of the upper surface of the second-first pattern **142** except for the outer side portion thereof.

[0145] In addition, the outermost side portion of the lower surface of the second-second pattern 143 and an outermost side portion of the upper surface of the second-first pattern 142 are located to be lower than the remaining central portion of the upper surface of the second-first pattern 142 except for the outer side portion thereof.

**[0146]** Further, the outermost side portion of the lower surface of the second-second pattern **143** and the outermost side portion of the upper surface of the second-first pattern **142** are located to be lower than both the remaining central portion of the upper surface of the second-first pattern **142** except for the outer side portion thereof and a remaining central portion of the lower surface of the second-second pattern **143** except for the outer side portion thereof.

[0147] In addition, a thickness of the outer side portion of the second-second pattern 143 is larger than that of the central portion of the second-second pattern 143.

**[0148]** Accordingly, a distance from the outer side portion of the lower surface of the second-second pattern **143** to the lowermost insulating layer in the first direction perpendicular to the upper surface of the lowermost insulating layer is smaller than that from the central portion except for the outer side portion of the lower surface of the second-second pattern **143** to the lowermost insulating layer.

**[0149]** In addition, a thickness of the second-second pattern **143** gradually increases toward the outer side portion of the second-second pattern **143** from the central portion thereof. On the contrary, a thickness of the second-first pattern **142** gradually decreases toward the outer side portion of the second-first pattern **142** from the central portion thereof.

**[0150]** In addition, a width of the second-second pattern **143** may gradually increase toward an upper portion thereof. In other words, at least a part of a side surface of the second-second pattern **143** protrudes in a longitudinal direction than a side surface of the second-first pattern **142**. In other words, at least a part of a left-side surface of the second-second pattern **143** includes a portion that further protrudes in a left-side longitudinal direction than a left-side surface of the second-first pattern **142**. Further, at least a part of a right-side surface of the second-second pattern **143** includes a portion that further protrudes a portion that further protrudes a portion that further **143** includes a portion that further **144**.

**[0151]** Meanwhile, the second-first pattern **142** may have a fourth height H4 and the second-second pattern **143** may have a fifth height H5. Here, the height may refer to a thickness of each of the plating seed layer **141**, the second-first pattern **142**, and the second-second pattern **143** in a vertical direction.

**[0152]** The height of the plating seed layer **141** is lower than the fourth height H4 of the second-first pattern **142**. That is, the thickness of the plating seed layer **141** is thinner than that of the second-first pattern **142**.

[0153] Furthermore, the fourth height H4 of the second-first pattern 142 may be higher than the fifth height H5 of the second-second pattern 143. In other words, the thickness of the second-first pattern 142 is thicker than that of the second-second pattern 143.

[0154] At this point, the thickness of the second-second pattern 143 may be in a range of 1 to  $13 \mu m$ . Preferably, the

thickness of the second-second pattern 143 may be in a range of 3 to 10 µm. More preferably, the thickness of the second-second pattern 143 may be in a range of 3 to  $6 \,\mu\text{m}$ . [0155] That is, when the height of the second-second pattern 143 is more than 1 µm, an overspreading phenomenon of the lower conductive layer according to the present invention may be inhibited, and when the height of the second-second pattern 143 is in a range from 3 to 6 µm, an overhang portion of the lower conductive layer 150 may be minimized and the overspreading phenomenon of the lower conductive layer 150 may be inhibited completely. Here, the overspreading phenomenon may include a phenomenon in which the metal of the lower conductive layer 150 spreads into the second-second pattern 143 of the underlying layer in the plating process of the lower conductive layer 150. In addition, the overspreading phenomenon may include a phenomenon in which a metal material constituting the lower conductive layer 150 penetrates into a space between a mask and the second-second pattern 143 in the plating process of the lower conductive layer 150.

**[0156]** The lower conductive layer **150** is disposed on the second-second pattern **143**. At this point, the lower conductive layer **150** includes a non-contact region not in contact with the second pad **140** and a contact region in contact with the second pad **140**.

[0157] In other words, the lower conductive layer 150 includes a contact region in which the lower conductive layer 150 is in contact with at least one of the plating seed layer 141, the second-first pattern 142, and the second-second pattern 143. At this point, the contact region of the lower conductive layer 150 may be in contact with the second-second pattern 143. In other words, a lower surface of the lower conductive layer 150 includes a contact portion in which the lower surface of the lower conductive layer 150 includes a contact portion in which the lower surface of the lower conductive layer 150 is in contact with an upper surface of the second-second pattern 143 and the side surface of the second-second pattern 143.

[0158] Further, the lower conductive layer 150 is spaced apart from the plating seed layer 141, the second-first pattern 142 and the second-second pattern 143, and includes a non-contact region in which the lower conductive layer 150 is not in contact with all of the plating seed layer 141, the second-first pattern 142, and the second-second pattern 143. In other words, the lower surface of the lower conductive layer 150 includes a non-contact portion which is floating in air as the lower surface of the lower conductive layer 150 is not in contact with the plating seed layer 141, the secondfirst pattern 142, and the second-second pattern 143. At this point, the non-contact portion of the lower surface of the lower conductive layer 150 may be an outer side portion of the lower surface of the lower conductive layer 150. Furthermore, the contact portion of the lower surface of the lower conductive layer 150 may be a remaining central portion of the lower surface of the lower conductive layer 150 except for the outer side portion of the lower surface thereof.

[0159] As described above, the lower conductive layer 150 is not disposed only at the upper surface of the secondsecond pattern 143, but is bent at least once and disposed also at the side surface of the second-second pattern 143. In addition, an end portion of a portion of the lower conductive layer 150 which is disposed at the side surface of the second-second pattern 143 is spaced apart from the secondsecond pattern 143. As a result, the lower conductive layer **150** has an overhang structure and is disposed on the second pad **140**, more specifically, on the second-second pattern **143**.

**[0160]** Meanwhile, a width of the non-contact portion of the lower conductive layer **150** may be in a range of 2 to 6  $\mu$ m. Preferably, the width of the non-contact portion of the lower conductive layer **150** may be in a range of 2 to 3  $\mu$ m. **[0161]** Here, the width of the non-contact portion of the lower conductive layer **150** may refer to a thickness (or length, height, or width) in a longitudinal direction in the drawing.

[0162] At this point, a thickness of the lower conductive layer 150 and the thickness of the upper conductive layer 130 are different from each other. Accordingly, the width of the non-contact portion in the lower conductive layer 150 is different from that of the non-contact portion in the upper conductive layer 130. Preferably, the upper conductive layer 130 is thicker than the lower conductive layer 150 so that the width of the non-contact portion in the lower conductive layer 150 may be smaller than that of the non-contact portion in the upper conductive layer 130.

**[0163]** In other words, each of the upper conductive layer **130** and the lower conductive layer **150** may include a first region in direct contact with an upper surface of the first or second pad, a second region extending from the first region and in direct contact with a side surface of the first or second pad, and a third region extending from the second region and spaced from the first and second pads.

**[0164]** Further, the thickness of the upper conductive layer **130** in the longitudinal direction of the first region may be greater than that of the lower conductive layer **150** in the longitudinal direction of the first region. Furthermore, the thickness of the upper conductive layer **130** in the lateral direction of the second region may be greater than that of the lower conductive layer **150** in the lateral direction of the second region.

**[0165]** In addition, an end portion of the third region of the upper conductive layer **130** is located to be higher than the outer side region of the upper surface of the first-first pattern constituting the first pad, and an end portion of the third region of the lower conductive layer **150** is located to be lower than the outer side region of the lower surface of the second-first pattern constituting the second pad.

**[0166]** Furthermore, the thickness of the upper conductive layer **130** in the longitudinal direction of the third region may be different from that of the lower conductive layer **150** in the longitudinal direction of the third region.

**[0167]** In the present invention, the thickness of the third region in the upper conductive layer or the lower conductive layer may be minimized by the difference in thickness, and thus a problem occurring due to the third region deviated from the second region can be minimized.

**[0168]** Meanwhile, a height H6 of the lower conductive layer **150** may be determined by characteristics required in the lower conductive layer **150**. In other words, the thickness of the lower conductive layer **150** is determined by a function of the second pad **140** disposed under the lower conductive layer **150**.

**[0169]** At this point, the second pad **140** is formed for soldering bonding to be bonded to an external substrate. Therefore, the lower conductive layer **150** should have a thickness sufficient to satisfy the soldering characteristics. Accordingly, the lower conductive layer **150** may have a thickness that satisfies a range of 0.05 to 0.3  $\mu$ m. At this

point, when the lower conductive layer 150 has a thickness of less than 5 µm, the second-second pattern which is an underlying layer may be exposed. In addition, when the lower conductive layer 150 has a thickness of more than 0.3 μm, there is a problem that a material cost due to excessive use of gold (Au) forming the lower conductive layer 150 is increased. Therefore, in the present invention, the lower conductive layer 150 has a thickness that satisfies a range of 0.05 to 0.3 µm. Meanwhile, in the range of the thickness of the lower conductive layer 150, the thickness of the upper conductive layer 130 is included. At this point, even though some values in the thickness range overlap, the thicknesses of the lower conductive layer 150 and the upper conductive layer 130 are formed to be different from each other. For example, when the thickness of the lower conductive layer 150 is 0.3  $\mu$ m, the upper conductive layer 130 may have a thickness in a range of 0.31 to 0.8 µm which is larger than 0.3  $\mu$ m but not in a range of 0.2 to 0.8  $\mu$ m.

[0170] Meanwhile, as described above, the lower conductive layer 150 of the present invention includes only a layer including gold (Au). In other words, the lower conductive layer 150 including gold is directly disposed on the secondsecond pattern 143 formed of a metal including the copper. [0171] Meanwhile, as described above, the upper conductive layer 130 and the lower conductive layer 150 are formed of the same metal material and formed in the same process, but have different thicknesses. In other words, the upper conductive layer 130 formed on the first pad 120 formed for wire bonding is thicker than the lower conductive layer 150 formed on the second pad 140 formed for soldering.

[0172] At this point, in the present invention, the upper conductive layer 130 and the lower conductive layer 150 are introduced into one plating tank, and accordingly, the plating process is performed at both surfaces of the insulating substrate 110 simultaneously, so that the upper conductive layer 130 and the lower conductive layer 150 having different thicknesses are formed.

**[0173]** Meanwhile, the overhang structure of the upper metal layer shown in FIGS. **3** and **4** is merely an embodiment, and the structure of the overhang may be variously modified.

[0174] FIGS. 5(a)-5(c) are views illustrating a modified example of an overhang structure shown in FIGS. 3 and 4. [0175] Referring to FIGS. 5(a)-5(c), the lower surface of the upper conductive layer 130 may be in contact with only the upper surface of the first-second pattern 123. In other words, in FIG. 3, the upper conductive layer 130 is in contact with not only the upper surface of the first-second pattern 123 but also the side surface thereof. But, as shown in FIG. 5(a), the lower surface of the upper conductive layer 130 may be in contact with only the upper surface of the first-second pattern 123, and accordingly, the lower surface of the upper conductive layer 130 may extend in a direction parallel to the upper surface of the first-second pattern 123. [0176] In addition, as shown in FIG. 5(b), the lower surface of the upper conductive layer 130 may be in contact with both the upper surface and the side surface of the first-second pattern 123. However, the non-contact region of the upper conductive layer 130 may have a shape that is not extended in a direction perpendicular to the upper surface of the upper conductive layer 130, but is bent in an outward direction.

[0177] Further, as shown in FIG. 5(c), the lower surface of the upper conductive layer 130 may be in contact with both

the upper surface and the side surface of the first-second pattern **123**. However, the non-contact region of the upper conductive layer **130** may have a shape that is not extended in a direction perpendicular to the upper surface of the upper conductive layer **130**, but is bent in an inward direction.

[0178] Although the upper conductive layer 130 and the lower conductive layer 150 are formed simultaneously in the related art, the upper conductive layer 130 and the lower conductive layer 150 have the same thickness due to a manufacturing process problem. This is because an adsorption amount of gold ions, which is the metal material forming each of the conductive layers, did not react to a current change. In other words, in the related art, the insulating substrate 110 was vertically introduced in a vertical plating tank, so that upper and lower surfaces of the insulating substrate 110 were respectively plated.

**[0179]** At this point, a space for plating at the upper surface of the insulating substrate **110** in the plating tank and a space for plating at the lower surface of the insulating substrate **110** were connected to each other, so that a plating solution was freely moved between the upper surface region and the lower surface region. Accordingly, even though the plating current for the upper surface and the plating current for the lower surface were differently applied to each other, due to high conductivity of gold plating solution and limitation of a rack equipment mechanism of a plating apparatus, it was indicated that an adsorption amount of gold ions formed in each of regions was similar, so that it was difficult to control the upper conductive layer **130** and the lower conductive layer **150** to a desired thickness.

**[0180]** Meanwhile, as described above, in the conventional plating apparatus, when plating is performed with a plating solution of copper (Cu) or nickel (Ni) instead of gold (Au), since conductivity and ion-mobility of the copper or nickel are remarkably lower than those of gold, it is difficult to form different plating layers at both surfaces even in the open state as described above.

**[0181]** However, when gold is plated, there is a situation where ions transfer to an opposite surface at different current densities due to mobility and high conductivity of the gold ions, so that the upper conductive layer **130** and the lower conductive layer **150**, which are formed at the both surfaces, have the same thickness.

**[0182]** In addition, as described above, since an area of the first pad **120** is narrower than that of the second pad **140** and an plating area with respect to the second pad **140** is larger than that of the first pad **120**, in the related art, when the same current density is applied in the plating process, a current with respect to the second pad **140** having a large area flows toward the first pad **120** having the small area, and as a result, a conductive layer having the same thickness is formed at the first pad **120** and the second pad **140**.

**[0183]** On the other hand, in the present invention, the upper conductive layer **130** and the lower conductive layer **150** are formed by a new method, so that the upper conductive layer **130** and the lower conductive layer **150** may be formed to have different thicknesses even by simultaneously plating both surfaces of the insulating substrate **110**.

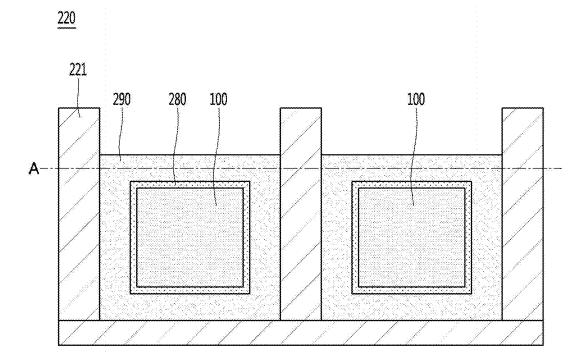

**[0184]** FIG. **6** is a view illustrating a plating apparatus according to an embodiment of the present invention, and FIG. **7** is a view illustrating a detailed structure of a substrate support of the plating apparatus shown in FIG. **6**.

[0185] Referring to FIG. 6, a plating apparatus 200 includes a plating tank 210 in which a gold plating solution

is accommodated, a plurality of electrodes **240**, **250**, **260** and **270**, a first pedestal **220** and a second pedestal **230**.