(12)

# **Patentschrift**

(21) Aktenzeichen: 10 2020 115 954.4

(22) Anmeldetag: 17.06.2020(43) Offenlegungstag: 02.09.2021

(45) Veröffentlichungstag

der Patenterteilung: 08.08.2024

(51) Int Cl.: **G11C 7/00** (2006.01)

**G11C 16/08** (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

16/805,574 28.02.2020 US

(73) Patentinhaber:

Western Digital Technologies, Inc., San Jose, CA, US

(74) Vertreter:

Dehns Germany Partnerschaft mbB, 80333 München, DE (72) Erfinder:

Ben-Rubi, Refael, San Jose, CA, US; Cohen, Moshe, San Jose, CA, US

(56) Ermittelter Stand der Technik:

US 9 830 992 B1 US 2019 / 0 303 236 A1

(54) Bezeichnung: DATENSPEICHER MIT VERBESSERTER LESELEISTUNG DURCH VERMEIDEN VON LEITUNGSENTLADUNG

(57) Hauptanspruch: Datenspeichervorrichtung (104), aufweisend:

eine Speichervorrichtung (110): und

eine an die Speichervorrichtung gekoppelte Steuereinrichtung (108), die konfiguriert ist zum Durchführen der folgenden Schritte in der angegebenen Reihenfolge:

Empfangen (402) einer Vielzahl von Lesebefehlen für eine Wortleitung;

Umordnen (408) der Lesebefehle von einer niedrigsten Messspannung zu einer höchsten Messspannung; und Ausführen der Lesebefehle, wobei das Ausführen der Lesebefehle Messen der Spannung einschließt und wobei die Wortleitung nicht zwischen Lesebefehlen entladen wird.

#### **Beschreibung**

#### HINTERGRUND DER OFFENBARUNG

#### Gebiet der Offenbarung

**[0001]** Ausführungsformen der vorliegenden Offenbarung beziehen sich im Allgemeinen auf ein effizientes Lesen, das eine Leitungsentladung zwischen Lesevorgängen vermeidet.

#### Beschreibung des Stands der Technik

**[0002]** In einem nichtflüchtigen Speicher, wie einem NAND-Flash-Speicher, werden Schreib- und Lesevorgänge ausgeführt, um Daten in die/aus der Speichervorrichtung zu schreiben und zu lesen. Ein Lesevorgang weist Mess- und Übertragungsuntervorgänge auf. Der Messvorgang von einem von mehreren Untervorgänge.

**[0003]** Während eines Lesevorgangs werden Spannungen an die Wortleitung und Bitleitung angelegt, um die Spannung für den Ort zu erfassen, an dem sich die Daten befinden. Während des Lesevorgangs kann sich Ladung an den Wortleitungen und den Bitleitungen aufbauen. Daher ist es üblich, die Wortleitung und die Bitleitung zu entladen, sobald die Daten gelesen wurden. Die Entladung findet zwischen Lesevorgängen statt. Mit anderen Worten weist jeder Lesevorgang mindestens eine Entladung auf, bevor der nächste Lesevorgang stattfindet.

**[0004]** Das Entladen der Wortleitung und der Bitleitung benötigt Zeit. Wenn es einen Chip mit vielen Blöcken gibt, nimmt die parasitäre Kapazität zu, und die Lade- und Entladezeit der Leitung für den Abtastuntervorgang wird erhöht. Wenn der Lesevorgang zu langsam ist, ist ein Teil des gelesenen Benutzerszenarios ineffizient

[0005] Daher besteht im Stand der Technik Bedarf an einem Lesevorgang, der die Leseeffizienz erhöht.

[0006] US 2019/0303236 A1 betrifft eine Speichervorrichtung, die eingerichtet ist, Basis-Lesedaten basierend auf Basis-Lesespannungen und Rückgewinnungs-Lesedaten basierend auf Rückgewinnungs-Lesespannungen für Speicherzellen effizient bereitzustellen, wobei Rückgewinnungs-Lesedaten durch eine auf einem Speicherchip befindliche Schaltung erhalten werden können bevor sie von einem außerhalb des Speicherchips befindlichen Schaltung angefordert oder gebraucht werden. US 9830992 B1 betrifft ein Betriebsverfahren für Speicherzellen, in dem ein Vor-Spannungspuls vor einem Lese-Spannungspuls angelegt wird, wobei der Vor-Spannungspuls größer als eine maximale Schwellenspannung oder kleiner als eine minimale Schwellenspannung ist.

#### KURZDARSTELLUNG DER OFFENBARUNG

**[0007]** Bereitgestellt werden Datenspeichervorrichtungen mit den Merkmalen der unabhängigen Ansprüche. Abhänigige Ansprüche betreffen bevorzugte Ausführungsformen.

[0008] Die vorliegende Offenbarung bezieht sich allgemein auf ein effizientes Lesen, das eine Leitungsentladung zwischen Lesevorgängen vermeidet. Wenn mehrere Lesebefehle für eine gemeinsame Wortleitung vorhanden sind, können diese Lesebefehle von der niedrigsten Messspannung zur höchsten Messspannung angeordnet werden. Da die Messspannung für jeden Lesebefehl zunimmt und die Lesebefehle für dieselbe Wortleitung sind, kann die normale Entladung, die nach dem Lesen im Lesevorgang stattfindet, eliminiert werden, bis der Lesebefehl mit der höchsten Messspannung ausgeführt worden ist. An diesem Punkt kann die Entladung stattfinden. Da eine Entladung nicht nach jedem Messen im Lesevorgang stattfindet, wird die Leseeffizienz erhöht.

[0009] In einer Ausführungsform weist eine Speichervorrichtung auf: eine Speichervorrichtung; und eine Steuereinrichtung, die an die Speichervorrichtung gekoppelt ist. Der Steuereinrichtung ist konfiguriert zum: Empfangen einer Vielzahl von Lesebefehlen für eine Wortleitung; Umordnen der Lesebefehle von einer niedrigsten Messspannung zu einer höchsten Messspannung; und Ausführen der Lesebefehle, wobei das Ausführen der Lesebefehle Messen der Spannung einschließt und wobei die Wortleitung nicht zwischen Lesebefehlen entladen wird.

**[0010]** In einer weiteren Ausführungsform weist eine Datenspeichervorrichtung auf: eine Speichervorrichtung; und eine Steuereinrichtung, die an die Speichervorrichtung gekoppelt ist. Die Steuereinrichtung ist konfiguriert zum: Empfangen eines ersten Lesebefehls für eine Wortleitung, wobei der erste Lesebefehl eine erste Messspannung aufweist; Prüfen einer Lesewarteschlange auf weitere Lesebefehle für die Wortleitung; Bestimmen, dass ein zweiter Lesebefehl in der Lesewarteschlange vorhanden ist; Ausführen des zweiten Lesebefehls; Ausführen des ersten Lesebefehls, wobei der erste Lesebefehl vor dem Entladen der Wortleitung ausgeführt wird; und Entladen der Wortleitung.

**[0011]** In einer weiteren Ausführungsform weist eine Datenspeichervorrichtung auf: eine Speichervorrichtung; Mittel zum Umordnen einer Reihenfolge der Ausführung einer Vielzahl von Lesebefehlen für eine Wortleitung; und Mittel zum Ausführen der Vielzahl von Lesebefehlen, ohne die Wortleitung zwischen der Ausführung der einzelnen Lesebefehle zu entladen.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

[0012] Zur Verdeutlichung der Art und Weise, wie die vorstehend dargelegten Merkmale der vorliegenden Offenbarung im Detail verstanden werden können, kann eine ausführlichere Beschreibung der Offenbarung, die vorstehend kurz zusammengefasst ist, unter Bezugnahme auf Ausführungsformen erfolgen, von denen einige in den beigefügten Zeichnungen veranschaulicht sind. Es ist jedoch zu beachten, dass in den beigefügten Zeichnungen nur typische Ausführungsformen dieser Offenbarung veranschaulicht sind und diese daher nicht als ihren Schutzumfang einschränkend anzusehen sind, da die Offenbarung andere ebenso wirksame Ausführungsformen zulassen kann.

Fig. 1 ist eine schematische Darstellung eines Systems zum Speichern von Daten;

**Fig.** 2A ist eine schematische Darstellung der 8 Spannungspegel für den Lesevorgang für einen TLC-Speicher.

Fig. 2B ist eine schematische Darstellung der Spannung gegenüber der Zeit für einen Lesemessvorgang.

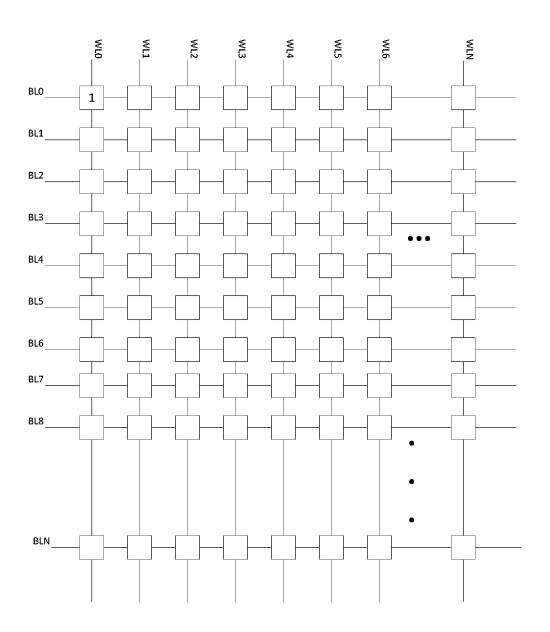

**Fig.** 3 ist eine schematische Darstellung einer Speichervorrichtungsseite mit mehreren Bitleitungen und Wortleitungen.

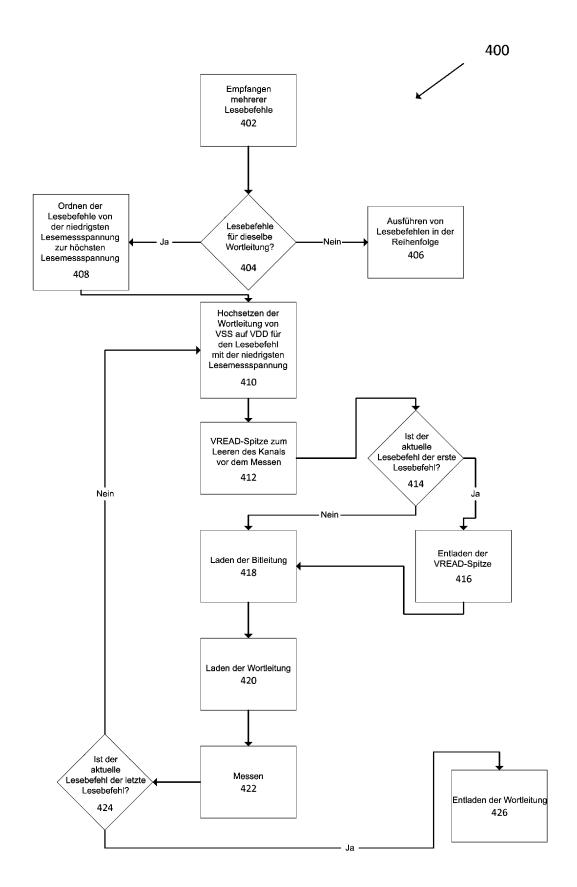

**Fig.** 4 ist ein Flussdiagramm, das einen Lesemessvorgang gemäß einer Ausführungsform veranschaulicht.

**[0013]** Zum besseren Verständnis wurden, soweit möglich, identische Bezugszeichen verwendet, um identische Elemente zu bezeichnen, die den Figuren gemein sind. Es ist vorgesehen, dass die in einer Ausführungsform offenbarten Elemente ohne besondere Aufzählung vorteilhaft auf andere Ausführungsformen angewendet werden können.

#### **DETAILLIERTE BESCHREIBUNG**

[0014] Im Folgenden wird auf die Ausführungsformen der Offenbarung verwiesen. Es versteht sich jedoch, dass die Offenbarung nicht auf bestimmte beschriebene Ausführungsformen beschränkt ist. Stattdessen wird jede Kombination der folgenden Merkmale und Elemente, unabhängig davon, ob sie sich auf verschiedene Ausführungsformen beziehen oder nicht, zur Umsetzung und Praxis der Offenbarung in Betracht gezogen. Auch wenn Ausführungsformen der Offenbarung Vorteile gegenüber anderen möglichen Lösungen und/oder dem Stand der Technik erzielen können, bedeutet die Tatsache, ob durch eine bestimmte Ausführungsform ein besonderer Vorteil erzielt wird oder nicht, keine Einschränkung der Offenbarung. Die folgenden Gesichtspunkte, Merkmale, Ausführungsformen und Vorteile sind daher nur veranschaulichend und gelten nicht als Elemente oder Einschränkungen der beigefügten Ansprüche, es sei denn, sie werden ausdrücklich in einem oder mehreren Ansprüchen erwähnt. Ebenso soll eine Bezugnahme auf "die Offenbarung" nicht als Verallgemeinerung eines hierin offenbarten erfinderischen Gegenstands ausgelegt werden und soll nicht als Element oder Einschränkung der beigefügten Ansprüche betrachtet werden, es sei denn, dies wird ausdrücklich in einem Anspruch bzw. in Ansprüchen angegeben.

[0015] Die vorliegende Offenbarung bezieht sich allgemein auf ein effizientes Lesen, das eine Leitungsentladung zwischen Lesevorgängen vermeidet. Wenn mehrere Lesebefehle für eine gemeinsame Wortleitung vorhanden sind, können diese Lesebefehle von der niedrigsten Messspannung zur höchsten Messspannung angeordnet werden. Da die Messspannung für jeden Lesebefehl zunimmt und die Lesebefehle für dieselbe Wortleitung sind, kann die normale Entladung, die nach dem Lesen im Lesevorgang stattfindet, eliminiert

werden, bis der Lesebefehl mit der höchsten Messspannung ausgeführt worden ist. An diesem Punkt kann die Entladung stattfinden. Da eine Entladung nicht nach jedem Messen im Lesevorgang stattfindet, wird die Leseeffizienz erhöht.

[0016] Fig. 1 ist eine schematische Darstellung eines Systems 100 zum Speichern von Daten. Das System 100 zum Speichern von Daten gemäß einer Ausführungsform schließt eine Host-Vorrichtung 102 und eine Datenspeichervorrichtung 104 ein. Die Host-Vorrichtung 102 schließt einen dynamischen Direktzugriffsspeicher (dynamic random-access memory, DRAM) 112 ein. Die Host-Vorrichtung 102 kann eine breite Palette von Vorrichtungen einschließen, wie etwa Computerserver, Network-Attached-Storage-Einheiten (NAS-Einheiten), Desktop-Computer, Notebook-Computer (d. h. Laptop-Computer), Tablet-Computer (d. h. "Smart Pad"), Set-Top-Boxen, Telefonhandapparate (d. h. "Smartphones"), Fernseher, Kameras, Anzeigevorrichtungen, digitale Medienplayer, Videospielkonsolen, Video-Streaming-Vorrichtungen und Automobilanwendungen (d. h. Abbildung, autonomes Fahren). In bestimmten Ausführungsformen schließt die Host-Vorrichtung 102 eine beliebige Vorrichtung mit einer Verarbeitungseinheit oder einer beliebigen Form von Hardware ein, die in der Lage ist, Daten zu verarbeiten, einschließlich einer Universalverarbeitungseinheit, spezieller Hardware (wie einer anwendungsspezifischen integrierten Schaltung (application specific integrated circuit, ASIC)), konfigurierbarer Hardware wie einem feldprogrammierbares Gate-Array (field programmable gate array, FPGA) oder einer anderen Form von Verarbeitungseinheit, die mittels Softwareanweisungen, Mikrocode oder Firmware konfiguriert ist.

[0017] Die Datenspeichervorrichtung 104 kommuniziert mit der Host-Vorrichtung 102 über eine Schnittstelle 106, die in der Datenspeichervorrichtung 104 enthalten ist. Die Datenspeichervorrichtung 104 schließt eine Steuereinrichtung 108, einen Puffer 114, eine Flash-Übersetzungsschicht (flash translation layer, FTL) 116 und eine oder mehrere Speichervorrichtungen 110 ein. Die Speichervorrichtung 104 kann ein internes Speicherlaufwerk sein, wie eine Notebook-Festplatte oder eine Desktop-Festplatte. Die Datenspeichervorrichtung 104 kann eine entfernbare Massenspeichervorrichtung sein, wie unter anderem eine tragbare, entnehmbare Speichervorrichtung, etwa eine Speicherkarte (z. B. eine SD-Karte (Secure Digital-Karte), eine micro-SD-Karte (Micro Secure Digital-Karte) oder eine Multimedia-Karte (MMC)) oder eine universelle serielle Bus-Vorrichtung (USB-Vorrichtung). Die Speichervorrichtung 104 kann die Form einer eingebetteten Massenspeichervorrichtung annehmen, wie eines eingebetteten eSD/eMMC-Flash-Speichers, der in die Host-Vorrichtung 102 eingebettet ist. Die Speichervorrichtung 104 kann auch eine beliebige andere Art von interner Speichervorrichtung, Wechselspeichervorrichtung, eingebetteter Speichervorrichtung, externer Speichervorrichtung oder Netzwerkspeichervorrichtung sein.

**[0018]** Bei der Speichergorrichtung 110 kann es sich ohne Beschränkung darauf um interne oder externe Speichereinheiten handeln. Die Speichervorrichtung 110 beruht auf einem Halbleiterspeicherchip, in dem Daten gespeichert werden können, als Direktzugriffspeicher (RAM), Nurlesespeicher (ROM) oder anderen Formen von RAM und ROM. RAM wird zur temporären Speicherung von Daten verwendet, wohingegen ROM zum dauerhaften Speichern von Daten verwendet wird.

**[0019]** Die Datenspeichervorrichtung 104 schließt eine Steuereinrichtung 108 ein, die Vorgänge der Speichervorrichtung 104 verwaltet, wie etwa das Schreiben in die und Lesen aus der Speichervorrichtung 110. Die Steuereinrichtung 108 führt durch computerlesbaren Programmcode (z. B. Software oder Firmware) ausführbare Befehlen (hierin bezeichnet als "Befehle") für die Übertragung von Daten aus. Die Befehle können von verschiedenen Komponenten der Steuereinrichtung 108 ausgeführt werden, wie einem Prozessor, Logikgattern, Schaltern, anwendungsspezifischen integrierten Schaltungen (ASICs), programmierbaren Logiksteuereinrichtungen, eingebetteten Mikrosteuerungen und anderen Komponenten der Steuereinrichtung 108.

**[0020]** Die Datenspeichervorrichtung 104 schließt einen Puffer 114 ein, der ein Bereich von physischem Speicher ist, der zur Zwischenspeicherung von Daten verwendet wird, während diese von einem Ort zu einem anderen (d. h. von der Host-Vorrichtung 102 zur Datenspeichervorrichtung 104) verschoben werden.

**[0021]** In einigen Ausführungsformen kann die FTL 116 eine Übersetzung einer logischen in eine physische Adresse, eine Speicherbereinigung, einen Abnutzungsausgleich, einen Fehlerkorrekturcode (error correction code, ECC), Verwaltung fehlerhafter Blöcke und andere nicht aufgeführte Funktionen ausführen. Die Übersetzung einer logischen in eine physische Adresse bezieht sich auf die Abbildung logischer Adressen aus dem Dateisystem auf physische Adressen der Speichervorrichtung 110, wie eines NAND-Flash-Speichers.

**[0022]** Daten können zu oder von dem DRAM 112 der Host-Vorrichtung 102 an die Datenspeichervorrichtung 104 übertragen werden. Ein Datenübertragungsweg kann von dem DRAM 112 der Hostvorrichtung 102

ausgehen und über die Schnittstelle 106 der Datenspeichervorrichtung 104 mit der Steuereinrichtung 108 kommunizieren. Die Daten gelangen dann durch den Puffer 114 der Datenspeichervorrichtung 104 und werden in der Speichervorrichtung 110 gespeichert. Die Steuereinrichtung 108 ist dazu konfiguriert, die Übersetzungstabelle der FTL 116 der Datenspeicherorte von innerhalb einer Speichervorrichtung 110 zu aktualisieren.

**[0023] Fig.** 2A ist eine schematische Darstellung der 8 Spannungspegel für den Lesevorgang für einen TLC-Speicher. Der TLC-Speicher besteht aus 3 Bits, in denen ein Programmierzustand von entweder 0 oder 1 existieren kann. Der Programmierzustand bezieht sich auf den Zustand der Speicherzelle, ob die Speicherzelle leer ist (d. h. keine Daten vorliegen) oder ob die Speicherzelle programmiert ist (d. h. Daten vorliegen). Darüber hinaus kann die Anzahl eindeutiger Kombinationen von Programmierzuständen in der folgenden Gleichung gelöst werden: (Gesamtanzahl der Spannungspegel) = 2^(Anzahl der Bits pro Speicherzelle). Für den TLC-Speicher beträgt die Anzahl der Spannungspegel acht, da 2^3=8.

**[0024]** Wenn die Anzahl von Bits zunimmt, kann die Speicherzelle mehr Informationen aufzeichnen, was zu einer größeren Datenspeicherung führt. Ferner kann die Gleichung für eine eindeutige Kombination von Programmierzuständen auf einen SLC-Speicher, einen TLC-Speicher, einen QLC-Speicher, einen Penta-Schicht-Zellen-Speicher (PLC-Speicher) und andere höhere Iterationen eines Schichtzellenspeichers angewendet werden.

**[0025]** Der Programmierzustand von 0 bezieht sich auf einen programmierten Zustand, wohingegen sich der Programmierzustand von 1 auf einen gelöschten Zustand bezieht. Der TLC-Speicher weist 8 Spannungspegel auf, wobei einer gelöscht ist und sieben programmiert sind. Darüber hinaus weist der eine Spannungspegel, der gelöscht ist, eine Bitkombination von 111 auf. Wenn bei einer beliebigen Speicherzelle die Bitkombination nur den Programmierzustand 1 enthält, wird der Programmierzustand gelöscht (z. B. 1 für SLC, 11 für MLC und 1111 für QLC). Unter Aufführung beginnend bei der niedrigsten Schwellenspannung, bezeichnet mit Vt auf der x-Achse, bis zur höchsten Schwellenspannung in **Fig.** 2 sind die Spannungspegel für den gelöschten Zellzustand 111, für Zellzustand A 110, für Zellzustand B 100, für Zellzustand C 000, für Zellzustand D 010, für Zellzustand E 011, für Zellzustand F 001 und für Zellzustand G 101.

[0026] Die Bits für den Zellzustand (d. h. ###) sind obere Seite, mittlere Seite, untere Seite. Außerdem beziehen sich die Leitungen zwischen den Kurven, die mit A, B, C, D, E, F und G bezeichnet sind, auf die Schwellen- oder Referenzspannung. Für andere Speicherzellen kann die Anzahl der Schwellen- oder Referenzspannungen durch die folgende Gleichung gelöst werden: (Anzahl der Schwellen- oder Referenzspannungen) = (Gesamtzahl der Spannungspegel) - 1. Die einzelnen Datenseiten können gelesen werden, indem eine Anzahl von Vergleichen an Schwellenpunkten durchgeführt wird, um zu bestimmen, ob die Zellenspannung niedriger oder höher als der Schwellenwert ist. Die Anzahl von Vergleichen, die für jede ausgelesene Seite erforderlich ist, hängt von der verwendeten Bitcodierung ab. In Fig. 2 sind die programmierten Zustände durch die "Höcker" der Wahrscheinlichkeitsverteilung an der Oberseite und die Schwellenspannungspositionen dargestellt, die unten aufgeführt sind (d. h. A bis G mit den vertikalen Linien). Verschiedene Codierungsschemata sind möglich, aber gegenwärtig wird, wie in der Tabelle gezeigt, ein 2-3-2-Schema verwendet.

#### Tabelle:

| Zellzustand            | Löschen | Α | В | С | D | Е | F | G |

|------------------------|---------|---|---|---|---|---|---|---|

| Obere Seite gelesen    | 1       | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

| Mittlere Seite gelesen | 1       | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| Untere Seite gelesen   | 1       | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

[0027] Fig. 2B ist eine schematische Darstellung der Spannung gegenüber der Zeit für einen Lesemessvorgang. Wenn die Speichervorrichtung, wie etwa die Datenspeichervorrichtung 104 aus Fig. 1, einen Lesebefehl für eine logische Blockadresse (LBA) empfängt, bestimmt die Steuereinrichtung, wie etwa die Steuereinrichtung 108 aus Fig. 1, den Ort der LBA in einer Übersetzungstabelle. Der Ort der LBA wird durch den Schnittpunkt der Wortleitung und der Bitleitung bezeichnet. Um zu bestimmen ob der Knoten (d. h. Schnittpunkt der Wortleitung und der Bitleitung) Daten enthält, kann ein Lesemessvorgang verwendet werden kann.

[0028] Während eines Lesemessvorgangs wird Spannung an die Wortleitung (WL) geliefert, an der sich die LBA befindet, um die Spannung von VSS (d. h. Nullspannung) auf VDD (d. h. Versorgungsspannung) zu

erhöhen. Während der VREAD-Stufe kommt es zu einer Spannungsspitze, um den Kanal vor dem Messen zu leeren. Die Spannungsspitze beruht auf der Notwendigkeit, etwaige gespeicherte Elektronen aufgrund von Unvollkommenheiten in dem Produktionsmetall zu entladen. Die VREAD-Spitzenspannung wird an VSS entladen, um den Lesevorgang vorzubereiten.

[0029] Nach dem Entladen der anfänglichen VREAD-Spitzenspannung wird die Bitleitung auf VCGRV1 geladen. Anschließend wird die Wortleitung auf VCGRV2 geladen. Bei einer Spannung von VCGRV1 und VCGRV2 bestimmt der Leseverstärker (SA) den Zustand der Bitleitung (d. h. 1 oder 0). Der Zustand des Bits kann durch den Prozess des Vergleichs der Spannung mit den Schwellenwerten registriert werden, die oben in Bezug auf Fig. 2A erörtert wurden. Die Verstärkung von VSS zu VDD, VREAD-Spitze und der VCGRV1-Lesemessvorgang ist die Anfangstaktphase R\_CLK. Der Lesemessvorgang bei VCGRV2 ist die zweite Taktphase, RWL\_CLK, des Lesevorgangs. Es sei angemerkt, dass es keine Entladung zwischen dem Laden der Bitleitung auf VCGRV1 und dem Laden der Wortleitung auf VCGRV2 stattfindet.

**[0030]** Nach dem Bestimmen der beiden Schwellenspannungen wird die Spannung von den Wortleitungen und den internen Hochspannungsknoten entladen. Wenn die Spannung entladen wird, kann jedoch in dem Produktionsmetall aufgrund seiner natürlichen Kapazität ein Teil der Spannung erhalten bleiben. Die Entladung ist die letzte Stufe der Taktphase, bezeichnet als RR\_CLK.

[0031] Zusätzlich kann der aufgeführte Prozess in der gleichen Reihenfolge stattfinden, in der die Lesemessvorgänge für dieselbe Wortleitung empfangen werden. Wenn die Lesemessvorgänge jedoch umgeordnet werden, sodass die Spannungen, die für einen Lesemessvorgang benötigt werden, in der Reihenfolge von niedrig zu hoch sind, kann der Gesamtbetrieb optimiert oder verbessert werden. Zum Beispiel wenn die folgenden drei Messungen der Reihe nach empfangen werden: hohe Lesemessspannung, mittlere Lesemessspannung und niedrige Messspannung. Bei jedem Lesevorgang müssen aufgrund der Erhaltung der Spannung in dem Produktionsmetall die Wortleitung und die internen Hochspannungsknoten entladen werden, bevor der nachfolgende Lesevorgang stattfindet. Ferner muss vor der Bitleitungs- und der Wortleitungsladung jeder Lesemessung der VREAD-Spike stattfinden, um den Kanal von etwaigen zurückgebliebenen Elektronen zu befreien.

[0032] Wenn jedoch die Reihenfolge der Lesemessvorgänge für dieselbe Wortleitung von einer niedrigen Lesemessspannung zu einer mittleren Lesemessspannung auf eine hohe Lesemessspannung umgeordnet wird, kann die Notwendigkeit einer Spannungsentladung und einer VREAD-Spitze zum Leeren des Kanals eliminiert werden. Die VREAD-Spitze tritt vor der niedrigen Lesemessspannung auf. Die Wortleitung und die Bitleitung werden von niedriger Lesemessspannung auf mittlere Lesemessspannung und von mittlerer Lesemessspannung auf hohe Lesemessspannung geladen. Nach dem Auftreten der hohen Lesemessspannung findet die Entladung der Spannung von der Wortleitung und den Hochspannungsknoten statt. Wenn die Lesemessvorgänge von niedrigen Spannung zu einer erforderlichen hohen Spannung umgeordnet werden, kann die Lesezeit verringert werden, da weniger Entladungsvorgänge vorliegen und die benötigte Spannung für den Betrieb insgesamt möglicherweise niedriger ist.

[0033] Wenn somit ein Lesezugriff zur Ausführung eintrifft, prüft die Firmware, ob es ausstehende Leseanforderungen für dieselbe Wortleitung vorliegen. Wenn die Firmware auf andere Lesevorgänge von Seiten in derselben Wortleitung stößt, ändert die Firmware die Reihenfolge der Lesevorgänge, damit diese unter einem Gesichtspunkt der Messung optimal ist. Das Kriterium zum Wählen der Seitenlesereihenfolge liegt darin, dass die nächste Messung für Seiten ist, für die die benötigte Wortleitungsladungsergänzung minimal ist. Auf diese Weise besteht keine Notwendigkeit zum Entladen und erneuten Laden. Im besten Fall für einen QLC-Speicher mit 16 Spannungspegel können 16 Messungen ohne Entladung dazwischen stattfinden. Es wird jedoch ein Effizienzzuwachs erzielt, solange zwei Messungen für eine einzelne Wortleitung vorliegen, die umgeordnet werden können. Für unterschiedliche Seiten nutzt Firmware eine Pegelmessung, die zu einer Seitenmessung gehört, und führt die eine Seitenmessung vor oder nach einer zweiten Pegelmessung aus, die zu einer zweiten Seitenmessung gehört. Die Firmware führt die anderen Seitenmessungen in einer optimalen Reihenfolge aus.

**[0034] Fig.** 3 ist eine schematische Darstellung einer Speichervorrichtungsseite mit mehreren Bitleitungen und Wortleitungen. Jeder Knoten der Seite liegt dort, wo sich eine Wortleitung und eine Bitleitung schneiden (z. B. schneiden sich WL0 und BL0 am oberen linken Knoten 1 der Seite). Der Knoten stellt einen möglichen Ort zum Speichern von Daten in einer Speicherzelle dar. Die Wortleitungen sind durch die horizontalen Linien und die Bitleitungen durch die vertikalen Linien gekennzeichnet.

**[0035]** Ferner kann **Fig.** 3 eine Seite in einer Speichervorrichtung wie etwa der Speichervorrichtung 110 aus **Fig.** 1 beschreiben. Die Speichervorrichtung, wie NAND-Flash-Speicher, kann einen oder mehrere Chips aufweisen. Jeder von dem einen oder den mehreren Chips weist eine oder mehrere Ebenen auf. Jede der einen oder mehreren Ebenen weist einen oder mehrere Löschblöcke auf. Jeder von dem einen oder den mehreren Löschblöcke weist eine oder mehrere Wortleitungen (z. B. 256 Wortleitungen) auf. Jede der einen oder mehreren Wortleitungen kann auf einer oder mehreren Seiten adressiert werden. Eine Seitengröße kann 16 k x 8 Bits oder 128 kB betragen. Die Seitengröße ist weder beschränkend noch einschränkend, und es können andere Größen für Seiten gelten. Daten werden im Allgemeinen sequenziell an die Wortleitungen auf einer Seite geschrieben (d. h. in der Reihenfolge von WL0 bis WL1 bis WL2 und so weiter). 272247

[0036] Der Knoten kann aus einem Floating-Gate-Transistor bestehen, der ein Steuer-Gate, ein Floating-Gate, einen Isolator, ein P-Substrat, eine Source und einen Drain aufweist. Die Wortleitungen sind am Steuer-Gate des Transistors angeschlossen und die Bitleitungen verbinden die Source und den Drain mit der Zelle. Elektrischer Strom gelangt durch die Source in die Zelle und tritt durch den Drain aus. Wenn eine Spannung an die Wortleitung angelegt wird, öffnet sich das Steuer-Gate und bestimmt, ob die Zelle eine Ladung aufweist (d. h. das Bit eine 0 oder eine 1 ist). Ein Bitzustand von 1 bezieht sich auf eine gelöschte Zelle, in der keine Elektronen im Floating-Gate vorhanden sind. Wenn jedoch Elektronen in dem Floating-Gate vorhanden sind, ist der Bitzustand der Zelle 0, was sich auf eine Zelle bezieht, die Daten enthält. Wenn eine positive Ladung an die Bitleitung und die Wortleitung angelegt wird, werden Elektronen in der Source zum Drain bewegt. Wenn die Elektronen von der Source zum Train wandern, können einige Elektronen den Isolator umgehen und in das Floating-Gate gelangen, wodurch Daten in die Zelle geschrieben werden.

**[0037] Fig.** 4 ist ein Flussdiagramm 400, das einen Leserfassungsvorgang gemäß einer Ausführungsform veranschaulicht. Das Verfahren veranschaulicht mögliche Ausführungsformen von **Fig.** 2A, **Fig.** 2B und **Fig.** 3. Das Verfahren wird verwendet, um einen effizienten Prozess zum Lesen von Daten von einer individuellen Wortleitung zu bestimmen.

**[0038]** Bei Block 402 empfängt die Speichervorrichtung, wie die Speichereinrichtung 104 aus **Fig.** 1, mehrere Lesebefehle. Die Steuereinrichtung, wie die Steuereinrichtung 108, bestimmt bei Block 404, ob einer oder mehrere der Lesebefehle für dieselbe Wortleitung gelten. Wenn die Lesebefehle nicht für dieselbe Wortleitung gelten, werden die Lesebefehle bei Block 406 der Reihe nach ausgeführt.

[0039] Wenn jedoch die Lesebefehle für dieselbe Wortleitung gelten, ordnet die Steuereinrichtung bei Block 408 die Lesebefehle von der niedrigsten Lesemessspannung zur höchsten Lesemessspannung. Für drei Lesebefehle zum Beispiel, die in zufälliger Reihenfolge empfangen werden und bei denen der erste Lesebefehl eine hohe Lesemessspannung ist, der zweite Lesebefehl eine mittlere Lesemessspannung ist und der dritte Lesebefehl eine niedrige Lesemessspannung ist, ordnet die Steuereinrichtung die Lesebefehle in der Reihenfolge dritter Lesebefehl (d. h. niedrige Lesemessspannung), zweiter Lesebefehl (d. h. mittlere Lesemessspannung) und erster Lesebefehl (d. h. hohe Lesemessspannung) um.

**[0040]** Bei Block 410 wird für den Lesebefehl mit der niedrigsten Lesemessspannung eine Spannung an die Wortleitung angelegt, um die Ladung von VSS auf VDD zu verstärken. VSS kann als Massespannung oder Nullspannung betrachtet werden. VDD kann als die Quellenspannung oder die Spannung betrachtet werden, die an die Wortleitung angelegt wird. Bei Block 412 nimmt die Spannung zu, bezeichnet durch VREAD-Spitze, um den Kanal vor dem Messen zu leeren.

[0041] Nach der VREAD-Spitze bestimmt die Steuereinrichtung bei Block 414, ob der aktuelle Lesebefehl der erste Lesebefehl ist. Wenn der aktuelle Lesebefehl der erste Lesebefehl ist, wird bei Block 416 die VREAD-Spitze entladen, um den Kanal von Restelektronen zu leeren, woraufhin bei Block 418 mit der Bitleitungsladung fortgefahren wird. Wenn der aktuelle Lesebefehl nicht der erste Lesebefehl ist oder wenn die VREAD-Spitze entladen wurde, wird die Bitleitung bei Block 418 geladen, was VCGRV1 aus Fig. 2B sein kann. Nach der Bitleitungsladung bei Block 418 wird bei Block 420 die Wortleitung geladen, wad VCGRV2 aus Fig. 2B sein kann.

[0042] Die Steuereinrichtung bestimmt bei Block 422 den Bitzustand der Speicherzelle unter Verwendung des Messverstärkers. Der Bitzustand der Speicherzelle wird durch VCGRV1 aus der Bitleitungsladung und VCGRV2 aus der Wortleitungsladung bestimmt. VCGRV1 kann die untere Spannungsschwelle sein und VCGRV2 kann die obere Spannungsschwelle sein. Der Bitzustand wird unter Verwendung eines Vergleichs der Spannung mit den in Fig. 2A beschriebenen Schwellenspannungen bestimmt. Nach dem Messen bestimmt die Steuereinrichtung bei Block 424, ob der aktuelle Lesebefehl der letzte Lesebefehl ist. Wenn der

aktuelle Lesebefehl nicht der letzte Lesebefehl ist (d. h. weitere Lesebefehle in der Warteschlange sind), startet der Prozess erneut durch Hochsetzen der Wortleitung von VSS auf VDD für den nachfolgenden Lesemessspannungslesebefehl bei Block 410. Wenn jedoch der aktuelle Lesebefehl der letzte Lesebefehl ist, wird die Wortleitung bei Block 426 entladen.

**[0043]** Man betrachte das folgende Beispiel für **Fig.** 4. Die Datenspeichervorrichtung empfängt bei Block 402 mehrere Lesebefehle, und bei Block 404 wird bestimmt, dass die mehreren Lesebefehle für dieselbe Wortleitung gelten. Die Lesebefehle sind in der folgenden Reihenfolge eingetroffen: Lesebefehl mit hoher Messspannung, Lesebefehl mit mittlerer Messspannung und Lesebefehl mit niedriger Messspannung. Die Steuereinrichtung ordnet dann bei Block 408 die Lesebefehle wie folgt: Lesebefehl mit niedriger Messspannung, Lesebefehl mit mittlerer Messspannung und Lesebefehl mit hoher Messspannung. Die Steuereinrichtung fährt dann zuerst mit dem Verarbeiten des Lesebefehls mit niedriger Messspannung fort.

[0044] Die Wortleitung wird bei Block 410 für den Lesebefehl mit niedriger Messspannung von VSS auf VDD hochgesetzt. Danach tritt bei Block 412 die VREAD-Spitze auf, um den Kanal vor der Erfassung zu leeren. Die Steuereinrichtung bestimmt bei Block 414, dass der Lesebefehl mit niedriger Messspannung der erste Lesebefehl ist, und entlädt somit bei Block 416 die VREAD-Spitze. Die Bitleitung wird dann bei Block 418 geladen, gefolgt vom Laden der Wortleitung bei Block 420. Das Messen erfolgt dann bei Block 422. Die Steuereinrichtung bestimmt dann bei Block 424, dass der Lesebefehl mit niedriger Messspannung nicht der letzte Lesebefehl ist, und bereitet sich daher auf die Verarbeitung des nächsten Lesebefehls (d. h. den Lesebefehl mit mittlerer Messspannung) vor.

[0045] Die Wortleitung wird dann bei Block 410 für den Lesebefehl mit mittlerer Messspannung von VSS auf VDD hochgesetzt. VSS an diesem Zeitpunkt, wenn die Messspannung von dem vorherigen Lesebefehl. Bei Block 412 tritt die VREAD-Spitze auf, um den Kanal vor der Erfassung zu leeren. Die Steuereinrichtung bestimmt bei Block 414, dass der Lesebefehl mit mittlerer Messspannung nicht der erste Lesebefehl ist, und lädt somit bei Block 418 die Bitleitung. Die Wortleitung wird dann bei Block 420 geladen, gefolgt vom Messen des Lesebefehls mit mittlerer Messspannung bei Block 422. Die Steuereinrichtung bestimmt dann bei Block 424, dass der Lesebefehl mit mittlerer Messspannung nicht der letzte Lesebefehl ist, und bereitet sich daher auf die Verarbeitung des nächsten Lesebefehls (d. h. den Lesebefehl mit hoher Messspannung) vor.

**[0046]** Die Wortleitung wird dann bei Block 410 für den Lesebefehl mit mittlerer Messspannung von VSS auf VDD hochgesetzt. VSS an diesem Zeitpunkt, wenn die Messspannung von dem vorherigen Lesebefehl. Bei Block 412 tritt die VREAD-Spitze auf, um den Kanal vor der Erfassung zu leeren. Die Steuereinrichtung bestimmt bei Block 414, dass der Lesebefehl mit hoher Messspannung nicht der erste Lesebefehl ist, und lädt somit bei Block 418 die Bitleitung. Die Wortleitung wird dann bei Block 420 geladen, gefolgt vom Messen des Lesebefehls mit hoher Messspannung bei Block 422. Die Steuereinrichtung bestimmt bei Block 424, dass der Lesebefehl mit hoher Messspannung der letzte Lesebefehl ist, und entlädt somit bei Block 426 die Wortleitung.

[0047] In einer Ausführungsform weist eine Speichervorrichtung auf: eine Speichervorrichtung; und eine Steuereinrichtung, die an die Speichervorrichtung gekoppelt ist. Der Steuereinrichtung ist konfiguriert zum: Empfangen einer Vielzahl von Lesebefehlen für eine Wortleitung; Umordnen der Lesebefehle von einer niedrigsten Messspannung zu einer höchsten Messspannung; und Ausführen der Lesebefehle, wobei das Ausführen der Lesebefehle Messen der Spannung einschließt und wobei die Wortleitung nicht zwischen Lesebefehlen entladen wird. Die Steuereinrichtung ist weiterhin dazu konfiguriert, einen ersten Lesebefehl der Vielzahl von Lesebefehlen durch einen Prozess auszuführen, der aufweist: Hochsetzen der Wortleitung von VSS auf VDD; VREAD-Spitze, um einen Kanal vor dem Messen zu leeren; Entladen der VREAD-Spitze; Laden der Bitleitung; Laden der Wortleitung; und Messen. Die Steuereinrichtung ist weiterhin dazu konfiguriert, einen zweiten Lesebefehl der Vielzahl von Lesebefehlen durch einen Prozess auszuführen, der aufweist: Hochsetzen der Wortleitung von VSS auf VDD; VREAD-Spitze, um einen Kanal vor dem Messen zu leeren; Laden der Bitleitung; Laden der Wortleitung; und Messen. Die Steuereinrichtung ist weiterhin dazu konfiguriert, einen dritten Lesebefehl der Vielzahl von Lesebefehlen durch einen Prozess auszuführen, der aufweist: Hochsetzen der Wortleitung von VSS auf VDD; VREAD-Spitze, um einen Kanal vor dem Messen zu leeren; Laden der Bitleitung; Laden der Wortleitung; Messen; und Entladen der Wortleitung. Die Steuereinrichtung ist dazu konfiguriert, den ersten Lesebefehl vor dem zweiten Lesebefehl auszuführen, wobei die Steuereinrichtung dazu konfiguriert ist, den zweiten Lesebefehl vor dem dritten Lesebefehl auszuführen. Die Steuereinrichtung ist dazu konfiguriert, mindestens einen von dem zweiten Lesebefehl und dem dritten Lesebefehl vor dem Empfangen des ersten Lesebefehls zu empfangen. Die Steuereinrichtung ist dazu konfiguriert, die Wortleitung nach dem Ausführen eines letzten Lesebefehls für die Wortleitung zu entladen.

[0048] In einer weiteren Ausführungsform weist eine Datenspeichervorrichtung auf: eine Speichervorrichtung; und eine Steuereinrichtung, die an die Speichervorrichtung gekoppelt ist. Die Steuereinrichtung ist konfiguriert zum: Empfangen eines ersten Lesebefehls für eine Wortleitung, wobei der erste Lesebefehl eine erste Messspannung aufweist; Prüfen einer Lesewarteschlange auf weitere Lesebefehle für die Wortleitung; Bestimmen, dass ein zweiter Lesebefehl in der Lesewarteschlange vorhanden ist; Ausführen des zweiten Lesebefehls; Ausführen des ersten Lesebefehls, wobei der erste Lesebefehl vor dem Entladen der Wortleitung ausgeführt wird; und Entladen der Wortleitung. Der zweite Lesebefehl für die Wortleitung weist eine zweite Messspannung auf, die niedriger als die erste Messspannung ist. Während der Ausführung des zweiten Lesebefehls findet eine VREAD-Spitzen-Entladung statt. Während der Ausführung des ersten Lesebefehls findet keine VREAD-Spitzen-Entladung statt. Die Steuereinrichtung ist weiterhin dazu konfiguriert zu bestimmen, dass ein dritter Lesebefehl in der Lesewarteschlange vorliegt, wobei der zweite Lesebefehl in der Reihenfolge vor dem dritten Lesebefehl eingereiht ist. Die Steuereinrichtung ist weiterhin dazu konfiguriert, den dritten Lesebefehl nach dem ersten Lesebefehl auszuführen, und wobei der dritte Lesebefehl vor dem Entladen der Wortleitung ausgeführt wird. Während der Ausführung des zweiten Lesebefehls findet eine VREAD-Spitzen-Entladung statt, wobei während der Ausführung des ersten Lesebefehls keine VREAD-Spitzen-Entladung stattfindet und wobei während der Ausführung des dritten Lesebefehls keine VREAD-Spizen-Entladung stattfindet.

[0049] In einer weiteren Ausführungsform weist eine Datenspeichervorrichtung auf: eine Speichervorrichtung; Mittel zum Umordnen einer Reihenfolge der Ausführung einer Vielzahl von Lesebefehlen für eine Wortleitung; und Mittel zum Ausführen der Vielzahl von Lesebefehlen, ohne die Wortleitung zwischen der Ausführung der einzelnen Lesebefehle zu entladen. Die Datenspeichervorrichtung weist weiterhin Mittel zum Bestimmen auf, dass mehrere Lesebefehle für die Wortleitung in einer Warteschlange sind. Die Datenspeichervorrichtung weist weiterhin Mittel zum Ausführen mindestens eines Lesebefehls der Vielzahl von Lesebefehlen auf, ohne eine VREAD-Spitzen-Entladung durchzuführen. Die Datenspeichervorrichtung weist weiterhin Mittel zum Entladen der Wortleitung nach dem Ausführen der Vielzahl von Lesebefehlen auf. Die Datenspeichervorrichtung weist weiterhin Mittel zum Bestimmen auf, dass alle Lesebefehle für die Wortleitung ausgeführt wurden. Die Datenspeichervorrichtung weist weiterhin Mittel zum Ausführen einer Vielzahl von Lesebefehlen in Warteschlangenreihenfolge auf, wobei die Vielzahl von Lesebefehlen für verschiedene Wortleitungen gilt.

**[0050]** Durch das Ordnen von Lesemessungen an einer gemeinsamen Wortleitung, derart, dass jeder nachfolgende Lesevorgang eine höhere Lesespannung verwendet, kann das Entladen zwischen Lesemessungen vermieden werden, was die Leseleistung erhöht und den Stromverbrauch verringert.

**[0051]** Während sich das Vorstehende auf Ausführungsformen der vorliegenden Offenbarung bezieht, können andere und weitere Ausführungsformen der Offenbarung ausgearbeitet werden, ohne vom grundlegenden Schutzumfang davon abzuweichen, und der Schutzumfang wird durch die nachstehenden Ansprüche bestimmt.

#### Patentansprüche

1. Datenspeichervorrichtung (104), aufweisend:

eine Speichervorrichtung (110): und

eine an die Speichervorrichtung gekoppelte Steuereinrichtung (108), die konfiguriert ist zum Durchführen der folgenden Schritte in der angegebenen Reihenfolge:

Empfangen (402) einer Vielzahl von Lesebefehlen für eine Wortleitung;

Umordnen (408) der Lesebefehle von einer niedrigsten Messspannung zu einer höchsten Messspannung; und

Ausführen der Lesebefehle, wobei das Ausführen der Lesebefehle Messen der Spannung einschließt und wobei die Wortleitung nicht zwischen Lesebefehlen entladen wird.

2. Datenspeichervorrichtung gemäß Anspruch 1, wobei die Steuereinrichtung weiterhin dazu konfiguriert ist, einen ersten Lesebefehl der Vielzahl von Lesebefehlen durch einen Prozess auszuführen, der aufweist: Hochsetzen (410) der Wortleitung von VSS auf VDD;

VREAD-Spitze (412), um einen Kanal vor dem Messen zu leeren;

Entladen (416) der VREAD-Spitze;

Laden (418) der Bitleitung;

Laden (420) der Wortleitung; und

Messen (422).

3. Datenspeichervorrichtung gemäß Anspruch 2, wobei die Steuereinrichtung weiterhin dazu konfiguriert ist, einen zweiten Lesebefehl der Vielzahl von Lesebefehlen durch einen Prozess auszuführen, der aufweist:

Hochsetzen (410) der Wortleitung von VSS auf VDD;

VREAD-Spitze (412), um einen Kanal vor dem Messen zu leeren;

Laden (418) der Bitleitung;

Laden (420) der Wortleitung; und

Messen (422).

4. Datenspeichervorrichtung gemäß Anspruch 3, wobei die Steuereinrichtung weiterhin dazu konfiguriert ist, einen dritten Lesebefehl der Vielzahl von Lesebefehlen durch einen Prozess auszuführen, der aufweist: Hochsetzen (410) der Wortleitung von VSS auf VDD;

VREAD-Spitze (412), um einen Kanal vor dem Messen zu leeren;

Laden (418) der Bitleitung;

Laden (420) der Wortleitung;

Messen (422); und

Entladen (426) der Wortleitung.

- 5. Datenspeichervorrichtung gemäß Anspruch 4, wobei die Steuereinrichtung dazu konfiguriert ist, den ersten Lesebefehl vor dem zweiten Lesebefehl auszuführen, wobei die Steuereinrichtung dazu konfiguriert ist, den zweiten Lesebefehl vor dem dritten Lesebefehl auszuführen.

- 6. Datenspeichervorrichtung gemäß Anspruch 5, wobei die Steuervorrichtung dazu konfiguriert ist, mindestens einen von dem zweiten Lesebefehl und dem dritten Lesebefehl vor dem Empfangen des ersten Lesebefehls zu empfangen.

- 7. Datenspeichervorrichtung gemäß Anspruch 1, wobei die Steuereinrichtung dazu konfiguriert ist, die Wortleitung nach dem Ausführen eines letzten Lesebefehls für die Wortleitung zu entladen.

- 8. Datenspeichervorrichtung (104), aufweisend:

eine Speichervorrichtung (110); und

eine an die Speichervorrichtung gekoppelte Steuereinrichtung (108), die konfiguriert ist zum Durchführen der folgenden Schritte in der angegebenen Reihenfolge:

Empfangen eines ersten Lesebefehls für eine Wortleitung, wobei der erste Lesebefehl eine erste Messspannung aufweist;

Prüfen einer Lesewarteschlange auf weitere Lesebefehle für die Wortleitung;

Bestimmen, dass ein zweiter Lesebefehl in der Lesewarteschlange vorhanden ist, wobei der zweite Lesebefehl für die Wortleitung eine zweite Messspannung aufweist, die niedriger als die erste Messspannung ist; Ausführen des zweiten Lesebefehls;

Ausführen des ersten Lesebefehls, wobei der erste Lesebefehl vor dem Entladen der Wortleitung ausgeführt wird; und

Entladen der Wortleitung.

- 8-1. Datenspeichervorrichtung gemäß Anspruch 8, wobei während der Ausführung des zweiten Lesebefehls eine VREAD-Spitzen-Entladung (416) stattfindet.

- 10. Datenspeichervorrichtung gemäß Anspruch 9, wobei während der Ausführung des ersten Lesebefehls keine VREAD-Spitzen-Entladung (418) stattfindet.

- 11. Datenspeichervorrichtung gemäß Anspruch 8, wobei die Steuereinrichtung weiterhin dazu konfiguriert ist, zu bestimmen, dass ein dritter Lesebefehl in der Lesewarteschlange vorliegt, wobei der zweite Lesebefehl in der Reihenfolge vor dem dritten Lesebefehl eingereiht ist.

- 12. Datenspeichervorrichtung gemäß Anspruch 11, wobei die Steuereinrichtung weiterhin dazu konfiguriert, den dritten Lesebefehl nach dem ersten Lesebefehl auszuführen, und wobei der dritte Lesebefehl vor dem Entladen der Wortleitung ausgeführt wird.

- 13. Datenspeichervorrichtung gemäß Anspruch 12, wobei während der Ausführung des zweiten Lesebefehls eine VREAD-Spitzen-Entladung stattfindet, wobei während der Ausführung des ersten Lesebefehls

keine VREAD-Spitzen-Entladung stattfindet und wobei während der Ausführung des dritten Lesebefehls keine VREAD-Spizen-Entladung stattfindet.

14. Datenspeichervorrichtung (104), aufweisend:

eine Speichervorrichtung (110);

Mittel zum Umordnen einer Reihenfolge der Ausführung einer Vielzahl von Lesebefehlen für eine Wortleitung; und

Mittel zum Ausführen der Vielzahl von Lesebefehlen, ohne die Wortleitung zwischen der Ausführung der einzelnen Lesebefehle zu entladen.

- 15. Datenspeichervorrichtung gemäß Anspruch 14, weiterhin aufweisend Mittel zum Bestimmen, dass mehrere Lesebefehle für die Wortleitung in einer Warteschlange sind.

- 16. Datenspeichervorrichtung gemäß Anspruch 14, weiterhin aufweisend Mittel zum Ausführen mindestens eines Lesebefehls der Vielzahl von Lesebefehlen, ohne eine VREAD-Spitzen-Entladung durchzuführen.

- 17. Datenspeichervorrichtung gemäß Anspruch 14, weiterhin aufweisend Mittel zum Entladen der Wortleitung nach dem Ausführen der Vielzahl von Lesebefehlen.

- 18. Datenspeichervorrichtung gemäß Anspruch 14, weiterhin aufweisend Mittel zum Bestimmen, dass alle Lesebefehle für die Wortleitung ausgeführt wurden.

- 19. Datenspeichervorrichtung gemäß Anspruch 14, weiterhin aufweisend Mittel zum Ausführen einer Vielzahl von Lesebefehlen in Warteschlangenreihenfolge auf, wobei die Vielzahl von Lesebefehlen für verschiedene Wortleitungen gilt.

Es folgen 4 Seiten Zeichnungen

# Anhängende Zeichnungen

Figur 1

Figur 2A

Figur 2B

Figur 3

Figur 4