US 20190148358A1

### (19) United States (12) Patent Application Publication (10) Pub. No.: US 2019/0148358 A1

### Davis et al.

May 16, 2019 (43) **Pub. Date:**

### (54) SEMICONDUCTOR DEVICES WITH PACKAGE-LEVEL CONFIGURABILITY

- (71) Applicant: Micron Technology, Inc., Boise, ID (US)

- (72)Inventors: James E. Davis, Meridian, ID (US); John B. Pusey, Meridian, ID (US); Zhiping Yin, Boise, ID (US); Kevin G. Duesman, Boise, ID (US)

- (21) Appl. No.: 16/007,903

- (22) Filed: Jun. 13, 2018

### **Related U.S. Application Data**

(63) Continuation of application No. 15/811,572, filed on Nov. 13, 2017, now Pat. No. 10,128,229.

### **Publication Classification**

(51) Int. Cl.

| H01L 27/02  | (2006.01) |

|-------------|-----------|

| H01L 23/00  | (2006.01) |

| H01L 25/065 | (2006.01) |

| H01L 25/00  | (2006.01) |

| H01L 49/02  | (2006.01) |

| H01L 27/115 | (2017.01) |

- (52) U.S. Cl.

- CPC H01L 27/0292 (2013.01); H01L 2224/48464 (2013.01); H01L 27/0288 (2013.01); H01L 24/13 (2013.01); H01L 25/0657 (2013.01);

H01L 25/50 (2013.01); H01L 24/49 (2013.01); H01L 2225/06506 (2013.01); H01L 2225/0651 (2013.01); H01L 2225/06527 (2013.01); H01L 2225/06562 (2013.01); H01L 2225/06565 (2013.01); H01L 28/40 (2013.01); H01L 2224/49112 (2013.01); H01L 2224/4845 (2013.01); H01L 2224/48227 (2013.01); H01L 2224/48145 (2013.01); H01L 2224/13028 (2013.01); H01L 27/115 (2013.01); H01L 24/48 (2013.01)

#### (57)ABSTRACT

A semiconductor device assembly includes a substrate and a die coupled to the substrate. The die includes a first contact pad electrically coupled to a first circuit on the die including at least one active circuit element, and a second contact pad electrically coupled to a second circuit on the die including only passive circuit elements. The substrate includes a substrate contact electrically coupled to both the first and second contact pads. The semiconductor device assembly can further include a second die including a third contact pad electrically coupled to a third circuit on the second die including at least a second active circuit element, and a fourth contact pad electrically coupled to a fourth circuit on the second die including only passive circuit elements. The substrate contact can be electrically coupled to the third contact pad and electrically disconnected from the fourth contact pad.

Figure 2 (Prior Art)

### SEMICONDUCTOR DEVICES WITH PACKAGE-LEVEL CONFIGURABILITY

### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application is a continuation of U.S. application Ser. No. 15/811,572, filed Nov. 13, 2017, which is incorporated herein by reference in its entirety.

**[0002]** This application contains subject matter related to a concurrently-filed U.S. Patent Application by James E. Davis, Kevin G. Duesman, Jeffrey P. Wright, and Warren L. Boyer, entitled "SEMICONDUCTOR DEVICES WITH POST-PROBE CONFIGURABILITY". The related application, of which the disclosure is incorporated by reference herein, is assigned to Micron Technology, Inc., and is identified by attorney docket number 010829-9271.US00.

### TECHNICAL FIELD

**[0003]** The present disclosure generally relates to semiconductor devices, and more particularly relates to semiconductor devices with package-level configurability.

### BACKGROUND

**[0004]** Packaged semiconductor dies, including memory chips, microprocessor chips, and imager chips, typically include one or more semiconductor dies mounted on a substrate and encased in a plastic protective covering or covered by a heat-conducting lid. The die can include active circuits (e.g., providing functional features such as memory cells, processor circuits, and/or imager devices) and/or passive features (e.g., capacitors, resistors, etc.) as well as bond pads electrically connected to the circuits. The bond pads can be electrically connected to terminals outside the protective covering to allow the die to be connected to higher level circuitry.

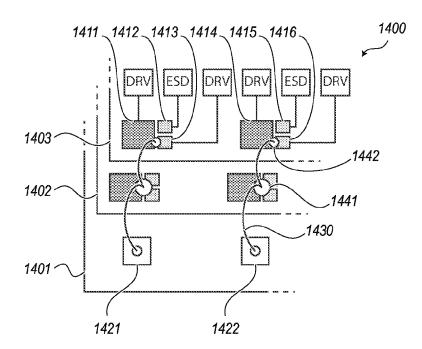

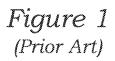

[0005] For example, FIG. 1 is a simplified partial crosssectional view of a semiconductor device assembly 100 including multiple semiconductor dies 102 and 103 stacked in a shingled fashion on a substrate 101 and covered by an encapsulant 170. Each die includes one or more contact pads, such as contact pads 122 and 123 to provide connectivity to a corresponding integrated circuit, such as circuits 162 and 163. The contact pads 122 and 123 can be connected to a substrate contact 121 by wirebonds 131 and 132 (shown in a daisy-chain configuration), to provide connectivity to circuits 162 and 163 via solder ball 151 (by way of via 152). [0006] With some semiconductor dies, various bond pads can be connected to multiple circuits in a die. For example, in a NAND memory die, a single bond pad may be connected to both an active driver circuit and a passive ESD protection circuit (e.g., including one or more capacitors). The ESD protection circuit can be designed to provide a desired amount of capacitance to protect the single active driver circuit. In a semiconductor device assembly including multiple such NAND memory dies with active driver circuits connected in parallel (e.g., with the corresponding bond pad from each NAND memory die connected to the same external terminal), the excess capacitance provided by the ESD protection circuit from each die being connected in parallel can degrade device performance. This can be addressed by designing different NAND memory dies for different package densities (e.g., a NAND memory die configured to be packaged alone, a different NAND memory die with less capacitive ESD protection circuits configured to be packaged in a stack of two, yet another NAND memory die with even less capacitive ESD protection circuits configured to be packaged in a stack of four, etc.), but designing and fabricating multiple different semiconductor dies for each possible package configuration is prohibitively expensive. Accordingly, there is a need for a semiconductor die that can be configured with different amounts of ESD protection depending upon the configuration in which the die is packaged.

### BRIEF DESCRIPTION OF THE DRAWINGS

**[0007]** FIG. **1** is a simplified partial cross-sectional view of a semiconductor device assembly including multiple semiconductor dies stacked on a substrate.

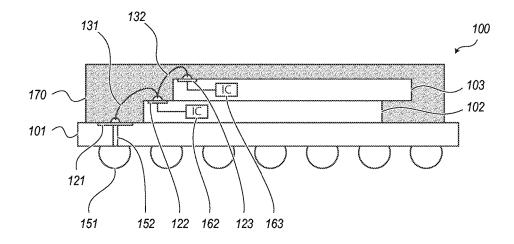

**[0008]** FIG. **2** is a simplified schematic view of a semiconductor device assembly.

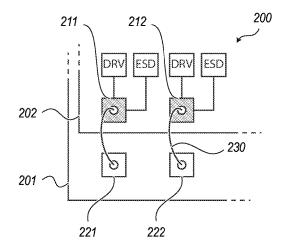

**[0009]** FIG. **3** is a simplified schematic view of a semiconductor device in accordance with an embodiment of the present technology.

**[0010]** FIGS. **4-6** are simplified schematic views of semiconductor device assemblies in accordance with embodiments of the present technology.

**[0011]** FIG. 7 is a simplified schematic view of a semiconductor device in accordance with an embodiment of the present technology.

**[0012]** FIGS. **8-14** are simplified schematic views of semiconductor device assemblies in accordance with embodiments of the present technology.

**[0013]** FIGS. **15-17** are simplified partial cross-sectional views of semiconductor devices in accordance with embodiments of the present technology.

[0014] FIG. 18 is a schematic view showing a system that includes a semiconductor device assembly configured in accordance with an embodiment of the present technology. [0015] FIG. 19 is a flow chart illustrating a method of making a semiconductor device in accordance with an embodiment of the present technology.

#### DETAILED DESCRIPTION

**[0016]** In the following description, numerous specific details are discussed to provide a thorough and enabling description for embodiments of the present technology. One skilled in the relevant art, however, will recognize that the disclosure can be practiced without one or more of the specific details. In other instances, well-known structures or operations often associated with semiconductor devices are not shown, or are not described in detail, to avoid obscuring other aspects of the technology. In general, it should be understood that various other devices, systems, and methods in addition to those specific embodiments disclosed herein may be within the scope of the present technology.

**[0017]** As discussed above, when semiconductor dies with an ESD protection circuit connected to the same bond pad as an active circuit (e.g., a driver circuit) are connected together in different package densities, the amount of capacitance provided by the ESD protection circuit cannot be optimized for each package density. Accordingly, several embodiments of semiconductor devices in accordance with the present technology can provide package-level configurability of a provided capacitance to overcome this challenge.

**[0018]** Several embodiments of the present technology are directed to semiconductor device assemblies including a

substrate and a die coupled to the substrate. The die includes a first contact pad electrically coupled to a first circuit on the die including at least one active circuit element, and a second contact pad electrically coupled to a second circuit on the die including only passive circuit elements. The substrate includes a substrate contact electrically coupled to both the first and second contact pads. The semiconductor device assemblies can further include a second die including a third contact pad electrically coupled to a third circuit on the second die including at least a second active circuit element, and a fourth contact pad electrically coupled to a fourth circuit on the second die including only passive circuit elements. The substrate contact can be electrically coupled to the third contact pad and electrically disconnected from the fourth contact pad.

**[0019]** Specific details of several embodiments of semiconductor devices are described below. The term "semiconductor device" generally refers to a solid-state device that includes a semiconductor material. A semiconductor device can include, for example, a semiconductor substrate, wafer, or die that is singulated from a wafer or substrate. Throughout the disclosure, semiconductor devices are generally described in the context of semiconductor dies; however, semiconductor devices are not limited to semiconductor dies.

[0020] The term "semiconductor device package" can refer to an arrangement with one or more semiconductor devices incorporated into a common package. A semiconductor package can include a housing or casing that partially or completely encapsulates at least one semiconductor device. A semiconductor device package can also include an interposer substrate that carries one or more semiconductor devices and is attached to or otherwise incorporated into the casing. The term "semiconductor device assembly" can refer to an assembly of one or more semiconductor devices, semiconductor device packages, and/or substrates (e.g., interposer, support, or other suitable substrates). The semiconductor device assembly can be manufactured, for example, in discrete package form, strip or matrix form, and/or wafer panel form. As used herein, the terms "vertical," "lateral," "upper," and "lower" can refer to relative directions or positions of features in the semiconductor device or device assembly in view of the orientation shown in the Figures. For example, "upper" or "uppermost" can refer to a feature positioned closer to or closest to, respectively, the top of a page than another feature or portion of the same feature. These terms, however, should be construed broadly to include semiconductor devices having other orientations, such as inverted or inclined orientations where top/bottom, over/under, above/below, up/down, and left/ right can be interchanged depending on the orientation.

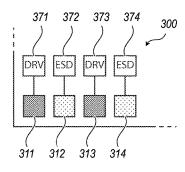

**[0021]** FIG. **2** is a simplified schematic view of a semiconductor device assembly **200** including a semiconductor die **202** coupled to a substrate **201**. The die includes contact pads, such as contact pads **211** and **212**, which are each connected to both an integrated circuit with active components (schematically illustrated as a driver (DRV) circuit), and an integrated circuit with passive components (schematically illustrated as an electrostatic discharge (ESD) protection circuit). The contact pads **211** and **212** are electrically coupled by wirebonds **230** to substrate contacts **221** and **222**. As can be seen with reference to FIG. **2**, if semiconductor die **202** has been configured with an amount of capacitance suitable to provide ESD protection for a single driver circuit, then adding another such semiconductor die to the assembly 200 can undesirably increase the capacitance "seen" by the substrate contacts 221 and 222. [0022] To address this problem, embodiments of the present technology can provide a semiconductor die in which an active circuit, and the passive circuit configured to provide ESD protection thereto, are connected to separate contact pads, such that a desired amount of capacitance can be provided regardless of the number of dies provided in a package assembly. For example, FIG. 3 is a simplified schematic view of a semiconductor device 300 in accordance with an embodiment of the present technology. Semiconductor device 300 includes a plurality of contact pads, such as first through fourth contact pads 311-314, for providing connectivity to circuits in the semiconductor device 300. For example, the first contact pad 311 provides connectivity to a first circuit 371 with active components (e.g., a driver circuit), and the second contact pad 312 provides connectivity to a second circuit 372 with passive components (e.g., an ESD protection circuit). Similarly, the third contact pad 313 provides connectivity to a third circuit 373 with active components (e.g., a driver circuit), and the fourth contact pad 314 provides connectivity to a fourth circuit 374 with passive components (e.g., an ESD protection circuit). By providing each passive circuit with a dedicated contact pad, semiconductor device 300 makes possible different packaging densities utilizing multiple identical semiconductor dies, while providing a desired amount of ESD protection and without, e.g., excess capacitance causing the driver circuits 371 and 373 to consume excess power.

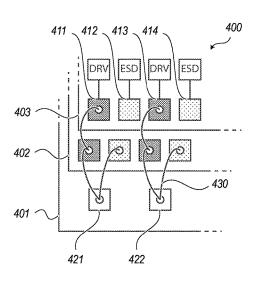

[0023] This can be better understood with reference to FIG. 4, which is a simplified schematic view of a semiconductor device assembly 400 in accordance with an embodiment of the present technology. Assembly 400 includes a substrate 401 and two semiconductor dies 402 and 403 (e.g., identical semiconductor dies). Like the semiconductor device 300 illustrated in FIG. 3 above, each semiconductor die 402 and 403 includes multiple contact pads, such as first through fourth contact pads 411-414, each providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit). Because each ESD protection circuit is provided with a dedicated contact pad, the assembly 400 can be configured with a desired amount of ESD protection for each driver circuit.

[0024] As can be seen with reference to FIG. 4, the substrate 401 includes two substrate contacts 421 and 422. The first substrate contact 421 is connected (e.g., by wirebonds 430) to the first contact pad 411 (corresponding to a driver circuit) of each semiconductor die 402 and 403 in the assembly 400, but is connected to the second contact pad 412 (corresponding to an ESD protection circuit) of only one semiconductor die 402 in the assembly 400. Similarly, the second substrate contact 422 is connected (e.g., by wirebonds 430) to the third contact pad 413 (corresponding to a driver circuit) of each semiconductor die 402 and 403 in the assembly 400, but is connected to the fourth contact pad 414 (corresponding to an ESD protection circuit) of only one semiconductor die 402 in the assembly 400. By leaving electrically disconnected from the substrate contacts 421 and 422 the second and fourth contact pads 412 and 414 (corresponding to ESD protection circuits) on the upper semiconductor die 403, the capacitance of the circuit to which each substrate contact 421 and 422 is connected is less than

it would be if ESD protection circuits from each die in the assembly **400** were connected.

[0025] Although FIG. 4 has been described and illustrated as including multiple identical semiconductor dies, in other embodiments of the present technology semiconductor device assemblies with different types of dies can be provided with similar features. For example, in one embodiment a semiconductor device assembly can include a logic die and a memory die, one or both of which can include discrete contact pads for passive circuits to be connected as desired during packaging. Moreover, although FIG. 4 has been described and illustrated as including semiconductor dies with two driver circuits, it will be readily apparent to those skilled in the art that this embodiment is but one example, and semiconductor dies with different numbers of driver circuits can also be provided. Furthermore, FIG. 4 has been described and illustrated as providing contact pads for ESD protection circuits separate from contact pads for driver circuits, in other embodiments circuits with other active elements besides drivers can be provided, and other circuits including only passive components (e.g., resistors, capacitors, inductors, etc.) can likewise be provided.

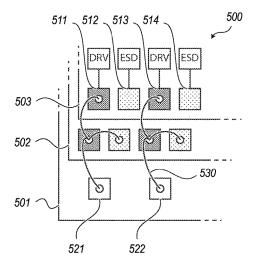

[0026] Although FIG. 4 has been described and illustrated with multiple wirebonds at each substrate contact 421 and 422 for providing connectivity to multiple contact pads in one of the semiconductor dies 402 in the assembly 400, in other embodiments of the present technology, other wirebond arrangements can be used. For example, FIG. 5 is a simplified schematic view of a semiconductor device assembly 500 in accordance with an embodiment of the present technology. Assembly 500 includes a substrate 501 and two semiconductor dies 502 and 503, each including multiple contact pads, such as first through fourth contact pads 511-514, for providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit).

[0027] As can be seen with reference to FIG. 5, the substrate 501 includes two substrate contacts 521 and 522. The first substrate contact 521 is connected by a wirebond 530 to the first contact pad 511 (corresponding to a driver circuit) of the first semiconductor die 502, which is connected in turn by another wirebond 530 to the first contact pad 511 (corresponding to a driver circuit) of the second semiconductor die 503. The first substrate contact 521 is further connected to the second contact pad 512 (corresponding to an ESD protection circuit) of only one semiconductor die 502 in the assembly 500 (e.g., by a wirebond between the first contact pad 511 and the second contact pad 512 of the first semiconductor die 502). Similarly, the second substrate contact 522 is connected by a wirebond 530 to the third contact pad 513 (corresponding to a driver circuit) of the first semiconductor die 502, which is connected in turn by another wirebond 530 to the third contact pad 513 (corresponding to a driver circuit) of the second semiconductor die 503. The second substrate contact 522 is further connected to the fourth contact pad 514 (corresponding to an ESD protection circuit) of only one semiconductor die 502 in the assembly 500 (e.g., by a wirebond between the third contact pad 513 and the fourth contact pad 514 of the first semiconductor die 502).

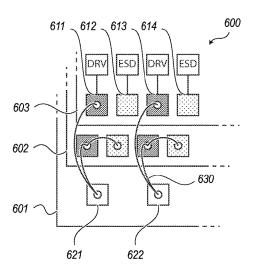

**[0028]** Still other wirebond arrangements are possible, for example as illustrated in FIG. **6**, which is a simplified schematic view of a semiconductor device assembly **600** in accordance with an embodiment of the present technology.

Assembly 600 includes a substrate 601 and two semiconductor dies 602 and 603, each including multiple contact pads, such as first through fourth contact pads 611-614, for providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit).

[0029] As can be seen with reference to FIG. 6, the substrate 601 includes two substrate contacts 621 and 622. The first substrate contact 621 is connected by a wirebond 630 directly to the first contact pad 611 (corresponding to a driver circuit) of the first semiconductor die 602, and by another wirebond directly to the first contact pad 611 (corresponding to a driver circuit) of the second semiconductor die 603. The first substrate contact 621 is further connected to the second contact pad 612 (corresponding to an ESD protection circuit) of only one semiconductor die 602 in the assembly 600 (e.g., by a wirebond between the first contact pad 611 and the second contact pad 612 of the first semiconductor die 602). Similarly, the second substrate contact 622 is connected by a wirebond 630 directly to the third contact pad 613 (corresponding to a driver circuit) of the first semiconductor die 602, and by another wirebond directly the third contact pad 613 (corresponding to a driver circuit) of the second semiconductor die 603. The second substrate contact 622 is further connected to the fourth contact pad 614 (corresponding to an ESD protection circuit) of only one semiconductor die 602 in the assembly 600 (e.g., by a wirebond between the third contact pad 613 and the fourth contact pad 614 of the first semiconductor die 602).

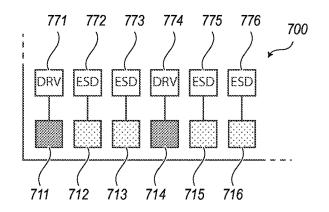

[0030] Although in the foregoing examples semiconductor dies have been described and illustrated as including a single ESD protection circuit corresponding to each driver circuit, in other embodiments of the present technology, additional configurability can be provided by including multiple ESD protection circuits with dedicated contact pads corresponding to each driver circuit on a semiconductor die. For example, FIG. 7 is a simplified schematic view of a semiconductor device 700 in accordance with an embodiment of the present technology. Semiconductor device 700 includes a plurality of contact pads, such as first through sixth contact pads 711-716, for providing connectivity to circuits in the semiconductor device 700. For example, the first contact pad 711 provides connectivity to a first circuit 771 with active components (e.g., a driver circuit), and the second and third contact pads 712 and 713 provide connectivity to second and third circuits 772 and 773, respectively, which include only passive components (e.g., ESD protection circuits). Similarly, the fourth contact pad 714 provides connectivity to a fourth circuit 774 with active components (e.g., a driver circuit), and the fifth and sixth contact pads 715 and 716 provide connectivity to fifth and sixth circuits 775 and 776, respectively, which include only passive components (e.g., ESD protection circuits). By providing each active circuit with multiple corresponding passive circuits, each with their own dedicated contact pad, semiconductor device 700 makes possible different packaging densities utilizing multiple identical semiconductor dies, while providing a desired amount of ESD protection without, e.g., excess capacitance causing the driver circuits 771 and 774 to consume excess power.

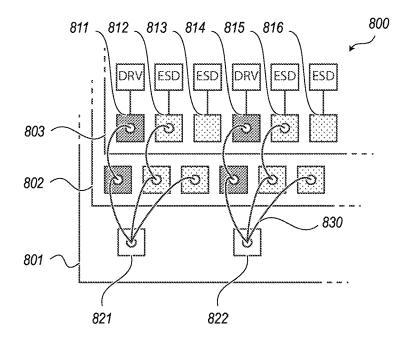

**[0031]** This can be better understood with reference to FIG. **8**, which is a simplified schematic view of a semiconductor device assembly **800** in accordance with an embodiment of the present technology. Assembly **800** includes a

substrate **801** and two semiconductor dies **802** and **803** (e.g., identical semiconductor dies). Like the semiconductor device **700** illustrated in FIG. **7** above, each semiconductor die **802** and **803** includes multiple contact pads, such as first through sixth contact pads **811-816**, each providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit). Because each ESD protection circuit is provided with a dedicated contact pad, the assembly **800** can be configured with a desired amount of ESD protection for each driver circuit.

[0032] As can be seen with reference to FIG. 8, the substrate 801 includes two substrate contacts 821 and 822. The first substrate contact 821 is connected (e.g., by wirebonds 830) to the first contact pad 811 (corresponding to a driver circuit) of each semiconductor die 802 and 803 in the assembly 800, and is connected to the second contact pad 812 (corresponding to an ESD protection circuit) of each semiconductor die 802 and 803 in the assembly 800, but is connected to the third contact pad 813 (corresponding to another ESD protection circuit) of only one semiconductor die 802 in the assembly 800. Similarly, the second substrate contact 822 is connected (e.g., by wirebonds 830) to the fourth contact pad 814 (corresponding to a driver circuit) of each semiconductor die 802 and 803 in the assembly 800, and is connected to the fifth contact pad 815 (corresponding to an ESD protection circuit) of each semiconductor die 802 and 803 in the assembly 800, but is connected to the sixth contact pad 816 (corresponding to another ESD protection circuit) of only one semiconductor die 802 in the assembly 800. By leaving electrically disconnected from the substrate contacts 821 and 822 the third and sixth contact pads 813 and 816 (corresponding to ESD protection circuits) on the upper semiconductor die 803, the capacitance of the circuit to which each substrate contact 821 and 822 is connected is less than it would be if ESD protection circuits from each die in the assembly 800 were connected.

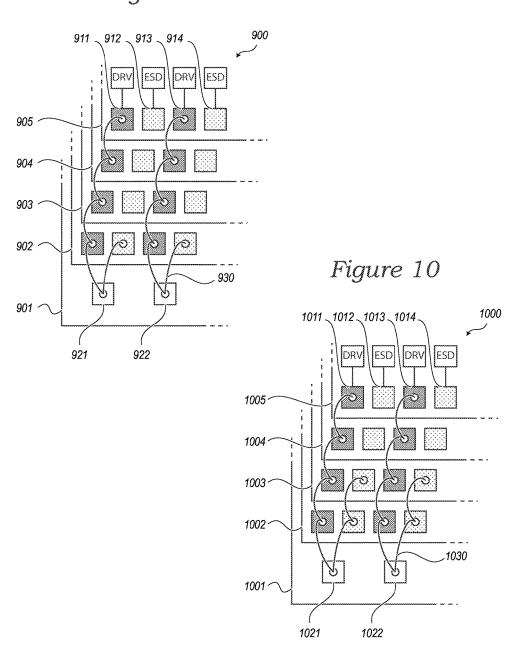

[0033] Although in the foregoing embodiments semiconductor device assemblies have been illustrated and described with two semiconductor dies, in other embodiments of the present technology semiconductor device assemblies can include different numbers of dies. For example, FIG. 9 is a simplified schematic view of a semiconductor device assembly 900 including four semiconductor dies in accordance with an embodiment of the present technology. Assembly 900 includes a substrate 901 and four semiconductor dies 902-905 (e.g., identical semiconductor dies). Like the semiconductor device 300 illustrated in FIG. 3 above, each semiconductor die 902-905 includes multiple contact pads, such as first through fourth contact pads 911-914, each providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit). Because each ESD protection circuit is provided with a dedicated contact pad, the assembly 900 can be configured with a desired amount of ESD protection for each driver circuit.

[0034] As can be seen with reference to FIG. 9, the substrate 901 includes two substrate contacts 921 and 922. The first substrate contact 921 is connected (e.g., by wirebonds 930) to the first contact pad 911 (corresponding to a driver circuit) of each semiconductor die 902-905 in the assembly 900, but is connected to the second contact pad 912 (corresponding to an ESD protection circuit) of only one semiconductor die 902 in the assembly 900. Similarly, the

second substrate contact **922** is connected (e.g., by wirebonds **930**) to the third contact pad **913** (corresponding to a driver circuit) of each semiconductor die **902-905** in the assembly **900**, but is connected to the fourth contact pad **914** (corresponding to an ESD protection circuit) of only one semiconductor die **902** in the assembly **900**. By leaving electrically disconnected from the substrate contacts **921** and **922** the second and fourth contact pads **912** and **914** (corresponding to ESD protection circuits) on three of the semiconductor dies **903-905**, the capacitance of the circuit to which each substrate contact **921** and **922** is connected is less than it would be if ESD protection circuits from each die in the assembly **900** were connected.

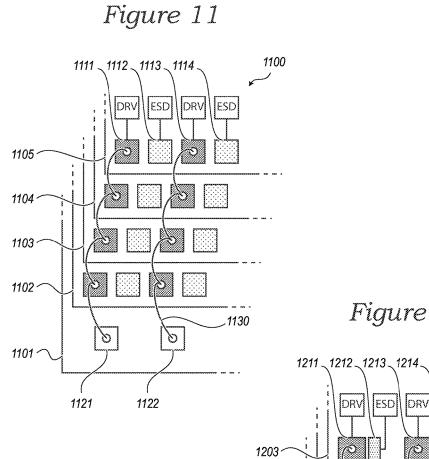

**[0035]** Although in the embodiment illustrated in FIG. 9 the ESD protection circuits of only one die in the assembly are connected to the substrate contacts, in other embodiments a semiconductor device assembly can include multiple dies that have ESD protection circuits connected to the substrate contact(s) thereof. For example, FIG. 10 is a simplified schematic view of a semiconductor device assembly 1000 in accordance with an embodiment of the present technology. Assembly 1000 includes a substrate 1001 and four semiconductor dies 1002-1005 (e.g., identical semiconductor dies), each including multiple contact pads, such as first through fourth contact pads 1011-1014, for providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit).

[0036] As can be seen with reference to FIG. 10, the substrate 1001 includes two substrate contacts 1021 and 1022. The first substrate contact 1021 is connected (e.g., by wirebonds 1030) to the first contact pad 1011 (corresponding to a driver circuit) of each semiconductor die 1002-1005 in the assembly 1000, but is connected to the second contact pad 1012 (corresponding to an ESD protection circuit) of only two of the semiconductor dies 1002 and 1003 in the assembly 1000. Similarly, the second substrate contact 1022 is connected (e.g., by wirebonds 1030) to the third contact pad 1013 (corresponding to a driver circuit) of each semiconductor die 1002-1005 in the assembly 1000, but is connected to the fourth contact pad 1014 (corresponding to an ESD protection circuit) of only two of the semiconductor dies 1002 and 1003 in the assembly 1000. By leaving electrically disconnected from the substrate contacts 1021 and 1022 the second and fourth contact pads 1012 and 1014 (corresponding to ESD protection circuits) on two of the semiconductor dies 1004 and 1005, the capacitance of the circuit to which each substrate contact 1021 and 1022 is connected is less than it would be if ESD protection circuits from each die in the assembly 1000 were connected.

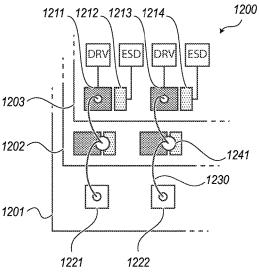

[0037] Although in the foregoing embodiments semiconductor device assemblies have been illustrated in which at least one die includes attached ESD protection circuits, in other embodiments of the present technology semiconductor device assemblies can include multiple dies, all of which include ESD protection circuits that are not connected (e.g., reliant on the inherent capacitance of the multiple driver circuits, such that there is no need for additional capacitance). For example, FIG. **11** is a simplified schematic view of a semiconductor device assembly **1100** in accordance with an embodiment of the present technology. Assembly **1100** includes a substrate **1101** and four semiconductor dies **1102-1105** (e.g., identical semiconductor dies), each including multiple contact pads, such as first through fourth contact pads **1111-1114**, for providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit).

[0038] As can be seen with reference to FIG. 11, the substrate 1101 includes two substrate contacts 1121 and **1122**. The first substrate contact **1121** is connected (e.g., by wirebonds 1130) to the first contact pad 1111 (corresponding to a driver circuit) of each semiconductor die 1102-1105 in the assembly 1100, but is connected to none of the second contact pads 1112 (corresponding to an ESD protection circuit) of any of the semiconductor dies 1102-1105 in the assembly 1100. Similarly, the second substrate contact 1122 is connected (e.g., by wirebonds 1130) to the third contact pad 1113 (corresponding to a driver circuit) of each semiconductor die 1102-1105 in the assembly 1100, but is connected to none of the fourth contact pads 1114 (corresponding to an ESD protection circuit) of any of the semiconductor dies 1102-1105 in the assembly 1100. By leaving electrically disconnected from the substrate contacts 1121 and 1122 the second and fourth contact pads 1112 and 1114 (corresponding to ESD protection circuits) on all of the semiconductor dies 1102-1105, the capacitance of the circuit to which each substrate contact 1121 and 1122 is connected is less than it would be if ESD protection circuits from any of the dies in the assembly 1100 were connected.

[0039] Although in the foregoing embodiments the dedicated contact pad for each connected ESD protection circuit is illustrated and described as having a corresponding dedicated wirebond, in other embodiments of the present technology contact pads can be connected in other ways. For example, FIG. 12 is a simplified schematic view of a semiconductor device assembly 1200 in accordance with an embodiment of the present technology. Assembly 1200 includes a substrate 1201 and two semiconductor dies 1202 and 1203 (e.g., identical semiconductor dies). Each semiconductor die 1202 and 1203 includes multiple contact pads, such as first through fourth contact pads 1211-1214, each providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit). The second and fourth contact pads 1212 and 1214 are disposed immediately adjacent the corresponding first and third contact pads 1211 and 1213, respectively, so that a single wirebond 1230 can be used to connect both pads.

[0040] As can be seen with reference to FIG. 12, the substrate 1201 includes two substrate contacts 1221 and 1222. The first substrate contact 1221 is connected by a single wirebond 1230 to both the first contact pad 1211 (corresponding to a driver circuit) and the second contact pad 1212 (corresponding to an ESD protection circuit) of the first semiconductor die 1202 (e.g., with a solder bond 1241). The first substrate contact 1221 is further connected by a wirebond 1230 between the solder bond 1241 connecting the first and second contact pads 1211 and 1212 of the first semiconductor die 1202 and the first contact pad 1211 (corresponding to a driver circuit) of the second semiconductor die 1203. Similarly, the second substrate contact 1222 is connected by a single wirebond 1230 to both the third contact pad 1213 (corresponding to a driver circuit) and the fourth contact pad 1214 (corresponding to an ESD protection circuit) of the first semiconductor die 1202 (e.g., with a solder bond 1241). The second substrate contact 1222 is further connected by a wirebond 1230 between the solder bond 1241 connecting the third and fourth contact pads 1213 and 1214 of the first semiconductor die 1202 and the third contact pad 1213 (corresponding to a driver circuit) of the second semiconductor die 1203.

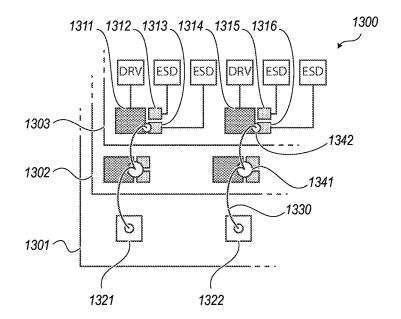

[0041] The foregoing approach of connecting to multiple contact pads with a single wirebond can be extended to embodiments of the present technology in which more than one ESD protection circuit is provided for each driver circuit. For example, FIG. 13 is a simplified schematic view of a semiconductor device assembly 1300 in accordance with an embodiment of the present technology. Assembly 1300 includes a substrate 1301 and two semiconductor dies 1302 and 1303 (e.g., identical semiconductor dies). Each semiconductor die 1302 and 1303 includes multiple contact pads, such as first through sixth contact pads 1311-1316, each providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit). The second and third contact pads 1312 and 1313 are disposed immediately adjacent the corresponding first contact pad 1311, so that a single wirebond 1330 can be used to connect the first contact pad 1311 to one or both (or neither) of the second and third contact pads 1312 and 1313. Similarly, the fifth and sixth contact pads 1315 and 1316 are disposed immediately adjacent the corresponding fourth contact pad 1314, so that a single wirebond 1330 can be used to connect the fourth contact pad 1314 to one or both (or neither) of the fifth and sixth contact pads 1315 and 1316.

[0042] As can be seen with reference to FIG. 13, the substrate 1301 includes two substrate contacts 1321 and 1322. The first substrate contact 1321 is connected by a single wirebond 1330 to the first, second and third contact pads 1311-1313 of the first semiconductor die 1302 (e.g., with a first solder bond 1341). The first substrate contact 1321 is further connected by a wirebond 1330 between the first solder bond 1341 and a second solder bond 1342 spanning the first and third contact pads 1311 and 1313 of the second semiconductor die 1303. Similarly, the second substrate contact 1322 is connected by a single wirebond 1330 to the fourth, fifth and sixth contact pads 1314-1316 of the first semiconductor die 1302 (e.g., with a first solder bond 1341). The second substrate contact 1322 is further connected by a wirebond 1330 between the first solder bond 1341 and a second solder bond 1342 spanning the fourth and sixth contact pads 1314 and 1316 of the second semiconductor die 1303.

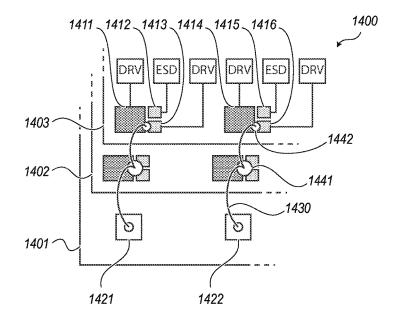

[0043] The foregoing approach of connecting to multiple contact pads with a single wirebond can be extended to embodiments of the present technology in which multiple circuits on a die can be optionally connected by a single wirebond. For example, FIG. 14 is a simplified schematic view of a semiconductor device assembly 1400 in accordance with an embodiment of the present technology. Assembly 1400 includes a substrate 1401 and two semiconductor dies 1402 and 1403 (e.g., identical semiconductor dies). Each semiconductor die 1402 and 1403 includes multiple contact pads, such as first through sixth contact pads 1411-1416, each providing connectivity to either a circuit with active components (e.g., a driver circuit) or a circuit with passive components (e.g., an ESD protection circuit). In a manner to that illustrated in FIG. 13, above, the second and third contact pads 1412 and 1414 are disposed immediately adjacent the corresponding first contact pad 1411, so that a single wirebond 1430 can be used to connect

the first contact pad 1411 to one or both (or neither) of the second and third contact pads 1412 and 1414. Similarly, the fifth and sixth contact pads 1415 and 1416 are disposed immediately adjacent the corresponding fourth contact pad 1414, so that a single wirebond 1430 can be used to connect the fourth contact pad 1414 to one or both (or neither) of the fifth and sixth contact pads 1415 and 1416. Unlike in FIG. 13, however, the third and sixth contact pads 1413 and 1416 are connected not to an additional ESD protection circuit, but are instead connected to a second driver circuit.

[0044] As can be seen with reference to FIG. 14, the substrate 1401 includes two substrate contacts 1421 and 1422. The first substrate contact 1421 is connected by a single wirebond 1430 to the first, second and third contact pads 1411-1414 of the first semiconductor die 1402 (e.g., with a first solder bond 1441). The first substrate contact 1421 is further connected by a wirebond 1430 between the first solder bond 1441 and a second solder bond 1442 spanning the first and third contact pads 1411 and 1414 of the second semiconductor die 1403. Similarly, the second substrate contact 1422 is connected by a single wirebond 1430 to the fourth, fifth and sixth contact pads 1414-1416 of the first semiconductor die 1402 (e.g., with a first solder bond 1441). The second substrate contact 1422 is further connected by a wirebond 1430 between the first solder bond 1441 and a second solder bond 1442 spanning the fourth and sixth contact pads 1414 and 1416 of the second semiconductor die 1403.

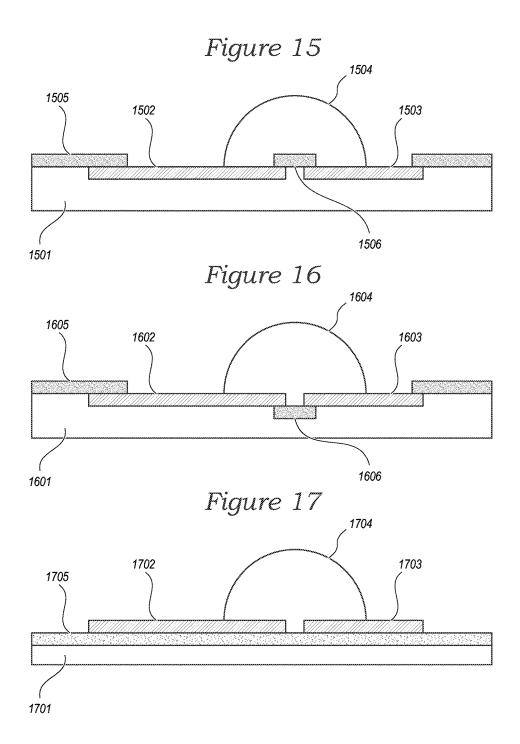

[0045] In a similar fashion, other embodiments of the present technology can provide semiconductor dies with closely-spaced bond pads for optionally connecting any number of different circuits, with any desired function in addition to or in lieu of ESD protection circuits and driver circuits. Moreover, closely-spaced bond pads, such as those illustrated in the examples of FIGS. 12-14 above, can be provided in any one of a number of ways. For example, FIG. 15 illustrates a simplified partial cross-sectional view of a semiconductor device in accordance with an embodiment of the present technology. In the semiconductor device 1501 illustrated in FIG. 15, closely spaced bond pads 1502 and 1503 are provided under a layer of passivation or polymide material 1505, and therefore separated by a small region 1506 of the passivation or polymide material. A solder ball 1504 of sufficient volume can be provided to bridge this region 1506 of passivation or polymide material, and therefore connect the closely spaced bond pads 1502 and 1503. [0046] By way of further example, FIG. 16 illustrates a simplified partial cross-sectional view of another semiconductor device in accordance with an embodiment of the present technology. In the semiconductor device 1601 illustrated in FIG. 16, closely spaced bond pads 1602 and 1603 are provided under a layer of passivation or polymide material 1605, but additional process steps have been undertaken to eliminate the passivation or polymide material 1605 from between the closely spaced bond pads 1602 and 1603 (e.g., by including an etch stop material 1606 under the region between the closely spaced bond pads 1602 and 1603, to permit etching away the passivation or polymide material 1605 from between them). This arrangement facilitates easily connecting a solder ball 1604 to both the closely spaced bond pads 1602 and 1603 (due to the absence of non-wettable material between them).

[0047] In yet another example, FIG. 17 illustrates a simplified partial cross-sectional view of another semiconductor

device in accordance with an embodiment of the present technology. In the semiconductor device **1701** illustrated in FIG. **17**, closely spaced bond pads **1702** and **1703** are provided over a layer of passivation or polymide material **1705** (e.g., in a redistribution layer). This arrangement also facilitates easily connecting a solder ball **1704** to both the closely spaced bond pads **1702** and **1703** (due to the absence of non-wettable material between them).

**[0048]** Although in the foregoing examples semiconductor device packages have been illustrated in which circuits with passive elements (e.g., ESD protection circuits) have been illustrated and described with dedicated contact pads for providing connectivity via wirebonds, those skilled in the art will readily understand that other methods of die-to-die or die-to-substrate connectivity can also be used to provide package-level connection configurability. For example, semiconductor dies in which circuits of passive components have dedicated TSVs can be arranged in non-shingled stacks, with optional connectivity provided by the inclusion or omission of solder joints between adjacent TSVs in the stack. Other interconnection techniques can likewise be provided.

[0049] Moreover, although in the foregoing examples semiconductor device assemblies have been described as including a single stack of semiconductor dies, in other embodiments of the present technology, a semiconductor device assembly can include multiple stacks of semiconductor dies in which passive circuits can optionally be connected via dedicated contact pads. For example, in one embodiment of the present technology, a semiconductor device assembly can include multiple laterally-separated stacks of semiconductor dies (e.g., two stacks of four dies each, two stacks of eight dies each, four stacks of four dies each, etc.) in which less than all of the available ESD circuits in each stack are electrically coupled to an active circuit. In another embodiment, a semiconductor device assembly can include a single stack of semiconductor dies in which subsets of the dies in the stack are separately connected to the substrate (e.g., a shingled stack with eight dies grouped as a first subset electrically coupled to the substrate, with less than all of the available dies in the first subset having electrically coupled ESD circuits, and another eight dies above the first eight dies, with a shingle offset direction opposite that of the first subset, grouped as a second subset electrically coupled to the substrate separately from the first subset, with less than all of the available dies in the second subset having electrically coupled ESD circuits, etc.).

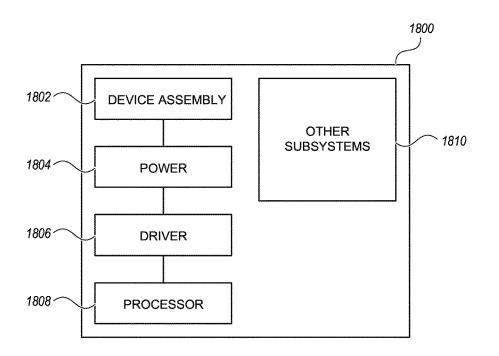

[0050] Any one of the semiconductor device assemblies described above with reference to FIGS. 3-17 can be incorporated into any of a myriad of larger and/or more complex systems, a representative example of which is system 1800 shown schematically in FIG. 18. The system 1800 can include a semiconductor device assembly 1802, a power source 1804, a driver 1806, a processor 1808, and/or other subsystems or components 1810. The semiconductor device assembly 1802 can include features generally similar to those of the semiconductor devices described above with reference to FIGS. 3-15. The resulting system 1800 can perform any of a wide variety of functions, such as memory storage, data processing, and/or other suitable functions. Accordingly, representative systems 1800 can include, without limitation, hand-held devices (e.g., mobile phones, tablets, digital readers, and digital audio players), computers, vehicles, appliances and other products. Components of the system **1800** may be housed in a single unit or distributed over multiple, interconnected units (e.g., through a communications network). The components of the system **1800** can also include remote devices and any of a wide variety of computer readable media.

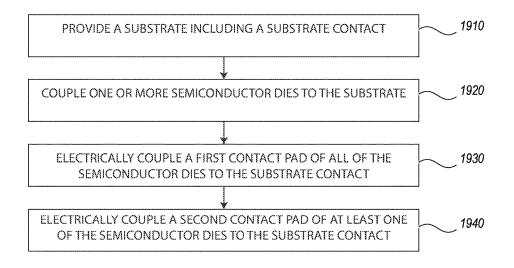

[0051] FIG. 19 is a flow chart illustrating a method of making a semiconductor device assembly. The method includes providing a substrate that includes a substrate contact (box 1910) and coupling one or more semiconductor dies to the substrate (box 1920). Each of the one or more semiconductor dies includes a first contact pad electrically coupled to a first circuit on the semiconductor die including at least one active circuit element, and a second contact pad electrically coupled to a second circuit on the semiconductor die including at least one active circuit element, and a second contact pad electrically coupled to a second circuit on the semiconductor die including only passive circuit elements. The method further includes electrically coupling the first contact pad of all of the one or more semiconductor dies to the substrate contact (box 1930) and electrically coupling the second contact pads of at least one of the one or more semiconductor dies to the substrate contact (box 1940).

**[0052]** From the foregoing, it will be appreciated that specific embodiments of the invention have been described herein for purposes of illustration, but that various modifications may be made without deviating from the scope of the invention. Accordingly, the invention is not limited except as by the appended claims.

1. A semiconductor device assembly, comprising:

- a substrate;

- a die coupled to the substrate, the die including:

- a first contact pad electrically coupled to a first circuit on the die including at least one active circuit element, and

- a second contact pad electrically coupled to a second circuit on the die including only passive circuit elements;

- wherein the substrate includes a substrate contact electrically coupled to both the first contact pad and the second contact pad on the die by a single wirebond and a solder ball in electrical contact with the wirebond, the first contact pad and the second contact pad, and

- wherein the first die further includes a third contact pad electrically coupled to a third circuit on the first die

including only passive circuit elements, and wherein the substrate contact is electrically coupled to the third contact pad on the first die by the wirebond, and wherein the solder ball is further in electrical contact with the third contact pad.

2. The semiconductor device assembly of claim 1, wherein the die is a first die, further comprising:

a second die including:

- a fourth contact pad electrically coupled to a fourth circuit on the second die including at least a second active circuit element, and

- a fifth contact pad electrically coupled to a fifth circuit on the second die including only passive circuit elements;

- wherein the substrate contact is electrically coupled to the fourth contact pad on the second die, and

- wherein the fifth contact pad on the second die is electrically disconnected from the substrate contact.

**3**. The semiconductor device assembly of claim **2**, wherein the first and second dies are identical dies, wherein the first contact pad on the first die corresponds to the fourth contact pad on the second die, and the second contact pad on the first die corresponds to the fifth contact pad on the second die.

**4**. The semiconductor device assembly of claim **2**, wherein the first and second dies are stacked in a shingled configuration.

5. The semiconductor device assembly of claim 2, wherein the substrate contact is electrically coupled to the fourth contact pad by a wirebond between the first and fourth contact pads.

6. The semiconductor device assembly of claim 1, wherein the first circuit is a driver circuit.

7. The semiconductor device assembly of claim 1, wherein the second circuit includes one or more capacitors to provide electrostatic discharge (ESD) protection.

**8**. The semiconductor device assembly of claim **1**, wherein the die is a NAND memory die.

9-13. (canceled)

\* \* \* \*