US 20200395961A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2020/0395961 A1

# (10) Pub. No.: US 2020/0395961 A1 (43) Pub. Date: Dec. 17, 2020

# Perez et al.

## (54) SYSTEM AND METHOD FOR DIVIDING THE CARRIER CENTER FREQUENCY OF AN RF MODULATED SIGNAL BY A NON-INTEGER DIVISOR

- (71) Applicant: Innophase, Inc., San Diego, CA (US)

- (72) Inventors: Roc Berenguer Perez, San Diego, CA (US); Yang Xu, San Diego, CA (US)

- (21) Appl. No.: 16/842,629

- (22) Filed: Apr. 7, 2020

# **Related U.S. Application Data**

(63) Continuation of application No. 16/439,412, filed on Jun. 12, 2019, now Pat. No. 10,651,876.

#### **Publication Classification**

| (51) | Int. Cl.   |           |

|------|------------|-----------|

|      | H04B 1/04  | (2006.01) |

|      | H03L 7/197 | (2006.01) |

|      | H03L 7/099 | (2006.01) |

# (52) U.S. Cl.

CPC ...... H04B 1/04 (2013.01); H03L 7/099 (2013.01); H03L 7/1974 (2013.01)

# (57) **ABSTRACT**

An example method according to some embodiments includes receiving, from a modulator, a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; generating, by an injection-locked ring oscillator (ILRO), a plurality of phases of the phase-modulated carrier output signal at a plurality of outputs of the ILRO; generating a decoupled fractional frequency output signal by sequentially selecting, using a multiplexer, successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases, the decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency; and generating, based on the decoupled fractional frequency output signal, a desired phase-modulated carrier output signal that is decoupled from the modulator, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

FIG. 1

**FIG. 2**

FIG. 3

400

FIG. 4

**FIG. 9**

FIG. 11

## SYSTEM AND METHOD FOR DIVIDING THE CARRIER CENTER FREQUENCY OF AN RF MODULATED SIGNAL BY A NON-INTEGER DIVISOR

#### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This present application is a Continuation of U.S. application Ser. No. 16/439,412, filed Jun. 12, 2019, entitled "SYSTEM AND METHOD FOR DIVIDING THE CAR-RIER CENTER FREQUENCY OF AN RF MODULATED SIGNAL BY A NON-INTEGER DIVISOR," which is hereby incorporated by reference in its entirety.

#### BACKGROUND

**[0002]** Inductors and inductive components suffer from mutual coupling and therefore frequency of oscillators can be disturbed by other nearby electromagnetic fields. This effect is called frequency pulling. As a result, frequency pulling in transmitters (and receivers) may cause such devices to transmit (or receive) signals with altered carrier frequencies. An oscillator or oscillator circuit may generate a sinusoidal signal with a particular resonance frequency and harmonics (or multiples) of that particular resonance frequency. If an oscillator generates a sinusoidal signal with a resonance frequencies may include the frequencies  $2*\omega_0$ ,  $3*\omega_0$ ,  $4*\omega_0$ , and other multiples of  $\omega_0$ .

### SUMMARY

[0003] An example method disclosed herein in accordance with some embodiments may include: receiving, from a modulator, a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; generating, by an injectionlocked ring oscillator (ILRO), a plurality of phases of the phase-modulated carrier output signal at a plurality of outputs of the ILRO; generating a decoupled fractional frequency output signal by sequentially selecting, using a multiplexer, successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases, the decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency; and generating, based on the decoupled fractional frequency output signal, a desired phase-modulated carrier output signal that is decoupled from the modulator, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

**[0004]** According to the example method, in some embodiments, an oscillation frequency of the ILRO may be tuned to be substantially-near the carrier center frequency of the phase-modulated carrier output signal.

**[0005]** According to the example method, in some embodiments, generating the plurality of phases may further include tuning an oscillation frequency of the ILRO to be substantially near the carrier center frequency.

**[0006]** According to the example method, in some embodiments, generating the plurality of phases may further include injecting, by an injection circuit coupled to the ILRO, the phase-modulate carrier output signal into the ILRO.

**[0007]** The example method may further include, in some embodiments, transmitting the desired phase-modulated car-

rier output signal having the generated carrier center frequency equal to the desired carrier center frequency.

**[0008]** According to the example method, in some embodiments, the carrier center frequency of the phase-modulated carrier output signal may be 1.25 times the center frequency of the decoupled fractional frequency output signal.

**[0009]** According to the example method, in some embodiments, receiving the phase-modulated carrier output signal may include receiving phase-modulated carrier signals with phases of 0 degrees and 180 degrees.

**[0010]** According to the example method, in some embodiments, generating, by the ILRO, the plurality of phases of the phase-modulated carrier output signal generates phases of 0, 90, 180, and 270 degrees.

**[0011]** The example method may further include, in some embodiments, aligning the plurality of phases of the phase-modulated carrier output signal into a plurality of pairs of phases.

**[0012]** According to the example method, in some embodiments, generating the desired phase-modulated carrier output signal based on the decoupled fractional frequency output signal may include: dividing by 2 the center frequency of the decoupled fractional frequency output signal.

**[0013]** Further according to the example method, in some embodiments, dividing by 2 the center frequency of the decoupled fractional frequency output signal may include: triggering a divide-by-2 output signal to go high upon a rising edge of the decoupled fractional frequency output signal; and resetting the divide-by-2 output signal to low after an adjustable period of time, wherein a center frequency of the divide-by-2 output signal may be half the center frequency of the decoupled fractional frequency output signal.

**[0014]** According to the example method, in some embodiments, sequentially selecting successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases may include repeating a sequential process that may include: responsive to detecting a rising edge of a current phase of the plurality of phases, selecting a portion of a next phase of the plurality of phases; setting a next portion of the decoupled fractional frequency output signal equal to the selected portion of the next phase; and setting the current phase equal to the next phase.

**[0015]** Further according to the example method, in some embodiments, the sequential process may further include delaying the current phase prior to detecting the rising edge of the current phase.

**[0016]** An example apparatus disclosed herein in accordance with some embodiments may include: a digitallycontrolled oscillator (DCO) circuit configured to output a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; an injection-locked ring oscillator (ILRO) configured to generate a plurality of phases of the phasemodulated carrier output signal at a plurality of outputs of the ILRO; and a fractional frequency division circuit coupled to the plurality of outputs of the ILRO, the fractional frequency division circuit configured to sequentiallyselect, using a multiplexer (MUX), successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases to generate a decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency. [0017] According to the example apparatus, in some

embodiments, the ILRO may be configured such that an oscillation frequency of the ILRO is tuned to be substantially-near the carrier center frequency of the phase-modulated carrier output signal.

**[0018]** The example apparatus may further include, in some embodiments, an injection circuit coupled to the ILRO and to an output of the DCO circuit and configured to inject the phase-modulate carrier output signal into the ILRO.

**[0019]** The example apparatus may further include, in some embodiments, an integer frequency division circuit coupled to the fractional frequency division circuit and configured to generate, based on the decoupled fractional frequency output signal, a desired phase-modulated carrier output signal that is decoupled from the DCO circuit, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

[0020] Further according to the example apparatus, in some embodiments, the integer frequency division circuit may be further configured to generate the desired phasemodulated carrier output signal based on the decoupled fractional frequency output signal by dividing by 2 the center frequency of the decoupled fractional frequency output signal. In some embodiments, the integer frequency division circuit may be further configured to trigger an integer frequency division output signal to go high upon a rising edge of the decoupled fractional frequency output signal. In some embodiments, the integer frequency division circuit may be further configured to reset the integer frequency division output signal to low after an adjustable period of time. In some embodiments, a center frequency of the integer frequency division output signal may be equal to half the center frequency of the fractional frequency output signal.

**[0021]** Further according to the example apparatus, the example apparatus may further include, in some embodiments, an amplifier configured to amplify the desired phase-modulated carrier output signal for transmission.

**[0022]** According to the example apparatus, in some embodiments, the fractional frequency division circuit may include the MUX and multiple delay flip-flops, the multiple delay flip-flops having respective outputs configured to sequentially select the successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases.

**[0023]** According to the example apparatus, in some embodiments, the carrier center frequency of the phase-modulated carrier output signal may be 1.25 times the center frequency of the decoupled fractional frequency output signal.

**[0024]** According to the example apparatus, in some embodiments, the DCO circuit may be configured to output the phase-modulated carrier output signal with phases of 0 degrees and 180 degrees.

**[0025]** According to the example apparatus, in some embodiments, the ILRO may be further configured to generate the phases of 0, 90, 180, and 270 degrees of the phase-modulated carrier output signal.

**[0026]** According to the example apparatus, in some embodiments, the fractional frequency division circuit may

be further configured to align the plurality of phases of the phase-modulated carrier output signal into a plurality of pairs of phases.

**[0027]** According to the example apparatus, in some embodiments, the fractional frequency division circuit may be configured to repeat a sequential process including: responsive to detecting a rising edge of a current phase of the plurality of phases, selecting a portion of a next phase of the plurality of phases; setting a next portion of the decoupled fractional frequency output signal equal to the selected portion of the next phase; and setting the current phase equal to the next phase.

**[0028]** Further according to the example apparatus, the example apparatus may further include, in some embodiments, a delay element coupled to the fractional frequency division circuit and configured to delay the current phase prior to detecting the rising edge of the current phase.

[0029] Another example apparatus disclosed herein in accordance with some embodiments may include: a processor; and a non-transitory computer-readable medium storing instructions that are operative, when executed by the processor, to perform the functions including: receiving, from a modulator, a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; generating, by an injectionlocked ring oscillator (ILRO) a plurality of phases of the phase-modulated carrier output signal at a plurality of outputs of the ILRO; generating a decoupled fractional frequency output signal by sequentially selecting, using a multiplexer, successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases, the decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency; and generating, based on the decoupled fractional frequency output signal, a desired phase modulated carrier output signal that is decoupled from the modulator, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

# BRIEF DESCRIPTION OF THE DRAWINGS

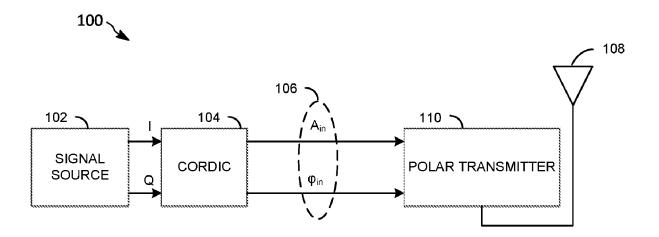

**[0030]** FIG. **1** is a block diagram of an example polar coordinate conversion and polar transmission system in accordance with some embodiments.

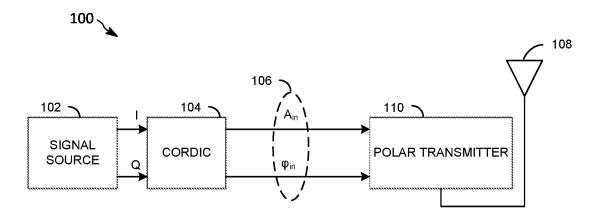

**[0031]** FIG. **2** is a block diagram of an example polar transmitter in accordance with some embodiments.

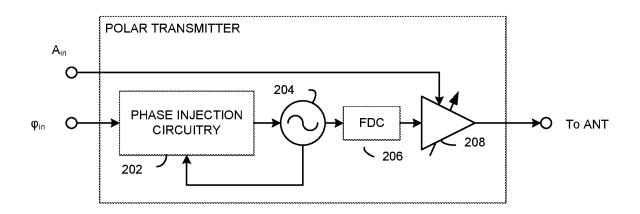

**[0032]** FIG. **3** is a system diagram illustrating an arrangement of components for generating a fractional frequency output signal according to some embodiments.

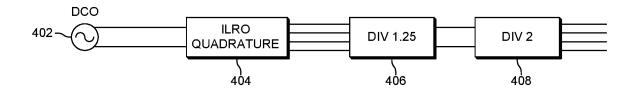

**[0033]** FIG. **4** is a schematic illustration showing an example configuration for modifying a carrier center frequency outputted by a digitally-controlled oscillator (DCO) according to some embodiments.

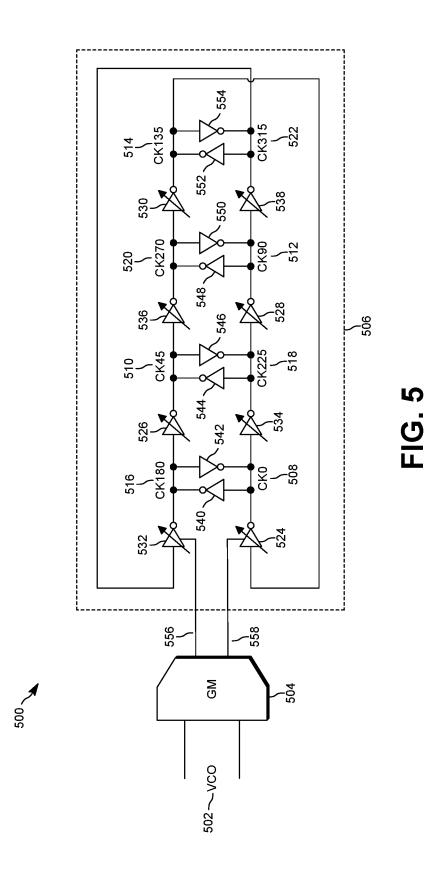

**[0034]** FIG. **5** is a schematic illustration showing an example injection-locked ring oscillator (ILRO) quadrature circuit according to some embodiments.

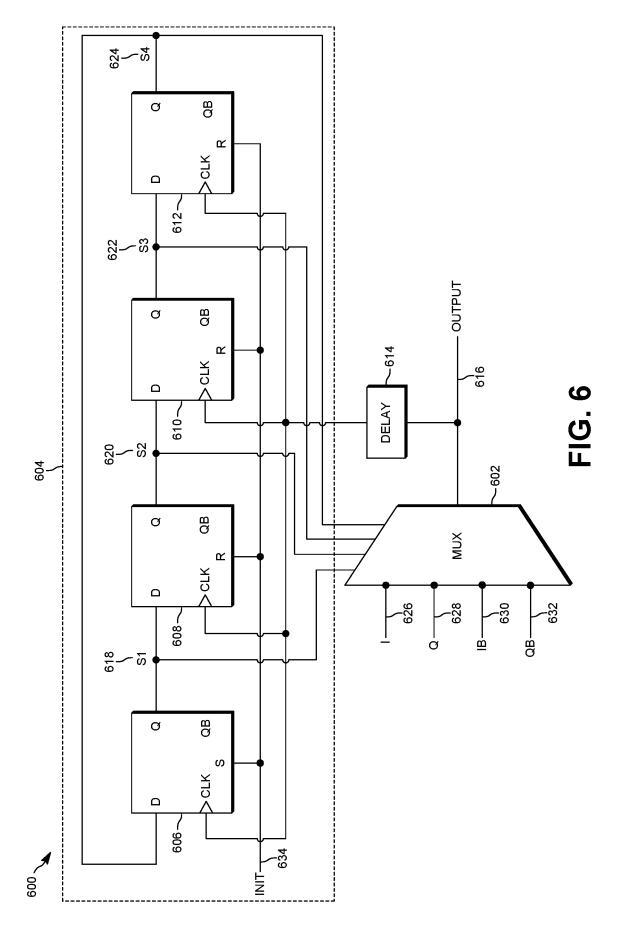

**[0035]** FIG. **6** is a schematic illustration showing an example circuit for generating a fractional frequency output signal according to some embodiments.

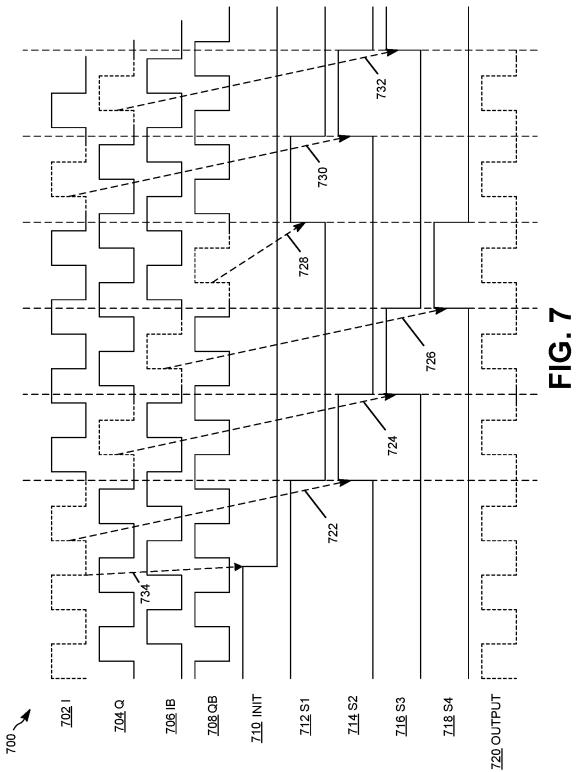

**[0036]** FIG. 7 is a timing diagram showing example relative timing relationships for phase signals and a fractional frequency output signal according to some embodiments.

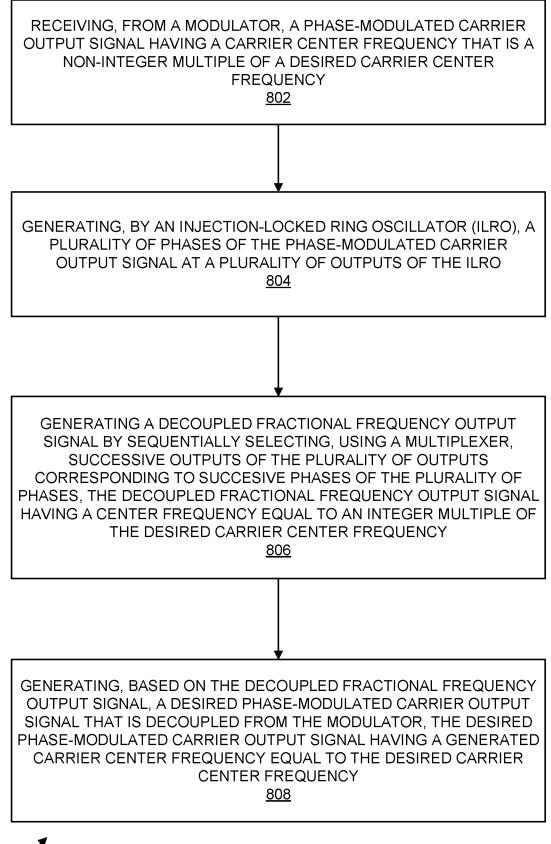

**[0037]** FIG. **8** is a flowchart illustrating an example process for generating a fractional frequency output signal according to some embodiments.

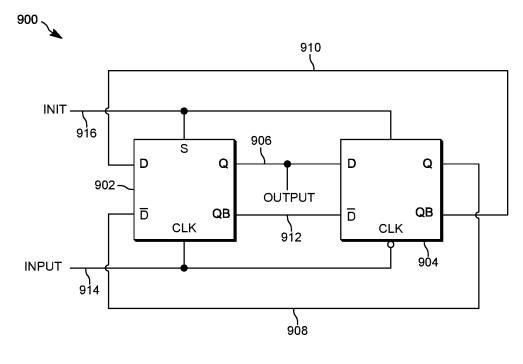

**[0038]** FIG. 9 is a schematic illustration showing an example circuit for dividing a carrier center frequency by 2 according to some embodiments.

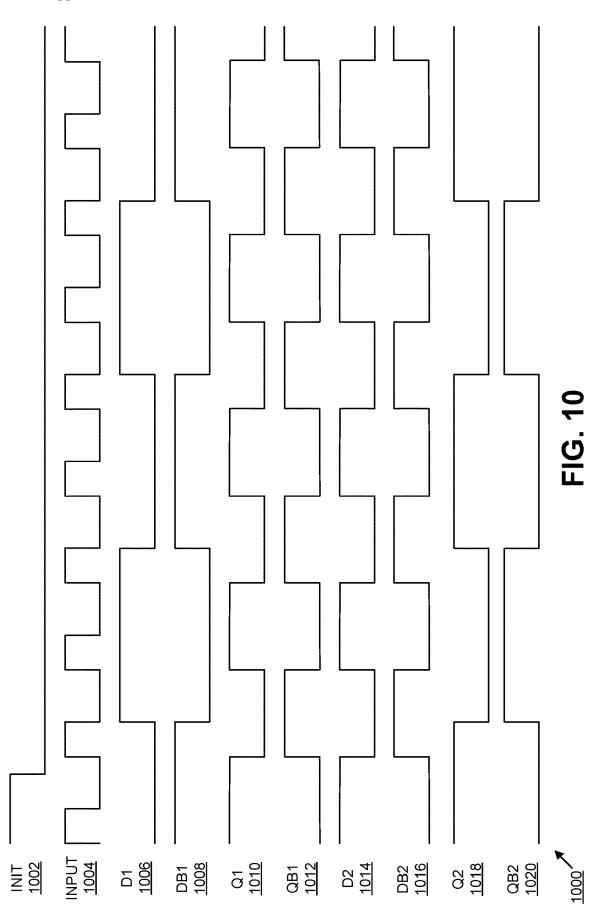

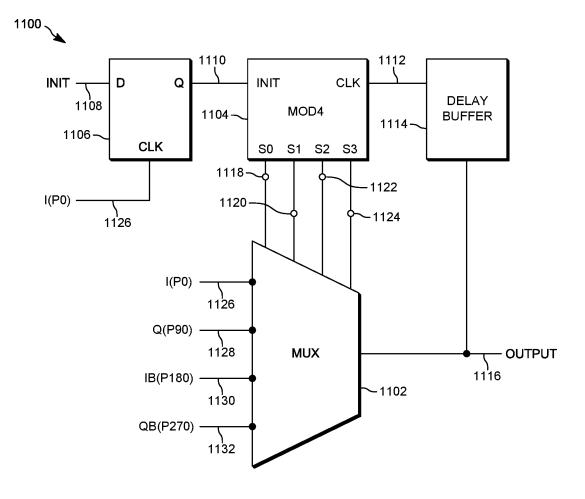

**[0039]** FIG. **10** is a timing diagram showing example relative timing relationships for phase signals and a divideby-2 circuit output signal according to some embodiments. **[0040]** FIG. **11** is a schematic illustration showing an example circuit for generating a fractional frequency output signal according to some embodiments.

**[0041]** The entities, connections, arrangements, and the like that are depicted in—and described in connection with—the various figures are presented by way of example and not by way of limitation. As such, any and all statements or other indications as to what a particular figure "depicts," what a particular element or entity in a particular figure "is" or "has," and any and all similar statements—that may in isolation and out of context be read as absolute and therefore limiting—may only properly be read as being constructively preceded by a clause such as "In at least one embodiment, . . . ." For brevity and clarity of presentation, this implied leading clause is not repeated ad nauseum in the detailed description of the drawings.

## DETAILED DESCRIPTION

**[0042]** In accordance with some embodiments, to reduce frequency pulling, a fractional divider circuit may be used. Systems and methods described herein in accordance with some embodiments may use a fractional divider to reduce coupling between two or more inductive and/or capacitive elements for some embodiments. For example, an amplifier, such as a digital power amplifier, may have inductive elements that become coupled to inductive elements of a modulator circuit, such as a digitally-controlled oscillator circuit described herein.

[0043] FIG. 1 is a block diagram of an example polar coordinate conversion and polar transmission system 100 in accordance with some embodiments. A signal source 102 is provided to generate in-phase (I) and quadrature (Q) values of a signal to be transmitted. Signal source 102 may be any source of I and Q values known to those of skill in the art, such as encoders for frequency modulated or phase-modulated radio-frequency signals, such as signals modulated using phase shift keying (PSK) or quadrature amplitude modulation (QAM). As the term is used in the present disclosure, phase-modulated signals include signals that are modulated in phase (e.g., binary phase-shift keying (BPSK), quadrature phase-shift keying (QPSK), 8-PSK, or 16-PSK) as well as signals that are modulated in both phase and amplitude (e.g., 16-QAM, 64-QAM, or 256-QAM, or multicarrier combinations of such signals, as in Orthogonal Frequency Division Multiplexed (OFDM) signals). Frequency modulated signals include, among others, frequency shift keying (FSK) signals such as binary frequency-shift keying (BFSK) signals, multiple frequency-shift keying (MFSK) signals, and minimum-shift keying (MSK) signals. [0044] The in-phase and quadrature signals from signal source 102 are provided to a coordinate rotation digital computer (CORDIC) logic circuit 104. The CORDIC logic circuit 104 converts the Cartesian I and Q signals to a corresponding polar signal that includes digital amplitude and phase signals. The amplitude signal  $A_{in}$  and the phase signal  $\varphi_{in}$  are provided through a polar signal input 106 to a polar transmitter 110. The polar transmitter 110 generates a phase-and-amplitude modulated radio-frequency (RF) output signal corresponding to the polar signal and transmits the signal at an antenna 108. In some embodiments, the radiofrequency signal, also referred to herein as a modulated carrier signal, has a frequency in the range of 2412 MHz-2484 MHz, although the use of the polar transmitter 110 is not limited to that frequency range. In general, a polar transmitter and/or transceiver in accordance with some of the embodiments disclosed herein may be used at any suitable frequency. Some particular frequency bands and ranges include those for LTE (4G) (e.g., 700 MHz-6 GHz), 5G (e.g., 600 MHz-6 GHz, 24-86 GHz), and any applicable frequency bands for standards such as LTE, GSM, WiMax and WiFi 802.11 standards (e.g., 2.4 GHz, 5 GHz, 900 MHz), although it will be understood that any frequency may be used in accordance with a particular implementation. [0045] The polar transmitter 110 includes power amplifier circuitry (not shown) in FIG. 1 in accordance with some embodiments described herein.

[0046] Some examples and implementations of, e.g., polar transmitter architecture and digital power amplifiers such as may be used, e.g., in the example polar coordinate conversion and polar transmission system 100 of FIG. 1 in accordance with some embodiments are described in greater detail in the following: U.S. patent application Ser. No. 16/241,842, filed Jan. 7, 2019, entitled "SYSTEMS AND METHODS FOR MAXIMIZING POWER EFFICIENCY OF A DIGITAL POWER AMPLIFIER IN A POLAR TRANSMITTER": U.S. Pat. No. 9.391.625, issued on Jul. 12, 2016, entitled "WIDEBAND DIRECT MODULATION WITH TWO-POINT INJECTION IN DIGITAL PHASE LOCKED LOOPS"; U.S. Pat. No. 9,608,648, issued on Mar. 28, 2017, entitled "WIDEBAND DIRECT MODULATION WITH TWO-POINT INJECTION IN DIGITAL PHASE LOCKED LOOPS"; U.S. Pat. No. 9,985,638, issued on May 29, 2018, entitled "WIDEBAND DIRECT MODULATION WITH TWO-POINT INJECTION IN DIGITAL PHASE LOCKED LOOPS"; U.S. Pat. No. 10,148,230, issued Dec. 4, 2018, entitled "ADAPTIVE DIGITAL PREDISTOR-TION FOR POLAR TRANSMITTER," the entirety of each of which is incorporated herein by reference. In still further embodiments, the polar transmitter may include a linearization circuit, examples of which are described in U.S. patent application Ser. No. 16/125,510, filed Sep. 7, 2018, entitled "FREQUENCY CONTROL WORD LINEARIZATION FOR AN OSCILLATOR," the entirety of which is incorporated herein by reference.

**[0047]** In some embodiments, the CORDIC logic circuit **104** may include a signal phase generator and a signal envelope generator (not shown in FIG. 1). According to some embodiments, the baseband in-phase (I) signals and quadrature (Q) signals are received at the CORDIC logic circuit **104** from the signal source **102**, with the signal phase generator configured to process the I and Q signals and perform a rectangular-to-polar conversion to generate the phase signal  $\varphi_{in}$ . In some embodiments, the signal phase generator is a CORDIC calculator. According to some embodiments, the signal envelope generator is configured to process the I and Q signals received at the CORDIC logic circuit **104** and perform a rectangular-to-polar conversion to generate an envelope signal, for example the amplitude signal  $A_{in}$  of FIG. **1**. The envelope signal may correspond to

the envelope of a desired information-modulated transmit signal, such as the envelope formed by the magnitude of the I and Q signals received at the CORDIC logic circuit. The envelope signal may, e.g., be digital in nature and be used to control a digitally switching amplifier within the polar transmitter **110**.

**[0048]** FIG. **2** is a block diagram of an example polar transmitter **200** in accordance with some embodiments. The polar transmitter **200** is an example implementation of the polar transmitter **110** of FIG. **1**.

[0049] In the example of FIG. 2, the polar transmitter 200 receives the amplitude signal  $A_{in}$  and the phase signal  $\varphi_{in}$ output by the CORDIC logic circuit 104 of FIG. 1. According to the example, the phase signal  $\varphi_{in}$  is injected using phase injection circuitry 202 into a phase-locked loop that includes a digitally-controlled oscillator (DCO) 204. The phase injection circuitry 202 compares the phase of the DCO output with the phase identified by the phase signal  $\varphi_{in}$  and controls the DCO such that the phase of the DCO output more closely matches the phase of phase signal  $\varphi_{in}$ . The oscillating signal that is generated by the DCO 204 and that is the DCO output is, e.g., after processing by FDC 206, then amplified by power amplifier circuitry 208, with the gain of the power amplifier circuitry 208 being controlled by the digital amplitude signal  $A_{in}$ . The radio-frequency output of the power amplifier circuitry **208** is provided to an antenna (e.g., antenna 108) for transmission.

**[0050]** In some embodiments, the polar transmitter **110** of FIG. **1** may be further simplified. In another example of a polar transmitter, the incoming phase signal in may be processed at a differentiator with the output of the differentiator then applied to a DCO, e.g., the DCO **204**. The output of the DCO may be applied to a loop filter and then fed back and combined at the input the DCO with the output of the differentiator. The resulting DCO output may be applied to an amplifier (e.g., the power amplifier circuitry **208** of FIG. **2**) to generate an amplified transmit signal (e.g., controlled by the amplitude signal  $A_{in}$ ).

**[0051]** In some embodiments, a frequency division circuit (FDC) **206** (including, e.g., phase generation and frequency division circuitry) may be placed between the DCO **204** and the power amplifier circuitry **208**, as shown in FIG. **2**. The digital oscillator (e.g., DCO **204**) may operate at a higher frequency than the frequency ultimately transmitted at the antenna and may, e.g., undergo a frequency division to, e.g., reduce oscillator pulling caused by the amplifier (e.g., power amplifier circuitry **208**).

**[0052]** In accordance with some embodiments, to reduce frequency pulling, a fractional divider circuit may be used. Systems and methods described herein in accordance with some embodiments may use a fractional divider to reduce coupling between two or more inductive and/or capacitive elements for some embodiments. For example, an amplifier, such as a digital power amplifier, may have inductive elements that become coupled to inductive elements of a modulator circuit, such as a digitally-controlled oscillator circuit described herein.

**[0053]** FIG. **3** is a system diagram **300** illustrating an example arrangement of components for generating a fractional frequency output signal according to some embodiments. For some embodiments, a digitally-controlled oscillator (DCO) circuit **302** (such as DCO **204** of FIG. **2**) may include inputs to receive data to be transmitted and to receive a control signal to control the oscillation frequency

of the DCO circuit. The DCO circuit **302** may include a DCO to generate a phase-modulated carrier output signal having a carrier center frequency.

[0054] A fractional divider circuit (FDC) 304 (such as FDC 206 of FIG. 2) may include a phase generation circuit 306 (such as, e.g., a phase offset circuit) and a fractional frequency division circuit 308. An input of the phase generation circuit 306 of the FDC 304 may be coupled to an output of the DCO circuit 302. The output of the DCO circuit 302 may be used to inject a phase-modulated carrier output signal into the phase generation circuit 306. The phase generation circuit 306 may be configured to generate a set of phase-modulated carrier output signals with different phases. The term phase signals may refer to two or more signals respectively corresponding to two or more phases of a phase-modulated carrier output signal. For example, the phase-modulated carrier output signal may have a phase of 0 degrees, and the phase generation circuit may generate a set of phase signals with phases of 0 degrees, 90 degrees, 180 degrees, and 270 degrees. For some embodiments, the DCO circuit 302 may generate phase-modulated carrier output signals with phases of 0 degrees and 180 degrees, and the phase generation circuit 306 may generate a set of signals with phases of 0 degrees, 90 degrees, 180 degrees, and 270 degrees. With some embodiments, the phase generation circuit may generate signals with phases of 0 degrees, 45 degrees, 90 degrees, 135 degrees, 180 degrees, 225 degrees, 270 degrees, and 315 degrees. In some embodiments, the phase generation circuit 306 may generate other sets of phase signals by using different divider ratios. For some embodiments, the phase generation circuit 306 may include circuits allocated for particular frequency ranges of the phase-modulated carrier output signal. For example, the phase generation circuit 306 may be configured to generate a set of phase signals with a first sub-circuit for a phasemodulated carrier output signal with a carrier center frequency range of 800 MHz to 2.5 GHz and with a second sub-circuit for a phase-modulated carrier output signal with a carrier center frequency range of 2.5 GHz to 6.25 GHz. Some embodiments of the phase generation circuit 306 may use multiple sub-circuits with other frequency ranges.

[0055] An input of the fractional frequency division circuit **308** may be coupled to an output (e.g., one or more outputs) of the phase generation circuit 306. As will be described in more detail, in some embodiments, the fractional frequency division circuit 308 may be configured to select portions of the set of phase signals. In some embodiments, successively selecting later and later phases of a signal, the period of the signal may be extended. Due to the inverse relationship between the period and the frequency of the signal, the frequency decreases with increases in the period, and vice versa, and frequency division is performed. The fractional frequency division circuit 308 may generate a fractional frequency output signal with a center frequency equal to the phase-modulated carrier output signal's carrier center frequency divided by a non-integer divisor. In some embodiments, the fractional frequency division circuit 308 may generate an output signal with a duty cycle modified to correspond to an adjustment of the modulator carrier frequency. For example, the fractional frequency division circuit 308 may receive a set of phase signals with phases of 0, 90, 180, and 270 degrees, respectively. According to the example, each signal in the set of phase signals may have a duty cycle of 50% (such as a square wave with approximately 50% of the time with a voltage above 3.3V and approximately 50% of the time with a voltage below 0.8V). With some embodiments, the fractional frequency division circuit **308** may select portions of the phase signal inputs to generate an output signal with an adjusted duty cycle. For example, if the non-integer divisor is equal to 1.25, the output of the fractional frequency division circuit **308** may have a duty cycle of 40%. Of course, other duty cycles may be used. The output of the fractional frequency division circuit **308** may be generated by sequentially selecting portions of 4 quadrature phases (such as phase signals with phases of 0, 90, 180, and 270 degrees, respectively).

[0056] An input of a power amplifier (such as power amplifier circuitry 208 of FIG. 2), shown as digital power amplifier (DPA) 310 in FIG. 3 may be coupled to an output of the fractional frequency division circuit 308 of the FDC 304. For some embodiments, the DPA 310 may be configured to amplify a fractional frequency output signal. A radio frequency (RF) antenna 312 may be coupled to an output of the DPA 310 and configured to transmit the amplified fractional frequency output signal. For some embodiments, the RF antenna 312 also may be configured to transmit a desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency. Use of a fractional frequency division circuit helps to solve a pulling problem that may arise in some implementations due to, e.g., inductive elements of the DPA 310 coupling with inductive elements of the DCO circuit 302. The fractional frequency division circuit 308 may enable a modulator's phase-modulated carrier output signal to have a carrier frequency that is a non-integer multiple of a desired carrier center frequency, thus mitigating pulling effects. For example, in some embodiments, the desired phase-modulated carrier output signal may be configured to have a desired carrier center frequency that is decoupled from the modulator and the modulator's phase-modulated carrier output signal. This decoupling of carrier frequency (in the sense of the carrier frequencies not being non-harmonic, non-integer multiples of one another) between, e.g., the signal output by the DCO circuit 302 and, e.g., the signal output by the fractional frequency division circuit 308 limits electromagnetic interference between these signals, as well as between the DCO output signal and signals downstream from the fractional frequency division circuit 308, e.g., in this case the desired phase-modulated carrier output signal.

[0057] In some embodiments, an integer frequency division circuit such as a divide-by-N circuit (where N is a positive integer greater than 1) may be included before the DPA 310. In some embodiments, the fractional frequency division circuit 308 may include, e.g., a divide-by-N circuit such as a divide-by-2 (where N=2) circuit. In some embodiments, an integer frequency division circuit (a divide-by-N circuit, such as, e.g., a divide-by-2 circuit, where N=2) may be coupled between (not shown in FIG. 3) the fractional frequency division circuit 308 and the DPA 310. Similarly, the fractional divider circuit (FDC) 304 may include an integer frequency division circuit (a divide-by-N circuit), either as part of the fractional frequency division circuit 308 or coupled to the fractional frequency division circuit 308. In some embodiments, an integer frequency division circuit may be coupled between the FDC 304 and the DPA 310, such that, e.g., the integer frequency division circuit is not part of the FDC 304.

[0058] The present disclosure provides an example apparatus in accordance with some embodiments that includes: a processor; and a non-transitory computer-readable medium storing instructions that are operative, when executed by the processor, to perform functions including: receiving, from a modulator, a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; generating, by an injectionlocked ring oscillator (ILRO), a plurality of phases of the phase-modulated carrier output signal at a plurality of outputs of the ILRO; generating a decoupled fractional frequency output signal by sequentially selecting, using a multiplexer, successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases, the decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency; and generating, based on the decoupled fractional frequency output signal, a desired phase modulated carrier signal that is decoupled from the modulator, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

[0059] FIG. 4 is a schematic illustration showing an example configuration for modifying a carrier center frequency outputted by a digitally-controlled oscillator (DCO) 402 according to some embodiments. For some embodiments, the digitally-controlled oscillator (DCO) 402 may be used to generate a phase-modulated carrier output signal having a modulator carrier center frequency. The circuit 400 shown in FIG. 4 may be used to generate a fractional frequency output signal with a center frequency that is a non-harmonic (e.g., a non-integer multiple) frequency of the modulator carrier center frequency. In some embodiments, a DCO circuit (such as DCO circuit 302 of FIG. 3) may include inputs for receiving data to be transmitted and for receiving a control signal for controlling the DCO 402. The control signal may be generated by a processor, a processorbased circuit, or a component-based circuit for some embodiments. The DCO 402 (which may be part of a DCO circuit) may generate, e.g., two or more phase signals of the phase-modulated carrier output signal. For example, the DCO circuit may be configured to generate a pair of digitally-controlled oscillator signals having respective phases of 0 degrees and 180 degrees. The output of the DCO 402 may be connected to the inputs of an injection-locked ring oscillator (ILRO) 404 such that the phase signals of the phase-modulated carrier output signal are received by the ILRO 404.

**[0060]** For some embodiments, the DCO **402** may generate phase-modulated carrier output signals with phases of 0 degrees and 180 degrees, respectively, and a 50% duty cycle. In other embodiments, the DCO **402** may be used to generate phase-modulated carrier output signals with phases of 0 degrees and 180 degrees, respectively, and a 25% duty cycle.

[0061] For some embodiments, the ILRO 404 may be a sub-circuit of the phase generation circuit 306 shown in FIG. 3. The ILRO 404 may be configured to tune (or lock) the oscillation frequency of the ILRO to be substantially-near the carrier center frequency of the DCO 402 (or the phase-modulated carrier output signal). For some embodiments, the ILRO 404 be used to generate quadrature phase signals. For example, the ILRO 404 may output signals with phases of 0, 90, 180, and 270 degrees.

**[0062]** In some embodiments, the ILRO **404** and/or the divider stages **406**, **408** may be selectively disabled and, e.g., the output signals from the DCO may be provided directly to an output, e.g., to a DPA such as DPA **310** of FIG. **3**.

[0063] In some embodiments, each set of phase signals that are outputted by the ILRO 404 may be received by a non-integer fractional divider such as divide-by-1.25 circuit 406. Some embodiments of the divide-by-1.25 circuit 406 may be used to divide a carrier frequency of an input signal by a non-integer divisor equal to 1.25. For some embodiments, the divide-by-1.25 circuit 406 may output two phases of a fractional frequency output signal. The carrier frequency of the two phase signal outputs (or fractional frequency output signal(s)) may be divided by 2 by a divideby-2 circuit 408 to generate 4 phase outputs. Some embodiments of the fractional frequency division circuit 308 of FIG. 3 may include the divide-by-2 circuit 408 of FIG. 4. For some embodiments, the divide-by-2 circuit 408 may be coupled between the divide-by-1.25 circuit 406 and an input to a digital power amplifier (DPA) (shown, for example, as DPA 310 in FIG. 3). For some embodiments, the phase generation circuit 306 of FIG. 3 may correspond to the ILRO 404 of FIG. 4. In some embodiments, the fractional frequency division circuit 308 of FIG. 3 may correspond to not only the divide-by-1.25 circuit 406 but also the divide-by-2 circuit 408 of FIG. 4. In some embodiments, the fractional frequency division circuit 308 of FIG. 3 may not include an integer frequency division circuit such as the divide-by-2 circuit 408 of FIG. 4. For some embodiments, the divideby-1.25 circuit 406 may include a multiplexer to sequentially select successive phases of a phase-modulated carrier signal.

**[0064]** In operation, with some embodiments, the DCO may operate at  $2.5*f_0$ , (e.g., 1.25\*2=2.5) where  $f_0$  is the carrier frequency of an RF transmitted signal. In some embodiments, if  $f_0$  is between 1.6 GHz and 2.0 GHz, the DCO may operate at  $2.5*f_0$ , which correlates to a DCO frequency range of 4 GHz to 5 GHz.

**[0065]** Using one frequency range as a non-limiting illustrative example, in some embodiments, to transmit an RF signal in the mid-band (MB) and industrial, scientific, and medical (ISM) frequency ranges (1.7 GHz-2.5 GHz), the frequency of the DCO **402** may be set to a frequency between 4.25 GHz and 6.25 GHz, e.g.,  $2.5*f_0$ , (e.g., 1.25\*2=2.5). For example, at the lower end of the MB and ISM frequency range (1.7 GHz), if the DCO **402** is set to 4.25 GHz, the ILRO **404** may generate an input to the divide-by-1.25 circuit **406** with a carrier frequency of 4.25 GHz. The divide-by-1.25 circuit **406** may generate an input to the divide-by-2 circuit **408** with a carrier frequency of 3.4 GHz. The divide-by-2 circuit **408** may generate an output signal with a carrier frequency of 1.7 GHz.

**[0066]** Likewise, for the upper end of the MB and ISM frequency range (2.5 GHz), if the frequency of the DCO **402** is set to 6.25 GHz, the ILRO **404** may generate an input to the divide-by-1.25 circuit **406** with a carrier frequency of 6.25 GHz. The divide-by-1.25 circuit **406** may generate an input to the divide-by-2 circuit **408** with a carrier frequency of 5.0 GHz. The divide-by-2 circuit **408** may generate an output signal with a carrier frequency of 2.5 GHz. These are merely example frequencies and frequency ranges and other frequencies and ranges may be used.

**[0067]** It will be understood that the particular divider circuit block and divisor used are merely examples, and that

other values (e.g., non-integer divisor(s) other than or in addition to 1.25, integer divisor(s) other than or in addition to 2) may be used in other implementations in accordance with some embodiments.

[0068] FIG. 5 is a schematic illustration 500 showing an example injection-locked ring oscillator (ILRO) quadrature circuit according to some embodiments. For some embodiments, one or more voltage-controlled oscillator (VCO) signals 502 may be inputted into a transconductance  $(g_m)$ signal conditioning circuit 504, or transconductance amplifier 504. The circuit 504 serves to inject an output signal from the VCO or DCO (e.g. DCO 402 of FIG. 4 or DCO circuit 302 of FIG. 3) into the ILRO 506 as a pair of output signals 556, 558. Some embodiments of the transconductance  $(g_m)$  signal conditioning circuit 504 may convert the VCO voltage signal pair 502 into a voltage and current signal or a current signal (e.g., as output signals 556, 558). The VCO signal pair 502 may be a phase signal pair with one signal having, for example, a phase of 0 degrees and the other signal having a phase of 180 degrees. In some embodiments, complementary phase pair signals 556, 558 enter the example ILRO quadrature circuit 506 at dedicated signal inputs to respective adjustable delay inverters 532, 524. A pair of inverter outputs CK0 and CK180 (508, 516) are connected with inverter pairs 540, 542. If the CK0 signal 508 switches state, the inverter pairs 540, 542 may cause the CK180 signal 516 to switch state and vice versa. A similar operation occurs for a set of adjustable delay inverter outputs CK45 (510), CK90 (512), CK135 (514), CK225 (518), CK270 (520), CK315 (522) and a corresponding set of respective inverter pairs 544, 546, 548, 550, 552, 554. The ILRO 506 as shown in FIG. 5 is arranged so that one ILRO feedback connects between the CK315 adjustable delay inverter output 522 to the opposite side adjustable delay inverter 524. Likewise, a second ILRO feedback connects between the CK135 adjustable delay inverter output 514 to the opposite side adjustable delay inverter 532. In some embodiments, there may be no "cross" feedback of inverter outputs as shown in the example of FIG. 5. For example, in some embodiments, rather than a ring oscillator (e.g., implemented as an ILRO) with an even number of inverter stages (here N=4 adjustable delay inverters in each path), a ring oscillator (e.g., implemented as an ILRO) with an odd number of inverters (e.g., N=3 in each path) may be used, in which case the signal may generally be fed back directly to the first inverter stage in the path of inverter stages.

[0069] With some embodiments, generating a set of phase signals may include generating, from the pair of voltagecontrolled oscillator signals 502, the set of phase signal pairs 508, 510, 512, 514, 516, 518, 520, 522. The set of phase signal pairs may be generated by a ring oscillator, such as the ILRO 506, as shown in FIG. 5. Although a VCO signal pair 502 is described in FIG. 5 as an example of, e.g., a digitally-controlled oscillator (DCO) signal pair, in some embodiments an ICO (current controlled oscillator) signal pair may be used. The phase generation circuit 306 of FIG. 3 may include an ILRO, such as the one shown in FIG. 5. A phase generation circuit (such as the ILRO 506 of FIG. 5) may be configured to generate, from the pair of voltagecontrolled oscillator signals 502 (e.g., as output signals 556, 558 from circuit 504), the set of phase signal pairs 508, 510, 512, 514, 516, 518, 520, 522, and elements (such as adjustable-delay inverters 524, 526, 528, 530, 532, 534, 536, 538) of the phase circuit generating the set of phase signal pairs

508, 510, 512, 514, 516, 518, 520, 522 may be arranged in a ring oscillator configuration. For some embodiments, elements (such as adjustable-delay inverters 524, 526, 528, 530, 532, 534, 536, 538) generating a set of phase signal pairs may be separated by inverter pairs (such as inverter pairs 540, 542, 544, 546, 548, 550, 552, 554 of FIG. 5). Such inverter pairs 540, 542, 544, 546, 548, 550, 552, 554 may be used to align a plurality of phases (such as the set of adjustable delay inverter outputs CK0 (508), CK45 (510), CK90 (512), CK135 (514), CK180 (516), CK225 (518), CK270 (520), and CK315 (522)) of a phase-modulated carrier output signal. It will be understood that these are merely examples and other implementations are possible in accordance with some embodiments, and that in some cases merely a subset of the phase signal pairs that may be generated in an example implementation of a phase generation circuit (including, e.g., an ILRO circuit) may be utilized in subsequent processing, such as a non-integer fractional divider such as divide-by-1.25 circuit 406 of FIG. 4.

[0070] For some embodiments, an oscillation frequency of the ILRO 506 may be tuned to be substantially-near a carrier center frequency of a phase-modulated carrier output signal with the carrier center frequency. In some embodiments, the ILRO 506 may be coupled to the output of a DCO circuit, a VCO circuit, or the transconductance  $(g_m)$  signal conditioning circuit 504. An injection circuit (such as the transconductance  $(g_m)$  signal conditioning circuit 504) may inject the phase-modulated signal into the ILRO to generate a plurality of phases of the phase-modulated signal (such as the phase signals CK0 (508), CK90 (512), CK180 (516), and CK270 (520)) in some embodiments. Other sets of phase signals may be generated, such as CK0 (508), CK45 (510), CK90 (512), CK135 (514), CK180 (516), CK225 (518), CK270 (520), and CK315 (522). For some embodiments, the transconductance  $(g_m)$  signal conditioning circuit 504 may inject a phase-modulated signal with phases of 0 degrees and 180 degrees into the ILRO 506.

**[0071]** FIGS. **6** and **7** are complementary figures that will be described together. FIG. **6** is a schematic illustration showing an example circuit **600** for generating a fractional frequency output signal according to some embodiments. FIG. **7** is a timing diagram **700** showing example relative timing relationships for phase input signals and a fractional frequency output signal according to some embodiments. In some embodiments, the circuit shown in FIG. **6** may correspond to, and serve as an example implementation of, the divide-by-1.25 circuit **406** of FIG. **4**.

[0072] For some embodiments, a multiplexer (MUX), such as a MUX 602 of FIG. 6, may be used to sequentially select successive phases of a plurality of phases of a phasemodulated signal (such as phase signals I 626, Q 628, IB 630, and QB 632) to provide a fractional frequency output signal 616 having a center frequency equal to the carrier center frequency divided by a (here non-integer) carrier frequency divisor. For example, the carrier frequency divisor may be 1.25 in some embodiments. In some embodiments, the carrier frequency divisor may be equal to a phase skip count divided by a phase count. For instance, the phase count may be 4, such as shown in FIG. 6 with four phase signals 626, 628, 630, 632 injected into the MUX 602. The phase skip count may be 5 to generate a fractional frequency output signal with a center frequency equal to the carrier center frequency divided by 5/4 or 1.25.

[0073] Some embodiments of the fractional frequency division circuit 308 of FIG. 3 may be as shown in FIG. 6, with the phase generation circuit 306 of FIG. 3 outputting a set of phase signals of the modulated carrier signal, such as signals with phase offsets of 0, 90, 180, and 270 degrees. The set of phase signals 626, 628, 630, 632 (which may correspond to the signals with phase offsets of 0, 90 180, and 270 degrees) may be received by the multiplexer (MUX) 602. Select signals 618, 620, 622, 624 for the MUX 602 are connected to outputs of a set of D-Flip-Flops 606, 608, 610, 612. The D-Flip-Flops 606, 608, 610, 612 may be arranged in a ring configuration 604 that enable a series of states to be repeated and cycled through. In some embodiments, the multiplexer selection ring oscillator 604 may be coupled to the multiplexer 602. The phase signals 626, 628, 630, 632, which are labeled as I, Q, IB, and QB respectively, may correspond to timing signals I 702, Q 704, IB 706, and QB 708 of FIG. 7. Select signals S1 618, S2 620, S3 622, and S4 624 of the MUX 602 may correspond to timing diagram signals S1 712, S2 714, S3 716, and S4 718 of FIG. 7. The fractional frequency output signal 616 may correspond to a timing diagram output signal 720 of FIG. 7. Also, the initialization signal 634 of FIG. 6 may correspond to initialization signal 710 of FIG. 7. A delay element 614 may be inserted between the fractional frequency output signal 616 and the clock inputs to the D-Flip-Flops 606, 608, 610, 612.

[0074] For some embodiments, the initialization signal 634 may be configured to hold the first D-Flip-Flop 606 in a set state (which may occur by setting an "S" pin in a high state) and the second, third and fourth D-Flip-Flops 608, 610, 612 in a reset state (which may occur by setting an "R" pin in a high state). As a result, the Q pin output signals (S1 618, S2 620, S3 622, and S4 624) may be equal to 1, 0, 0, 0, respectively, while the initialization signal 634 is high. The left side of FIG. 7 shows the initialization signal 710 in a high (or "1") state while the S1 712 is high and the S2 714, S3 716, and S4 718 are low. Initializing the select signals S1 618, S2 620, S3 622, S4 624 to the 1, 0, 0, 0 state causes the MUX 602 to select the I signal 626 for the fractional frequency output signal 616. FIG. 7 shows the output signal 720 equal to the I signal 702 while the initialization signal 710 is high. To aid in understanding the timing diagram of FIG. 7, the source of the MUX output signal 720 is shown with dotted lines for the corresponding portion of the I 702, Q 704, IB 706, and QB 708 signals.

[0075] As shown in FIG. 7, the initialization signal 710 may be equal to a high (or "1") state long enough to enable the D-Flip-Flops 606, 608, 610, 612 to initialize the outputs (S1 618, S2 620, S3 622, and S4 624) to the 1, 0, 0, 0 state. The fractional frequency output signal 616 may be connected to the D-Flip-Flop clock signals via the delay element 614. With the initialization signal 634, 710 high, the MUX 602 initializes to select the I signal 626, 702 as the fractional frequency output signal 616, 720. As the initialization signal 634, 710 first goes low, the D signal input (which is connected to the S4 signal 624) of the first D-Flip-Flop 606 is equal to 0 while the Q signal output (which is connected to the S1 signal 618) is equal to 1. Hence, the first D-Flip-Flop 606 waits for the clock signal to go high before changing the state of the corresponding Q signal output 618. For some embodiments, the D-Flip-Flop clock signals may be delayed versions of the fractional frequency output signal 616, 720. FIG. 7 shows a delay between the output signal 720 going high and the S1 712, S2 714, S3 716, and S4 718 signals changing states. The dashed arrows of FIG. 7 indicate the point at which the applicable MUX input signal (which is equal to the output signal 720 at those points in time) goes high and eventually leads the point at which the MUX select signals S1 712, S2 714, S3 716, and S4 718 signals change states.

[0076] For example, the I signal 626, 702 may be a 50% duty cycle signal that is one of the inputs to the MUX 602. The I signal 626, 702 may correspond to a modulator input signal with a phase of 0 degrees. The Q 628, 704, IB 630, 706, and QB 632, 708 signals may correspond to phases of 90, 180, and 270 degrees, respectively. With the I signal 626, 702 equal to a 50% duty signal that corresponds to a 0 degree phase, the Q signal 628, 704 may correspond to a 90 degree phase and may be a quarter cycle delayed version of the I signal 626, 702. Likewise, the IB signal 630, 706 may correspond to a 180 degree phase and may be a half cycle delayed version of the I signal 626, 702. The QB signal 632, 708 may correspond to a 270 degree phase and may be a three quarters cycle delayed version of the I signal 626, 702 (or a half cycle delayed version of the Q signal 628, 704). The changes in the MUX select signals S1 (618, 712), S2 (620, 714), S3 (622, 716), and S4 (624, 718) cause changes in the source of the MUX output signal 720. For MUX input signals that are quarter cycle delayed versions of each other, changing the MUX select signals S1 (618, 712), S2 (620, 714), S3 (622, 716), and S4 (624, 718) may cause the MUX output signal 720 to insert quarter cycle delays. For MUX input signals I (626, 702), Q (628, 704), IB (630, 706), and QB (632, 708) with a 50% duty cycle and quarter cycle delays between each signal, the fractional frequency output signal 616, 720 may have a 40% duty cycle as shown in FIG. 7. In some embodiments, receiving a 50% duty cycle input signal and outputting a 40% duty cycle output signal may correspond to dividing a phase-modulated carrier output signal's carrier center frequency by 1.25. For some embodiments, the MUX input signals I (626, 702), Q (628, 704), IB (630, 706), and QB (632, 708) may correspond to the 4 phase signals that are inputs to the divide-by-1.25 circuit 406 of FIG. 4.

[0077] For some embodiments, selecting portions of the set of phase signals 626, 702, 628, 704, 630, 706, 632, 708 may be a repeating process for generating a series of signals that includes: selecting a first phase signal 626, 702 as a first portion of the fractional frequency output signal 616, 720; responsive to detecting a rising edge of the first phase signal 626, 702, selecting a second phase signal 628, 704 as a second portion of the fractional frequency output signal 616, 720; responsive to detecting a rising edge of the second phase signal 628, 704, selecting a third phase signal 630, 706 as a third portion of the fractional frequency output signal 616, 720; responsive to detecting a rising edge of the third phase signal 630, 706, selecting a fourth phase signal 632, 708 as a fourth portion of the fractional frequency output signal 616, 720; and responsive to detecting a rising edge of the fourth phase signal 632, 708, repeating the process for generating the series of signals. With some embodiments, a fractional frequency division circuit (such as the circuit shown in FIG. 6) may be configured to perform a repeating process for generating the series of phase signals.

**[0078]** With some embodiments, sequentially selecting successive phases of the plurality of phases (of a phase-modulated carrier output signal) may include repeating a sequential process of responsively detecting a rising edge of

a current phase signal (such as a rising edge of the I signal 702) and selecting a next phase signal (such as shown by dashed arrows 722, 724, 726, 728, 730, 732 of FIG. 7 for successive selections) for a next portion of the fractional frequency output signal. For example, the rising edge of the I signal 702 may trigger a delayed selection of the next phase signal (such as the Q signal 704). The next phase signal may become the current phase signal upon selection. For example, the falling edge of the S1 712 signal and corresponding rising edge of the S2 714 signal may cause the output signal 720 to switch sources from the I signal 702 to the Q signal 704, which are highlighted by dotted signals in FIG. 7. For some embodiments, the current phase signal may be delayed prior to detecting the rising edge of the current phase signals. For example, the delay element 614 may be located between the fractional frequency output signal 616 (which may be equal to the current phase signal) and the clock input pins of the D flip-flops 606, 608, 610, 612 that may be used to detect rising edges.

[0079] Some embodiments for selecting portions of the set of phase signals 626, 702, 628, 704, 630, 706, 632, and 708 may include using the multiplexer selection ring oscillator 604 and may include initializing each element (or a set of states) in the multiplexer selection ring oscillator 604 and indicating a completion of initialization of the multiplexer selection ring oscillator 604 using a state change of the modulator input signal (such as the low to high transition of the I signal 702 triggering 734 the initialization line 710 to go low).

[0080] FIG. 8 is a flowchart 800 illustrating an example process for generating a fractional frequency output signal according to some embodiments. Example systems and methods may implement an example process in accordance with some embodiments, where the example process may include: receiving 802, from a modulator, a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; generating 804, by an injection-locked ring oscillator (ILRO), a plurality of phases of the phase-modulated carrier output signal at a plurality of outputs of the ILRO; generating 806 a decoupled fractional frequency output signal by sequentially selecting, using a multiplexer (MUX), successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases, the decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency; and generating 808, based on the decoupled fractional frequency output signal, a desired phase-modulated carrier output signal that is decoupled from the modulator, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

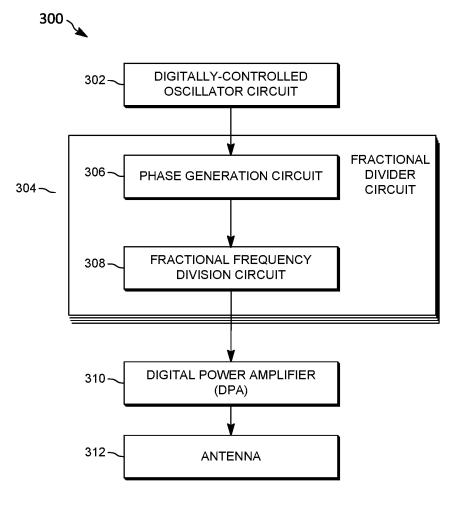

**[0081]** FIGS. 9 and 10 are complementary figures that will be described together. FIG. 9 is a schematic illustration 900 showing an example circuit for dividing a carrier center frequency by 2 according to some embodiments. FIG. 10 is a timing diagram 1000 showing example relative timing relationships for phase signals and a divide-by-2 circuit output signal according to some embodiments. In some embodiments, the circuit shown in FIG. 9 may correspond to, and serve as an example implementation of, the divide-by-2 circuit 408 of FIG. 4.

**[0082]** For some embodiments, an initialization signal **916** of FIG. **9** may correspond to an initialization signal **1002** of

FIG. 10. An input signal 914 of FIG. 9 may correspond to an input signal 1004 of FIG. 10. A set of D 910, DB 908, Q 906, QB 912, and CLK 914 signals of first D-Flip-Flop 902 of FIG. 9 may correspond to a set of D1 1006, DB1 1008, Q1 1010, QB1 1012, and INPUT 1004 signals of FIG. 10. The set of D 906, DB 912, Q 908, QB 910, and CLK 914 signals of second D-Flip-Flop 904 of FIG. 9 may correspond to a set of D2 1014, DB2 1016, Q2 1018, QB2 1020, and INPUT 1004 signals of FIG. 10.

[0083] The initialization signal 1002 of FIG. 10 may be equal to a high (or "1") state to initialize the Q1 1010 and the Q2 1018 signals to a high state, which may initialize the first D-Flip-Flop's Q signal 906 (Q1 1010) and the second D-Flip-Flop's Q signal 908 (Q2 1018) to a high state. With the falling edge of the initialization signal 916, 1002, the first and second D-Flip-Flops 902, 904 trigger Q signal output state changes upon rising and falling edges, respectively, of the INPUT signal 914, 1004.

[0084] A series of states for the Q1 1010, 906 and Q2 1018, 908 output signals may repeat for some embodiments. Upon the rising edge of the INPUT signal with the INIT signal 1002 equal to a low state, the Q1 1010, 906 signal changes from high to low to match D1 1006, 910. Upon the next falling edge of the INPUT signal 1004, 914, the Q2 signal 1018, 908 changes from high to low to match the D2 signal 1014, 906. Upon the next rising edge of the INPUT signal 1004, 914, the Q1 signal 1010, 906 changes from low to high to match the D1 signal 1006, 910. The next falling edge of the INPUT signal 1004, 914 causes the Q2 signal 1018, 908 to change from low to high to match the D2 signal 1014, 906. With some embodiments, the input signal 914, 1004 with a 40% duty cycle may injected into the divideby-2 circuit 900, and the output signal (Q1) 906, 1010 may be generated with a 50% duty cycle and a carrier center frequency that is half the carrier center frequency of the input signal 914, 1004, such as the example shown in FIG. 10.

**[0085]** FIG. **11** is a schematic illustration showing an example circuit for generating a fractional frequency output signal according to some embodiments. In some embodiments, the circuit shown in FIG. **11** may correspond to the divide-by-1.25 circuit **406** of FIG. **4**.

[0086] Some embodiments of the fractional frequency division circuit 308 of FIG. 3 may be as shown in the circuit 1100 of FIG. 11. A set of phase signals 1126, 1128, 1130, 1132 may be received by a multiplexer (MUX) 1102. Select signals 1118, 1120, 1122, 1124 for the MUX 1102 are connected to a set of outputs S0, S1, S2, S3 of a modulo 4 (MOD4) counter 1104. The MOD4 counter may operate such that a series of states are repeated for the S0, S1, S2, S3 outputs. The phase signals 1126, 1128, 1130, 1132, which are labeled as I, Q, IB, and QB respectively, may correspond to the timing signals I 702, Q 704, IB 706, and QB 708 of FIG. 7. The select signals S0 1118, S1 1120, S2 1122, and S3 1124 of the MUX 1102 may correspond to timing diagram signals S1 712, S2 714, S3 716, and S4 718 of FIG. 7. An output signal 1116 of the MUX 1102 may correspond to timing diagram output signal 720 of FIG. 7. Also, the initialization signal 1108 of FIG. 11 may correspond to initialization signal 710 of FIG. 7. A delay element 1114 may be inserted between the MUX output 1116 and a clock input 1112 to the MOD4 counter 1104.

[0087] For some embodiments, an initialization signal 1108 may be injected into a D-Flip-Flop 1106. The D-Flip-

Flop 1106 outputs a Q signal 1110, which may be connected to an initialization pin of the MOD4 counter 1104 to initialize the MOD4 counter 1104 to the counter output signals (S0 1118, S1 1120, S2 1122, and S3 1124) equal to 1, 0, 0, 0, respectively, while the initialization signal 1108 is high. Initializing the select signals S0 1118, S1 1120, S2 1122, S3 1124 equal to 1000 may cause the MUX 1102 to select the I (P0) signal 1126 for the MUX output signal 1116. [0088] As shown in FIG. 7, the initialization signal 710 (which may correspond to the D-flip-flop's initialization signal 1108 for some embodiments) may be equal to a high (or "1") state long enough to enable the MOD4 counter 1104 of FIG. 11 to initialize the outputs (S0 1118, S1 1120, S2 1122, and S3 1124) to the 1, 0, 0, 0 state. The MUX output 1116 may be connected to the MOD4 counter's clock signal 1112 via the delay element 1114. With the initialization signal 1108, 710 high, the MUX 1102 initializes to select the I signal (P0) 1126, 702 as the output signal 1116, 720. For some embodiments, the MOD4 counter's clock signal 1112 is a delayed version of the MUX output signal 1116. Hence, each rising edge of the MUX output signal 1116 may cause a delayed rising edge of the MOD4 counter clock signal 1112. For example, the delay buffer 1114 may cause a quarter cycle delay in a rising edge of the MUX output signal 1116 and the respective rising edge of the MOD4 counter's clock signal 1112.

[0089] For example, the I signal 1126, 702 may be a 50% duty cycle signal that is one of the inputs to the MUX 1102. The I signal 1126, 702 may correspond to a modulator input signal with a phase of 0 degrees. The Q 1128, 704, IB 1130, 706, and QB 1132, 708 signals may correspond to phases of 90, 180, and 270 degrees, respectively. With the I signal 1126, 702 equal to a 50% duty signal that corresponds to a 0 degree phase, the Q signal 1128, 704 may correspond to a 90 degree phase and may be a quarter cycle delayed version of the I signal 1126, 702. Likewise, the IB signal 1130, 706 may correspond to a 180 degree phase and may be a half cycle delayed version of the I signal 1126, 702. The QB signal 1132, 708 may correspond to a 270 degree phase and may be a three quarters cycle delayed version of the I signal 1126, 702. The changes in the MUX select signals S0 (1118), S1 (1120), S2 (1122), and S3 (1124) cause changes in the source of the MUX output signal 1116. For the MUX input signals I (1126, 702), Q (1128, 704), IB (1130, 706), and QB (1132, 708) with a 50% duty cycle and quarter cycle delays between each signal, the MUX output signal 1116, 720 may have a 40% duty cycle as shown in FIG. 7. Receiving a 50%duty cycle input signal and outputting a 40% duty cycle output signal may correspond for some embodiments to dividing a phase-modulated carrier output signal's carrier center frequency by 1.25. For some embodiments, the MUX input signals I (1126, 702), Q (1128, 704), IB (1130, 706), and QB (1132, 708) may correspond to the 4 phase signals that are inputs to the divide-by-1.25 circuit 406 of FIG. 4. [0090] An example method disclosed herein in accordance with some embodiments may include: receiving, from a modulator, a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; generating, by an injectionlocked ring oscillator (ILRO), a plurality of phases of the phase-modulated carrier output signal at a plurality of outputs of the ILRO; generating a decoupled fractional frequency output signal by sequentially selecting, using a multiplexer, successive outputs of the plurality of outputs

corresponding to successive phases of the plurality of phases, the decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency; and generating, based on the decoupled fractional frequency output signal, a desired phase-modulated carrier output signal that is decoupled from the modulator, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

**[0091]** According to the example method, in some embodiments, an oscillation frequency of the ILRO may be tuned to be substantially-near the carrier center frequency of the phase-modulated carrier output signal.

**[0092]** According to the example method, in some embodiments, generating the plurality of phases may further include tuning an oscillation frequency of the ILRO to be substantially near the carrier center frequency.

**[0093]** According to the example method, in some embodiments, generating the plurality of phases may further include injecting, by an injection circuit coupled to the ILRO, the phase-modulate carrier output signal into the ILRO.

**[0094]** The example method may further include, in some embodiments, transmitting the desired phase-modulated carrier output signal having the generated carrier center frequency equal to the desired carrier center frequency.

**[0095]** According to the example method, in some embodiments, the carrier center frequency of the phase-modulated carrier output signal may be 1.25 times the center frequency of the decoupled fractional frequency output signal.

**[0096]** According to the example method, in some embodiments, receiving the phase-modulated carrier output signal may include receiving phase-modulated carrier signals with phases of 0 degrees and 180 degrees.

**[0097]** According to the example method, in some embodiments, generating, by the ILRO, the plurality of phases of the phase-modulated carrier output signal generates phases of 0, 90, 180, and 270 degrees.

**[0098]** The example method may further include, in some embodiments, aligning the plurality of phases of the phase-modulated carrier output signal into a plurality of pairs of phases.

**[0099]** According to the example method, in some embodiments, generating the desired phase-modulated carrier output signal based on the decoupled fractional frequency output signal may include: dividing by 2 the center frequency of the decoupled fractional frequency output signal.

**[0100]** Further according to the example method, in some embodiments, dividing by 2 the center frequency of the decoupled fractional frequency output signal may include: triggering a divide-by-2 output signal to go high upon a rising edge of the decoupled fractional frequency output signal; and resetting the divide-by-2 output signal to low after an adjustable period of time, wherein a center frequency of the divide-by-2 output signal may be half the center frequency of the decoupled fractional frequency output signal.

**[0101]** According to the example method, in some embodiments, sequentially selecting successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases may include repeating a sequential process that may include: responsive to detecting a rising

edge of a current phase of the plurality of phases, selecting a portion of a next phase of the plurality of phases; setting a next portion of the decoupled fractional frequency output signal equal to the selected portion of the next phase; and setting the current phase equal to the next phase.

**[0102]** Further according to the example method, in some embodiments, the sequential process may further include delaying the current phase prior to detecting the rising edge of the current phase.

[0103] An example apparatus disclosed herein in accordance with some embodiments may include: a digitallycontrolled oscillator (DCO) circuit configured to output a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; an injection-locked ring oscillator (ILRO) configured to generate a plurality of phases of the phasemodulated carrier output signal at a plurality of outputs of the ILRO; and a fractional frequency division circuit coupled to the plurality of outputs of the ILRO, the fractional frequency division circuit configured to sequentiallyselect, using a multiplexer (MUX), successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases to generate a decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency. [0104] According to the example apparatus, in some embodiments, the ILRO may be configured such that an oscillation frequency of the ILRO is tuned to be substantially-near the carrier center frequency of the phase-modulated carrier output signal.

**[0105]** The example apparatus may further include, in some embodiments, an injection circuit coupled to the ILRO and to an output of the DCO circuit and configured to inject the phase-modulate carrier output signal into the ILRO.

**[0106]** The example apparatus may further include, in some embodiments, an integer frequency division circuit coupled to the fractional frequency division circuit and configured to generate, based on the decoupled fractional frequency output signal, a desired phase-modulated carrier output signal that is decoupled from the DCO circuit, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

[0107] Further according to the example apparatus, in some embodiments, the integer frequency division circuit may be further configured to generate the desired phasemodulated carrier output signal based on the decoupled fractional frequency output signal by dividing by 2 the center frequency of the decoupled fractional frequency output signal. In some embodiments, the integer frequency division circuit may be further configured to trigger an integer frequency division output signal to go high upon a rising edge of the decoupled fractional frequency output signal. In some embodiments, the integer frequency division circuit may be further configured to reset the integer frequency division output signal to low after an adjustable period of time. In some embodiments, a center frequency of the integer frequency division output signal may be equal to half the center frequency of the fractional frequency output signal.

**[0108]** Further according to the example apparatus, the example apparatus may further include, in some embodiments, an amplifier configured to amplify the desired phase-modulated carrier output signal for transmission.

**[0109]** According to the example apparatus, in some embodiments, the fractional frequency division circuit may include the MUX and multiple delay flip-flops, the multiple delay flip-flops having respective outputs configured to sequentially select the successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases.

**[0110]** According to the example apparatus, in some embodiments, the carrier center frequency of the phase-modulated carrier output signal may be 1.25 times the center frequency of the decoupled fractional frequency output signal.

**[0111]** According to the example apparatus, in some embodiments, the DCO circuit may be configured to output the phase-modulated carrier output signal with phases of 0 degrees and 180 degrees.

**[0112]** According to the example apparatus, in some embodiments, the ILRO may be further configured to generate the phases of 0, 90, 180, and 270 degrees of the phase-modulated carrier output signal.

**[0113]** According to the example apparatus, in some embodiments, the fractional frequency division circuit may be further configured to align the plurality of phases of the phase-modulated carrier output signal into a plurality of pairs of phases.

**[0114]** According to the example apparatus, in some embodiments, the fractional frequency division circuit may be configured to repeat a sequential process including: responsive to detecting a rising edge of a current phase of the plurality of phases, selecting a portion of a next phase of the plurality of phases; setting a next portion of the decoupled fractional frequency output signal equal to the selected portion of the next phase; and setting the current phase equal to the next phase.

**[0115]** Further according to the example apparatus, the example apparatus may further include, in some embodiments, a delay element coupled to the fractional frequency division circuit and configured to delay the current phase prior to detecting the rising edge of the current phase.

[0116] Another example apparatus disclosed herein in accordance with some embodiments may include: a processor; and a non-transitory computer-readable medium storing instructions that are operative, when executed by the processor, to perform the functions including: receiving, from a modulator, a phase-modulated carrier output signal having a carrier center frequency that is a non-integer multiple of a desired carrier center frequency; generating, by an injectionlocked ring oscillator (ILRO) a plurality of phases of the phase-modulated carrier output signal at a plurality of outputs of the ILRO; generating a decoupled fractional frequency output signal by sequentially selecting, using a multiplexer, successive outputs of the plurality of outputs corresponding to successive phases of the plurality of phases, the decoupled fractional frequency output signal having a center frequency equal to an integer multiple of the desired carrier center frequency; and generating, based on the decoupled fractional frequency output signal, a desired phase modulated carrier output signal that is decoupled from the modulator, the desired phase-modulated carrier output signal having a generated carrier center frequency equal to the desired carrier center frequency.

**[0117]** In the foregoing specification, specific embodiments have been described. However, one of ordinary skill in the art appreciates that various modifications and changes

can be made without departing from the scope of the invention as set forth in the claims below. Accordingly, the specification and figures are to be regarded in an illustrative rather than a restrictive sense, and all such modifications are intended to be included within the scope of present teachings.

**[0118]** The benefits, advantages, solutions to problems, and any element(s) that may cause any benefit, advantage, or solution to occur or become more pronounced are not to be construed as a critical, required, or essential features or elements of any or all the claims. The invention is defined solely by the appended claims including any amendments made during the pendency of this application and all equivalents of those claims as issued.

[0119] Moreover in this document, relational terms such as first and second, top and bottom, and the like may be used solely to distinguish one entity or action from another entity or action without necessarily requiring or implying any actual such relationship or order between such entities or actions. The terms "comprises," "comprising," "has", "having," "includes", "including," "contains", "containing" or any other variation thereof, are intended to cover a nonexclusive inclusion, such that a process, method, article, or apparatus that comprises, has, includes, contains a list of elements does not include only those elements but may include other elements not expressly listed or inherent to such process, method, article, or apparatus. An element proceeded by "comprises . . . a", "has . . . a", "includes . . . a", "contains . . . a" does not, without more constraints, preclude the existence of additional identical elements in the process, method, article, or apparatus that comprises, has, includes, contains the element. The terms "a" and "an" are defined as one or more unless explicitly stated otherwise herein. The terms "substantially", "essentially", "approximately", "about" or any other version thereof, are defined as being close to as understood by one of ordinary skill in the art, and in one non-limiting embodiment the term is defined to be within 10%, in another embodiment within 5%, in another embodiment within 1% and in another embodiment within 0.5%. The term "coupled" as used herein is defined as connected, although not necessarily directly and not necessarily mechanically. A device or structure that is "configured" in a certain way is configured in at least that way, but may also be configured in ways that are not listed.