US 20190356328A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2019/0356328 A1

# Ben Shem et al.

## Nov. 21, 2019 (43) **Pub. Date:**

#### (54) LOOKUP-TABLE-BASED SIGMA-DELTA ADC FILTER

- (71) Applicant: Sony Semiconductor Solutions Corporation, Kanagawa (JP)

- (72) Inventors: Ariel Ben Shem, Hasharon (IL); Itai Shvartz, Petach-Tikva (IL)

- (21) Appl. No.: 16/058,482

- (22) Filed: Aug. 8, 2018

### **Related U.S. Application Data**

(60) Provisional application No. 62/672,893, filed on May 17, 2018.

#### **Publication Classification**

| (51) Int. Cl. |           |

|---------------|-----------|

| H03M 3/00     | (2006.01) |

| H04N 5/378    | (2006.01) |

| H04N 5/369    | (2006.01) |

(52) U.S. Cl. CPC ..... H03M 3/32 (2013.01); H04N 5/3698 (2013.01); H04N 5/378 (2013.01); H03M 3/458 (2013.01)

#### (57) ABSTRACT

An analog-to-digital converter comprises a sigma-delta modulator; and an ADC filter configured to store a plurality of partial sums as respective entries in a plurality of lookup tables, retrieve at least one of the plurality of partial sums based on an output of the sigma-delta modulator, and calculate a filter output by adding retrieved ones of the plurality of partial sums together.

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

| Clock 3 | a0 a1 a2 a3 | b0 b1 b2 | c0 c1 c1 | op op |  |  | Clock 7 | a0 a1 a2 a3 a4 a5 a6 a7 | b0 b1 b2 b3 b4 b5 b6 | c0 c1 c2 c3 c4 c5 | d0 d1 d2 d3 d4 | e0 e1 e2 e3 | 10 f0 f1 f2 | g0 g1 g1 |         |

|---------|-------------|----------|----------|-------|--|--|---------|-------------------------|----------------------|-------------------|----------------|-------------|-------------|----------|---------|

| Clock 2 | a0 a1 a2    | b0 b1 b1 | c0 c0    |       |  |  | Clock 6 | a0 a1 a2 a3 a4 a5 a6    | b0 b1 b2 b3 b4 b5    | c0 c1 c2 c3 c4    | d0 d1 d2 d3    | e0 e1 e2    | f0 f1 H     |          | FIG. 9A |

| Clock 1 | a0 a1       | 0q 0q    |          |       |  |  | Clock 5 | a0 a1 a2 a3 a4 a5       | b0 b0 b1 b2 b3 b4    | c0 c1 c2 c3       | d0 d0 d1 d2    | e0 e1 e1    | 40<br>V     |          | EIC     |

| Clock 0 | a0 a0       |          |          |       |  |  | Clock 4 | a0 a1 a2 a3 a4          | b0 b1 b2 b3          | c0 c1 c2          | d0 d0 d7       | e0 e0       |             |          |         |

| 1        |                                         |                                                                                                                             |                                                                                                                  |                                                                      |                         | r                    |                | <b></b>  |                   | 5                                                     |                                                                                                                                           |                                                                                                                                          |                                                                                                                                         |                                           |                                                                                                                                         |                                                                                                                                        |                                                                                                      |

|----------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------|----------------------|----------------|----------|-------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|          | a7                                      | b7                                                                                                                          | c7                                                                                                               | d7                                                                   | е7                      |                      |                |          |                   | a15                                                   | ld :                                                                                                                                      | с7                                                                                                                                       | d7                                                                                                                                      | е7                                        | 4                                                                                                                                       | ĝ7                                                                                                                                     | h7                                                                                                   |

|          | a6                                      | 9q                                                                                                                          | с6                                                                                                               | d6                                                                   | e6                      | £9                   |                |          |                   | a14                                                   | b14                                                                                                                                       | c6                                                                                                                                       | gg                                                                                                                                      | e6                                        | f6                                                                                                                                      | g6                                                                                                                                     | h6                                                                                                   |

|          | a5                                      | p5                                                                                                                          | ς <sub>Σ</sub>                                                                                                   | d5                                                                   | е5                      | ង                    | g2             |          |                   | a13                                                   | b13                                                                                                                                       | c13                                                                                                                                      | £                                                                                                                                       | е5                                        | £                                                                                                                                       | β                                                                                                                                      | h5                                                                                                   |

|          | a4                                      | þ4                                                                                                                          | c4                                                                                                               | d4                                                                   | e4                      | f4                   | g4             | h4       |                   | a12                                                   | b12                                                                                                                                       | c12                                                                                                                                      | d12                                                                                                                                     | e4                                        | <b>1</b> 4                                                                                                                              | g4                                                                                                                                     | h4                                                                                                   |

| Clock 11 | a11                                     | p3                                                                                                                          | S                                                                                                                | d3                                                                   | e3                      | β                    | g3             | h3       | Clock 15          | a11                                                   | b11                                                                                                                                       | c11                                                                                                                                      | d11                                                                                                                                     | e11                                       | ង                                                                                                                                       | g3                                                                                                                                     | h3                                                                                                   |

| Cloc     | a10                                     | b10                                                                                                                         | c2                                                                                                               | d2                                                                   | e2                      | 5                    | g2             | h2       | Cloc              | a10                                                   | b10                                                                                                                                       | c10                                                                                                                                      | d10                                                                                                                                     | e10                                       | 110                                                                                                                                     | g2                                                                                                                                     | h2                                                                                                   |

|          | a9                                      | 6q                                                                                                                          | 60                                                                                                               | d1                                                                   | e1                      | 1                    | g1             | h1       |                   | a9                                                    | 6q                                                                                                                                        | <i>6</i> 5                                                                                                                               | ф                                                                                                                                       | 69                                        | ф                                                                                                                                       | <i>6</i> 6                                                                                                                             | h1                                                                                                   |

|          | a8                                      | b8                                                                                                                          | c8                                                                                                               | 0p                                                                   | e0                      | f0                   | g0             | оч       |                   | a8                                                    | b8                                                                                                                                        | 68                                                                                                                                       | d8                                                                                                                                      | e8                                        | f8                                                                                                                                      | g8                                                                                                                                     | h0                                                                                                   |

|          | a0<br>a8                                | b0<br>b8                                                                                                                    | 03<br>83                                                                                                         | d0<br>d8                                                             | e0                      | Q                    | g0             | 04       |                   | a0<br>a8                                              | b0<br>b8                                                                                                                                  | 03<br>83                                                                                                                                 | 99<br>99                                                                                                                                | e0<br>e8                                  | f0<br>10                                                                                                                                | g0<br>g8                                                                                                                               | h0<br>h8                                                                                             |

|          |                                         |                                                                                                                             |                                                                                                                  |                                                                      | 1                       |                      |                |          |                   |                                                       | 1                                                                                                                                         |                                                                                                                                          |                                                                                                                                         |                                           |                                                                                                                                         |                                                                                                                                        |                                                                                                      |

|          | a7                                      | b7                                                                                                                          | c7                                                                                                               | d7                                                                   |                         |                      |                |          |                   | t a7                                                  | b7                                                                                                                                        | c7                                                                                                                                       | ۲b                                                                                                                                      | е7                                        | 17                                                                                                                                      | g7                                                                                                                                     | h7                                                                                                   |

|          | a6                                      | pq                                                                                                                          | c6                                                                                                               | <del>у</del> р                                                       | e6                      |                      |                |          |                   | 3 a14                                                 | p6                                                                                                                                        | 90                                                                                                                                       | gg                                                                                                                                      | e6                                        | f6                                                                                                                                      | <u> </u>                                                                                                                               | h6                                                                                                   |

|          | a5                                      | 55<br>D                                                                                                                     | c5                                                                                                               | ß                                                                    | eΣ                      | £5                   |                |          |                   | 2 a13                                                 | 2 b13                                                                                                                                     | c5                                                                                                                                       | ß                                                                                                                                       | е5                                        | £                                                                                                                                       | g5                                                                                                                                     | h5                                                                                                   |

| 0        | a4                                      | b4                                                                                                                          | c4                                                                                                               | d4                                                                   | e4                      | f4                   | g4             |          | 4                 | a12                                                   | b12                                                                                                                                       | c12                                                                                                                                      | d4                                                                                                                                      | 64                                        | f4                                                                                                                                      | <u>g</u> 4                                                                                                                             | h4                                                                                                   |

| Clock 10 | ) a3                                    | p3                                                                                                                          | с3                                                                                                               | ಭ                                                                    | e3                      | с<br>С               | ങ              | h3       | Clock 14          | a11                                                   | b11                                                                                                                                       | c11                                                                                                                                      | d11                                                                                                                                     | e3                                        | 33                                                                                                                                      | <u>g</u> 3                                                                                                                             | h3                                                                                                   |

| Clo      | a10                                     | b2                                                                                                                          | c2                                                                                                               | d2                                                                   | e2                      | 5                    | g2             | h2       | Clo               | a10                                                   | b10                                                                                                                                       | c10                                                                                                                                      | d10                                                                                                                                     | e10                                       | 42                                                                                                                                      | g2                                                                                                                                     | Р7                                                                                                   |

|          | a9                                      | 69                                                                                                                          | c1                                                                                                               | ਰ                                                                    | e,                      | ŧ                    | g<br>T         | Ĕ        |                   | a9                                                    | 6q                                                                                                                                        | 93<br>93                                                                                                                                 | 윙                                                                                                                                       | 69                                        | £9                                                                                                                                      | g1                                                                                                                                     | 4                                                                                                    |

|          | a8                                      | b8                                                                                                                          | c0                                                                                                               | do<br>do                                                             | e0                      | Q<br>Q               | о<br>Сб        | 04       |                   | a8                                                    | b8                                                                                                                                        | 83                                                                                                                                       | 쯍                                                                                                                                       | e8                                        | 8                                                                                                                                       | g0                                                                                                                                     | 94                                                                                                   |

|          | $\sim$                                  | $\cap \infty$                                                                                                               | 8                                                                                                                | 0                                                                    | 0                       | ę                    | g              | 오        |                   | ag ao                                                 | 09 89                                                                                                                                     | රි සි                                                                                                                                    | පි සි                                                                                                                                   | မ္မွ                                      | Q Q                                                                                                                                     | g0<br>g8                                                                                                                               | 오                                                                                                    |

|          | a0<br>a8                                | b0<br>b8                                                                                                                    | с0<br>с8                                                                                                         | в                                                                    | e0                      | ų                    | ß              | ے        |                   | ອີອ                                                   | م م                                                                                                                                       | 00                                                                                                                                       | סס                                                                                                                                      | 00                                        | 4                                                                                                                                       | 6<br>0                                                                                                                                 | ع                                                                                                    |

|          | a(<br>3                                 | ãã                                                                                                                          | ΰΰ                                                                                                               | ס                                                                    | Ð                       | ¥ I                  | 5              | -        |                   | ຫ ຫ                                                   | م م                                                                                                                                       | 00                                                                                                                                       | סס                                                                                                                                      | ΦΦ                                        | æ æ                                                                                                                                     | 5 5                                                                                                                                    | _ 2                                                                                                  |

|          | a7 a(                                   | pi<br>Pi                                                                                                                    | c7 c                                                                                                             | σ                                                                    | Ð                       | ¥                    | 0              |          |                   | a7 a                                                  | q<br>PZ                                                                                                                                   | c7 c                                                                                                                                     | p<br>2p                                                                                                                                 | e7 e                                      | 17<br>11                                                                                                                                | g7 g                                                                                                                                   | ے <u>ا</u>                                                                                           |

|          |                                         |                                                                                                                             |                                                                                                                  | d6<br>d6                                                             | Ū                       |                      | 5              |          |                   | a6 a7                                                 |                                                                                                                                           |                                                                                                                                          |                                                                                                                                         |                                           |                                                                                                                                         |                                                                                                                                        | 40 P                                                                                                 |

|          | a7                                      | b7                                                                                                                          | c7                                                                                                               |                                                                      | e5                      |                      | 57             |          |                   | a7                                                    | b5 b6 b7                                                                                                                                  | c7                                                                                                                                       | -12                                                                                                                                     | e7                                        | f7                                                                                                                                      | g7                                                                                                                                     |                                                                                                      |

| 6        | a6 a7                                   | b6 b7                                                                                                                       | c6 c7                                                                                                            | d6                                                                   |                         | <i>f</i> 4           | 57             |          | 13                | a12 a13 a6 a7                                         | b6 b7                                                                                                                                     | c6 c7                                                                                                                                    | d6 d7                                                                                                                                   | e6 e7                                     | f6 f7                                                                                                                                   | g6 g7                                                                                                                                  | 94                                                                                                   |

| lock 9   | a5 a6 a7                                | b5 b6 b7                                                                                                                    | c5 c6 <i>c7</i>                                                                                                  | d5 d6                                                                | e5                      |                      | <u>a</u><br>33 |          | ock 13            | a11 a12 a13 a6 a7                                     | b11 b12 b5 b6 b7                                                                                                                          | c5 c6 c7                                                                                                                                 | d3 d4 d5 d6 d7                                                                                                                          | e5 e6 e7                                  | f5 f6 f7                                                                                                                                | g5 g6 <i>g</i> 7                                                                                                                       | h5 <i>h</i> 6                                                                                        |

| Clock 9  | a4 a5 a6 a7                             | b4 b5 b6 b7                                                                                                                 | c4 c5 c6 c7                                                                                                      | d4 d5 <i>d</i> 6                                                     | e4 e5                   | f4                   |                | h2       | Clock 13          | a12 a13 a6 a7                                         | <i>b</i> 12 b5 b6 b7                                                                                                                      | c4 c5 c6 c7                                                                                                                              | d4 d5 d6 d7                                                                                                                             | e4 e5 e6 e7                               | f4 f5 f6 f7                                                                                                                             | g4 g5 g6 g7                                                                                                                            | h4 h5 <i>h</i> 6                                                                                     |

| Clock 9  | a3 a4 a5 a6 a7                          | b3 b4 b5 b6 b7                                                                                                              | c3 c4 c5 c6 <i>c7</i>                                                                                            | d3 d4 d5 <i>d</i> 6                                                  | e3 e4 e5                | f3 f4                | g3             |          | Clock 13          | a11 a12 a13 a6 a7                                     | b11 b12 b5 b6 b7                                                                                                                          | c11 c4 c5 c6 c7                                                                                                                          | d3 d4 d5 d6 d7                                                                                                                          | e3 e4 e5 e6 e7                            | f3 f4 f5 f6 f7                                                                                                                          | g3 g4 g5 g6 g7                                                                                                                         | h3 h4 h5 <i>h</i> 6                                                                                  |

| Clock 9  | a2 a3 a4 a5 a6 a7                       | b2 b3 b4 b5 b6 b7                                                                                                           | c2 c3 c4 c5 c6 c7                                                                                                | d2 d3 d4 d5 <i>d</i> 6                                               | e2 e3 e4 e5             | 12 13 14             | g2 g3          | h2 h2    | Clock 13          | a10 a11 a12 a13 a6 a7                                 | b10 b11 b12 b5 b6 b7                                                                                                                      | c10 <i>c11</i> c4 c5 c6 c7                                                                                                               | <i>d10</i> d3 d4 d5 d6 d7                                                                                                               | e2 e3 e4 e5 e6 e7                         | f2 f3 f4 f5 f6 f7                                                                                                                       | 92 93 94 95 96 <i>9</i> 7                                                                                                              | h2 h3 h4 h5 h6                                                                                       |

|          | a8 a9 a2 a3 a4 a5 a6 a7                 | b1 b2 b3 b4 b5 b6 b7                                                                                                        | c0 c1 c2 c3 c4 c5 c6 c7                                                                                          | d1 d2 d3 d4 d5 d6                                                    | e1 e2 e3 e4 e5          | f1 f2 f3 f4          | g1 g2 g3       | h1 h2 h1 | Clock 13          | a8 a9 a10 a11 a12 <i>a1</i> 3 a6 a7                   | b9 b10 b11 <i>b1</i> 2 b5 b6 b7                                                                                                           | c8 c9 c10 c11 c4 c5 c6 c7                                                                                                                | d8 d9 <i>d10</i> d3 d4 d5 d6 d7                                                                                                         | e8 e9 e2 e3 e4 e5 e6 e7                   | f0 f1 f2 f3 f4 f5 f6 f7                                                                                                                 | g0 g1 g2 g3 g4 g5 g6 <i>g</i> 7                                                                                                        | h1 h2 h3 h4 h5 <i>h</i> 6                                                                            |

|          | a8 a9 a2 a3 a4 a5 a6 a7                 | b0 b1 b2 b3 b4 b5 b6 b7                                                                                                     | c0 c1 c2 c3 c4 c5 c6 c7                                                                                          | d0 d1 d2 d3 d4 d5 d6                                                 | e0 e1 e2 e3 e4 e5       | f0 f1 f2 f3 f4       | g0 g1 g2 g3    | h0 h1 h2 | Clock 13          | a8 a9 a10 a11 a12 <i>a1</i> 3 a6 a7                   | b8 b9 b10 b11 <i>b12</i> b5 b6 b7                                                                                                         | c8 c9 c10 c11 c4 c5 c6 c7                                                                                                                | d8 d9 <i>d10</i> d3 d4 d5 d6 d7                                                                                                         | e8 e9 e2 e3 e4 e5 e6 e7                   | f0 f1 f2 f3 f4 f5 f6 f7                                                                                                                 | g0 g1 g2 g3 g4 g5 g6 <i>g</i> 7                                                                                                        | h0 h1 h2 h3 h4 h5 h6                                                                                 |

|          | a8 a9 a2 a3 a4 a5 a6 a7                 | b0 b1 b2 b3 b4 b5 b6 b7                                                                                                     | c0 c1 c2 c3 c4 c5 c6 c7                                                                                          | d0 d1 d2 d3 d4 d5 d6                                                 | e0 e1 e2 e3 e4 e5       | f0 f1 f2 f3 f4       | g0 g1 g2 g3    | h0 h1 h2 | Clock 13          | a8 a9 a10 a11 a12 <i>a1</i> 3 a6 a7                   | b8 b9 b10 b11 <i>b12</i> b5 b6 b7                                                                                                         | c8 c9 c10 c11 c4 c5 c6 c7                                                                                                                | d8 d9 <i>d10</i> d3 d4 d5 d6 d7                                                                                                         | e8 e9 e2 e3 e4 e5 e6 e7                   | f0 f1 f2 f3 f4 f5 f6 f7                                                                                                                 | g0 g1 g2 g3 g4 g5 g6 <i>g</i> 7                                                                                                        | h0 h1 h2 h3 h4 h5 h6                                                                                 |

|          | a0 a8 a9 a2 a3 a4 a5 a6 a7              | b0 b0 b1 b2 b3 b4 b5 b6 b7 b8                                                                                               | c0 c1 c2 c3 c4 c5 c6 c7                                                                                          | d0 d1 d2 d3 d4 d5 d6                                                 | e0 e1 e2 e3 e4 e5       | f0 f1 f2 f3 f4       | g0 g1 g2 g3    | h0 h1 h2 | Clock 13          | a0 a8 a9 a10 a11 a12 a13 a6 a7                        | b0 b8 b9 b10 b11 b12 b5 b6 b7                                                                                                             | c0         c8         c9         c10         c11         c4         c5         c6         c7                                             | d0         d8         d9         d10         d3         d4         d5         d6         d7                                             | e0 e8 e9 e2 e3 e4 e5 e6 e7                | f0<br>f8 f0 f1 f2 f3 f4 f5 f6 f7                                                                                                        | g0 g1 g2 g3 g4 g5 g6 <i>g</i> 7                                                                                                        | h0 h1 h2 h3 h4 h5 h6                                                                                 |

|          | a7 a8 a9 a2 a3 a4 a5 a6 a7              | $\frac{b7}{b8}$ b0 b1 b2 b3 b4 b5 b6 b7                                                                                     | c0         c1         c2         c3         c4         c5         c6         c7                                  | d0 d1 d2 d3 d4 d5 d6                                                 | e0 e1 e2 e3 e4 e5       | f0 f1 f2 f3 f4       | g0 g1 g2 g3    | h0 h1 h2 | Clock 13          | a7 a0 a8 a9 a10 a11 a12 a13 a6 a7                     | b7 <u>b0</u> b8 b9 b10 b11 <i>b1</i> 2 b5 b6 b7                                                                                           | c7 c9 c9 c10 c11 c4 c5 c6 c7                                                                                                             | d0         d8         d9         d10         d3         d4         d5         d6         d7                                             | e7 e0 e8 e9 e2 e3 e4 e5 e6 e7             | <i>i</i> 7 <sup>f0</sup> f0 f1 f2 f3 f4 f5 f6 f7                                                                                        | g0         g1         g2         g3         g4         g5         g6         g7                                                        | h0 h1 h2 h3 h4 h5 h6                                                                                 |

|          | a6 a7 <u>a8</u> a8 a9 a2 a3 a4 a5 a6 a7 | b6 b7 b0 b1 b2 b3 b4 b5 b6 b7 b8                                                                                            | c0         c1         c2         c3         c4         c5         c6         c7                                  | d0         d1         d2         d3         d4         d5         d6 | e0 e1 e2 e3 e4 e5       | f0 f1 f2 f3 f4       | g0 g1 g2 g3    | h0 h1 h2 |                   | a6 a7 a0 a8 a9 a10 a11 a12 a13 a6 a7                  | b6 b7 b9 b8 b9 b10 b11 b12 b5 b6 b7                                                                                                       | c6         c7         c0         c8         c9         c10         c11         c4         c5         c6         c7                       | d6 d7 d0 d8 d9 d10 d3 d4 d5 d6 d7                                                                                                       | e6 e7 e9 e9 e9 e2 e3 e4 e5 e6 e7          | f6 <i>i7</i> <sup>f0</sup> f0 f1 f2 f3 f4 f5 f6 f7                                                                                      | g6 g0 g1 g2 g3 g4 g5 g6 g7                                                                                                             | h0 h1 h2 h3 h4 h5 h6                                                                                 |

|          | a5 a6 a7 a8 a9 a2 a3 a4 a5 a6 a7        | b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7                                                                                            | c5         c6         c0         c1         c2         c3         c4         c5         c6         c7            | <i>d</i> <sup>5</sup> d0 d1 d2 d3 d4 d5 <i>d</i> 6                   | e0 e1 e2 e3 e4 e5       | f0 f1 f2 f3 f4       | g0 g1 g2 g3    | h0 h1 h2 |                   | a5 a6 a7 <u>a8</u> a8 a9 a10 a11 a12 <i>a13</i> a6 a7 | b5 b6 b7 b9 b8 b9 b10 b11 b12 b5 b6 b7                                                                                                    | c5 c6 c7 c9 c9 c9 c10 c11 c4 c5 c6 c7                                                                                                    | d5 d6 d7 d0 d3 d9 d10 d3 d4 d5 d6 d7                                                                                                    | e5 e6 e7 e9 e9 e9 e2 e3 e4 e5 e6 e7       | f5 f6 <i>f7</i> <sup>f0</sup> f0 f1 f2 f3 f4 f5 f6 f7                                                                                   | g5 g6 97 g0 g1 g2 g3 g4 g5 g6 g7                                                                                                       | h5 h0 h1 h2 h3 h4 h5 h6                                                                              |

|          | a4 a5 a6 a7 a0 a8 a9 a2 a3 a4 a5 a6 a7  | b4         b5         b6         b7         b0         b1         b2         b3         b4         b5         b6         b7 | c4         c5         c6         c0         c1         c2         c3         c4         c5         c6         c7 | d4 d5 d0 d1 d2 d3 d4 d5 d6                                           | e4 e0 e1 e2 e3 e4 e5    | 10 10 11 12 13 14    | g0 g1 g2 g3    | h0 h1 h2 | Clock 12 Clock 13 | <i>a1</i> 2 a5 a6 a7 a0 a8 a9 a10 a11 a12 a13 a6 a7   | b4         b5         b6         b7         b0         b8         b9         b10         b11         b12         b5         b6         b7 | c4         c5         c6         c7         c0         c8         c9         c10         c11         c4         c5         c6         c7 | d4         d5         d6         d7         d0         d8         d9         d10         d3         d4         d5         d6         d7 | e4 e5 e6 e7 e9 e8 e9 e2 e3 e4 e5 e6 e7    | f4         f5         f6         f7         f0         f1         f2         f3         f4         f5         f6         f7             | g4         g5         g6         g0         g1         g2         g3         g4         g5         g6         g7                       | h4         h5         h0         h1         h2         h3         h4         h5         h6         h |

|          | a3 a4 a5 a6 a7 a8 a9 a2 a3 a4 a5 a6 a7  | b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7                                                                                      | c3     c4     c5     c6     c0     c0     c1     c2     c3     c4     c5     c6     c7                           | d3 d4 d5 d0 d1 d2 d3 d4 d5 d6                                        | e3 e4 e0 e1 e2 e3 e4 e5 | 13 10 10 11 12 13 14 | g0 g1 g2 g3    | h0 h1 h2 |                   | a11 a12 a5 a6 a7 a0 a8 a9 a10 a11 a12 a13 a6 a7       | <i>b11</i> b4 b5 b6 b7 <u>b8</u> b8 b9 b10 b11 <i>b12</i> b5 b6 b7                                                                        | c3 c4 c5 c6 c7 c0 c8 c9 c10 c11 c4 c5 c6 c7                                                                                              | d3 d4 d5 d6 d7 d0 d3 d9 d1 d3 d4 d5 d6 d7                                                                                               | e3 e4 e5 e6 e7 e8 e9 e9 e2 e3 e4 e5 e6 e7 | f3         f4         f5         f6 <i>I</i> f0         f0         f1         f2         f3         f4         f5         f6         f7 | g3         g4         g5         g6         g0         g0         g1         g2         g3         g4         g5         g6         g7 | h3 h4 h5 h0 h1 h2 h3 h4 h5 h6                                                                        |

e0

Q

00

a0 a8 b0

в

g0

<u>о</u>ч

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

g

РЧ

FIG. 9B

FIG. 11

FIG. 14

FIG. 15

#### LOOKUP-TABLE-BASED SIGMA-DELTA ADC FILTER

### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

**[0001]** This application relates generally to analog-todigital conversion. More specifically, this application relates to a system and method for calculating an output from a sigma-delta analog-to-digital converter that minimizes peak power consumption.

#### 2. Description of Related Art

**[0002]** Image sensing devices typically consist of an image sensor, generally an array of pixel circuits, as well as signal processing circuitry and any associated control or timing circuitry. Within the image sensor itself, charge is collected in a photoelectric conversion device of the pixel circuit as a result of the impingement of light and an electrical signal is generated therefrom. The electrical signal is routed through a collection of analog readout circuits, which may comprise signal amplifiers, signal condition circuits, vertical signal lines (VSLs), sample and hold (S/H) circuits, and analog-to-digital converters (ADCs). Among other operations, the signals from the VSLs are sampled and then converted into digital values by ADCs.

[0003] In an image sensor, there are typically a very large number of individual photoelectric conversion devices (e.g. tens of millions), and many ADCs working in parallel. Each ADC in the image sensor is shared by a large number of photoelectric conversion devices; for example, a column or multiple columns of photoelectric conversion devices may share a single ADC, a rectangular block of photoelectric conversion devices may share an ADC, and the like. As the number of pixels in the image sensor increases, the number of ADCs also increases. As a result, the power consumption of the ADCS becomes an increasingly large factor as the image resolution (i.e., number of pixels) increases. As the total power consumption in an image sensor in a mobile device increases, not only is there an increase in the power drawn from a battery and resultant decrease in operating time of the mobile device, but there is also an increase in the temperature of the silicon and resultant degradation in the noise performance of the sensor. Accordingly, there exists a need to improve the power consumption characteristics of an image sensor that uses sigma-delta ADCs.

#### BRIEF SUMMARY OF THE INVENTION

**[0004]** Various aspects of the present disclosure relate to processing pixels of an image sensor with reduced peak power consumption.

**[0005]** In one exemplary aspect of the present disclosure, there is provided an analog-to-digital converter, comprising a sigma-delta modulator; and an ADC filter configured to store a plurality of partial sums as respective entries in a plurality of lookup tables, retrieve at least one of the plurality of partial sums based on an output of the sigma-delta modulator, and calculate a filter output by adding retrieved ones of the plurality of partial sums together.

**[0006]** In another exemplary aspect of the present disclosure, there is provided an analog-to-digital conversion circuit, comprising a plurality of sigma-delta modulators; and a plurality of ADC filters respectively corresponding to the plurality of sigma-delta modulators, wherein the plurality of ADC filters are respectively configured to store a plurality of partial sums as respective entries in a plurality of lookup tables, retrieve at least one of the plurality of partial sums based on an output of the sigma-delta modulator, and calculate a filter output by adding retrieved ones of the plurality of partial sums together.

**[0007]** In another exemplary aspect of the present disclosure, there is provided a method of calculating an output in an analog-to-digital converter, comprising storing, by an ADC filter, a plurality of partial sums as respective entries in a plurality of lookup tables; receiving, by the ADC filter and from a sigma-delta modulator, an output; retrieving, by the ADC filter, at least one of the plurality of partial sums based on the output; and adding, by the ADC filter, retrieved ones of the plurality of partial sums together so as to generate the output.

**[0008]** In this manner, various aspects of the present disclosure provide for improvements in at least the technical fields of imaging and image processing.

**[0009]** This disclosure can be embodied in various forms, including hardware or circuits controlled by computerimplemented methods, computer program products, computer systems and networks, user interfaces, and application programming interfaces; as well as hardware-implemented methods, signal processing circuits, image sensor circuits, application specific integrated circuits, field programmable gate arrays, and the like. The foregoing summary is intended solely to give a general idea of various aspects of the present disclosure, and does not limit the scope of the disclosure in any way.

#### DESCRIPTION OF THE DRAWINGS

**[0010]** These and other more detailed and specific features of various embodiments are more fully disclosed in the following description, reference being had to the accompanying drawings, in which:

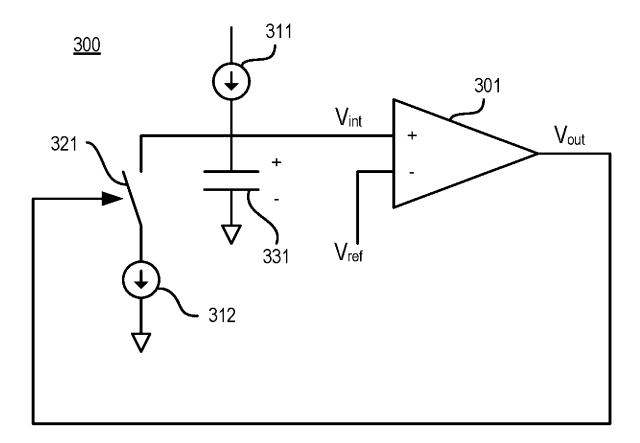

[0011] FIG. 1 illustrates an exemplary image sensor according to various aspects of the present disclosure;

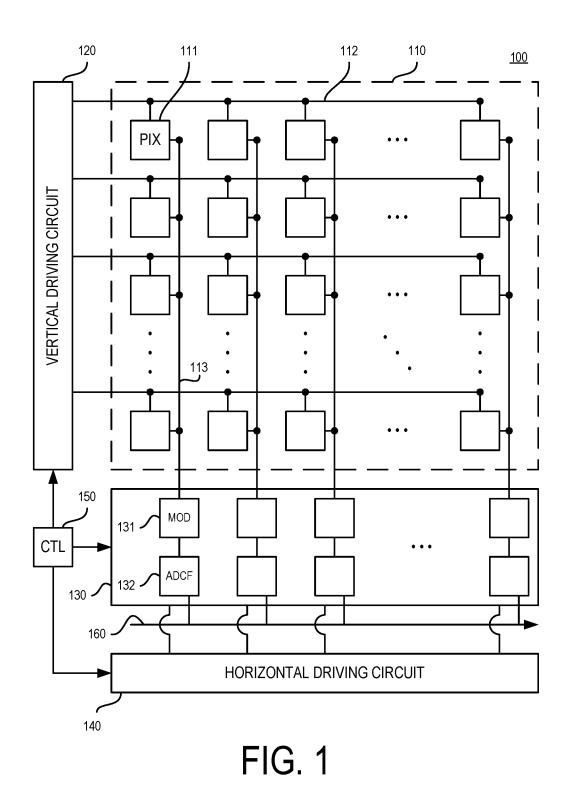

**[0012]** FIG. **2** illustrates an exemplary pixel circuit according to various aspects of the present disclosure;

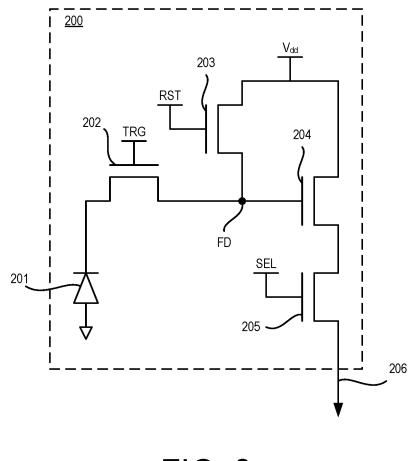

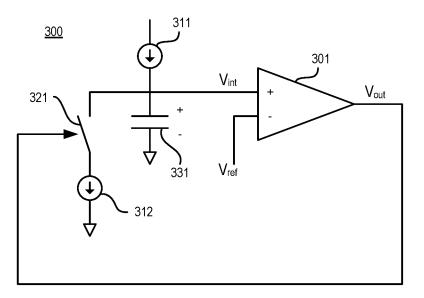

**[0013]** FIG. **3** illustrates an exemplary first-order currentmode sigma-delta modulator according to various aspects of the present disclosure:

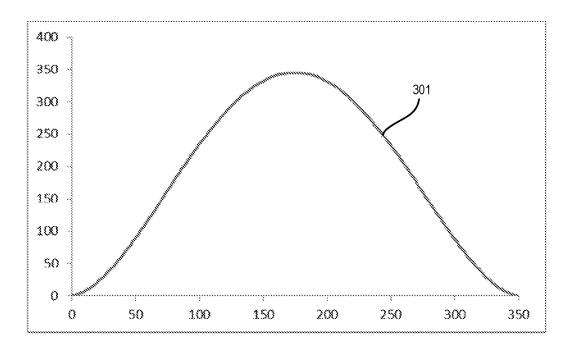

**[0014]** FIG. **4** illustrates an exemplary impulse response of an ADC filter according to various aspects of the present disclosure;

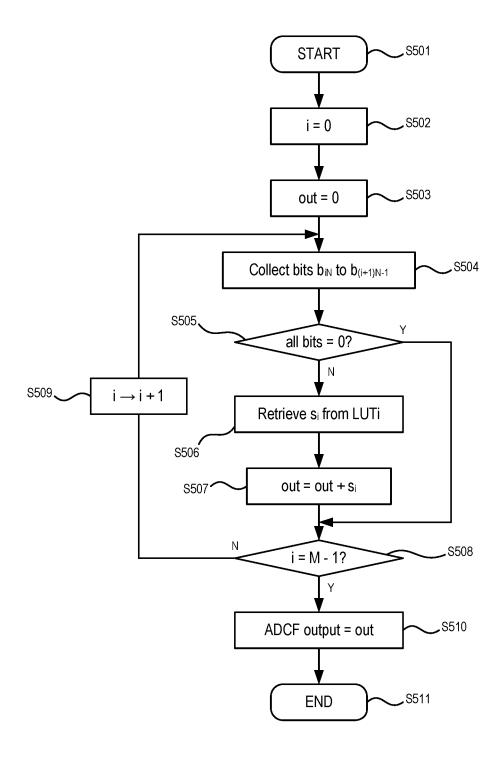

**[0015]** FIG. **5** illustrates an exemplary process flow for calculating the output in an ADC filter according to various aspects of the present disclosure;

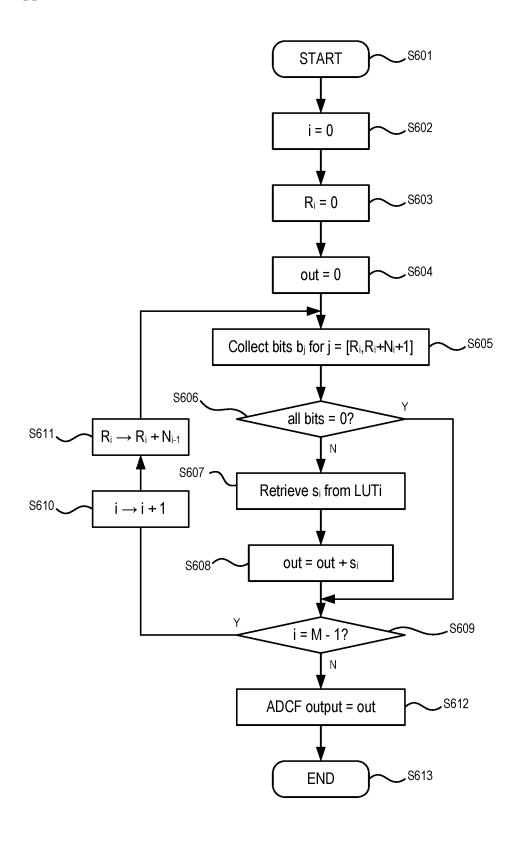

**[0016]** FIG. **6** illustrates another exemplary process flow for calculating the output in an ADC filter according to various aspects of the present disclosure;

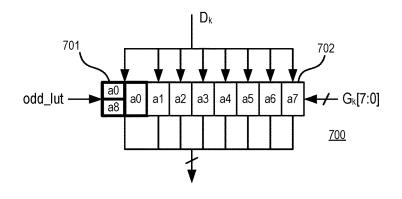

**[0017]** FIG. 7 illustrates an exemplary latch circuit array according to various aspects of the present disclosure;

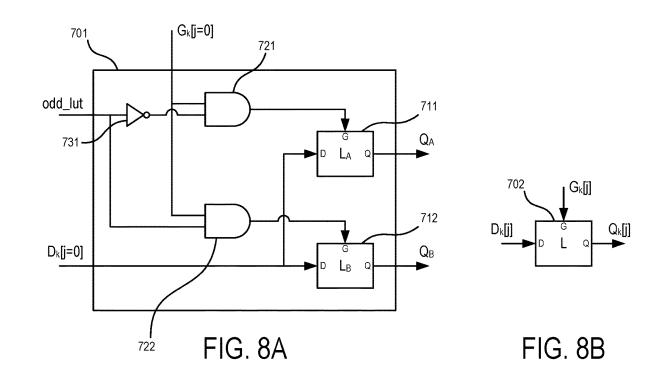

**[0018]** FIGS. **8**A and **8**B illustrate exemplary latch circuits for the exemplary latch circuit array according to FIG. 7;

[0019] FIGS. 9A and 9B illustrate exemplary clock cycles according to various aspects of the present disclosure;

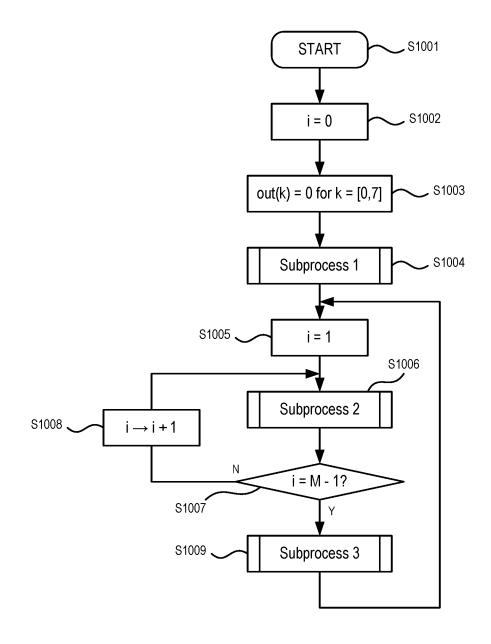

**[0020]** FIG. **10** illustrates another exemplary process flow for calculating the output in an ADC filter according to various aspects of the present disclosure;

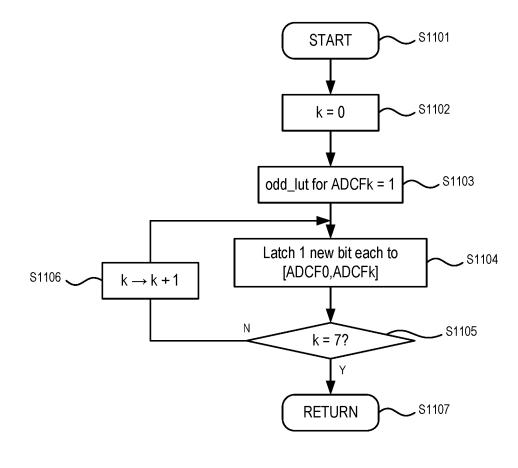

**[0021]** FIG. **11** illustrates an exemplary subprocess flow in the exemplary process flow according to FIG. **10**;

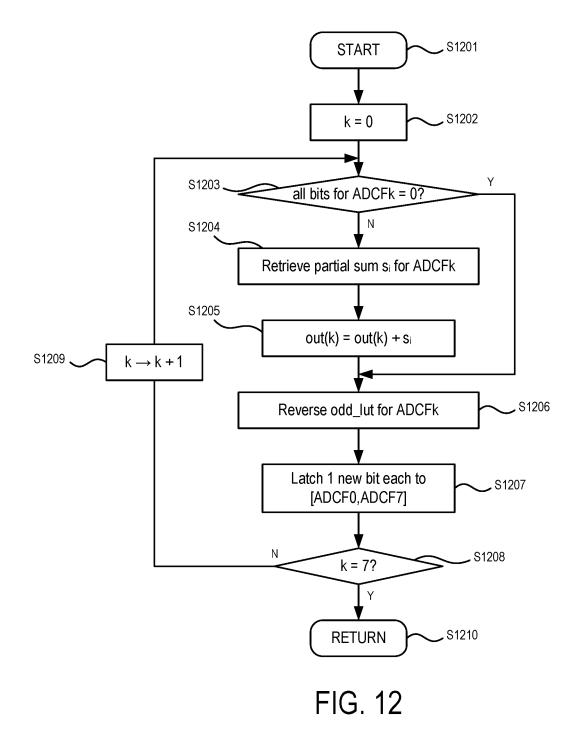

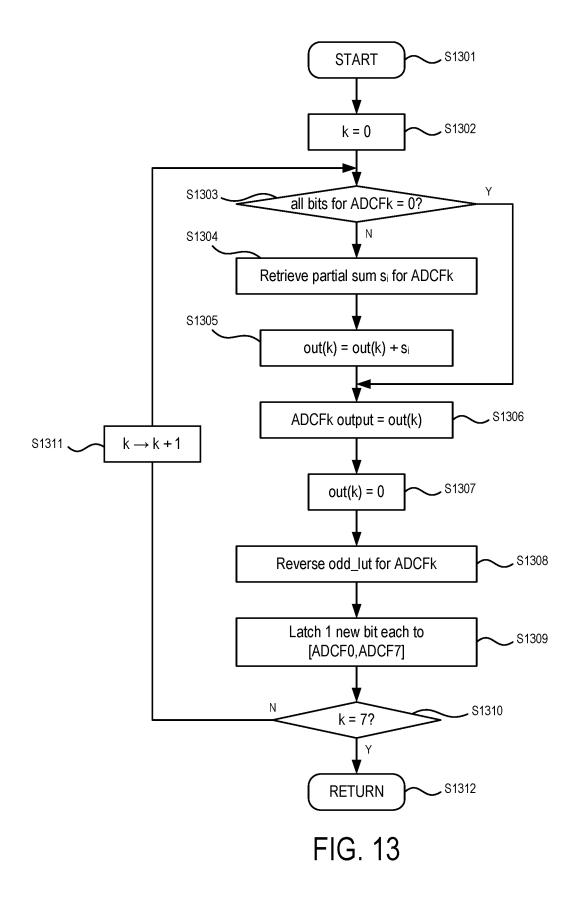

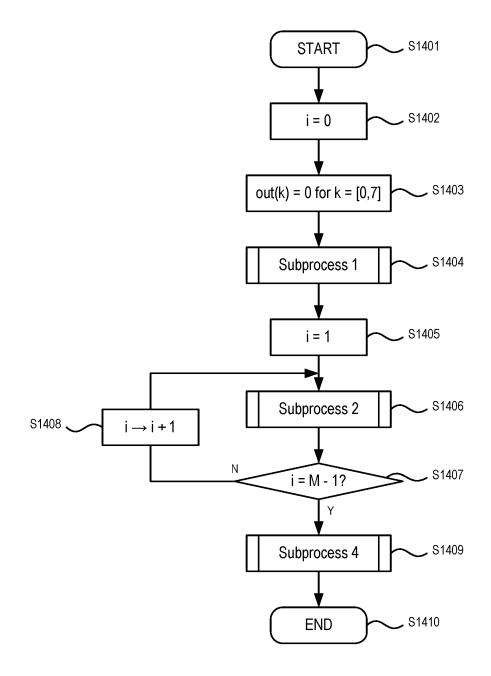

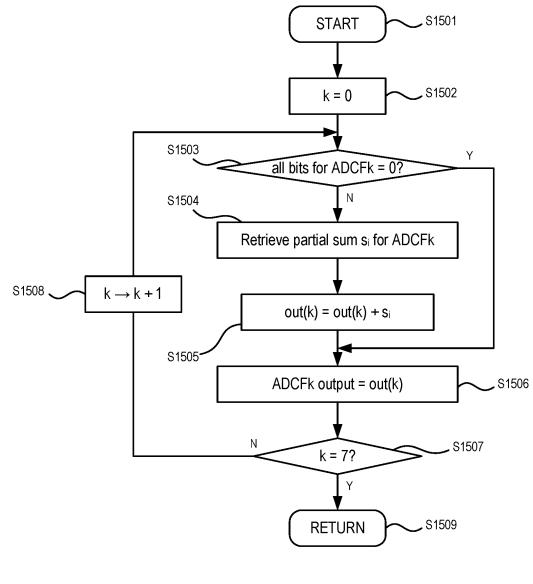

[0022] FIG. 12 illustrates another exemplary subprocess flow in the exemplary process flow according to FIG. 10; [0023] FIG. 13 illustrates another exemplary subprocess flow in the exemplary process flow according to FIG. 10; [0024] FIG. 14 illustrates another exemplary process flow according to various aspects of the present disclosure; and [0025] FIG. 15 illustrates an exemplary subprocess flow in the exemplary process flow according to FIG. 14.

#### DETAILED DESCRIPTION

**[0026]** In the following description, numerous details are set forth, such as circuit configurations, flowcharts, data tables, system configurations, and the like, in order to provide an understanding of one or more aspects of the present invention. It will be readily apparent to one skilled in the art that these specific details are merely exemplary and not intended to limit the scope of this application.

[0027] Moreover, while the present disclosure focuses mainly on examples in which the various circuits are used in image sensors, it will be understood that this is merely one example of an implementation. It will further be understood that the disclosed circuits can be used in any device in which there is a need to convert an analog signal to a digital signal; for example, an audio signal processing circuit, an industrial measurement and control circuit, a memory array, and so on. [0028] The systems, circuits, and methods disclosed herein may, for example, provide for a peak power reduction of approximately 50% and an area reduction of about 16% for a lookup table with a width of 6 bits. Depending on the particular semiconductor processing technology used in manufacturing, on the frequency of operation, on the width of the lookup table, etc., the benefits may be modified from this example.

[0029] [Image Sensor]

[0030] FIG. 1 illustrates an image sensor 100. The image sensor 10 includes a rectangular array 110 of M×N pixel circuits 111, where M and N are positive integers. The pixel circuits 111 are located at intersections where horizontal signal lines 112 and VSLs 113 cross one another. The horizontal signal lines 112 are operatively connected to a vertical driving circuit 120, also known as a "row scanning circuit," at a point outside of the pixel array 110, and carry signals from the vertical driving circuit 120 to a particular row of the pixel circuits 111. Pixels in a particular column output an analog signal corresponding to an amount of incident light to the VSL 113. For illustration purposes, only a subset of the pixel circuits 110 are actually shown in FIG. 1; however, in practice the image sensor 100 may have up to tens of millions of pixel circuits ("megapixels" or MP) or more.

[0031] The VSL 113 conducts the analog signal for a particular column to a column circuit 130, also known as a "signal processing circuit." A row selection switch may connect the VSL 113 to the column circuit 130. While FIG. 1 illustrates one VSL 113 for each column in the pixel array 110, the present disclosure is not so limited. For example, more than one VSL 113 may be provided for each column. Moreover, while FIG. 1 illustrates a single column circuit 130 for all columns, the image sensor 10 may utilize a plurality of column circuits 130. The analog electrical signal generated in the pixel circuit 111 is retrieved by the column circuit 130 and is then converted to a digital value. Such a conversion typically requires several circuit components

such as S/H circuits, ADCs, and timing and control circuits, with each circuit component serving a purpose in the conversion. For example, the purpose of the S/H circuit may be to sample the analog signals from different time phases of the photodiode operation, after which the analog signals may be converted to digital form by the ADC.

**[0032]** The ADC is preferably a sigma-delta ADC. As illustrated in FIG. **1**, the sigma-delta ADC includes a sigma-delta modulator **131** and a decoder filter **132**, also called an ADC filter or ADCF. Furthermore, while FIG. **1** illustrates a single ADC for a column of the pixel circuit **111**, other ADC architectures are possible within the context of the present disclosure. These architectures include multiple ADCs for each column, a single ADC for multiple columns, an ADC for a sub-region (e.g. K×L pixel circuits **111** where K and L are positive integers smaller than M and N, respectively), and the like.

**[0033]** The column circuit **130** may be capable of performing the method of correlated double sampling (CDS). CDS is capable of overcoming some pixel noise related issues by sampling each pixel circuit **111** twice. First, the reset voltage  $V_{reset}$  of a pixel circuit **111** is sampled. This may also be referred to as the P-phase value or cds value. Subsequently, the data voltage  $V_{data}$  of the pixel circuit **111** (that is, the voltage after the pixel circuit **111** has been exposed to light) is sampled. This may also be referred to as the D-phase value or light-exposed value. The reset value  $V_{reset}$  is then subtracted from the data value  $V_{data}$  to provide a value which reflects the amount of light falling on the pixel circuit **111**.

[0034] The column circuit 130 is controlled by a horizontal driving circuit 140, also known as a "column scanning circuit." Each of the vertical driving circuit 120, the column circuit 130, and the horizontal driving circuit 140 receive one or more clock signals from a controller 150. The controller 150 controls the timing and operation of various image sensor components such that analog signals from the pixel array 110, having been converted to digital signals in the column circuit 130, are output via an output circuit 160 for signal processing, storage, transmission, and the like.

[0035] FIG. 2 illustrates an exemplary pixel circuit 200 according to various aspects of the present disclosure. The pixel circuit 200 may be implemented in an image sensor such as the image sensor 100 described above; that is, the pixel circuit 200 may be the pixel circuit 110. As shown in FIG. 2, the pixel circuit 200 includes a photoelectric conversion device 201 (for example, a photodiode), a floating diffusion FD, a transfer transistor 202, a reset transistor 203, an amplification transistor 204, a selection transistor 205, and a VSL 206. The VSL 206 may be common to a plurality of pixel circuits within the same column. Alternatively, the VSL 206 may be shared among multiple columns. Gate electrodes of the transfer transistor 202, the reset transistor 203, and the selection transistor 205 receive signals TRG, RST, and SEL, respectively. These signals may, for example, be provided by the control or timing circuitry. Light falling on the photoelectric conversion device 201 is converted into an analog electrical signal that is output via the VSL 206.

**[0036]** While FIG. 2 illustrates a pixel circuit 200 having four transistors in a particular configuration, the present disclosure is not so limited and may apply to a pixel circuit having fewer or more transistors as well as other elements, such as capacitors, resistors, and the like. Moreover, while FIG. 1 illustrates the amplification transistor 215 disposed

between the selection transistor **216** and a power supply voltage  $V_{dd}$ , the selection transistor **216** may instead be disposed between the amplification transistor **216** and the power supply voltage  $V_{dd}$ . Additionally, the present disclosure may be extended to configurations where one or more transistors are shared among multiple photoelectric conversion devices.

[0037] FIG. 3 illustrates a first order current-mode sigmadelta modulator 300, which may be an example of the sigma-delta modulator 131 illustrated in FIG. 1. The modulator 300 receives the input analog signal from a pixel circuit, such as the pixel circuit 200, as an input current  $I_{in}$ , (represented as a current source 311) and uses a feedback circuit to convert the analog signal into a binary sequence  $V_{out}$  under the control of a clock.

[0038] The modulator 300 further includes a clocked comparator quantizer 301, a reference current source 312 that outputs a current  $I_{ref}$  a switch 321, and an integrating capacitor 331. The comparator 301 is configured to compare a voltage  $V_{int}$  on the capacitor 331 with a reference voltage  $V_{ref}$  and to output voltage  $V_{out}$  as a comparison result. The switch 321 is configured such that when an output of the comparator 301 is at a high level, the switch 321 is closed. Conversely, when the output of the comparator 301 is at a low level, the switch 321 is opened. To achieve this, the switch 321 may preferably be a transistor, such as a MOS transistor.

**[0039]** While FIG. **3** illustrates a first order current mode sigma-delta modulator, high order sigma-delta modulators (e.g. second or third order) may be used. Additionally, a voltage mode sigma-delta modulator, which receives an analog voltage as an input instead of an analog current, may be used without departing from the present disclosure. In any event, the output of the sigma-delta modulator **300** is output to an ADCF, such as the decoder filter **132**, which digitally filters the binary sequence  $V_{out}$  and down-samples the output to the desired multi-bit digital signal. Specifically, the ADCF calculates a weighted average of the binary signal using weights given by the impulse response of a filter.

**[0040]** FIG. **4** illustrates an example of an impulse response of an ADCF where the length of the impulse response is 350. As illustrated, every impulse response term has a positive value; however, an impulse response with both positive and negative terms may also be used. For a given impulse response, the output of the ADCF can be calculated according to the following expression (1):

$$y_n = y_{mL} = \sum_{k=0}^{L-1} h_k b_{k+mL}$$

(1)

**[0041]** Above, L represents the length of the ADCF impulse response plus lookup table size minus 1,  $h_k$  represents the impulse response,  $b_n$  represents the input to the ADCF (i.e., the output binary sequence of the sigma-delta modulator), and  $y_n$  is the output of the ADCF (i.e., the multi-bit output samples). For simplicity of illustration, expression (1) is written as a convolution sum by suitably replacing the impulse response of the filter by its mirror image. As illustrated in FIG. **4**, L=350.

**[0042]** Typically, this calculation is performed once for a segment of L binary samples from the sigma-delta modulator. After the output is computed,  $y_n$  (where n=m×L) repre-

sents a down-sample sequence which comprises multi-bit sample values. Because  $b_n$  is either 0 or 1 for any n, the calculation of  $y_n$  is equivalent to summing the impulse response values  $h_k$  which correspond to the 1s in the binary sequence  $b_n$ . To generate an output value using an ADCF of length L in a direct implementation of expression (1), the number of necessary summations is between 0 and L-1 depending on the number of is in the bit stream. The ADCF consumes maximum power when the binary sequence  $b_n$  is all 1s. In this case, the peak power consumption level for the ADCF is denoted as  $P_{max}$ . To significantly reduce the number of additions required to compute each output, and thereby to reduce the peak power consumption level, the sum in expression (1) may be broken up into a plurality of terms where each term represents a partial sum that can be retrieved by lookup tables.

#### First Example of an Output Computation Procedure

**[0043]** In one example, the sum in expression (1) may be broken up into a plurality of terms having equal size. In other words, an integer M may be chosen such that the sum in expression (1) is partitioned into M groups where each group includes N coefficients. In this case, the relationship  $M \times N=L$  holds. The filtering procedure of expression (1) may thus be rewritten according to the following expression (2):

$$y_n = y_{mL} = \sum_{i=0}^{M-1} S_i$$

(2)

**[0044]** Above,  $s_i$  is a partial sum represented by the following expression (3):

$$S_i \sum_{j=0}^{n-1} h_{iN+j} b_{iN+j+mL}$$

(3)

[0045] As noted above, each of the bit values  $b_n$  is binary; that is, either 0 or 1. Because there are N terms in expression (3), there are  $2^N$  possible output values for  $s_i$ , each of which correspond to one of the possible  $2^N$  bit patterns for the set  $\{b_{iN+mL}, b_{iN+mL+1}, \dots, b_{(i+1)N+mL-1}\}$ . Therefore, the set of all possible partial sum values  $s_i$  may be pre-calculated and stored in a table. In an implementation corresponding to an ADCF, the desired value s, may be retrieved from the table using the bit pattern as an address. Because the all-zero bit pattern always results in a zero value for s<sub>i</sub>, this entry may be excluded and it is only necessary to store  $2^{N}-1$  entries. [0046] With a set of lookup tables LUTi for all i from 0 to M-1, it is possible to partition a given binary input stream into blocks of bits which are then used as addresses to retrieve the value of the partial sum s, for each i. The retrieved partial sums may themselves be summed to produce the ADCF output. This requires M-1 additions to calculate an output value from the ADCF, which is substantially lower than the L-1 additions in the absence of partitioning, by a factor of approximately N. Therefore, the power consumption is approximately  $(1/N) \times P_{max}$ .

**[0047]** This lookup table can be implemented by a combination of multiplexer (MUXs) and adders. For example, a

4

lookup table of 8:1 can be either 256 entries with 8-bit addresses, two 4:1 MUXs each having sixteen entries plus an additional adder, or four 2:1 MUXs each having four entries plus three additional adders. Each of the above are different implementations of an equivalent 8:1 lookup table with tradeoffs between the number of MUXs and the number of adders.