## (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 110517644 A (43)申请公布日 2019.11.29

(21)申请号 201810496008.X

(22)申请日 2018.05.22

(71)申请人 元太科技工业股份有限公司 地址 中国台湾新竹科学工业园区新竹市力 行一路3号

(72)发明人 蔡学宏 陈蔚宗 王裕霖 林柏辛

(74)专利代理机构 北京律诚同业知识产权代理 有限公司 11006

代理人 梁挥 祁建国

(51) Int.CI.

**G09G** 3/34(2006.01)

权利要求书1页 说明书5页 附图3页

#### (54)发明名称

可抑制电磁干扰的显示装置及显示驱动电 路

#### (57)摘要

本发明涉及一种可抑制电磁干扰的显示装置及显示驱动电路。显示装置包括基板、主动阵列、显示驱动器以及薄膜晶体管(Thin-Film Transistor,TFT)调节电路。主动阵列设置于基板上,并包括多条数据线、多条闸极线以及多个像素,其中数据线纵横交错于闸极线,像素耦接于数据线与闸极线的交错处。显示驱动器设置于基板上,其用以回应调节后序列数据时脉信号产生用以驱动数据线及/或闸极线的信号。薄膜晶体管调节电路设置于基板上并耦接显示驱动器。薄膜晶体管调节电路包括一或多个薄膜晶体管,其用以回应预设闸极偏压衰减序列数据时脉信号。不驱动器提供调节后序列数据时脉信号。

CN 110517644 A

1.一种显示装置,其特征在于,包括:

#### 基板:

主动阵列,设置于该基板上,该主动阵列包括多条数据线、多条闸极线以及多个像素, 该些数据线纵横交错于该些闸极线,该些像素耦接于该些数据线与该些闸极线的交错处;

显示驱动器,设置于该基板上,该显示驱动器用以回应调节后序列数据时脉信号,产生用以驱动该些数据线及/或该些闸极线的信号;以及

薄膜晶体管调节电路,设置于该基板上并耦接该显示驱动器,该薄膜晶体管调节电路包括至少一个薄膜晶体管,并用以回应预设闸极偏压衰减序列数据时脉信号的振幅,以对该显示驱动器提供该调节后序列数据时脉信号。

- 2.如权利要求1所述的显示装置,其特征在于,该薄膜晶体管调节电路包括多个并联设置的薄膜晶体管,各该薄膜晶体管接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

- 3.如权利要求1所述的显示装置,其特征在于,该薄膜晶体管调节电路包括多个串联设置的薄膜晶体管以形成薄膜晶体管串,该薄膜晶体管串接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

- 4.如权利要求1所述的显示装置,其特征在于,该薄膜晶体管调节电路由单一个该薄膜晶体管实现,该薄膜晶体管接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

- 5. 如权利要求1所述的显示装置,其特征在于,还包括:

印刷电路板, 耦接该薄膜晶体管调节电路, 该印刷电路板用以对该薄膜晶体管调节电路提供该序列数据时脉信号。

6. 如权利要求1所述的显示装置,其特征在于,还包括:

电子墨水层,叠于该主动阵列之上。

7.一种显示驱动电路,用于驱动显示装置的主动阵列,其特征在于,包括:

显示驱动器,设置于基板上,该显示驱动器用以回应调节后序列数据时脉信号,产生用以驱动该主动阵列的信号;以及

薄膜晶体管调节电路,设置于该基板上并耦接该显示驱动器,该薄膜晶体管调节电路包括至少一个薄膜晶体管,并用以回应预设闸极偏压衰减序列数据时脉信号的振幅,以对该显示驱动器提供该调节后序列数据时脉信号。

- 8. 如权利要求7所述的显示驱动电路,其特征在于,该薄膜晶体管调节电路包括多个并 联设置的薄膜晶体管,各该薄膜晶体管接于该序列数据时脉信号以及该调节后序列数据时 脉信号之间,并受控于该预设闸极偏压。

- 9. 如权利要求7所述的显示驱动电路,其特征在于,该薄膜晶体管调节电路包括多个串 联设置的薄膜晶体管以形成薄膜晶体管串,该薄膜晶体管串接于该序列数据时脉信号以及 该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

- 10.如权利要求7所述的显示驱动电路,其特征在于,该薄膜晶体管调节电路由单一个该薄膜晶体管实现,该薄膜晶体管接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

# 可抑制电磁干扰的显示装置及显示驱动电路

#### 技术领域

[0001] 本发明涉及显示装置领域,且特别是关于一种可抑制电磁干扰(Electromagnetic Interference, EMI)的显示装置及显示驱动电路。

### 背景技术

[0002] 电磁干扰 (Electromagnetic Interference, EMI) 指的是电子信号的电磁能量对周遭的元件、装置、设备、以及生物组织产生的影响。严重的电磁干扰可能导致电子装置故障,甚至危害使用者的身体健康。目前国际对于电子产品的电磁干扰现象日渐重视,并要求电子产品在上市前须符合一定的抗电磁干扰标准。

[0003] 以显示装置为例,显示装置须通过电磁干扰测试才可上市贩售。然而,随着显示装置的分辨率需求越来越高,显示驱动器传送数据信号及扫描信号的传输速率也必须跟着提升,导致显示装置的电磁干扰现象越趋严重。有鉴于此,有需要提出一种改良的显示技术,以降低显示装置的电磁干扰。

#### 发明内容

[0004] 为了解决上述技术问题,本发明目的在于提供一种显示装置及显示驱动电路,可通过适当地衰减提供给显示驱动器的序列数据时脉信号(Serial DataClock,SDCLK),有效降低显示装置的电磁干扰,让显示装置可通过电磁干扰测试。

[0005] 具体地说,本发明公开了一种显示装置,其中包括:

[0006] 基板:

[0007] 主动阵列,设置于该基板上,该主动阵列包括多条数据线、多条闸极线以及多个像素,该些数据线纵横交错于该些闸极线,该些像素耦接于该些数据线与该些闸极线的交错处;

[0008] 显示驱动器,设置于该基板上,该显示驱动器用以回应调节后序列数据时脉信号, 产生用以驱动该些数据线及/或该些闸极线的信号;以及

[0009] 薄膜晶体管调节电路,设置于该基板上并耦接该显示驱动器,该薄膜晶体管调节电路包括至少一个薄膜晶体管,并用以回应预设闸极偏压衰减序列数据时脉信号的振幅,以对该显示驱动器提供该调节后序列数据时脉信号。

[0010] 该显示装置,其中该薄膜晶体管调节电路包括多个并联设置的薄膜晶体管,各该薄膜晶体管接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

[0011] 该显示装置,其中该薄膜晶体管调节电路包括多个串联设置的薄膜晶体管以形成薄膜晶体管串,该薄膜晶体管串接于该序列数据时脉信号以及该调节后序列数据时脉信号 之间,并受控于该预设闸极偏压。

[0012] 该显示装置,其中该薄膜晶体管调节电路由单一个该薄膜晶体管实现,该薄膜晶体管接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极

偏压。

[0013] 该显示装置,其中还包括:

[0014] 印刷电路板, 耦接该薄膜晶体管调节电路, 该印刷电路板用以对该薄膜晶体管调节电路提供该序列数据时脉信号。

[0015] 该显示装置,其中还包括:

[0016] 电子墨水层,叠于该主动阵列之上。

[0017] 本发明还公开了一种显示驱动电路,用于驱动显示装置的主动阵列,其中包括:

[0018] 显示驱动器,设置于基板上,该显示驱动器用以回应调节后序列数据时脉信号,产生用以驱动该主动阵列的信号;以及

[0019] 薄膜晶体管调节电路,设置于该基板上并耦接该显示驱动器,该薄膜晶体管调节电路包括至少一个薄膜晶体管,并用以回应预设闸极偏压衰减序列数据时脉信号的振幅,以对该显示驱动器提供该调节后序列数据时脉信号。

[0020] 该显示驱动电路,其中该薄膜晶体管调节电路包括多个并联设置的薄膜晶体管,各该薄膜晶体管接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

[0021] 该显示驱动电路,其中该薄膜晶体管调节电路包括多个串联设置的薄膜晶体管以形成薄膜晶体管串,该薄膜晶体管串接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

[0022] 该显示驱动电路,其中该薄膜晶体管调节电路由单一个该薄膜晶体管实现,该薄膜晶体管接于该序列数据时脉信号以及该调节后序列数据时脉信号之间,并受控于该预设闸极偏压。

### 附图说明

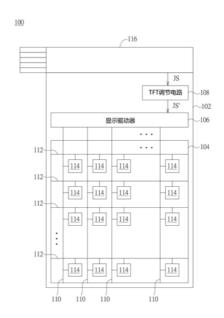

[0023] 图1为根据本发明一实施例的显示装置的框图:

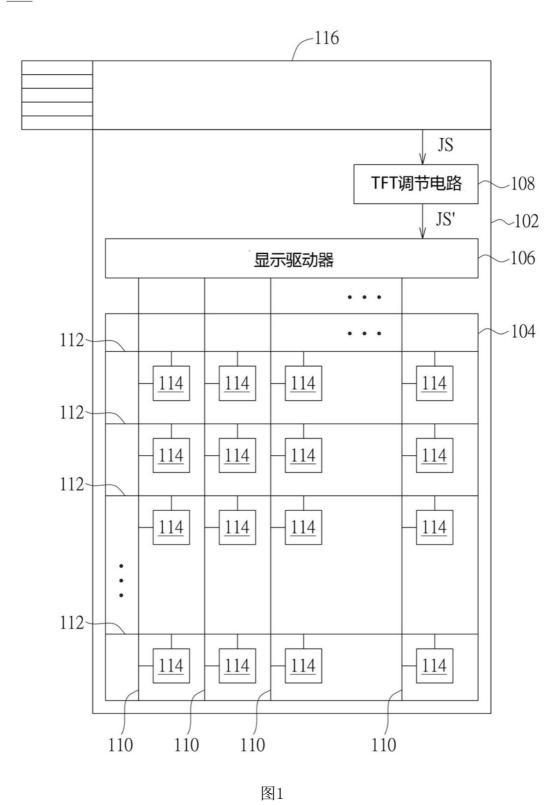

[0024] 图2为依据本发明一实施例的薄膜晶体管调节电路的电路图;

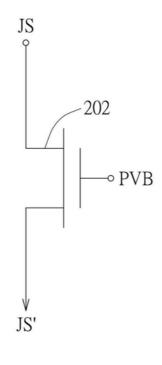

[0025] 图3为依据本发明另一实施例的薄膜晶体管调节电路的电路图;

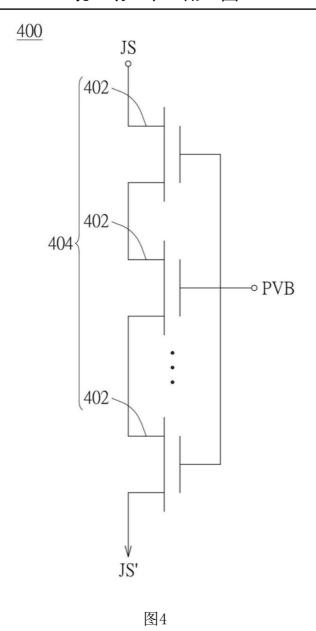

[0026] 图4为依据本发明又一实施例的薄膜晶体管调节电路的电路图:

[0027] 图5为根据本发明一实施例的显示装置的剖面图。

[0028] 符号说明:

[0029] 100、500:显示装置;

102:基板;

[0030] 104: 主动阵列:

106:显示驱动器:

[0031] 108、200、300、400:薄膜晶体管调节电路:

110:数据线;

[0032] 112:闸极线;

114:像素:

[0033] 116:印刷电路板:

JS:序列数据时脉信号;

[0034] JS':调节后序列数据时脉信号;

202、302、402:薄膜晶体管;

[0035] PVB:预设闸极偏压;

502:电子墨水层:

[0036] 506:电子墨水单元。

# 具体实施方式

[0037] 为让本发明的上述特征和效果能阐述的更明确易懂,下文特举实施例,并配合说明书附图作详细说明如下。

[0038] 图1为根据本发明一实施例的显示装置100的框图。显示装置100可以是任何类型的显示器,其主要包括基板102、主动阵列104、显示驱动器106以及薄膜晶体管(Thin-Film Transistor,TFT)调节电路108,显示装置100还可包括印刷电路板116。

[0039] 主动阵列104设置于基板102上,并包括多条数据线110、多条闸极线112以及多个像素114。数据线110纵横交错于闸极线112,其中像素114耦接于数据线110与闸极线112的交错处,以形成配置于基板102的显示区的像素阵列。

[0040] 显示驱动器106设置于基板102上,其用以回应调节后序列数据时脉信号JS'产生用以驱动数据线110及/或闸极线112的信号。显示驱动器106可以是一数据驱动器 (data driver)、一闸极驱动器 (gate driver)、或两者的结合。虽然图1绘示显示驱动器106耦接数据线110而作为数据驱动器,但应注意显示驱动器106亦可耦接闸极线112而作为闸极驱动器,或是同时耦接数据线110以及闸极线112而作为两者共同的驱动器。相较于主动阵列104,显示驱动器106设置在基板102上被遮蔽的非显示区。

[0041] 调节后序列数据时脉信号JS'是序列数据时脉信号(Serial Data Clock,SDCLK) JS衰减后的结果。调节后序列数据时脉信号JS'可透过薄膜晶体管调节电路108来产生。如第1图所示,薄膜晶体管调节电路108设置于基板102上并耦接显示驱动器106,例如设置于基板102上的非显示区。薄膜晶体管调节电路108可包括受控于预设闸极偏压的一或多个薄膜晶体管。薄膜晶体管调节电路108可回应预设闸极偏压对序列数据时脉信号JS的振幅作衰减,以对显示驱动器106提供调节后序列数据时脉信号JS'。薄膜晶体管调节电路108中的薄膜晶体管可例如与主动阵列104于同一制程中制作完成。关于薄膜晶体管调节电路108的电路细节将配合第2、3、4图作描述。

[0042] 调节后序列数据时脉信号JS'/序列数据时脉信号JS决定了显示驱动器106的工作时脉。显示驱动器106可根据调节后序列数据时脉信号JS'产生用以驱动数据线110的数据信号及/或用以驱动闸极线112的闸极信号。

[0043] 透过上述配置,可有效抑制显示装置100中的电磁干扰效应。进一步说,研究发现来自显示信号源(未绘示于图中)的序列数据时脉信号JS往往是一高频信号(例如,频率约在50MHz),若将其直接提供给显示驱动器106作为工作时脉,序列数据时脉信号JS将成为电磁干扰的主要来源之一。由于电磁干扰与电子信号的振幅以及频率有高度的正相关,故通过适当地衰减序列数据时脉信号JS的振幅,再将衰减后的结果(即,调节后序列数据时脉信号JS')提供给显示驱动器106作使用,可有效降低显示装置100的电磁干扰。

[0044] 根据本发明的一方面,显示驱动器106以及薄膜晶体管调节电路108可视为设置于显示装置100的基板102上的一显示驱动电路。在一实施例中,显示驱动器106可以是一芯片,而薄膜晶体管调节电路108可耦接至显示驱动器106中原本用以接收序列数据时脉信号JS的芯片脚位。

[0045] 印刷电路板116耦接薄膜晶体管调节电路108。印刷电路板116可对薄膜晶体管调节电路108提供序列数据时脉信号JS。印刷电路板可以是一柔性印刷电路(flexible printed circuit,FPC)板,其作为基板102上电子元件与外部显示信号源之间的信号传输界面。

[0046] 根据本发明实施例,薄膜晶体管调节电路108可由一或多个薄膜晶体管来实现。所述之一或多个薄膜晶体管的闸极可回应一预设闸极偏压而呈现一导通电阻(RON),由此将接收到的序列数据时脉信号JS适当地衰减为调节后序列数据时脉信号JS'。

[0047] 以下将配合第2、3、4图说明薄膜晶体管调节电路的不同实施例。但应注意该等实施例并非穷举性或限制性的,在一些应用中,可允许适当地修饰及/或结合该等实施例。

[0048] 图2为依据本发明一实施例的薄膜晶体管调节电路200的电路图。在此实施例中,薄膜晶体管调节电路200包括单一个薄膜晶体管202。薄膜晶体管202接于序列数据时脉信号JS以及调节后序列数据时脉信号JS'之间,并受控于预设闸极偏压PVB。举例来说,薄膜晶体管202的一端(如漏极/源极)可耦接至印刷电路板116以接收序列数据时脉信号JS,另一端(如源极/漏极)则是耦接至显示驱动器106以对其提供调节后序列数据时脉信号JS'。

[0049] 预设闸极偏压PVB的大小可被规划成可让薄膜晶体管202呈现一导通电阻。因此,相较于序列数据时脉信号JS,调节后序列数据时脉信号JS'的振幅衰减。调节后序列数据时脉信号JS'的振幅衰减程度可取决于显示驱动器106的芯片判定电压。举例来说,调节后序列数据时脉信号JS'的振幅衰减程度可被要求可使调节后序列数据时脉信号JS'的衰减后位准仍可被显示驱动器106识别,且位准变换特征与调节前的序列数据时脉信号JS仍维持一致。换言之,薄膜晶体管调节电路200并不会改变显示驱动器106的显示操作特征。

[0050] 图3绘示依据本发明另一实施例的薄膜晶体管调节电路300的电路图。在此实施例中,薄膜晶体管调节电路300包括多个并联设置的薄膜晶体管302,且各个薄膜晶体管302可接于序列数据时脉信号JS以及调节后序列数据时脉信号JS'之间,并受控于预设闸极偏压PVB。

[0051] 举例来说,各个薄膜晶体管302的其中一端(如漏极/源极)可耦接至印刷电路板116以接收序列数据时脉信号JS,另一端(如源极/漏极)则是耦接至显示驱动器106以对显示驱动器106提供调节后序列数据时脉信号JS'。预设闸极偏压PVB施加于该等薄膜晶体管302的控制端(如闸极),以控制薄膜晶体管调节电路300的等效导通电阻。

[0052] 图4为依据本发明又一实施例的薄膜晶体管调节电路400的电路图。在此实施例中,薄膜晶体管调节电路400包括多个薄膜晶体管402,该等薄膜晶体管402为串联设置以形成薄膜晶体管串404。薄膜晶体管串404接于序列数据时脉信号JS以及调节后序列数据时脉信号JS"之间,并受控于预设闸极偏压PVB。

[0053] 举例来说,薄膜晶体管串404中的首、尾两个薄膜晶体管402可分别耦接至印刷电路板116以及显示驱动器106,以自印刷电路板116接收序列数据时脉信号JS,并对显示驱动器106输出调节后序列数据时脉信号JS'。预设闸极偏压PVB可施加于该等薄膜晶体管402的控制端(如闸极),以控制薄膜晶体管串404的等效导通电阻。

[0054] 图5根据本发明一实施例的显示装置500的剖面图。显示装置500的配置如同第1图中的显示装置100,但还包括电子墨水层502以作为一电子纸显示器。电子墨水层502可叠于主动阵列104之上。电子墨水层502包括多个电子墨水单元506。每个电子墨水单元506可具有双稳态/多稳态特性,使得影像在写入后能够持续保留。举例来说,电子墨水单元506可由具有带电粒子的液体来实现。透过对电子墨水单元506施加电场,可使带电粒子在液体中移动。带电粒子可具有不同的色彩,例如黑色及白色。因此,通过驱动主动阵列104中的电极以控制具有欲显示色彩的带电粒子上浮,可使电子墨水层502显示欲呈现的影像。

[0055] 根据本发明实施例,可提出一种可抑制电磁干扰的显示装置及显示驱动电路。研究发现,传统上使用于显示装置中的序列数据时脉信号为形成电磁干扰的主要来源之一。因此,通过适当地衰减提供给显示驱动器的序列数据时脉信号,可以有效降低电磁干扰,让显示装置可通过电磁干扰测试。此外,在本发明实施例中,序列数据时脉信号的衰减是透过薄膜晶体管元件来实现。薄膜晶体管可设置于显示装置的基板上并当作可变电阻以减弱序列数据时脉信号的强度。透过此方式,当显示装置无法通过电磁干扰测试,开发者将不需重新设计电路板,而只需调整提供至薄膜晶体管的预设闸极偏压,即可改善电磁干扰问题。且因序列数据时脉信号的信号强度被适当地衰减,亦可减轻显示装置操作时的电力消耗。

100

<u>200</u>

图2

<u>300</u>

<u>500</u>

506 506 506 506

-502

图5