(19)

Europäisches Patentamt European Patent Office Office européen des brevets

# (11) **EP 4 230 974 A1**

**EUROPEAN PATENT APPLICATION** (12)(43) Date of publication: (51) International Patent Classification (IPC): G01J 11/00 (2006.01) G01J 1/42<sup>(2006.01)</sup> 23.08.2023 Bulletin 2023/34 H01L 27/146 (2006.01) H01L 31/10 (2006.01) H01L 31/107 (2006.01) H01L 27/144 (2006.01) (21) Application number: 23177334.2 H01L 31/02 (2006.01) H04N 25/79 (2023.01) G01J 1/44<sup>(2006.01)</sup> (22) Date of filing: 24.01.2019 (52) Cooperative Patent Classification (CPC): G01J 1/44: G01J 11/00: H01L 27/14609: H01L 27/14634; H01L 27/14636; H01L 31/02027; H04N 25/79; G01J 2001/4466 (84) Designated Contracting States: TAMURA, Yusei AL AT BE BG CH CY CZ DE DK EE ES FI FR GB Shizuoka, 435-8558 (JP) GR HR HU IE IS IT LI LT LU LV MC MK MT NL NO MAKINO, Kenji PL PT RO RS SE SI SK SM TR Shizuoka, 435-8558 (JP) BABA, Takashi (30) Priority: 26.01.2018 JP 2018011824 Shizuoka, 435-8558 (JP) YAMAMOTO, Koei (62) Document number(s) of the earlier application(s) in Shizuoka, 435-8558 (JP) accordance with Art. 76 EPC: 19744603.2 / 3 745 102 (74) Representative: EIP Fairfax House (71) Applicant: Hamamatsu Photonics K.K. 15 Fulwood Place Hamamatsu-shi, Shizuoka 435-8558 (JP) London WC1V 6HU (GB) (72) Inventors: Remarks: FUJITA, Takuya This application was filed on 05-06-2023 as a Shizuoka, 435-8558 (JP) divisional application to the application mentioned under INID code 62.

# (54) **PHOTODETECTOR DEVICE**

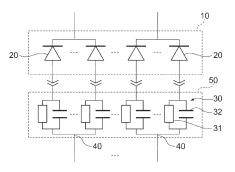

(57)A photodetector device includes an avalanche photodiode array substrate 10 formed from compound semiconductor. A plurality of avalanche photodiodes 20 arranged to operate in a Geiger mode are two-dimensionally arranged on the avalanche photodiode array substrate 10. A circuit substrate 50 includes a plurality of output units 30 which are connected to each other in parallel to form at least one channel 40. Each of the output units 30 includes a passive quenching element 31 and a capacitative element 32. The passive quenching element 31 is connected in series to at least one of the plurality of avalanche photodiodes 20. The capacitative element 32 is connected in series to at least one of the avalanche photodiodes 20 and is connected in parallel to the passive quenching element 31.

Fig.7

EP 4 230 974 A1

30

35

### Description

### **Technical Field**

**[0001]** The present invention relates to a photodetector device.

### **Background Art**

**[0002]** A photodetector device in which a plurality of avalanche photodiodes are two-dimensionally arranged is known (for example, Patent Literature 1). The plurality of avalanche photodiodes is arranged to operate in a Geiger mode. The plurality of avalanche photodiodes are formed on a semiconductor substrate formed from compound semiconductor.

### **Citation List**

### Patent Literature

[0003] Patent Literature 1: Japanese Unexamined Patent Publication No. 2012-531753

### **Summary of Invention**

### **Technical Problem**

[0004] In a case where a plurality of avalanche photodiodes formed on the semiconductor substrate formed from the compound semiconductor is arranged to operate in the Geiger mode, a dark pulse and an after pulse increase in correspondence with a temperature variation. When a noise increases due to the dark pulse and the after pulse, there is a concern that a signal from the avalanche photodiodes may not be appropriately detected. [0005] There is known a configuration in which passive guenching elements are arranged in series to the avalanche photodiodes to guench avalanche multiplication in a case where the avalanche photodiodes is arranged to operate in the Geiger mode. Whether or not an avalanche multiplication process that occurs inside the avalanche photodiodes connected to the passive quenching element is appropriately quenched is determined depending on a resistance value of the passive quenching element. When the resistance value of the quenching elements is not sufficient, there is a concern that appropriate quenching is not realized due to occurrence of a latching current or the like. It is necessary to select a sufficient resistance value of the quenching elements for appropriate quenching.

**[0006]** As the resistance value of the passive quenching elements is larger, time necessary for quenching of the avalanche photodiodes which are connected to the passive quenching elements in series increases. As the time necessary for the quenching increases, dead time for which light cannot be detected by the avalanche photodiodes increases. As described above, there is a demand for a circuit design including passive quenching elements having an optimal resistance value to make appropriate quenching and reduction of the dead time compatible with each other and to secure photodetection sensitivity and photodetection time resolution.

**[0007]** Since a parasitic capacitance in the passive quenching elements also has an influence on a pulse signal, and thus removal of the parasitic capacitance is also demanded. It is also demanded to improve a peak

- 10 value of the pulse signal to further improve the photodetection time resolution. It is very difficult to design a device in which the plurality of avalanche photodiodes formed on the semiconductor substrate formed from the compound semiconductor are arranged to operate in the Gei-

- <sup>15</sup> ger mode so as to satisfy all of the above-described desired conditions.

**[0008]** An object of an aspect of the invention is to provide a photodetector device in which photodetection sensitivity and an improvement of photodetection time res-

20 olution are compatible in a configuration in which a plurality of avalanche photodiodes are formed on a semiconductor substrate formed from compound semiconductor.

### 25 Solution to Problem

**[0009]** According to an aspect of the invention, there is provided a photodetector device including an avalanche photodiode array substrate and a circuit substrate. The avalanche photodiode array substrate is formed from compound semiconductor. The avalanche photodiode array substrate is mounted on the circuit substrate. A plurality of avalanche photodiodes are two-dimensionally arranged in the avalanche photodiode array substrate. The plurality of avalanche photodiode is ar-

ranged to operate in a Geiger mode. The circuit substrate includes a plurality of output units connected to each other in parallel. The plurality of output units form at least one channel. Each of the output units includes a passive

quenching element and a capacitative element. The passive quenching element is connected in series to at least one of the plurality of avalanche photodiodes. The capacitative element is connected in series to at least one of the avalanche photodiodes, and is connected in parallel

to the passive quenching element

to the passive quenching element. [0010] In this aspect, the plurality of output units including the passive quenching element and the capacitative element are provided in the circuit substrate different from the avalanche photodiode array substrate. Accord-50 ing to this, a space capable of forming the plurality of output units can be further expanded in comparison to a case where the plurality of output units are arranged in the avalanche photodiode array substrate. When the output units are provided in the circuit substrate separate 55 from the avalanche photodiode array substrate, a parasitic capacitance that occurs between a configuration of the avalanche photodiodes and the output units can be reduced. In this case, a manufacturing process different

15

from that of the avalanche diode array substrate can also be used. Accordingly, the design of the plurality of output units becomes easy. The capacitative element provided in the photodetector device is connected in series to at least one of the avalanche photodiodes and is connected in parallel to the passive quenching element. According to this, a peak value of a pulse signal transmitted from the avalanche photodiode that is connected in series to the capacitative element can be improved due to the electrostatic capacitance of the capacitative element. Accordingly, a pulse signal transmitted from the plurality of avalanche photodiodes is easily detected, and light detection resolution can be further improved.

**[0011]** In the aspect, the passive quenching element may be formed by a first polysilicon layer provided in the circuit substrate. The capacitative element may be formed by a second polysilicon layer provided in the circuit substrate, a dielectric layer stacked on the second polysilicon layer, and a third polysilicon layer stacked on the dielectric layer. The first polysilicon layer may be formed at the same height as in the second polysilicon layer or the third polysilicon layer in a thickness direction of the circuit substrate. In this case, the plurality of output units can be formed by a simple manufacturing process.

### Advantageous Effects of Invention

**[0012]** According to the aspect of the invention, there is provided a photodetector device capable of securing photodetection accuracy with a simple design in a configuration in which a plurality of avalanche photodiodes are formed on a semiconductor substrate formed from compound semiconductor.

# **Brief Description of Drawings**

# [0013]

FIG. 1 is a perspective view of a photodetector device according to an embodiment.

FIG. 2 is a view illustrating a cross-sectional configuration of the photodetector device.

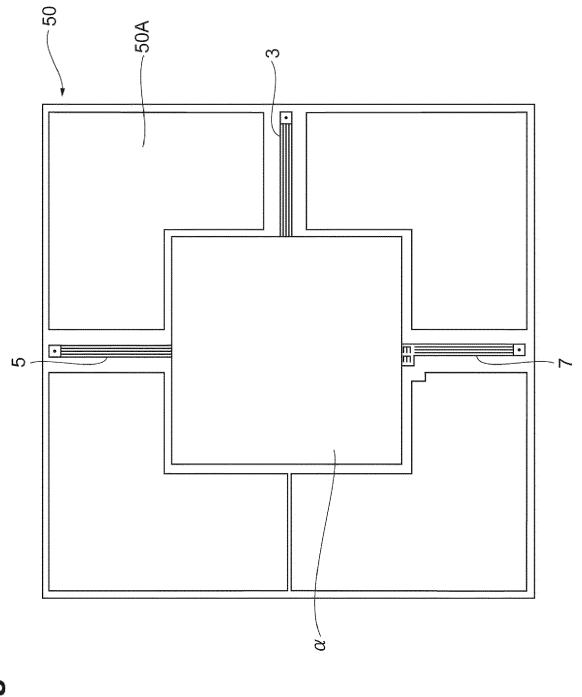

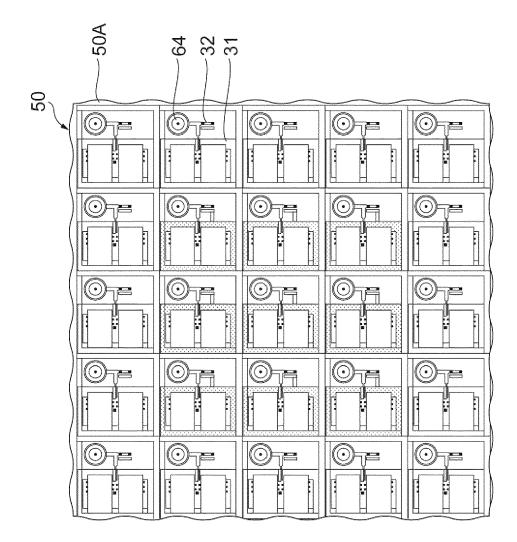

FIG. 3 is a plan view of a circuit substrate.

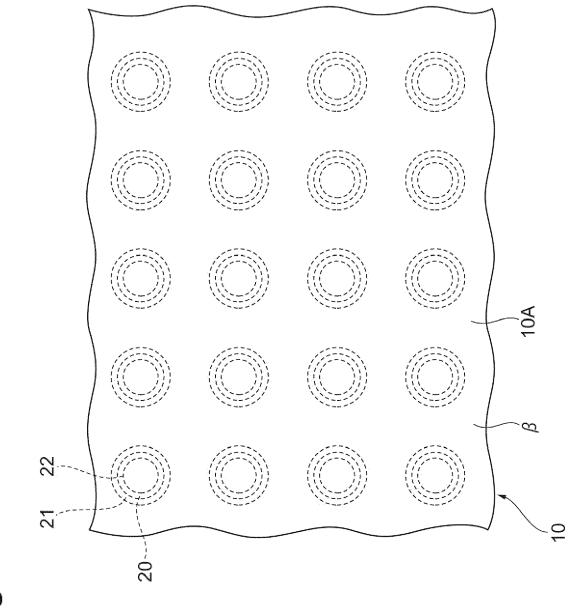

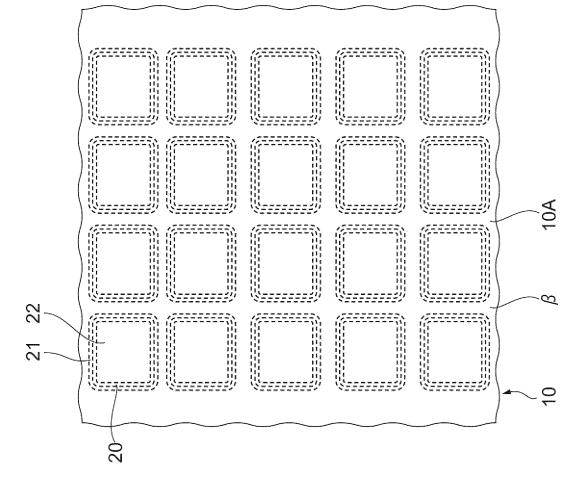

FIG. 4 is a plan view of a photodetection region of an avalanche photodiode array substrate.

FIG. 5 is a view illustrating a configuration of a circuit substrate.

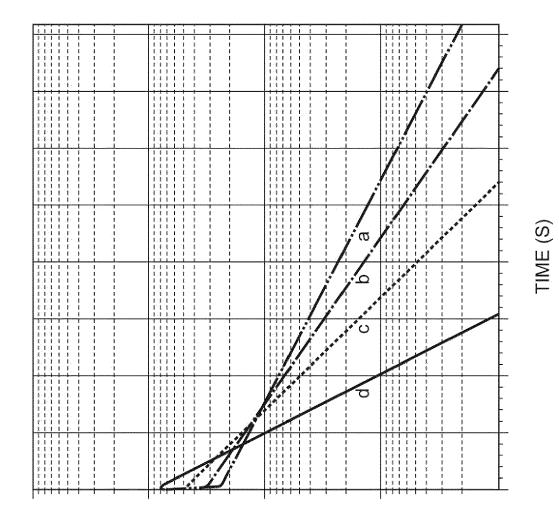

FIG. 6 is a view illustrating a circuit configuration capable of being used in the photodetector device.

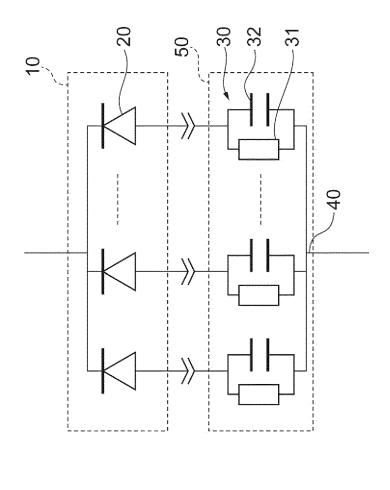

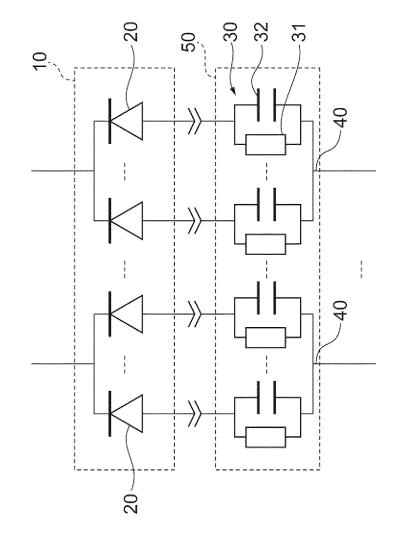

FIG. 7 is a view illustrating a circuit configuration capable of being used in a photodetector device according to a modification example of this embodiment.

FIG. 8 is a plan view of a mounting region of the circuit substrate.

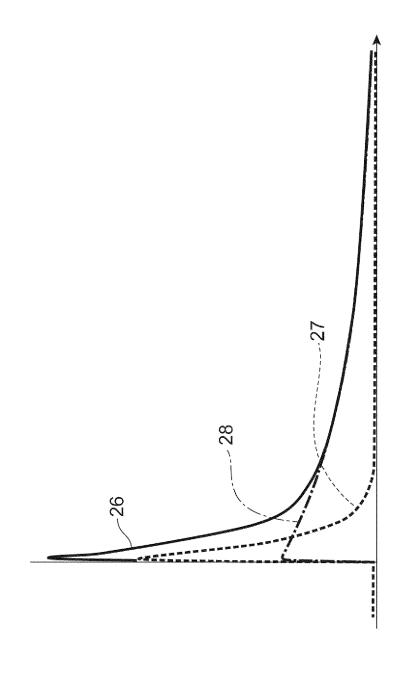

FIG. 9 is a view illustrating components of a pulse signal transmitted from an avalanche photodiode. FIG. 10 is a view illustrating characteristics of a recharge pulse.

FIG. 11 is a view illustrating characteristics of a fast pulse.

### 5 Description of Embodiments

**[0014]** Hereinafter, an embodiment of the invention will be described in detail with reference to the accompanying drawings. Note that, in description, the same reference

numeral will be given to the same elements or elements having the same function, and redundant description thereof will be omitted.

**[0015]** First, a whole configuration of a photodetector device according to this embodiment will be described

with reference to FIG. 1 to FIG. 8. FIG. 1 is a perspective view of the photodetector device according to this embodiment. FIG. 2 is a view illustrating a cross-sectional configuration of the photodetector device according to this embodiment. In FIG. 2, hatching is omitted to improve

visibility. FIG. 3 a plan view of a circuit substrate. FIG. 4 is a plan view illustrating a part of an avalanche photodiode array substrate. FIG. 6 is a view illustrating a circuit configuration capable of being used in the photodetector device according to this embodiment. FIG. 8 is a plan

view illustrating a part of the circuit substrate.

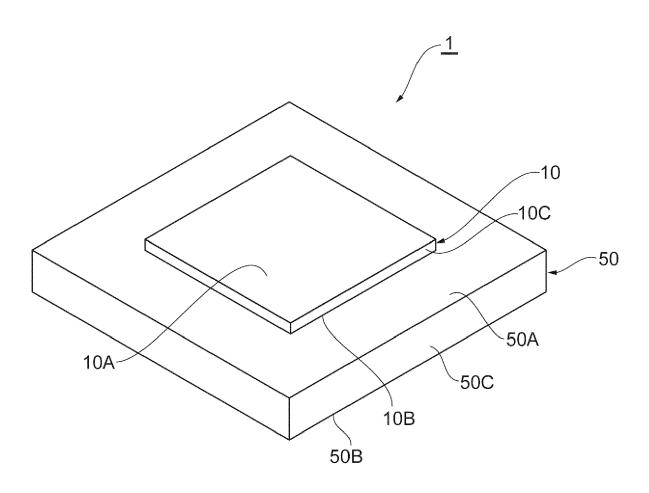

[0016] As illustrated in FIG. 1, a photodetector device 1 includes an avalanche photodiode array substrate 10 and a circuit substrate 50. Hereinafter, "avalanche photodiode" is referred to as "APD". "Avalanche photodiode

30 array substrate" is referred to as "APD array substrate". The circuit substrate 50 is disposed to face the APD array substrate 10. The APD array substrate 10 and the circuit substrate 50 have a rectangular shape in plan view.

[0017] The APD array substrate 10 includes a main surface 10A and a main surface 10B which are opposite to each other, and a side surface 10C. The circuit substrate 50 includes a main surface 50A and a main surface 50B which are opposite to each other, and a side surface 50C. The main surface 10B of the APD array substrate

40 10 faces the main surface 50A of the circuit substrate 50. A plan parallel to the respective main surfaces of the APD array substrate 10 and the circuit substrate 50 is an XYaxis plan, and a direction orthogonal to the respective main surface is a Z-axis direction.

<sup>45</sup> [0018] The side surface 50C of the circuit substrate 50 is located on an outer side in the XY-axis plane direction in comparison to the side surface 10C of the APD array substrate 10. That is, in plan view, an area of the circuit substrate 50 is greater than an area of the APD array substrate 10. The side surface 10C of the APD array substrate 10 and the side surface 50C of the circuit substrate 50 may be flush with each other. In this case, in plan view, an outer edge of the APD array substrate 10 and an outer edge of the circuit substrate 50 match each other.

**[0019]** A glass substrate may be disposed on the main surface 10A of the APD array substrate 10. The glass substrate and the APD array substrate 10 are optically

connected to each other by an optical adhesive. The glass substrate may be directly formed on the APD array substrate 10. The side surface 10C of the APD array substrate 10 and a side surface of the glass substrate may be flush with each other. In this case, in plan view, the outer edge of the APD array substrate 10 and the outer edge of the glass substrate match each other. In addition, the side surface 10C of the APD array substrate 10, the side surface 50C of the circuit substrate 50, and the side surface of the glass substrate may be flush with each other. In this case, in plan view, the outer edge of the date to the date surface 50C of the circuit substrate 50, and the side surface of the glass substrate may be flush with each other. In this case, in plan view, the outer edge of the APD array substrate 50, and the outer edge of the circuit substrate 50, and the outer edge of the glass substrate match each other.

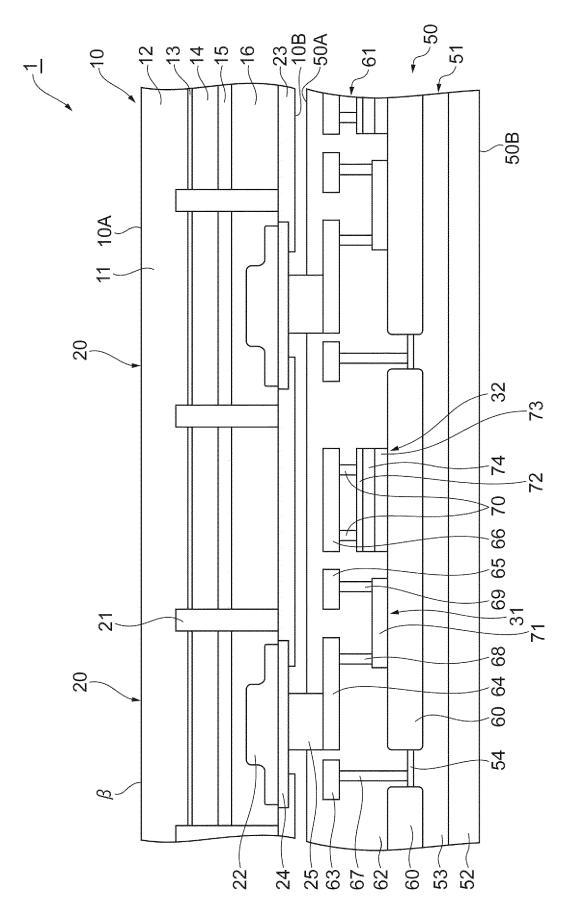

**[0020]** The APD array substrate 10 is mounted on the circuit substrate 50. As illustrated in FIG. 2, the APD array substrate 10 and the circuit substrate 50 are connected to each other by the bump electrode 25. Specifically, as illustrated in FIG. 3, the APD array substrate 10 is connected to the bump electrode 25 over a mounting region  $\alpha$  disposed at the center of the circuit substrate 50 when viewed from a thickness direction of the APD array substrate 10. In this embodiment, the mounting region  $\alpha$  has a rectangular shape.

**[0021]** The circuit substrate 50 includes a ground line 3, a cathode line 5, and an anode line 7 at the periphery of the mounting region  $\alpha$ . The ground line 3, the cathode line 5, and the anode line 7 extend from the mounting region  $\alpha$ . The ground line 3 is connected to a ground electrode 63 to be described later. The cathode line 5 is electrically connected to the APD array substrate 10 mounted in the mounting region  $\alpha$ , and can be used for application of a voltage to the APD array substrate 10. The anode line 7 is connected to metal layers 65 and 66 to be described later, and is used in read-out of a signal transmitted from the APD array substrate 10.

**[0022]** The APD array substrate 10 includes a plurality of APDs 20 which is arranged to operate in a Geiger mode. As illustrated in FIG. 4, the plurality of APDs 20 are two-dimensionally arranged in a photodetection region  $\beta$  of the semiconductor substrate 11 when viewed from the thickness direction of the APD array substrate 10. The photodetection region  $\beta$  has a rectangular shape, and overlaps the mounting region  $\alpha$  of the circuit substrate 50 when viewed from the thickness direction of the APD array substrate 10.

**[0023]** The APD array substrate 10 includes an N-type semiconductor substrate 11 formed from compound semiconductor. The semiconductor substrate 11 includes a substrate 12 formed from InP that forms the main surface 10A. A buffer layer 13 formed from InP, an absorption layer 14 formed from InGaAsP, an electric field relaxing layer 15 formed from InGaAsP, a multiplication layer 16 formed from InP are formed on the substrate 12 in this order from the main surface 10A side to the main surface 10B side. The absorption layer 14 may be formed from InGaAs, InGaAs, InAl-

GaAs, CdTe, HgCdTe, or the like.

**[0024]** As illustrated in FIG. 2 and FIG. 4, each of the APDs 20 is surrounded by an insulating portion 21 when viewed from the thickness direction of the APD array sub-

<sup>5</sup> strate 10. The APD 20 includes a P-type active area 22 that is formed by doping the multiplication layer 16 with impurities from the main surface 10B side. Examples of the doping impurities include zinc (Zn). For example, the insulating portion 21 is provided by forming a polyimide

<sup>10</sup> film in a trench formed through wet etching or dry etching. The active area 22 formed in a circular shape when viewed from the thickness direction, and the insulating portion 21 is formed in an annular shape along an edge of the active area 22. The insulating portion 21 reaches

<sup>15</sup> the substrate 12 from the main surface 10B side of the semiconductor substrate 11 in the thickness direction of the APD array substrate 10

**[0025]** FIG. 5 is a view illustrating a part of an avalanche photodiode array substrate capable of being used

<sup>20</sup> in photodetector device according to a modification example of this embodiment. As illustrated in FIG. 5, the active area 22 may be formed in an approximately rectangular shape when viewed from the thickness direction. Here, the approximately rectangular shape is a rectan-

<sup>25</sup> gular shape with rounded corners. According to this, concentration of an electric field to the corners of the active area 22 is suppressed. In this case, the insulating portion 21 is formed in an annular shape along an edge of the active area 22 having an approximately rectangular

<sup>30</sup> shape.

**[0026]** The APD array substrate 10 includes an insulating layer 23 and a plurality of electrode pads 24. The insulating layer 23 covers the semiconductor substrate 11 on the main surface 10B side. Each of the electrode pads 24 is formed on the semiconductor substrate 11 on the main surface 10B side for every APD 20, and is in contact with the active area 22. The electrode pad 24 is exposed from the insulating layer 23, and is connected to the circuit substrate 50 through the bump electrode 25.

40 [0027] As illustrated in FIG. 2, the circuit substrate 50 is connected to the APD array substrate 10 on the main surface 50A side through the bump electrode 25. The circuit substrate 50 includes a plurality of output unit 30. As illustrated in FIG. 6, the plurality of output units 30 are

<sup>45</sup> connected to each other in parallel, and forms one channel 40. Each of the plurality of output units 30 is connected in series to each of the APDs 20 provided in the APD array substrate 10. The output unit 30 includes a passive quenching element 31 and a capacitative element 32

<sup>50</sup> which are connected to each other in parallel. Any of the passive quenching element 31 and the capacitative element 32 is connected in series to the APD 20.

[0028] FIG. 7 is a view illustrating a circuit configuration capable of being used in a photodetector device according to a modification example of this embodiment. As illustrated in FIG. 7, a plurality of channels 40 may be formed in the circuit substrate 50. In this case, each of the channels 40 is formed by a plurality of output units

35

30 connected to each other in parallel. At least one of the plurality of channels 40 may be formed by the plurality of output units 30 connected to each other in parallel.

**[0029]** The circuit substrate 50 includes a silicon substrate 51, and a wiring layer 61 stacked on the silicon substrate 51. As illustrated in FIG. 2, the silicon substrate 51 includes a P<sup>+</sup> layer 52, a P<sup>-</sup> layer 53, and a P<sup>+</sup> layer 54 in this order from the main surface 50B side to the main surface 50A side. The P<sup>+</sup> layer 52 is provided by doping the P<sup>-</sup> layer 53 with impurities. The P<sup>+</sup> layer 54 is provided by doping the P<sup>-</sup> layer 53 with impurities. Examples of the doping impurities in the P<sup>-</sup> layer 53 include boron. For example, an oxide film layer 60 formed in an element isolation process by thermal oxidation is provided between the silicon substrate 51 and the wiring layer 61. The P<sup>+</sup> layer 54 is exposed from the oxide film layer 60, and is in contact with the wiring layer 61.

**[0030]** The wiring layer 61 includes an insulating layer 62, a ground electrode 63, an electrode pad 64, metal layers 65 and 66, vias 67, 68, 69, and 70, polysilicon layers 71, 72, and 73, and a dielectric layer 74. The ground electrode 63, the electrode pad 64, the metal layers 65 and 66, the vias 67, 68, 69, and 70, the polysilicon layers 71, 72, and 73, and the dielectric layer 74 are provided for every APD 20. The ground electrode 63, the electrode 63, the electrode pad 64, and the metal layers 65 and 66 are formed in the same layer. In other words, the ground electrode 63, the electrode pad 64, and the metal layers 65 and 66 are formed at the same height in the thickness direction of the circuit substrate 50.

**[0031]** For example, the insulating layer 62 is formed from SiO<sub>2</sub>. For example, the ground electrode 63, the electrode pad 64, and the metal layers 65 and 66 are formed from AI, AICu, AISiCu, or the like. The ground electrode 63, the electrode pad 64, and the metal layers 65 and 66 may be formed from the same material. For example, the vias 67, 68, 69, and 70 is formed from tungsten (W). For example, the dielectric layer 74 is formed from SiO<sub>2</sub> or Si<sub>3</sub>N<sub>4</sub>.

**[0032]** The wiring layer 61 is covered with the insulating layer 62. The P<sup>+</sup> layer 54 of the silicon substrate 51 is connected to the via 67 exposed from the insulating layer 62 of the wiring layer 61 to the silicon substrate 51 side. The P<sup>+</sup> layer 54 is connected to the ground electrode 63 through the via 67. The ground electrode 63 is disposed with respect to the electrode pad 64 and the metal layers 65 and 66 through the insulating layer 62 at an arrangement height of the ground electrode 63 in the thickness direction of the circuit substrate 50. The ground electrode 63 is not directly connected to the electrode pad 64 and the metal layers 65 and 66 and the directly connected to the electrode pad 64 and the metal layer 63 is not directly connected to the electrode pad 64 and the metal layers 65 and 66.

**[0033]** The electrode pad 64 is exposed from the insulating layer 62 and is connected to the APD 20 through the bump electrode 25. As illustrated in FIG. 8, a plurality of the electrode pads 64 are two-dimensionally arranged on the main surface 50A side. Each of the electrode pads 64 is connected to the polysilicon layer 71 through the via 68. The polysilicon layer 71 is connected to the metal

layer 65 through the via 69. The electrode pad 64 is disposed with respect to the metal layers 65 and 66 through the insulating layer 62 at an arrangement height of the electrode pad 64 in the thickness direction of the circuit

<sup>5</sup> substrate 50. The electrode pad 64 is not directly connected to the metal layers 65 and 66. The polysilicon layer 71 is included in a first polysilicon layer.

[0034] The polysilicon layer 71 constitutes the passive quenching element 31. According to the above-de scribed configuration, the passive quenching element 31 is connected in series to the APD 20 through the bump electrode 25, the electrode pad 64, and the via 68. That is, a pulse signal transmitted from the APD 20 is input to

the passive quenching element 31 through the bump

electrode 25, the electrode pad 64, and the via 68. The pulse signal input to the passive quenching element 31 is output from the channel 40 through the passive quenching element 31, the via 69 and the metal layer 65.

[0035] The electrode pad 64 is connected to the metal

layer 66 at the arrangement height of the electrode pad 64 in the thickness direction of the circuit substrate 50. The metal layer 66 is connected to the polysilicon layer 72 through the via 70. The polysilicon layer 72 is stacked on the dielectric layer 74. The dielectric layer 74 is

stacked on the polysilicon layer 73. The polysilicon layer

73 is connected to the metal layer 65 through a via (not illustrated). The polysilicon layer 71 and the polysilicon layer 73 are formed at the same height in the thickness direction of the circuit substrate 50. The polysilicon layer

30 71 and the polysilicon layer 72 may be formed at the same height in the thickness direction of the circuit substrate 50. The polysilicon layer 72 is included in a third polysilicon layer. The polysilicon layer 73 is included in a second polysilicon layer.

<sup>35</sup> [0036] The polysilicon layer 72, the dielectric layer 74, and the polysilicon layer 73 constitute the capacitative element 32. According to the above-described configuration, the capacitative element 32 is connected in series to the APD 20 through the bump electrode 25, the elec-

40 trode pad 64, and the via 68. That is, a pulse signal transmitted from the APD 20 is input to the polysilicon layer 72 of the capacitative element 32 through the bump electrode 25, the electrode pad 64 and the via 68. A pulse signal is output from the polysilicon layer 73 of the capa-

<sup>45</sup> citative element 32 in correspondence with input of the pulse signal to the polysilicon layer 72 of the capacitative element 32. The pulse signal output from the capacitative element 32 is output from the channel 40 through a via (not illustrated) and the metal layer 65.

<sup>50</sup> **[0037]** Both the passive quenching element 31 and the capacitative element 32 are electrically connected to the electrode pad 64 and the metal layer 65. Accordingly, the passive quenching element 31 and the capacitative element 32 are connected to each other in parallel.

<sup>55</sup> [0038] Next, an operational effect of the photodetector device 1 will be described with reference to FIG. 9 to FIG.

11. FIG. 9 illustrates a pulse signal output from the APD 20. As illustrated in FIG. 9, a pulse signal 26 from the

APD 20 is classified into a fast pulse 27 and a recharge pulse 28. The fast pulse 27 is a pulse component having a peak value of the pulse signal. The recharge pulse 28 is a component that is detected after detection of the fast pulse 27 and has a pulse width longer than that of the fast pulse 27.

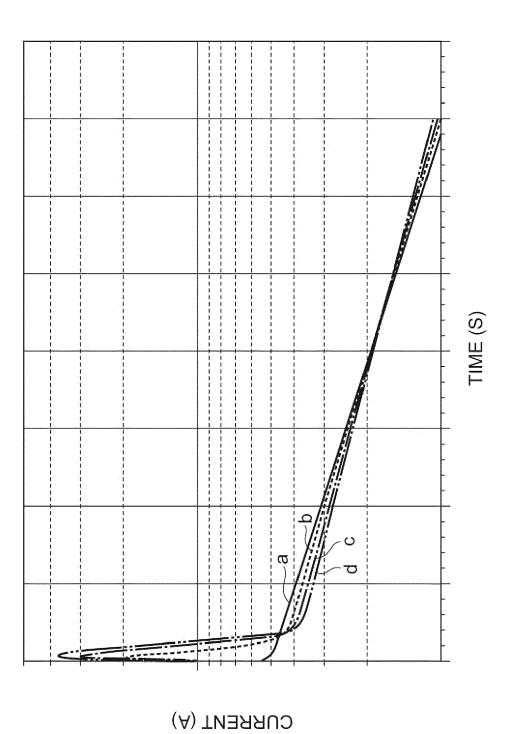

**[0039]** FIG. 10 illustrates a waveform of a pulse signal output from the APD 20 in a state in which the capacitative element 32 is excluded from the output unit 30 and a resistance value of the passive quenching element 31 is set as a parameter. FIG. 10 is an integer graph in which a unit of the vertical axis is set as a current (A) and a unit of the horizontal axis is set as time (s). Each of a plurality of pieces of data a, b, c, and d is data of the pulse signal in a case where a passive quenching element 31 having a different resistance value is provided in the output unit 30. In the order of the plurality of pieces of data a, b, c, and d, the passive quenching element 31 having a higher resistance value is provided.

**[0040]** As illustrated in FIG. 10, the smaller the resistance value of the passive quenching element 31 is, the steeper an inclination of the recharge pulse 28 is. The steeper the inclination of the recharge pulse 28, the shorter time necessary for quenching is, and the shorter dead time for which light is not detected by the APD 20 is. When using the passive quenching element 31 with a great resistance value, it is possible to realize appropriate quenching in which occurrence of a latching current or the like is suppressed. However, the greater the resistance value is, the further the dead time increases.

**[0041]** A pulse width of the pulse signal from the APD 20 connected to the passive quenching element 31 varies in response to the resistance value of the passive quenching element 31. As illustrated in FIG. 10, the greater the resistance value of the passive quenching element 31 is, the further the dead time of the APD 20 connected in series to the passive quenching element 31 increases. Accordingly, there is a demand for a circuit design including the passive quenching element 31 having an optimal resistance value to make appropriate quenching and a reduction of the dead time compatible with each other and to secure photodetection sensitivity and photodetection time resolution.

**[0042]** In the photodetector device 1, a plurality of the output units 30 including the passive quenching element 31 and the capacitative element 32 are provided in the circuit substrate 50 separate from the APD array substrate 10. According to this, a space capable of forming the plurality of output units 30 can be further expanded in comparison to a case where the plurality of output units 30 are arranged in the APD array substrate 10. Accordingly, the design of the plurality of output units 30 becomes easy.

**[0043]** Since the plurality of output units 30 are provided in the circuit substrate 50 separate from the APD array substrate 10, a parasitic capacitance that occurs between the configuration of the APD 20 and the output units 30 can be reduced. A manufacturing process dif-

ferent from that of the APD array substrate 10 can also be used. Since manufacturing processes which are respectively appropriate for the APD array substrate 10 and the circuit substrate 50 can be used, design of the plurality of output units 30 becomes easy.

**[0044]** FIG. 11 illustrates a waveform of a pulse signal output from the APD 20 in a state in which the passive quenching element 31 is set to a constant value, and an electrostatic capacitance of the capacitative element 32

<sup>10</sup> is set as a parameter. FIG. 11 is a univariate graph in which a unit of the vertical axis is current (A) and a unit of the horizontal axis is time (s). Data a is data of a pulse signal in a case where the capacitative element 32 is excluded from the output unit 30. Each of a plurality of

pieces of data b, c, and d is data of a pulse signal in a case where a capacitative element 32 having a different electrostatic capacitance is provided in the output unit 30. In the order of the plurality of pieces of data b, c, and d, the capacitative element 32 having a higher electrostatic capacitance is provided.

**[0045]** As illustrated in FIG. 11, when the capacitative element 32 is provided, a peak value of the fast pulse 27 is improved. The higher the electrostatic capacitance of the capacitative element 32 is, the greater the peak value

of the fast pulse 27 is. Accordingly, when providing the capacitative element 32, time resolution of a pulse signal from the plurality of APDs 20 is improved. The greater the peak value of the fast pulse 27 is, the more easily the pulse signal from the plurality of APD 20 is detected.

30 [0046] In the photodetector device 1, the capacitative element 32 that is connected in series to at least one of the APDs 20, and is connected in parallel to the passive quenching element 31. According to the configuration, the peak value of the pulse signal from the APD 20 that

is connected in series to the capacitative element 32 can be improved based on the electrostatic capacitance of the capacitative element 32 due to the characteristics described with reference to FIG. 11. Accordingly, the pulse signal from the plurality of APDs 20 is easily detected, and the photodetection time resolution can be improved. The photodetector device 1 can count the number of incident photons while realizing desired photodetection sensitivity and photodetection time resolution.

<sup>45</sup> **[0047]** In a configuration in which the plurality of APDs 20 operate in the Geiger mode in the APD array substrate 10 formed from the compound semiconductor, electric field strength applied to the APDs 20 is reduced, and thus an influence of a noise can be suppressed.

50 [0048] The photodetector device 1 includes the polysilicon layers 71 and 73 provided on the circuit substrate 50, the dielectric layer 74 provided on the polysilicon layer 73, and the polysilicon layer 72 provided on the dielectric layer 74. The passive quenching element 31 is formed

55 by the polysilicon layer 71, and the capacitative element 32 is formed by the polysilicon layer 73, the dielectric layer 74, and the polysilicon layer 72. The polysilicon layer 71 is formed at the same height as in the polysilicon

10

15

25

40

45

50

55

layer 72 or the polysilicon layer 73 in the thickness direction of the circuit substrate 50. In this case, the plurality of output units 30 can be formed in a simple manufacturing process.

**[0049]** Hereinbefore, description has been given of the embodiment of the invention, but the invention is not limited to the above-described embodiment, and various modifications can be made in a range not departing from the gist.

**[0050]** For example, the passive quenching element 31 may be formed by a metal thin film instead of the polysilicon layer 71. The capacitative element 32 may be formed by two metal layers instead of the polysilicon layers 72 and 73. In this case, the capacitative element 32 has a configuration in which two parallel metal layers sandwich the dielectric layer 74.

### **Reference Signs List**

**[0051]** 1: photodetector device, 10: APD array substrate, 20: APD, 30: output unit, 31: passive quenching element, 32: capacitative element, 40: channel, 50: circuit substrate, 71, 72, 73: polysilicon layer, 74: dielectric layer.

**[0052]** The content of this description contains the following numbered clauses:

1. A photodetector device comprising:

an avalanche photodiode array substrate in <sup>30</sup> which a plurality of avalanche photodiodes arranged to operate in a Geiger mode are twodimensionally arranged, the avalanche photodiode array substrate being formed from compound semiconductor; and <sup>35</sup>

a circuit substrate on which the avalanche photodiode array substrate is mounted,

wherein the circuit substrate includes a plurality of output units connected to each other in parallel to form at least one channel,

each of the output units includes a passive quenching element connected in series to at least one of the plurality of avalanche photodiodes, and a capacitative element connected in series to at least one of the avalanche photodiodes and connected in parallel to the passive quenching element.

2. The photodetector device according to claim 1,

wherein the passive quenching element is formed by a first polysilicon layer provided in the circuit substrate,

the capacitative element is formed by a second polysilicon layer provided in the circuit substrate, a dielectric layer stacked on the second polysilicon layer, and a third polysilicon layer stacked on the dielectric layer, and the first polysilicon layer is formed at the same height as in the second polysilicon layer or the third polysilicon layer in a thickness direction of the circuit substrate.

### Claims

1. A photodetector device comprising:

a first layer in which a plurality of avalanche photodiodes arranged to operate in a Geiger mode are two-dimensionally arranged, the first layer being formed from compound semiconductor; and

a second layer including a plurality of output units connected to each other in parallel to form at least one channel, overlapping the first layer, and being formed from silicon,

wherein each of the output units includes a quenching element connected in series to at least one of the plurality of avalanche photodiodes.

- 2. The photodetector device according to claim 1, wherein each of the avalanche photodiodes has an active area surrounded by an insulating portion when viewed from the thickness direction of the first layer, and the insulating portion is formed from a trench.

- 3. The photodetector device according to claim 1-2,

wherein the active area of each of the avalanche photodiodes is formed in a circular shape when viewed from the thickness direction, and the insulating portion is formed in an annular shape along an edge of the active area.

4. The photodetector device according to claim 2-3,

wherein the first layer is formed from a third layer and a fourth layer disposed on the third layer in such a manner that the third layer is located between the second layer and the fourth layer, the third layer has a surface facing the second layer, is formed from compound semiconductor, and includes a buffer layer, an absorption layer, an electric field relaxing layer, and the trench reaches the fourth layer from the surface of the third layer.

- 5. The photodetector device according to claim 1-4, wherein the second layer includes a plurality of channels, each of which is formed from the plurality of output units connected to each other in parallel.

- **6.** The photodetector device according to claim 1-5, wherein the first layer and the second layer are con-

nected through a bump electrode.

- The photodetector device according to claim 1-6, wherein the quenching element includes a passive quenching element.

- The photodetector device according to claim 7, wherein the second layer includes a capacitative element connected in series to at least one of the avalanche photodiodes and connected in parallel to <sup>10</sup> the passive quenching element.

- 9. The photodetector device according to claim 8, wherein the passive quenching element is formed by a first metal layer provided in the second layer, <sup>15</sup> the capacitative element is formed by a second metal layer provided in the second layer, a dielectric layer stacked on the second metal layer, and a third metal layer stacked on the dielectric layer, and the first metal layer is formed at the same height as in the second <sup>20</sup> metal layer or the third metal layer in a thickness direction of the second layer.

30

25

35

40

45

50

55

Fig.2

Fig.6

Fig.7

(А) СОВЯЕИТ (А)

EP 4 230 974 A1

\_

# **EUROPEAN SEARCH REPORT**

Application Number

EP 23 17 7334

|                                                                                  |                                                            | DOCUMENTS CONSIDERED TO BE REI                                                                                                                                                                                                              | LEVANT                        |                      |                                            |  |

|----------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------|--------------------------------------------|--|

|                                                                                  | Category                                                   | Citation of document with indication, where appropri<br>of relevant passages                                                                                                                                                                | iate,                         | Relevant<br>to claim | CLASSIFICATION OF THE<br>APPLICATION (IPC) |  |

| 10                                                                               | x                                                          | US 2014/291486 A1 (NAGANO TERUMASA<br>AL) 2 October 2014 (2014-10-02)                                                                                                                                                                       | A [JP] ET                     | 1,5-7                | INV.<br>G01J1/42                           |  |

|                                                                                  | Y                                                          | * paragraph [0028] - paragraph [00                                                                                                                                                                                                          | 073];                         | 1-8                  | G01J11/00                                  |  |

|                                                                                  | A                                                          | figures 1-10 *                                                                                                                                                                                                                              |                               | 9                    | H01L27/146<br>H01L31/10                    |  |

| 15                                                                               | x                                                          | WO 2010/151888 A1 (AMPLIFICATION<br>TECHNOLOGIES INC [US]; LINGA KRISE<br>29 December 2010 (2010-12-29)                                                                                                                                     |                               | 1,4-8                | H01L31/107<br>H01L27/144<br>H01L31/02      |  |

|                                                                                  | Y                                                          | * paragraph [0026] - paragraph [00<br>figures 1,2,7-11 *                                                                                                                                                                                    | 064];                         | 1-8                  | H04N25/79<br>G01J1/44                      |  |

| 20                                                                               | Y                                                          | US 2017/186798 A1 (YANG MING-HSIEM<br>AL) 29 June 2017 (2017-06-29)                                                                                                                                                                         | N [TW] ET :                   | 2                    |                                            |  |

|                                                                                  | A                                                          | <pre>* paragraph [0022] - paragraph [00 figures 2, 3 *</pre>                                                                                                                                                                                | 028];                         | 1,3-9                |                                            |  |

| 25                                                                               | Y                                                          | US 2014/312448 A1 (HARMON ERIC S<br>23 October 2014 (2014-10-23)                                                                                                                                                                            | [US])                         | 2,3                  |                                            |  |

|                                                                                  | A                                                          | * paragraph [0066] - paragraph [00<br>figures 8-21 *                                                                                                                                                                                        | 087];                         | 1,4-9                |                                            |  |

| 30                                                                               | Y                                                          | <br>US 2013/270666 A1 (SATO KENICHI [JP] ET                                                                                                                                                                                                 |                               | 8                    | TECHNICAL FIELDS<br>SEARCHED (IPC)         |  |

|                                                                                  |                                                            | AL) 17 October 2013 (2013-10-17)<br>* paragraphs [0080] - [0085]; figu<br>33,34 *                                                                                                                                                           | ures                          |                      | G01J<br>H01L<br>H04N                       |  |

| 35                                                                               |                                                            |                                                                                                                                                                                                                                             |                               |                      |                                            |  |

| 40                                                                               |                                                            |                                                                                                                                                                                                                                             |                               |                      |                                            |  |

| 45                                                                               |                                                            |                                                                                                                                                                                                                                             |                               |                      |                                            |  |

| 1                                                                                | The present search report has been drawn up for all claims |                                                                                                                                                                                                                                             |                               |                      |                                            |  |

| 50 🗐                                                                             |                                                            | Place of search Date of completio                                                                                                                                                                                                           | on of the search              |                      | Examiner                                   |  |

| (P04C01                                                                          |                                                            | Munich 13 July                                                                                                                                                                                                                              |                               | -                    | tter, Fritz                                |  |

| 20<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25<br>25 | X : pari<br>Y : pari<br>doc<br>A : tech                    | CATEGORY OF CITED DOCUMENTS T : theory or principle underlying the invention<br>E : particularly relevant if taken alone<br>: particularly relevant if combined with another<br>document of the same category<br>: technological background |                               |                      |                                            |  |

| 55 <sup>1</sup> 0 0                                                              | O : nor                                                    | -written disclosure & :                                                                                                                                                                                                                     | member of the san<br>document | ne patent family     | , corresponding                            |  |

5

# EP 4 230 974 A1

# ANNEX TO THE EUROPEAN SEARCH REPORT ON EUROPEAN PATENT APPLICATION NO.

EP 23 17 7334

5

This annex lists the patent family members relating to the patent documents cited in the above-mentioned European search report. The members are as contained in the European Patent Office EDP file on The European Patent Office is in no way liable for these particulars which are merely given for the purpose of information.

| 13-07-2023 |

|------------|

|------------|

|    | Patent document<br>cited in search report |    | Publication<br>date |    | Patent family<br>member(s) |        | Publication date |

|----|-------------------------------------------|----|---------------------|----|----------------------------|--------|------------------|

|    | US 2014291486                             | A1 | 02-10-2014          | CN | 103890972                  | Δ      | 25-06-2014       |

|    | 00 1011101                                |    | 02 10 2014          | CN | 105870244                  |        | 17-08-2016       |

|    |                                           |    |                     |    | 112012004412               |        | 07-08-2014       |

| 5  |                                           |    |                     | JP | 5926921                    |        | 25-05-2016       |

|    |                                           |    |                     | JP | 2013089919                 |        | 13-05-2013       |

|    |                                           |    |                     | TW | 201318154                  |        | 01-05-2013       |

|    |                                           |    |                     | TW | 201717370                  |        | 16-05-2017       |

|    |                                           |    |                     | US | 2014291486                 |        | 02-10-2014       |

|    |                                           |    |                     | US | 2016254307                 |        | 01-09-2016       |

|    |                                           |    |                     | WO | 2013058001                 |        | 25-04-2013       |

|    | <br>WO 2010151888                         | A1 | 29-12-2010          | EP | 2446483                    | A1     | 02-05-2012       |

|    |                                           |    |                     | IL | 217196                     | A      | 30-04-2017       |

|    |                                           |    |                     | JP | 2012531753                 | A      | 10-12-2012       |

|    |                                           |    |                     | US | 2011018086                 | A1     | 27-01-2011       |

|    |                                           |    |                     | WO | 2010151888                 | A1     | 29-12-2010       |

|    | US 2017186798                             | A1 | 29-06-2017          | CN | 106920808                  | A      | 04-07-201        |

|    |                                           |    |                     | TW | 201724488                  |        | 01-07-201        |

|    |                                           |    |                     | US | 2017186798                 | A1     | 29-06-2017       |

|    | US 2014312448                             | A1 | 23-10-2014          | EP | 2987186                    |        | 24-02-2010       |

|    |                                           |    |                     | JP | 6383516                    |        | 29-08-2018       |

|    |                                           |    |                     | JP | 2016519435                 |        | 30-06-2010       |

|    |                                           |    |                     | US | 2014312448                 |        | 23-10-2014       |

| 35 |                                           |    |                     | US | 2015270430                 |        | 24-09-201        |

|    |                                           |    |                     |    | 2014172697                 | A1<br> | 23-10-2014       |

|    | US 2013270666                             | A1 | 17-10-2013          | CN | 103190000                  |        | 03-07-2013       |

|    |                                           |    |                     | EP | 2634821                    |        | 04-09-2013       |

| 40 |                                           |    |                     | JP | 5562207                    |        | 30-07-2014       |

|    |                                           |    |                     | JP | 2012099580                 |        | 24-05-2012       |

|    |                                           |    |                     | KR | 20140001889                |        | 07-01-2014       |

|    |                                           |    |                     | TW | 201232800                  |        | 01-08-2012       |

|    |                                           |    |                     | US | 2013270666                 |        | 17-10-2013       |

|    |                                           |    |                     |    | 2012057082                 | A1<br> | 03-05-2012       |

For more details about this annex : see Official Journal of the European Patent Office, No. 12/82

# **REFERENCES CITED IN THE DESCRIPTION**

This list of references cited by the applicant is for the reader's convenience only. It does not form part of the European patent document. Even though great care has been taken in compiling the references, errors or omissions cannot be excluded and the EPO disclaims all liability in this regard.

### Patent documents cited in the description

• JP 2012531753 A [0003]