## UK Patent Application (19)GB (11)2627807

04.09.2024

4000

(21) Application No:

2303120.6

(22) Date of Filing:

02.03.2023

(71) Applicant(s):

**Imagination Technologies Limited** (Incorporated in the United Kingdom) Imagination House, Home Park Estate, KINGS LANGLEY, Hertfordshire, WD4 8LZ, **United Kingdom**

(72) Inventor(s):

Gunduz Vehbi Demirci Cagatay Dikici **Grant Michael Stevens** Le Yang

(74) Agent and/or Address for Service:

Slingsby Partners LLP

1 Kingsway, LONDON, WC2B 6AN, United Kingdom

(51) INT CL:

G06T 1/40 (2006.01) G06T 1/20 (2006.01)

G06N 3/0464 (2023.01) G06V 10/82 (2022.01)

(56) Documents Cited:

Liu et al. 2020, "Deep Adaptive Inference Networks for Single Image Super-Resolution", [online], Available from: https://arxiv.org/abs/2004.03915 Park et al. 2017, "Faster CNNs with Direct Sparse Convolutions and Guided Pruning", International Conference on Learning Representations, [online], Available from: https://arxiv.org/pdf/1608.01409.pdf

(58) Field of Search:

INT CL G06N

Other: SEARCH-PATENT, SEARCH-NPL. INTERNET

- (54) Title of the Invention: Methods and systems for performing a sparse submanifold deconvolution on a GPU Abstract Title: Sparse submanifold deconvolution based on active positions of the output tensor.

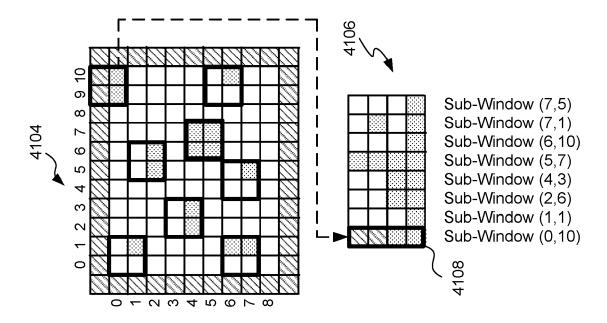

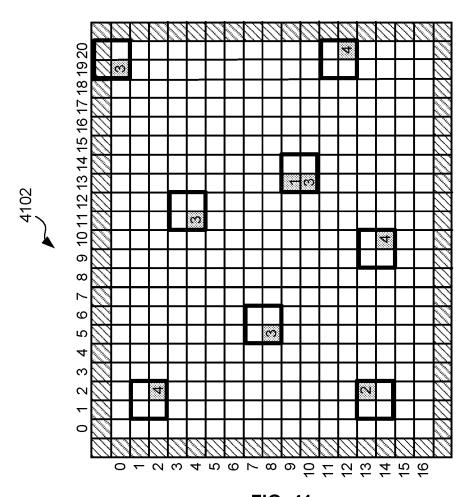

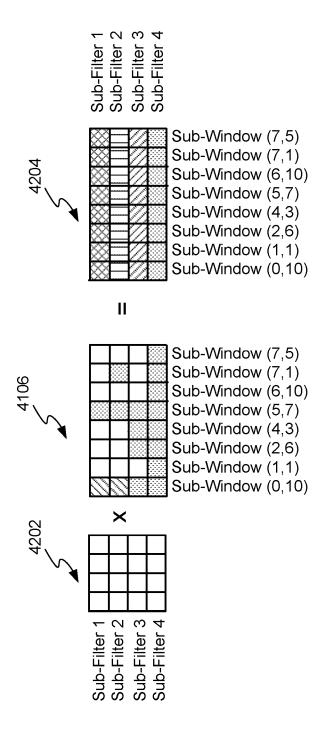

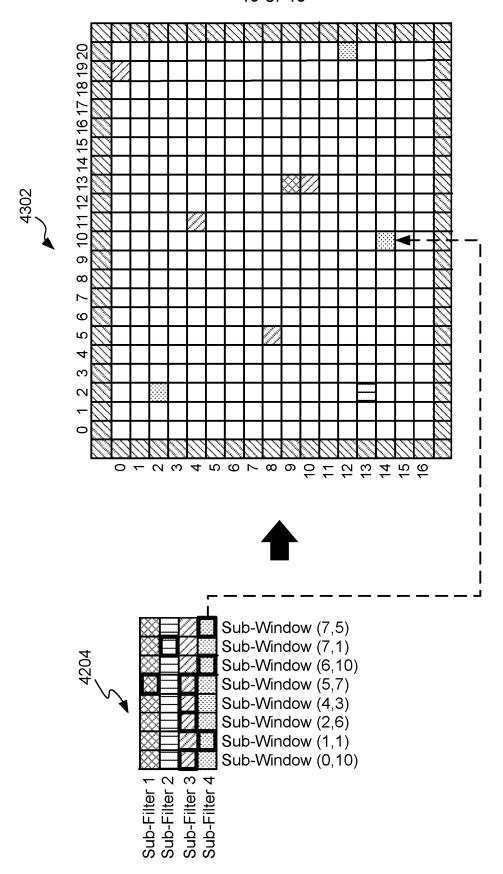

- (57) A method of implementing a sparse submanifold deconvolution between an input tensor and a filter, representable as a direct convolution between an input tensor and a plurality of sub-filters comprising weights of the filter, the method comprising: receiving the input tensor (4104, fig 41) in dense format, identifying active positions of the output tensor (4102, fig 41), generating, using an indexed-unfold operation, an input matrix (4106, fig 41) comprising elements of the input tensor in each non-zero sub-window (4108, fig 41) relevant to the active positions of the output tensor, and multiplying the input matrix with a weight matrix (4202, fig 42) comprising the sub-filters to generate an output matrix (4204, 42). The method may further comprise generating, using an indexed fold operation, the output tensor (4302, fig 43) by identifying, based on the active positions, the position in the output tensor of each element in the output matrix, and placing the elements into the corresponding positions in the output tensor. Also disclosed is a method of performing a convolution on the output tensor using a neural network accelerator to generate partial outputs which are combined to generate an output tensor.

FIG. 4

FIG. 5

FIG. 6

FIG. 9

FIG. 12

FIG. 14

FIG. 15

FIG. 18

FIG. 20

FIG. 21

FIG. 22

FIG. 23

FIG. 24

FIG. 25

( \L-, \L-) \W \ ( \O, \L-) \W

26 of 48

FIG. 26

FIG. 29

W 3, 2

$w_{3,3}$

$b_{5,4}$

$b_{5,5}$

Output Tensor  $\boldsymbol{B}$

$|b_{5,5}|$ b<sub>1,1</sub> b<sub>1,2</sub> b<sub>1,3</sub> b<sub>1,4</sub> b<sub>1,5</sub>  $|b_{2,1}||b_{2,2}||b_{2,3}||b_{2,4}||b_{2,5}|$ b3,1 b3,2 b3,3 b3,4 b3,5 | b4,2 | b4,3 | b4,4 | b4,5 | b<sub>5,2</sub> b<sub>5,3</sub> b<sub>5,4</sub> 3006 DECONVOLUTION (STRIDE 2 x 2)  $W_{I,I}$   $W_{I,2}$   $W_{I,3}$ W3,1 W3,2 W3,3 FILTER W3004 INPUT TENSOR A3002  $a_{l,I} | a_{l,2}$  $a_{2,1} a_{2,2}$

FIG. 30

31 of 48

## DECONVOLUTION (STRIDE 2)

FIG. 31

FIG. 32

33 of 48  $W_2$  $a_5$  $W_2$ PADDED VERSION OF INPUT TENSOR A $W_2$  $a_4$ 0 INVALID bs1-11 bs2-1 bs1-2 bs2-2 bs1-3 bs2-3 bs1-4 bs2-4 bs1-5 bs2-5 bs1-6 bs2-6  $a_3$  $W_2$ 0  $b_{s2-1}b_{s1-2}b_{s2-2}b_{s1-3}b_{s2-3}b_{s1-4}b_{s2-4}b_{s1-5}b_{s2-5}b_{s1-6}$  $a_2$  $W_2$  $a_I$  $W_2$ 0  $b_{s2-6}$  $b_{s2-5}$  $b_{s2-3}$  $b_{s2-2}$  $b_{s2-4}$  $b_{s2-I}$ SUB-OUTPUT DECONVOLUTION (STRIDE 2) SECOND **TENSOR**  $B_{S2}$ INTERLEAVE  $\mathcal{M}_I$ 0 INVALID  $W_3$  $a_5$  $\mathcal{M}_I$ PADDED VERSION OF INPUT TENSOR A $W_3$  $a_4$  $\mathcal{M}_{J}$  $a_3$ **OUTPUT TENSOR**  $W_3$ **OUTPUT TENSOR**  $\mathcal{M}_J$ CROPPED  $W_3$  $a_2$  $\mathcal{M}_I$ B  $W_3$  $a_I$  $\mathcal{M}_I$  $b_{sI-3}$  $b_{sI-4}$  $b_{sI-6}$  $b_{sI-5}$  $b_{sI-I}$ SUB-OUTPUT  $b_{sI-2}$ Tensor  $B_{\scriptscriptstyle SI}$ FIG. 33

| 1    |   |          |   |          |   |   |   |   |

|------|---|----------|---|----------|---|---|---|---|

| 3502 | 7 | <i>†</i> | 2 | <i>†</i> | 7 | 4 | 2 | 4 |

| 36   | I | 3        | I | 3        | I | 3 | I | 3 |

|      | 2 | 4        | 2 | 7        | 2 | 7 | 2 | 4 |

|      | I | 3        | I | 3        | I | 3 | I | 3 |

|      | 2 | 4        | 2 | 4        | 2 | 4 | 2 | 4 |

|      | I | 3        | I | 3        | I | 3 | I | 3 |

|      | 2 | <i>†</i> | 2 | 4        | 2 | 4 | 2 | 4 |

|      | I | 3        | Ι | 3        | I | 3 | I | 3 |

UTPUT TENSOR E

FIG. 36

FIG. 37

FIG. 40

FIG. 41

FIG. 43

FIG. 45

FIG. 46

FIG. 47

# METHODS AND SYSTEMS FOR PERFORMING A SPARSE SUBMANIFOLD DECONVOLUTION ON A GPU

#### TECHNICAL FIELD

**[0001]** This application is directed to methods and systems for performing a sparse submanifold deconvolution on a graphics processing unit (GPU).

#### **BACKGROUND**

10

25

30

**[0002]** As is known to those of skill in the art, a point cloud is a set of individual data points plotted in two-dimensional (2D) or three-dimensional (3D) space. For example, each point in a 3D point cloud may represent a measurement at a particular x, y and z location. A point cloud may be used to represent an object in space. Point clouds may by generated by a sensor, such as, but not limited to, a LiDAR scanner or a depth camera. As is known to those of skill in the art, a LiDAR scanner uses light in the form of a pulsed laser to measure distances. As point clouds do not typically have a point for each possible co-ordinate, point clouds are considered to be sparse datasets.

[0003] There are a wide range of real-world artificial intelligence applications which point clouds can be used in, such as augmented/virtual reality (e.g. layout detection for interior scenes) and autonomous driving (e.g. to extract the driveable regions). As a result, performing deep learning tasks on point clouds has received significant attention from both academia and industry and artificial neural networks (referred to herein simply as neural networks) have been developed to process point clouds, which may be referred to herein as a point cloud neural networks. As is known to those of skill in the art, a neural network comprises one or more interconnected layers that can be used for machine learning applications. In particular, a neural network can be used in signal processing applications, including, but not limited to, image processing and computer vision applications.

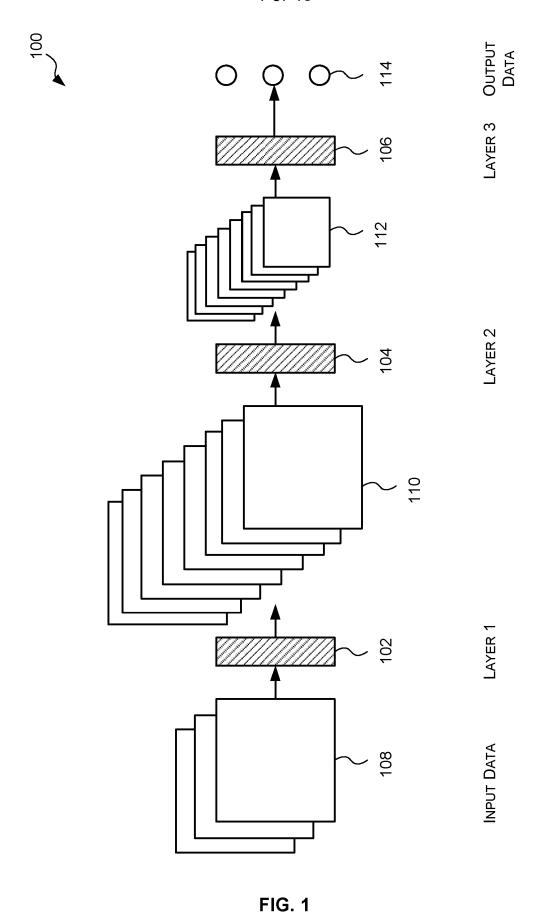

[0004] FIG. 1 illustrates an example neural network 100 that comprises a plurality of layers 102, 104, 106. Each layer 102, 104, 106 receives input data, and processes the input data in accordance with the layer to produce output data. The output data is either provided to another layer as the input data or is output as the final output data of the neural network. For example, in the neural network 100 of FIG. 1, the first layer 102 receives the original input data 108 to the neural network 100 and processes the input data in accordance with the first layer 102 to produce output data 110. The output data 110 of the first layer 102 becomes the input data to the second layer 104, and the second layer 104 processes the input data 110 in accordance with the second layer 104 to produce output data 112. The output data 112 of the second layer 104 becomes the input data to the third layer 106, and the third layer 106 processes the input data 112 in accordance with the third layer 106 to produce output data 114. The output data 114 of the third layer 106 is then output as the final output data of the neural network. Where the neural network is used for

classification, the final output data may be a vector of length A, wherein A is the number of classes and each value in the vector represents the probability of a certain class.

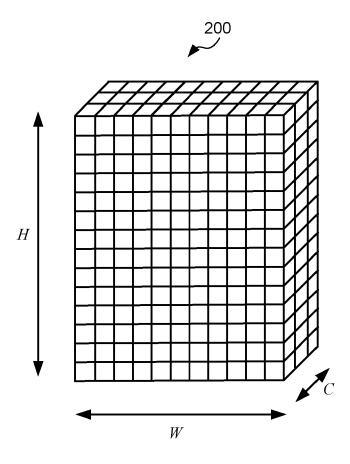

[0005] The data input to and output from a layer of a neural network can be described as a tensor. As is known to those of skill in the art, a tensor is a generalization of vectors and matrices and can be considered an n-dimensional array. A vector is a one-dimensional tensor, and a matrix is a two-dimensional tensor. The tensors in a neural network are often, but are not necessarily, four-dimensional. Reference is made to FIG. 2 which illustrates an example four-dimensional (4D) tensor 200 in which one dimension (e.g. corresponding to the batch size) has been suppressed for visualisation purposes. The 4D tensor 200 may be described as comprising one or more 3D tensors, wherein each 3D tensor comprises C planes of data. Each plane has a height H and a width W. Each plane may be referred to as a channel of the tensor. The number of 3D tensors may be referred to as the batch size. In a traditional neural network each 3D tensor may be, for example, an image. An element of a tensor may be referred to as a pixel.

10

15

20

25

30

**[0006]** The processing that is performed on the input tensor to a layer depends on the type of layer. For example, each layer of a neural network may be one of a plurality of different types. Common neural network layer types include, but are not limited to, a convolution layer, an activation layer, a normalisation layer, a pooling layer, a fully connected layer, and a batch normalisation layer. It will be evident to a person of skill in the art that these are only example neural network layer types and there may be other neural network layer types.

**[0007]** A convolution layer convolves the input tensor with weights associated with the layer Specifically, each convolution layer is associated with a plurality of weights  $w_1 \dots w_g$ , which may also be referred to as filter weights or coefficients. The weights are grouped to form one or more filters. Each filter is moved or slid across the input tensor in one or more dimensions in accordance with the stride in that dimension, and the dot-product of the input data and the weights of that filter is calculated at each filter location. The elements of the input tensor that are applied to the filter weights at a particular filter location are referred to as a window of the input tensor. There may be a bias per filter which is added to the result of the corresponding dot products.

[0008] There are many different types of convolution layers. Traditional neural networks often have one or more 2D or 3D convolution layers. In a 2D convolution (which may be referred to herein as a standard 2D convolution), each filter has a dimension  $K_H \times K_W \times C_{in}$  (i.e., each filter may comprise a set of  $K_H \times K_W \times C_{in}$  weights W) wherein  $C_{in}$  is the number of channels of the input tensor such that each filter generates a channel of the output. Each filter channel may be described as a kernel of size  $K_H \times K_W$ . Accordingly, depending on the number of channels, a filter may comprise one or more kernels. Each filter is slid across the input tensor in steps  $S_H$  and  $S_W$  in the H and W dimensions respectively, which are referred to as the strides of the convolution.

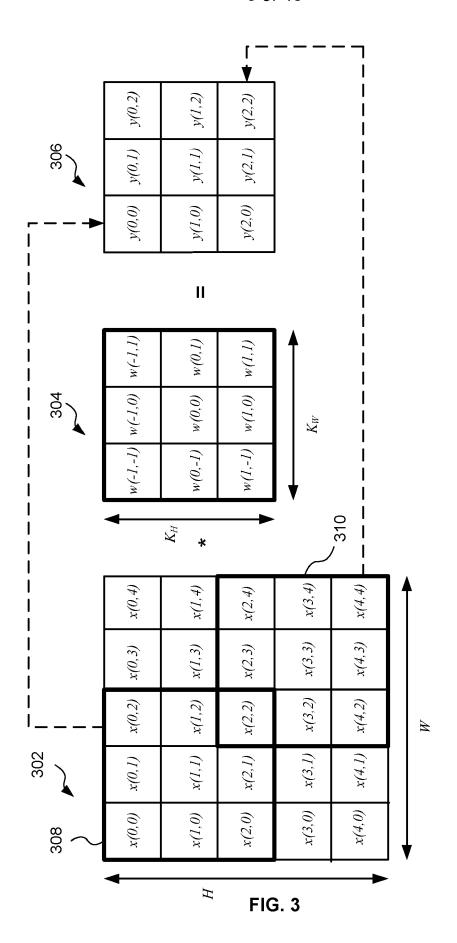

**[0009]** Reference is now made to FIG. 3 which illustrates an example 2D convolution with strides of 1 (i.e.,  $s_H = s_W = 1$ ) between an input tensor 302 with a height H, width W, and one channel (i.e. C=1) and a set of weights that form one filter 304 with kernel size  $K_H \times K_W$ , and one channel. The filter 304 is convolved with the input tensor 302 to produce one channel, or one plane, of the output tensor 306. Specifically, the filter 304 is slid over the input tensor 302 in the width dimension W and the height dimension H one element at a time and the dot product of the input elements and the weights is generated at each filter position. In this example, the first position of the filter with respect to the input tensor 302 is when the centre of the filter W(0,0) is aligned with W(0,1) such that the first element of the output W(0,0) is equal to the dot product of the input elements in the window 308 and the weights of the filter 304. Similarly, the last position of the filter with respect to the input tensor 302 is when the centre of the filter W(0,0) is aligned with W(0,0), such that the last element of the output tensor W(0,0) is equal to the dot product of the input elements in the window 310 and the weights of the filter 304. A 3D convolution is similar to a 2D convolution except the filters are also slid across the input tensor in a third (e.g. z or channel) dimension.

[0010] Point cloud neural networks, however, may comprise one or more 2D or 3D sparse submanifold convolutions layers. A 2D/3D sparse submanifold convolution is the same as its corresponding standard 2D/3D convolution except that the output elements are only calculated for positions of the filter in which one or more predetermined elements of the filter kernel is/are aligned with an active position of the input tensor. An active position of the input tensor is a height and width position of the input tensor in which at least one channel of the input tensor has a non-zero value or element at that position. The one or more predetermined elements of the filter kernel may comprise the centre element of the filter kernel and/or one or more elements close to the centre of the filter kernel. In the examples described herein there is a single predetermined element of the filter kernel that is the centre element of the filter kernel. However, it will be evident to a person of skill in the art that this is an example only. A sparse submanifold convolution is designed to work on a sparse input tensor.

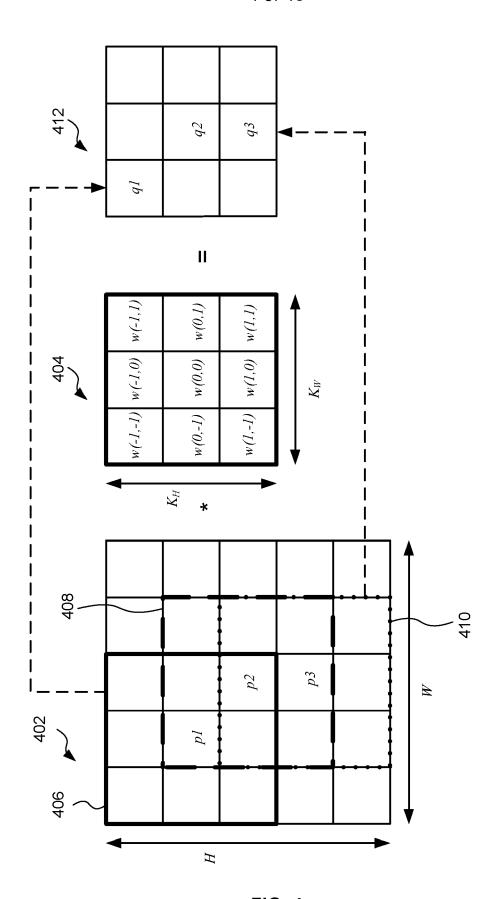

**[0011]** Reference is now made to FIG. 4 which illustrates an example 2D sparse submanifold convolution with strides of 1 (i.e.,  $s_H = s_W = 1$ ) between an input tensor 402 with a height H, width W, and one channel (i.e., C=1) and a set of weights that form one filter 404 with a kernel size of  $K_H \times K_W$ , and one channel, wherein the one or more predetermined elements of the filter kernel comprises the element at the centre of the filter kernel (i.e. w(0,0)). The input tensor 402 only has three non-zero elements, thus the input tensor 402 has three active positions -p1, p2, p3. Accordingly, there are only three positions of the filter with respect to the input tensor 402 (or three windows of the input tensor), denoted 406, 408, 410, in which the centre of the filter 404 is aligned with an active position (which will be referred to herein as the active windows of the input tensor). Thus, only three elements q1, q2, q3 of the output tensor 412 are generated. Output element q1 is equal to the dot product of the elements in the first active window 406 and the weights of the filter 404, and output element q3 is equal to the dot product of the elements

of the third active window 410 and the weights of the filter 404. A 3D sparse submanifold convolution is similar to a 2D sparse submanifold convolution except the filters are also slid across the input tensor in a third (e.g. z) dimension.

**[0012]** As sparse submanifold convolution layers are becoming more popular in neural networks it is important to be able to implement sparse submanifold convolutions in a hardware efficient manner (e.g., in a manner that requires less silicon area and/or less processing power).

**[0013]** The embodiments described below are provided by way of example only and are not limiting of implementations which solve any or all of the disadvantages of known methods and systems for implementing a sparse submanifold convolution.

#### 10 SUMMARY

15

20

25

30

**[0014]** This Summary is provided to introduce a selection of concepts in a simplified form that are further described below in the Detailed Description. This Summary is not intended to identify key features or essential features of the claimed subject matter, nor is it intended to be used to limit the scope of the claimed subject matter.

[0015] Described herein are methods of implementing a sparse submanifold deconvolution on a graphics processing unit, the sparse submanifold deconvolution being representable as a direct convolution between an input tensor to the sparse submanifold deconvolution and each of a plurality of a sub-filters, each sub-filter of the plurality of sub-filters comprising a subset of weights of a filter of the sparse submanifold deconvolution. The methods include: receiving, at the graphics processing unit, the input tensor in a dense format; receiving, at the graphics processing unit, information identifying target positions of an output tensor of the sparse submanifold deconvolution; performing, at the graphics processing unit, an indexed unfold operation on the input tensor based on the identified target positions of the output tensor to generate an input matrix comprising elements of the input tensor in each sub-window of the input tensor relevant to at least one of the identified target positions of the output tensor; and performing, at the graphics processing unit, a matrix multiplication between a weight matrix and the input matrix to generate an output matrix that comprises elements of the output tensor at the identified target positions.

**[0016]** A first aspect provides a method of implementing a sparse submanifold deconvolution on a graphics processing unit, the sparse submanifold deconvolution being representable as a direct convolution between an input tensor to the sparse submanifold deconvolution and each of a plurality of a sub-filters, each sub-filter of the plurality of sub-filters comprising a subset of weights of a filter of the sparse submanifold deconvolution, the method comprising: receiving, at the graphics processing unit, the input tensor in a dense format; receiving, at the graphics processing unit, information identifying target positions of an output tensor of the sparse submanifold deconvolution; performing, at the graphics processing unit, an indexed unfold operation on the input tensor based on the identified target positions of the output tensor to generate an input matrix comprising elements of the input tensor in each sub-window of the input tensor relevant to at least

one of the identified target positions of the output tensor; and performing, at the graphics processing unit, a matrix multiplication between a weight matrix and the input matrix to generate an output matrix that comprises elements of the output tensor at the identified target positions.

**[0017]** The output tensor may have at least a height dimension, a width dimension and a channel dimension and a target position of the output tensor may be a height and width position of the output tensor.

**[0018]** The information identifying the target positions of the output tensor may comprise a target position list that comprises height and width co-ordinates of each target position of the output tensor.

10 **[0019]** A sub-window of the input tensor may be a window of the input tensor used to compute at least one element of an output tensor of one of the direct convolutions.

**[0020]** Performing the indexed unfold operation on the input tensor may comprise identifying, from the identified target positions of the output tensor and one or more parameters of the sparse submanifold deconvolution, each sub-window of the input tensor relevant to at least one of the identified target positions of the output tensor.

15

20

25

30

**[0021]** A sub-window of the input tensor may be relevant to a target position if that sub-window is used to generate an element of the output tensor of the sparse submanifold deconvolution at that target position.

**[0022]** The elements of a channel of the output tensor of the sparse submanifold deconvolution may be divisible into a plurality of blocks wherein each element in a block is generated by a same sub-window of the input tensor and a different sub-filter of a filter, and identifying the sub-window of the input tensor relevant to an identified target position may comprise identifying the block of the output tensor that the identified target position forms part of, and mapping the identified block of the output tensor to the sub-window of the input tensor used to generate that block.

**[0023]** An identified block of the output tensor may be mapped to a sub-window of the input tensor using a position in the output tensor of a predetermined element of the block and the one or more parameters of the sparse submanifold deconvolution.

**[0024]** Performing the indexed unfold operation on the input tensor may comprise identifying the elements of each relevant sub-window from one or more parameters of the sparse submanifold deconvolution.

**[0025]** Identifying the elements of a relevant sub-window may comprise identifying a position in the input tensor of a predetermined element in the sub-window and implementing a series of nested loops to move through the elements in the sub-window from the identified position, the series of nested loops comprising a loop for each dimension of the sub-window.

**[0026]** Performing the indexed unfold operation on the input tensor may comprise storing the elements of each relevant sub-window in the input matrix.

**[0027]** The method may further comprise receiving a zeroed input matrix, and the elements of the relevant sub-windows of the input tensor may be stored in the received input matrix.

**[0028]** Performing the indexed unfold operation on the input tensor may comprise identifying, from one or more parameters of the sparse submanifold deconvolution, which sub-filter of the plurality of sub-filters is relevant to each of the identified target positions of the output tensor.

**[0029]** The elements of a channel of the output tensor may be divisible into a plurality of blocks wherein each element in a block is generated by a same sub-window of the input tensor and a different sub-filter of a filter, and identifying which sub-filter of the plurality of sub-filters is relevant to an identified target position of the output tensor may comprise identifying the block that the target position forms part of and a location of the target position within that block.

10

15

20

25

30

**[0030]** The input matrix may comprise a column for each relevant sub-window of the input tensor and each column of the input matrix may comprise the elements of the input tensor in the corresponding relevant sub-window.

**[0031]** The weight matrix may comprise a row for each sub-filter relevant to at least one identified target position of the output tensor, and each row of the weight matrix may comprise all weights forming the corresponding sub-filter.

**[0032]** The method may further comprise performing, at the graphics processing unit, an indexed fold operation on the output matrix based on the identified target positions of the output tensor to generate the output tensor in a dense format.

**[0033]** Performing the indexed fold operation on the output matrix may comprise identifying, based on the identified target positions of the output tensor and one or more parameters of the sparse submanifold deconvolution, elements in the output matrix that correspond to the identified target positions of the output tensor, and storing each element of the output matrix that corresponds to an identified target position at that target position of a channel of the output tensor.

**[0034]** The output matrix may comprise, for each relevant sub-window, an element for each relevant sub-filter, and an element of the output matrix is determined to correspond to an identified target position if that element was generated by the sub-window and sub-filter relevant to that identified target position.

**[0035]** The method may further comprise receiving, at the graphics processing unit, a zeroed output tensor, and the elements of the output matrix corresponding to an identified target position are written to the received output tensor.

**[0036]** Performing the indexed fold operation on the output matrix may further comprise storing zeroes at each position of the output tensor that does not comprise an element of the output matrix.

**[0037]** A second aspect provides a graphics processing unit configured to perform the method of the first aspect.

[0038] The graphics processing unit may be embodied in hardware on an integrated circuit.

**[0039]** A third aspect provides a computer readable storage medium having stored thereon computer readable code configured to cause a graphics processing unit to perform the method of the first aspect when the code is run.

**[0040]** The method of the first aspect may be implemented as part of processing data in accordance with a neural network to perform a signal processing task.

10

15

20

25

**[0041]** The input tensor of the first aspect may comprise image data such that performing the sparse submanifold deconvolution comprises a method of processing image data.

[0042] The image data may comprise a point cloud data set generated by an image sensor.

**[0043]** The sparse submanifold deconvolution of the first aspect may be a 3D sparse submanifold deconvolution and the input tensor may comprise a 3D point cloud data set.

**[0044]** A fourth aspect provides a method of implementing a standard convolution on a central processing unit, the method comprising: receiving, at the central processing unit, an input tensor in a dense format; performing, at the central processing unit, an indexed unfold operation on the input tensor based on the identified active positions of the input tensor to generate an input matrix comprising elements of the input tensor in each non-zero window of the input tensor; and performing, at the central processing unit, a matrix multiplication between a weight matrix and the input matrix to generate an output matrix that comprises elements of an output tensor of the standard convolution based on the non-zero windows of the input tensor.

**[0045]** A fifth aspect provides a method of implementing a sequence of two sparse submanifold convolutions, the method comprising: receiving, at a graphics processing unit, an input tensor, in a dense format, to a first sparse submanifold convolution of the sequence; identifying, at the graphics processing unit, active positions of the input tensor; performing, at the graphics processing unit, an indexed unfold operation on the input tensor based on the identified active positions to generate an input matrix comprising elements of the input tensor in each active window of the input tensor; performing, at the graphics processing unit, a matrix multiplication between a weight matrix and the input matrix to generate an output matrix that comprises elements of an output tensor of the first sparse submanifold convolution based on the active windows; providing the output matrix to a neural network accelerator as an input tensor, in a sparse format, to a second sparse submanifold convolution of the sequence; performing, at the neural network accelerator, for each position of a

kernel of the second sparse submanifold convolution, a 1x1 convolution between the received input matrix and weights of filters of the sparse submanifold convolution at that kernel position to generate a plurality of partial outputs; and combining appropriate partial outputs of the plurality of partial outputs to generate an output tensor, in sparse format, of the second sparse submanifold convolution.

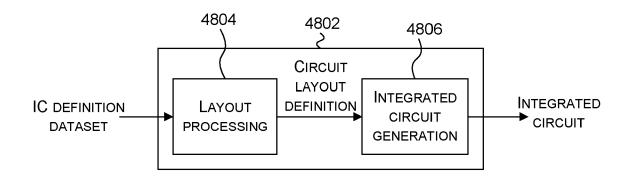

[0046] The neural network accelerators, convolution processing units, convolution engines, and graphics processing units described herein may be embodied in hardware on an integrated circuit. There may be provided a method of manufacturing, at an integrated circuit manufacturing system, a neural network accelerator, convolution processing unit, convolution engine or graphics processing unit described herein. There may be provided an integrated circuit definition dataset that, when processed in an integrated circuit manufacturing system, configures the system to manufacture an integrated circuit that embodies a neural network accelerator, convolution processing unit, convolution engine or graphics processing unit described herein. There may be provided a non-transitory computer readable storage medium having stored thereon a computer readable description of a neural network accelerator, convolution processing unit, convolution engine or graphics processing unit that, when processed in an integrated circuit manufacturing system, causes the integrated circuit manufacturing system to manufacture an integrated circuit embodying the neural network accelerator, convolution processing unit, convolution engine or graphics processing unit.

[0047] There may be provided an integrated circuit manufacturing system comprising: a non-transitory computer readable storage medium having stored thereon a computer readable description of a neural network accelerator, convolution processing unit, convolution engine or graphics processing unit described herein; a layout processing system configured to process the computer readable description so as to generate a circuit layout description of an integrated circuit embodying the neural network accelerator, convolution processing unit, convolution engine or graphics processing unit; and an integrated circuit generation system configured to manufacture an integrated circuit embodying the neural network accelerator, convolution processing unit, convolution engine or graphics processing unit according to the circuit layout description.

**[0048]** There may be provided computer program code for performing any of the methods described herein. There may be provided non-transitory computer readable storage medium having stored thereon computer readable instructions that, when executed at a computer system, cause the computer system to perform any of the methods described herein.

**[0049]** The above features may be combined as appropriate, as would be apparent to a skilled person, and may be combined with any of the aspects of the examples described herein.

#### BRIEF DESCRIPTION OF THE DRAWINGS

10

15

20

25

30

35

**[0050]** Examples will now be described in detail with reference to the accompanying drawings in which:

- [0051] FIG. 1 is a schematic diagram of an example neural network;

- [0052] FIG. 2 is a schematic diagram illustrating an example tensor;

- [0053] FIG. 3 is a schematic diagram illustrating an example 2D convolution;

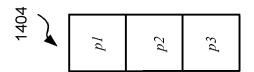

- [0054] FIG. 4 is a schematic diagram illustrating an example 2D sparse submanifold convolution;

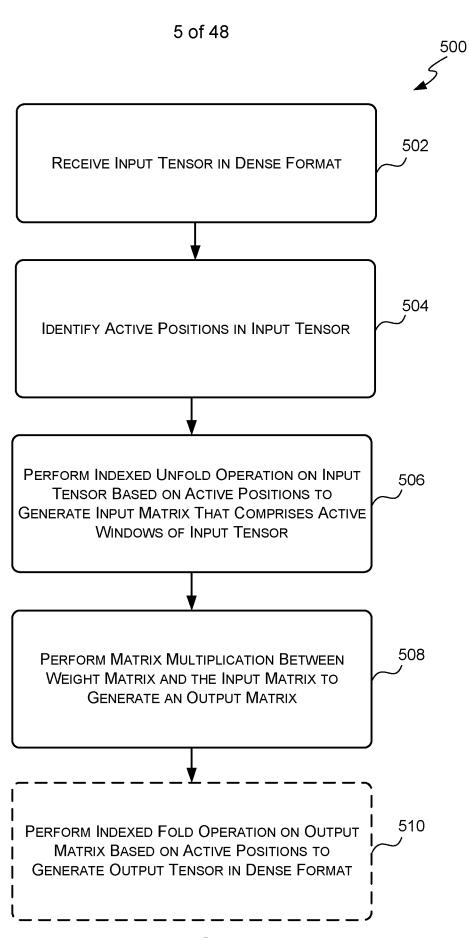

- 5 **[0055]** FIG. 5 is a flow diagram of an example method of performing a sparse submanifold convolution using a GPU;

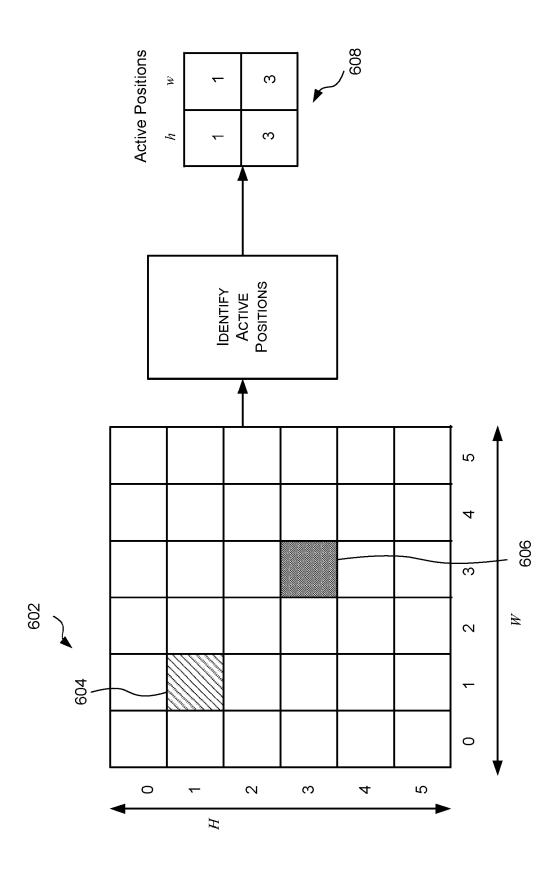

- **[0056]** FIG. 6 is a schematic diagram illustrating an example method of generating a list of active positions for an example input tensor;

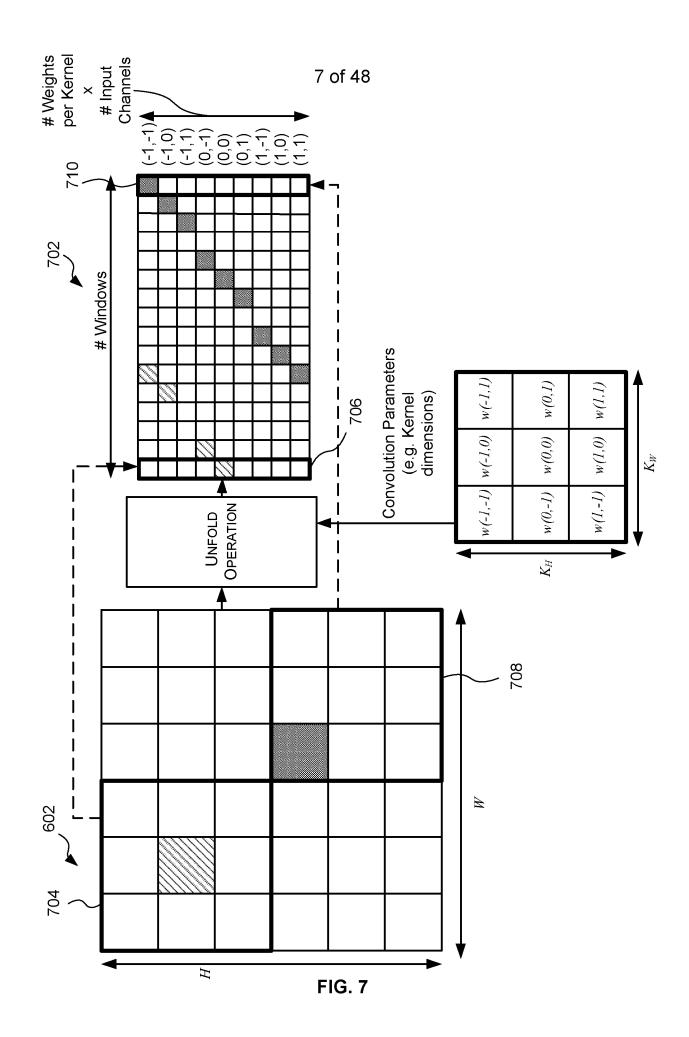

- [0057] FIG. 7 is a schematic diagram illustrating an example unfold operation;

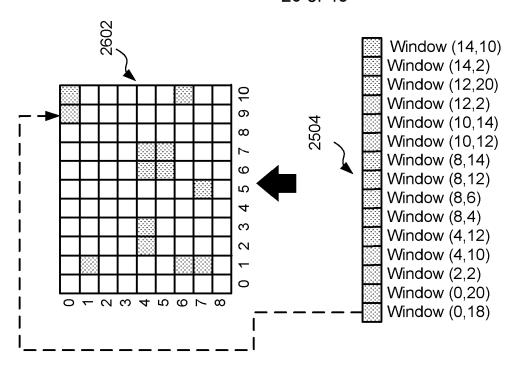

- 10 **[0058]** FIG. 8 is a schematic diagram illustrating an example indexed unfold operation to implement a sparse submanifold convolution;

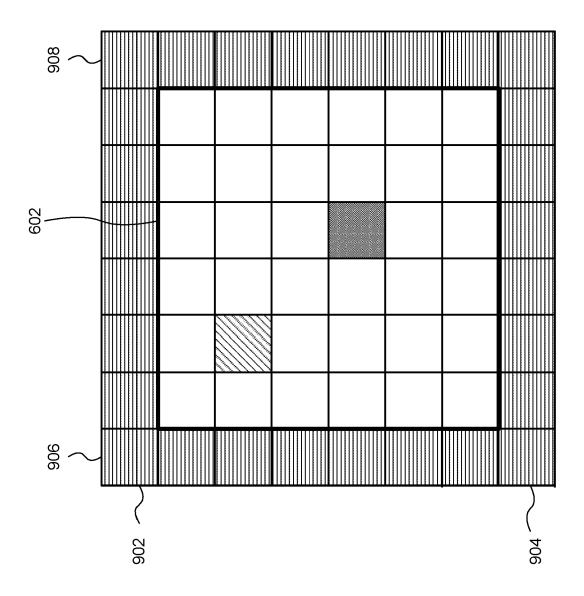

- [0059] FIG. 9 is a schematic diagram illustrating an example padded input tensor;

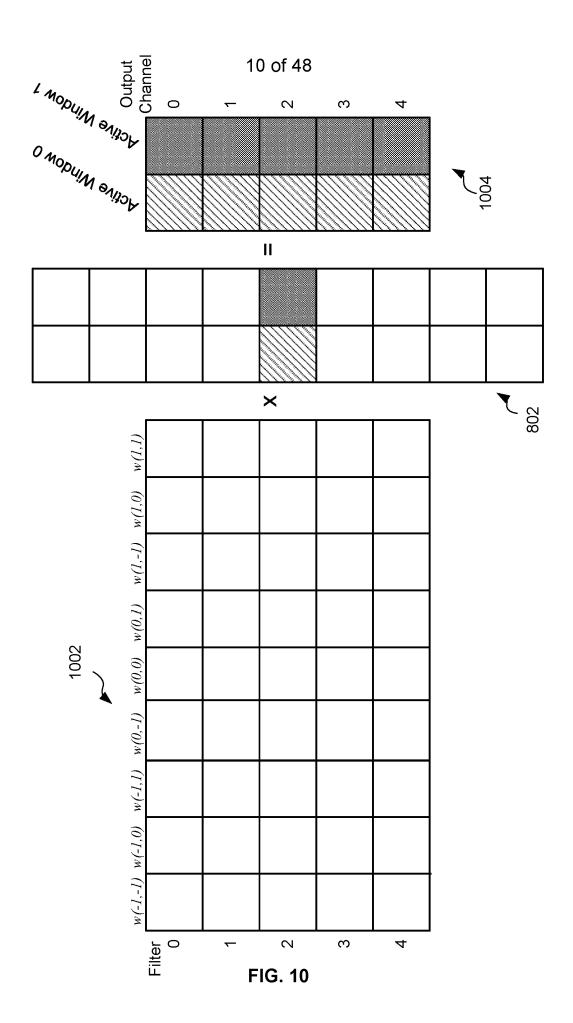

- **[0060]** FIG. 10 is a schematic diagram illustrating an example matrix multiplication between a weight matrix and an input matrix to implement a sparse submanifold convolution;

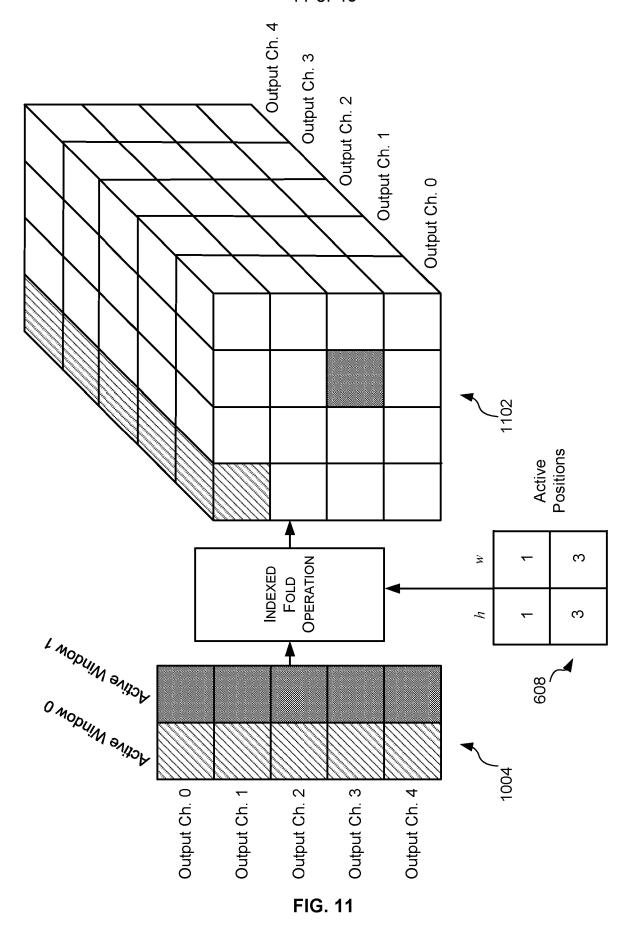

- 15 **[0061]** FIG. 11 is a schematic diagram illustrating an example indexed fold operation to implement a sparse submanifold convolution;

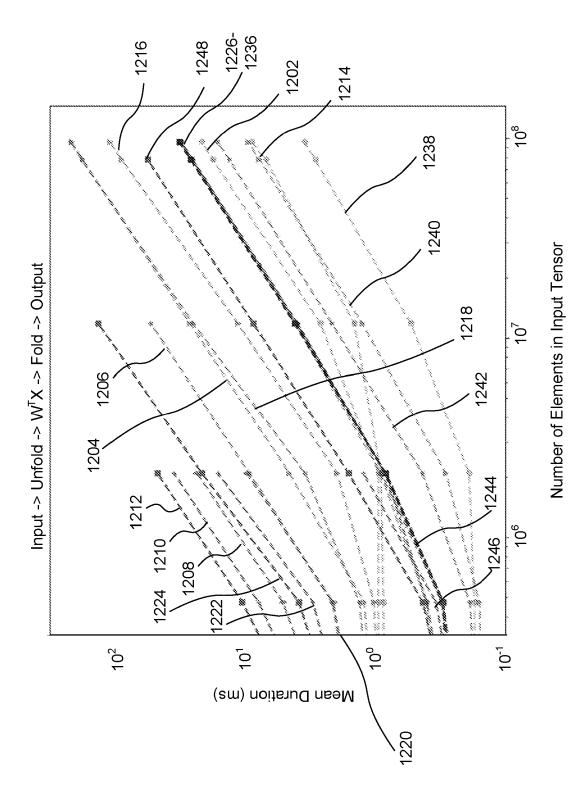

- **[0062]** FIG. 12 is a graph of the mean duration to implement an example sparse submanifold convolution on a GPU for different sized 3D input tensors using different methods and different levels of sparsity;

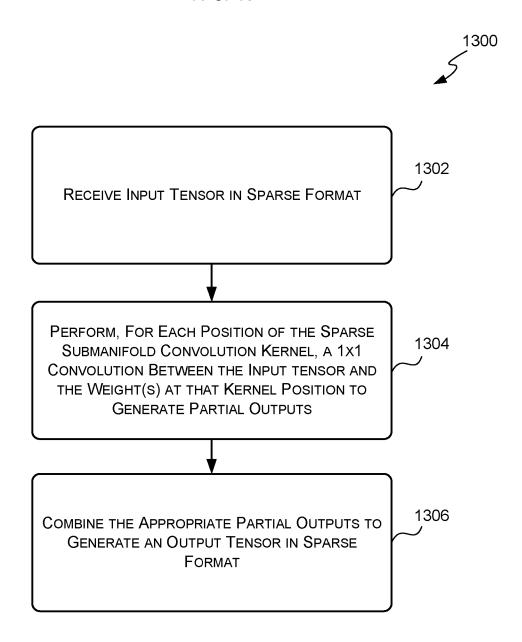

- 20 **[0063]** FIG. 13 is a flow diagram of an example method of implementing a sparse submanifold convolution using a neural network accelerator;

- [0064] FIG. 14 is a schematic diagram illustrating dense and sparse formats of an example tensor;

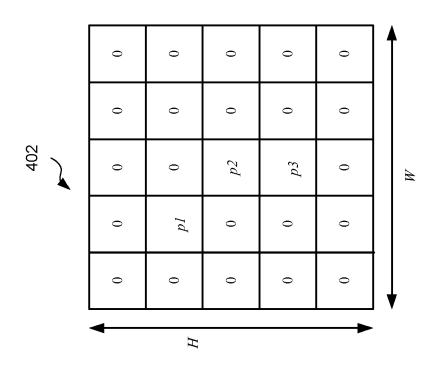

- [0065] FIG. 15 is a schematic diagram illustrating the sub-filters for an example filter to implement a sparse submanifold convolution;

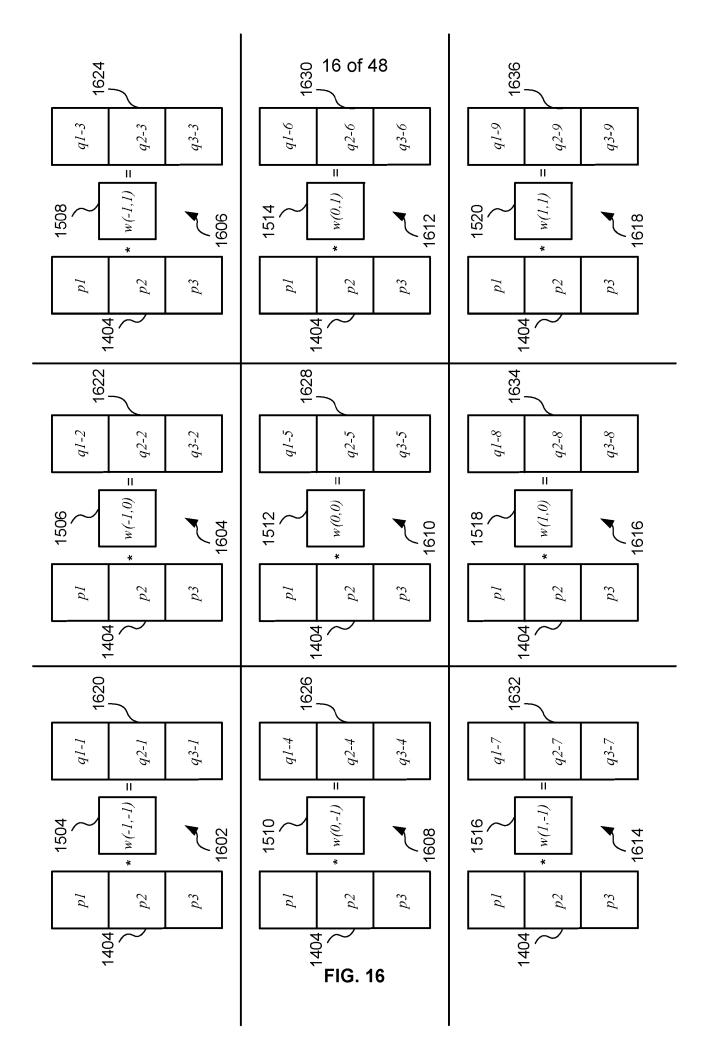

- **[0066]** FIG. 16 is a schematic diagram illustrating 1x1 convolutions performed on the input tensor in sparse format of FIG. 14 using the sub-filters of FIG. 15 to implement an example sparse submanifold convolution;

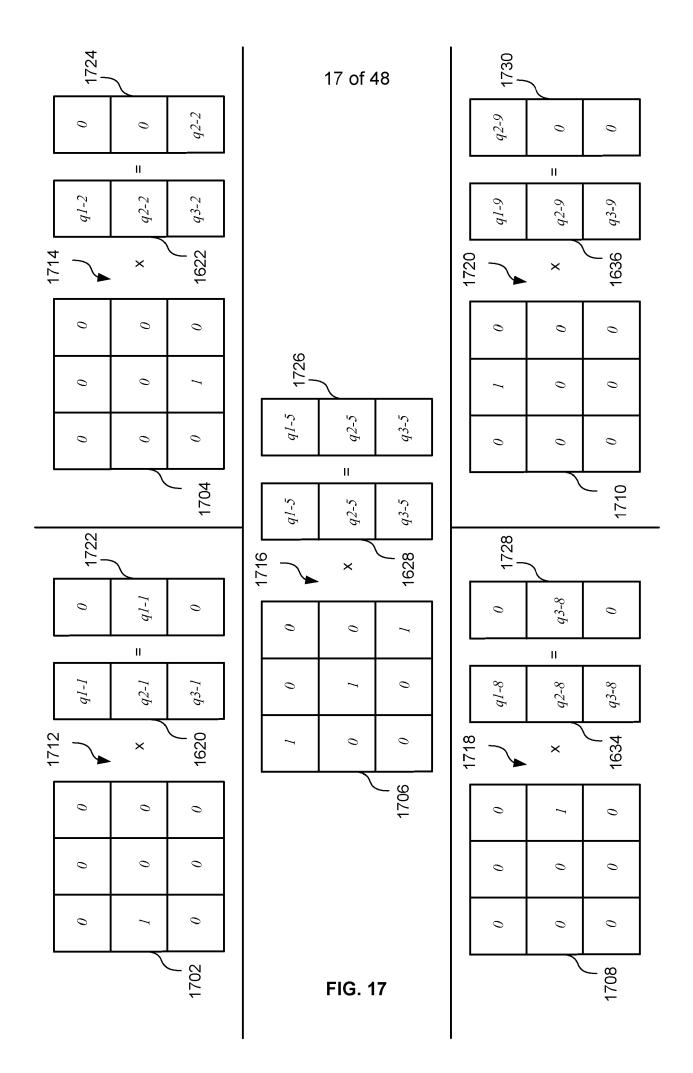

- **[0067]** FIG. 17 is a schematic diagram illustrating matrix multiplications between the 1x1 convolution outputs of FIG. 16 and corresponding scatter matrices to implement an example sparse submanifold convolution;

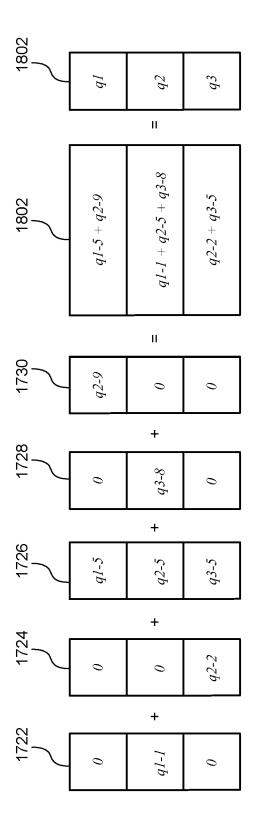

- **[0068]** FIG. 18 is a schematic diagram illustrating combining the matrix multiplication outputs of FIG. 17 to implement an example sparse submanifold convolution;

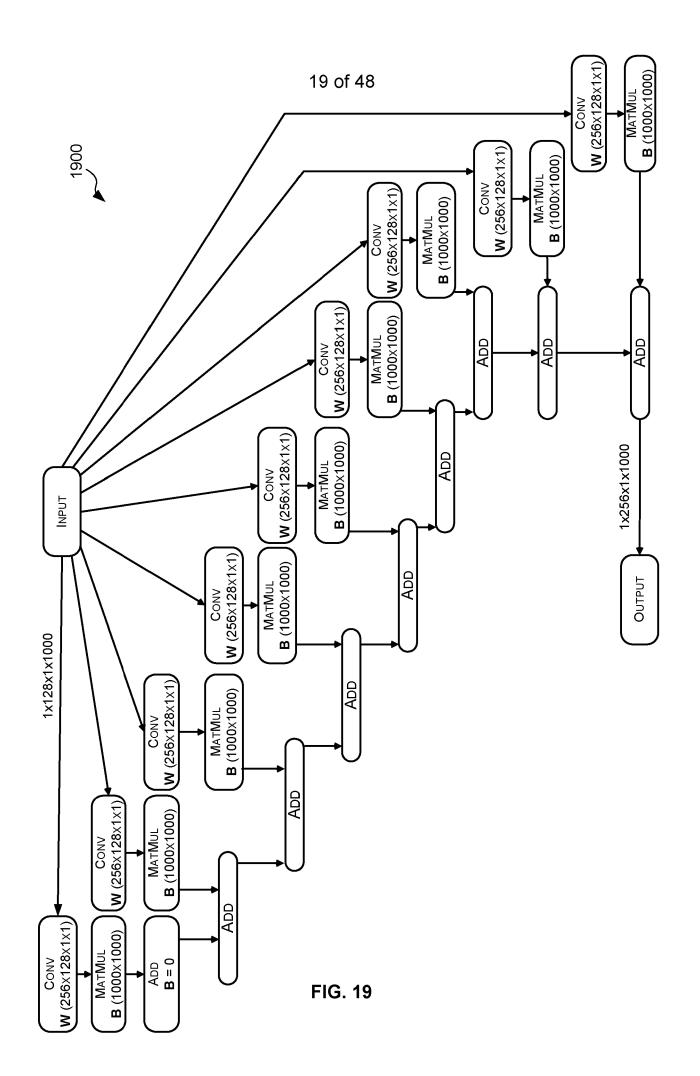

- **[0069]** FIG. 19 is an example inference graph to implement the method of FIG. 13 for an example sparse submanifold convolution in accordance with a first example;

- **[0070]** FIG. 20 is an example inference graph to implement the method of FIG. 13 for an example sparse submanifold convolution in accordance with a second example;

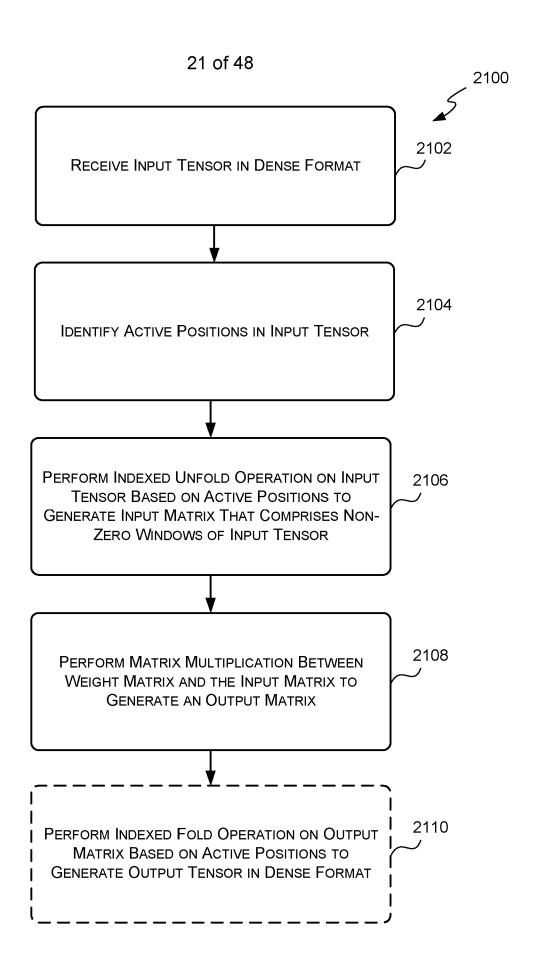

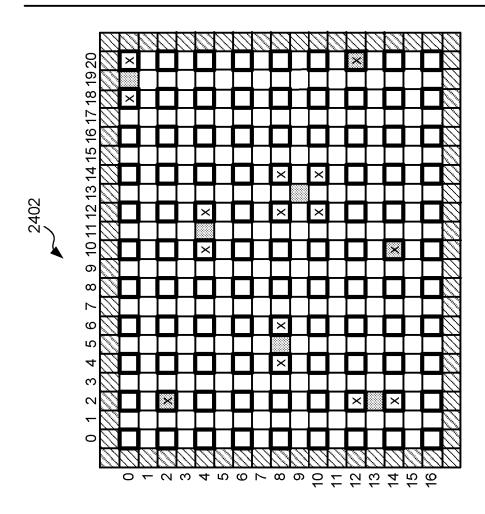

- [0071] FIG. 21 is a flow diagram of an example method to implement a standard convolution using a GPU;

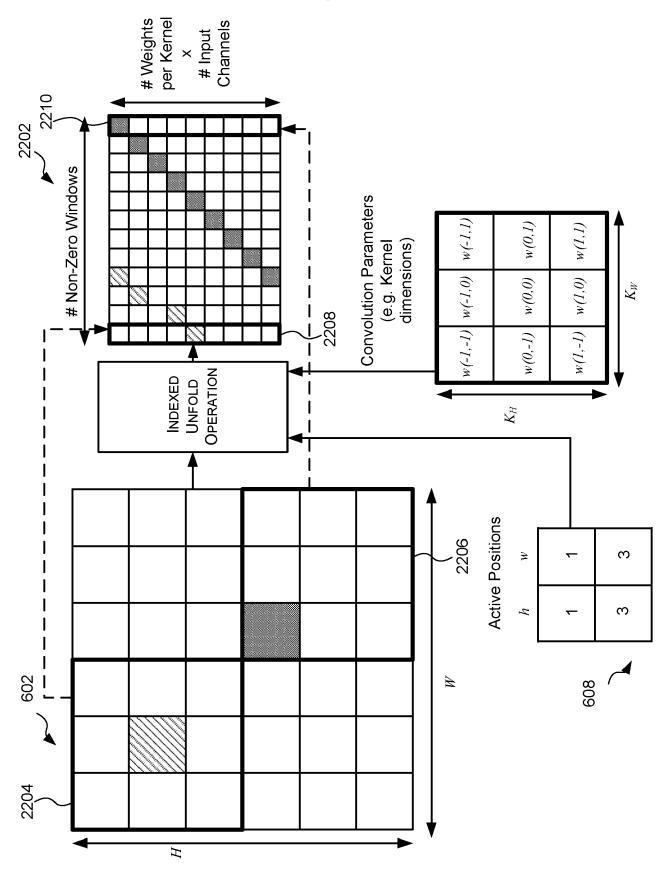

- **[0072]** FIG. 22 is a schematic diagram illustrating an example indexed unfold operation performed on an example input tensor to implement an example standard convolution;

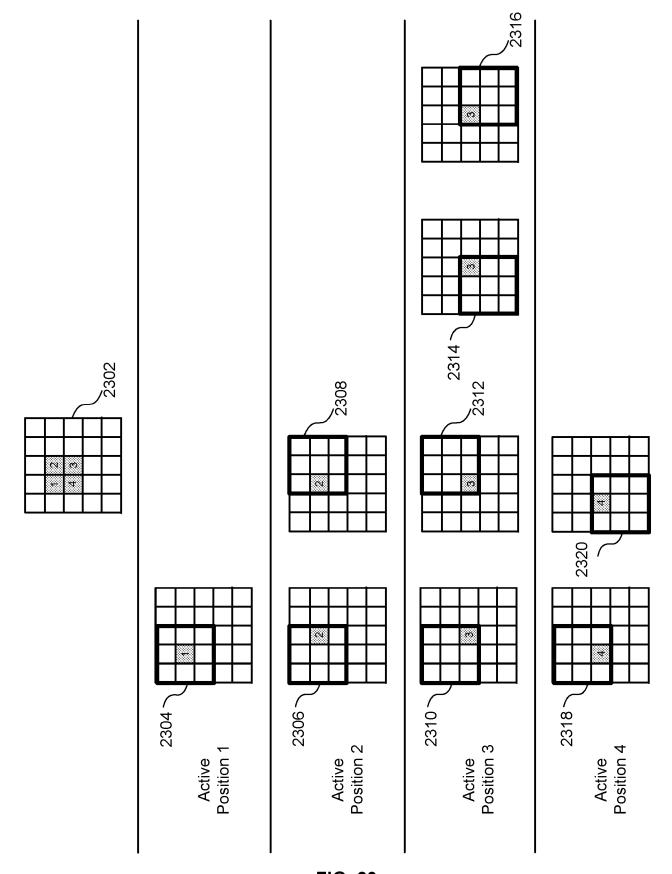

- [0073] FIG. 23 is a schematic diagram illustrating identifying the windows that each of a plurality of active positions form part of to implement a standard convolution;

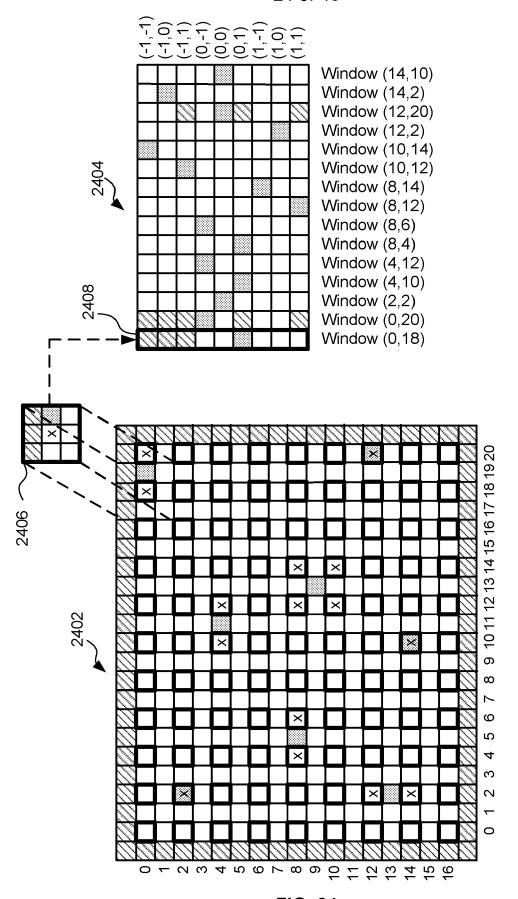

- **[0074]** FIG. 24 is a schematic diagram illustrating an example unfold operation performed on another example input tensor to implement an example standard convolution;

- [0075] FIG. 25 is a schematic diagram illustrating a matrix multiplication between the input matrix generated in FIG. 24 and a weight matrix to implement an example standard convolution;

- 20 **[0076]** FIG. 26 is a schematic diagram illustrating an example indexed fold operation performed on the output of the matrix multiplication of FIG. 25 to implement an example standard convolution;

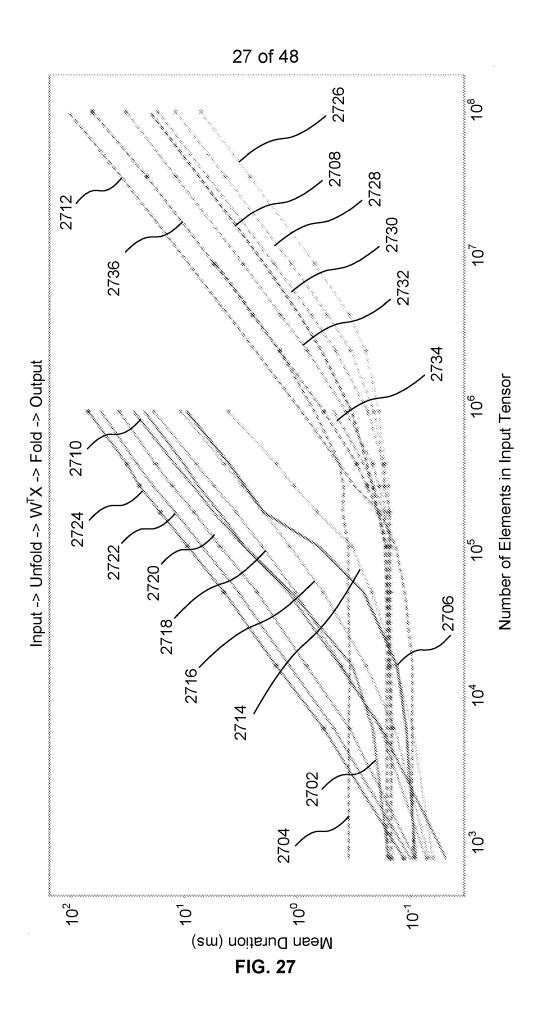

- **[0077]** FIG. 27 is a graph of the mean duration to implement an example 2D convolution operation on a GPU or CPU for different sized 2D input tensors and different levels of sparsity using different methods;

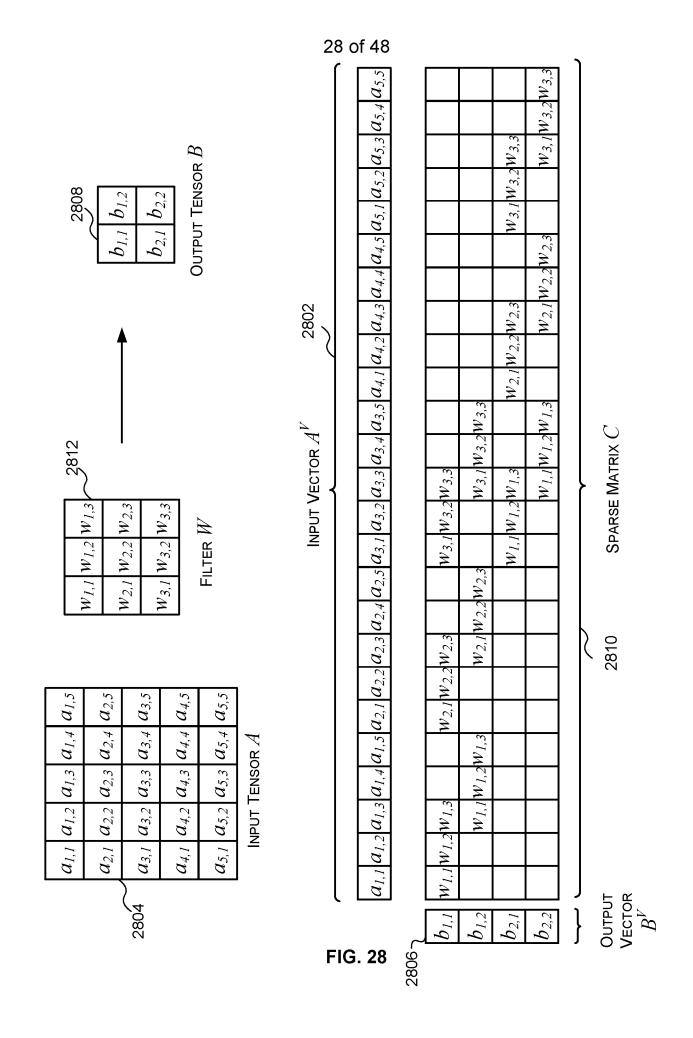

- 25 [0078] FIG. 28 is a schematic diagram illustrating an example 2D convolution;

- [0079] FIG. 29 is a schematic diagram illustrating an example 2D deconvolution;

- **[0080]** FIG. 30 is a schematic diagram illustrating an example 2D deconvolution;

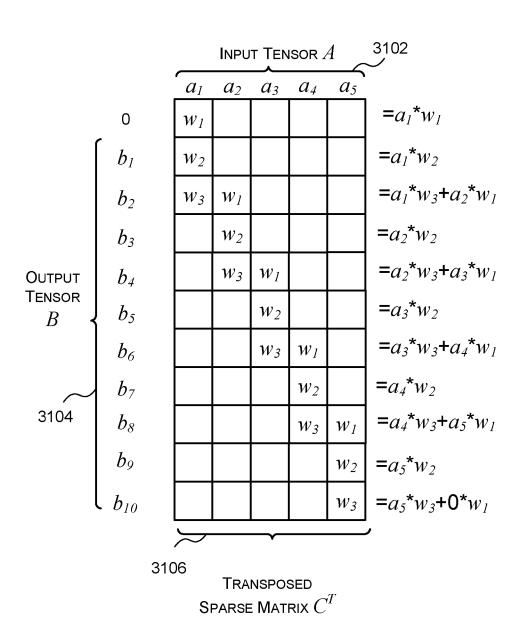

- **[0081]** FIG. 31 is a schematic diagram illustrating implementing an example 2D deconvolution using a transposed sparse matrix;

- **[0082]** FIG. 32 is a schematic diagram illustrating implementing an example 2D deconvolution using a padded input tensor;

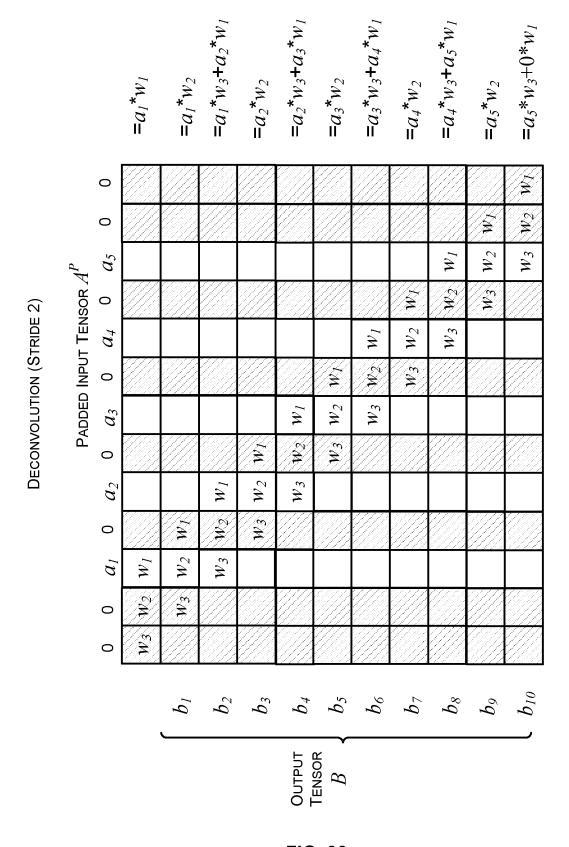

- **[0083]** FIG. 33 is a schematic diagram illustrating implementing an example 2D deconvolution using multiple direct convolutions;

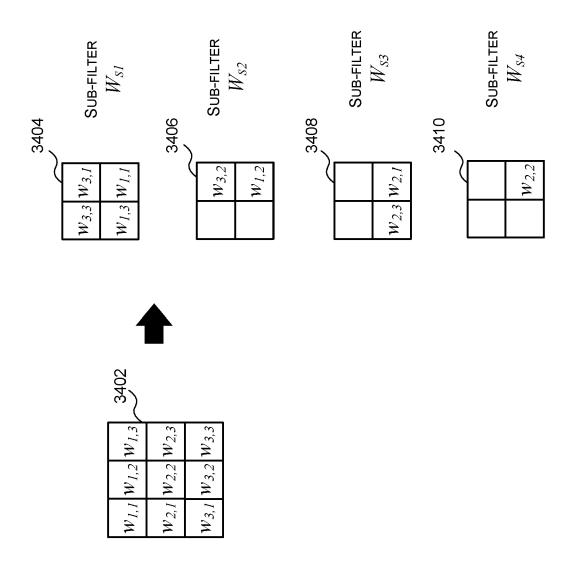

- [0084] FIG. 34 is a schematic diagram illustrating the sub-filters for implementing an example 2D deconvolution using multiple direct convolutions;

- **[0085]** FIG. 35 is a schematic diagram illustrating interleaving the outputs of multiple direct convolutions:

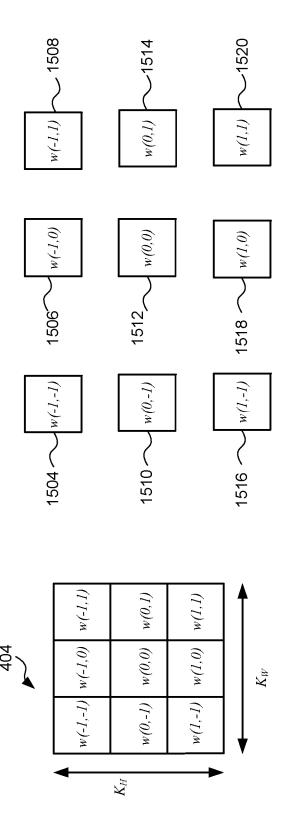

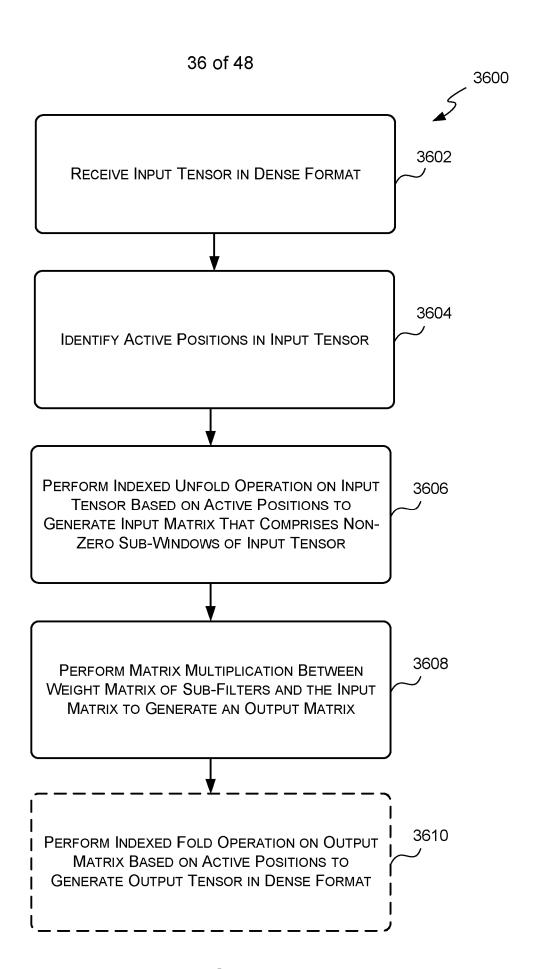

- [0086] FIG. 36 is a flow diagram of an example method of implementing a deconvolution using a 10 GPU;

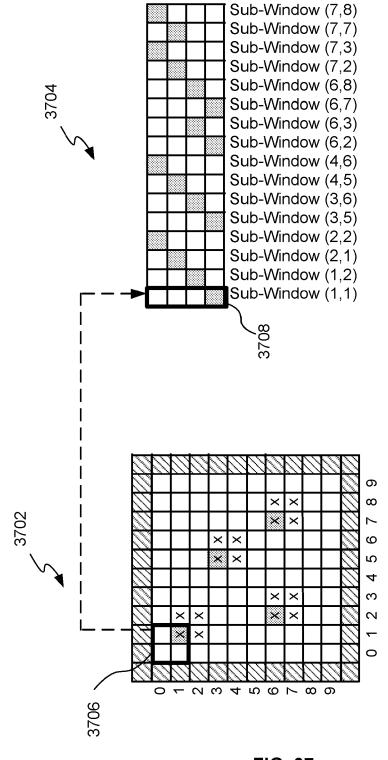

- **[0087]** FIG. 37 is a schematic diagram illustrating an example indexed unfold operation performed on an example input tensor to generate an input matrix to perform an example deconvolution;

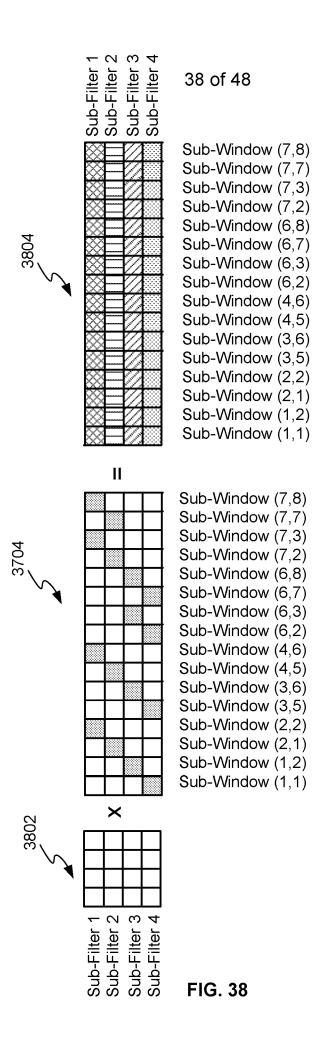

- [0088] FIG. 38 is a schematic diagram illustrating a matrix multiplication between the input matrix of FIG. 37 and a weight matrix to perform an example deconvolution;

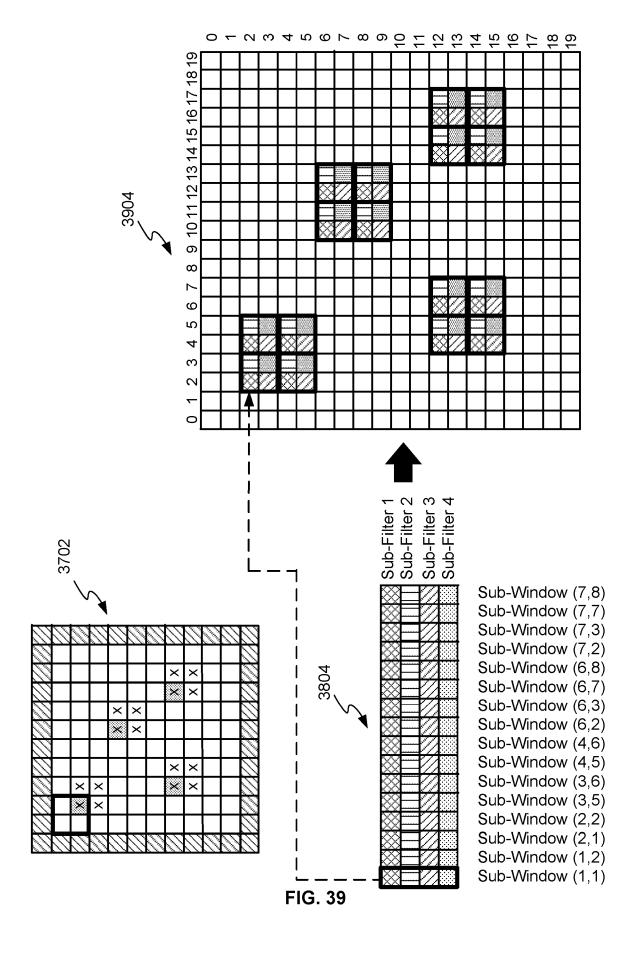

- **[0089]** FIG. 39 is a schematic diagram illustrating an indexed fold operation performed on the output matrix of FIG. 38 to perform an example deconvolution;

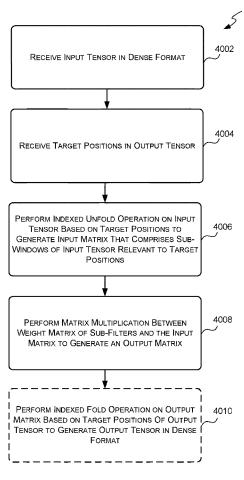

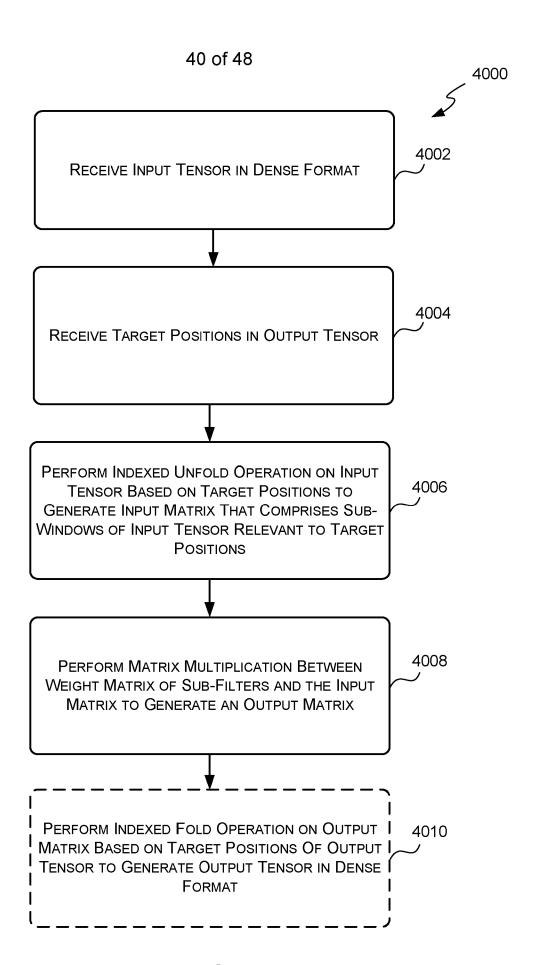

- **[0090]** FIG. 40 is a flow diagram of an example method of implementing a sparse submanifold deconvolution using a GPU;

- [0091] FIG. 41 is a schematic diagram illustrating an example indexed unfold operation performed on an input tensor to generate an input matrix to implement an example sparse submanifold deconvolution;

- [0092] FIG. 42 is a schematic diagram illustrating a matrix multiplication between the input matrix of FIG. 41 and a weight matrix to implement an example sparse submanifold deconvolution;

- [0093] FIG. 43 is a schematic diagram illustrating an indexed fold operation performed on the output matrix of FIG. 42 to implement an example sparse submanifold deconvolution;

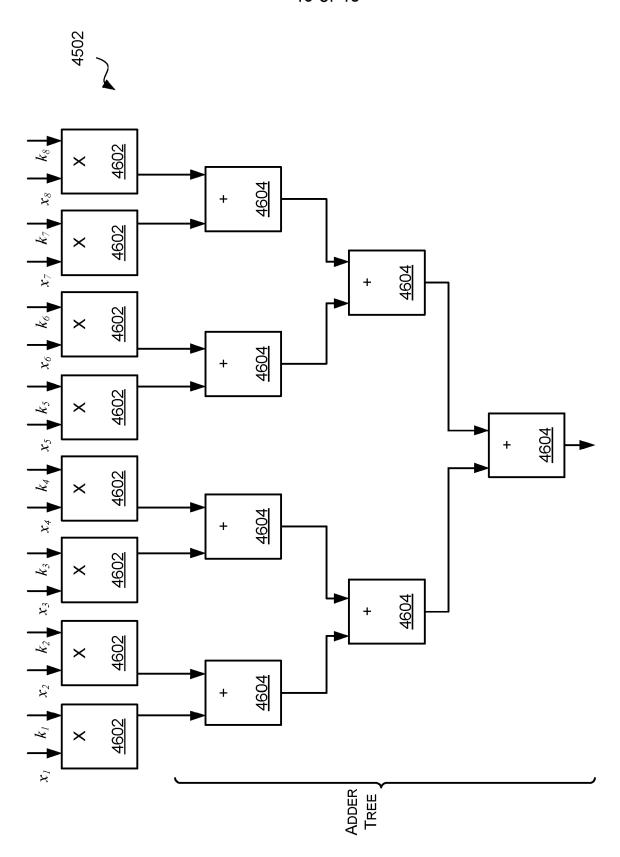

- **[0094]** FIG. 44 is a block diagram of an example neural network accelerator for implementing any of the NNA-based methods described herein;

- [0095] FIG. 45 is a block diagram of an example implementation of the convolution processing unit of FIG. 44;

- [0096] FIG. 46 is a block diagram of an example implementation of a convolution engine of FIG. 45;

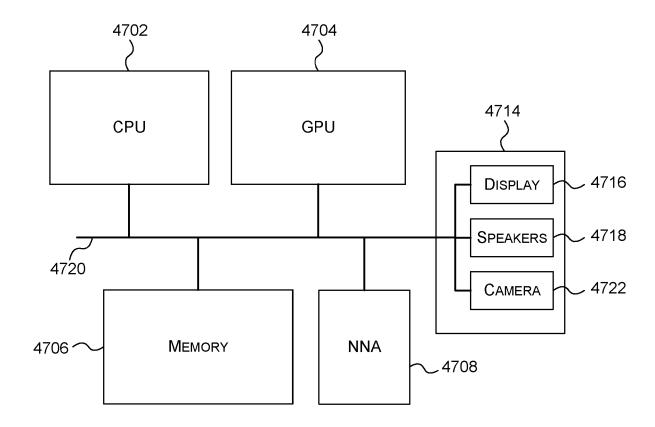

**[0097]** FIG. 47 is a block diagram of an example computer system in which a graphics processing unit and/or a neural network accelerator described herein may be implemented; and

**[0098]** FIG. 48 is a block diagram of an integrated circuit manufacturing system for generating an integrated circuit embodying a graphics processing unit, a neural network accelerator, a convolution processing unit or a convolution engine described herein.

**[0099]** The accompanying drawings illustrate various examples. The skilled person will appreciate that the illustrated element boundaries (e.g., boxes, groups of boxes, or other shapes) in the drawings represent one example of the boundaries. It may be that in some examples, one element may be designed as multiple elements or that multiple elements may be designed as one element. Common reference numerals are used throughout the figures, where appropriate, to indicate similar features.

#### DETAILED DESCRIPTION

10

15

20

25

30

35

**[0100]** The following description is presented by way of example to enable a person skilled in the art to make and use the invention. The present invention is not limited to the embodiments described herein and various modifications to the disclosed embodiments will be apparent to those skilled in the art.

[0101] Embodiments will now be described by way of example only.

**[0102]** As described above, as sparse submanifold convolution layers are becoming more popular in neural networks it is important to be able to implement sparse submanifold convolutions in a hardware efficient manner (e.g., in a manner that requires less silicon area or less processing power).

[0103] Methods which are known to the Applicant, which is not an admission that they are known outside of the Applicant company or that they are well-known, for implementing a sparse submanifold convolution on a GPU, such as those implemented by TorchSparse and SpConv, include performing a gather operation, a matrix multiply (MatMul) operation, and a scatter operation. Specifically, in GPU implementations: (1) the active points in the input tensor are determined; (2) a HashMap is then built to store the information of which (active) points need to be multiplied by each weight; (3) a gather operation is then used to generate, from the HashMap, an input data matrix (or a set of input data matrices) and a parameter/weight matrix (or a set of parameter matrices) so that each (active) point is multiplied by the relevant weight; (4) a matrix multiplication is performed between the input matrix/matrices and the parameter matrix/matrices to generate partial results; and (5) a scatter-add operation is then performed, based on the HashMap, to combine the partial results to generate the final outputs and put them in the correct location in the output tensor. However, the gather and scatter operations can be time and resource intensive to implement.

**[0104]** Accordingly, the inventors have developed methods for implementing a sparse submanifold convolution in a more hardware efficient manner, compared to the methods known to the Applicant, using a GPU and/or a neural network accelerator (NNA) which take advantage of the hardware features of GPUs and NNAs respectively. Specifically, the methods described herein for implementing a submanifold convolution are particularly adapted to take into consideration the internal functioning of a GPU and/or an NNA. In particular, as described in more detail below, the GPU-based methods are designed to take advantage of the parallel architecture (e.g. SIMD architecture) of GPUs and the NNA-based methods are designed to take advantage of the architecture of NNAs that enable convolution operations to be implemented in a hardware efficient (in terms of time and resources) manner.

# **GPU Implementations of Sparse Submanifold Convolution**

10

15

20

25

30

35

[0105] The inventors have determined that a sparse submanifold convolution can be performed efficiently on a GPU by performing an indexed unfold operation on an input tensor in dense format to generate an input matrix of active windows of the input tensor, performing a matrix multiplication between a weight matrix and the input matrix, and, optionally, performing an indexed fold operation on the output of the matrix multiplication to generate an output tensor in dense format. GPUs are often implemented using a single instruction multiple data (SIMD) architecture. The inventors have determined that indexed unfold operations, matrix multiplications, and indexed fold operations can all be performed very efficiently in a parallelised manner using a SIMD architecture allowing a sparse submanifold convolution to be performed in a very hardware and resource efficient manner using the specific hardware structure of a GPU in the manner described herein.

[0106] Reference is now made to FIG. 5 which illustrates an example method 500 of implementing a sparse submanifold convolution using a GPU. The method 500 begins at block 502 where an input tensor in dense format is received at the GPU. An input tensor in dense format, which may also be referred to as a densified input tensor, comprises each possible element of the tensor regardless of whether the element is at an active position or not. As described above, an active location or position in an input tensor is a height and width position or location (which may also be referred to as an x,y position, a y,x position, a column and row position, or a row and column position) in which at least one channel of the input tensor has a non-zero value. For example, if the element at height and width position (1,2) of the first channel of an input tensor is non-zero, then that element is at an active position, and the elements at height and width position (1,2) of the other channels are also at an active position, regardless of whether they are non-zero. In contrast, an input tensor in sparse format includes only elements of the corresponding tensor in dense format that are at an active location or position. In other words, an input tensor in sparse format does not include the elements of the input tensor in dense format at non-active positions or locations. For example, if all of the elements at height and width position (1,1) of the input tensor in dense format are zero then the height and width position (1,1) is not an active position and thus the sparse version of that input tensor will not include any elements at height and width position (1,1) of the input tensor in dense format. Once the input tensor in dense format has been received, the method 500 proceeds to block 504.

**[0107]** At block 504, the GPU identifies the active locations or positions in the received input tensor. As noted above, an active location is a height and width position or location of the input tensor in which at least one channel of the input tensor has a non-zero value. Each active location or position may be identified with a set of indices – a height or row index, and a width or column index.

[0108] The active locations or positions in the received input tensor may be identified using any suitable technique. For example, there are available software modules, such as the nonzero function in PyTorch®, which can be run efficiently on a GPU, which, when provided with an input tensor will return a list of non-zero co-ordinates of that input tensor. This list will include the coordinates of every non-zero element in the input tensor. This means that if there are two channels that have non-zero elements at the same height and width position, then that height and width position will be identified twice, once for each channel. Since an active location is a height and width position in which at least one channel has a non-zero value, the list of co-ordinates generated by the nonzero function may be further processed to identify only the unique height and width positions or co-ordinates in the list. In other words, the list of the co-ordinates generated by the nonzero function may be further processed to eliminate duplicate height and width positions or coordinates. In another example, the active locations or positions in the received input tensor may be identified by first using SpConv's from dense function (which relies on the PyTorch®'s to sparse function) to generate a tensor in sparse format, in coordinate format, from the input tensor in dense format and then identifying the active locations from the tensor in sparse format.

10

15

20

25

30

35

[0109] In some cases, the output of this block 504 may be a list of the height and width (or column and row) co-ordinates or indices of the active positions. For example, FIG. 6 shows an example 6x6 input tensor 602 with a single channel. The input tensor 602 has only two active positions 604, 606. Accordingly, the output of block 504 for this example input tensor 602 may be an active position list 608 that comprises the height and width co-ordinates or indices for each of the two active positions 604, 606. Specifically, the active position list 608 may comprise an entry for each active position that identifies a height (e.g. row) and width (e.g. column) location or position. For example, as shown in FIG. 6, the active position list 608 may comprise an entry for the first active position 604 that identifies its location as a height (row) of 1 and a width (column) of 1, and an entry for the second active position 606 that identifies its location as a height (row) of 3 and a width (column) of 3.

**[0110]** Once the active locations or positions in the received input tensor have been identified, the method 500 proceeds to block 506.

**[0111]** At block 506, the GPU performs an indexed unfold operation (which may also be referred to as a sparse unfold operation) on the received input tensor based on the active locations or

positions identified in block 504 to generate an input matrix that comprises the elements of the active windows of the input tensor. In a standard unfold operation (which may also be referred to as an image to column (im2col) operation or a default unfold operation), the elements of the input tensor in each window are placed in a column of the input matrix. As described above, each window generates one output element per channel of the output tensor. Accordingly, if there are P elements in each channel of the output tensor (meaning there are P windows of the input tensor), there will be P columns in the input matrix of a standard unfold operation. An unfold operation can also be described as a flattening operation. A standard unfold operation will now be explained via an example.

10

20

25

30

35

[0112] Reference is now made to FIG. 7 which illustrates a standard unfold operation performed on the example 6x6 input tensor 602 of FIG. 6 to perform a 2D convolution with filters with 3x3 kernels to generate an input matrix 702. In this example, each channel of the output tensor will be of size 4x4, therefore there are sixteen elements in each channel of the output tensor. Each element in a channel of the output tensor is generated from a different window of the input tensor 602. Since there are sixteen windows of the input tensor used to generate the output tensor, there are sixteen columns in the input matrix 702. Each column of the input matrix 702 comprises the elements of one window of the input tensor 602, wherein each element in a window is placed in a different row. In this example each window comprises a 3x3 block of elements in the input tensor 602 thus there are nine elements per window. As a result, the input matrix 702 has nine rows. Each row corresponds to a position in the window, and the elements of a window are placed in the rows in accordance with their position in the window. In the example shown in FIG. 7 the elements in a window are unrolled from left to right and top to bottom, such that the element in the top left corner of the window is placed in the first row, the element in the centre of the window is placed in the fifth row, and the element in the bottom right of the window is placed in the last or ninth row. For example, the elements in the first window 704 of the input tensor 602 are placed in the first column 706 of the input matrix 702 as shown in FIG. 7; and the elements in the last window 708 of the input tensor 602 are placed in the last column 710 of the input matrix 702 as shown in FIG. 7. However, it is evident that this is an example only and the elements of a window can be placed in the input matrix in any order so long as the elements of each window are placed in the same order (e.g. the elements of the first window are placed in a column in the same order as the elements of a second window are placed in a second column).

**[0113]** Although in the example of FIG. 7 the input tensor 602 only has one channel, it will be evident that a standard unfold operation can be equally applied to input tensors with more than one channel by adding n rows to the input matrix for each additional channel, where n is the number of elements in the filter kernel. For example, where each kernel is 3x3 such that each window comprises 9 elements of the input tensor per channel, then 9 rows are added to the input matrix for each additional channel of the input tensor.

**[0114]** However, as explained above, in a sparse submanifold convolution, elements of the output tensor are only generated for windows of the input tensor in which one or more

predetermined elements (the centre element in this example) of the window is/are active (which may be referred to herein as the active windows). Therefore, only the columns of the input matrix 702 corresponding to active windows are used in a sparse submanifold convolution. As a result, there are lot of columns in an input matrix generated by a standard unfold operation that are not required for a sparse submanifold convolution.

[0115] Accordingly, the inventors have developed an indexed unfold operation in which the input tensor only comprises a column for each active window, wherein the active windows are identified from the active locations or positions identified in block 504. Specifically, the indexed unfold operation uses the active locations or positions, and the sparse submanifold convolution parameters (e.g. stride, dilation, kernel size) to determine the active windows of the input tensor, and then generates an input matrix with a column for each active window, wherein each column comprises the elements in the corresponding active window. For example, as shown in FIG. 8, if a sparse submanifold convolution with 3x3 kernels at strides of 1 is to be performed on the input tensor 602 of FIG. 6 (with only two active positions) then there are only two active windows 804, 806. An indexed unfold operation performed on the input tensor 602 therefore results in an input matrix 802 with only two columns – the first column corresponds to the first active window 804 with the first active position at the centre, and the second column corresponds to the second active window 806 with the second active position at the centre.

10

15

35

[0116] In some cases, padding may be applied to the input tensor so that any active point on an edge (i.e. in the first/last column or first/last row) of the input tensor can be the centre of a window. The number of rows and columns of padding that are added are based on the size of the kernel. For example, where a filter has a kernel with a height  $K_H$  then  $\left\lfloor \frac{K_H}{2} \right\rfloor$  rows of padding may be added to each of the top and the bottom of the input tensor; and where a filter has a kernel with a width  $K_W$  then  $\left\lfloor \frac{K_W}{2} \right\rfloor$  columns of padding may be added to each of the left and the right of the input tensor. For example, as shown in FIG. 9, for a 3x3 kernel, a row of padding 902, 904 may be added to each of the top and bottom of the input tensor 602, and a column of padding 906, 908 may be added to each of the left and right of the tensor. Where the input tensor has been padded in this manner, and the stride is one in each dimension, there will be an active window for each active position of the input tensor and the input matrix generated by an indexed unfold operation will have a column for each active position.

**[0117]** Using an indexed unfold operation, as opposed to a standard unfold operation, to generate an input matrix can significantly reduce the size of the input matrix which can significantly reduce the computations to implement the matrix multiplication of block 508 (described below). Table 1 illustrates the size of the input matrix when generated from an indexed unfold operation compared to the size of the input matrix when generated from a standard unfold operation for an example input tensor of size [1, 1, 1000, 1000] (i.e. one batch, one channel, a height of 1000 and a width of 1000) for a sparse submanifold convolution with a 3x3 kernel, strides and dilations of 1 and no padding, for different levels of sparsity. Generally the sparser the input tensor, the smaller the

input matrix generated by an indexed unfold operation and the more memory efficient the method described with respect to FIG. 5 is.

Table 1

| Sparsity                        | 0%           | 50%          | 80%          | 90%          | 99%         |

|---------------------------------|--------------|--------------|--------------|--------------|-------------|

| Standard<br>Unfold<br>Operation |              |              | [1,9,996004] |              |             |

| Indexed<br>Unfold<br>Operation  | [1,9,996004] | [1,9,500000] | [1,9,200000] | [1,9,100000] | [1,9,10000] |

5

10

15

20

25

[0118] The indexed unfold operation may be implemented on the GPU in any suitable manner. In one example, where there is an active window per active position, the indexed unfold operation may be implemented by indexing each active location (e.g. from 0 to the number of active locations) and, for each active position/location, identifying the surrounding positions/locations (i.e. the positions/locations in the window of the input tensor centred at the active position) using multiple nested loops, one for each dimension of a window. For example, where the windows are 2D windows with a height dimension and a width dimension, there may be one loop for the height dimension and another for the width dimension. Specifically, for a 2D convolution with 2D windows, an offset may be created for each of the height and width dimensions that is equal to  $\frac{k-1}{2}$ where k is the size of the kernel in that dimension, and then the GPU is configured to loop from offset to +offset from the respective active location. Where the windows are 3D with a channel dimension, there may be an additional loop that loops through the channels. The element at each identified position is then copied into the appropriate position of the input matrix. As described above, each column in the input matrix may correspond to one active window. The values at the offset positions, starting from top left, may be ordered from top down. This may be implemented by having a separate thread for each active location/position. Since the same operations are performed for each active position, this can be efficiently implemented by a SIMD architecture e.g. applying a single instruction (or set of instructions) to multiple pieces of input data (i.e., multiple active positions).

**[0119]** Where there are less active windows than there are active positions due to the stride, dilation, or other sparse submanifold convolution parameters, then the indexed unfold operation may be implemented on the GPU by, prior to identifying the positions/locations surrounding the active position (e.g. using the nested loops), performing a validity check to determine if the active position produces or induces an active window, and only identifying the surrounding

positions/locations and adding the elements from the identified positions to the input matrix if the active position induces an active window.

**[0120]** In some cases, in addition to receiving the input tensor in dense format, and the active positions, the indexed unfold operation may also receive a zeroed input matrix with the desired shape (e.g. height = elements per kernel x number of channels, width = number of active windows) and the GPU may be configured to write the active window elements to the appropriate location in the received input matrix.

**[0121]** Once the GPU has performed an indexed unfold operation on the input tensor to generate an input matrix with the elements of each active window of the input tensor, the method 500 proceeds to block 508.

10

15

20

25

3.0

35

[0122] At block 508, the GPU performs a matrix multiplication operation (which may be referred to as a MatMul operation) between a weight matrix and the input matrix generated in block 506 to generate an output matrix. FIG. 10 illustrates an example of a matrix multiplication between a weight matrix 1002 and the input matrix 802 of FIG. 8. The weight matrix 1002 may comprise a row for each filter, and a column for each weight in a filter. For example, in FIG. 10 there are five filters with 3x3 kernels and one channel (thus each filter comprises nine weights). Therefore, the weight matrix 1002 comprises five rows and nine columns. Each column corresponds to a position in the filter and the weights of a filter are placed in the columns in accordance with their place in the filter. In the example shown in FIG. 10 the weights in a filter are unrolled from left to right and top to bottom, such that the weight in the top left corner of a filter is placed in the first column, the weight in the centre of the filter is placed in the fifth column, and the weight in the bottom right of the filter is placed in the last or ninth column. It will be evident to a person of skill in the art that this is an example only and that the weights can be placed in any order in the weight matrix so long as their order corresponds to the order of the elements of each active window in the input matrix. Specifically, if element at position (-1,-1) of an active window is placed in row 0, then the weight at position (-1,-1) of the filter should be placed in column 0.

**[0123]** The matrix multiplication between the weight matrix 1002 and the input matrix 802 generates an output matrix 1004 which comprises, for each active window, an output element for each channel of the output tensor (i.e., for each filter of the sparse submanifold convolution). The output matrix 1004 may have a column for each active window and a row for each output channel such that each column comprises an output element for the corresponding active window for each output channel. In the example shown in FIG. 10 there are two active windows and five output channels, so the example output matrix 1004 has two columns and five rows. The matrix multiplication may be parallelised on the GPU, by, for example, processing each column of the input matrix in a separate thread.

[0124] Once the GPU has performed the matrix multiplication the method 500 may end or the method 500 may proceed to block 510. Specifically, the output matrix 1004 generated in block 508

comprises all of the non-zero elements of the output tensor (in other words the output matrix corresponds to the output tensor in sparse format) and thus the output matrix 1004 may be simply output, or an output tensor in dense format may be first generated from the output matrix 1004. When the method is performed as part of a neural network, whether or not the output matrix is converted to an output tensor in dense format may depend on what input tensor format is expected by the next layer in the neural network.

**[0125]** At block 510, the GPU performs an indexed fold operation on the output matrix generated in block 508 to generate an output tensor 1102 in dense format. The indexed fold operation is the opposite of the indexed unfold operation performed in block 506. Specifically, the indexed fold operation uses the active windows to generate an output tensor in dense format (e.g. a densified output tensor) from the output matrix 1004 generated in block 508. In other words, the indexed fold operation generates an output tensor with the elements of the output matrix 1004 in the correct position of the output tensor in dense format and zeros elsewhere.

10

15

20

25

30

35

**[0126]** A standard fold operation (which may also be referred to as a column to image (col2im) operation) receives an output matrix in dense format – i.e. an output matrix that comprises a row per output channel with an output element for each element of that channel - and converts each row of the received matrix to a plane of the output tensor in accordance with the size of a channel of the output tensor. For example, if each channel of the output tensor is of size 5x5, then a standard fold operation places every five elements in the same row of the received matrix in a different row of the corresponding channel. For example, the first five elements in the first row of the received matrix would be placed in the first channel of the output tensor, the next five elements in the first row of the received matrix would be placed in the second row of the received matrix would be placed in the second row of the received matrix would be placed in the second row of the received matrix would be placed in the second row of the received matrix would be placed in the second row of the received matrix would be placed in the second channel and so on.

[0127] In contrast to a standard fold operation, an indexed fold operation receives an output matrix in sparse format – i.e., the received matrix does not comprise an element for every element of the output tensor in dense format. An indexed fold operation also receives information indicating the position in the output tensor corresponding to each active window of the input tensor (this may be information (e.g. indices) identifying the active positions identified in block 504; information specifically identifying the active windows (e.g. indices of an element of each active window) (which may be generated as part of block 506); or information specifically identifying the position in the output tensor corresponding to each active window (which may be generated as part of block 506)). The information indicating the position in the output tensor corresponding to each active window is then used to place the elements of the sparse output matrix in the correct location of the output tensor in dense format. The elements at all other positions may then be set to zero.

**[0128]** Where there is an active window per active position (e.g. because the input is padded and the stride is 1 in all directions), then the height and width of the input tensor will be the same as

the height and the width of the output tensor, and the elements in the sparse output matrix 1004 can be simply placed in the same location in the output tensor as the corresponding active position. For example, in such cases, if an active window is centred at active position (1,1) then the output elements based on that active window will be placed at position (1,1) of the corresponding output channel. If, however, there is not an active window per active position and the received information does not explicitly identify the output position corresponding to each active window, the location of each element in the output matrix 1004 is determined from the received information and/or the parameters of the sparse submanifold convolution. For example, active windows can be determined from the active locations and the parameters of the sparse submanifold convolution (e.g. filter dimensions, strides, dilations), and the position in the output tensor corresponding to each active window can be determined from the active window and the parameters of the sparse submanifold convolution.

**[0129]** FIG. 11 illustrates an example indexed fold operation performed on the output matrix 1004 of FIG. 10. It can be seen that, based on the active position list 608 and the sparse submanifold convolution parameters, it can be determined that each element of the output matrix 1004 associated with the first active window is to be placed at location (0,0) of the corresponding channel of the output tensor 1102, and each element in the output matrix 1004 associated with the second active window is to be placed at location (2,2) of the corresponding channel of the output tensor 1102.

**[0130]** The indexed fold operation may be implemented on the GPU in any suitable manner. In one example, where there is an active window per active position of the input tensor, an indexed fold operation may be implemented on the GPU by, for example, creating an index for each active position/location (e.g. from 0 to n where there are n+1 active locations in the input tensor). Then, for each active position/location, the GPU may be configured to determine the associated location in the output tensor from the location of the corresponding active position and the kernel parameters, then loop through each output channel and place or copy the appropriate element of the output matrix in the determined location in the corresponding channel of the output tensor. Each active location may get its own thread.

**[0131]** Where there are less active windows than active positions, due to, for example, the stride, dilation, or other convolution parameters, then the indexed fold operation may be implemented on the GPU by, prior to determining the associated location in the output tensor for an active position, performing a validity check on the active position to determine if the active position produces or induces an active window, and only determining the associated location in the output tensor and performing the copying if the active position induces an active window. For example, if the stride is two for a sparse submanifold convolution, then the validity check may comprise determining if the active position is at or on an odd index, and if it is determined that the active position is at or on an odd index determining that the active position does not induce an active window.

**[0132]** In some cases, in addition to receiving the sparse submanifold convolution parameters, information identifying the active windows, and the output matrix generated in block 508, the indexed fold operation may also receive a zeroed output tensor of the appropriate dimensions and may write the elements of the received matrix to the received output tensor. In such cases, a zero may not have to be explicitly written to the positions of the output tensor that do not comprise an element of the output matrix.

[0133] Once the indexed fold operation has been performed, the method 500 may end.

[0134] In the examples described above, a row of the weight matrix corresponds to a filter (i.e., comprises all of the weights of a filter) and a column of the input matrix corresponds to a window of the input tensor (i.e., comprises all of the elements in the window of the input tensor), and the weight matrix is multiplied with the input matrix, such that the dot product of a row of the weight matrix and a column of the input matrix is calculated, to obtain the output matrix. However, it will be evident to a person of skill in the art that this is an example only and in other examples, the rows and columns of the weight matrix and the input matrix may be reversed (in other words the weight matrix and the input matrix may be transposed) and the transposed input matrix may be multiplied with the transposed weight matrix to obtain the transpose of the output matrix.

**[0135]** In some cases, the input matrix may be transposed after the indexed unfold operation, and the output matrix may be transposed prior to the indexed fold operation. However the weight matrix may be transposed offline and simply provided to the GPU as an input. In some cases, where a sequence of two or more sparse submanifold convolutions are performed only the input matrix of the first sparse submanifold convolution may be transposed and only the output matrix of the last sparse submanifold convolution is transposed. Specifically, the middle convolutions are simply performed with transposed matrices.

**[0136]** As described in more detail below, testing has shown that the described method of implementing a sparse submanifold convolution allows a sparse submanifold convolution to be implemented more efficiently in terms of computing time and resources than known GPU-based methods.

### **Test Results**

10

15

25

30

35

12.

**[0137]** Reference is now made to FIG. 12 which shows a graph of the mean duration, in ms, to implement an example sparse submanifold convolution on a GPU (i) for different sized 3D input tensors (MNIST), (ii) using different methods (TorchSparse, SpConv, PyTorch Conv3D and the method described herein with respect to FIG. 5 which is referred to as the "Sparse Unfold" method); and (iii) with different levels of sparsity. Table 2 summarises the different combinations of sparse submanifold convolution implementation methods, and input tensor sparsity shown in FIG.

22

# Table 2

| Element in FIG. 12 | Method         | Sparsity |

|--------------------|----------------|----------|

| 1202               | TorchSparse    | 99%      |

| 1204               | TorchSparse    | 90%      |

| 1206               | TorchSparse    | 80%      |

| 1208               | TorchSparse    | 50%      |

| 1210               | TorchSparse    | 25%      |

| 1212               | TorchSparse    | 0%       |

| 1214               | SpConv         | 99%      |

| 1216               | SpConv         | 90%      |

| 1218               | SpConv         | 80%      |

| 1220               | SpConv         | 50%      |

| 1222               | SpConv         | 25%      |

| 1224               | SpConv         | 0%       |

| 1226               | PyTorch Conv3D | 99%      |

| 1228               | PyTorch Conv3D | 90%      |

| 1230               | PyTorch Conv3D | 80%      |

| 1232               | PyTorch Conv3D | 50%      |

| 1234               | PyTorch Conv3D | 25%      |

| 1236               | PyTorch Conv3D | 0%       |

| 1238               | Sparse Unfold  | 99%      |

| 1240               | Sparse Unfold  | 90%      |

| 1242               | Sparse Unfold  | 80%      |

| 1244 | Sparse Unfold | 50% |

|------|---------------|-----|

| 1246 | Sparse Unfold | 25% |

| 1248 | Sparse Unfold | 0%  |

**[0138]** It can be seen from FIG. 12 that the method described herein with respect to FIG. 5 for implementing a sparse submanifold convolution outperforms known GPU-based methods for implementing a sparse submanifold convolution when the input data is highly sparse (e.g. at least 90% sparsity).

## **NNA Implementations of Sparse Submanifold Convolution**

10

15

20

25

30

**[0139]** Performing forward and backward passes of a neural network is often expensive to implement on a CPU or GPU in terms of computations, bandwidth and power. Accordingly, neural network accelerators (NNAs) have been developed that allow neural networks to be implemented in a hardware efficient manner (e.g., in a manner that requires less silicon area or less processing power).

**[0140]** An NNA is hardware that is designed to accelerate the processing of a neural network. As is known to those of skill in the art, a hardware accelerator is hardware designed to perform a specific set of one or more functions more efficiently than a general processing unit, such as a central processing unit (CPU). Accordingly, in contrast to a general CPU which can be configured to perform any number of functions, an accelerator can only perform a limited set of one or more functions. NNAs have one or more network processing hardware units (which may simply be referred to as processing units) which are each designed to accelerate one or more neural network operations. A neural network operation is defined herein as an operation that is used to implement all or a part of a neural network layer. A neural network layer may be implemented by one or more neural network operations. Example neural network operations include, but are not limited to, convolution operations, non-linear operations, pooling operations and normalisation operations.

**[0141]** An NNA may therefore have, for example, a convolution processing unit which is configured to accelerate convolution operations, an activation processing unit which is configured to accelerate non-linear operations, a pooling processing unit which is configured to accelerate pooling operations, and/or a normalisation processing unit configured to accelerate normalisation operations. It will be evident to a person of skill in the art that this is just an example set of network processing hardware units that an NNA may have, and NNAs may have additional network processing hardware units, fewer network processing hardware units or a different combination of network processing hardware units. An example NNA is described below with reference to FIG. 44.

[0142] The inventors have determined that a sparse submanifold convolution can be performed efficiently using an NNA by performing, for each kernel location, a 1x1 convolution between the input tensor in sparse format and the weight(s) at that kernel location to generate partial outputs and then combining the appropriate partial outputs to generate the final output elements. The combining of the partial outputs generated by the 1x1 convolutions may be implemented in a number of different ways. In some cases, where, for example, the NNA comprises a hardware component that can perform a scatter-add operation, the combining of the partial outputs may be implemented by performing a scatter-add operation on the partial outputs using that hardware component. In other cases, where, for example the NNA does not have a hardware component that can perform a scatter-add operation, the combining may be implemented by performing a matrix multiplication between the output of each 1x1 convolution and a corresponding scatter matrix, and combining the results of the matrix multiplications. These methods take advantage of the hardware structure of NNAs that allows convolution operations to be performed in a hardware efficient manner.

**[0143]** Reference is now made to FIG. 13 which illustrates an example method 1300 for implementing a sparse submanifold convolution using an NNA. The method 1300 begins at block 1302 where an input tensor in sparse format is received at the NNA. As described above, an input tensor in dense format comprises each element of an input tensor, regardless of whether the element is at an active position. In contrast, an input tensor in sparse format includes only elements of an input tensor in dense format that are at an active position. For example, FIG. 14 shows the input tensor of FIG. 4 with three active positions/locations (p1, p2, p3) in dense format 402 and the same input tensor in sparse format 1404. It can be seen in FIG. 14 that the input tensor in sparse format 1404 only includes the elements of the input tensor in dense format 402 at the active locations or positions. In the example shown in FIG. 14 the input tensor in dense format 402 only has one channel, thus the input tensor in sparse format only has one channel; however, if the input tensor in dense format has multiple channels, then the input tensor in sparse format will also have multiple channels. In other words, an input tensor in sparse format will comprise, for each active position, an element for each channel. Once the input tensor in sparse format has been received at the NNA, the method 1300 proceeds to block 1304.

**[0144]** At block 1304, the NNA performs, for each position or location within the kernel of the filter(s) of the sparse submanifold convolution, a 1x1 convolution on the received input tensor using the weight(s) at that kernel position or location. As described above, an NNA often comprises hardware, such as a convolution processing unit (i.e., a convolution hardware accelerator), to accelerate convolution operations. Accordingly, the NNA may efficiently perform the 1x1 convolutions using such hardware.

**[0145]** As described above, a sparse submanifold convolution applies one or more filters of weights to active windows of an input tensor. Each filter of a sparse submanifold convolution may be referred to herein as a sparse submanifold filter. Each sparse submanifold filter comprises one or more kernels of size  $K_H \times K_W$ , where  $K_H$  is the height of the kernel (i.e., the number of weights in