US012112707B2

# (12) United States Patent

Xiao et al.

(54) PIXEL CIRCUIT HAVING CONTROL CIRCUIT FOR CONTROLLING A LIGHT EMITTING ELEMENT AND DRIVING METHOD THEREOF, DISPLAY PANEL AND DISPLAY APPARATUS

(71) Applicant: **BOE TECHNOLOGY GROUP CO.,**

LTD., Beijing (CN)

(72) Inventors: Li Xiao, Beijing (CN); Haoliang

Zheng, Beijing (CN); Hao Chen, Beijing (CN); Minghua Xuan, Beijing (CN); Dongni Liu, Beijing (CN); Seungwoo Han, Beijing (CN); Liang Chen, Beijing (CN); Jiao Zhao, Beijing

(CN); Xue Dong, Beijing (CN)

(73) Assignee: **BOE TECHNOLOGY GROUP CO.**,

LTD., Beijing (CN)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 18/308,385

(22) Filed: Apr. 27, 2023

(65) Prior Publication Data

US 2023/0260461 A1 Aug. 17, 2023

# Related U.S. Application Data

- (63) Continuation of application No. 17/620,398, filed as application No. PCT/CN2020/126034 on Nov. 3, 2020, now Pat. No. 11,688,347.

- (51) **Int. Cl.**

**G09G 3/3258** (2016.01) **G09G 3/3291** (2016.01)

(52) U.S. Cl.

CPC ....... *G09G 3/3258* (2013.01); *G09G 3/3291* (2013.01)

(10) Patent No.: US 12,112,707 B2

(45) **Date of Patent:**

Oct. 8, 2024

(58) Field of Classification Search

CPC ...... G09G 3/3258

(Continued)

(56) References Cited

U.S. PATENT DOCUMENTS

2011/0164016 A1 7/2011 Kang et al. 2014/0320544 A1 10/2014 Kim

(Continued)

FOREIGN PATENT DOCUMENTS

107564473 A 1/2018 108538245 A 9/2018

CN

CN

(Continued)

OTHER PUBLICATIONS

International Search Report and Written Opinion (w/ English Translation) for corresponding PCT Application No. PCT/CN2020/126034, issued on Jul. 26, 2021, 15 pages.

(Continued)

Primary Examiner — Long D Pham

(74) Attorney, Agent, or Firm — Dority & Manning, P.A.

(57) ABSTRACT

A pixel circuit includes a driving circuit, a first control circuit and a second control circuit. The driving circuit is configured to receive a data signal in response to a scan signal, and generate, in response to a first enable signal, a driving signal according to a first voltage and the data signal. The first control circuit is configured to: receive a first input signal in response to a first control signal, and transmit a third input signal in response to the first input signal; and receive a second input signal in response to a second control signal, and transmit a second enable signal in response to the second input signal. The second control circuit is configured to transmit the driving signal to an element to be driven in response to one of the third input signal and the second enable signal.

### 20 Claims, 20 Drawing Sheets

# US 12,112,707 B2 Page 2

| (58)            | B) Field of Classification Search USPC            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | FOREIGN PATENT DOCUMENTS                  |                             |  |

|-----------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------------|-----------------------------|--|

|                 | See application file for complete search history. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CN<br>CN<br>CN | 109064972 A<br>111179849 A<br>111223444 A | 12/2018<br>5/2020<br>6/2020 |  |

| (56)            | References U.S. PATENT DO                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CN<br>CN<br>CN | 111354314 A<br>111462679 A<br>111477163 A | 6/2020<br>7/2020<br>7/2020  |  |

| 2018/0096651 A1 |                                                   | OTHER PUBLICATIONS  Office Action (w/ English Translation) for corresponding CN Application No. 202080002627.4, issued on Dec. 26, 2022, 11 pages. Office Action (w/ English Translation) for corresponding TW Application No. 110135545, issued on Jun. 14, 2022, 6 pages. Notice of Allowance for corresponding U.S. Appl. No. 17/620,398, issued on Mar. 3, 2023, 7 pages.  Ex parte Quayle Office Action for corresponding U.S. Appl. No. 17/620,398, issued on Dec. 6, 2022, 7 pages.  * cited by examiner |                |                                           |                             |  |

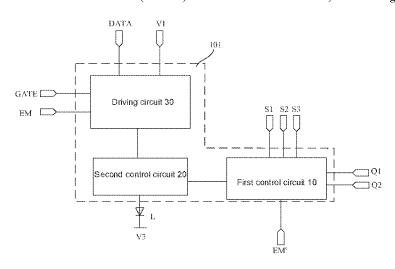

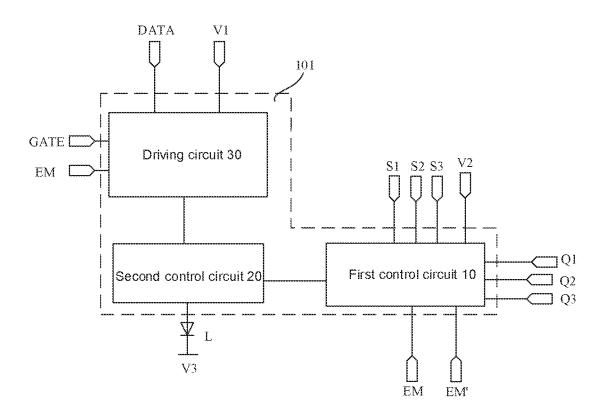

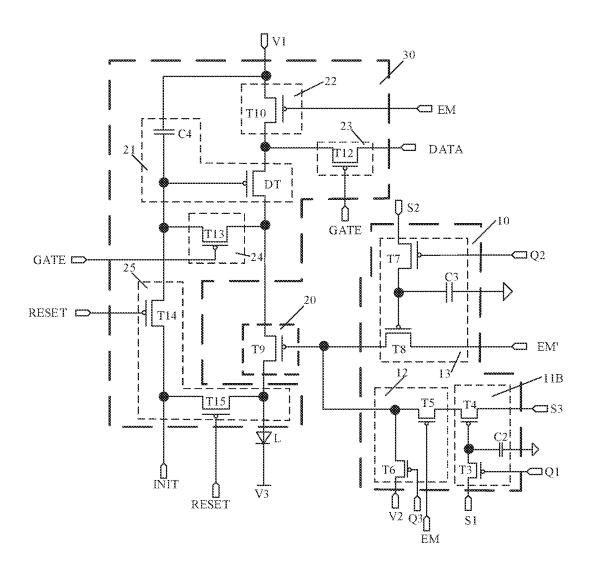

FIG. 1

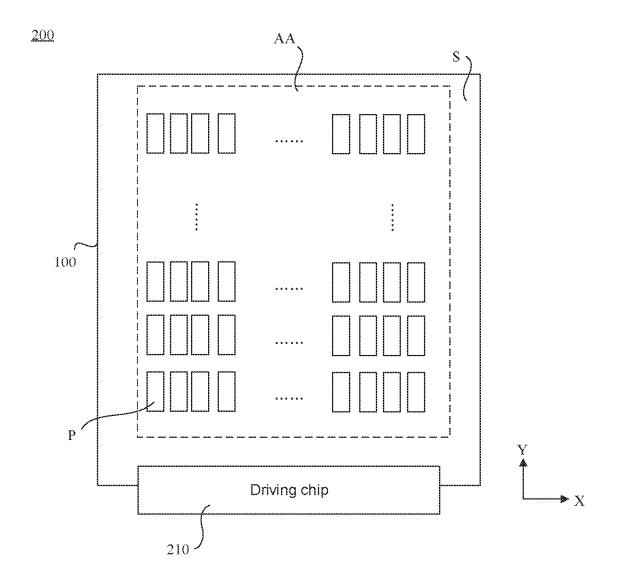

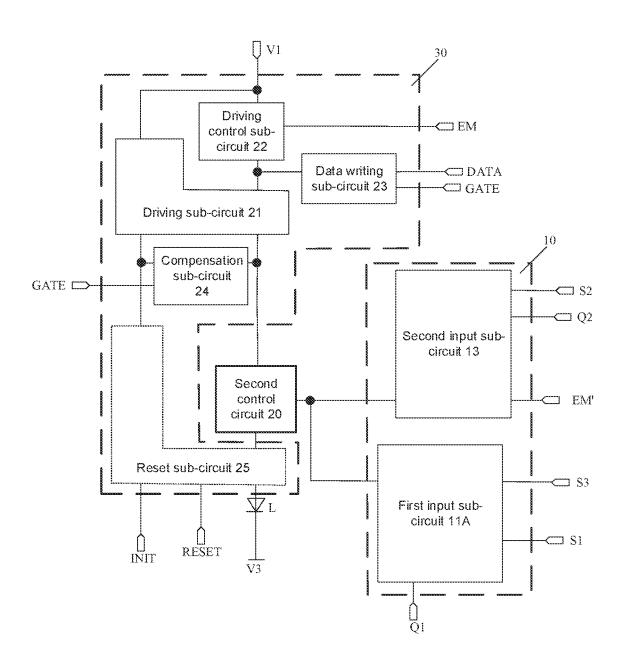

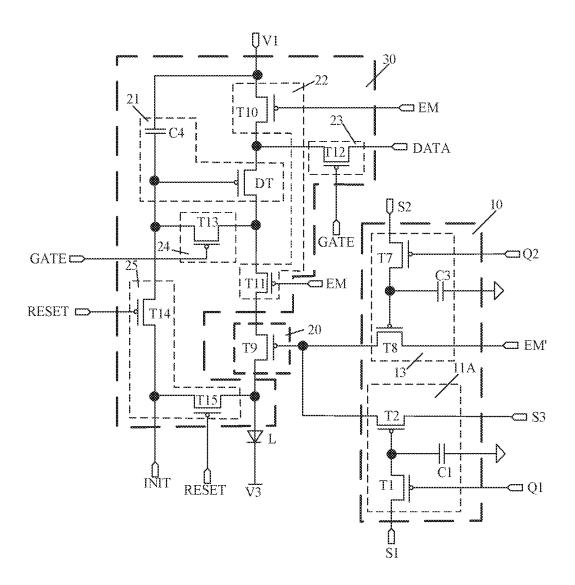

FIG. 2

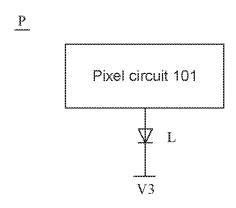

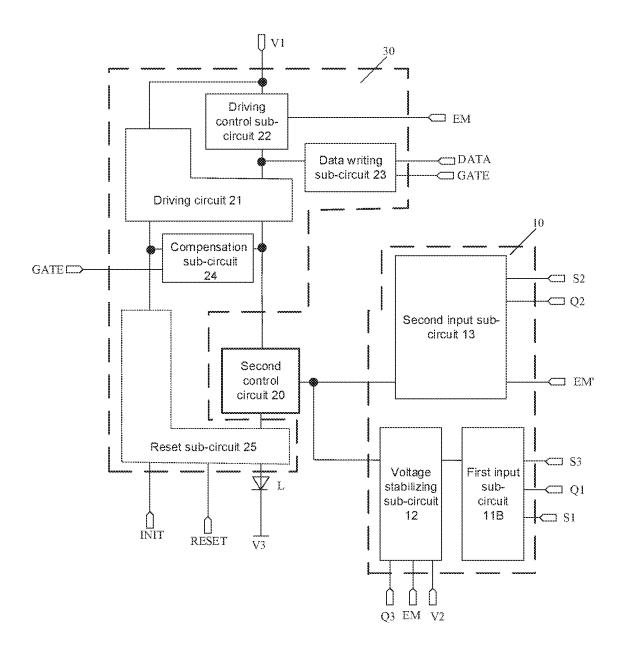

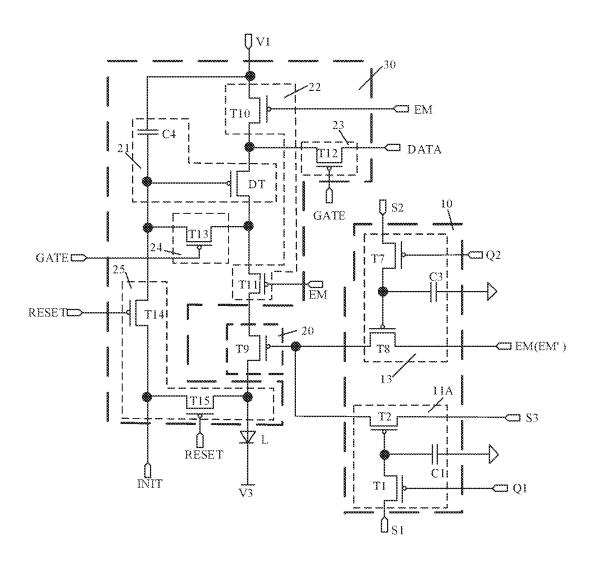

FIG. 3

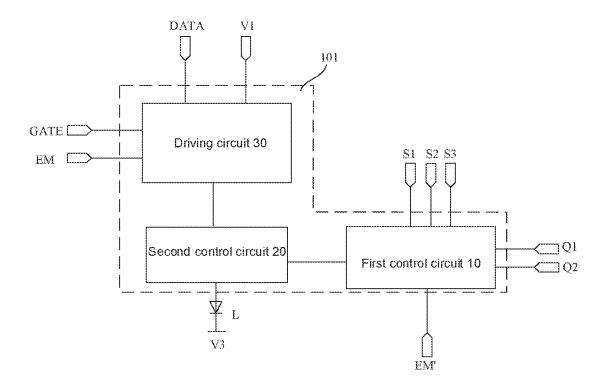

FIG. 4

FIG. 5A

FIG. 5B

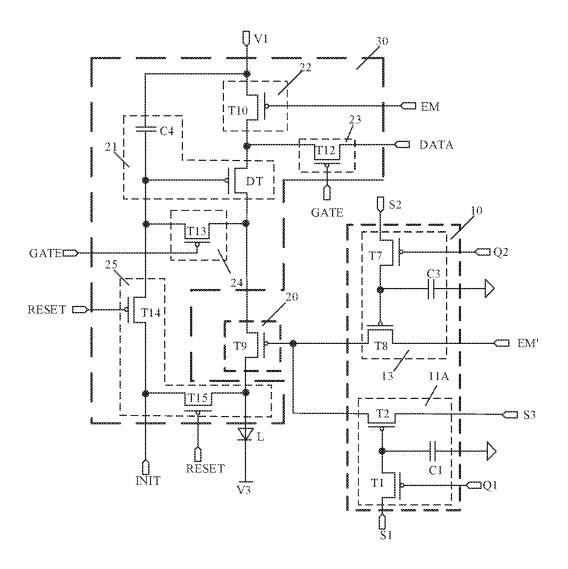

FIG. 6A

FIG. 6B

FIG. 6C

FIG. 6D

FIG. 7A

FIG. 7B

FIG. 7C

FIG. 7D

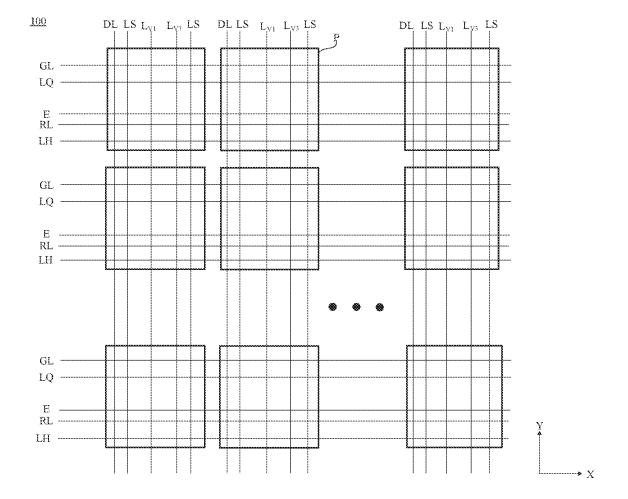

FIG. 8

FIG. 9

FIG. 10

FIG. 11

FIG. 12

FIG. 13

FIG. 14

# PIXEL CIRCUIT HAVING CONTROL CIRCUIT FOR CONTROLLING A LIGHT EMITTING ELEMENT AND DRIVING METHOD THEREOF, DISPLAY PANEL AND DISPLAY APPARATUS

# CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. Ser. No. 17/620, 398, filed on Dec. 17, 2021, which claims priority to International Patent Application No. PCT/CN2020/126034, filed on Nov. 3, 2020, which are incorporated herein by reference in their entirety.

#### TECHNICAL FIELD

The present disclosure relates to the field of display technologies, and in particular, to a pixel circuit and a driving method thereof, a display panel and a display <sup>20</sup> apparatus.

#### **BACKGROUND**

The display market is currently booming, and as the <sup>25</sup> consumer demand for various display products such as laptops, smart phones, TVs, tablets, smart watches, and fitness wristbands continues to increase, more new display products will emerge in future.

#### **SUMMARY**

In an aspect, a pixel circuit is provided. The pixel circuit includes a driving circuit, a first control circuit and a second control circuit. The driving circuit is coupled to at least a 35 data signal terminal, a scan signal terminal, a first voltage terminal and a first enable signal terminal. The first control circuit is coupled to at least a second enable signal terminal, a first control signal terminal, a first input signal terminal, a second control signal terminal, a second input signal terminal and a third input signal terminal. The second control circuit is coupled to the driving circuit and the first control circuit, and is configured to be coupled to an element to be driven.

The driving circuit is configured to receive a data signal 45 received at the data signal terminal in response to a scan signal received at the scan signal terminal, and generate, in response to a first enable signal received at the first enable signal terminal, a driving signal according to a first voltage at the first voltage terminal and the data signal.

The first control circuit is configured to: receive a first input signal received at the first input signal terminal in response to a first control signal received at the first control signal terminal, and transmit a third input signal received at the third input signal terminal in response to the first input 55 signal; and receive a second input signal received at the second input signal terminal in response to a second control signal received at the second control signal received at the second enable signal received at the second enable signal terminal in response to the second input signal. 60

The second control circuit is further configured to receive one of the third input signal and the second enable signal, and transmit the driving signal from the driving circuit to the element to be driven in response to the one of the third input signal and the second enable signal, so as to control an 65 operating duration of the element to be driven in a period in which the first enable signal is at an active level. In the

2

period where the first enable signal is at the active level, a sum of periods in which the third input signal is at the active level is less than a duration of the second enable signal being at the active level. A frequency of the third input signal is multiple times a frequency of the second enable signal.

In some embodiments, the frequency of the third input signal is in a range from 3000 Hz to 60000 Hz; and a frequency of the first enable signal and the frequency of the second enable signal are each in a range from  $60~\mathrm{Hz}$  to  $120~\mathrm{Hz}$

In some embodiments, in a case where the element to be driven displays a medium or high grayscale, the second control circuit is configured to transmit the driving signal to the element to be driven in response to the second enable signal, so as to control the operating duration of the element to be driven.

In some embodiments, in a case where the element to be driven displays a low grayscale, the second control circuit is configured to transmit the driving signal to the element to be driven in response to the third input signal, so as to control the operating duration of the element to be driven.

In some embodiments, in a case where the element to be driven displays a medium or high grayscale, in the period in which the first enable signal is at the active level, the duration of the second enable signal being at the active level is equal to a duration of the first enable signal being at the active level.

In some embodiments, in a case where the element to be driven displays a medium grayscale, in the period in which the first enable signal is at the active level, the duration of the second enable signal being at the active level is less than the duration of the first enable signal being at the active level.

In some embodiments, the first control circuit is further coupled to a third control signal terminal, the first enable signal terminal and a second voltage terminal. The first control circuit is further configured to transmit a second voltage at the second voltage terminal to the second control circuit in response to a third control signal received at the third control signal terminal; and the first control circuit being configured to transmit the third input signal in response to the first input signal includes: the first control circuit being configured to transmit the third input signal to the second control circuit in response to the first enable signal received at the first enable signal terminal and the first input signal.

In some embodiments, the first control circuit includes a first input sub-circuit. The first input sub-circuit is coupled to the first control signal terminal, the first input signal terminal and the third input signal terminal. The first input sub-circuit is configured to receive the first input signal received at the first input signal terminal in response to the first control signal received at the first control signal termi55 nal, and transmit the third input signal received at the third input signal terminal to the second control circuit in response to the first input signal.

In some embodiments, the first input sub-circuit is further coupled to the second control circuit. The first input sub-circuit includes a first transistor, a second transistor and a first capacitor. A control electrode of the first transistor is coupled to the first control signal terminal, and a first electrode of the first transistor is coupled to the first input signal terminal. A control electrode of the second transistor is coupled to a second electrode of the first transistor, a first electrode of the second transistor is coupled to the third input signal terminal, and a second electrode of the second transistor is coupled to the second transistor.

sistor is coupled to the second control circuit. The first capacitor is coupled to the second electrode of the first transistor.

In some embodiments, the first control circuit further includes a voltage stabilizing sub-circuit. The voltage stabilizing sub-circuit is coupled to the first enable signal terminal, the first input sub-circuit, the second control circuit, the third control signal terminal and the second voltage terminal. The voltage stabilizing sub-circuit is configured to transmit the second voltage at the second voltage terminal to the second control circuit in response to the third control signal received at the third control signal terminal, and transmit the third input signal from the first input sub-circuit to the second control circuit in response to the first enable signal received at the first enable signal terminal.

In some embodiments, the first input sub-circuit includes a third transistor, a fourth transistor and a second capacitor. A control electrode of the third transistor is coupled to the first control signal terminal, and a first electrode of the third 20 transistor is coupled to the first input signal terminal. A control electrode of the fourth transistor is coupled to a second electrode of the third transistor, a first electrode of the fourth transistor is coupled to the third input signal terminal, and a second electrode of the fourth transistor is 25 coupled to the voltage stabilizing sub-circuit. The second capacitor is coupled to the second electrode of the third transistor.

The voltage stabilizing sub-circuit includes a fifth transistor and a sixth transistor. A control electrode of the fifth 30 transistor is coupled to the first enable signal terminal, a first electrode of the fifth transistor is coupled to the first input sub-circuit, and a second electrode of the fifth transistor is coupled to the second control circuit. A control electrode of the sixth transistor is coupled to the third control signal 35 terminal, a first electrode of the sixth transistor is coupled to the second voltage terminal, and a second electrode of the sixth transistor is coupled to the second control circuit.

In some embodiments, the first control circuit further includes a second input sub-circuit. The second input sub- 40 circuit is coupled to the second control signal terminal, the second input signal terminal and the second control circuit. The second input sub-circuit is configured to receive the second input signal received at the second input signal terminal in response to 45 the second control signal received at the second control signal terminal, and transmit the second enable signal received at the second control circuit in response to the second input signal.

In some embodiments, the second input sub-circuit 50 includes a seventh transistor, an eighth transistor and a third capacitor. A control electrode of the seventh transistor is coupled to the second control signal terminal, and a first electrode of the seventh transistor is coupled to the second input signal terminal. A control electrode of the eighth 55 transistor is coupled to a second electrode of the seventh transistor, a first electrode of the eighth transistor is coupled to the second enable signal terminal, and a second electrode of the eighth transistor is coupled to the second control circuit. The third capacitor is coupled to the second electrode of the seventh transistor.

In some embodiments, the second control circuit includes a ninth transistor. A control electrode of the ninth transistor is coupled to the first control circuit, a first electrode of the ninth transistor is coupled to the driving circuit, and a second 65 electrode of the ninth transistor is configured to be coupled to the element to be driven.

4

In some embodiments, the driving circuit includes a driving sub-circuit, a driving control sub-circuit, a data writing sub-circuit and a compensation sub-circuit. The driving sub-circuit includes a driving transistor and a fourth capacitor. A first terminal of the fourth capacitor is coupled to the first voltage terminal, and a second terminal of the fourth capacitor is coupled to a control electrode of the driving transistor.

The driving control sub-circuit is coupled to at least the first enable signal terminal, the first voltage terminal and the driving transistor. The data writing sub-circuit is coupled to the scan signal terminal, the data signal terminal and a first electrode of the driving transistor. The compensation sub-circuit is coupled to the scan signal terminal, the control electrode of the driving transistor and a second electrode of the driving transistor.

The driving control sub-circuit is configured to make the first voltage terminal and the second control circuit form a conductive path through the driving transistor in the driving sub-circuit in response to the first enable signal received at the first enable signal terminal. The data writing sub-circuit is configured to write the data signal received at the data signal terminal into the first electrode of the driving transistor in response to the scan signal received at the scan signal terminal. The compensation sub-circuit is configured to write the data signal and a threshold voltage of the driving transistor in to the control electrode of the driving transistor in response to the scan signal received at the scan signal terminal. The driving sub-circuit is configured to generate a driving signal according to the data signal and the first voltage at the first voltage terminal.

In some embodiments, the driving control sub-circuit includes a tenth transistor. A control electrode of the tenth transistor is coupled to the first enable signal terminal, a first electrode of the tenth transistor is coupled to the first voltage terminal, and a second electrode of the tenth transistor is coupled to the first electrode of the driving transistor. The second electrode of the driving transistor is coupled to the second control circuit.

In some embodiments, the driving control sub-circuit includes a tenth transistor and an eleventh transistor. A control electrode of the tenth transistor is coupled to the first enable signal terminal, a first electrode of the tenth transistor is coupled to the first voltage terminal, and a second electrode of the tenth transistor is coupled to the first electrode of the driving transistor. A control electrode of the eleventh transistor is coupled to the first enable signal terminal, a first electrode of the eleventh transistor is coupled to the second electrode of the driving transistor, and a second electrode of the eleventh transistor is coupled to the second control circuit.

In another aspect, a display panel is provided. The display panel includes pixel circuit as described in any of the above embodiments and elements to be driven. The elements to be driven are coupled to the pixel circuits.

In some embodiments, the display panel further includes a plurality of first signal lines and a plurality of second signal lines. First control signal terminals and second control signal terminals that are coupled to a row of pixel circuits are coupled to a same first signal line, first input signal terminals and second input signal terminals that are coupled to a column of pixel circuits are coupled to two second signal lines, and the first input signal terminals and second input signal terminals are coupled to different second signal lines.

In some embodiments, first control signal terminals and second control signal terminals that are coupled to a row of pixel circuits are coupled to two first signal lines, the first

control signal terminals and the second control signal terminals are coupled to different first signal lines, and first input signal terminals and second input signal terminals that are coupled to a column of pixel circuits are coupled to a same second signal line.

In some embodiments, the display panel further includes a plurality of shift register circuits connected in cascade, and each shift register circuit is coupled to third input signal terminals that are coupled to a row of pixel circuits. The shift register circuit is configured to transmit the third input signal 10 to the third input signal terminals of the pixel circuits coupled to the shift register circuit.

In yet another aspect, a display apparatus is provided. The display apparatus includes the display panel described in any of the above embodiments and a driving chip. The driving chip is coupled to the display panel. The driving chip is configured to provide signals to the display panel.

In yet another aspect, a driving method of a pixel circuit is provided. The pixel circuit includes a driving circuit, a first control circuit and a second control circuit. The driving 20 accordance with some embodiments; circuit is coupled to at least a data signal terminal, a scan signal terminal, a first voltage terminal and a first enable signal terminal. The first control circuit is coupled to at least a second enable signal terminal, a first control signal terminal, a first input signal terminal, a second control signal 25 terminal, a second input signal terminal and a third input signal terminal. The second control circuit is coupled to the driving circuit and the first control circuit, and is configured to be coupled to an element to be driven.

The driving method includes:

receiving, by the driving circuit, a data signal received at the data signal terminal in response to a scan signal received at the scan signal terminal, and generating, by the driving circuit, a driving signal according to a first voltage at the first voltage terminal and the data signal, in response to a first 35 enable signal received at the first enable signal terminal;

receiving, by the first control circuit, a first input signal received at the first input signal terminal in response to a first control signal received at the first control signal terminal, and transmitting, by the first control circuit, a third input 40 signal received at the third input signal terminal in response to the first input signal; or, receiving, by the first control circuit, a second input signal received at the second input signal terminal in response to a second control signal received at the second control signal terminal, and transmit- 45 ting, by the first control circuit, a second enable signal received at the second enable signal terminal in response to the second input signal; and

receiving, by the second control circuit, one of the third input signal and the second enable signal, and transmitting, by the second control circuit, the driving signal from the driving circuit to the element to be driven in response to the one of the third input signal and the second enable signal, so as to control an operating duration of the element to be driven in a period in which the first enable signal is at an 55 active level.

In the period where the first enable signal is at the active level, a sum of periods in which the third input signal is at the active level is less than a duration of the second enable signal being at the active level. A frequency of the third input 60 signal is multiple times a frequency of the second enable signal.

#### BRIEF DESCRIPTION OF THE DRAWINGS

In order to describe technical solutions in the present disclosure more clearly, accompanying drawings to be used

in some embodiments of the present disclosure will be introduced briefly below. Obviously, the accompanying drawings to be described below are merely accompanying drawings of some embodiments of the present disclosure, and a person of ordinary skill in the art can obtain other drawings according to these drawings. In addition, the accompanying drawings in the following description may be regarded as schematic diagrams, and are not limitations on actual sizes of products, actual processes of methods and actual timings of signals involved in the embodiments of the present disclosure.

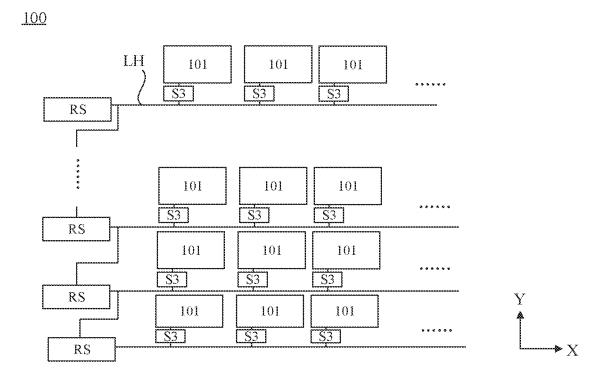

FIG. 1 is a structural diagram of a display apparatus, in accordance with some embodiments;

FIG. 2 is a structural diagram of a sub-pixel, in accordance with some embodiments;

FIG. 3 is a structural diagram of a pixel circuit, in accordance with some embodiments;

FIG. 4 is a structural diagram of another pixel circuit, in

FIG. 5A is a structural diagram of yet another pixel circuit, in accordance with some embodiments;

FIG. 5B is a structural diagram of yet another pixel circuit, in accordance with some embodiments;

FIG. 6A is a structural diagram of yet another pixel circuit, in accordance with some embodiments;

FIG. 6B is a structural diagram of yet another pixel circuit, in accordance with some embodiments;

FIG. 6C is a structural diagram of yet another pixel 30 circuit, in accordance with some embodiments;

FIG. 6D is a structural diagram of yet another pixel circuit, in accordance with some embodiments;

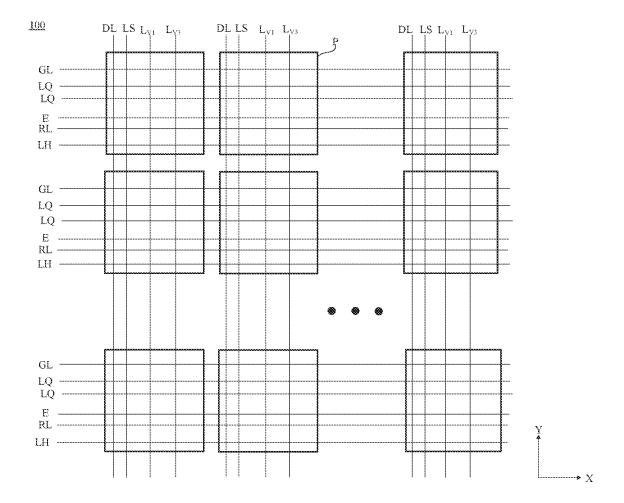

FIG. 7A is a structural diagram of a display panel, in accordance with some embodiments;

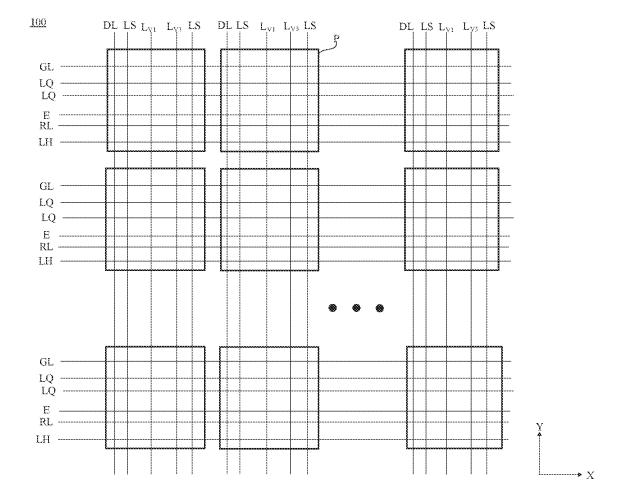

FIG. 7B is a structural diagram of another display panel, in accordance with some embodiments;

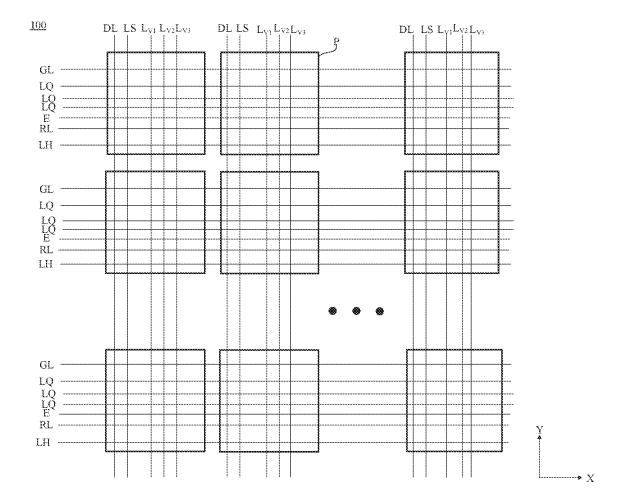

FIG. 7C is a structural diagram of yet another display panel, in accordance with some embodiments;

FIG. 7D is a structural diagram of yet another display panel, in accordance with some embodiments;

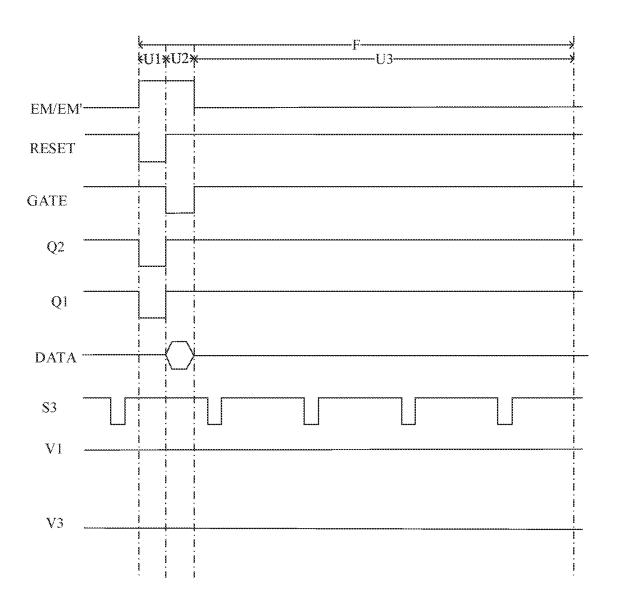

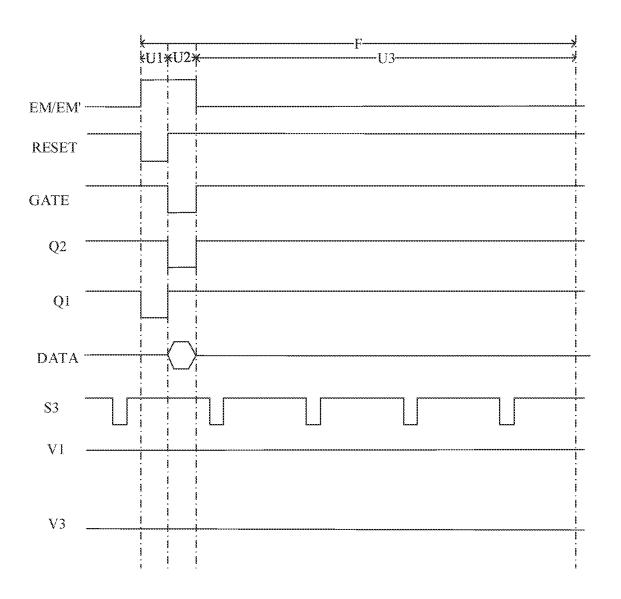

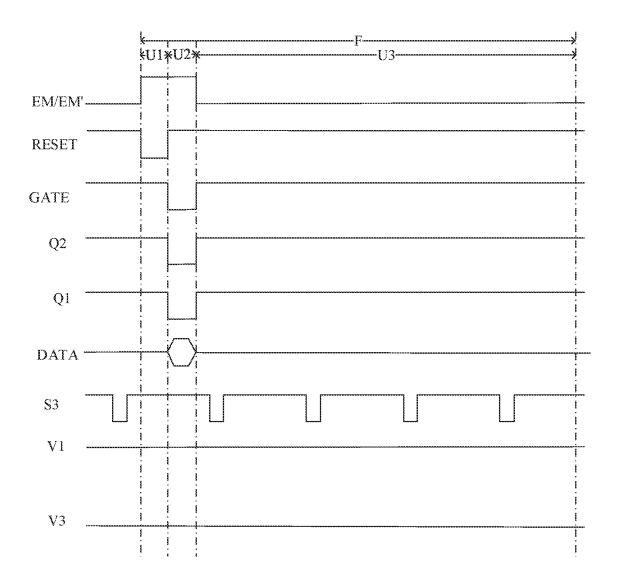

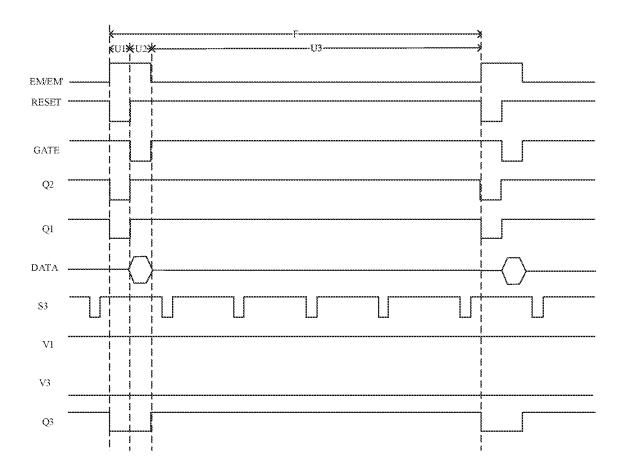

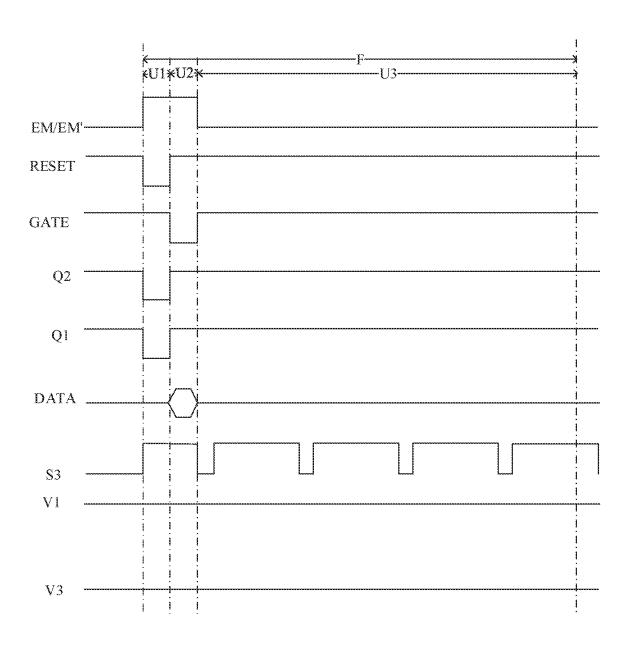

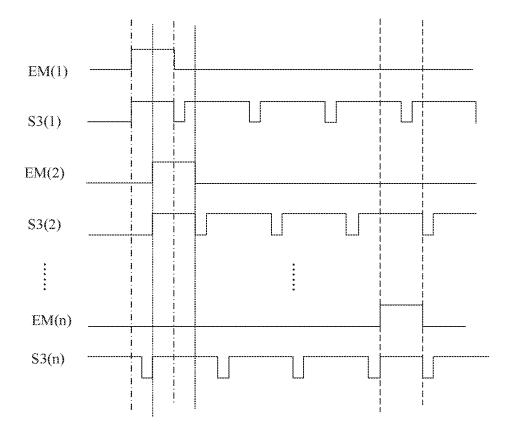

FIG. 8 is a timing diagram of signals for driving a pixel circuit, in accordance with some embodiments;

FIG. 9 is another timing diagram of signals for driving a pixel circuit, in accordance with some embodiments;

FIG. 10 is yet another timing diagram of signals for driving a pixel circuit, in accordance with some embodiments:

FIG. 11 is yet another timing diagram of signals for driving a pixel circuit, in accordance with some embodi-

FIG. 12 is yet another timing diagram of signals for driving a pixel circuit, in accordance with some embodiments:

FIG. 13 is a structural diagram of yet another display panel, in accordance with some embodiments; and

FIG. 14 is yet another timing diagram of signals for driving a pixel circuit, in accordance with some embodiments.

## DETAILED DESCRIPTION

Technical solutions in some embodiments of the present disclosure will be described clearly and completely below with reference to the accompanying drawings. Obviously, the described embodiments are merely some but not all embodiments of the present disclosure. All other embodiments obtained on a basis of the embodiments of the present

disclosure by a person of ordinary skill in the art shall be included in the protection scope of the present disclosure.

Unless the context requires otherwise, throughout the description and the claims, the term "comprise" and other forms thereof such as the third-person singular form "com- 5 prises" and the present participle form "comprising" are construed as an open and inclusive meaning, i.e., "including, but not limited to". In the description of the specification, the terms such as "one embodiment", "some embodiments", "exemplary embodiments", "example", "specific example" or "some examples" are intended to indicate that specific features, structures, materials or characteristics related to the embodiment(s) or example(s) are included in at least one embodiment or example of the present disclosure. Schematic representations of the above terms do not necessarily 15 refer to the same embodiment(s) or example(s). In addition, the specific features, structures, materials, or characteristics may be included in any one or more embodiments or examples in any suitable manner.

Hereinafter, the terms "first" and "second" are only used 20 for descriptive purposes, and are not to be construed as indicating or implying relative importance or implicitly indicating the number of indicated technical features. Thus, a feature defined with "first" or "second" may explicitly or implicitly include one or more of the features. In the 25 description of the embodiments of the present disclosure, the term "a plurality of", "the plurality of" or "multiple" means two or more unless otherwise specified.

In the description of some embodiments, the terms "coupled" and "connected" and derivatives thereof may be 30 used. For example, the term "connect" may be used in the description of some embodiments to indicate that two or more components are in direct physical or electrical contact with each other. As another example, the term "coupled" may be used in the description of some embodiments to 35 indicate that two or more components are in physical contact or there is an electrical signal path between the two or more components. For example, two components are connected through a signal line, or there may be other electrical elements or circuits between the two components, but there 40 is a signal path between the two components through other electrical elements. However, the term "coupled" or "communication coupling" may also mean that two or more components are not in direct contact with each other, but yet still cooperate or interact with each other. The embodiments 45 disclosed herein are not necessarily limited to the content

The phrase "A and/or B" includes the following three combinations: only A, only B, and a combination of A and B.

As used herein, the term "if" is optionally construed to mean "when" or "in a case where" or "in response to determining" or "in response to detecting," depending on the context. Similarly, the phrase "if it is determined" or "if [a strued to mean "in a case where it is determined" or "in response to determining" or "in a case where [the stated condition or event] is detected" or "in response to detecting [the stated condition or event]," depending on the context.

The use of the phrase "applicable to" or "configured to" 60 herein means an open and inclusive expression, which does not exclude devices that are applicable to or configured to perform additional tasks or steps.

The term such as "about" or "approximately" as used herein include a stated value and an average value within an 65 acceptable range of deviation of a particular value. The acceptable range of deviation is determined by a person of

ordinary skill in the art in view of the measurement in question and the error associated with a particular amount of measurement (i.e., the limitations of the measurement sys-

Self-luminous devices have attracted extensive attention due to their characteristics of high brightness and wide color gamut. However, photoelectric conversion properties (including photoelectric conversion efficiency, uniformity and color coordinates) of the self-luminous device will change as a current flowing through the self-luminous device change. For example, at a low current density, the luminous efficiency of the self-luminous device will decrease as the current density decreases, and thus the brightness uniformity of different self-luminous devices is poor. If the self-luminous device is applied to a display apparatus, a uniformity of display grayscales will be reduced, which results in disorder of the grayscales and color shift, and then affects a display effect of a display apparatus.

Embodiments of the present disclosure provide a display apparatus. For example, the display apparatus may be any apparatus that displays images whether in motion (e.g., videos) or stationary (e.g., static images), and whether literal or graphical. More specifically, the display apparatus may be one of a variety of electronic apparatuses, and the described embodiments may be implemented in or associated with the variety of electronic apparatuses, such as (but are not limited to) a mobile telephone, a wireless device, a personal data assistant (PDA), a hand-held or portable computer, a global positioning system (GPS) receiver/navigator, a camera, an MPEG-4 Part 14 (MP4) video player, a video camera, a game console, a watch, a clock, a calculator, a TV monitor, a flat-panel display, a computer monitor, a car display (e.g., an odometer display), a navigator, a cockpit controller and/or display, a camera view display (e.g., a rear view camera display in a vehicle), an electronic photo, an electronic billboard or sign, a projector, an architectural structure, a packaging and aesthetic structure (e.g., a display for an image of a piece of jewelry), etc. Embodiments of the present disclosure do not particularly limit a specific form of the display apparatus.

In some embodiments of the present disclosure, as shown in FIG. 1, the display apparatus 200 includes a display panel 100. The display panel 100 has a display area AA and a peripheral area S. The peripheral area S is located on at least a side of the display area AA.

The display panel 100 includes a plurality of sub-pixels P disposed in the display area AA. For example, the plurality of sub-pixels P may be arranged in an array. For example, sub-pixels P arranged in a line in a first direction X in FIG. 1 are referred to as sub-pixels in the same row, and subpixels P arranged in a line in a second direction Y in FIG. 1 are referred to as sub-pixels in the same column. The first direction X may be perpendicular to the second direction Y.

In some embodiments, as shown in FIG. 2, each sub-pixel stated condition or event] is detected" is optionally con- 55 P includes a pixel circuit 101 and an element L to be driven. The pixel circuit 101 is coupled to the element L to be driven, and the pixel circuit 101 is used to provide a driving signal to the element L to be driven, so as to drive the element L to be driven to operate.

For example, a first electrode of the element L to be driven is coupled to the pixel circuit 101, and a second electrode of the element L to be driven is coupled to a third voltage terminal V3. For example, the third voltage terminal V3 is configured to transmit a third voltage, and the third voltage is a direct current (DC) voltage. For example, the third voltage is a DC low voltage. For example, the third voltage is -3 V.

For example, the element to be driven includes a current-driven type device. Further, the current-driven type device may be a current-type light-emitting diode, such as a micro light-emitting diode (micro LED), a mini light-emitting diode (MED), an organic light-emitting diode (OLED), or a quantum dot light-emitting diode (QLED). In this case, an operating duration of the element to be driven described herein may be understood as a light-emitting duration of the element to be driven; and an operating frequency of the element to be driven may be understood as a light-emitting frequency of the element to be driven. For example, the first electrode and the second electrode of the element to be driven are an anode and a cathode of the light-emitting diode, respectively.

In a case where the element to be driven emits light, since 15 a brightness presented by the element to be driven when emitting light is related to the light-emitting duration and a driving current of the element to be driven, the brightness of the element to be driven may be controlled by adjusting the light-emitting duration and/or the driving current of the 20 element to be driven. For example, if driving currents of two elements to be driven are the same, and light-emitting durations thereof are different, display brightnesses of the two elements to be driven are different; if driving currents of two elements to be driven are different, and light-emitting 25 durations thereof are the same, display brightnesses of the two elements to be driven are also different; and if driving currents and light-emitting durations of two elements to be driven are both not the same, whether display brightnesses of the two elements to be driven are the same needs to be 30 analyzed concretely.

The display panel further includes a base substrate, and the pixel circuit and the element to be driven are both located on the base substrate. For example, the base substrate may include a rigid base (or referred to as a hard base) such as 35 glass, or a flexible base such as polyimide (Pl); and may further include a thin film such as a buffer layer disposed on the rigid base or the flexible base.

Some embodiments of the present disclosure provide a pixel circuit. As shown in FIG. 3, the pixel circuit  $101\,$  40 includes a first control circuit 10, a second control circuit 20, and a driving circuit 30.

The driving circuit **30** is coupled to at least a data signal terminal DATA, a scan signal terminal GATE, a first voltage terminal V1, and a first enable signal terminal EM.

The first control circuit 10 is coupled to at least a second enable signal terminal EM', a first control signal terminal Q1, a first input signal terminal S1, a second control signal terminal Q2, a second input signal terminal S2, and a third input signal terminal S3.

The second control circuit 20 is coupled to the driving circuit 30, the first control circuit 10, and the element L to be driven.

The driving circuit 30 is configured to: receive a data signal received at the data signal terminal DATA, in 55 response to a scan signal received at the scan signal terminal GATE; and generate a driving signal according to a first voltage at the first voltage terminal V1 and the data signal, in response to a first enable signal received at the first enable signal terminal EM.

The first control circuit 10 is configured to: receive a first input signal received at the first input signal terminal S1, in response to a first control signal received at the first control signal terminal Q1; and transmit a third input signal received at the third input signal terminal S3, in response to the first 65 input signal. The first control circuit 10 is further configured to: receive a second input signal received at the second input

10

signal terminal S2, in response to a second control signal received at the second control signal terminal Q2; and transmit a second enable signal received at the second enable signal terminal EM', in response to the second input signal.

The second control circuit 20 is configured to receive one of the third input signal and the second enable signal, and transmit the driving signal from the driving circuit 30 to the element L to be driven in response to the one of the third input signal and the second enable signal, so as to control the operating duration of the element L to be driven.

It will be noted that, in an image frame, a period in which the first enable signal is at an active level is considered to be an operating period (e.g., a third period in the image frame described below) of the element to be driven. It can be understood that, in the operating period of the element to be driven, there is a case where a driving signal cannot make the element to be driven to be operate. For example, in a case where the element to be driven is a light-emitting diode (LED), and a driving signal received by the element to be driven cannot make the element to be driven to be lit, the element to be driven displays zero grayscale. In the case where the element to be driven is the LED, the operating frequency described in the embodiments refers to the lightemitting frequency of the element to be driven in the operating period, and the operating duration described in the embodiments refers to the light-emitting duration of the element to be driven in the operating period.

For example, the first voltage received at the first voltage terminal is a DC voltage, e.g., a DC high voltage. For example, the first voltage is 7 V. For example, in a case where the first voltage received at the first voltage terminal is a high voltage, the third voltage received at the third voltage terminal is a low voltage; alternatively, in a case where the first voltage received at the first voltage terminal is a low voltage, the third voltage received at the third voltage terminal is a high voltage.

For example, the second enable signal terminal and the first enable signal terminal are coupled to a same signal line; and the second enable signal is the same as the first enable signal. In this way, in the period in which the first enable signal is at the active level in the image frame, a duration of the second enable signal being at an active level is equal to a duration of the first enable signal being at the active level.

For another example, the second enable signal terminal and the first enable signal terminal are different signal terminals. In a case where the sub-pixel where the pixel circuit is located displays a medium or high grayscale, the second enable signal is the same as the first enable signal. In a case where the sub-pixel where the pixel circuit is located displays a medium grayscale, an amplitude of the driving signal is maintained within a relatively high value range, and thus the duration of the second enable signal being at the active level is controlled to be less than the duration of the first enable signal being at the active level.

For example, the third input signal received at the third input signal terminal is a pulse signal. That is, in an image frame, the third input signal has a plurality of pulses. For example, a frequency of the third input signal is greater than a frequency of the second enable signal. That is, in unit time, the number of periods in which the second enable signal is at the active level is less than the number of periods in which the third input signal is at an active level. For example, in the period where the first enable signal is at the active level in the image frame, a sum of periods in which the third input signal is at the active level is less than the duration of the second enable signal being at the active level.

For example, the third input signal is a high frequency pulse signal. For example, the frequency of the third input signal is in a range from 3000 Hz to 60000 Hz, such as 3000 Hz or 60000 Hz. For example, frequencies of the first enable signal and the second enable signal are in a range from 60 5 Hz to 120 Hz, such as 60 Hz or 120 Hz. For example, a frame frequency of the display panel is 60 Hz (that is, the display panel may display 60 frames of images within 1 second), and a display duration of each image frame is equal. In this way, in a case where the third input signal is the 10 high-frequency signal with a frequency of 3000 Hz, in one image frame, if the element to be driven is to present a brightness of a low grayscale, the element to be driven may receive approximately 50 active periods of the high-frequency signal in a light-emitting period.

For example, in the case where the sub-pixel where the pixel circuit is located displays the medium or high gray-scale, the first input signal is at a high level (inactive level) during an active period of the first control signal received at the first control signal terminal Q1, and the second input 20 signal is at a low level (active level) during an active period of the second control signal received at the second control signal terminal Q2. In the case where the sub-pixel where the pixel circuit is located displays the low grayscale, the first input signal is at a low level (active level) during the 25 active period of the first control signal received at the first control signal terminal Q1, and the second input signal is at a high level (inactive level) during the active period of the second control signal received at the second control signal terminal Q2.

The first control circuit will not simultaneously transmit the second enable signal and the third input signal to the second control circuit. For example, in the case where the sub-pixel where the pixel circuit is located displays the medium or high grayscale, the first control circuit transmits 35 the second enable signal to the second control circuit; and in the case where the sub-pixel where the pixel circuit is located displays the low grayscale, the first control circuit transmits the third input signal to the second control circuit.

In a case where the element to be driven displays different 40 grayscales, by controlling the first control circuit to transmit the second enable signal or the third input signal to the second control circuit, a turn-on frequency of the second control circuit is controlled, a frequency at which the driving circuit and the element to be driven form a conductive path 45 is controlled, and then a frequency at which the driving signal is transmitted to the element to be driven may be controlled. The frequency at which the conductive path is formed determines a total operating duration of the element to be driven, and in the image frame, the total operating 50 duration of the element to be driven is a sum of operating sub-durations of the element to be driven when the conductive path is formed multiple times. In this way, a luminous intensity of the element to be driven may be controlled by controlling the amplitude of the driving signal and the 55 frequency at which the driving signal is transmitted to the element to be driven, thereby realizing a corresponding grayscale display.

It will be understood that, a range of the amplitude of the driving signal should be a range where the luminous efficiency of the element to be driven is high and stable, the color coordinate of the element to be driven is good, and a dominant wavelength of light exiting from the element to be driven is stable. For example, a range of the amplitude of the driving signal may be a range where the amplitude of the 65 driving signal is relatively large. Therefore, the data signal provided by the data signal terminal when the element to be

driven displays the medium or high grayscale may have a same value range as the data signal provided by the data signal terminal when the element to be driven displays the low grayscale.

12

In the case where the sub-pixel where the pixel circuit is located displays the medium or high grayscale, the first control circuit transmits the second enable signal to the second control circuit. In the light-emitting period of the element to be driven in the sub-pixel, the second control circuit is in a turn-on state all the time in response to the second enable signal, so that the driving circuit and the element to be driven form the conductive path all the time, and the driving signal is continuously transmitted to the element to be driven, Since the amplitude of the driving signal corresponding to the medium or high grayscale is relatively high, the element to be driven may operate under the driving signal with a relatively high amplitude, thereby ensuring the operating efficiency (luminous efficiency) of the element to be driven.

In the case where the sub-pixel where the pixel circuit is located displays the low grayscale, the first control circuit transmits the third input signal to the second control circuit: and in the light-emitting period of the element to be driven in the sub-pixel, the second control circuit is in turn-on and turn-off states alternately in response to the third input signal with high-frequency pulses, so that the driving signal is intermittently transmitted to the element to be driven, and correspondingly, the element to be driven periodically receives the driving signal. For example, the element to be driven stops receiving the driving signal for a period of time after receiving the driving signal for a period of time, then receives the driving signal for a period of time, and then stops receiving the driving signal for a period of time. In this way, a duration of the driving circuit and the element to be driven forming the conductive path is shortened, and a duration of the driving signal being transmitted to the element to be driven is shortened. Therefore, in the case where the sub-pixel where the pixel circuit is located displays the low grayscale, the amplitude of the driving signal may be maintained in a relatively high value range or at a relatively large fixed value, and the sub-pixel achieves a corresponding low grayscale display by changing the operating duration of the element to be driven. As a result, it improves the operating efficiency of the element to be driven, avoid problems of low operating efficiency and high power consumption of the element to be driven in a case where the low grayscale is displayed under a low current amplitude, avoid reduction in the uniformity of the displayed grayscales, and avoid occurrence of a color shift of the display. Thus, the display effect of the display panel is improved.

For example, the amplitude of the driving signal is related to the data signal received at the data signal terminal, and the data signal may be a signal that enables the element to be driven to have a relatively high operating efficiency. For example, the data signal may be a signal that changes in a relatively high amplitude range or a signal with a relatively high fixed amplitude. In this case, in the pixel circuit, the driving circuit controls an amplitude range of the driving signal, and the first control circuit and the second control circuit control the duration of the driving signal being transmitted to the element to be driven and the frequency at which the driving signal is transmitted to the element to be driven, so that the grayscale display corresponding to the sub-pixel is controlled.

Moreover, in an image frame, in a case where the subpixel displays the low grayscale, compared with a situation

where the element to be driven does not operate for a long time after operating for a short time, which results in that human eyes will obviously view flicker, in the embodiments of the present disclosure, the element to be driven is intermittently in the operating state, so that the operating states and non-operating states of the element to be driven alternate with a relatively large alternating frequency (that is, a brightness-darkness alternating frequency of the element to be driven is high), thereby being not easy to view the flicker by human eyes. As a result, the display effect is improved.

Therefore, in the pixel circuit provided in the embodiments of the present disclosure, the driving circuit generates the driving signal according to the first voltage and the written data signal. The first control circuit receives the first 15 input signal in response to the first control signal, and transmits the third input signal in response to the first input signal; the first control circuit receives the second input signal in response to the second control signal, and transmits the second enable signal in response to the second input 20 signal; and the second control circuit transmits the received driving signal from the driving circuit to the element to be driven in response to the received signal from the first control circuit, and controls the operating duration of the element to be driven. In this case, when the element to be 25 driven displays different grayscales, in the case where the sub-pixel where the pixel circuit is located displays the medium or high grayscale, the first control circuit transmits the second enable signal to the second control circuit, so that the element to be driven always operates under the driving signal with a relatively high amplitude, which ensures the operating efficiency of the element to be driven: and in the case where the sub-pixel where the pixel circuit is located displays the low grayscale, the first control circuit transmits the third input signal to the second control circuit so that the element to be driven is intermittently in the operating state, and by controlling the operating duration of the element to be driven, the element to be driven may also achieve a corresponding grayscale display under the driving signal 40 with a relatively high amplitude, which improves the operating efficiency of the element to be driven. In addition, the operating frequency of the element to be driven is relatively high, which may prevent human eyes from viewing the flicker, and thus the display effect is improved.

For example, as shown in FIGS. 6A to 6D, the second control circuit 20 includes a ninth transistor T9. A control electrode of the ninth transistor T9 is coupled to the first control circuit 10, a first electrode of the ninth transistor T9 is coupled to the driving circuit 30, and a second electrode of the ninth transistor T9 is coupled to the element L to be driven.

In some embodiments, as shown in FIG. **5**A, the first control circuit **10** includes a first input sub-circuit **11**A. The first input sub-circuit **11**A is coupled to the first control 55 signal terminal Q**1**, the first input signal terminal S**1** and the third input signal terminal S**3**. The first input sub-circuit **11**A is further coupled to the second control circuit **20**.

The first input sub-circuit 11A is configured to receive the first input signal received at the first input signal terminal S1 60 in response to the first control signal received at the first control signal terminal Q1, and transmit the third input signal received at the third input signal terminal S3 to the second control circuit 20 in response to the first input signal.

For example, as shown in FIG. **6**A, the first input subcircuit **11**A includes a first transistor T**1**, a second transistor T**2** and a first capacitor C**1**.

14

A control electrode of the first transistor T1 is coupled to the first control signal terminal Q1, and a first electrode of the first transistor T1 is coupled to the first input signal terminal S1.

A control electrode of the second transistor T2 is coupled to a second electrode of the first transistor T1, a first electrode of the second transistor T2 is coupled to the third input signal terminal S3, and a second electrode of the second transistor T2 is coupled to the second control circuit 20.

For example, as shown in FIG. 6A, in the case where the second control circuit 20 includes the ninth transistor T9, the second electrode of the second transistor T2 is coupled to the control electrode of the ninth transistor T9.

The first capacitor C1 is coupled to the second electrode of the first transistor T1. For example, a first terminal of the first capacitor C1 is coupled to the second electrode of the first transistor T1, and a second terminal of the first capacitor C1 is coupled to a fixed voltage terminal.

For example, the fixed voltage terminal is configured to transmit a fixed voltage signal, such as a DC voltage signal. For example, the fixed voltage signal is a ground signal, or the fixed voltage signal is approximately a ground signal. For example, the fixed voltage terminal may be a ground terminal.

It will be understood that, the first capacitor in the first input sub-circuit may store the written first input signal, so as to control a voltage of the control electrode of the second transistor to be a voltage of the first input signal.

In some embodiments, as shown in FIG. 4, the first control circuit 10 is further coupled to a third control signal terminal Q3, the first enable signal terminal EM, and a second voltage terminal V2.

The first control circuit 10 is further configured to transmit a second voltage at the second voltage terminal V2 to the second control circuit 20, in response to a third control signal received at the third control signal terminal Q3. The first control circuit 10 being configured to transmit the third input signal in response to the first input signal includes: the first control circuit 10 being configured to transmit the third input signal to the second control circuit 20, in response to the first enable signal received at the first enable signal terminal EM and the first input signal.

For example, the second voltage received at the second voltage terminal is a DC voltage, such as a DC high voltage.

In this case, the first control circuit 10 may further transmit the second voltage to the second control circuit 20, so as to control the second control circuit 20 to receive the DC voltage. In a period in which the sub-pixel does not emit light, it is possible to avoid an influence on voltage stability of an element in the second control circuit 20 in a case where the third input signal is the pulse signal.

In some embodiments, as shown in FIG. 5B, the first control circuit 10 includes a first input sub-circuit 11B and a voltage stabilizing sub-circuit 12.

The first input sub-circuit 11B is coupled to the first control signal terminal Q1, the first input signal terminal S1, the third input signal terminal S3 and the voltage stabilizing sub-circuit 12. The first input sub-circuit 11B is configured to receive the first input signal received at the first input signal terminal S1 in response to the first control signal received at the first control signal terminal Q1, and transmit the third input signal received at the third input signal terminal S3 to the voltage stabilizing sub-circuit 12 in response to the first input signal.

The voltage stabilizing sub-circuit 12 is coupled to the first input sub-circuit 11B, the first enable signal terminal

EM, the third control signal terminal Q3, the second voltage terminal V2 and the second control circuit 20. In the case where the second control circuit 20 includes the ninth transistor T9, as shown in FIG. 6B, the voltage stabilizing sub-circuit 12 is coupled to the control electrode of the ninth 5 transistor T9.

The voltage stabilizing sub-circuit 12 is configured to transmit the second voltage at the second voltage terminal V2 to the second control circuit 20 in response to the third control signal received at the third control signal terminal 10 Q3, and transmit the third input signal output from the first input sub-circuit 11B to the second control circuit 20 in response to the first enable signal received at the first enable signal terminal EM.

In this case, the voltage stabilizing sub-circuit 12 trans- 15 mits the third input signal to the second control circuit 20 in a case where the first enable signal is at the active level. In this way, in a period in which the first enable signal is at an inactive level, the third input signal will not be transmitted to the second control circuit 20. Therefore, it may improve 20 a stability of a voltage of the second control circuit 20, e.g., a voltage of the control electrode of the ninth transistor T9 in the second control circuit 20. Moreover, in the period in which the first enable signal is at the inactive level, the voltage stabilizing sub-circuit 12 transmits the second volt- 25 age to the second control circuit 20, so that the second control circuit 20 receives a stable voltage, and then the voltage of the control electrode of the ninth transistor T9 is stable, which ensures the voltage stability of the second control circuit 20.

For example, as shown in FIG. 6B, the first input subcircuit 11B includes a third transistor T3, a fourth transistor T4, and a second capacitor C2.

A control electrode of the third transistor T3 is coupled to the first control signal terminal Q1, and a first electrode of 35 the third transistor T3 is coupled to the first input signal terminal S1.

A control electrode of the fourth transistor T4 is coupled to the second electrode of the third transistor T3, a first electrode of the fourth transistor T4 is coupled to the third 40 input signal terminal S3, and a second electrode of the fourth transistor T4 is coupled to the voltage stabilizing sub-circuit 12

The second capacitor C2 is coupled to the second electrode of the third transistor T3. For example, a first terminal 45 of the second capacitor C2 is coupled to the second electrode of the third transistor T3, and a second terminal of the second capacitor C2 is coupled to a fixed voltage terminal.

For example, the fixed voltage terminal is configured to transmit a fixed voltage signal. For example, the fixed 50 voltage signal includes a DC voltage signal. For example, the fixed voltage signal is a ground signal, or the fixed voltage signal is approximately a ground signal. For example, the fixed voltage terminal may be the ground terminal.

It will be understood that, the second capacitor C2 in the first input sub-circuit 11B may store the written first input signal, so as to control a voltage of the control electrode of the fourth transistor to be the voltage of the first input signal.

The voltage stabilizing sub-circuit 12 includes a fifth 60 transistor T5 and a sixth transistor T6.

A control electrode of the fifth transistor T5 is coupled to the first enable signal terminal EM, a first electrode of the fifth transistor T5 is coupled to the first input sub-circuit 11B, and a second electrode of the fifth transistor T5 is 65 coupled to the second control circuit 20. In the case where the first input sub-circuit 11B includes the fourth transistor

16

T4, the first electrode of the fifth transistor T5 is coupled to the second electrode of the fourth transistor T4. In the case where the second control circuit 20 includes the ninth transistor T9, the second electrode of the fifth transistor T5 is coupled to the control electrode of the ninth transistor T9.

A control electrode of the sixth transistor T6 is coupled to the third control signal terminal Q3, a first electrode of the sixth transistor T6 is coupled to the second voltage terminal V2, and a second electrode of the sixth transistor T6 is coupled to the second control circuit 20. In the case where the second control circuit 20 includes the ninth transistor T9, the second electrode of the sixth transistor T6 is coupled to the control electrode of the ninth transistor T9.

In some embodiments, as shown in FIGS. 5A and 5B, the first control circuit 10 further includes a second input sub-circuit 13.

The second input sub-circuit 13 is coupled to the second control signal terminal Q2, the second input signal terminal S2, the second enable signal terminal EM' and the second control circuit 20. In the case where the second control circuit 20 includes the ninth transistor T9, the second input sub-circuit 13 is coupled to the control electrode of the ninth transistor T9.

The second input sub-circuit 13 is configured to receive the second input signal received at the second input signal terminal S2 in response to the second control signal received at the second control signal terminal Q2, and transmit the second enable signal received at the second enable signal terminal EM' to the second control circuit 20 in response to the second input signal.

For example, as shown in FIGS. 6A to 6D, the second input sub-circuit 13 includes a seventh transistor T7, an eighth transistor T8 and a third capacitor C3.

A control electrode of the seventh transistor T7 is coupled to the second control signal terminal Q2, and a first electrode of the seventh transistor T7 is coupled to the second input signal terminal S2.

A control electrode of the eighth transistor T8 is coupled to a second electrode of the seventh transistor T7, a first electrode of the eighth transistor T8 is coupled to the second enable signal terminal EM', and a second electrode of the eighth transistor T8 is coupled to the second control circuit 20.

The third capacitor C3 is coupled to the second electrode of the seventh transistor T7. For example, a first terminal of the third capacitor C3 is coupled to the second electrode of the seventh transistor T7, and a second terminal of the third capacitor C3 is coupled to a fixed voltage terminal.

For example, the fixed voltage terminal is configured to transmit a fixed voltage signal. For example, the fixed voltage signal includes a DC voltage signal. For example, the fixed voltage signal is a ground signal, or the fixed voltage signal is approximately a ground signal. For example, the fixed voltage terminal may be the ground terminal.

It will be understood that, the third capacitor C3 in the second input sub-circuit 13 may store the written second input signal, so as to control a voltage of the control electrode of the eighth transistor to be a voltage of the second input signal.

In the case where the second control circuit 20 includes the ninth transistor T9, the second electrode of the eighth transistor T8 is coupled to the control electrode of the ninth transistor T9.

In some embodiments, as shown in FIGS. 5A and 5B, the driving circuit 30 includes a driving sub-circuit 21, a driving control sub-circuit 22, a data writing sub-circuit 23 and a compensation sub-circuit 24.

As shown in FIGS. 6A to 6D, the driving sub-circuit 21 5 includes a driving transistor DT and a fourth capacitor C4. A first terminal of the fourth capacitor C4 is coupled to the first voltage terminal V1, and a second terminal of the fourth capacitor C4 is coupled to a control electrode of the driving

The data writing sub-circuit 23 is coupled to the scan signal terminal GATE, the data signal terminal DATA and a first electrode of the driving transistor DT in the driving sub-circuit 21. The compensation sub-circuit 24 is coupled to the scan signal terminal GATE, the control electrode of the driving transistor DT, and a second electrode of the driving transistor DT. The driving control sub-circuit 24 is coupled to at least the first enable signal terminal EM, the first voltage terminal V1 and the driving transistor DT in the  $_{20}$  to the scan signal terminal GATE, a first electrode of the driving sub-circuit 21.

The data writing sub-circuit 23 is configured to write the data signal received at the data signal terminal DATA into the first electrode of the driving transistor DT in the driving sub-circuit **21**, in response to the scan signal received at the 25 scan signal terminal GATE.

The driving sub-circuit 21 is configured to generate a driving signal according to the written data signal and the first voltage at the first voltage terminal V1.

The driving control sub-circuit 22 is configured to make 30 the first voltage terminal V1 and the second control circuit 20 form a conductive path through the driving transistor DT in the driving sub-circuit 21, in response to the first enable signal received at the first enable signal terminal EM.

The compensation sub-circuit **24** is configured to write the 35 data signal and a threshold voltage of the driving transistor DT into the control electrode of the driving transistor DT, in response to the scan signal received at the scan signal terminal GATE. In this way, it may avoid an influence of the threshold voltage of the driving transistor DT on the driving 40 signal.

For example, as shown in FIGS. 6A and 6B, the driving control sub-circuit 22 includes a tenth transistor T10.

A control electrode of the tenth transistor T10 is coupled to the first enable signal terminal EM, a first electrode of the 45 tenth transistor T10 is coupled to the first voltage terminal V1. and a second electrode of the tenth transistor T10 is coupled to a first electrode of the driving transistor DT.

The second electrode of the driving transistor DT is coupled to the second control circuit 20. In the case where 50 the second control circuit 20 includes the ninth transistor T9, the second electrode of the driving transistor DT is coupled to the first electrode of the ninth transistor T9

For another example, as shown in FIGS. 6C and 6D, the driving control sub-circuit 22 includes a tenth transistor T10 55 and an eleventh transistor T11.

A control electrode of the tenth transistor T10 is coupled to the first enable signal terminal EM, a first electrode of the tenth transistor T10 is coupled to the first voltage terminal V1, and a second electrode of the tenth transistor T10 is 60 coupled to the first electrode of the driving transistor DT.

A control electrode of the eleventh transistor T11 is coupled to the first enable signal terminal EM, a first electrode of the eleventh transistor T11 is coupled to the second electrode of the driving transistor DT, and a second electrode of the eleventh transistor T11 is coupled to the second control circuit 20.

18

In the case where the second control circuit 20 includes the ninth transistor T9, the second electrode of the eleventh transistor T11 is coupled to the first electrode of the ninth transistor T9.

It will be understood that, in the period in which the first enable signal is at the inactive level, e.g., a period when the data signal is written, the eleventh transistor T11 is in a turn-off state due to the control of the first enable signal, so that the driving transistor DT is disconnected from the second control circuit 20, which avoids a situation where an accuracy of writing of the data signal is affected due to an influence of the pulse signal of the third input signal on a voltage of the second electrode of the driving transistor DT in a case where the second control circuit 20 receives the third input signal.

For example, as shown in FIGS. 6A to 6D, the data writing sub-circuit 23 includes a twelfth transistor T12.

A control electrode of the twelfth transistor T12 is coupled twelfth transistor T12 is coupled to the data signal terminal DATA, and a second electrode of the twelfth transistor T12 is coupled to the first electrode of the driving transistor DT.

For example, as shown in FIGS. 6A to 6D, the compensation sub-circuit 24 includes a thirteenth transistor T13.

A control electrode of the thirteenth transistor T13 is coupled to the scan signal terminal GATE, a first electrode of the thirteenth transistor T13 is coupled to the second electrode of the driving transistor DT, and a second electrode of the thirteenth transistor T13 is coupled to the control electrode of the driving transistor DT.

It will be understood that, the thirteenth transistor T13 may write the data signal and the threshold voltage of the driving transistor DT into the control electrode of the driving transistor DT, so as to achieve threshold voltage compen-

In some embodiments, as shown in FIGS. 5A and 5B, the driving circuit 30 further includes a reset sub-circuit 25. The reset sub-circuit 25 is coupled to the driving sub-circuit 21, the element L to be driven, the reset signal terminal RESET and an initial signal terminal INIT.

The reset sub-circuit 25 is configured to transmit an initial signal received at the initial signal terminal INIT to the driving sub-circuit 21 and the element L to be driven, in response to the reset signal received at the reset signal terminal RESET. In this way, the driving sub-circuit 21 and the element L to be driven may be reset to avoid interference of signals.

It will be noted that, a voltage of the initial signal may be selected according to actual situations, which is not limited here. For example, the initial signal may be a high-level signal or a low-level signal.

For example, as shown in FIGS. 6A to 6D, the reset sub-circuit 26 includes a fourteenth transistor T14 and a fifteenth transistor T15.

A control electrode of the fourteenth transistor T14 is coupled to the reset signal terminal RESET, a first electrode of the fourteenth transistor T14 is coupled to the initial signal terminal INIT, and a second electrode of the fourteenth transistor T14 is coupled to the driving sub-circuit 21.

A control electrode of the fifteenth transistor T15 is coupled to the reset signal terminal RESET, a first electrode of the fifteenth transistor T15 is coupled to the initial signal terminal INIT, and a second electrode of the fifteenth transistor T15 is coupled to the element L to be driven.

For example, the second electrode of the fourteenth transistor T14 is coupled to the control electrode of the

driving transistor DT. The second electrode of the fifteenth transistor T15 is coupled to the first electrode of the element L to be driven.

19

It can be understood that, the fourteenth transistor T14 may transmit the initial signal to the control electrode of the 5 driving transistor DT, so as to reset a voltage of the control electrode of the driving transistor DT; and the fifteenth transistor T15 may transmit the initial signal to the first electrode of the element L to be driven, so as to reset a voltage of the first electrode of the element L to be driven.

In some embodiments, the first enable signal terminal and the second enable signal terminal are coupled to a same signal line. In this way, referring to FIG. 6D, the first electrode of the eighth transistor T8 is coupled to the first enable signal terminal EM.

It will be noted that, a specific implementation manner of the driving circuit is not limited to the manner described above, and it may be any implementation manner that is used, e.g., a conventional connection manner well known to those skilled in the art, as long as implementation of 20 corresponding functions is ensured. A circuit that can implement the functions of the above-mentioned driving circuit is, for example, a circuit capable of providing the driving signal, which is within the protection scope of the present disclosure.

In some embodiments, as shown in FIGS. 7A to 7D, the display panel 100 further includes a plurality of scan signal lines GL, a plurality of data signal lines DL, a plurality of enable signal lines E, and a plurality of reset signal lines RL.

In some examples, scan signal terminals GATE that are 30 coupled to pixel circuits in a row of sub-pixels are coupled to a scan signal line GL, first enable signal terminals EM that are coupled to the pixel circuits in the row of sub-pixels are coupled to an enable signal line E, and reset signal terminals RESET that are coupled to the pixel circuits in the row of 35 sub-pixels are coupled to a reset signal line RL; and data signal terminals DATA that are coupled to pixel circuits in a column of sub-pixels are coupled to a data signal line DL. For example, second enable signal terminals and the first enable signal terminals that are coupled to the pixel circuits 40 in the row of sub-pixels may be coupled to the same enable signal line E. For another example, the row of pixel circuits are coupled to two enable signal lines, and the second enable signal terminals and the first enable signal terminals are coupled to different enable signal lines.

In some examples, the scan signal terminal GATE and one of the first control signal terminal O1 and the second control signal terminal Q2 that are coupled to the same pixel circuit are coupled to the same scan signal line, and the reset signal terminal RESET and the other of the first control signal 50 terminal Q1 and the second control signal terminal Q2 that are coupled to the same pixel circuit are coupled to the same reset signal line. In some examples, the first input signal terminal S1 and the second input signal terminal S2 that are coupled to the same pixel circuit are coupled to the same 55 signal line, such as a second signal line described below; therefore, by controlling amplitudes of signals transmitted by the second signal line, the signals with different amplitudes are provided to the first input signal terminal S1 and the second input signal terminal S2. With this design, it is 60 possible to have a relatively generous wiring space to facilitate realization of a relatively high resolution.

In some embodiments, as shown in FIGS. 7A to 7D, the display panel 100 further includes a plurality of first signal lines LQ and a plurality of second signal lines LS.

For example, first control signal terminals Q1 and second control signal terminals Q2 that are coupled to a row of pixel

20

circuits are coupled to the same first signal line LQ, first input signal terminals S1 and second input signal terminals S2 that are coupled to a column of pixel circuits are coupled to two second signal lines LS, and the first input signal terminals S1 and the second input signal terminals S2 are coupled to different second signal lines LS. In this case, as shown in FIG. 7A, a row of sub-pixels is coupled to the same first signal line LQ, and a column of sub-pixels is coupled to two second signal lines LS.

It can be understood that, a timing of the first control signal and a timing of the second control signal are the same, and a timing of the first input signal and a timing of the second input signal are different.

In this way, the first control circuit 10 simultaneously receives the first input signal and the second input signal in response to the signal at the first control signal terminal Q1 and the second control signal terminal Q2, so that the pixel circuit control the element to be driven to display a corresponding grayscale.