# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

H01L 27/115 (2006.01) H01L 21/8247

(2006.01)

(21) 출원번호 **10-2006-0121420**

(22) 출원일자 **2006년12월04일**

심사청구일자 **2010년11월26일**

(65) 공개번호 **10-2008-0050752**

(43) 공개일자 2008년06월10일

(56) 선행기술조사문헌

KR1020010003086 A\*

KR1020050092508 A

KR1020020096610 A

KR1020050002422 A

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2012년07월23일

(11) 등록번호 10-1166098

(24) 등록일자 2012년07월10일

(73) 특허권자

## 에스케이하이닉스 주식회사

경기도 이천시 부발읍 경충대로 2091

(72) 발명자

#### 이성훈

서울특별시 강동구 천중로49길 58, 107동 911호 (길동, 우성아파트)

(74) 대리인

신영무

전체 청구항 수 : 총 1 항

심사관 : 이우리

## (54) 발명의 명칭 비휘발성 메모리 소자의 제조 방법

## (57) 요 약

본 발명은 비휘발성 메모리 소자의 제조 방법에 관한 것으로, 플로팅 게이트를 U자형으로 형성함으로 써, 플로팅 게이트와 컨트롤 게이트 간 접촉 계면 면적을 증가시켜 커플링 비(coupling ratio)를 증가시키고, 플로팅 게이트 간 소자 분리막의 일정 부분을 식각하여 후속 형성되는 컨트롤 게이트가 플로팅 게이트 간 위치에 형성되게 함으로써 간섭 효과(interference effect)를 감소시킬 수 있는 비휘발성 메모리 소자의 제조 방법에 관한 것이다.

## 대 표 도 - 도2k

### 특허청구의 범위

#### 청구항 1

반도체 기판 상에 터널 절연막, 도전막 및 하드 마스크막 패턴을 형성하는 단계;

상기 하드 마스크막 패턴의 측벽에 절연성 스페이서를 형성하는 단계;

상기 하드 마스크막 패턴 및 상기 절연성 스페이서를 식각 마스크로 사용하는 식각 공정으로 상기 도 전막, 상기 터널 절연막 및 상기 반도체 기판을 식각하여 트렌치를 형성하는 단계;

상기 트렌치 내부에 소자 분리막을 형성하는 단계;

상기 절연성 스페이서를 제거하는 단계;

상기 절연성 스페이서가 제거된 상기 하드 마스크막 패턴의 측벽 및 상기 도전막의 측벽에 도전막 스 페이서를 형성하는 단계; 및

상기 하드 마스크막 패턴을 제거하는 단계를 포함하는 비휘발성 메모리 소자의 제조 방법.

#### 청구항 2

청구항 2은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서.

상기 하드 마스크막 패턴은 순차로 적충된 제1 질화막, 제1 산화막, 제2 질화막, 제2 산화막, 및 제3 질화막을 포함하는 비휘발성 메모리 소자의 제조 방법.

### 청구항 3

청구항 3은(는) 설정등록료 납부시 포기되었습니다.

상기 하드 마스크막 패턴은 하드 마스크막 패터닝시 식각 마스크로 이용하는 감광막 패턴의 폭보다 작은 폭을 갖도록 형성되는 비휘발성 메모리 소자의 제조 방법.

#### 청구항 4

청구항 4은(는) 설정등록료 납부시 포기되었습니다.

제 3 항에 있어서.

상기 하드 마스크막 패턴은 산소 가스 $(0_2 \text{ gas})$ 를 플로우시켜 식각 마스크로 이용되는 감광막 패턴을 등방성 식각시키면서 하드 마스크막을 식각하여 패터닝된 비휘발성 메모리 소자의 제조 방법.

### 청구항 5

청구항 5은(는) 설정등록료 납부시 포기되었습니다.

제 2 항에 있어서,

상기 하드 마스크 패턴은 상기 제3 질화막 상부에 적충된 에싱가능막 및 반사 방지막을 더 포함하고,

상기 절연성 스페이서를 형성하는 단계 이전에 상기 반사 방지막 및 상기 에싱가능막을 제거하는 단계를 더 포함하는 비휘발성 메모리 소자의 제조 방법.

### 청구항 6

청구항 6은(는) 설정등록료 납부시 포기되었습니다.

제 3 항에 있어서,

상기 절연성 스페이서는 상기 감광막 패턴 폭과 상기 하드 마스크막 패턴 폭의 차로 정의되는 리세스 영역과 동일한 폭으로 형성되는 비휘발성 메모리 소자의 제조 방법.

#### 청구항 7

청구항 7은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 절연성 스페이서는 실리콘 산화막(SiO<sub>2</sub>)으로 형성되는 비휘발성 메모리 소자의 제조 방법.

### 청구항 8

청구항 8은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 도전막 스페이서를 형성하는 단계는

상기 절연성 스페이서가 제거된 전체 구조 표면을 따라 플로팅 게이트용 도전막을 형성하는 단계; 및

상기 하드 마스크 패턴 및 상기 소자 분리막이 노출되도록 상기 플로팅 게이트용 도전막을 스페이서 식각 방법으로 식각하는 단계를 포함하는 비휘발성 메모리 소자의 제조 방법.

#### 청구항 9

청구항 9은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 도전막 및 도전막 스페이서는 플로팅 게이트로 형성되는 비휘발성 메모리 소자의 제조 방법.

### 청구항 10

청구항 10은(는) 설정등록료 납부시 포기되었습니다.

제 9 항에 있어서,

상기 플로팅 게이트는 U자 형태를 갖는 비휘발성 메모리 소자의 제조 방법.

#### 청구항 11

청구항 11은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 도전막 및 도전막 스페이서 각각은 폴리실리콘막으로 형성되는 비휘발성 메모리 소자의 제조 방법.

## 청구항 12

청구항 12은(는) 설정등록료 납부시 포기되었습니다.

제 2 항에 있어서,

상기 트렌치를 형성하는 단계에서 상기 하드 마스크막 패턴의 상기 제3 질화막이 제거되고, 상기 제2 산화막은 일부 식각되는 비휘발성 메모리 소자의 제조 방법.

### 청구항 13

청구항 13은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 소자 분리막은 SOG, BPSG, PETEOS, USG, PSG 및 IPO 중에서 선택되는 어느 하나로 형성되는 비휘발성 메모리 소자의 제조 방법.

## 청구항 14

청구항 14은(는) 설정등록료 납부시 포기되었습니다.

제 12 항에 있어서.

상기 소자 분리막을 형성하는 단계는

상기 트렌치를 포함한 전체 구조 상부에 절연막을 형성하는 단계;

상기 절연막을 상기 제2 질화막이 노출되는 시점까지 평탄화하는 단계;

상기 도전막의 측벽이 노출되도록 상기 절연막을 리세스시키는 단계; 및

상기 제2 질화막을 제거하는 단계를 포함하는 비휘발성 메모리 소자의 제조 방법.

### 청구항 15

청구항 15은(는) 설정등록료 납부시 포기되었습니다.

제 14 항에 있어서.

상기 절연성 스페이서를 제거하는 단계에서 상기 제1 산화막이 상기 절연성 스페이서와 동시에 제거되는 비휘발성 메모리 소자의 제조 방법.

### 청구항 16

청구항 16은(는) 설정등록료 납부시 포기되었습니다.

제 14 항에 있어서,

상기 제2 질화막은 인산 용액을 사용하여 제거하는 비휘발성 메모리 소자의 제조 방법.

#### 청구항 17

청구항 17은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 절연성 스페이서는 HF 희석액, NH₄OH, H₂O₂ 및 H₂O로 구성된 SC-1 또는 BOE(Buffer Oxide Etchant; HF와 NH₄F가 100:1 또는 300:1로 혼합된 용액)를 식각액으로 사용하는 세정 공정으로 제거되는 비휘 발성 메모리 소자의 제조 방법.

### 청구항 18

청구항 18은(는) 설정등록료 납부시 포기되었습니다.

제 1 항에 있어서,

상기 절연성 스페이서 제거 시 상기 소자 분리막이 터널 절연막의 외벽 일부를 노출시키도록 리세스 되는 비휘발성 메모리 소자의 제조 방법.

## 명세서

## 발명의 상세한 설명

## 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

[0015] 본 발명은 비휘발성 메모리 소자의 제조 방법에 관한 것으로, 특히 플로팅 게이트와 컨트롤 게이트 간 커플링 비(coupling ratio)를 증가시키고, 플로팅 게이트 간 간섭 효과(interference effect)를 감소시킬 수 있는 비휘발성 메모리 소자의 제조 방법에 관한 것이다.

[0016] NAND형 비휘발성 메모리 소자는 데이터를 저장하기 위한 다수의 셀이 직렬 연결되어 하나의 스트링(string)을 구성하며, 셀 스트링과 드레인 및 셀 스트링과 소오스 사이에 각각 드레인 선택 트랜지스터 및 소오스 선택

트랜지스터가 형성된다. 이러한 NAND형 비휘발성 메모리 소자의 셀은 반도체 기판 상의 소정 영역에 터널 절연막, 플로팅 게이트, 유전체막 및 컨트롤 게이트가 적충된 게이트를 형성하고, 게이트 양측에 접합부를 형성함으로써 형성된다.

- [0017] 이러한 NAND형 비휘발성 메모리 소자는 셀의 상태가 인접한 주변 셀의 동작에 의해 영향을 받기 때문에 셀의 상태를 일정하게 유지하는 것이 매우 중요하다. 이러한 인접한 주변 셀의 동작, 특히 프로그램 동작으로 인해 셀의 상태가 변하게 되는 것을 간섭 효과(interference effect)라 한다. 즉, 간섭 효과란 독출하려는 제1 셀과 인접한 제2 셀을 프로그램하게 되면 제2 셀의 플로팅 게이트의 차지 변화로 인한 커패시턴스(capacitance) 작용으로 인해 제1 셀의 독출시 제1 셀의 문턱 전압(Threshold Voltage; Vth)보다 높은 문턱 전압이 독출되는 현상을 일컫는 것으로, 독출 셀의 플로팅 게이트의 차지는 변화하지 않지만, 인접 셀의 상태 변화에 의해 실제 셀의 상태가 왜곡되어 보이는 현상을 일컫는다. 이러한 간섭 효과로 인해 셀의 상태가 변하게 되며, 이는 불량율을 증가시켜 수율을 저하시키는 결과를 초래한다. 따라서, 간섭 효과를 최소화하는 것이 셀의 상태를 일정하게 유지하는데 효과적이라 할 수 있다.

- [0018] 한편, 일반적인 NAND형 플래시 메모리 소자의 제조 공정에서 SA-STI(Self Aligned-Shallow Trench Isolation) 공정을 이용하여 소자 분리막 및 플로팅 게이트의 일부를 형성하는데, 아래의 도면을 참조하면 그 공정을 간략하게 설명하면 다음과 같다.

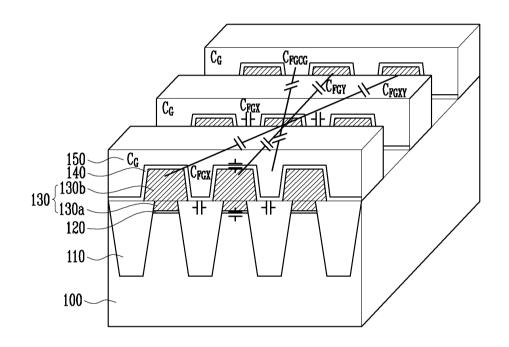

- [0019] 도 1은 종래의 낸드형 비휘발성 메모리 소자를 도시한 사시도이다.

- [0020] 도 1을 참조하면, 반도체 기판(100) 상부에 터널 절연막(120) 및 제1 폴리실리콘막(130a)을 형성한 후 제1 폴리실리콘막(130a)을 형성한 후 제1 폴리실리콘막(130a) 및 터널 절연막(120)의 소정 영역을 식각하고, 반도체 기판(100)을 소정 깊이로 식각하여 트렌치를 형성한 후 절연막을 채우고 연마 공정을 실시하여 소자 분리막(110)을 형성한다. 이후 제2 폴리실리콘막(130b)을 형성하고 식각하여 제1 폴리실리콘막(130a)과 제2 폴리실리콘막(130b)으로 이루어지는 플로팅 게이트(130)를 형성한다. 플로팅 게이트(130) 상부에 유전체막(140) 및 폴리실리콘막으로 이루어진 컨트롤 게이트(150)를 형성한다.

- [0021] 상기와 같이 SA-STI 공정을 이용하여 비휘발성 메모리 소자를 제조하게 되면 플로팅 게이트로 작용되는 제1 폴리실리콘막(130a)과 인접한 제1 폴리실리콘막(130a) 사이에 소자 분리막(110)이 형성되어 있기 때문에 제1 폴리실리콘막(130a)들 사이의 기생 커패시터(capacitor)에 의해 간섭(interference)이 발생할 수 있다.

- [0022] 일반적으로 게이트간 간섭은 플로팅 게이트 간의 거리와 플로팅 게이트의 높이에 비례한다. 즉, 플로팅 게이트 간의 거리가 멀고, 플로팅 게이트의 높이가 감소하면 간섭은 감소한다. 그러나 이와 반대로 플로팅 게이트 의 높이가 감소하면 플로팅 게이트와 컨트롤 게이트의 계면 면적이 감소하여 커플링 비가 감소하는 문제점이 발생한다.

## 발명이 이루고자 하는 기술적 과제

[0023] 본 발명은 U자형 플로팅 게이트를 형성하여 플로팅 게이트와 컨트롤 게이트 간 접촉 계면 면적을 증가시켜 커플링 비를 증가시키고, 플로팅 게이트 간 소자 분리막의 일정 부분을 식각하여 후속 형성되는 콘트롤 게이트 가 플로팅 게이트 간의 위치에 형성되게 함으로써 플로팅 게이트 간 간섭 효과를 감소시키는 비휘발성 메모리소자의 제조 방법을 제공하는 데 있다.

#### 발명의 구성 및 작용

[0024] 상기한 목적을 달성하기 위하여 본 발명에 따른 비휘발성 메모리 소자의 제조 방법은, 반도체 기판상에 터널 절연막, 도전막 및 하드 마스크막 패턴을 형성하는 단계, 상기 하드 마스크막 패턴의 측벽에 절연성 스페이서를 형성하는 단계, 상기 하드 마스크막 패턴 및 상기 절연성 스페이서를 식각 마스크로 사용하는 식각 공정으로 상기 도전막, 상기 터널 절연막 및 상기 반도체 기판을 식각하여 트렌치를 형성하는 단계, 상기 트렌치 내부에 소자 분리막을 형성하는 단계, 상기 절연성 스페이서를 제거하는 단계, 상기 절연성 스페이서가 제거된 상기 하드 마스크막 패턴의 측벽 및 상기 도전막의 측벽에 도전막 스페이서를 형성하는 단계, 및 상기 하드 마스크막 패턴을 제거하는 단계를 포함한다.

[0025]

이하, 첨부된 도면들을 참조하여 본 발명의 실시예를 보다 상세히 설명한다. 그러나, 본 발명의 실시예들은 여러 가지 다른 형태로 변형될 수 있으며, 본 발명의 범위가 아래에서 상술하는 실시예들로 인해 한정되어지는 것으로 해석되어져서는 안되며, 당업계에서 보편적인 지식을 가진 자에게 본 발명을 보다 완전하게 설명하기 위해서 제공되어지는 것으로 해석되는 것이 바람직하다.

[0026]

도 2a 내지 도 2k는 본 발명의 일 실시예에 따른 비휘발성 메모리 소자의 제조 방법을 설명하기 위한 공정단면도이다.

[0027]

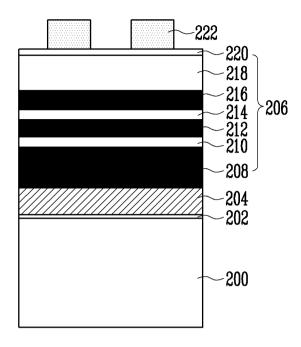

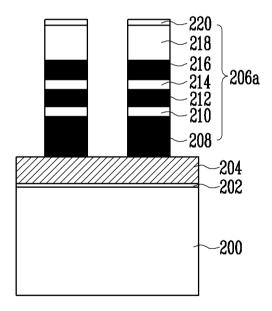

우선, 도 2a를 참조하면, 반도체 기판(200) 상부에 터널 절연막(202), 플로팅 게이트용 제1 도전막(204) 및 하드 마스크막(206)을 순차적으로 적충하여 형성한다. 여기서, 터널 절연막(202)은 실리콘 산화막(SiO<sub>2</sub>)으로 형성할 수 있으며, 이 경우 산화막(202)은 산화(Oxidation) 공정에 의해 형성할 수 있다.

[0028]

플로팅 게이트용 제1 도전막(204)은 폴리실리콘막, 금속막 또는 이들의 적층막으로 형성할 수 있다. 바람직하게, 상기 제1 도전막(204)은 하부 기판과의 표면 접착성이 우수한 폴리실리콘막으로 형성한다. 제1 도전막(204)은 화학기상증착(Chemical Vapor Deposition; CVD) 방법 또는 물리기상증착(Physical Vapor Deposition; PVD) 방법으로 증착하여 형성할 수 있으며, 바람직하게 저압화학기상증착(Low Pressure CVD; LPCVD) 방법으로 형성할 수 있다.

[0029]

하드 마스크막(206)은 제1 질화막(208), 제1 산화막(210), 제2 질화막(212), 제2 산화막(214), 제3 질화막(216), 에싱가능막(ashable layer; 218) 및 반사방지막(Anti Reflective Coating Layer; ARC, 220)을 순차적으로 적층하여 형성한다. 제1, 제2 및 제3 질화막(208, 212, 216)은 CVD 방법, 예컨대 LPCVD 방법을 이용하여 실리콘 질화막(SixNy) 또는 실리콘 산화질화막(SiON)과 같은 질화물 계열의 물질(이하 '질화막'이라한다)로 형성한다. 여기서, 제2 질화막(212)은 후속한 소자 분리막 형성 시 화학적 기계적 연마(Chemical Vapor Deposition; CMP) 공정을 이용한 평탄화과정에서 종료점(end point)을 알려주는 연마정지막으로 사용하기 위하여 형성한다. 제1 산화막(210)은 실리콘 산화막(SiO<sub>2</sub>)으로 형성할 수 있으며, 이 경우 산화 공정으로 형성할 수 있다. 제2 산화막(214)은 실리콘 산화막(SiO<sub>2</sub>)으로 형성할 수 있으며, CVD 방법, 예컨대 LPCVD 방법으로 형성할 수 있다.

[0030]

에성가능막(218)은 에성(ashing)으로 제거할 수 있는 물질이면 적용 가능하며, 아모퍼스 카본막 (amorphous carbon) 또는 수지막(resin)으로 형성할 수 있다. 바람직하게는 에싱가능막(218)은 아모퍼스 카본 막으로 형성한다. 반사방지막(220)은 감광막(photo resist layer)을 이용한 사진 공정(Photolithography) 시반사 방지를 위해 실리콘 산화질화막(SiON)으로 형성할 수 있으며, CVD 방법으로 형성한다.

[0031]

이후, 포토레지스트(Photo Resist; PR)를 하드 마스크막(206) 상부에 스핀 코팅(spin coating) 방법으로 도포하여 감광막(미도시)을 형성한 후 기 제작된 마스크를 이용한 사진 및 식각 공정으로 패터닝하여 하드 마스크막(206)을 패터닝하기 위한 감광막 패턴(222)을 형성한다.

[0032]

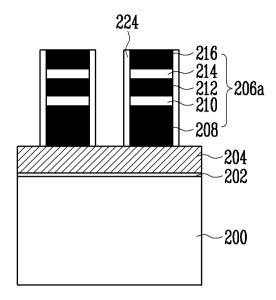

도 2b를 참조하면, 감광막 패턴(222)을 식각 마스크로 한 건식 식각(dry etch) 방법으로 하드 마스크 막(206)을 소정 영역 식각한다. 건식 식각 공정 시 과량의 산소 가스(0₂ gas)를 플로우(flow)시켜 감광막 패턴(222)을 등방성(isotropic) 식각시키면서 하드 마스크막(206)을 식각하여 패터닝한다. 따라서, 하드 마스크막 패턴(206a)은 감광막 패턴(222)의 폭보다 작은 폭을 갖도록 형성된다. 여기서, 감광막 패턴(222)의 폭과 패터 닝된 하드 마스크막 패턴(206a)의 폭의 차이는 리세스 영역으로 정의하기로 한다.

[0033]

이렇게, 리세스 영역만큼 하드 마스크막 패턴(206a)이 감광막 패턴(222)의 폭보다 작은 폭을 갖도록 형성됨으로써 후속 공정에서 하드 마스크막 패턴(206a)이 리세스된 영역에 스페이서를 이용하여 플로팅 게이 트의 모양을 U자형으로 형성할 수 있게 된다.

[0034]

이후, 감광막 패턴(222) 및 하드 마스크막 패턴(206a)의 반사방지막(220) 및 에싱가능막(218)을 제거하다.

[0035]

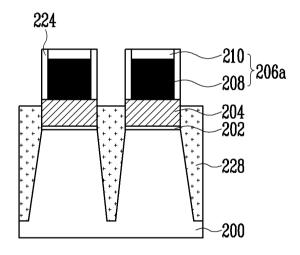

도 2c를 참조하면, 하드 마스크막 패턴(206a) 측벽의 리세스 영역에 스페이서(224)를 형성한다. 스페이서(224)는 산화막으로 형성하며, 이 경우 실리콘 산화막(SiO<sub>2</sub>)으로 형성할 수 있다. 스페이서(224)는 하드 마스크막 패턴(206a)의 리세스 영역과 동일한 폭으로 형성하여 감소된 하드 마스크막 패턴(206a)의 폭을 보상해줌으로써 소자 분리막 패턴 식각 완료 후 감광막 패턴(222)으로 형성할 수 있는 것과 동일한 활성 영역의 폭을 확보하도록 한다.

[0036]

스페이서(224)는 하드 마스크막 패턴(206a)을 포함하는 반도체 기판(200) 상부에 리세스 영역과 동일 한 폭의 산화막(미도시)을 증착한 후 스페이서 식각 방법을 이용하여 수평부에 증착된 산화막을 제거하고 수 직부에 증착된 산화막만을 잔류시킴으로써 하드 마스크막 패턴(206a)의 측벽에만 형성된다.

[0037]

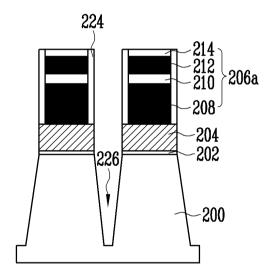

도 2d를 참조하면, 하드 마스크막 패턴(206a) 및 스페이서(224)를 식각 마스크로 하여 제1 도전막(204), 터널 절연막(202) 및 반도체 기판(200)을 소정 영역 식각하여 반도체 기판(200)의 소자 분리 영역에 트렌치(226)를 형성한다. 이렇게, 트렌치(226)는 반도체 기판(200)에 SA-STI(Self Aligned-Shallow Trench Isolation) 공정을 실시하여 형성하는 것이 바람직하다. 한편, 트렌치(226) 형성 과정에서 제3 질화막(216)이 제거되고, 제2 산화막(214)도 일부 식각된다.

[0038]

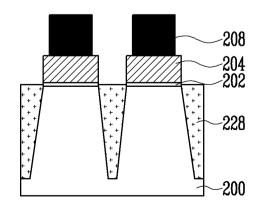

도 2e를 참조하면, 트렌치(226)를 채우도록 트렌치(226)를 포함하는 반도체 기판(200) 상부에 절연물질을 증착하여 갭 필 절연막(미도시)을 형성한 후 하드 마스크막 패턴(206a)의 제2 질화막(212)이 노출되는시점까지 평탄화한다.

[0039]

갭 필 절연막은 SOG(Spin On Glass), BPSG(Boron-Phosphorus Silicate Glass), PETEOS(Plasma Enhanced Tetra Ortho Silicate Glass), USG(Undoped Silicate Galss), PSG(Phosphorus Silicate Glass) 및 IPO(Inter Poly Oxide) 중에서 선택되는 어느 하나를 이용하여 형성할 수 있다. 여기서, 평탄화는 CMP 공정으로 실시할 수 있다. 이로써, 트렌치(226)를 채우는 소자 분리막(228)이 형성된다.

[0040]

한편, 트렌치(226)를 채우기 위한 갭 필 절연막 증착 전에는 트렌치(226) 형성 시 식각 공정으로부터 발생한 손상(damage)을 치유하기 위하여 측벽 산화 공정을 더 실시할 수 있다. 또한, 트렌치(226) 내부로 갭 필 절연막의 매립 특성을 향상시키기 위하여 하드 마스크막 패턴(206a), 제1 도전막(204), 터널 절연막(202)의 측벽 및 트렌치(226) 내부에 라이너 산화막을 더 형성할 수 있다.

[0041]

도 2f를 참조하면, 도면으로 도시하지는 않았지만 주변회로 영역을 마스크로 씌우고 셀 영역을 오픈한 상태에서 제1 도전막(204)의 외벽 일부가 노출되도록 소자 분리막(228)을 소정 두께만큼 식각하여 리세스 (recess)시킨다. 리세스 공정은 제2 질화막(212)에 대한 식각 선택비가 높은 조건을 이용한 건식 식각(dry etch) 방법으로 실시하며, 제2 질화막(212)을 식각정지막으로 사용한다. 이후, 제2 질화막(212)을 제거한다. 제2 질화막(212)의 제거는 인산 용액(H<sub>4</sub>PO<sub>4</sub>)을 사용하여 실시할 수 있다.

[0042]

이렇게, 제2 질화막(212)을 식각정지막으로 사용하여 제2 질화막(212)의 일부를 남긴 후, 제2 질화막(212)을 제거하고 제1 산화막(210)의 일부만을 남김으로써 제1 질화막(208)의 두께를 일정하게 유지하도록 하여 후속 증착될 플로팅 게이트용 제2 도전막(미도시)의 높이를 일정하게 하도록 한다.

[0043]

도 2g를 참조하면, 플로팅 게이트용 제2 도전막(미도시) 증착 전 반도체 기판(200)의 세정 공정을 실시한다. 이 과정에서 소자 분리막(228)이 일부 두께만큼 식각되어 터널 절연막(202)의 외벽 일부가 노출되며, 소자 분리막(228)의 유효 필드 산화막 두께(Effective Field Oxide Height; EFH)가 제어된다.

[0044]

상기한 바와 같이, 소자 분리막(228)이 터널 절연막(202)의 외벽 일부를 노출시키도록 형성됨으로써 활성 영역과 활성 영역 사이의 소자 분리 영역이 좁은 60nm 이하의 소자에서도 후속 형성되는 컨트롤 게이트 가 플로팅 게이트 간에 위치하도록하여 플로팅 게이트 간 기생 커패시터(capacitor)로 인한 간섭 효과를 감소 시킬 수 있다.

[0045]

세정 공정의 식각액으로는 HF 희석액, NH<sub>4</sub>OH, H<sub>2</sub>O<sub>2</sub> 및 H<sub>2</sub>O로 구성된 SC-1 또는 BOE(Buffer Oxide Etchant; HF와 NH<sub>4</sub>F가 100:1 또는 300:1로 혼합된 용액)를 이용할 수 있다.

[0046]

한편, 세정 공정 시 스페이서(224)와 하드 마스크막 패턴(206a)의 제1 산화막(210)도 제거된다. 반면, 하드 마스크막 패턴(206a)의 제1 질화막(208)은 식각액에 대해 낮은 식각 선택비를 갖으므로 식각되지 않는다.

[0047]

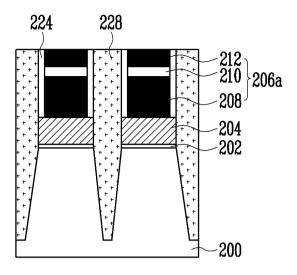

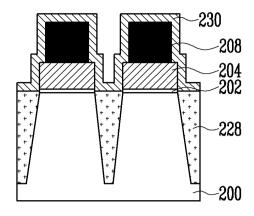

도 2h를 참조하면, 하드 마스크막 패턴(206a)의 제1 질화막(208)을 포함하는 반도체 기판(200) 상부에 플로팅 게이트용 제2 도전막(230)을 형성한다. 제2 도전막(230)은 제1 도전막(204) 상부에 제1 도전막(204)의 폭보다 좁은 폭을 갖는 제1 질화막(208)으로 인해 단차를 갖도록 형성된다. 여기서, 제2 도전막(230)은 폴리실리콘막, 금속막 또는 이들의 적충막으로 형성할 수 있다. 바람직하게는 폴리실리콘막으로 형성한다. 제2 도전막(230)은 CVD 방법 또는 PVD 방법으로 형성하며, 바람직하게 LPCVD 방법으로 형성한다.

[0048]

도 2i를 참조하면, 제2 도전막(230)을 스페이서 식각 방법으로 식각하여 제1 도전막(204) 및 하드 마

스크막 패턴(206a)의 제1 질화막(208)의 측벽에 제2 도전막 스페이서(230a)를 형성한다. 여기서, 스페이서 식각 방법으로 인해 수평부에 증착된 제2 도전막(230)은 제거되고 수직부에 증착된 제2 도전막(230)만이 하드 마스크막 패턴(206a)의 제1 질화막(208) 및 제1 도전막(204)의 측벽에 잔류된다.

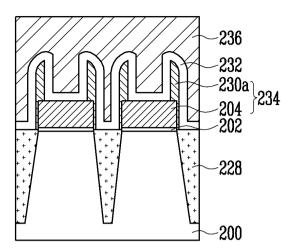

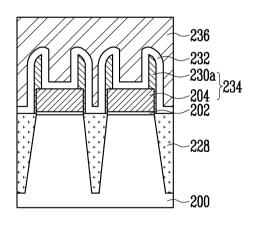

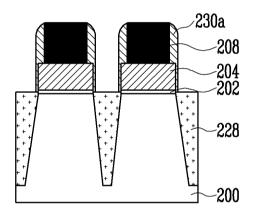

[0049] 도 2j를 참조하면, 하드 마스크막 패턴(206a)의 제1 질화막(208)을 제거한다. 제1 질화막(208)은 질화막(208)에 대해 높은 식각 선택비를 갖는 인산 용액(H<sub>3</sub>PO<sub>4</sub>)을 이용한 습식 식각 공정으로 제거할 수 있다. 이로써, 제1 도전막(204) 상부의 양말단부에 돌출된 제2 도전막 스페이서(230a)가 형성된다.

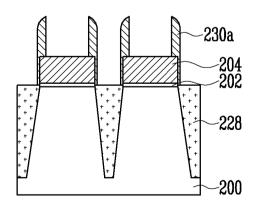

도 2k를 참조하면, 플로팅 게이트용 제2 도전막 스페이서(230a)를 포함한 반도체 기판(200) 상부에 유전체막(232)을 형성한다. 유전체막(232)은 산화막, 질화막, 산화막이 순차적으로 적층된 ONO(Oxide-Nitride-Oxide) 구조로 형성될 수 있다. 유전체막(232)은 CVD 방법에 의해 형성할 수 있으며, 바람직하게 LPCVD 방법에 의해 형성할 수 있다.

이어서, 유전체막(232) 상부에는 컨트롤 게이트용 제3 도전막(미도시)을 형성한다. 제3 도전막은 폴리실리콘막, 금속막 또는 이들의 적충막으로 형성할 수 있다. 제3 도전막은 CVD 또는 PVD 방법에 의해 형성할 수 있다.

이후, 통상적인 공정으로 제3 도전막, 유전체막(232), 제2 도전막 스페이서(230a) 및 제1 도전막 (204)을 순차적으로 패터닝한다. 이로써, 제1 도전막(204) 및 제2 도전막 스페이서(230a)로 이루어진 플로팅 게이트(234)와 제3 도전막으로 이루어진 컨트롤 게이트(236)가 형성된다. 이 경우, 플로팅 게이트(234)는 요 (발) 형태, 즉 U자 형태를 갖도록 형성된다.

상기한 바와 같이, 플로팅 게이트(234)가 U자형으로 형성되어 플로팅 게이트(234)와 컨트롤 게이트 (236) 간 접촉 계면 면적이 증가되므로 커플링 비가 증가되고, 이로 인해 프로그램 속도가 개선된다.

또한, 플로팅 게이트(234) 사이에 유전체막(232) 및 컨트롤 게이트(236)가 형성되어 플로팅 게이트(234) 사이를 서로 이격시킴으로써 플로팅 게이트(234) 간 간섭 효과를 개선할 수 있다.

본 발명은 이상에서 살펴본 바와 같이 바람직한 실시예에 대하여 설명하였지만, 본 발명은 이에 한정되는 것은 아니며, 본 발명이 속하는 기술분야의 통상의 지식을 가진 자라면 특허청구범위와 발명의 상세한설명 및 첨부한 도면의 범위 안에서 여러 가지로 변형하여 실시하는 것이 가능하고 이 또한 본 발명의 범위에속하는 것은 당연하다.

#### 발명의 효과

[0050]

[0051]

T00521

[0053]

[0054]

[0055]

[0057]

[0056] 본 발명은 플로팅 게이트를 U자형으로 형성함으로써, 플로팅 게이트와 컨트롤 게이트 간 접촉 계면 면적을 증가시켜 커플링 비를 증가시켜 셀의 프로그램 속도를 개선할 수 있다.

또한, 본 발명은 플로팅 게이트 간 소자 분리막의 일정 부분을 식각하여 후속 형성되는 컨트롤 게이트가 플로팅 게이트 간 위치에 형성되게 함으로써 플로팅 게이트 간 간섭 효과를 감소시킬 수 있다.

### 도면의 간단한 설명

[0001] 도 1은 종래의 낸드형 비휘발성 메모리 소자를 도시한 사시도이다.

[0002] 도 2a 내지 도 2k는 본 발명의 일 실시예에 따른 비휘발성 메모리 소자의 제조 방법을 설명하기 위한 공정단 면도이다.

[0003] <도면의 주요 부분에 대한 부호의 설명>

[0004] 200 : 반도체 기판 202 : 터널 절연막

[0005] 204 : 제 1 도전막 206 : 하드 마스크막

[0006] 206a : 하드 마스크막 패턴 208 : 제1 질화막

[0007] 210 : 제1 산화막 212 : 제2 질화막

[0008] 214 : 제2 산화막 216 : 제3 질화막

[0009] 218 : 에싱가능막 220 : 반사방지막

[0010] 222 : 감광막 패턴 224 : 스페이서

[0011] 226 : 트렌치 228 : 소자 분리막

[0012] 230 : 제2 도전막 230a : 제2 도전막 스페이서

[0013] 232 : 유전체막 234 : 플로팅 게이트

[0014] 236 : 컨트롤 게이트

## 도면

## 도면1

도면2a

# 도면2b

# 도면2c

# 도면2d

# *도면2e*

# *도면2f*

# 도면2g

# 도면2h

# 도면2i

# *도면2j*

# 도면2k