## (19) SU (11) 1130858 A

3(51) G 06 F 5/02

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

## ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

- (21) 3626723/24-24

- (22) 26.07.83

- (46) 23.12.84. Бюл. № 47

- (72) Е.М.Митюшин и А.Э.Трифель

- (71) Всесоюзный научно-исследовательский институт нефтепромысловой геофизики

- (53) 681.325(088.8)

- (56) 1. Авторское свидетельство СССР № 468236, кл. G 06 F 5/02, 1972.

- 2. Патент ФРГ № 1269655, кл. G 06 F 5/02, опублик. 1974 (прототип).

(54) (57) 1. ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ, содержащий группу двоичных счетчиков, первую группу элементов И, распределитель импульсов, генератор импульсов, первую группу элементов ИЛИ, элемент задержки, умножитель, группу двоично-десятичных счетчиков, разрядные выходы которых являются выходами преобразователя, выход переноса і-го двоично-десятичного счетчика группы [i=1-(h-1)], где (n+1) - число разрядов выходного кода, соединен с первым входом і-го элемента ИЛИ первой группы, выход которого соединен с входом сложения (n+1)-го двоично-десятичного счетчика группы, выход переноса п-го двоично-десятичного счетчика группы соединен с входом сложения (n+1)-го двоично-десятичного счетчика группы, выходы распределителя импульсов соединены с первыми входами соответствующих элементов И первой группы, выходы которых соединены со счетными входами соответствующих двоичных счетчиков группы, выход j-го (j=2-n) элемента И первой группы соединен с (1-1)-м входом умножителя, выход первого элемента И первой группы соединен с входом сложения первого двоично-десятичного счетчика группы, вход сброса распределителя импульсов соединен с выходами заема двоичных счетчиков группы, о т л и ч ающийся тем, что, с целью повышения быстродействия, в него введены первый и второй элементы И, делитель частоты и вторая группа элементов ИЛИ, а двоично-десятичные счетчики группы выполнены реверсивными, причем выход заема (j-1)-го двоично-десятичного счетчика группы соединен с первым входом (1-1)-го элемента ИЛИ второй группы, выход которого соединен с входом вычитај-го двоично-десятичного счетния чика группы, выход заема п-го двоично-десятичного счетчика группы соединен с входом вычитания (n+1)-го двоично-десятичного счетчика группы, первый и второй выходы умножителя соединены с первыми входами первого и второго элементов И соответственно, вторые входы которых соединены с вторым и третьим выходами распределителя импульсов, а выходы соединены с вторыми входами элементов ИЛИ первой группы соответственно, выход второго элемента И через элемент задержки соединен с вторым входом первого элемента ИЛИ второй группы. второй вход второго элемента ИЛИ которой соединен с выходом элемента И первой группы, вторыс входы элементов И которой через делитель частоты соединены с выходом генератора импульсов и тактовым вхо-

SU 1130858

20

дом умножителя, информационные входы двоичных счетчиков группы являются информационным входом преобразователя, вход пуска которого соединен с входом пуска распределителя

импульсов, второй выход умножителя

соединен с входом вычитания первого

двоично-десятичного счетчика группы.

2. Преобразователь по п.1, о т - л и ч а ю щ и й с я тем, что в нем умножитель содержит счетчик, элемент И-НЕ, элемент И и элемент ИЛИ, входы которого являют-

ся группой входов умножителя, а выкод элемента ИЛИ соединен с входом

сброса счетчика, выход старшего разряда которого через элемент НЕ соединен с первым входом элемента И,

второй вход которого является тактовым входом умножителя, выходы которого являются выходами элементов

И-НЕ и И соответственно, выход элемента И соединен с синхровходом счетчика и первым входом элемента И-НЕ,

второй вход которого соединен с выходом младшего разряда счетчика.

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для обработки дискретной информации.

Известно устройство для преобразования двоичного кода в двоичнодесятичный, содержащее двоичный и десятичный счетчики, разбитые на секции, собирательные схемы перевода

весовых значений граничных разрядов

каждого двоичного кода в соответствующее весовое значение десятичного

разряда, элементы И и элементы ИЛИ,

дешифраторы нуля двоичного счетчика [1],

Однако этот преобразователь имеет большое время преобразования, которое определяется временем последовательного преобразования младших разрядов.

Наиболее близким к изобретению по технической сущности и схемному построению является преобразователь двоичного кода в двоично-десятичный, содержащий последовательный десятичный декадный счетчик, двоичные счетчики, распределитель импульсов, группу элементов И, группу элементов ИЛИ, умножитель, элемент задержки, причем элементы ИЛИ включены на входы старшей, средней и младшей декад двоично-десятичного счетчика, соответственно первые входы элемен-35 тов И подключены к соответствующим выходам распределителя импульсов, а вторые входы элементов И подключены к генератору тактовых импуль сов [2].

Недостатком известного преобразователя является относительно низкое быстродействие, связанное с тем, что десятичный эквивалент граничных разрядов двоичного кода представляется только положительными числами.

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный, содержащий группу двоичных счетчиков, первую группу элементов И, распределитель импульсов, генератор импульсов, первую группу элементов ИЛИ, элемент задержки, умножитель, группу двоично-десятичных счетчиков, разрядные выходы которых являются выходами преобразователя, выход переноса і-го двоично-десятичного счетчика группы (i=1-(n-1), где (h+1)-го - число разрядов выходного кода, соединен с первым входом элемента ИЛИ первой группы, выход которого соединен с входом сложения (i+1)-го двоично-десятичного счетчика группы, выход переноса п-го двоично-десятичного счетчика группы соединен с входом сложения (n+1)-го двоично-десятичного счетчика группы, выходы распределителя импульсов соединены с первыми входами соответствующих элементов И первой группы, выходы которых соединены со счетными входами соответствующих двоичных

2

счетчиков группы, выход (¡≈2-n) элемента И первой группы соединен с (ј-1)-м входом умножителя, выход первого элемента И первой группы соединен с входом сложения первого двоично-десятичного счетчика группы, вход сброса распределителя импульсов соединен с выходами заема двоичных счетчиков группы, дополнительно введены первый и второй элементы И, делитель частоты и вторая группа элементов ИЛИ, а двоичнодесятичные счетчики группы выполнены реверсивными, причем выход заема (1-1)-го двоично-десятичного счетчи- 15 ка группы соединен с первым входом (;-1)-го элемента ИЛИ второй группы, выход которого соединен с входом выј-го двоично-десятичного читания счетчика группы, выход заема п-го 20 двоично-десятичного счетчика группы соединен с входом вычитания (м+1)-го двоично-десятичного счетчика группы, первый и второй выходы умножителя соединены с первыми входами первого и второго элементов И соответственно, вторые входы которых соединены с вторыми и третьими выходами распределителя импульсов, а выходы соединены с вторыми входами элементов ИЛИ 30 первой группы соответственно, выход второго элемента И через элемент задержки соединен с вторым входом первого элемента ИЛИ второй группы, второй вход второго элемента ИЛИ которой соединен с выходом h-го элемента И первой группы, вторые входы элементов И которой через делитель частоты соединены с выходом генератора импульсов и с тактовым входом умножителя, информационные входы двоичных счетчиков группы являются информационным входом преобразователя, вход пуска которого соединен с входом пуска распределителя импульсов, второй выход умножителя соединен с входом вычитания первого двоично-десятичного счетчика группы.

Умножитель содержит счетчик, элемент И-НЕ, элемент НЕ, элемент И и элемент ИЛИ, входы которого являются группой входов умножителя, а выход элемента ИЛИ соединен с входом сброса счетчика, выход старшего разряда которого через элемент НЕ соеди-55 нен с первым входом элемента И, второй вход которого является тактовым входом умножителя, выходы которого

являются выходами элементов И-НЕ и И соответственно, выход элемента И соединен с синхровходом счетчика и первым входом элемента И-НЕ, второй вход которого соединен с выходом младшего разряда счетчика.

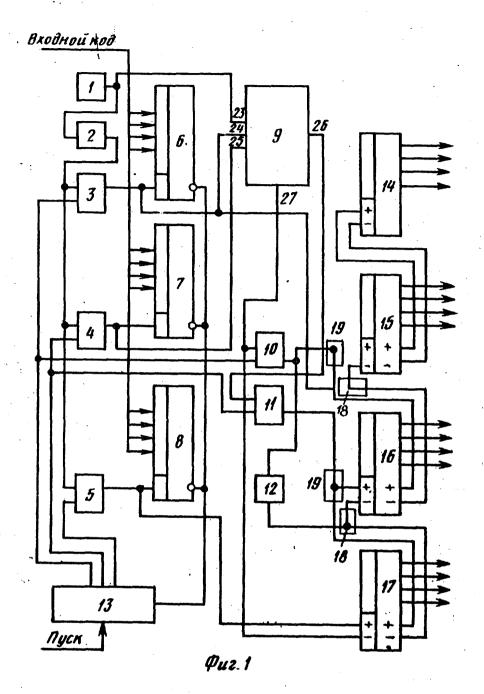

На фиг.1 показана блок-схема пред лагаемого преобразователя: на фиг. 2блок-схема умножителя.

Предлагаемый преобразователь ч содержит генератор 1 импульсов, делитель 2 частоты, элементы И 3-5 первой группы, двоичные счетчики 6-8 группы, умножитель 9, элементы И 10 и 11, элемент 12 задержки, распределитель 13 импульсов, двоичнодесятичные счетчики 14-17 группы, первую и вторую группы элементов ИЛИ 18 и 19.

Умножитель (фиг.2) содержит элемент И-НЕ 20, элемент ИЛИ 21, элемент НЕ 22, тактовый вход 23, входы 24 и 25 умножителя, выходы 26 и 27 умножителя, (на выходе 26 появляется результат умножения на 2, а на выходе 27 - на 4), счетчик 28 и элемент И 29.

Преобразователь работает следующим образом.

В исходном состоянии в двоичные счетчики 6-8 записан двенадцатиразрядный двоичный код. По команде "Пуск" распределитель импульсов подает разрешение на элемент И 3. подключенный к двоичному счетчику 6 старшей тетрады, на вход вычитания которой поступает тактовая частота от генератора 1 импульсов через делитель 2 импульсов. В момент равенства кода на выходе счетчика нулю на вход распределителя 13 импульсов поступает сигнал, который переключает его и подает разрешение на элемент И 4, отключая тактовые импульсы с входа старшей тетрады. После того, как на выходе счетчика 7 будет код, равный нулю, аналогичным образом включается младшая тетрада двоичного счетчика. Таким образом, на выходе элемента И 3 появляется количество импульсово соответствующее коду числа, записанному в двоичном счетчике 6 %, , на выходе элементов И 4 и И 5 - соответственно число импульсов  $N_2$  и  $N_3$ , количество которых соответствует кодам двоичных счетчиков 7 и 8. Для получения числе в двоично-десятичном коде на вход

последовательного двоично-десятичного счетчика необходимо подать количество импульсов  $N_1$ , умноженное на 256, число импульсов  $N_2$ , умноженное на 16, и  $N_2$  – на 1.

Умножение числа импульсов на 256 можно осуществить как 256  $N_4$  = = 100  $\cdot$  4 $N_1$  - 100  $\cdot$  1 $N_4$  - 10  $\cdot$  4 $N_4$  - 1  $\cdot$  4 $\cdot$  4 $\cdot$  1  $\cdot$  4 $\cdot$  1  $\cdot$  4 $\cdot$  1  $\cdot$  4 $\cdot$  2  $\cdot$  2  $\cdot$  2  $\cdot$  2  $\cdot$  3  $\cdot$  2  $\cdot$  3  $\cdot$  4  $\cdot$  3  $\cdot$  3  $\cdot$  3  $\cdot$  3  $\cdot$  3  $\cdot$  4  $\cdot$  3  $\cdot$  4  $\cdot$  3  $\cdot$  3  $\cdot$  3  $\cdot$  4  $\cdot$  4  $\cdot$  3  $\cdot$  4  $\cdot$  4  $\cdot$  3  $\cdot$  4  $\cdot$  4

Так как веса двоично-десятичных счетчиков 15-17 соответственно равны 100, 10 и 1, то необходимо количество импульсов, умноженное на 4, подать на вход сложения двоично-десятичного счетчика 15, на вход вычитания подать непосредственно сами импульсы, а на вход вычитания счетчиков 16 и 17 соответственно подается количество импульсов N<sub>1</sub>, умноженное на 4.

После обнуления двоичного счетчика 6 распределитель импульсов подключает счетчик 7. На выходе элемента И 4 до полного обнуления этого счетчика будет  $N_2$  импульсов.

Умножение числа импульсов N<sub>2</sub> на 16 возможно осуществить следующим образом

$16N_2 = 10 \cdot 2N_2 - 1 \cdot 4N_2$ , т.е. на вход сложения счетчика 16 необходимо подать количество импуль $cob N_1$ , умноженное на 2, а на вход вычитания счетчика 17  $N_2$ , умноженное на 4. Импульсы на выходе элемента И 5 непосредственно подаются на вход сложения счетчика 17. Элемен-35 ты И 10 и 12 служат для коммутации выходов умножителя сигналов на входы двоично-десятичных счетчиков. При опросе счетчика 6 открыт элемент И 10, и умноженные импульсы с выхода 40 27 умножителя сигналов 9 поступают на вход сложения счетчика 15 и через элемент 12 задержки на вход вычитания счетчика 16.

Во время опроса счетчика 7 элемент И 10 выключен, а включен элемент И 11, который коммутирует выход 26 умножителя 9 на вход сложения счетчика 16. Умножитель 9 представляет собой устройство, которое при подаче на его вход одного импульса выдает на выходе 27 четыре, а на выходе 26 - два импульса, длительность и период следования которых такие, что они укладываются за период между входными импульсами.

Умножитель работает следующим образом.

При поступлении на вход (24 или 25) импульса счетчик сбрасывается, через элемент НЕ 22 открывается элемент И 29, и на счетный вход поступают импульсы. При поступлении четвертого импульса на выходе третьего разряда счетчика 28 появляется единица, и элемент И 29 закрывается. На выход 27 пройдут четыре импульса, а через элемент И 20 - каждый нечетный импульс и поэтому на выходе 26 будут два импульса.

Распределитель 13 импульсов может быть выполнен по стандартной схеме или на сдвиговом регистре или на счетчике с дешифратором.

"Используя предлагаемое устройство, возможно проводить преобразование двоичных чисел с большим количеством разрядов. Для преобразования 16-разрядного кода количества импульсов старшей тетрады необходимо умножить на 4096.

Это можно представить в следую-

$4096N_4 = 1000 \cdot 4N_4 + 100 \cdot 1N_4 - 1 \cdot 4N_4$

т.е. устройство усложняется незначительно за счет введения двух дополнительных элементов И и одного разряда распределителя импульсов.

Предлагаемый преобразователь позволяет существенно повысить скорость преобразования, так как в известном преобразователе на прибавление числа 256 требуется 6 импульсов, а в предложенном только 4.