# (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 106601199 B (45)授权公告日 2019.03.12

(21)申请号 201610975369.3

(22)申请日 2016.11.07

(65)同一申请的已公布的文献号 申请公布号 CN 106601199 A

(43)申请公布日 2017.04.26

(73)专利权人 深圳市华星光电技术有限公司 地址 518132 广东省深圳市光明新区塘明 大道9-2号

(72)发明人 徐向阳

(74)专利代理机构 广州三环专利商标代理有限 公司 44202

代理人 郝传鑫 熊永强

(51) Int.CI.

*G09G* 3/36(2006.01) *G02F* 1/1362(2006.01)

# (56)对比文件

CN 105280150 A, 2016.01.27,

KR 20080001403 A,2008.01.03,

US 2007182667 A1,2007.08.09,

CN 105374330 A,2016.03.02,

审查员 史孝波

权利要求书1页 说明书4页 附图3页

#### (54)发明名称

液晶面板驱动电路及液晶显示器

### (57)摘要

本发明提供一种液晶面板驱动电路及液晶显示器。液晶面板驱动电路包括:数据线、栅极扫描线、第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管、第一像素电极、第二公共电极和控制信号生成装置。控制信号生成装置生成控制信号。控制信号的周期为帧周期。控制信号在相邻两帧间的间隔时段内为高电平,在其他时段内为低电平。通过在每帧扫描显示完成后,将第一公共电极与第二公共电极连接通过一次,将第一公共电极上的直流电荷释放到第二公共电极上,进而保证第一公共电极不会因为电荷累积而影响液晶面板显示效果。

1.一种液晶面板驱动电路,包括:数据线、栅极扫描线、第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管、第一像素电极和第二像素电极;其特征在于,还包括第一公共电极、第二公共电极和控制信号生成装置;

其中,所述第一薄膜晶体管、所述第二薄膜晶体管、所述第三薄膜晶体管的栅极均与所述栅极扫描线连接,所述第一薄膜晶体管、所述第二薄膜晶体管的源极均与所述数据线连接,所述第一薄膜晶体管的漏极与所述第一像素电极相连,所述第二薄膜晶体管的漏极、所述第三薄膜晶体管的源极均与所述第二像素电极相连,所述第一像素电极与所述第二像素电极均与所述第二公共电极相连,所述第三薄膜晶体管的漏极与所述第一公共电极相连;

所述第一公共电极、所述第二公共电极分别与所述第四薄膜晶体管的漏极和源极相 连,所述第四薄膜晶体管的栅极与所述控制信号生成装置连接;

所述控制信号生成装置用于生成控制信号。

- 2.根据权利要求1所述的液晶面板驱动电路,其特征在于,所述控制信号的周期为帧周期,所述控制信号在相邻两帧之间的间隔时段内为高电平,在其他时段内为低电平。

- 3.根据权利要求1所述的液晶面板驱动电路,其特征在于,所述第一公共电极包括: 平行设置且位于边界的第一边界子公共电极和第二边界子公共电极;以及

垂直于所述第一边界子公共电极且将所述第一边界子公共电极和所述第二边界子公共电极连接的第一中间子公共电极;

所述第二公共电极包括:

平行设置且位于边界的第三边界子公共电极和第四边界子公共电极;以及

垂直于所述第三边界子公共电极且将所述第三边界子公共电极和所述第四边界子公 共电极连接的第二中间子公共电极:

所述第一边界子公共电极、所述第三边界子公共电极分别与所述第四薄膜晶体管的漏极和源极相连。

- 4.根据权利要求1所述的液晶面板驱动电路,其特征在于,所述第一公共电极与所述第二公共电极之间采用悬浮式结构连接。

- 5.根据权利要求1所述的液晶面板驱动电路,其特征在于,所述第一公共电极与所述第二公共电极之间采用静电保护回路连接。

- 6.根据权利要求5所述的液晶面板驱动电路,其特征在于,所述静电保护回路包括第五 薄膜晶体管和第六薄膜晶体管,其中,所述第五薄膜晶体管的源极、漏极分别与所述第六薄 膜晶体管的漏极、源极相连,所述第五薄膜晶体管的栅极和源极均与所述第一公共电极相 连,所述第六薄膜晶体管的栅极和源极均与所述第二公共电极相连。

- 7.一种液晶显示器,其特征在于,所述液晶显示器包括如权利要求1-6任一所述的液晶面板驱动电路。

# 液晶面板驱动电路及液晶显示器

#### 技术领域

[0001] 本发明涉及液晶显示器领域,尤其涉及一种液晶面板驱动电路及液晶显示器。

# 背景技术

[0002] 液晶显示器 (Liquid Crystal Display,简称LCD) 是最广泛使用的平板显示器之一,LCD包括设置有场发生电极诸如像素电极和公共电极的一对面板以及设置在两个面板之间的液晶 (Liquid Crystal,简称LC) 层。当电压被施加到场发生电极从而在LC层中产生电场,该电场决定了液晶层中的LC分子的取向,从而调整入射到液晶层的光的偏振,使LCD显示图像。

[0003] 目前业界发展出一种称为高分子安定化垂直配向(Polymer Stabilized Vertical Alignment,简称PSVA)的技术。该技术包括以下步骤:首先,在液晶材料中掺入适当浓度的单体化合物并且震荡均匀。接着,将混合后的液晶材料置于加热器上加温到达等向性状态。当液晶混合物降至室温时,液晶混合物会回到向列型状态。然后,将液晶混合物注入至液晶盒并施与电压。当施加电压使液晶分子排列稳定时,则使用紫外光或加热的方式让单体化合物进行聚合反应以成聚合物层,由此达到稳定配向的目的。

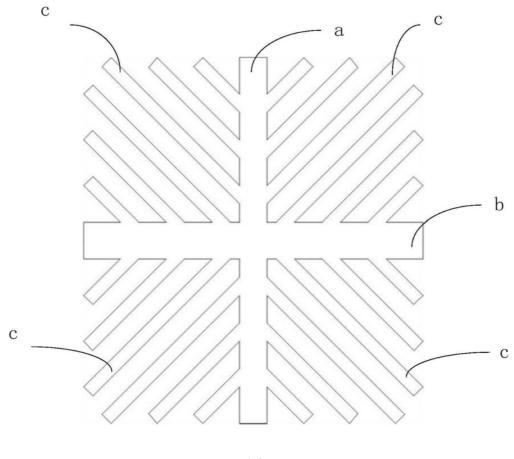

[0004] 为了增加视角,通常使用如图1所示的结构设计,包含条状的竖直主干a和条状的水平主干b,该竖直主干a和水平主干b统称为主干部(main-pixel),其中竖直主干a和水平主干b中心垂直相交,所谓的中心垂直相交,即指竖直主干a和水平主干b相互垂直,该竖直主干a和水平主干b将整个像素电极面积平均分成4个区域(sub-pixel),该4个像素电极区域称为分支部;每个像素电极区域都由与竖直主干a或水平主干b呈±45°,±135°角度的条状分支c平铺组成,也即各条状分支c与竖直主干a和水平主干b位于同一平面上,如此形成图1所示的关于上下和左右分别镜像对称的像素电极结构。

[0005] 这种像素电极结构,因分支部中的条状分支c与水平主干b和竖直主干a的夹角相同,会存在一定的视觉色差或视觉色偏,其面板穿透率下降。

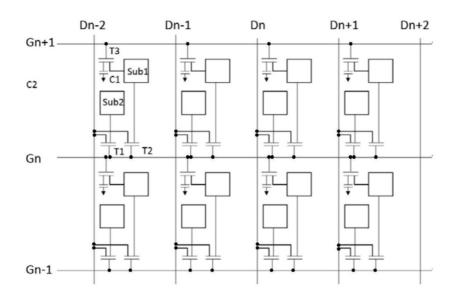

[0006] 为了改善视觉色差或视觉色偏,现有技术将子像素分成两个独立的像素电极,每个像素电极采用上述结构设计,其中一个像素电极又通过一个TFT连接到一个下拉电容上,基板结构如图2所示,其中包括数据线Dn-2至Dn+2,栅极扫描线Gn-1至Gn+1,像素开关T1、T2和T3,像素电极Sub1、Sub2和下拉电容C1,其中像素开关T1和T2分别为像素电极Sub1、Sub2的像素开关,T3为电荷共享开关,下拉电容C1主要作用是将像素电极Sub1的电荷拉低,使得像素电极Sub1、Sub2的电压不同进而消除面板因视角不同而产生的色偏现象。

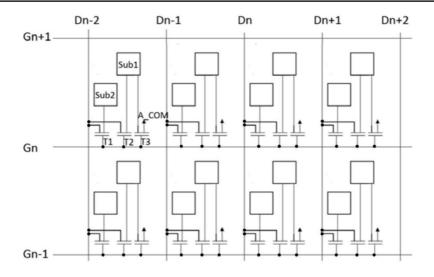

[0007] 由于下拉电容C1需要牺牲一部分开口率,因此为了提升开口率,采有3T结构将下拉电容C1拿掉,直接将T3的漏接连接到公共电极A\_COM上,如图3所示,由于公共电极A\_COM通常采用与栅极同层金属设计,T3的漏极通常采用与数据线同层金属设计,T3的漏极与公共电极通过过孔IT0连接,由于是将两层金属连接导通因此至少需要两个过孔才能连接,而每个像素电极都需要同样的过孔连接,因此在显示区形成的过孔数量较多,容易出现良率问题。

# 发明内容

[0008] 本发明提供一种液晶面板驱动电路及液晶显示器,用以解决现有技术中的驱动电路结构在显示区过孔数量多容易出现良率问题。

[0009] 本发明一方面提供一种液晶面板驱动电路,包括:数据线、栅极扫描线、第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管、第一像素电极、第二像素电极、第一公共电极、第二公共电极和控制信号生成装置;

[0010] 其中,第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管的栅极均与栅极扫描线连接,第一薄膜晶体管、第二薄膜晶体管的源极均与数据线连接,第一薄膜晶体管的漏极与第一像素电极相连,第二薄膜晶体管的漏极、第三薄膜晶体管的源极均与第二像素电极相连,第一像素电极与第二像素电极均与第二公共电极相连,第三薄膜晶体管的漏极与第一公共电极相连:

[0011] 第一公共电极、第二公共电极分别与第四薄膜晶体管的漏极和源极相连,第四薄膜晶体管的栅极与控制信号生成装置连接;

[0012] 控制信号生成装置用于生成控制信号。

[0013] 进一步的,控制信号的周期为帧周期,控制信号在相邻两帧之间的间隔时段内为高电平,在其他时段内为低电平。

[0014] 进一步的,第一公共电极包括平行设置的位于边界的第一边界子公共电极和第二边界子公共电极以及垂直于第一边界子公共电极且将第一边界子公共电极和第二边界子公共电极连接的第一中间子公共电极:

[0015] 第二公共电极包括平行设置的位于边界的第三边界子公共电极和第四边界子公共电极以及垂直于第三边界子公共电极且将第三边界子公共电极和第四边界子公共电极连接的第二中间子公共电极;

[0016] 第一边界子公共电极、第三边界子公共电极分别与第四薄膜晶体管的漏极和源极相连。

[0017] 进一步的,第一公共电极与第二公共电极之间采用悬浮式结构连接。

[0018] 进一步的,第一公共电极与第二公共电极之间采用静电保护回路连接。

[0019] 进一步的,静电保护回路包括第五薄膜晶体管和第六薄膜晶体管,其中,第五薄膜晶体管的源极、漏极分别与第六薄膜晶体管的漏极、源极相连,第五薄膜晶体管的栅极和源极均与第一公共电极相连,第六薄膜晶体管的栅极和源极均与第二公共电极相连。

[0020] 本发明另一方面提供一种液晶显示器,液晶显示器包括上述的液晶面板驱动电路。

[0021] 在本发明中,将第一公共电极和第二公共电极通过第四薄膜晶体管连接。第四薄膜晶体管由控制信号生成装置控制,控制信号生成装置生成控制信号。可通过设置控制信号来控制第一公共电极与第二公共电极上的直流电荷释放,如设置控制信号的周期为帧周期。控制信号在相邻两帧间的间隔时段内为高电平,在其他时段内为低电平,即栅极扫描驱动时段内为低电平。通过在每帧扫描显示完成后,将第一公共电极与第二公共电极连接通过一次,以将第一公共电极上的直流电荷释放到第二公共电极上,进而保证第一公共电极不会因为电荷累积而影响液晶面板显示效果。

# 附图说明

[0022] 在下文中将基于实施例并参考附图来对本发明进行更详细的描述。其中:

[0023] 图1为现有技术中的像素电极结构示意图;

[0024] 图2为现有技术中的一像素电极基板结构示意图;

[0025] 图3为现有技术中的另一像素电极基板结构示意图;

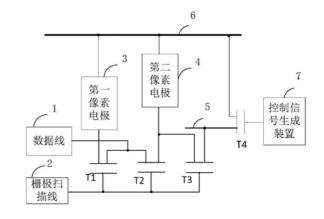

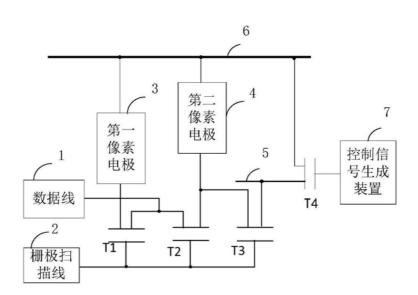

[0026] 图4为本发明实施例提供的液晶面板驱动电路的结构示意图;

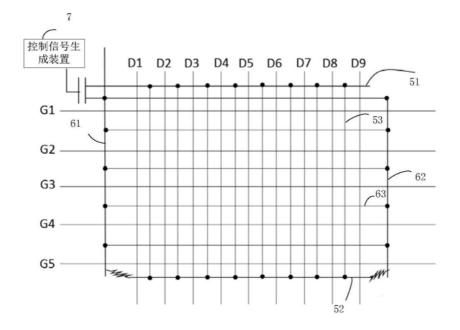

[0027] 图5为本发明实施例提供的第一公共电极和第二公共电极的结构示意图:

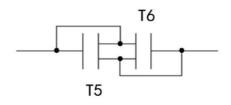

[0028] 图6为本发明实施例提供的静电保护回路结构示意图。

[0029] 在附图中,相同的部件使用相同的附图标记。附图并未按照实际的比例绘制。

# 具体实施方式

[0030] 下面将结合附图对本发明作进一步说明。

[0031] 图4为本发明实施例提供的液晶面板驱动电路的结构示意图;如图4所示,本实施例提供一种液晶面板驱动电路,包括:数据线1、栅极扫描线2、第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、第四薄膜晶体管T4、第一像素电极3、第二像素电极4、第一公共电极5、第二公共电极6和控制信号生成装置7。其中,第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3的栅极均与栅极扫描线2连接。第一薄膜晶体管T1、第二薄膜晶体管T2的源极均与数据线1连接。第一薄膜晶体管T1的漏极与第一像素电极3相连。第二薄膜晶体管T2的漏极、第三薄膜晶体管T3的源极均与第二像素电极4相连。第一像素电极3与第二像素电极4均与第二公共电极6相连。第三薄膜晶体管T3的漏极与第一公共电极5相连。第一公共电极5和连。第一公共电极5和连。第一公共电极5和连。第一次共电极5和连。第一次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和连。第二次共电极5和接触5和连。第二次共电极5和连由数120元,由第二次共电极5和连由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数120元,由数

[0032] 控制信号的周期为帧周期,控制信号在相邻两帧之间的间隔时段内为高电平,在其他时段内为低电平。

[0033] 在本实施例中,将第一公共电极5和第二公共电极6通过第四薄膜晶体管T4连接。 第四薄膜晶体管T4由控制信号生成装置7控制,控制信号生成装置7生成控制信号。控制信 号的周期为帧周期。控制信号在相邻两帧间的间隔时段内为高电平,在其他时段内为低电 平,即栅极扫描驱动时段内为低电平。通过在每帧扫描显示完成后,将第一公共电极5与第 二公共电极6连接通过一次,将第一公共电极5上的直流电荷释放到第二公共电极6上,进而 保证第一公共电极5不会因为电荷累积而影响液晶面板显示效果。

[0034] 具体的,第一公共电极5和第二公共电极6的具体结构如图5所示,G1-G5为栅极扫描线,D1-D9为数据线。第一公共电极5包括平行设置的位于边界的第一边界子公共电极51和第二边界子公共电极52,以及垂直于第一边界子公共电极51且将第一边界子公共电极51和第二边界子公共电极52连接的第一中间子公共电极53。第二公共电极6包括平行设置的位于边界的第三边界子公共电极61和第四边界子公共电极62,以及垂直于第三边界子公共电极61且将第三边界子公共电极61和第四边界子公共电极62连接的第二中间子公共电极63。第一边界子公共电极51、第三边界子公共电极61分别与第四薄膜晶体管T4的漏极和源极相连。上述第一公共电极5与第二公共电极6的具体结构设置,便于位于数据线1与栅极扫描线2之间的第一像素电极3、第二像素电极4与第一公共电极5、第二公共电极6之间的连

接。

[0035] 第一公共电极5与第二公共电极6之间采用悬浮式结构连接。

[0036] 第一公共电极5与第二公共电极6之间采用静电保护回路连接。为了避免静电释放,第一公共电极5与第二公共电极6采用静电保护回路连接。

[0037] 进一步的,静电保护回路如图6所示,静电保护回路包括第五薄膜晶体管T5和第六薄膜晶体管T6,其中,第五薄膜晶体管T5的源极、漏极分别与第六薄膜晶体管T6的漏极、源极相连,第五薄膜晶体管T5的栅极和源极均与第一公共电极5相连,第六薄膜晶体管T6的栅极和源极均与第二公共电极6相连。

[0038] 本发明另一实施例还提供一种液晶显示器,该液晶显示器包括上述的液晶面板驱动电路。

[0039] 虽然已经参考优选实施例对本发明进行了描述,但在不脱离本发明的范围的情况下,可以对其进行各种改进并且可以用等效物替换其中的部件。尤其是,只要不存在结构冲突,各个实施例中所提到的各项技术特征均可以任意方式组合起来。本发明并不局限于文中公开的特定实施例,而是包括落入权利要求的范围内的所有技术方案。

图1

图2

图3

图4

图5

图6