US010163472B2

# (12) United States Patent

## Mirichigni et al.

## (54) APPARATUSES AND METHODS FOR MEMORY OPERATIONS HAVING VARIABLE LATENCIES

- (71) Applicant: MICRON TECHNOLOGY, INC., Boise, ID (US)

- (72) Inventors: Graziano Mirichigni, Vimercate (IT); Corrado Villa, Sovico (IT); Luca Porzio, Casalnuovo di Napoli (IT)

- (73) Assignee: Micron Technology, Inc., Boise, ID (US)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 15/643,361

- (22) Filed: Jul. 6, 2017

## (65) **Prior Publication Data**

US 2017/0309318 A1 Oct. 26, 2017

## **Related U.S. Application Data**

- (63) Continuation of application No. 13/794,471, filed on Mar. 11, 2013, now Pat. No. 9,754,648. (Continued)

- (51) Int. Cl.

| G11C 7/22  | (2006.01) |

|------------|-----------|

| G06F 13/16 | (2006.01) |

| G11C 7/10  | (2006.01) |

- (58) Field of Classification Search CPC ... G06F 13/1689; G11C 5/066; G11C 7/1063; G11C 7/22; G11C 13/0061

See application file for complete search history.

# (10) Patent No.: US 10,163,472 B2

## (45) **Date of Patent: Dec. 25, 2018**

(56) **References Cited**

## U.S. PATENT DOCUMENTS

| 4,833,642 A | 5/1989 Ooi    |

|-------------|---------------|

| 5,287,469 A | 2/1994 Tsuboi |

|             | (Continued)   |

### FOREIGN PATENT DOCUMENTS

| 1497604 A | 5/2004   |

|-----------|----------|

| 1860460 A | 11/2006  |

| (Cor      | ntinued) |

CN CN

## OTHER PUBLICATIONS

U.S. Appl. No. 15/637,961, entitled "Apparatuses and Methods for Providing Data to a Configurable Storage Area", filed Jun. 29, 2017. (Continued)

Primary Examiner — Nathan Sadler (74) Attorney, Agent, or Firm — Dorsey & Whitney LLP

## (57) **ABSTRACT**

Apparatuses and methods for performing memory operations are described. In an example apparatus, a memory is configured to receive a memory instruction and perform a memory operation responsive to the memory instruction. The memory is further configured to provide an acknowledgement indicative of an end of the variable latency period wherein the acknowledgement includes information related to an acceptance of a memory instruction. Data associated with the memory instruction is exchanged with the memory following the acknowledgement. In an example method a read instruction and an address from which read data is to be read is received. A write operation is suspended responsive to the read instruction and an acknowledgement indicative of an end of the variable latency period is provided. Read data for the read instruction is provided and the write operation is continued to be suspended for a hold-off period following completion of the read operation.

## 13 Claims, 8 Drawing Sheets

| DQ3 | DQ2 | DQ1 | Current Read Instruction                                                      | Current Write Instruction                                          |

|-----|-----|-----|-------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 0   | 0   | 1   | Accepted                                                                      |                                                                    |

| 0   | 1   | 1   | Accepted but house keepi<br>Action: Issue house keepi                         | .,                                                                 |

| 1   | 0   | 1   | Accepted but there has be<br>previous operation (e.g. lo<br>Action: Check FSR | <u>م</u>                                                           |

| 1   | 1   | 1   | NA                                                                            | Rejected due to an error<br>(e.g. lock error)<br>Action: Check FSR |

|                              | U.S. | PATENT           | DOCUMENTS               | 20<br>20<br>20 |

|------------------------------|------|------------------|-------------------------|----------------|

| 5,369,616                    | A *  | 11/1994          | Wells                   | 20<br>20<br>20 |

| 5,546,344                    | Δ    | 8/1996           | Fawcett                 | 20             |

| 5,668,972                    |      | 9/1997           | Liu et al.              | 20             |

| 5,778,432                    |      | 7/1998           | Rubin et al.            | 20             |

| 5,822,244                    |      | 10/1998          | Hansen et al.           | 20             |

| 5,892,961                    |      | 4/1999           | Trimberger              | 20             |

| 5,893,149                    |      | 4/1999           | Hagersten et al.        | 20             |

| 5,953,522                    |      | 9/1999           | Fox et al.              | 20             |

| 6,026,034                    |      | 2/2000           | Suzuki et al.           | 20             |

| 6,201,739                    |      | 3/2001           | Brown et al.            | 20             |

| 6,412,045                    | B1   | 6/2002           | DeKoning et al.         | 20             |

| 6,546,462                    | B1   | 4/2003           | Palanca et al.          | 20             |

| 6,552,956                    | B2   | 4/2003           | Shibata                 | 20             |

| 6,629,224                    |      | 9/2003           | Suzuki et al.           | 20             |

| 6,879,540                    |      | 4/2005           | Maruyama et al.         | •              |

| 6,996,016                    |      | 2/2006           | Oh                      | 20             |

| 7,139,673                    | B1 * | 11/2006          | Vashi G06F 11/273       | 20             |

|                              |      |                  | 702/122                 | 20             |

| 7,173,863                    |      | 2/2007           | Conley et al.           | 20             |

| 7,219,251                    |      | 5/2007           | Adkisson                | 20<br>20       |

| 7,363,540                    |      | 4/2008           | Patel et al.            | 20             |

| 7,579,683                    |      | 8/2009           | Falik et al.            | 20             |

| 7,590,013                    |      | 9/2009           | Yu et al.               | 20             |

| 7,624,209                    |      | 11/2009          | Ansari et al.           | 20             |

| 7,643,334                    |      | 1/2010           | Lee et al.<br>Morita    | 20             |

| 7,802,039<br>7,865,658       |      | 9/2010<br>1/2011 | Lasser                  | 20             |

| 8,004,884                    |      | 8/2011           | Franceschini et al.     | 20             |

| 8,030,981                    |      | 10/2011          | Kim                     | 20             |

| 8,195,891                    |      | 6/2012           | Trika                   | 20             |

| 8,539,129                    |      | 9/2013           | Wang                    | 20             |

| 8,582,356                    |      | 11/2013          | Abdulla                 | 20             |

| 8,595,441                    |      | 11/2013          | Nakibly et al.          | 20             |

| 8,902,684                    |      | 12/2014          | Kwean                   | 20             |

| 9,042,156                    |      | 5/2015           | Nakura et al.           | 20             |

| 9,563,565                    | B2   | 2/2017           | Bernardi et al.         | 20             |

| 9,710,192                    | B2   | 7/2017           | Mirichigni et al.       | 20             |

| 9,727,493                    | B2   | 8/2017           | Mirichigni et al.       | 20             |

| 9,734,097                    |      | 8/2017           | Mirichigni et al.       | 20             |

| 9,740,485                    |      | 8/2017           | Mirichigni et al.       | 20             |

| 9,754,648                    |      | 9/2017           | Mirichigni G11C 7/22    | 20             |

| 9,928,171                    |      | 3/2018           | Mirichigni et al.       | 20             |

| 2002/0006074                 | Al*  | 1/2002           | Roohparvar G06F 13/1615 | 20<br>20       |

|                              |      |                  | 365/233.1               | 20             |

| 2002/0168816                 |      | 11/2002          | Shibata                 | 20             |

| 2003/0212865                 |      | 11/2003          | Hicken et al.           | 20             |

| 2004/0098549<br>2005/0068812 |      | 5/2004           | Dorst                   | 20             |

| 2003/0008812                 |      | 3/2005<br>2/2006 | Oh<br>Shimoyama         | 20             |

| 2006/0028883                 |      | 3/2006           | Shimoyama<br>Osborne    |                |

| 2006/0268619                 |      | 11/2006          | ~4                      |                |

| 2007/0005922                 |      | 1/2007           |                         |                |

| 2001/0003722                 | л    | 1/2007           | 711/167                 | CN             |

| 2007/0145151                 | Δ1   | 6/2007           | Nakamura et al.         | CN             |

| 2007/0150688                 |      | 6/2007           | Osborne                 | JP             |

| 200//0100000                 |      | 0,2007           | 711/168                 | 51             |

| 2007/0156991                 | A1   | 7/2007           | Gould et al.            |                |

| 2007/0217253                 |      | 9/2007           | Kim et al.              |                |

| 2008/0082707                 |      | 4/2008           | Gupta et al.            |                |

| 2008/0117682                 |      | 5/2008           | Byeon                   | "Ava           |

|                              |      |                  | 365/185.18              | Arcl           |

| 2008/0155301                 | A1   | 6/2008           | Ahvenainen et al.       | 2012           |

| 2008/0270811                 |      | 10/2008          | Chow et al.             |                |

| 2008/0304351                 | A1   | 12/2008          | Lim et al.              | 1576           |

| 2008/0307165                 |      | 12/2008          | Kazuhiro                | Exte           |

| 2008/0320214                 |      | 12/2008          | Ma et al.               | date           |

| 2009/0024778                 |      | 1/2009           | Morita                  | First          |

| 2009/0044190                 | A1   | 2/2009           | Tringali et al.         | 7012           |

|                              |      |                  |                         |                |

|                              |      |                  |                         |                |

| 2009/0157974 A1                     | 6/2009   | Lasser                        |

|-------------------------------------|----------|-------------------------------|

| 2009/0265514 A1                     | 10/2009  | Biles et al.                  |

| 2010/0013675 A1                     | 1/2010   | Bennett                       |

| 2010/0023675 A1                     | 1/2010   | Chen et al.                   |

| 2010/0124090 A1                     | 5/2010   | Arai                          |

| 2010/0124102 A1                     | 5/2010   | Lee et al.                    |

| 2010/0161880 A1                     | 6/2010   | You                           |

| 2010/0161932 A1                     | 6/2010   | Stern et al.                  |

| 2010/0172179 A1                     | 7/2010   | Gorobets et al.               |

| 2010/0174955 A1                     | 7/2010   | Carnevale et al.              |

| 2010/01/49939 A1<br>2010/0269118 A1 | 10/2010  | Arimilli et al.               |

| 2010/0209118 A1<br>2010/0293343 A1  |          |                               |

|                                     | 11/2010  | Perego<br>Shim at al          |

| 2011/0035536 A1                     | 2/2011   | Shim et al.                   |

| 2011/0047319 A1                     | 2/2011   | Jeon et al.                   |

| 2011/0055453 A1                     | 3/2011   | Bennett                       |

| 2011/0072190 A1                     | 3/2011   | Borracini et al.              |

| 2011/0153900 A1                     | 6/2011   | Zitlaw                        |

| 2011/0170354 A1                     | 7/2011   | DeCaro et al.                 |

| 2011/0197014 A1                     | 8/2011   | Yeh                           |

| 2011/0238866 A1                     | 9/2011   | Zitlaw                        |

| 2011/0289255 A1                     | 11/2011  | Wang et al.                   |

| 2011/0314324 A1                     | 12/2011  | Ozdemir                       |

| 2012/0017053 A1                     | 1/2012   | Yang et al.                   |

| 2012/0054419 A1                     | 3/2012   | Chen et al.                   |

| 2012/0066434 A1*                    | * 3/2012 | Zitlaw G06F 13/28             |

|                                     |          | 711/103                       |

| 2012/0117303 A1                     | 5/2012   | Carannante et al.             |

| 2012/0124317 A1                     | 5/2012   | Mirichigni et al.             |

| 2012/0131263 A1                     | 5/2012   | Yeh                           |

| 2012/0131304 A1                     | 5/2012   | Franceschini et al.           |

| 2012/0173809 A1                     | 7/2012   | Ko et al.                     |

| 2012/0179860 A1                     | 7/2012   | Falanga et al.                |

| 2012/0216085 A1                     | 8/2012   | Weingarten et al.             |

| 2012/0265922 A1                     | 10/2012  | Post et al.                   |

| 2012/0324141 A1                     | 12/2012  | Seong et al.                  |

| 2012/0331207 A1                     | 12/2012  | Lassa et al.                  |

| 2013/0036253 A1                     | 2/2013   | Baltar                        |

| 2013/0058175 A1                     | 3/2013   | Lin et al.                    |

| 2013/0159766 A1                     | 6/2013   | D'Abreu et al.                |

| 2013/0191601 A1                     | 7/2013   | Peterson et al.               |

| 2013/0191704 A1                     | 7/2013   | Eleftheriou et al.            |

| 2013/0262746 A1                     | 10/2013  | Srinivasan                    |

| 2013/0282967 A1                     | 10/2013  | Ramanujan                     |

| 2014/0013028 A1                     | 1/2014   | Rametta                       |

| 2014/0013028 A1<br>2014/0082259 A1  | 3/2014   | Yeh                           |

| 2014/0122814 A1                     | 5/2014   | Mirichigni et al.             |

| 2014/0122814 A1<br>2014/0122822 A1  | 5/2014   | Mirichigni et al.             |

|                                     | 5/2014   |                               |

|                                     | 7/2014   | Cornwell et al.               |

|                                     |          | Kuzmin et al.                 |

| 2014/0281182 A1                     | 9/2014   | Mirichigni et al.             |

| 2015/0052288 A1                     | 2/2015   | Mirichigni et al.             |

| 2015/0052299 A1                     | 2/2015   | Mirichigni et al.             |

| 2015/0095551 A1                     | 4/2015   | Confalonieri et al.           |

| 2015/0100744 A1                     | 4/2015   | Mirichigni<br>Maatalaana atal |

| 2015/0347038 A1                     | 12/2015  | Monteleone et al.             |

| 2017/0083263 A1                     | 3/2017   | Mirichigni et al.             |

| 2017/0147234 A1                     | 5/2017   | Frans et al.                  |

| 2017/0300413 A1                     | 10/2017  | Mirichigni et al.             |

| 2017/0308382 A1                     | 10/2017  | Mirichigni et al.             |

| 2017/0329534 A1                     | 11/2017  | Mirichigni et al.             |

|                                     |          |                               |

## FOREIGN PATENT DOCUMENTS

| 101256539 A  | 9/2008 |

|--------------|--------|

| 101820450 A  | 9/2010 |

| 2005108395 A | 4/2005 |

## OTHER PUBLICATIONS

"Available"—Definition from Wiktionary, the free dictionary— Archived revision by Tuvalkin (talk | contribs) as of 21:49, Jan. 5, 2012. https://en.wiktionary.org/w/index/php?title=available&oldid= 15765189 Downloaded Jan. 13, 2016.

Extended European Search Report for EP Application No. 13849956.1 dated Sep. 2, 2016.

First Rejection Action for Korean Patent Application No. 10-2015-7012530 dated Nov. 20, 2016.

## **Related U.S. Application Data**

(60) Provisional application No. 61/719,321, filed on Oct. 26, 2012.

## (56) **References Cited**

## (56) **References Cited**

## OTHER PUBLICATIONS

International Search Report & Written Opinion for Appl No. PCT/ US2013/066949 dated Feb. 14, 2014.

JEDEC—Low Power Double Data Rate 2 (LPDDR2), Feb. 2010. Notice of Rejection dated May 10, 2016 for JP Application No. 2015-539871.

2015-539871. Handy, J., "The Cache Memory Book Second Edition", Academic Press Prof., Inc., San Diego, CA, Jan. 1993, p. 67. Qureshi, et al., "Enhancing Lifetime and Security of PCM-Based

Qureshi, et al., "Enhancing Lifetime and Security of PCM-Based Main Memory with Start-Gap Wearing Leveling", Microarchitecture, 2009 42nd Annual IEEE/ACM International Symposium, Dec. 12-16, 2009, 14-23.

U.S. Appl. No. 15/857,435, entitled 'Apparatuses and Methods for Providing Data to a Configurable Storage Area', filed Dec. 28, 2017. U.S. Appl. No. 15/667,358, entitled "Apparatuses and Methods for Variable Latency Memory Operations", filed Aug. 2, 2017.

First Office Action dated Jul. 4, 2017 for Chinese Application No. 201380055987.0.

Second Office Action for CN Application No. 201380055987.0, dated Mar. 27.

English Translation of Third Office Action dated Sep. 12, 2018 for Chinese application No. 201380055987.0.

\* cited by examiner

Figure 2B

| Wait State | Asserted - "SHORT" | Asserted - "NORMAL" | Asserted - "LONG" |

|------------|--------------------|---------------------|-------------------|

| ğ          | 0                  | ····                | 0                 |

| ğ          | 0                  | 0                   | <b>~</b>          |

| 4A     |

|--------|

| ure    |

| 0<br>L |

| g | SQ | ğ   | Current Read Instruction Current Write Instruction                                 |

|---|----|-----|------------------------------------------------------------------------------------|

| 0 | 0  | *   | Accepted                                                                           |

| 0 | *  |     | Accepted but house keeping operation suggested                                     |

|   |    |     | Action: Issue house keeping instruction                                            |

|   | 0  | *** | Accepted but there has been an error during a previous operation (e.g. lock error) |

|   |    |     | Action: Check FSR                                                                  |

| * |    | ~~~ | Rejected due to an error<br>(e.g. lock error)                                      |

|   |    |     | AUROIL CIECA LON                                                                   |

Figure 5

Figure 4B

Figure 8

25

## APPARATUSES AND METHODS FOR MEMORY OPERATIONS HAVING VARIABLE LATENCIES

#### CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a continuation of U.S. application Ser. No. 13/794,471 filed Mar. 11, 2013, U.S. Pat. No. 9,754,648, 10issued on Sep. 5, 2017, which claims the filing benefit of U.S. Provisional Patent Application No. 61/719,321, filed Oct. 26, 2012. These applications and patent are incorporated by reference herein in their entirety and for all purposes.

#### TECHNICAL FIELD

Embodiments of the invention relate generally to memories, and include examples of write and read operations 20 having variable latencies which may be used with memories having phase change memory.

## BACKGROUND OF THE INVENTION

Memory devices may be provided in apparatuses such as computers or other electronic devices, including but not limited to portable memory devices, solid state drives, personal digital assistants, music players, cameras, phones, wireless devices, displays, chip sets, set top boxes, gaming 30 systems, vehicles, and appliances. There are many different types of memory including random-access memory (RAM), read only memory (ROM), dynamic random access memory (DRAM), synchronous dynamic random access memory (SDRAM), flash memory, and resistance variable memory, 35 embodiment of the invention. among others.

Apparatuses, such as resistance variable memory devices, may be used as non-volatile memory for a wide range of electronic devices. Resistance variable memory devices may include, for example, phase change memory (PCM) or 40 understanding of embodiments of the invention. However, it resistive memory (RR), among others. A physical layout of a PCM device may resemble that of a DRAM device where the capacitor of the DRAM cell is replaced by a phase change material, e.g., Germanium-Antimony-Telluride (GST) or other chalcogenide materials. That is, an access 45 device such as a diode or metal oxide semiconductor field effect transistor (MOSFET) can be connected in series with the phase change material. Chalcogenide materials can include compounds of sulfides, selenides, or tellurides, among others. GST has been used in rewriteable optical 50 discs, e.g., rewritable compact discs (CD-RW) and rewritable digital versatile discs (DVD-RW).

PCM may be written to change from a first state (e.g., logic "0") to a second state (e.g., logic "1") as with nonvolatile memories. PCM may also be written to change from 55 the second state to the first state. A conventional read operation to PCM is also similar to RAM. As such, PCM may be used in random-access memory. Write operations with PCM, however, are relatively slower than for conventional RAM. That is, time may be needed to manage and 60 complete write operations, such as preparing data to be written to memory, suspending a write operation in case of a read access request, as well as to monitor the progress of a write operation. Read operations may be slower than for conventional RAM and read operations cannot be performed 65 on a memory location that is involved in a concurrent write operation.

As a result of the limitations of using PCM as RAM replacement, operation of PCMs in memory systems is restricted in several ways. For example, write and read operations may not be performed at any time on any memory location. Status registers used for monitoring the progress of write operations may be regularly polled to determine completion of a write operation before starting a new write operation. Additionally, in some applications write operations are necessarily suspended for read operations and resumed upon completion of the read operation.

## BRIEF DESCRIPTION OF IDE DRAWINGS

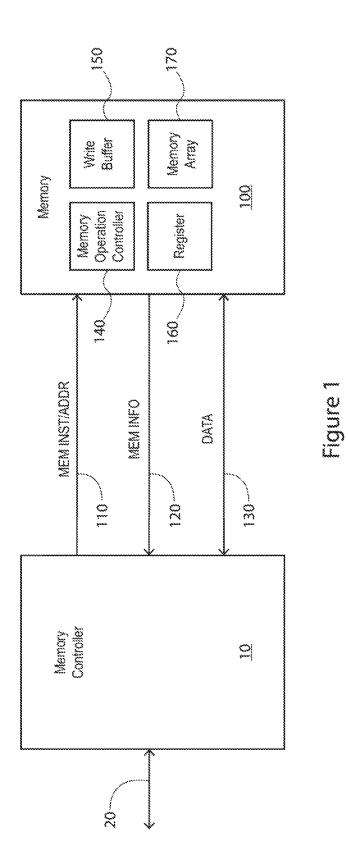

FIG. 1 is a block diagram of an apparatus according to an 15 embodiment of the invention.

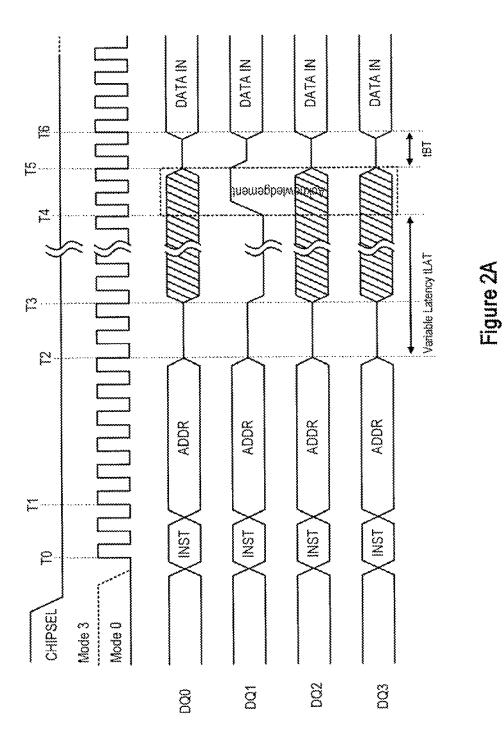

FIG. 2A is a timing diagram of various signals for a write operation according to an embodiment of the invention. FIG. 2B is a timing diagram of various signals for a write operation according to another embodiment of the invention.

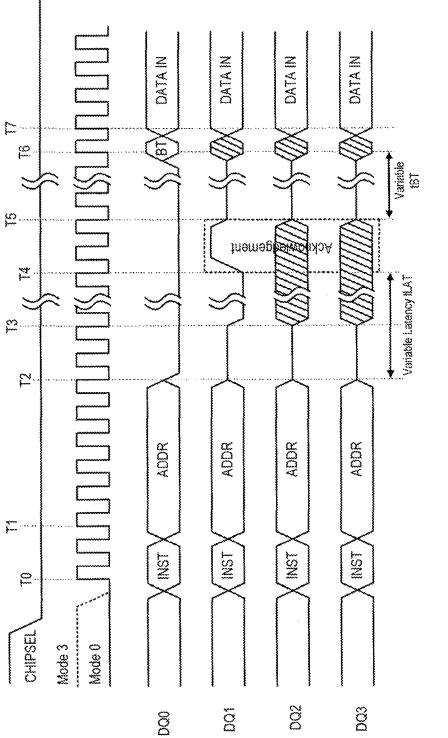

FIG. 3 is a timing diagram of various signals for a read operation according to an embodiment of the invention.

FIG. 4A is a table of wait states according to an embodiment of the invention. FIG. 4B is a timing diagram of various signals for a memory operation according to an embodiment of the invention.

FIG. 5 is a table of information provided by an acknowledgement according to an embodiment of the invention.

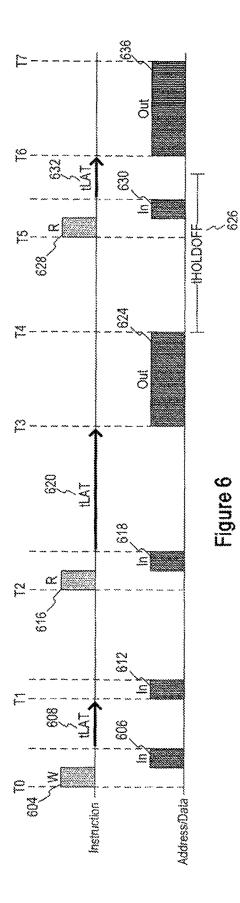

FIG. 6 is a sequence of read and write instructions according to an embodiment of the invention illustrating an example operation.

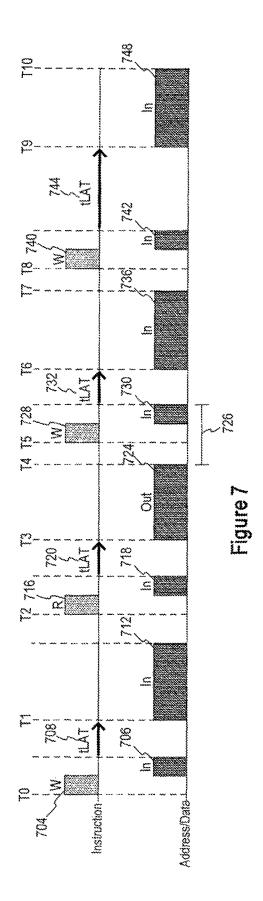

FIG. 7 is a sequence of read and write instructions according to an embodiment of the invention illustrating an example operation.

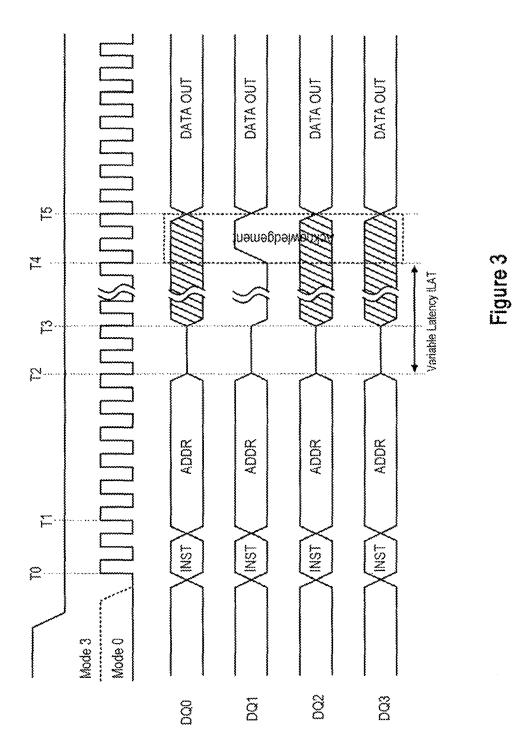

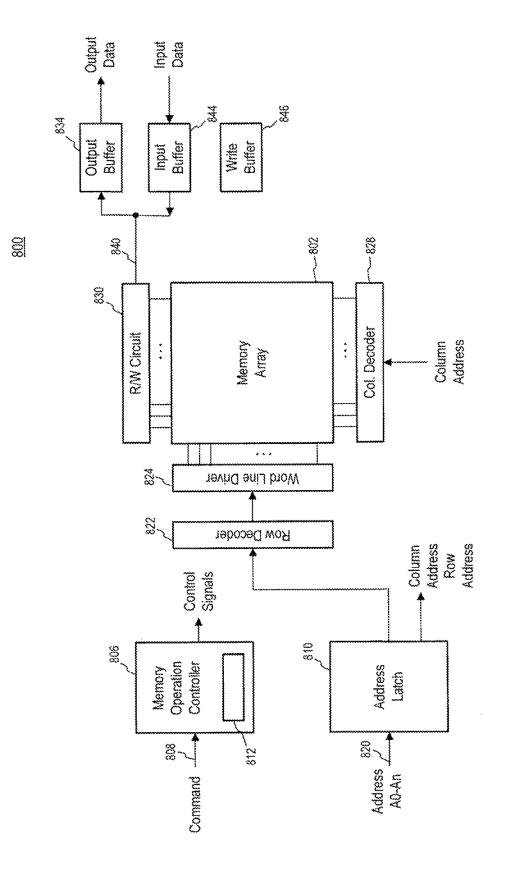

FIG. 8 is a block diagram of an apparatus according to an

#### DETAILED DESCRIPTION

Certain details are set forth below to provide a sufficient will be clear to one skilled in the art that embodiments of the invention may be practiced without these particular details. Moreover, the particular embodiments of the present invention described herein are provided by way of example and should not be used to limit the scope of the invention to these particular embodiments. In other instances, well-known circuits, control signals, timing protocols, and software operations have not been shown in detail in order to avoid unnecessarily obscuring the invention.

FIG. 1 illustrates an apparatus according to an embodiment of the invention. The apparatus may comprise circuitry, one or more semiconductor dice, a packaged semiconductor, a device including such circuitry, die, or package, and/or a system including such a device, and may include a memory controller 10 that is coupled to a memory 100. The memory controller 10 is also coupled to a system bus 20. The memory controller 10 provides the memory 100 memory instructions and memory addresses on a bus 110. The memory 100 includes a memory array 170 having memory cells for storing data, and further includes a memory operation controller 140 configured to receive the memory instructions and control memory operations of the memory 100. A write buffer 150 included in the memory 100 may be used to store write instructions and data and a register 160 may be used to store values related to the configuration and operation of the memory 100, as will be described in more detail below. Although shown as separate elements in FIG. 1, the memory operation controller 140, write buffer 150, and register 160 may be combined in various different arrangements that include one or more of the memory operation controller 140, write buffer 150, and register 160. For example, the memory operation controller 5 140 may include the register 160 in some embodiments.

The memory 100 performs memory operations in response to the memory instructions and addresses. The memory 100 provides various information to the memory controller 10 on a bus 120. As will be described in more 10 detail below, the information provided by the memory 100 may include information related to a memory operation performed for a memory instruction, remaining time of a variable latency period, an acknowledgement indicating an end of the variable latency period, as well as other infor- 15 mation that may be related to the memory 100. Data may be exchanged with the memory 100 over bus 130, for example, read data is provided by the memory 100 to the memory controller 10 for a read instruction, and in another example, write data is provided by the memory controller 10 to the 20 memory 100 for a write instruction.

The information provided by the memory 100 may be used in managing operations between the memory controller 10 and the memory 100. For example, the acknowledgement may be used as a wait signal for the system bus 20, which 25 remains busy until a memory operation ends. Another example is using the acknowledgement to determine whether to keep the system bus 20 busy until a memory operation is completed, or abort an operation (for example, deselecting the memory 100) in order to free the system bus 30 20 (for the same master for other operations or for other masters/peripherals such as frame buffers, etc.) and retry at a later time. Information related to the remaining time of a variable latency period may also be provided to assist in determining whether to keep the system bus 20 busy, or 35 abort an operation and retry at a later time.

In operation, memory instructions and memory addresses are received by the memory 100, for example, from the memory controller 10 and a memory operation is performed. A variable latency period tLAT follows receipt of the 40 memory instruction and memory address. An end of the latency period is indicated by an acknowledgement ACKNOWLEDGE provided by the memory 100, after which data may be exchanged with the memory (e.g., providing data to the memory controller 10 following the 45 ACKNOWLEDGE, receiving data from the memory controller 10 following the ACKNOWLEDGE, or both providing/receiving data following the ACKNOWLEDGE). During the tLAT period, the memory 100 may manage memory operations. For example, during the tLAT period the 50 invention are received by a memory to perform a write memory may prepare itself for the memory operation (e.g., such as preparing memory circuits for performing the memory operation), complete a memory operation in progress, suspending an operation in progress to begin performing the memory operation, or manage other memory opera- 55 tions. The memory 100 may also complete an operation in progress during the tLAT period, for example, before performing the memory operation for the memory instruction received. As such, the tLAT period may vary over a range of time, from relatively short to relatively long, with the 60 ACKNOWLEDGE indicating the end of the tLAT period. The ACKNOWLEDGE may also be used to inform a host if the tLAT period is ongoing or has ended. In some embodiments, the memory 100 may provide information related to the time for the tLAT period during the tLAT period. In an 65 example, the memory 100 provides information related to the time for the tLAT period, and may further provide

updated information related to the time for the tLAT period. The updated information may reflect how much longer the tLAT period may be.

In some embodiments, a memory operation controller in a memory (e.g., memory operation controller 140 of memory 100) may decode memory instructions and provide internal signals to manage resulting memory operations to allow data to be written to and allow data to be read from a memory array of the memory (e.g., memory array 170 of memory 100) without the same timing limitations of conventional phase change memory (PCM). For example, in some embodiments, data may be read from a location in the memory array even if the location is currently involved with a write operation. In some embodiments, suspension and resumption of internal memory operations (e.g., write and read operations) may be less constrained in comparison to convention PCMs, and thus provide greater operational flexibility of the memory. For example, a write operation may not necessarily be suspended in favor of a read operation, and suspended write operations may be resumed according to more flexible timing conditions.

In summary, during the tLAT period the memory is being prepared for the operation or to complete an operation. For example, during this time, the memory determines whether a previous operation is in progress; if not then a current operation may be performed immediately after a relatively short tLAT period. If a previous operation is already in progress, the memory will decide how to manage the current and previous operations, it may be that the previous operation is suspended to allow the current operation to be performed. In this case, the tLAT period may be relatively short. If, however, the memory decides to complete the previous operation before performing the current operation the LAT period may be relatively long.

Embodiments of the invention may be utilized with various memory interfaces. For example, some embodiments may be utilized with serial memory interfaces. Some embodiments of the invention may be utilized with memory mapped interfaces, including LPDDR2-N, NOR, as well as other memory interfaces as well.

Examples of memory instructions are a write instruction and a read instruction. A write instruction causes a write operation to be performed by the memory 100, with write data received by the memory being written to memory locations corresponding to a memory address. A read instruction causes a read operation to be performed by the memory 100, with read data provided by the memory from memory locations corresponding to a memory address.

Write instructions according to an embodiment of the operation. Generally, in such embodiments, the write instruction and memory address are received by the memory, and a variable latency period follows the receipt of the instruction and the address. An end of the latency period is indicated by an acknowledgement ACKNOWLEDGE provided by the memory, after which write data for the write instruction may be received by the memory. As will be described in more detail below, in some embodiments a maximum time for the tLAT period may be defined, for example, by programming a register that includes a value for a maximum tLAT. FIG. 2A illustrates the timing of a write operation according to an embodiment of the invention.

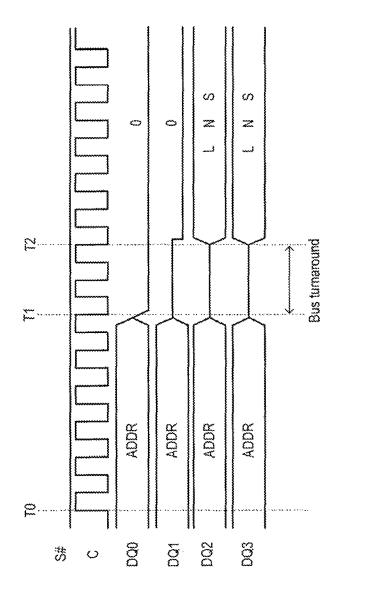

Prior to time T0 a memory select signal S/ (active low) and mode signals MODE become active, causing the memory to become active. Between times T0 and T1 a write instruction is received by the memory on input/outputs DQ0-DQ3 of the memory. Between times T1 and T2 an address corresponding to the location for the write instruction is received. Following time T2 is a latency period tLAT. The tLAT period may be variable, with an end of the tLAT period indicated by an acknowledgement ACKNOWL-EDGE provided by the memory. Between times T2 and T3 5 is a bus turnaround period to allow DQ0-DQ3 to change direction of the exchange of information, if desired. During the bus turnaround time DQ0-DQ3 may be in a highimpedance "Hi-Z" state, as shown in FIG. 2A. As previously discussed, the memory provides an ACKNOWLEDGE to 10 indicate an end of the tLAT period. The memory may use one or more of DQ0-DQ3 to provide the ACKNOWL-EDGE. In the embodiment of FIG. 2A, the memory uses DQ1 for the ACKNOWLEDGE. Following time T3 the memory provides a logic "0" on DQ1, and DQ0, DQ2, and 15 DQ3 may be any logic state (i.e., "don't care").

At time T4 the memory provides an ACKNOWLEDGE The ACKNOWLEDGE is represented in FIG. 2A as the memory changing the logic state of DQ1 from logic "0" to logic "1." The ACKNOWLEDGE may be provided by the 20 memory for a period of time (e.g., a number of clock cycles), after which write data may be received by the memory. In FIG. 2A, for example, the ACKNOWLEDGE is provided by the memory on DQ1 over two clock cycles from time T4 to time T5. Although illustrated in FIG. 2A as a change in logic 25 state from "0" to "1" on DQ1, the ACKNOWLEDGE may be provided on another DQ, or more than one DQ. The ACKNOWLEDGE may be represented by other than changing from "0" to "1," for example, "1" to "0," Hi-Z to a logic state, or other representations. Additionally, the 30 ACKNOWLEDGE may be provided by the memory for shorter or longer than that specifically illustrated in FIG. 2A. Following the ACKNOWLEDGE between times T4 and T5 may be a bus turnaround time tBT. The tBT may be provided in order to avoid bus contention between the memory 35 providing the ACKNOWLEDGE and receiving the write data. Write data is received by the memory at time T6 following the tBT.

The tBT may be a specific number of clock cycles tCK measured relative to the ACKNOWLEDGE. In the example 40 the particular embodiments described with reference to of FIG. 2A, the tBT is shown as 1 tCK, measured from a first rising edge after the ACKNOWLEDGE. In some embodiments, the tBT may be programmable, for example, by programming a register that includes a tBT setting. The tBT may be programmable as various configurable times or a 45 variable time. When the tBT is programmed as a configurable time, one of several choices of clock cycles may be selected, such as a tBT of 1 tCK, 2 tCK, or 3 tCK as measured relative to the ACKNOWLEDGE. In an example where the tBT is programmed as a configurable time of 1 50 tCK, FIG. 2A also illustrates the resulting tBT. For a configurable tBT of 2 tCK the time between T5 and T6 would be one clock cycle longer and for a configurable tBT of 3 tCK the time between T5 and T6 would be two clock cycles longer.

A variable tBT provides for the write data to be received by the memory at a variable time relative to the ACKNOWLEDGE. FIG. 2B illustrates a timing for a write operation having a variable tBT according to an embodiment of the invention. As with FIG. 2A, a memory select signal 60 S/ and mode signals MODE are active prior to time T0. At time T0 the write instruction is received by the memory and the address is received at time T1. Following T2 is the tLAT period, which as previously discussed, may be variable and have an end indicated by the ACKNOWLEDGE. A bus 65 turnaround period is shown between times T2 and T3 for DQ1-DQ3 as a Hi-Z slate. The memory receives a logic "0"

6

on DQ0. DQ0 is used to indicate an end of a variable tBT, as will be described in more detail below. At time T3 the memory provides a logic "0" on DQ1, which is used to provide the ACKNOWLEDGE; indicating an end of the tLAT period, and DQ2 and DQ3 are don't care. The ACKNOWLEDGE is provided by the memory between times T4 and T5 on DQ1, as represented by changing the logic state from "0" to "1." A variable tBT follows the acknowledge.

In FIG. 2B, the input/output DQ0 may be used by the memory to receive a tBT end indicator (BT) which indicates the end of the variable tBT. In the embodiment of FIG. 2B, the tBT end indicator is received by the memory on DQ0 at time T6, and precedes the write data received by the memory at T7. DQ1-DQ3 are don't care. The tBT end indicator notifies the memory of the end of the variable tBT and that write data will follow. In this manner, the length of tBT can be determined by the host (with an end indicated by BT), rather than having a configurable tBT (e.g., 1 tCK, 2 tCK, 3 tCK, etc.) and without using a separate dedicated signal line for the tBT end indicator. In other embodiments the tBT end indicator may be provided on a different DQ or on more than one DQ. Additionally, the tBT end indicator may be longer or shorter than that shown in FIG. 2B.

As previously described, during the tLAT period the memory may manage memory operations. For example, during the tLAT period the memory may prepare itself for the write operation, such as preparing memory circuits for performing the write operation, suspending an operation in progress to begin performing the write operation, or manage other memory operations. The memory may also complete an operation in progress during the tLAT period, for example, before performing the write operation for the write instruction. The tLAT period may vary over a range of time. In some embodiments, the time for a tLAT period may be characterized over a range from relatively short to relatively long, with the ACKNOWLEDGE indicating the end of the tLAT period.

It will be appreciated that the invention is not limited to FIGS. 2A and 2B. For example, in an embodiment of the invention the write instruction is 8-bits (1 byte) and the address is 24-bits (3 bytes) received over a plurality of clock cycles. However, instructions and addresses of different lengths may be used as well, and received over a number of clock cycles different than that illustrated in FIGS. 2A and 2B. Additionally, the order in which an instruction and address are received by the memory may be different without departing from the scope of the invention. FIGS. 2A and 2B illustrate embodiments where input/output DQ0-DQ3 are shared for instructions, addresses, and data. In some embodiments, however, memory instructions may be received on a dedicated input, and addresses and data share another input/output. In some embodiments, memory instructions and addresses may be received on a shared input, and data received/provided on dedicated input/outputs. The ACKNOWLEDGE is shown in FIGS. 2A and 2B as being provided over two clock cycles, but in other embodiments the ACKNOWLEDGE may be provided over a different number of clock cycles. The time at which the write data may be received may follow a specific number of clock cycles after the ACKNOWLEDGE, or in some embodiments, the write data may be received at a time after the ACKNOWLEDGE, for example, as previously discussed, after a configurable or variable bus turnaround time.

A buffer may be included in a memory (e.g., memory 100 of FIG. 1) in some embodiments and used to store write data and corresponding write instructions until a sufficient number of write instructions/data are accumulated, at which time write operations for the buffered write instructions are performed. As a result, several write instructions may have relatively short tLAT periods (those buffered) followed by a 5 write instruction having a tLAT period that is longer than the relatively short tLAT period. Write operations for the buffered write instructions are performed during the longer tLAT period. The buffer may be accessible so that buffered write data is accessible for a read operation if the buffered write 10 data is to be read, such as to keep cached data coherency.

Read instructions according to an embodiment of the invention are received by a memory to perform a read operation. Generally, in such embodiments, the read instruction and memory address are received by the memory, and 15 a variable latency period follows the receipt of the instruction and the address. An end of the latency period is indicated by an acknowledgement ACKNOWLEDGE provided by the memory, after which read data for the read instruction is provided by the memory. As will be described 20 in more detail below, in some embodiments a maximum time for the tLAT period may be defined, for example, by programming a register that includes a value for a maximum tLAT. FIG. **3** illustrates the timing of a read operation according to an embodiment of the invention.

Prior to time T0 a memory select signal S/ (active low) and mode signals MODE are active, causing the memory to become active. Between times T0 and T1 a read instruction is received by the memory. Between times T1 and T2 an address corresponding to the location for the read instruction 30 is received. Following time T2 is a latency period tLAT. The tLAT period may be variable, with an end of the tLAT period indicated by an acknowledgement ACKNOWLEDGE provided by the memory, after which read data may be provided by the memory. A bus turnaround period is shown between 35 times T2 and T3 for DQ0-DQ3 as a Hi-Z state. At time T3 the memory provides a logic "0" on DQ1, which is used to provide the ACKNOWLEDGE indicating an end of the tLAT period, and DQ0, DQ2, and DQ3 are don't care. The ACKNOWLEDGE is provided by the memory between 40 times T4 and T5 on DQ1, as represented by changing the logic state from "0" to "1." Read data is provided by the memory at time T5.

As previously described, during the tLAT period the memory may manage memory operations. For example, 45 during the tLAT period the memory may prepare itself for the read operation, such as preparing memory circuits for performing the read operation, suspending an operation in progress to begin performing the read operation, or manage other memory operations. The memory may also complete 50 an operation in progress during the tLAT period, for example, before performing the read operation for the read instruction. The tLAT period may vary over a range of time, with the ACKNOWLEDGE; indicating the end of the tLAT period. 55

It will be appreciated that the invention is not limited to the particular embodiment described with reference to FIG. **3**. For example, in an embodiment of the invention the read instruction is 8-bits (1 byte) and the address is 24-bits (3 bytes) received over a plurality of clock; cycles. However, 60 instructions and addresses of different lengths may be used as well, and received over a number of clock cycles different than that illustrated in FIG. **3**. Additionally, the order in which an instruction and address are received by the memory may be different without departing from the scope 65 of the invention. FIG. **3** illustrates an embodiment where input/outputs DQ0-DQ3 are shared for instructions,

addresses, and data. In some embodiments, however, memory instructions may be received on a dedicated input, and addresses and data share another input/output. In some embodiments, memory instructions and addresses may be received on a shared input, and data received/provided on dedicated input/outputs. The ACKNOWLEDGE is shown in FIG. **3** as being provided over two clock cycles, but in other embodiments the ACKNOWLEDGE may be provided over a different number of clock cycles.

As previously described, during a tLAT period a memory may manage memory operations. The time for the tLAT period may be affected by the manner in which the memory manages memory operations. As previously described, the ACKNOWLEDGE is provided by the memory to indicate an end of the tLAT period after which data is to be exchanged (e.g., write data provided to the memory for a write operation and read data provided by the memory for a read operation). In the embodiments illustrated with reference to FIGS. 2A, 2B, and 3, the end of the tLAT period coincides with the beginning of the ACKNOWLEDGE. In other embodiments, the end of a tLAT period may include the ACKNOWLEDGE and end coincident with ACKNOWLEDGE or extend several clock cycles after the ACKNOWLEDGE, but end before data is exchanged with 25 the memory.

In some embodiments, the ACKNOWLEDGE may be used to inform a host that the tLAT period is ongoing or has ended. For example, as previously described the memory may provide a signal on a DQ having a logic state that indicates whether the tLAT period is ongoing or ended, transitioning from one logic slate to another at the time the tLAT period ends (e.g., as part of the ACKNOWLEDGE indicating an end of the tLAT period). While the tLAT period is ongoing, signals on other DQs may be don't care, and/or at least one DQ is used to receive a signal from a host.

In some embodiments, information may be provided by the memory during the tLAT period, for example, related to the operation for a memory instruction. As previously discussed, the memory may provide information related to the time for the tLAT period, and may further provide updated information during the tLAT period related to the remaining time of the tLAT period. Example information that may be provided includes a wait state which is related to how much longer tLAT may be. The information may be represented by one or more signals, with the combination of the logic states of the signals indicating the information conveyed during tLAT. For example, a first signal (e.g., a first DQ signal) may have a logic slate that indicates whether the tLAT period is ongoing or has ended, transitioning from one logic state to the other at the time the tLAT period ends (e.g., as part of ACKNOWLEDGE indicating an end of the tLAT period). While the tLAT period is ongoing, a second and third signal (e.g., second and third DQ signals) may have a combination of logic states that indicates a wait state.

FIG. 4A illustrates a table of wait states provided by the memory on the input/outputs DQ2 and DQ3. Each of the wait states is indicated by a respective logic combination provided on DQ2-DQ3. For example, a "normal" wait state is indicated by a "10" combination provided on DQ2-DQ3, and "short" and "long" wait states are indicated by providing "00" and "01" combinations on DQ2-DQ3, respectively. In some embodiments, as previously discussed, the memory may use DQ1 to provide an ACKNOWLEDGE indicate whether the tLAT period is ongoing (e.g., DQ1="0") or ending (e.g., DQ1="1"). The logic "0" may be provided by the memory on DQ1 during the tLAT period, with the memory providing a logic "1" on DQ1 to indicate an end of

the tLAT period. The change of logic states on DQ1 may be included as part of the ACKNOWLEDGE indicating an end of the tLAT period.

The wait states of short, normal, and long are relative, and in some embodiments may be based on a measure of time. 5 For example, an increment of time may be used as a measure for normal and long wait states. An example increment of time may be 20 us. That is, when a remaining time for the tLAT period is greater than the time increment (e.g., greater than 20 us) a "01" combination is provided by the memory 10 on DQ2 and DQ3 to indicate that the wait state is long. When the remaining time for the tLAT period is less than the time increment (e.g., less than 20 us) a "10" combination is provided by the memory on DQ2 and DQ3 to indicate that the wait state is normal. The memory may provide a "00" 15 combination on DQ2 and DQ3 indicating a short wait state when the remaining time for the tLAT period is less than another time increment shorter than the time increment used as a measure for the normal and long wait states. For example, a short wait state may be provided when the 20 remaining time for the tLAT period is less than 1 us. Time increments other than those previously described may be used without departing from the scope of the invention. Moreover, additional or alternative wait states or other information may be conveyed during a tLAT period as well 25 as using other combinations of logic states to indicate the wait states or other information.

FIG. 4B illustrates the timing for a portion of a memory operation with the memory providing information related to the remaining time of the tLAT period according to an 30 embodiment of the invention. By time T0, the memory has received a memory instruction (not shown in FIG. 43) for a memory operation and the address associated with the memory instruction is received between times T0 and T1. Between times T1 and T2 is a bus turnaround time to avoid 35 bus contention between the memory receiving the address and providing information related to the remaining time of the tLAT period. The bus turnaround time following the address is shown in FIG. 4B as two tCKs long, however, the bus turnaround time may be other times as well, whether 40 configurable or variable in length. In the embodiment of FIG. 4B, information related to the remaining time of the tLAT period is provided by the memory using DQ2 and DQ3. The combination of logic states provided by the memory on DQ2 and DQ3 indicates whether, for example, 45 the remaining time for the tLAT period is "long" "normal," or "short." The information provided by the memory may update over the tLAT period, with for logic states of DQ2 and DQ3 updated by for memory accordingly.

The logic states of DQ0 and DQ1 may be used during the 50 tLAT period for other than providing information related to the remaining time for the tLAT period. DQ0 and DQ1 are shown in FIG. 4B as being driven to "0" logic states. However, DQ0 and DQ1 may be other logic states without departing from the scope of the invention. As previously 55 time when a memory instruction is received, the memory discussed, DO0 may be used by the memory during the tLAT period to receive a tBT end indicator BT (for variable tBT) and DQ1 may be used by the memory to provide an ACKNOWLEDGE by changing the logic state from logic "0" to logic "1" (not shown). In other embodiments, the 60 memory does not provide any information on either or both DQ0 and DQ1, and/or provides logic states other than those specifically illustrated in FIG. 4B.

As previously discussed, the ACKNOWLEDGE indicates an end of a tLAT period, and in some embodiments of the 65 invention may also include information. For example, the ACKNOWLEDGE may also include information related to

whether the memory instruction is accepted or rejected. If accepted, a memory operation for the accepted memory instruction will be performed. Information related to acceptance of a memory instruction may include further qualification, such as the instruction has been accepted but there is an error during an operation of a previous instruction, or the operation has been accepted but there is a warning due to the need of a house keeping operation (e.g., wear leveling, refresh, etc.). In contrast, if rejected, a memory operation for the rejected memory instruction will not be performed. A memory instruction may be rejected, for example, due to an error condition in the memory, or for other reasons that prevent the memory from performing the memory operation.

The ACKNOWLEDGE may be represented by one or more signals, with the combination of logic states of the signals indicative of the information conveyed by the ACKNOWLEDGE. For example, a first signal (e.g., a first data signal) may change logic states to represent an end of the tLAT period, and the combination of logic states of a second and third signal (e.g., second and third data signals) at the time the first signal has changed logic states may indicate additional information, such as acceptance or rejection of the memory instruction.

FIG. 5 illustrates a table of information provided by an ACKNOWLEDGE according to an embodiment of the invention. DQ1, DQ2, and DQ3 are used in the embodiment, and the combination of logic states provided by the memory on DQ1-DQ3 indicate the ACKNOWLEDGE information. As shown, the ACKNOWLEDGE may indicate the end of the tLAT period, and may further include information related to whether the instruction was accepted, accepted with qualification, or rejected due to an error.

Additional or alternative information may be included in the ACKNOWLEDGE as well as using other combinations of logic states to indicate the information without departing from the scope of the invention.

The time for the variable latency period may be based on various factors. For example, the time for the variable latency period may be based at least in part on a current memory operation. The time for the variable latency period may be further based at least in part on the memory instruction received. Where the memory is idle when a memory instruction is received, for example, the memory may begin performing the memory operation as soon as possible, resulting in a tLAT period that is relatively short. For example, receipt of a read instruction or a write instruction when the memory is idle results in the memory preparing to perform the memory operation and beginning the operation in a relatively short time, thus the tLAT period may be relatively short and the read data may be provided by the memory or the write data provided to the memory relatively soon after the read or write instruction, respectively, is received.

In contrast, if a memory operation is in progress at the may complete the operation in progress before beginning performance of the memory operation for the received memory instruction. As a result, the tLAT period may be longer than a relatively short tLAT period, and may be a relatively long tLAT period due to the time needed to complete the operation in progress. For example, a write operation may be in progress when a read instruction is received by the memory. The memory may complete the write operation before beginning the operation for the read instruction, thus, the tLAT period for the read instruction may be longer than a relatively short tLAT period. Where more than one write instruction is being performed (e.g.,

performing buffered write instructions) the tLAT period for the read instruction may be relatively long.

In some embodiments, the memory may suspend an operation in progress to begin performing the operation for a received memory instruction. The memory operation for 5 the received memory instruction may be completed without having to wait for the operation that is suspended to be completed. As a result, the tLAT period for the received memory instruction is shorter than a relatively long tLAT period, and may be a relatively short tLAT period. When the 10 operation for the received instruction is completed, the memory may resume performing the suspended operation. For example, an operation for a write instruction may be in progress when a read instruction is received by the memory. The memory may suspend the operation for the write 15 instruction and begin performing the operation for the received read instruction. By not waiting for the operation for the write instruction to complete before beginning operation for the read instruction, the tLAT for the read instruction will be a relatively long tLAT period.

The memory may continue suspending the operation that was in progress if additional memory instructions are received during performance of the received memory instruction, or in some embodiments, if additional memory instructions are received within a hold-off period tHOLD- 25 OFF. In some embodiments the tHOLDOFF period is measured from completion of the additional memory instruction. In some embodiments, the tHOLDOFF period is measured from, for example, receipt of the additional memory instructions, or a different event related to the additional memory 30 instruction. Receipt of a memory instruction within the tHOLDOFF period restarts the tHOLDOFF period at the completion of the memory operation so that other memory instructions received in the new tHOLDOFF period will continue to cause suspension of the suspended operation. 35 The tHOLDOFF period allows for additional memory instructions received within the tHOLDOFF period to be performed without prematurely resuming a suspended operation, as a result the additional memory instructions may have a tLAT period that may be a relatively short tLAT 40 period. The tHOLDOFF period may also be used to delay starting background operations within the memory, such as wear leveling, consolidating fragmented blocks of data in memory, performing device evaluation and adjustment, as well as other background operations. That is, background 45 operations are not started until after the tHOLDOFF period ends in order to avoid a relatively long tLAT period for any additional memory instructions.

For example, as in the previous example, a write operation in progress was suspended to begin performing the 50 operation for a read instruction. A tHOLDOFF period (i.e., first tHOLDOFF period) may begin following the completion of the read instruction, during which an additional read instruction is received. As a result, the suspended write operation remains suspended and the read operation for the 55 additional read instruction begins. Due to the continued suspension of the write operation, the tLAT period for the additional read instruction may be a relatively short tLAT period. Upon completion of the additional read instruction, another tHOLDOFF period (i.e., second tHOLDOFF period) 60 begins, during which receipt of other additional read instructions will cause the write operation to be further suspended. The further additional read instructions may also have a tLAT period that may be a relatively short tLAT period. However, in the event no other read instructions are received 65 during the second tHOLDOFF period the suspended write operation may be resumed and completed.

In some embodiments, receipt of a specific type or types of memory instructions will result in a suspended memory operation to be resumed. For example, assuming again a write operation is suspended upon receipt of read instruction. The read operation for the instruction begins and is completed, at which time a tHOLDOFF period begins. As previously described, receipt of a read instruction during the tHOLDOFF period may cause the suspended write operation to remain suspended. However, if a write instruction is received during the tHOLDOFF period, this type of memory instruction may cause the suspended write operation to resume immediately to be completed. The write operation for the new write instruction may be performed following completion of the previously suspended write operation, or in some embodiments, queued to be later performed, for example, due to receipt of a read instruction after the new write instruction was received but before completion of the resumed write operation.

Although previously described in the context of a sus-20 pended memory operation, the tHOLDOFF period may be available even when there are not any memory operations suspended. That is, a tHOLDOFF period may follow the completion of a memory operation, for example, a memory operation for a read instruction, during which time no other memory operations are initiated. A memory operation for an instruction received during the tHOLDOFF period may consequently have a relatively short tLAT given that no other memory operations are in progress. In some embodiments, receipt of write instructions during the tHOLDOFF period may force the tHOLDOFF period to immediately expire and not be restarted. The tHOLDOFF period may be used with suspended operations or when no other memory operations are pending to allow a memory to remain ready to perform a memory operation for an instruction received during the tHOLDOFF period, resulting in relatively short tLAT periods.

A maximum time for tLAT and the time for a tHOLDOFF period may be programmable in some embodiments of the invention. For example, a register may be included in a memory (e.g., register 160 of FIG. 1) which is used to store values indicative of a maximum tLAT, and store values indicative of the time for the tHOLDOFF period. The maximum time for tLAT may set the maximum tLAT time for a memory operation, and may be used by a memory, for example, to determine whether to suspend a current memory operation in progress, or to allow a current memory operation to complete before turning to the memory operation. Separate maximum tLATs may be set for read and write operations in some embodiments. The maximum tLAT value and/or the tHOLDOFF period may in some embodiments be programmable by a host and may be based on, for example, facilitating efficient execution of microcode. The value programmed for tLAT may identify one of several predefined maximum values in some embodiments. In some embodiments, a value may be stored in the register indicative of a maximum number of operations that may be performed during a tLAT period, thus establishing a maximum tLAT period.

FIG. **6** illustrates a sequence of read and write instructions according to an embodiment to illustrate an example operation of a memory.

At time T0 a write instruction 604 and address 606 are received by the memory. Assuming that the memory was idle prior to time T0, the write operation for the write instruction 604 will have a relatively short tLAT 608. As previously described, a buffer may be used to store instructions, address and write data to provide a relatively short

tLAT period, for example. As a result, write data 612 for the write instruction 604 can be received at time T1, which is relatively soon after the write instruction 604 was received at time T0. Following receipt of the write data 612 at time T1, internal memory operations are performed for the write 5 operation. As illustrated in the example of FIG. 6, at time T2 a read instruction 616 and address 618 are received by the memory. The read operation for the read instruction 616 will have a relatively long tLAT 620 assuming that the write operation for the write instruction 604 of time T0 is to be completed or suspended before performing the read operation. Following the tLAT 620, at time T3 read data 624 for the read instruction 616 is made available by the memory. A tHOLDOFF period 626 begins at time T4 following provision of the read data 624. Time T4 may represent the 15 completion of the read operation for the read instruction 616. At time T5 a read instruction 628 and address 630 are received by for memory. As illustrated in FIG. 6, the read instruction 628 is received within for tHOLDOFF period 626. Thus, the read operation for the read instruction 628 can 20 begin immediately, and will have a relatively short tLAT 632. Read data 636 is provided by for memory at time T6 following the tLAT 632, and through to time T7, which represents for end of the read operation for the read instruction 628. 25

By comparison, the tLAT 632 is shorter than the tLAT 620. As previously described, for tLAT 620 may have resulted from waiting for the write operation for the write instruction 604 to complete or be suspended before performing the read operation for the read instruction 616. In 30 contrast, the tLAT 632 of the read operation for the read instruction 628 is shorter because for memory was waiting the tHOLDOFF period 626 before turning to other memory operations. As such, the memory was able to begin performing for read operation for the read instruction 628 when it 35 was received within for tHOLDOFF period 626 at time T5. Although not shown in FIG. 6, read operations for subsequently received read operations will also have relatively short tLATs if the read instruction is received within a tHOLDOFF period. 40

As illustrated by FIG. 6, the write operation for the write instruction initially received is completed or suspended before initiating the read operation for the read instruction 616 received at time T2. As a result, the tLAT for the read instruction 616 will be relatively long to allow the write 45 operation to complete or be suspended. However, the read operation for the read instruction 628 received at time T5 has a tLAT that is relatively short due to receiving the mad instruction within the tHOLDOFF period 626. As previously discussed, memory operations for instructions received dur- 50 ing the tHOLDOFF period 626 may have relatively short tLAT because the memory remains idle for the tHOLDOFF period, after which it may resume a suspended memory operation. Thus, the operation for an instruction received during the tHOLDOFF period 626 can be performed without 55 waiting for another memory operation to complete or be suspended and consequently have a relatively short tLAT.

FIG. 7 illustrates a sequence of read and write instructions according to an embodiment to illustrate an example operation of a memory.

60

At time T0 a write instruction 704 and address 706 are received by the memory. Assuming that the memory was idle prior to time T0, the write operation for the write instruction 704 will have a relatively short tLAT 708. As a result, write data 712 for the write instruction 704 can be 65 received at time T1, which is relatively soon after the write instruction 704 was received at time T0. Following receipt

of the write data **712** at time **T1**, internal memory operations occur to perform the write operation. The internal memory operations may include writing the write data **712** to a write data buffer in which write data may be stored before being written to memory. As previously discussed, use of a write data buffer may allow for a write operation to be completed relatively quickly because writing write data to the write data buffer may take less time than writing write data to memory. At a later time, however, write data accumulated in the write data buffer will be written to memory, which may take a relatively long time, and may result in a memory operation for a subsequently received instruction having a relatively long tLAT. In the example of FIG. **7**, however, the tLAT **708** is illustrated as relatively short.

As illustrated in the example of FIG. 7, at time T2 a read instruction 716 and address 718 are received by the memory. The read operation for the read instruction 716 is illustrated in FIG. 7 with a relatively short tLAT 720. The tLAT 720 may be relatively short given that the write operation for the write instruction 704 may be completed by time T2. Following the tLAT 720, from time T3 to T4 read data 724 for the read instruction 716 is made available by the memory. A tHOLDOFF period 726 begins at time T4 after the completion of the read operation. As previously discussed, during the tHOLDOFF period the memory does not initiate or resume any memory operations.

At time T5 a write instruction 728 and address 730 are received by the memory. With the read operation for the read instruction 716 completing by time T4 and the (HOLDOFF period 726 still elapsing, the write operation for the write instruction 728 may begin immediately by forcing the tHOLDOFF period to expire and in a relatively short tLAT 732. Alter which write data 736 may be received by the memory at time T6. At time T7, receipt of the write data 736 is completed. In the example of FIG. 7, although the tLAT 732 is relatively short, the write operation for the write instruction 728 may begin internal memory operations to write the write data accumulated in a write data buffer to a memory array. For example, in some embodiments, a write instruction received during a tHOLDOFF period may cause a write operation to begin, or in the event a previous memory operation has been suspended, cause the suspended operation to resume. As a result, a write operation for a subsequently received memory instruction may have a tLAT longer than the relatively short tLAT 732. For example, at time T8 a write instruction 740 and address 742 are received by the memory. Although receipt of the write data for the write instruction 728 is completed by receipt of the write instruction 740 at time T8, the write operation for the write instruction 740 is illustrated in FIG. 7 as having a tLAT 744 that is longer than the relatively short tLAT 732. The longer tLAT 744 may result from the internal memory operations being performed for previous write instructions (e.g., write instructions 704 and 728). That is, as previously discussed the write operations for the write instructions 704 and 728 may have relatively short tLATs 708 and 732, but the write operation for the write instruction 728 may include writing buffered write data to a memory array. The write operation for the write instruction 728 may not complete by time T8 when the write instruction 740 is received by the memory causing a longer tLAT 744. Following the longer tLAT 744, write data for the write instruction 740 is received by the memory between times T9 and T10.

As illustrated by FIG. **7**, the write operation for the write instruction **704** initially received has a short tLAT **708**. The write operation is also completed in a relatively short time, for example, through the use of a write data buffer, before

20

receiving the read instruction 716 received at time T2. As a result, the tLAT 720 for the read instruction 716 will be relatively short. The write operation for the write instruction 728 received at time T5 also has a relatively short tLAT 732. A relatively short tLAT may be due to the fact that there are 5 no suspended operations that need to be resumed and completed, for example, the relatively short tLAT 732 may be due to at least in part on the use of a write data buffer to store the write data rather than being stored to the memory array, which typically takes more time than writing to the 10 write data buffer. For example, the short tLAT 732 may be due to the write instruction 728 being received within the tHOLDOFF period 726 following the completion of the read operation at time T4 for the read instruction 716. In contrast, the write operation for the write instruction 740 received at 15 time T8 has a tLAT 744 that is longer than tLAT 732. As previously discussed, the longer tLAT 744 may be due to, for example, performing operations for writing write data stored in the write data buffer to the memory array before receiving the write data 748 between times T9 and T10.

FIG. 8 is a schematic illustration of a portion of an apparatus (e.g. a memory device, such as a memory module, or a memory system, such as a solid-state drive) 800 according to an embodiment of the present invention. The apparatus 800 includes an array 802 of memory cells, which 25 may be, for example, resistance variable memory cells, including phase change memory cells, resistance variable random access memory cells, or other types of memory cells. The apparatus 800 also includes a memory operation controller 806 according to an embodiment of the invention, 30 the second data signal comprises acceptance or rejection of that may receive memory instructions through an instruction bus 808 and generate corresponding control signals within the apparatus 800 to cause various memory operations to be carried out. For example, the memory operation controller 806 may generate control signals for performing read opera- 35 tions and write operations according to embodiments of the invention. The memory operation controller 806 includes a register 812 that may be used to store values related to the configuration and operation of the apparatus 800. In some embodiments, the register 812 may store values indicative of 40 a maximum tLAT, and store values indicative of the time of the tHOLDOFF period, among other values. The register 812 is not limited to being included in the memory operation controller 806, and may be separate from the memory operation controller and/or included in another element of 45 apparatus 800.

Row and column address signals may be provided through an address bus 820 to an address latch 810 of the apparatus 800. In some embodiments, the address bus 820 may be combined with the instruction bus 808, and in some 50 embodiments the address bus 820 may be combined with a data bus. The address latch 810 may then output a separate column address and a separate row address. The row and column addresses may be provided by the address latch 810 to a row address decoder 822 and a column address decoder 55 828, respectively. The column address decoder 828 may select bit lines extending through the array 802 corresponding to respective column addresses. The row address decoder 822 may be connected to word line driver 824 that may activate respective rows of memory cells in the array 60 802 corresponding to received row addresses. The selected data line (e.g., a bit line or bit lines) corresponding to a received column address may be coupled to read/write circuitry 830 to provide read data to a data output buffer 834 via an input-output data bus 840. Write data may be pro- 65 vided to the memory array 802 through a data input buffer 844 and the memory array read/write circuitry 830. A buffer

846 of the apparatus 800 may be used to store write data and/or write instructions to be performed, a previously discussed.

From the foregoing it will be appreciated that, although specific embodiments of the invention have been described herein for purposes of illustration, various modifications may be made without deviating from the spirit and scope of the invention. Accordingly, the invention is not limited except as by the appended claims.

What is claimed is:

- 1. An apparatus, comprising:

- a memory controller configured to provide memory instructions; and

- a memory coupled to the memory controller, the memory configured to receive a memory instruction and addresses corresponding to a location for the memory instruction, the memory configured to provide an acknowledgement on a first data signal indicative of an end of a variable latency period that starts after receipt of the addresses and to provide information on a second data signal, the memory further configured to receive data associated by the memory instruction from the memory controller following the acknowledgment;

- wherein the memory instruction comprises a write instruction and wherein the data received comprises write data provided by the memory controller to the memory.

2. The apparatus of claim 1 wherein the information on the memory instruction.

3. The apparatus of claim 1 wherein the variable latency period includes a bus turn around time following receipt of the addresses.

4. The apparatus of claim 1 wherein the memory is configured to provide the first data signal having a first logic level during the variable latency period.

5. The apparatus of claim 4 wherein the memory is configured to provide the acknowledgement represented by the first data signal changing from the first logic level to a second logic level.

6. The apparatus of claim 1 wherein the memory is configured to provide the second data signal having a logic level indicative of the information.

- 7. An apparatus, comprising:

- a memory controller configured to provide memory instructions:

- a data bus coupled to the memory controller; and

- a memory coupled to the memory controller through the data bus and configured to receive a memory instruction therefrom and to perform a memory operation responsive thereto, the memory further configured to provide a first signal to the memory controller on the data bus that changes from a first to a second logic level to indicate an end of a variable latency period and to further provide a second signal to the memory controller on the data bus concurrently with the first signal having the second logic level, wherein the second signal represents additional information, the memory further configured to exchange data on the data bus associated with the memory instruction with the memory controller following the first signal changing from the second logic level;

- wherein the memory instruction comprises a write instruction and wherein the data exchanged comprises write data provided by the memory controller to the memory.

**8**. The apparatus of claim **7** wherein the memory is further configured to receive addresses corresponding to a location for the memory instruction.

**9**. The apparatus of claim **7** wherein the data bus is configured to be in a high-impedance state following receipt 5 of the addresses.

**10**. The apparatus of claim **7** wherein the data bus is configured to be in a high-impedance state following the first signal changing from the second logic level and before data is exchanged.

**11**. The apparatus of claim **7** wherein the memory instruction comprises a read instruction and wherein the data exchanged comprises read data provided by the memory to the memory controller.