# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 108490654 B (45) 授权公告日 2021.01.22

- (21) 申请号 201810291440.5

- (22) 申请日 2018.04.03

- (65) 同一申请的已公布的文献号 申请公布号 CN 108490654 A

- (43) 申请公布日 2018.09.04

- (73) 专利权人 京东方科技集团股份有限公司 地址 100015 北京市朝阳区酒仙桥路10号 专利权人 福州京东方光电科技有限公司

- (72) 发明人 王家敏 于洋

- (74) 专利代理机构 北京润泽恒知识产权代理有限公司 11319

代理人 莎日娜

(51) Int.CI.

GO2F 1/13 (2006.01)

### (56) 对比文件

- CN 101833910 A,2010.09.15

- CN 101334541 A,2008.12.31

- CN 101435968 A,2009.05.20

- CN 101930128 A, 2010.12.29

- CN 203350556 U,2013.12.18

- US 2005057273 A1,2005.03.17

审查员 于子江

权利要求书1页 说明书6页 附图3页

#### (54) 发明名称

一种阵列基板、阵列基板母板及显示装置

#### (57) 摘要

本申请提供了一种阵列基板、阵列基板母板及显示装置,其中阵列基板母板包括由切割线分成的第一测试区域和第二测试区域,第二测试区域内设置有多个测试单元,测试单元包括测试短路棒以及连接在测试短路棒上的多条信号线,测试短路棒用于向信号线输入检测信号;各测试单元的测试短路棒之间通过串接线依次串接,串接线跨越所述切割线;通过相同的测试短路棒进行切割工艺之前的Array测试和切割工艺之后的Cell测试,因此,测试短路棒本身的不良在Array测试阶段可以被检测出来,避免流入下一道工序,避免在Cell测试阶段出现因测试短路棒自身不良导致的点灯画面异常,进而提高Cell测试阶段的产能和良品率。

1.一种阵列基板母板,其特征在于,包括由切割线分成的第一测试区域和第二测试区域,所述第二测试区域内设置有多个测试单元,所述测试单元包括测试短路棒以及连接在所述测试短路棒上的多条信号线,所述测试短路棒用于向所述信号线输入检测信号;

各所述测试单元的所述测试短路棒之间通过串接线依次串接,所述串接线跨越所述切割线,分布在所述第一测试区域和所述第二测试区域;

所述第一测试区域设置有多个第一信号输入端子,串接的所述测试短路棒中,首位的测试短路棒和末位的测试短路棒通过引线连接至对应的所述第一信号输入端子,所述引线跨越所述切割线:

所述第一测试区域设置有多个第二信号输入端子,各所述测试短路棒还分别与对应的 所述第二信号输入端子连接;

所述测试短路棒包括第一短路棒和第二短路棒,所述信号线包括交替排布的第一信号 线和第二信号线,

所述第一短路棒与所述第一信号线连接,所述第二短路棒与所述第二信号线连接。

- 2.根据权利要求1所述的阵列基板母板,其特征在于,所述第一短路棒与所述第一信号 线同层设置并连接;所述第二短路棒与所述第二信号线非同层设置并连接。

- 3.根据权利要求2所述的阵列基板母板,其特征在于,所述第一短路棒、所述第一信号 线以及所述第二信号线与所述阵列基板母板的栅极层同步形成,所述第二短路棒与所述阵 列基板母板的数据线同步形成。

- 4.根据权利要求2所述的阵列基板母板,其特征在于,所述第二短路棒与所述第二信号 线通过金属层架桥连接。

- 5.根据权利要求4所述的阵列基板母板,其特征在于,所述金属层通过第一过孔与所述 第二短路棒连接,通过第二过孔与所述第二信号线连接。

- 6.根据权利要求5所述的阵列基板母板,其特征在于,所述第一过孔和所述第二过孔在第一方向上的尺寸大于或等于18μm,且小于或等于20μm;在与所述第一方向垂直的方向上的尺寸大于或等于28μm,且小于或等于32μm。

- 7.一种阵列基板,其特征在于,所述阵列基板为由权利要求1至6任一项所述的阵列基板母板沿所述切割线切割得到的包含所述第二测试区域的基板。

- 8.一种显示装置,其特征在于,包括权利要求7所述的阵列基板。

# 一种阵列基板、阵列基板母板及显示装置

## 技术领域

[0001] 本发明涉及显示技术领域,特别是涉及一种阵列基板、阵列基板母板及显示装置。

## 背景技术

[0002] 目前,在TFT-LCD检测领域,广泛采用短路棒(Shorting Bar)点灯的方式。由于其治具简单且点灯稳定,可有效降低运营成本及维护成本。然而,由于Cell测试短路棒与Array测试短路棒是分立设置的,在Array测试阶段无法检测出Cell测试短路棒上的过孔ITO开路不良等,导致具有Cell测试短路棒不良的阵列基板进入下一工序,进而在Cell测试阶段出现点灯画面异常(如X-Line不良等),严重影响Cell测试阶段的产能和良品率。

# 发明内容

[0003] 本发明提供一种阵列基板、阵列基板母板及显示装置,以提高Cell测试阶段的产能和良品率。

[0004] 为了解决上述问题,本发明公开了一种阵列基板母板,包括由切割线分成的第一测试区域和第二测试区域,所述第二测试区域内设置有多个测试单元,所述测试单元包括测试短路棒以及连接在所述测试短路棒上的多条信号线,所述测试短路棒用于向所述信号线输入检测信号;

[0005] 各所述测试单元的所述测试短路棒之间通过串接线依次串接,所述串接线跨越所述切割线,分布在所述第一测试区域和所述第二测试区域。

[0006] 可选地,所述第一测试区域设置有多个第一信号输入端子,串接的所述测试短路棒中,首位的测试短路棒和末位的测试短路棒通过引线连接至对应的所述第一信号输入端子,所述引线跨越所述切割线;

[0007] 所述第一测试区域设置有多个第二信号输入端子,各所述测试短路棒还分别与对应的所述第二信号输入端子连接。

[0008] 可选地,所述测试短路棒包括第一短路棒和第二短路棒,所述信号线包括交替排布的第一信号线和第二信号线,

[0009] 所述第一短路棒与所述第一信号线连接,所述第二短路棒与所述第二信号线连接。

[0010] 可选地,所述第一短路棒与所述第一信号线同层设置并连接;所述第二短路棒与所述第二信号线非同层设置并连接。

[0011] 可选地,所述第一短路棒、所述第一信号线以及所述第二信号线与所述阵列基板母板的栅极层同步形成,所述第二短路棒与所述阵列基板母板的数据线同步形成。

[0012] 可选地,所述第二短路棒与所述第二信号线通过金属层架桥连接。

[0013] 可选地,所述金属层通过第一过孔与所述第二短路棒连接,通过第二过孔与所述第二信号线连接。

[0014] 可选地,所述第一过孔和所述第二过孔在第一方向上的尺寸大于或等于18µm,且

小于或等于20μm;在与所述第一方向垂直的方向上的尺寸大于或等于28μm,且小于或等于32μm。

[0015] 为了解决上述问题,本发明还公开了一种阵列基板,所述阵列基板为由上述任一项所述的阵列基板母板沿所述切割线切割得到的包含所述第二测试区域的基板。

[0016] 为了解决上述问题,本发明还公开了一种显示装置,包括上述的阵列基板。

[0017] 与现有技术相比,本发明包括以下优点:

[0018] 本申请提供了一种阵列基板、阵列基板母板及显示装置,其中阵列基板母板包括由切割线分成的第一测试区域和第二测试区域,第二测试区域内设置有多个测试单元,测试单元包括测试短路棒以及连接在测试短路棒上的多条信号线,测试短路棒用于向信号线输入检测信号;各测试单元的测试短路棒之间通过串接线依次串接,串接线跨越所述切割线;通过相同的测试短路棒进行切割工艺之前的Array测试和切割工艺之后的Cell测试,因此,测试短路棒本身的不良在Array测试阶段可以被检测出来,避免流入下一道工序,避免在Cell测试阶段出现因测试短路棒自身不良导致的点灯画面异常,进而提高Cell测试阶段的产能和良品率。

## 附图说明

[0019] 为了更清楚地说明本发明实施例的技术方案,下面将对本发明实施例的描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

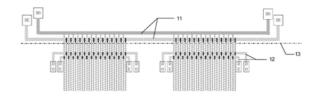

[0020] 图1示出了现有技术中一种阵列基板母板的结构示意图;

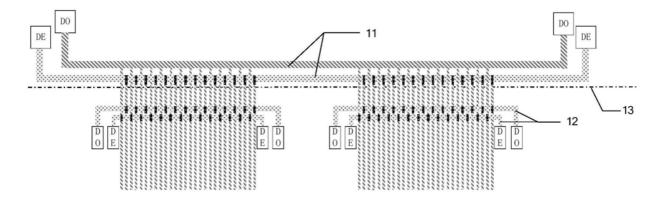

[0021] 图2示出了本申请一实施例提供的一种阵列基板母板的结构框图;

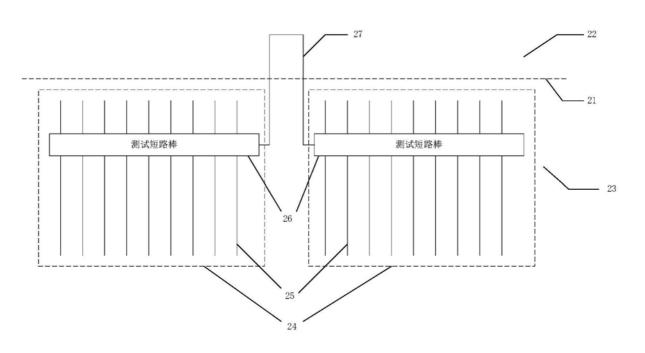

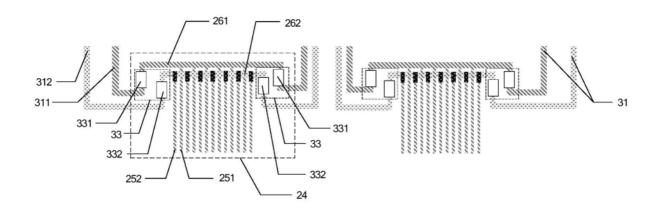

[0022] 图3示出了本申请一实施例提供的一种阵列基板母板的平面结构示意图:

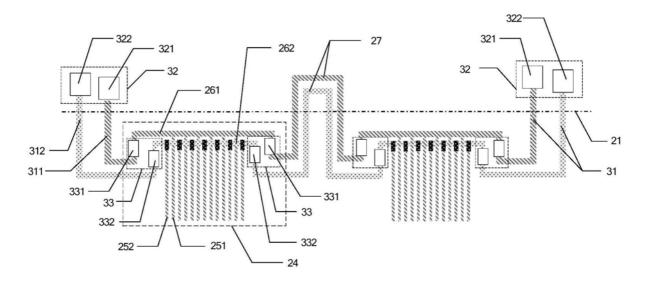

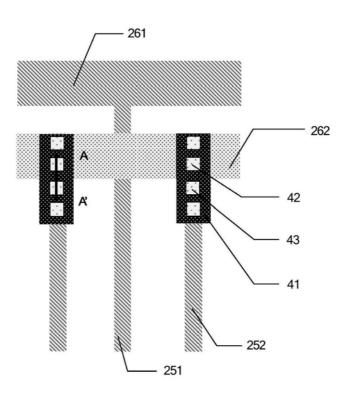

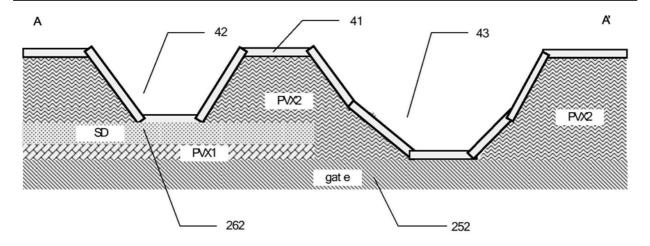

[0023] 图4示出了本申请一实施例提供的第二短路棒与第二信号线通过金属层架桥连接的平面结构示意图;

[0024] 图5示出了本申请一实施例提供的第二短路棒与第二信号线通过金属层架桥连接的剖面结构示意图:

[0025] 图6示出了本申请一实施例提供的一种阵列基板母板切割后的平面结构示意图;

[0026] 附图标记说明:

[0027] 11-现有技术中Array测试短路棒;12-现有技术中Cell测试短路棒;13-现有技术中切割线;21-切割线;22-第一测试区域;23-第二测试区域;24-测试单元;25-信号线;26-测试短路棒;27-串接线;261-第一短路棒;262-第二短路棒;251-第一信号线;252-第二信号线;31-引线;311-第一引线;312-第二引线;32-第一信号输入端子;321-第一偶数信号输入端子;322-第一奇数信号输入端子;33-第二信号输入端子;331-第二偶数信号输入端子;332-第二奇数信号输入端子;41-金属层;42-第一过孔;43-第二过孔。

#### 具体实施方式

[0028] 为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

[0029] 在显示面板的制作过程中,参照图1,一般会在Array测试阶段采用Array测试短路棒11对Array基板进行电学性能不良检测。Cell测试是对盒后的检测,一般采用Cell测试短路棒12对显示面板进行显示画面检查,检测电学性能不良和目视性不良。现有的Array测试短路棒11和Cell测试短路棒12分别位于由切割线13分成的两个区域,由于Array测试短路棒11和Cell测试短路棒12是分立设置的,所以在Array测试阶段无法检测出Cell测试短路棒12自身的不良,导致在Cell测试阶段出现点灯画面异常。

[0030] 为了解决这一问题,本申请一实施例提供了一种阵列基板母板,参照图2,该阵列基板母板可以包括:由切割线21分成的第一测试区域22和第二测试区域23,第二测试区域23内设置有多个测试单元24,测试单元24包括测试短路棒26以及连接在测试短路棒26上的多条信号线25,测试短路棒26用于向信号线25输入检测信号;各测试单元24的测试短路棒26之间通过串接线27依次串接,串接线27跨越切割线21,分布在第一测试区域22和第二测试区域23。

[0031] 需要注意的是,本实施例所述的阵列基板母板,是以沿切割线21切割之后得到一块阵列基板为例进行说明的。多个测试单元24可以对应于阵列基板上的多个bonding绑定区,具体测试单元的设置数量和大小可以根据输入信号的强弱以及阵列基板自身尺寸等因素确定,本申请对此不作具体限定。

[0032] 在实际应用中,测试短路棒26与信号线25的连接方式可以有多种,例如,测试短路棒26可以是与信号线25交叉设置并与所有的信号线25相连接的一根短路棒;也可以是包括与信号线25交叉设置,并与偶数列的信号线25连接的第一短路棒以及与奇数列的信号线25连接的第二短路棒等,对于后一种实现方式可以参考后续实施例的描述。

[0033] 在对上述的阵列基板母板进行切割之前,可以通过Array测试信号输入端子向测试短路棒26输入Array测试信号,再由测试短路棒26输出给信号线25,对Array基板进行测试。Array测试信号输入端子可以位于第一测试区域22,也可以位于第二测试区域23。而且,整个阵列基板母板可以共用一个Array测试信号输入端子,也可以为了防止信号衰减而设置多个Array测试信号输入端子与测试短路棒26连接,例如每个测试单元24的测试短路棒26各自连接至一个Array测试信号输入端子,或者仅将串接的测试短路棒26中首位和末位的测试短路棒26连接Array测试信号输入端子。

[0034] 在对上述的阵列基板母板沿切割线21进行切割工艺之后,可以采用相同的测试短路棒26进行Cell测试。Cell测试阶段通过Cell测试信号输入端子向测试短路棒26输入Cell测试信号,再由测试短路棒26输出给信号线25。Cell测试信号输入端子可以位于第二测试区域23。由于串接线27在切割工艺中被切断,多个测试单元24之间不再串联在一起,因此,每个测试单元24至少连接至一个Cell测试信号输入端子。

[0035] 本实施例中,通过相同的测试短路棒,可以进行切割工艺之前的Array测试和切割工艺之后的Cell测试,因此,测试短路棒本身的不良在Array测试阶段可以检测出来,避免流入下一道工序,避免在Cell测试阶段出现因短路棒不良导致的点灯画面异常,进而提高Cell测试阶段的产能和良品率。

[0036] 本实施例的一种实现方式中,参照图3,测试短路棒26可以包括第一短路棒261和第二短路棒262,信号线25可以包括交替排布的第一信号线251和第二信号线252,第一短路棒261与第一信号线251连接,第二短路棒262与第二信号线252连接。通过设置第一短路棒

261和第二短路棒262,不但在Array测试阶段可以检测出测试短路棒自身的不良,而且还可以在Array测试阶段进行DDS (data and data short)等不良检测。

[0037] 其中,第一信号线251可以连接阵列基板母板上偶数列的数据线,第二信号线252 可以连接阵列基板母板上奇数列的数据线;或者第一信号线251连接阵列基板母板上奇数列的数据线,第二信号线252连接阵列基板母板上偶数列的数据线。图3是以第一种情况为例示出的。

[0038] 具体的,第一短路棒261可以与第一信号线251同层设置并连接;第二短路棒262与第二信号线252非同层设置并连接。本实现方式中,第一短路棒261与第一信号线251同层设置并连接,不需要过孔转接信号,也就不会发生过孔ITO 0pen不良。需要注意的是,第一短路棒261与第一信号线251,以及第二短路棒262与第二信号线252的连接并不仅限于这一种连接方式,例如还可以第一短路棒261与第一信号线251非同层设置并连接,第二短路棒262与第二信号线252同层设置并连接;或者第一短路棒261与第一信号线251以及第二短路棒262与第二信号线252均是非同层设置并连接,具体的连接方式可以根据实际的结构以及工艺过程确定,本申请对此不作具体限定。

[0039] 当第一短路棒261与第一信号线251同层设置并连接;第二短路棒262与第二信号线252非同层设置并连接时,可以通过以下的具体结构实现:第一短路棒261、第一信号线251以及第二信号线252与阵列基板母板的栅极层同步形成,第二短路棒262与阵列基板母板的数据线同步形成。这种情况下,第二短路棒262与第二信号线252可以通过金属层架桥连接,还可以通过设置在第二短路棒262与第二信号线252之间绝缘层(例如数据线层和栅极层之间的栅极绝缘层)上的过孔实现连接。

[0040] 参照图4和图5,分别示出了第二短路棒与第二信号线通过金属层架桥连接的平面结构示意图和沿AA'的剖面结构示意图。上述的金属层架桥连接是指金属层41通过第一过孔42与第二短路棒262连接,同时金属层41通过第二过孔43与第二信号线252连接。具体的,金属层41可以是ITO(氧化铟锡)等。

[0041] 现有技术中Ce11测试短路棒12上的过孔尺寸大约为(8-10µm)\*(10-12µm),在生产过程中容易发生0pen不良。这是由于过孔处的金属层(如IT0)是围绕孔洞的一个圈,在工艺过程中如切割研磨时受到外力容易发生断裂,当过孔尺寸较小时,发生完全0pen的可能性较大。为了避免第一过孔42和第二过孔43处发生0pen不良,第一过孔42和第二过孔43的尺寸可以为(18-20µm)\*(28-32µm),如图4所示,形状可以制作成长方形,即在第一方向上的尺寸大于或等于18µm,且小于或等于20µm;在与第一方向垂直的方向上的尺寸大于或等于28µm,且小于或等于32µm。由于金属层断裂一处对信号传输影响不大,因此过孔越大,完全0pen的可能性越小。其中,第一方向例如可以是与阵列基板母板中的栅线平行的方向,与第一方向垂直的方向可以是与数据线平行的方向。

[0042] 本实施例中,由于第一短路棒261与第一信号线251是同层设置,所以不会发生过孔0pen不良,将第二短路棒262与第二信号线252连接的第一过孔42和第二过孔43采用大尺寸过孔设计可以降低发生过孔完全0pen的几率。也就是本实施例将测试短路棒不良导致的点灯画面异常假不良发生概率降低到最小。而且,即便在Array工艺中过孔处发生0pen不良,也可以在Array测试阶段检测出,可以对该类不良阵列基板母板进行焊接修复后,再投入下一道工序。

[0043] 参照图3,还示出了本实施例中Array测试信号输入端子和Cell测试信号输入端子的一种实现方式。第一测试区域22设置有多个第一信号输入端子32,串接的测试短路棒26中,首位的测试短路棒和/或末位的测试短路棒通过引线31连接至对应的第一信号输入端子32,引线31跨越切割线21;第一测试区域22设置有多个第二信号输入端子33,各测试短路棒26还分别与对应的第二信号输入端子33连接。

[0044] 其中,第一信号输入端子32可以包括与第一短路棒261连接的第一偶数信号输入端子321和与第二短路棒262连接的第一奇数信号输入端子322。第二信号输入端子33可以包括与第一短路棒261连接的第二偶数信号输入端子331和与第二短路棒262连接的第二奇数信号输入端子332。为了减小信号衰减对测试结果的影响,可以将首位的测试短路棒和末位的测试短路棒均通过引线31连接至第一信号输入端子32,如图3所示。并且,可以在每个测试单元24中测试短路棒26的左右两侧分别设置第二信号输入端子33,以减小信号衰减的影响。

[0045] 引线31可以包括连接第一偶数信号输入端子321和第一短路棒261的第一引线311,以及连接第一奇数信号输入端子322和第二短路棒262的第二引线312。

[0046] 第二信号输入端子33可以设置在第二测试区域23中的测试短路棒26上或者与测试短路棒26连接的串接线27或引线31上。第二信号输入端子33只要位于第二测试区域23并与测试短路棒26连接即可,本申请对其具体位置不作限定。

[0047] 其中,首位的测试短路棒是指串接的测试短路棒中的第一个测试短路棒,在图3中可以是最左侧测试单元中的测试短路棒;末位的测试短路棒是指串接的测试短路棒中最后一个测试短路棒,在图3中可以是最右侧测试单元中的测试短路棒。需要注意的是,这里的首位和末位是相对来说的,可以根据具体情况进行定义。

[0048] 下面将结合上述的阵列基板母板,以第二信号输入端子设置在第二测试区域中的测试短路棒上为例,分别对Array测试阶段和Cell测试阶段的信号传输过程进行说明。

[0049] 在Array测试阶段,对第一信号线251进行测试的信号传递如下:Array测试信号探针→第一偶数信号输入端子321→第一引线311→第一短路棒261→第二偶数信号输入端子331→第一短路棒261→第一信号线251;对第二信号线252进行测试的信号传递如下:Array测试信号探针→第一奇数信号输入端子322→第二引线312→第二短路棒262→第二奇数信号输入端子332→第二短路棒262→第一过孔42→第二过孔43→第二信号线252。

[0050] 在Ce11测试阶段,参照图6,位于切割线21外侧的第一测试区域22被切除,而且各测试单元24的测试短路棒26之间不再串联。对第一信号线251进行测试的信号传递如下:Ce11测试信号探针→第二偶数信号输入端子331→第一短路棒261→第一信号线251;对第二信号线252进行测试的信号传递如下:Ce11测试信号探针→第二奇数信号输入端子332→第二短路棒262→第一过孔42→第二过孔43→第二信号线252。

[0051] 本申请另一实施例还提供了一种阵列基板,该阵列基板可以由上述任一项所述的阵列基板母板沿所述切割线切割得到的包含所述第二测试区域的基板,如图6所示。

[0052] 本申请另一实施例还提供了一种显示装置,可以包括上述的阵列基板。

[0053] 本申请实施例提供了一种阵列基板、阵列基板母板及显示装置,其中阵列基板母板包括由切割线分成的第一测试区域和第二测试区域,第二测试区域内设置有多个测试单元,测试单元包括测试短路棒以及连接在测试短路棒上的多条信号线,测试短路棒用于向

信号线输入检测信号;各测试单元的测试短路棒之间通过串接线依次串接,串接线跨越所述切割线;通过相同的测试短路棒进行切割工艺之前的Array测试和切割工艺之后的Cell测试,因此,测试短路棒本身的不良在Array测试阶段可以被检测出来,避免流入下一道工序,避免在Cell测试阶段出现因测试短路棒自身不良导致的点灯画面异常,进而提高Cell测试阶段的产能和良品率。

[0054] 本说明书中的各个实施例均采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似的部分互相参见即可。

[0055] 最后,还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语"包括"、"包含"或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句"包括一个……"限定的要素,并不排除在包括所述要素的过程、方法、商品或者设备中还存在另外的相同要素。

[0056] 以上对本发明所提供的一种阵列基板、阵列基板母板及显示装置进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

图1

图2

图3

图4

图5

图6