## (12) United States Patent

## Tsai et al.

## (54) LAYOUT METHOD FOR COMPOUND SEMICONDUCTOR INTEGRATED CIRCUITS

- (71) Applicant: WIN Semiconductors Corp., Tao Yuan (TW)

- (72) Inventors: Shu-Hsiao Tsai, Tao Yuan (TW); Rong-Hao Svu, Tao Yuan (TW); Yi-Ling Liu, Tao Yuan (TW); Cheng-Kuo Lin, Tao Yuan (TW)

- Assignee: WIN SEMICONDUCTORS CORP., (73)Taoyuan (TW)

- Subject to any disclaimer, the term of this (\*) Notice: patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days. days.

- Appl. No.: 15/066,556 (21)

- Filed: (22)Mar. 10, 2016

#### (65)**Prior Publication Data**

US 2017/0110400 A1 Apr. 20, 2017

#### (30)**Foreign Application Priority Data**

Oct. 19, 2015 (TW) ..... 104134237 A

(51) Int. Cl.

| H01L 21/762 | (2006.01) |

|-------------|-----------|

| H01L 23/522 | (2006.01) |

| H01L 23/00  | (2006.01) |

| H01L 29/73  | (2006.01) |

| H01L 29/423 | (2006.01) |

|             |           |

U.S. Cl. (52) CPC ...... H01L 23/5221 (2013.01); H01L 21/762

(Continued)

(2013.01); H01L 23/564 (2013.01); H01L 29/0692 (2013.01); H01L 29/42304 (2013.01);

### US 9,991,198 B2 (10) Patent No.:

#### (45) Date of Patent: Jun. 5, 2018

- H01L 29/66242 (2013.01); H01L 29/73 (2013.01); H01L 29/737 (2013.01); H01L 29/7371 (2013.01); H01L 27/0207 (2013.01); H01L 27/0823 (2013.01)

- (58) Field of Classification Search None See application file for complete search history.

#### (56)**References** Cited

## U.S. PATENT DOCUMENTS

| 6,136,683    | A * | 10/2000 | Saito H01L 21/7682                     |

|--------------|-----|---------|----------------------------------------|

| 2003/0139513 | Al* | 7/2003  | 257/E21.581<br>HsuB29D 7/01<br>524/445 |

## (Continued)

Primary Examiner - Jay C Chang

(74) Attorney, Agent, or Firm - Muncy, Geissler, Olds & Lowe, P.C.

#### (57)ABSTRACT

A layout method for compound semiconductor integrated circuits, comprising following steps of: forming a first metal layer within a first circuit layout area which intersects with a second circuit layout area at an intersection area on a compound semiconductor substrate; defining an adjacent crossover area including said intersection area and a peripheral adjacent area thereof; a first dielectric area located within said adjacent crossover area and intersected with at least part of said intersection area; forming a first dielectric block within said first dielectric area or forming said first dielectric block within said first dielectric area and a second dielectric block outside said first dielectric area, the thickness of said second dielectric block is no greater than and the thickness of at least part of said second dielectric block is smaller than the thickness of said first dielectric block; forming a second metal layer within said second circuit layout area.

## 30 Claims, 26 Drawing Sheets

(51) Int. Cl.

| H01L 29/66  | (2006.01) |

|-------------|-----------|

| H01L 29/737 | (2006.01) |

| H01L 29/06  | (2006.01) |

| H01L 27/02  | (2006.01) |

| H01L 27/082 | (2006.01) |

#### (56) **References** Cited

U.S. PATENT DOCUMENTS

| 2010/0156559 A1* | 6/2010 | Wang H01P 1/184   |

|------------------|--------|-------------------|

|                  |        | 333/161           |

| 2014/0042642 A1* | 2/2014 | Chen H01L 23/5283 |

|                  |        | 257/775           |

\* cited by examiner

Fig. 1A

Fig. 1E

Fig. 1G

Fig. 1I

Fig. 1K

Fig. 1M

**U.S.** Patent

Sheet 10 of 26

Fig. 2B

Fig. 2C

Fig. 2D

# Fig. 2E

Fig. 2F

Fig. 2G

Fig. 2I

Fig. 2J

Fig. 2K

Fig. 2M

Fig. 3

10

65

## LAYOUT METHOD FOR COMPOUND SEMICONDUCTOR INTEGRATED CIRCUITS

## FIELD OF THE INVENTION

The present invention relates to a layout method for compound semiconductor integrated circuits, especially to a layout method for compound semiconductor integrated circuits with enhanced moisture resistance ability for the compound semiconductor integrated circuits.

## BACKGROUND OF THE INVENTION

In the compound semiconductor integrated circuits, when two metal layers having different potentials is required to cross-connect, the area of the cross-connection between two 15 metal layers requires good isolation. Conventional technology forms an isolation layer made of polyimide to isolate the cross-connection of two metal layers having different potentials. Usually an isolation layer of polyimide is firstly formed on a bottom metal layer, and then forming a top metal layer 20 on the polyimide isolation layer, wherein the bottom metal layer and the top metal layer are two metal layers having different potentials. However, the polyimide isolation layer is needed only in the intersection area and the adjacent area of the cross-connection of the bottom metal layer and the top layer. There is no need of the polyimide isolation layer in other area. The polyimide isolation layer usually will not be removed by etching in convention technology. Hence, the polyimide isolation layer is not only existing in the intersection area of the cross-connection of the bottom metal layer and the top layer, but also existing in other area where it does not need the polyimide isolation layer.

However, since the polyimide itself has such a rate of water absorption that the existence of the polyimide isolation layer will seriously affect the moisture resistance ability of the compound semiconductor integrated circuit. The <sup>35</sup> polyimide isolation layer in the intersection area of the cross-connection of the bottom metal layer and the top layer is needed for isolating the two layers having different potentials, the bottom metal layer and the top layer. But the existence of the polyimide isolation layer in other wide area <sup>40</sup> where does not need the polyimide isolation layer is the main reason that reduces the moisture resistance ability of the compound semiconductor integrated circuit.

Furthermore, the isolation layer must be made of a kind of low dielectric materials having a low dielectric constant, <sup>45</sup> in order to isolate the two layers having different potentials, the bottom metal layer and the top layer. And due to the existence of the isolation layer, especially the essential existence of the isolation layer in the intersection area of the cross-connection of the bottom metal layer and the top layer, <sup>50</sup> thus the impedance of the compound semiconductor integrated circuit around the intersection area of the crossconnection of the bottom metal layer and the top layer is affected by the isolation layer.

Accordingly, the inventor has developed a layout method <sup>55</sup> for compound semiconductor integrated circuits, which may avoid the above mentioned drawbacks, may significantly enhance the moisture resistance ability of the compound semiconductor integrated circuits, and also may enhance the performance of the compound semiconductor integrated <sup>60</sup> circuits, may take into account economic considerations. Therefore, the present invention then has been invented.

## SUMMARY OF THE INVENTION

There are two technical problems that the present invention is seeking to solve: the first one is that if the wide range, 2

where the isolation layer of polyimide is unnecessary, of the isolation layer of polyimide can be removed efficiently, the moisture resistance ability of the compound semiconductor integrated circuit may be significantly enhanced. Hence how to form an isolation layer to isolate the two layers having different potentials, the bottom metal layer and the top layer, and to efficiently remove the isolate layer in the wide range outside the intersection area of the cross-connection of the bottom metal layer and the top layer, so as to significantly enhance the moisture resistance ability of the compound semiconductor integrated circuit is the first technical problem that the present invention is seeking to solve.

The second is that if the wide range, where the isolation layer is unnecessary, of the isolation layer can be removed efficiently, not only the influence of the isolation layer to the impedance of the compound semiconductor integrated circuit may be reduced, but even more through designing and adjusting the thickness, area and shape of the isolation layer and choosing the dielectric constant of the low dielectric material for forming the isolation layer existed around the intersection area of the cross-connection of the bottom metal layer and the top layer are affected by the isolation layer, so as to affect the impedance of the compound semiconductor integrated circuit to benefit the performance of the compound semiconductor integrated circuit. Thereby the impedance is originally harmful to the compound semiconductor integrated circuit, now may be turned into benefiting the performance of the compound semiconductor integrated circuit. Hence how to reduce harmful impact of the isolation layer to the impedance of the compound semiconductor integrated circuit, by means of designing and adjusting the thickness, area and shape of the isolation layer and choosing the dielectric constant of the low dielectric material for forming the isolation layer existed around the intersection area of the cross-connection of the bottom metal layer and the top layer, so as to enhance the performance of the compound semiconductor integrated circuit. This is the second technical problem the present invention is seeking to solve.

In order to solve the problems mentioned the above and to achieve the expected effect, the present invention provides a layout method for compound semiconductor integrated circuits comprising following steps of: A1: defining a compound semiconductor integrated circuit layout area on a top surface of a compound semiconductor substrate, wherein said compound semiconductor integrated circuit layout area includes a first circuit layout area and a second circuit layout area; said first circuit layout area and said second circuit layout area intersect at an intersection area; an adjacent crossover area is defined to include said intersection area and a peripheral adjacent area of said intersection area; A2: defining a first dielectric area on said top surface of said compound semiconductor substrate, wherein said first dielectric area is located within said adjacent crossover area, and said first dielectric area intersects with at least part of said intersection area; a second dielectric area is defined as the area outside said first dielectric area on said top surface of said compound semiconductor substrate; A3: forming a first metal layer within said first circuit layout area; A4: forming a low dielectric block made of a low dielectric material, wherein said low dielectric block is formed within both said first dielectric area and said second dielectric area, wherein a first dielectric block is defined as said low dielectric block within said first dielectric area, a second dielectric block is defined as said low dielectric block within said second dielectric area; the thickness of said second dielectric block is no greater than the thickness of said first

dielectric block, and the thickness of at least part of said second dielectric block is smaller than the thickness of said first dielectric block; and A5: forming a second metal layer within said second circuit layout area.

In one embodiment, said low dielectric material has a 5 water absorption rate lower than 5%.

In one embodiment, said low dielectric material is at least one material selected from the group consisting of polybenzoxazole (PBO) and Benzo Cyclobutane (BCB).

In one embodiment of the layout method for compound 10 semiconductor integrated circuits, in the step of A4, forming said low dielectric block comprises following steps of: forming a first low dielectric layer within both said first dielectric area and said second dielectric area, wherein the thickness of said first low dielectric layer is equal to the 15 thickness of said second dielectric block; and forming a second low dielectric layer within said first dielectric area, wherein a sum of the thickness of said second low dielectric layer and the thickness of said first low dielectric layer is equal to the thickness of said first dielectric block. 20

In one embodiment of the layout method for compound semiconductor integrated circuits, in the step of A4, forming said low dielectric block comprises following steps of: forming a first low dielectric layer within both said first dielectric area and said second dielectric area, wherein the 25 thickness of said first low dielectric layer is equal to the thickness of said second dielectric block; forming a second low dielectric layer within both said first dielectric area and said second dielectric layer and the thickness of said second low dielectric layer and the thickness of said 30 first low dielectric layer is equal to the thickness of said first dielectric block; and removing said second low dielectric layer within said second dielectric area by using the exposure and development or etching.

In one embodiment of the layout method for compound 35 semiconductor integrated circuits, in the step of A4, forming said low dielectric block comprises following steps of: forming said low dielectric block within both said first dielectric area and said second dielectric area, wherein the thickness of said low dielectric block is equal to the thick- 40 ness of said first dielectric block; and removing said low dielectric block within said second dielectric area by using the exposure and development or etching, such that the thickness of said low dielectric block within said first dielectric area is equal to the thickness of said first dielectric 45 block, and the thickness of said low dielectric block within said second dielectric area is equal to the thickness of said second dielectric block.

In one embodiment of the layout method for compound semiconductor integrated circuits, in the step of A4, forming 50 said low dielectric block comprises following steps of: forming said low dielectric block within both said first dielectric area and said second dielectric area; and removing said low dielectric block within both said first dielectric area and said second dielectric area by using the exposure and 55 development or etching, such that the thickness of said low dielectric block within said first dielectric area is equal to the thickness of said first dielectric block, and the thickness of said low dielectric block within said second dielectric area is equal to the thickness of said second dielectric block. 60

In one embodiment, said peripheral adjacent area of said intersection area includes the area surrounding said intersection area within the range of 50 µm.

In one embodiment, said low dielectric material has a dielectric constant less than 7.

65

In one embodiment of the layout method for compound semiconductor integrated circuits, forming said first dielec4

tric block further comprises following step of: according to the need of an impedance of said compound semiconductor integrated circuit near said adjacent crossover area, deciding a thickness, an area and a shape of said first dielectric block corresponding to said adjacent crossover area, and a dielectric constant of said low dielectric material to form said first dielectric block, so as to enhance the performance of said compound semiconductor integrated circuits.

In one embodiment, the layout method for compound semiconductor integrated circuits further comprises following steps of: defining a power amplifier layout area within said compound semiconductor integrated circuit layout area; forming a power amplifier within said power amplifier layout area, wherein said power amplifier includes a first terminal, a second terminal and a third terminal; one of said first terminal and said second terminal is an output terminal of said power amplifier; said first terminal is electrically connected with one of said first metal layer and said second metal layer while said second terminal is electrically con-20 nected with the other one of said first metal layer and said second metal layer, such that said first terminal and said second terminal of said power amplifier are isolated by said first dielectric block; and according to the need of an output impedance between said first terminal and said second terminal of said power amplifier near said adjacent crossover area, deciding the thickness, the area and the shape of said first dielectric block corresponding to said adjacent crossover area, and a dielectric constant of said low dielectric material to form said first dielectric block, so as to enhance the performance of said compound semiconductor integrated circuit.

In one embodiment, said power amplifier is a bipolar transistor or a heterojunction bipolar transistor; said first terminal is a collector electrode, said second terminal is an emitter electrode, said third terminal is a base electrode; said output impedance is the impedance between said collector electrode and said emitter electrode of said power amplifier.

In one embodiment, said power amplifier is a field effect transistor; said first terminal is a drain electrode, said second terminal is a source electrode, said third terminal is a gate electrode; said output impedance is the impedance between said drain electrode and said source electrode of said power amplifier.

In one embodiment, the layout method for compound semiconductor integrated circuits further comprises following steps of: defining a main power amplifier layout area and a bias circuit power amplifier layout area within said compound semiconductor integrated circuit layout area; forming a main power amplifier within said main power amplifier layout area, wherein said main power amplifier includes a main power amplifier first terminal, a main power amplifier second terminal and a main power amplifier third terminal; said main power amplifier third terminal is an input terminal of said main power amplifier; forming a bias circuit power amplifier within said bias circuit power amplifier layout area, wherein said bias circuit power amplifier includes a bias circuit power amplifier first terminal, a bias circuit power amplifier second terminal and a bias circuit power amplifier third terminal; said bias circuit power amplifier first terminal is electrically connected with one of said first metal layer and said second metal layer while said main power amplifier third terminal is electrically connected with the other one of said first metal layer and said second metal layer, such that said bias circuit power amplifier first terminal and said main power amplifier third terminal are isolated by said first dielectric block; and according to the need of an impedance between said bias circuit power amplifier first

terminal and said main power amplifier third terminal near said adjacent crossover area, deciding a thickness, an area and a shape of said first dielectric block corresponding to said adjacent crossover area, and a dielectric constant of said low dielectric material to form said first dielectric block, so 5 as to enhance the performance of said compound semiconductor integrated circuit, wherein said impedance is an input impedance of said main power amplifier.

In one embodiment, said main power amplifier and said bias circuit power amplifier are a bipolar transistor or a 10 heterojunction bipolar transistor; said main power amplifier first terminal is a main power amplifier collector electrode, said main power amplifier second terminal is a main power amplifier emitter electrode, said main power amplifier third terminal is a main power amplifier base electrode, said bias 15 circuit power amplifier first terminal is a bias circuit power amplifier collector electrode, said bias circuit power amplifier second terminal is a bias circuit power amplifier second terminal is a bias circuit power amplifier second terminal is a bias circuit power amplifier emitter electrode, said bias circuit power amplifier third terminal is a bias circuit power amplifier base electrode, wherein said 20 input impedance is the impedance between said bias circuit power amplifier collector electrode and said main power amplifier base electrode.

In one embodiment, said main power amplifier and said bias circuit power amplifier are a field effect transistor, said 25 main power amplifier first terminal is a main power amplifier drain electrode, said main power amplifier second terminal is a main power amplifier source electrode, said main power amplifier third terminal is a main power amplifier gate electrode, said bias circuit power amplifier first terminal 30 is a bias circuit power amplifier drain electrode, said bias circuit power amplifier second terminal is a bias circuit power amplifier source electrode, said bias circuit power amplifier third terminal is a bias circuit power amplifier third terminal is a bias circuit power amplifier gate electrode; said input impedance is the impedance between 35 said bias circuit power amplifier drain electrode and said main power amplifier gate electrode.

In one embodiment of the layout method for compound semiconductor integrated circuits, between the step of A3 and the step of A4, further comprises a step of forming at 40 least one upper insulating layer, wherein said at least one upper insulating layer is formed on said compound semiconductor substrate and said first metal layer, and said at least one upper insulating layer is formed below said low dielectric block. 45

In one embodiment, said at least one upper insulating layer is made of at least one material selected from the group consisting of SiN and SiO<sub>2</sub>.

In one embodiment, the layout method for compound semiconductor integrated circuits before the step of A3 50 further comprises a step of forming at least one lower insulating layer, wherein said at least one lower insulating layer is formed on said compound semiconductor substrate, and said at least one lower insulating layer is formed below said first metal layer and said low dielectric block. 55

In one embodiment, said at least one lower insulating layer is made of at least one material selected from the group consisting of SiN and  $SiO_2$ .

In one embodiment, the layout method for compound semiconductor integrated circuits after the step of A5 further 60 comprises a step of forming at least one protection layer on said compound semiconductor integrated circuit.

In one embodiment, said at least one protection layer is made of at least one material selected from the group consisting of polybenzoxazole (PBO), SiN and SiO<sub>2</sub>.

65

The present invention further provides a layout method for compound semiconductor integrated circuits comprising 6

following steps of: B1: defining a compound semiconductor integrated circuit layout area on a top surface of a compound semiconductor substrate, wherein said compound semiconductor integrated circuit layout area includes a first circuit layout area and a second circuit layout area; said first circuit layout area and said second circuit layout area intersect at an intersection area; an adjacent crossover area is defined to include said intersection area and a peripheral adjacent area of said intersection area; B2: defining a first dielectric area on said top surface of said compound semiconductor substrate, wherein said first dielectric area is located within said adjacent crossover area, and said first dielectric area intersects with at least part of said intersection area; a second dielectric area is defined as the area outside said first dielectric area on said top surface of said compound semiconductor substrate; B3: forming a first metal layer within said first circuit layout area; B4: forming a first dielectric block made of a low dielectric material within said first dielectric area; and B5: forming a second metal layer within said second circuit layout area.

In one embodiment, said low dielectric material has a water absorption rate lower than 5%.

In one embodiment, said low dielectric material is at least one material selected from the group consisting of polybenzoxazole (PBO) and Benzo Cyclobutane (BCB).

In one embodiment of the layout method for compound semiconductor integrated circuits, in the step of B4, forming said first dielectric block comprises following steps of: forming a low dielectric block within both said first dielectric area and said second dielectric area; and removing said low dielectric block within said second dielectric area by using the exposure and development or etching, such that the thickness of said low dielectric block within said first dielectric area is equal to the thickness of said first dielectric block, and the thickness of said low dielectric block within said second dielectric area is equal to zero.

In one embodiment of the layout method for compound semiconductor integrated circuits, in the step of B4, forming said first dielectric block comprises following steps of: forming a low dielectric block within both said first dielectric area and said second dielectric area; and removing said low dielectric block within both said first dielectric area and said second dielectric area by using the exposure and development or etching, such that the thickness of said low dielectric block within said first dielectric area is equal to the thickness of said first dielectric block, and the thickness of said low dielectric block within said second dielectric area is equal to zero.

In one embodiment, said peripheral adjacent area of said intersection area includes the area surrounding said intersection area within the range of 50  $\mu$ m.

In one embodiment, said low dielectric material has a dielectric constant less than 7.

In one embodiment of the layout method for compound semiconductor integrated circuits, forming said first dielectric block further comprises following step of: according to the need of an impedance of said compound semiconductor integrated circuit near said adjacent crossover area, deciding a thickness, an area and a shape of said first dielectric block corresponding to said adjacent crossover area, and a dielectric constant of said low dielectric material to form said first dielectric block, so as to enhance the performance of said compound semiconductor integrated circuit.

In one embodiment, the layout method for compound semiconductor integrated circuits further comprises following steps of: defining a power amplifier layout area within said compound semiconductor integrated circuit layout area;

forming a power amplifier within said power amplifier layout area, wherein said power amplifier includes a first terminal, a second terminal and a third terminal; one of said first terminal and said second terminal is an output terminal of said power amplifier; said first terminal is electrically connected with one of said first metal layer and said second metal layer while said second terminal is electrically connected with the other one of said first metal layer and said second metal layer, such that said first terminal and said second terminal of said power amplifier are isolated by said 10 first dielectric block; and according to the need of an output impedance between said first terminal and said second terminal of said power amplifier near said adjacent crossover area, deciding the thickness, the area and the shape of said first dielectric block corresponding to said adjacent cross- 15 over area, and a dielectric constant of said low dielectric material to form said first dielectric block, so as to enhance the performance of said compound semiconductor integrated circuit.

In one embodiment, said power amplifier is a bipolar 20 transistor or a heterojunction bipolar transistor; said first terminal is a collector electrode, said second terminal is an emitter electrode, said third terminal is a base electrode; said output impedance is the impedance between said collector electrode and said emitter electrode of said power amplifier. 25

In one embodiment, said power amplifier is a field effect transistor; said first terminal is a drain electrode, said second terminal is a source electrode, said third terminal is a gate electrode; said output impedance is the impedance between said drain electrode and said source electrode of said power 30 amplifier.

In one embodiment, the layout method for compound semiconductor integrated circuits further comprises following steps of: defining a main power amplifier layout area and a bias circuit power amplifier layout area within said com- 35 pound semiconductor integrated circuit layout area; forming a main power amplifier within said main power amplifier layout area, wherein said main power amplifier includes a main power amplifier first terminal, a main power amplifier second terminal and a main power amplifier third terminal; 40 said main power amplifier third terminal is an input terminal of said main power amplifier; forming a bias circuit power amplifier within said bias circuit power amplifier layout area, wherein said bias circuit power amplifier includes a bias circuit power amplifier first terminal, a bias circuit 45 power amplifier second terminal and a bias circuit power amplifier third terminal; said bias circuit power amplifier first terminal is electrically connected with one of said first metal layer and said second metal layer while said main power amplifier third terminal is electrically connected with 50 the other one of said first metal layer and said second metal layer, such that said bias circuit power amplifier first terminal and said main power amplifier third terminal are isolated by said first dielectric block; and according to the need of an impedance between said bias circuit power amplifier first 55 the present invention, some preferred embodiments referred terminal and said main power amplifier third terminal near said adjacent crossover area, deciding the thickness, the area and the shape of said first dielectric block corresponding to said adjacent crossover area, and a dielectric constant of said low dielectric material to form said first dielectric block, so 60 as to enhance the performance of said compound semiconductor integrated circuit, wherein said impedance is an input impedance of said main power amplifier.

In one embodiment, said main power amplifier and said bias circuit power amplifier are a bipolar transistor or a 65 heterojunction bipolar transistor; said main power amplifier first terminal is a main power amplifier collector electrode,

said main power amplifier second terminal is a main power amplifier emitter electrode, said main power amplifier third terminal is a main power amplifier base electrode, said bias circuit power amplifier first terminal is a bias circuit power amplifier collector electrode, said bias circuit power amplifier second terminal is a bias circuit power amplifier emitter electrode, said bias circuit power amplifier third terminal is a bias circuit power amplifier base electrode; said input impedance is the impedance between said bias circuit power amplifier collector electrode and said main power amplifier base electrode.

In one embodiment, said main power amplifier and said bias circuit power amplifier are a field effect transistor; said main power amplifier first terminal is a main power amplifier drain electrode, said main power amplifier second terminal is a main power amplifier source electrode, said main power amplifier third terminal is a main power amplifier gate electrode, said bias circuit power amplifier first terminal is a bias circuit power amplifier drain electrode, said bias circuit power amplifier second terminal is a bias circuit power amplifier source electrode, said bias circuit power amplifier third terminal is a bias circuit power amplifier gate electrode; said input impedance is the impedance between said bias circuit power amplifier drain electrode and said main power amplifier gate electrode.

In one embodiment, the layout method for compound semiconductor integrated circuits, between the step of B3 and the step of B4, further comprises a step of forming at least one upper insulating layer; said at least one upper insulating layer is formed on said compound semiconductor substrate and said first metal layer, and said at least one upper insulating layer is formed below said first dielectric block.

In one embodiment, said at least one upper insulating layer is made of at least one material selected from the group consisting of SiN and SiO<sub>2</sub>.

In one embodiment, the layout method for compound semiconductor integrated circuits before the step of B3 further comprises a step of forming at least one lower insulating layer; said at least one lower insulating layer is formed on said compound semiconductor substrate, and said at least one lower insulating layer is formed below said first metal layer and said first dielectric block.

In one embodiment, said at least one lower insulating layer is made of at least one material selected from the group consisting of SiN and SiO<sub>2</sub>.

In one embodiment, the layout method for compound semiconductor integrated circuits after the step of B5 further comprises a step of forming at least one protection layer on said compound semiconductor integrated circuit.

In one embodiment, said at least one protection layer is made of at least one material selected from the group consisting of polybenzoxazole (PBO), SiN and SiO<sub>2</sub>.

For further understanding the characteristics and effects of to drawings are in detail described as follows.

## BRIEF DESCRIPTION OF DRAWINGS

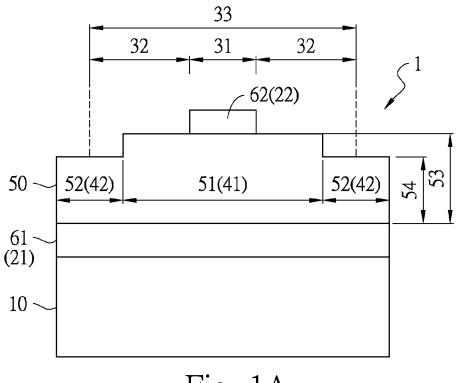

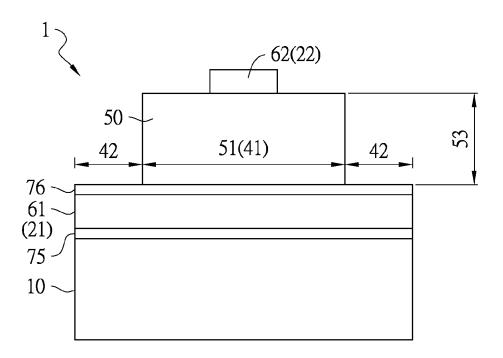

FIGS. 1 and 1A show, respectively, the top view and the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

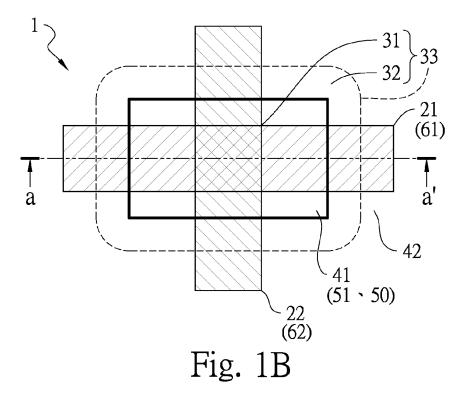

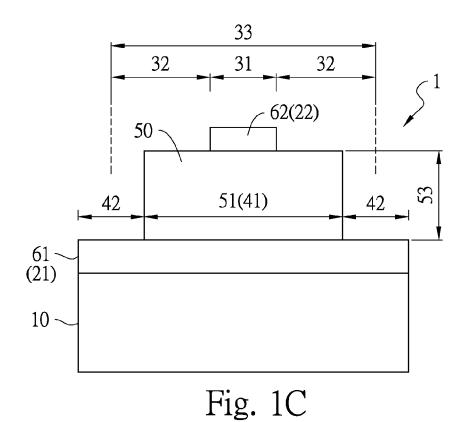

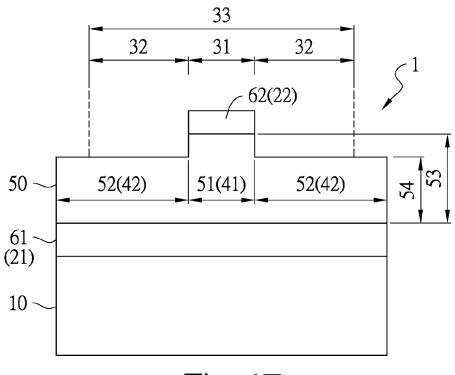

FIGS. 1B and 1C show, respectively, the top view and the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

10

25

50

65

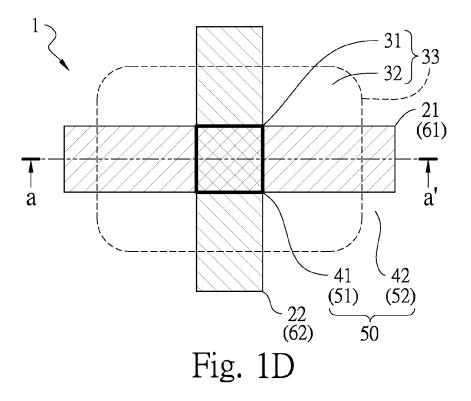

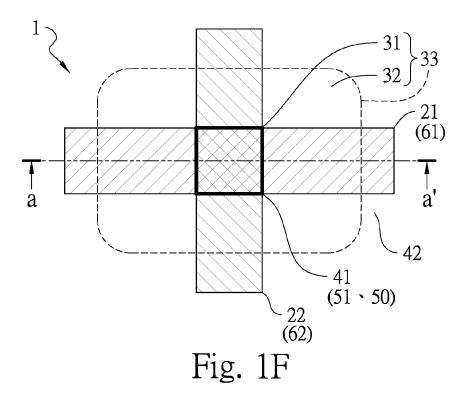

FIGS. 1D and 1E show, respectively, the top view and the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

FIGS. 1F and 1G show, respectively, the top view and the <sup>5</sup> cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

FIGS. 1H and 1I show, respectively, the top view and the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

FIGS. 1J and 1K show, respectively, the top view and the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

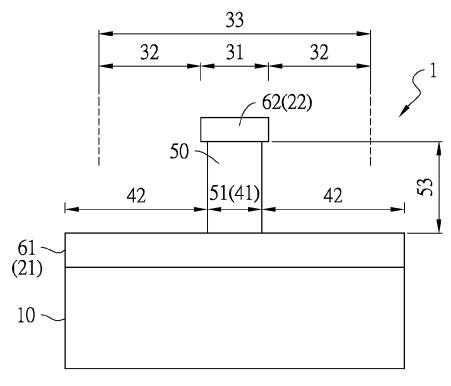

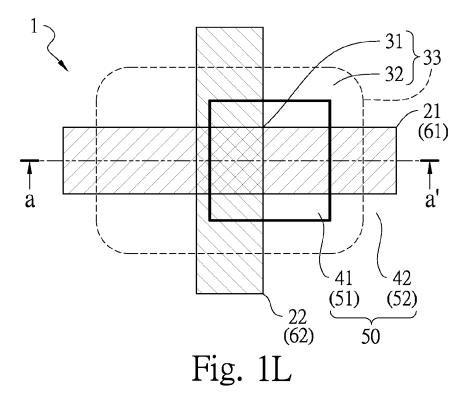

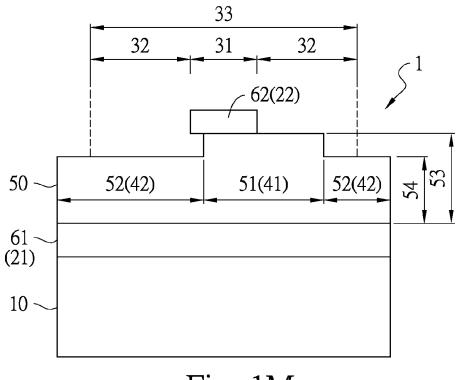

FIGS. 1L and 1M show, respectively, the top view and the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the pres-20 ent invention.

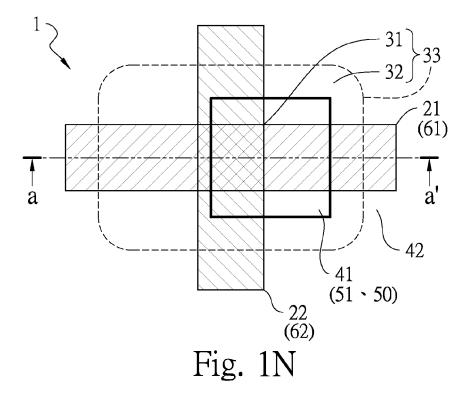

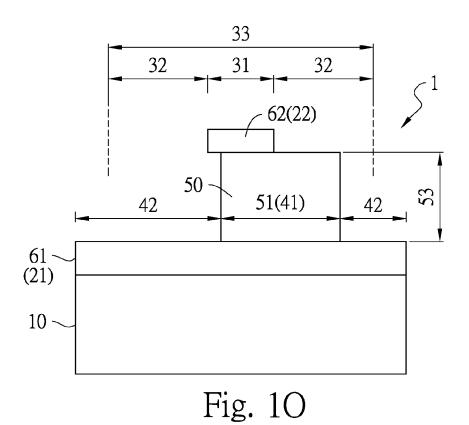

FIGS. 1N and 1O show, respectively, the top view and the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

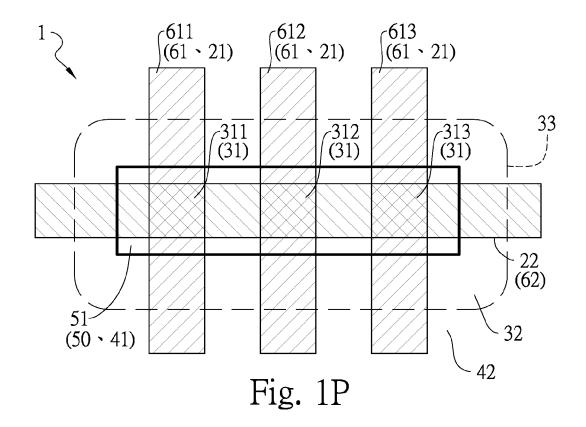

FIG. 1P shows the top view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

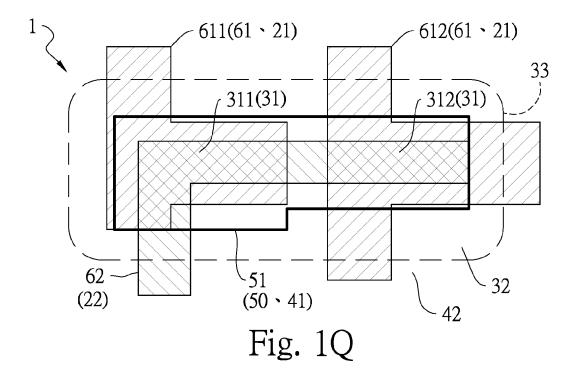

FIG. 1Q shows the top view of an embodiment of a layout method for compound semiconductor integrated circuits of 30 the present invention.

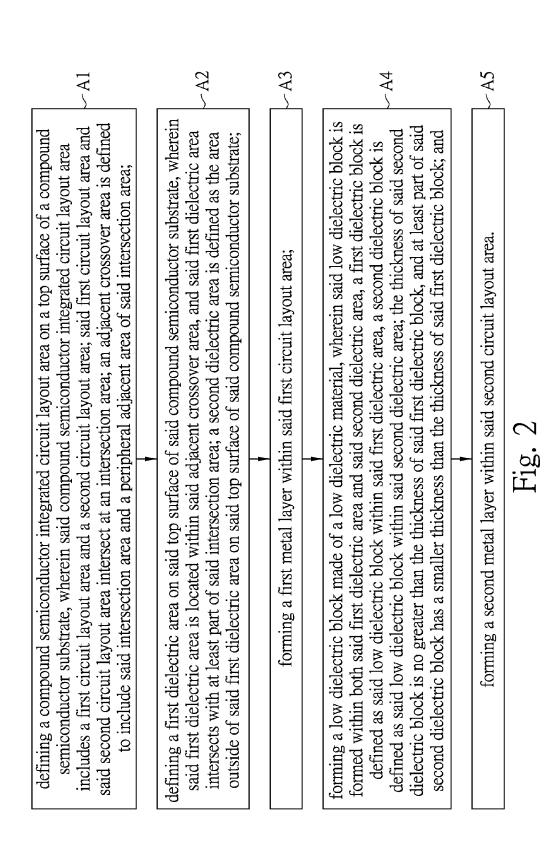

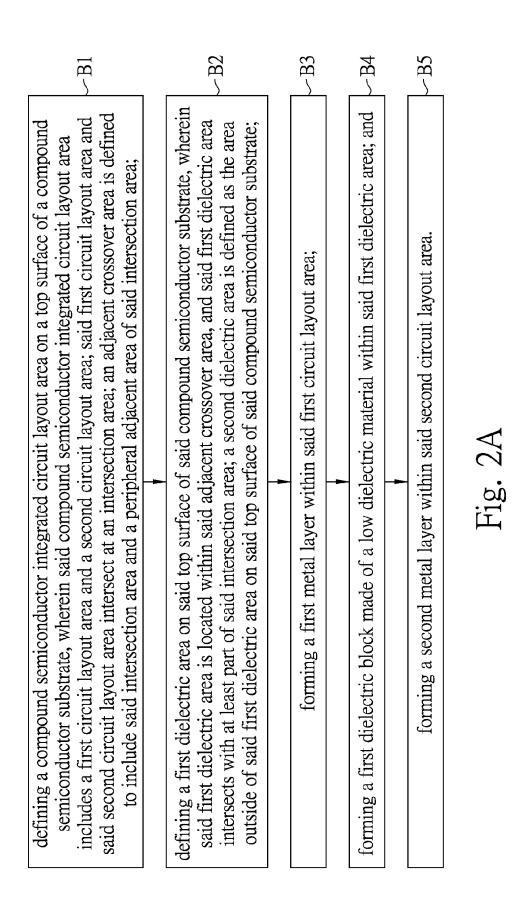

FIG. **2** shows the flow diagram of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

FIG. **2**A shows the flow diagram of another embodiment <sup>35</sup> of a layout method for compound semiconductor integrated circuits of the present invention.

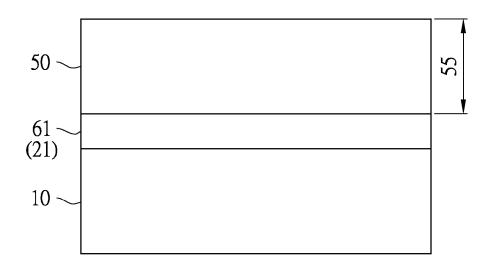

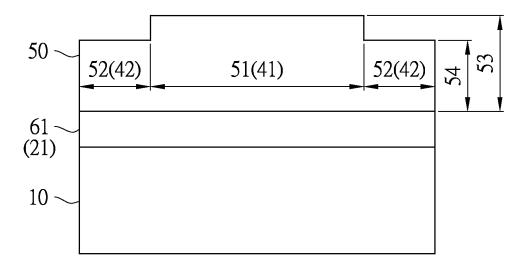

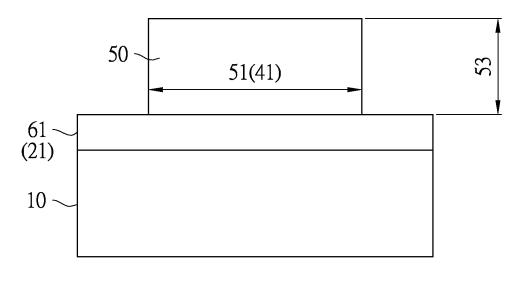

FIG. **2B-2**G show the cross-sectional schematic views of the process steps of the embodiments of a layout method for compound semiconductor integrated circuits of the present 40 invention.

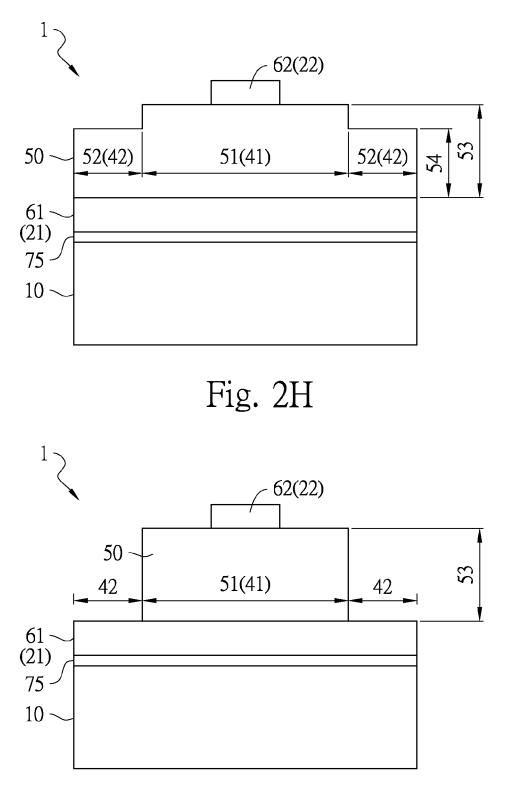

FIG. **2H** shows the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

FIG. **2I** shows the cross-sectional view of an embodiment 45 of a layout method for compound semiconductor integrated circuits of the present invention.

FIG. **2**J shows the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

FIG. **2K** shows the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

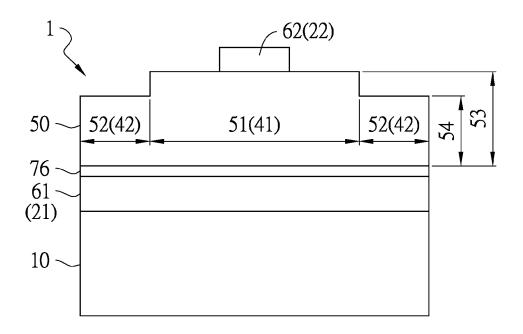

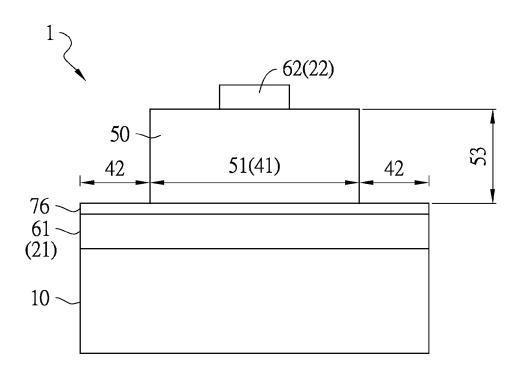

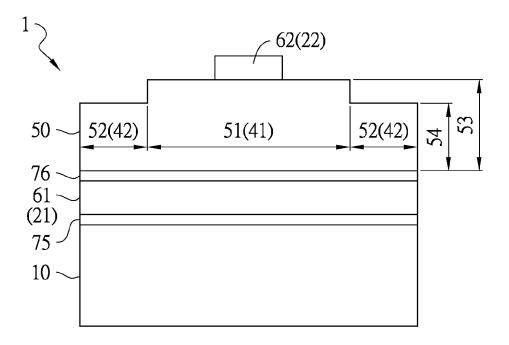

FIG. **2**L shows the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated 55 circuits of the present invention.

FIG. 2M shows the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

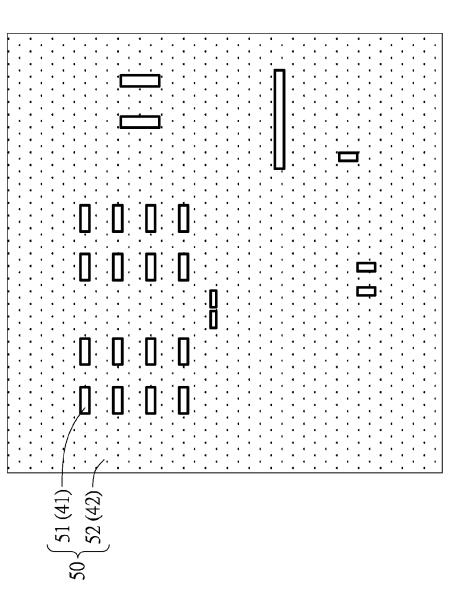

FIG. **3** shows the top schematic view of an embodiment <sup>60</sup> of a layout method for compound semiconductor integrated circuits of the present invention.

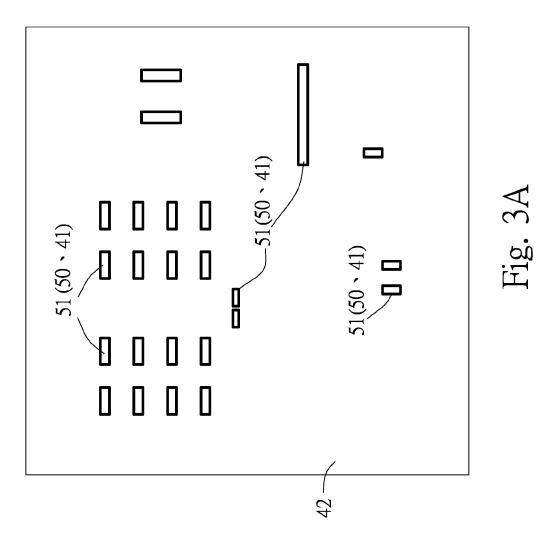

FIG. **3**A shows the top schematic view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

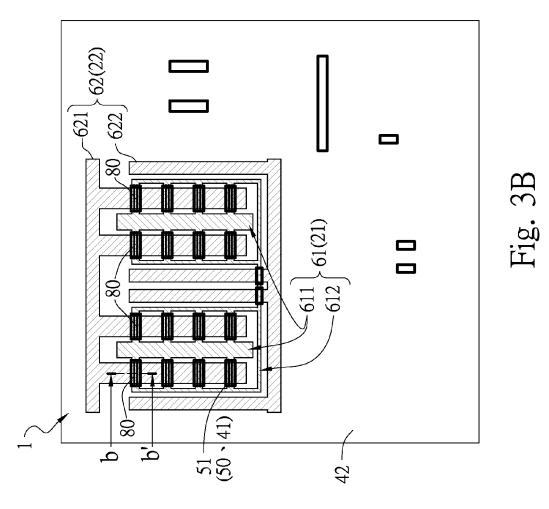

FIG. **3**B illustrates the schematic view of the partial circuit diagram of FIG. **3**A.

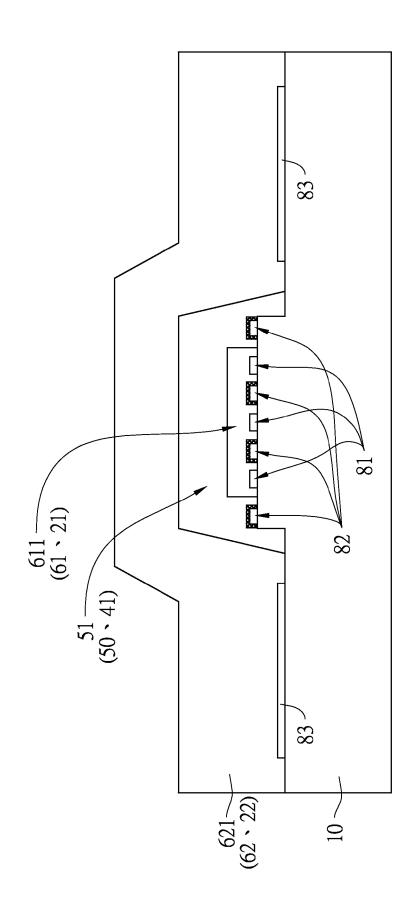

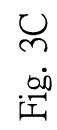

FIG. 3C shows the cross-sectional schematic view along the broken line b-b' in FIG. 3B.

FIG. **3D** shows the cross-sectional schematic view of the cross-sectional structure of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

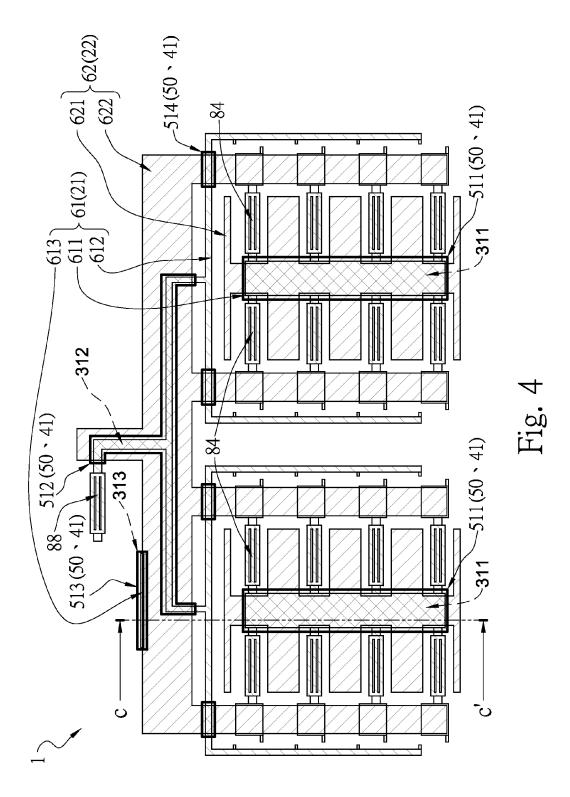

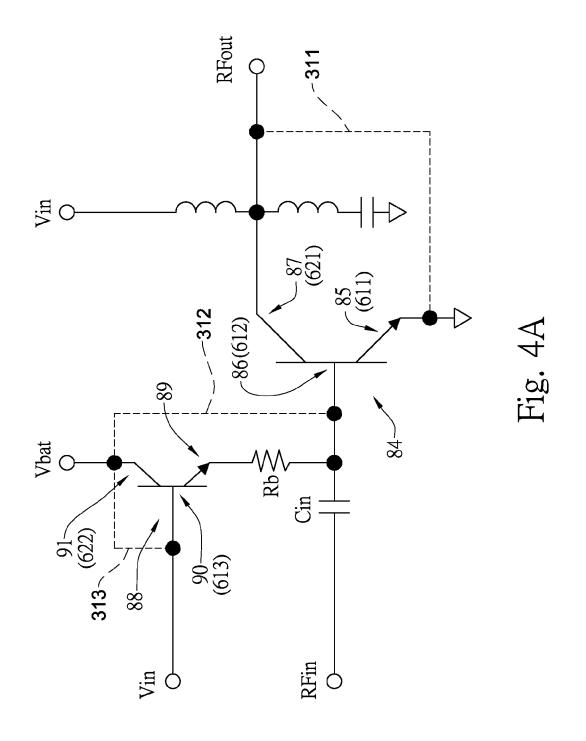

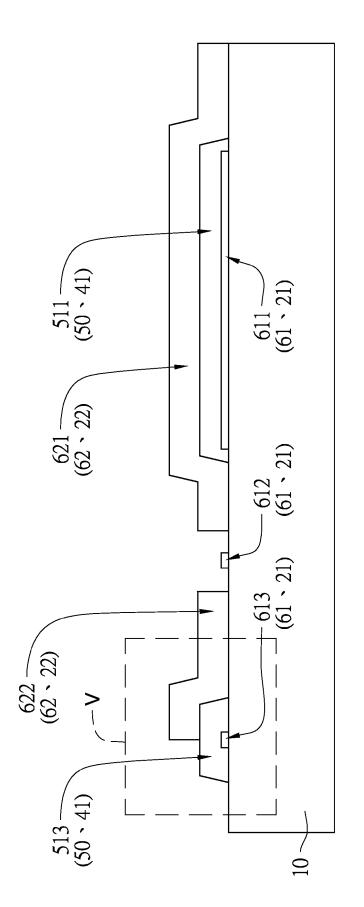

FIG. **4** shows the partial circuit layout schematic view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

FIG. **4**A shows the partial circuit diagram of the corresponding embodiment of FIG. **4**.

FIG. **4**B shows the cross-sectional schematic view along the broken line c-c' in FIG. **4**.

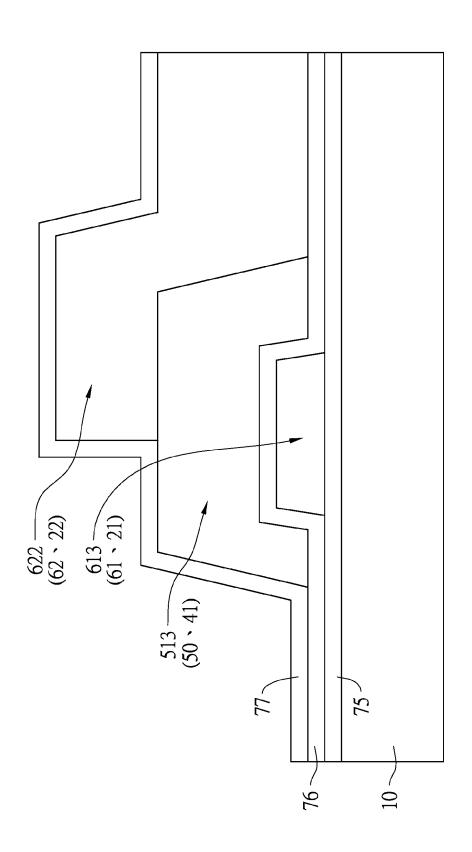

FIG. 4C shows the partial enlargement view of the block 15 V region in FIG. 4B.

## DETAILED DESCRIPTIONS OF PREFERRED EMBODIMENTS

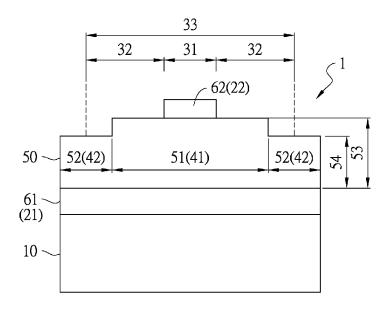

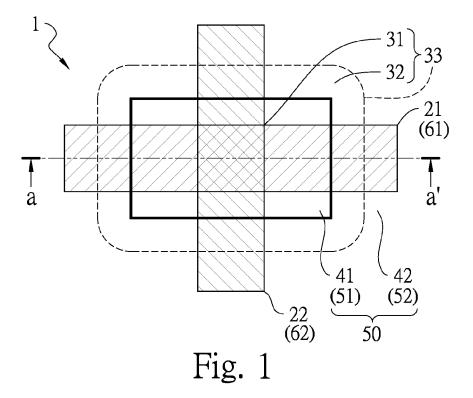

Please refer to FIGS. 1 and 1A (along the broken line a-a' in FIG. 1) which show, respectively, the top view and the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. A compound semiconductor integrated circuit layout area 1 is defined on a top surface of a compound semiconductor substrate 10, wherein the compound semiconductor integrated circuit layout area 1 includes a first circuit layout area 21 and a second circuit layout area 22. A first metal layer 61 is formed within the first circuit layout area 21. The first circuit layout area 21 and the second circuit layout area 22 intersect at an intersection area 31. An adjacent crossover area 33 is defined to include the intersection area 31 and a peripheral adjacent area 32 of the intersection area 31. A first dielectric area 41 (the thick border frame area) is defined on the top surface of the compound semiconductor substrate 10, wherein the first dielectric area 41 is located within the adjacent crossover area 33, and the first dielectric area 41 intersects with at least part of the intersection area 31 (in current embodiment, the first dielectric area 41 includes the whole intersection area 31). The area outside the first dielectric area 41 (the thick border frame area) on the top surface of the compound semiconductor substrate 10 is defined as a second dielectric area 42. A low dielectric block 50 made of a low dielectric material is formed on the compound semiconductor substrate 10 and the first metal layer 61. In current embodiment, the low dielectric block 50 is formed within both the first dielectric area 41 (the thick border frame area) and the second dielectric area 42. The low dielectric block 50 within the first dielectric area 41 is defined as a first dielectric block 51 (the thick border frame area). The first dielectric block 51 has a thickness 53. The low dielectric block 50 within the second dielectric area 42 is defined as a second dielectric block 52. The second dielectric block 52 has a thickness 54, wherein the thickness 54 of the second dielectric block 52 is no greater than the thickness 53 of the first dielectric block 51, and the thickness 54 of at least part of the second dielectric block 52 is smaller than the thickness 53 of the first dielectric block 51 (as shown in FIG. 1A). A second metal layer 62 is formed within the second circuit layout area 22. In current embodiment, the second metal layer 62 is formed on the first dielectric block 51 and the second dielectric block 52.

In the drawings of FIGS. 1, 1B, 1D, 1F, 1H, 1J, 1L, 1N, 1P, 1Q, 3 and 4 of the present invention, the first metal layer 61 is within the area where the hatching at 45 degrees, while the second metal layer 62 is within the area where the

hatching at 135 degrees. The intersection area 31 is the area where the hatching at 45 degrees and the hatching 135 degrees intersect at. The thick border frame area is the first dielectric area 41, which is also the area where the first dielectric block 51 is formed. Furthermore, in FIGS. 3 and 5 3A, the thick border frame area is also the first dielectric area 41 and also where the first dielectric block 51 is formed.

Please refer to FIGS. 1B and 1C (along the broken line a-a' in FIG. 1B) which show, respectively, the top view and the cross-sectional view of another embodiment of a layout 10 method for compound semiconductor integrated circuits of the present invention. A compound semiconductor integrated circuit layout area 1 is defined on a top surface of a compound semiconductor substrate 10, wherein the compound semiconductor integrated circuit layout area 1 includes a first circuit layout area 21 and a second circuit layout area 22. A first metal layer 61 is formed within the first circuit layout area 21. The first circuit layout area 21 and the second circuit layout area 22 intersect at an intersection area **31**. An adjacent crossover area **33** is defined to include 20 the intersection area 31 and a peripheral adjacent area 32 of the intersection area 31. A first dielectric area 41 (the thick border frame area) is defined on the top surface of the compound semiconductor substrate 10, wherein the first dielectric area 41 is located within the adjacent crossover 25 area 33, and the first dielectric area 41 intersects with at least part of the intersection area 31 (in current embodiment, the first dielectric area 41 includes the whole intersection area 31). The area outside the first dielectric area 41 (the thick border frame area) on the top surface of the compound 30 semiconductor substrate 10 is defined as a second dielectric area 42. A low dielectric block 50 made of a low dielectric material is formed on the compound semiconductor substrate 10 and the first metal layer 61. In current embodiment, the low dielectric block 50 is formed only within the first 35 dielectric area 41 (the thick border frame area), but not within the second dielectric area 42. Therefore, in current embodiment, there is no "second dielectric block 52" within the second dielectric area 42. The low dielectric block 50 within the first dielectric area 41 is defined as a first 40 dielectric block 51 (the thick border frame area). The first dielectric block 51 has a thickness 53. A second metal layer 62 is formed within the second circuit layout area 22. In current embodiment, the second metal layer 62 is formed on the first dielectric block 51 and the compound semiconduc- 45 tor substrate 10.

In the embodiments shown in FIG. 1~1C, the low dielectric block 50 may include both the first dielectric block 51 (the thick border frame area) and the second dielectric block 52 (referring to the embodiment shown in FIGS. 1 and 1A), 50 or include only the first dielectric block 51 (the thick border frame area) but without the second dielectric block 52 (referring to the embodiment shown in FIGS. 1B and 1C). The main function of the first dielectric block 51 is to isolate the two layers having different potentials, the first metal 55 intersection area 31 is where the first circuit layout area 21 layer 61 and the second metal layer 62. However the second dielectric block 52 will significantly reduce the moisture resistance ability of the compound semiconductor integrated circuit 1. Hence, when the thickness 54 of the second dielectric block 52 is no greater than the thickness 53 of the 60 first dielectric block 51, and the thickness 54 of at least part of the second dielectric block 52 is smaller than the thickness 53 of the first dielectric block 51, it will benefit enhancing the moisture resistance ability of the compound semiconductor integrated circuit 1. Especially when the 65 thickness 54 of the second dielectric block 52 is less than 90% of the thickness 53 of the first dielectric block 51, it

may significantly enhance the moisture resistance ability of the compound semiconductor integrated circuit 1. The less the thickness 54 of the second dielectric block 52 is, the more obvious the enhancement of the moisture resistance ability of the compound semiconductor integrated circuit 1 is. When the entire second dielectric block 52 is removed (i.e. as the embodiment shown in FIGS. 1 and 1C, without the second dielectric block 52), it has the excellent enhancement of the moisture resistance ability of the compound semiconductor integrated circuit 1.

Among all the embodiments of the present invention, some have a second dielectric block 52, while the other have no second dielectric block 52. In the embodiments having a second dielectric block 52 of the present invention, at least part of the second dielectric block 52 has a thickness 54 greater than 0 and smaller 90% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 85% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 80% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 75% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 70% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 65% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 60% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 55% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 50% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 45% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 40% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 35% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 30% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 25% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 20% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 15% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 12% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 10% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 9% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 8% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 7% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 6% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 5% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 4% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 3% of the thickness 53 of the first dielectric block 51, greater than 0 and smaller 2% of the thickness 53 of the first dielectric block 51, or greater than 0 and smaller 1% of the thickness 53 of the first dielectric block 51.

In all the embodiments of the present invention, the and the second circuit layout area 22 intersect at. The peripheral adjacent area 32 of the intersection area 31 is the area surrounding the intersection area 31 within the range of at least 50 µm, within the range of at least 47 µm, within the range of at least 45 µm, within the range of at least 43 µm, within the range of at least 40 µm, within the range of at least  $37 \,\mu\text{m}$ , within the range of at least  $35 \,\mu\text{m}$ , within the range of at least 33 µm, within the range of at least 30 µm, within the range of at least 28 µm, within the range of at least 25 μm, within the range of at least 23 μm, within the range of at least 20 µm, within the range of at least 17 µm, within the range of at least 15 µm, within the range of at least 12 µm,

10

within the range of at least  $10 \mu m$ , within the range of at least  $9 \mu m$ , within the range of at least  $8 \mu m$ , within the range of at least  $7 \mu m$ , within the range of at least  $6 \mu m$ , or within the range of at least  $5 \mu m$ . The adjacent crossover area **33** is defined to include the intersection area **31** and the peripheral 5 adjacent area **32** of the intersection area **31**.

Furthermore, when choosing the low dielectric material for the low dielectric block **50** in the present invention, it is chosen to have a low water absorption rate for the low dielectric block **50**. The water absorption rate of the low dielectric material for the low dielectric block **50** is at least lower than 5%, at least lower than 4.5%, at least lower than 4.5%, at least lower than 4%, at least lower than 3.5%, at least lower than 3%, at least lower than 2.5%, or at least lower than 2%.

In the embodiments of the present invention, the materials 15 for the low dielectric block **50** may be polybenzoxazole (PBO) or Benzo Cyclobutane (BCB). The best choice of the materials for the low dielectric block **50** may be photosensitive polybenzoxazole (PBO) or photosensitive Benzo Cyclobutane (BCB). The second dielectric block **52** may be 20 removed by the method of exposure and development or etching. When choosing photosensitive polybenzoxazole or photosensitive Benzo Cyclobutane as the material of the low dielectric block **50**, the second dielectric block **52** made of photosensitive polybenzoxazole or photosensitive Benzo 25 Cyclobutane may be easily entirely removed by the method of exposure and development within the second dielectric area **42**, so as to enhance the moisture resistance ability of the compound semiconductor integrated circuit **1**.

In all the embodiments of the present invention, the 30 material for the low dielectric block **50** has a dielectric constant at least less than 7, at least less than 6.7, at least less than 6.3, at least less than 6, at least less than 5.7, at least less than 5.3, at least less than 5, at least less than 4.7, at least less than 4.3, at least less than 4, at least less than 3.7, at least less than 3.3, at least less than 2, at least less than 2.7, at least less than 1.3, or at least less than 1.

Please refer to the embodiments shown in FIG. 1D~1O. In these embodiments, there are respectively various kinds of 40 the intersection area 31, the first dielectric block 51 (the thick border frame area) and the second dielectric block 52. From these embodiments, under the situation that there is only one single intersection area 31 but no other intersection area 31 within the peripheral adjacent area 32 of the intersection area 31, the first dielectric block 51 (the thick border frame area) and the second dielectric block 52 is shown.

Please refer to FIGS. 1D and 1E (along the broken line a-a' in FIG. 1D) which show, respectively, the top view and 50 the cross-sectional view of another embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIGS. 1 and 1A, except that the first dielectric area 41 (the thick border frame 55 area) and the intersection area 31 have the same size and completely overlap with each other.

Please refer to FIGS. 1F and 1G (along the broken line a-a' in FIG. 1F) which show, respectively, the top view and the cross-sectional view of another embodiment of a layout 60 method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIGS. 1D and 1E, except that the low dielectric block **50** is formed only within the first dielectric area **41** (the thick border frame area), but 65 there is no low dielectric block **50** in the second dielectric area **42**. Hence, in current embodiment, there is only the first

dielectric block **51** (the thick border frame area), but no "second dielectric block **52**". In current embodiment, the second metal layer **62** is formed on the first dielectric block **51** and the compound semiconductor substrate **10**.

Please refer to FIGS. 1H and 1I (along the broken line a-a' in FIG. 1H) which show, respectively, the top view and the cross-sectional view of another embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIGS. 1 and 1A, except that the first dielectric area 41 (the thick border frame area) is located totally inside the intersection area 31.

Please refer to FIGS. 1J and 1K (along the broken line a-a' in FIG. 1J) which show, respectively, the top view and the cross-sectional view of another embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIGS. 1H and 1I, except that the low dielectric block 50 is formed only within the first dielectric area 41 (the thick border frame area), but there is no low dielectric block 50 in the second dielectric area 42. Hence, in current embodiment, there is only the first dielectric block 51 (the thick border frame area), but no "second dielectric block 52". In current embodiment, the second metal layer 62 is formed on the first dielectric block 51 and the compound semiconductor substrate 10.

Please refer to FIGS. 1L and 1M (along the broken line a-a' in FIG. 1L) which show, respectively, the top view and the cross-sectional view of another embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIGS. 1 and 1A, except that the first dielectric area 41 (the thick border frame area) intersects with part of the intersection area 31.

Please refer to FIGS. 1N and 1O (along the broken line a-a' in FIG. 1N) which show, respectively, the top view and the cross-sectional view of another embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIGS. 1L and 1M, except that the low dielectric block 50 is formed only within the first dielectric area 41 (the thick border frame area), but there is no low dielectric block 50 in the second dielectric area 42. Hence, in current embodiment, there is only the first dielectric block 51 (the thick border frame area), but no "second dielectric block 52". In current embodiment, the second metal layer 62 is formed on the first dielectric block 51 and the compound semiconductor substrate 10.

Please refer to the embodiments of FIGS. 1P and 1Q. There are multiple intersection areas 31 with different variations in these embodiments respectively. And these multiple intersection areas 31 are very close in distance. Hence, in these embodiments, the peripheral adjacent area 32 of each intersection area 31 overlaps with other intersection area 31 and/or the peripheral adjacent area 32 of other intersection area 31. Therefore, the adjacent crossover area 33 may be a combination of the areas including these multiple intersection areas 31 and the peripheral adjacent areas 32 of these multiple intersection areas **31**. Please firstly refer to FIG. **1**P, which shows the top view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. A compound semiconductor integrated circuit layout area 1 is defined on a top surface of a compound semiconductor substrate 10 (not shown in the Figure), wherein the compound semiconductor integrated circuit layout area 1 includes a first circuit layout area 21 and a second circuit layout area 22. A first metal layer 61 is

formed within the first circuit layout area 21. The first circuit layout area 21 includes three areas. Hence, the first metal layer 61 is formed respectively in these three areas as a first metal layer the first area 611, a first metal layer the second area 612 and a first metal layer the third area 613. The first 5 circuit layout area 21 and the second circuit layout area 22 intersect at an intersection area 31. An adjacent crossover area 33 is defined to include the intersection area 31 and a peripheral adjacent area 32 of the intersection area 31. In current embodiment, the intersection area 31 includes three 10 areas: an intersection area the first area 311, an intersection area the second area 312 and an intersection area the third area 313. Since these three intersection areas 31 are very close in distance, hence, these multiple intersection areas 31 and the peripheral adjacent areas 32 of these multiple 15 intersection areas 31 form the adjacent crossover area 33 as shown in the FIG. 1P. In current embodiment, the adjacent crossover area 33 is a combination of areas including the intersection area the first area 311, the intersection area the second area **312**, the intersection area the third area **313**, the 20 peripheral adjacent area of the intersection area the first area **311**, the peripheral adjacent area of the intersection area the second area 312 and the peripheral adjacent area of the intersection area the third area 313. A first dielectric area 41 (the thick border frame area) is defined on the top surface of 25 the compound semiconductor substrate 10 (not shown in the Figure), wherein the first dielectric area 41 is located within the adjacent crossover area 33, and the first dielectric area 41intersects with at least part of the intersection area 31 (in current embodiment, the first dielectric area 41 includes the 30 intersection area the first area **311**, the intersection area the second area 312 and the intersection area the third area 313). The area outside the first dielectric area 41 (the thick border frame area) on the top surface of the compound semiconductor substrate 10 (not shown in the Figure) is defined as 35 a second dielectric area 42. A low dielectric block 50 made of a low dielectric material is formed on the compound semiconductor substrate 10 (not shown in the Figure) and the first metal layer 61. In current embodiment, the low dielectric block 50 is formed only within the first dielectric 40 area 41 (the thick border frame area), but there is no low dielectric block 50 in the second dielectric area 42. The low dielectric block 50 within the first dielectric area 41 is defined as a first dielectric block 51. The first dielectric block 51 has a thickness 53 (not shown in the Figure). Hence, in 45 current embodiment, there is only the first dielectric block 51 (the thick border frame area), but no "second dielectric block 52". A second metal layer 62 is formed within the second circuit layout area 22. In current embodiment, the second metal layer 62 is formed on the first dielectric block 50 51 and the compound semiconductor substrate 10. Furthermore, there is a variation of current embodiment. The main structure of the variation is mostly similar to the structure of current embodiment, except that the low dielectric block 50 is formed within both the first dielectric area 41 and the 55 second dielectric area 42. The low dielectric block 50 within the second dielectric area 42 is defined as a second dielectric block 52. The second dielectric block 52 has a thickness 54 (not shown in the Figure). The thickness 54 (not shown in the Figure) of at least part of the second dielectric block 52 60 is smaller than the thickness 53 (not shown in the Figure) of the first dielectric block 51. The second metal layer 62 is formed on the first dielectric block 51 and the second dielectric block 52.

Please refer to FIG. 1Q, which shows the top view of 65 another embodiment of a layout method for compound semiconductor integrated circuits of the present invention.

16

In current embodiment, the first circuit layout area 21 includes two areas. Hence, the first metal layer 61 is formed respectively in these two areas: a first metal layer the first area 611 and a first metal layer the second area 612. The first circuit layout area 21 and the second circuit layout area 22 intersect at an intersection area 31. An adjacent crossover area 33 is defined to include the intersection area 31 and a peripheral adjacent area 32 of the intersection area 31. In current embodiment, the intersection area 31 includes two areas: an intersection area the first area 311 and an intersection area the second area 312. Since these two intersection areas 31 are very close in distance, hence these two intersection areas 31 and the peripheral adjacent areas 32 of these two intersection areas 31 form the adjacent crossover area 33 as shown in the FIG. 1Q. In current embodiment, the adjacent crossover area 33 is a combination of areas including the intersection area the first area **311**, the intersection area the second area 312, the peripheral adjacent area of the intersection area the first area 311 and the peripheral adjacent area of the intersection area the second area 312. A first dielectric area 41 (the thick border frame area) is defined on the top surface of the compound semiconductor substrate 10 (not shown in the Figure), wherein the first dielectric area 41 is located within the adjacent crossover area 33, and the first dielectric area 41 intersects with at least part of the intersection area 31 (in current embodiment, the first dielectric area 41 includes the intersection area the first area 311 and the intersection area the second area 312).

Please refer to FIG. 2, which shows the flow diagram of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The layout method comprises following steps of: (please also referring to FIGS. 1, 1A, 1D, 1E, 1H, 1I, 1L and 1M) A1: defining a compound semiconductor integrated circuit layout area 1 on a top surface of a compound semiconductor substrate 10, wherein the compound semiconductor integrated circuit layout area 1 includes a first circuit layout area 21 and a second circuit layout area 22; the first circuit layout area 21 and the second circuit layout area 22 intersect at an intersection area 31; an adjacent crossover area 33 is defined to include the intersection area 31 and a peripheral adjacent area 32 of the intersection area 31; A2: defining a first dielectric area 41 (the thick border frame area) on the top surface of the compound semiconductor substrate 10, wherein the first dielectric area 41 is located within the adjacent crossover area 33, and the first dielectric area 41 intersects with at least part of the intersection area 31; a second dielectric area 42 is defined as the area outside the first dielectric area 41 on the top surface of the compound semiconductor substrate 10; A3: forming a first metal layer 61 within the first circuit layout area 21; A4: forming a low dielectric block 50 made of a low dielectric material, wherein the low dielectric block 50 is formed within both the first dielectric area 41 and the second dielectric area 42 (referring to FIGS. 1 and 1A), a first dielectric block 51 is defined as the low dielectric block 50 within the first dielectric area 41 (the thick border frame area); the first dielectric block 51 has a thickness 53; a second dielectric block 52 is defined as the low dielectric block 50 within the second dielectric area 42; the second dielectric block 52 has a thickness 54; the thickness 54 of the second dielectric block 52 is no greater than the thickness 53 of the first dielectric block 51, and the thickness 54 of at least part of the second dielectric block 52 is smaller than the thickness 53 of the first dielectric block 51 (referring to FIGS. 1 and 1A); and A5: forming a second metal layer 62 within the second circuit layout area **22**; so as to enhance the moisture resistance ability of the compound semiconductor integrated circuit **1**.

Please refer to FIG. 2A, which shows the flow diagram of another embodiment of a layout method for compound 5 semiconductor integrated circuits of the present invention. The layout method comprises following steps of: (please also referring to FIGS. 1B, 1C, 1F, 1Q 1J, 1K, 1N and 1O) B1: defining a compound semiconductor integrated circuit layout area 1 on a top surface of a compound semiconductor 10 substrate 10, wherein the compound semiconductor integrated circuit layout area 1 includes a first circuit layout area 21 and a second circuit layout area 22; the first circuit layout area 21 and the second circuit layout area 22 intersect at an intersection area 31; an adjacent crossover area 33 is defined 15 to include the intersection area 31 and a peripheral adjacent area 32 of the intersection area 31; B2: defining a first dielectric area 41 (the thick border frame area) on the top surface of the compound semiconductor substrate 10, wherein the first dielectric area 41 is located within the 20 adjacent crossover area 33, and the first dielectric area 41 intersects with at least part of the intersection area 31; a second dielectric area 42 is defined as the area outside the first dielectric area 41 on the top surface of the compound semiconductor substrate 10; B3: forming a first metal layer 25 61 within the first circuit layout area 21; B4: forming a first dielectric block 51 made of a low dielectric material within the first dielectric area 41 (referring to FIGS. 1B and 1C, the thick border frame area); the first dielectric block 51 has a thickness 53; and B5: forming a second metal layer 62 30 within the second circuit layout area 22; so as to enhance the moisture resistance ability of the compound semiconductor integrated circuit 1.

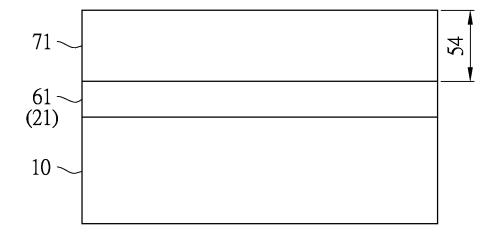

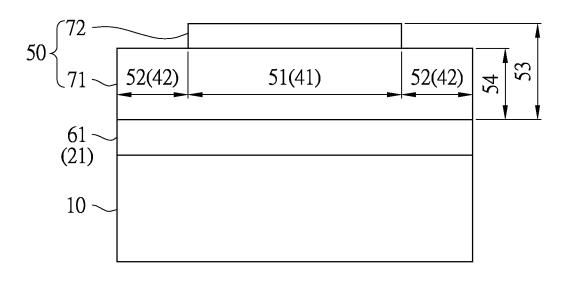

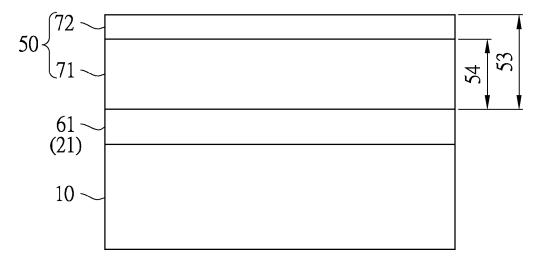

Please refer to FIGS. 2B and 2C, which show the crosssectional schematic views of the process steps of an embodi- 35 ment of a layout method for compound semiconductor integrated circuits of the present invention. In an embodiment, the A4 step of forming the low dielectric block 50 comprises following steps of: (referring to FIG. 2B) forming a first low dielectric layer 71 within both the first dielectric 40 area 41 and the second dielectric area 42, wherein the thickness of the first low dielectric layer 71 is equal to the thickness 54 of the second dielectric block 52; and (referring to FIG. 2C) forming a second low dielectric layer 72 within the first dielectric area 41, wherein a sum of the thickness of 45 the second low dielectric layer 72 and the thickness of the first low dielectric layer 71 (the thickness 54 of the second dielectric block 52) is equal to the thickness 53 of the first dielectric block 51. The first low dielectric layer 71 and the second low dielectric layer 72 have the same material as the 50 low dielectric material of the low dielectric block 50.

Please refer to FIGS. 2B, 2C and 2D, which show the cross-sectional schematic views of the process steps of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. In another 55 embodiment, the A4 step of forming the low dielectric block 50 comprises following steps of: (referring to FIG. 2B) forming a first low dielectric layer 71 within both the first dielectric area 41 and the second dielectric area 42, wherein the thickness of the first low dielectric layer 71 is equal to 60 the thickness 54 of the second dielectric block 52; (referring to FIG. 2D) forming a second low dielectric layer 72 within both the first dielectric area 41 and the second dielectric area 42, wherein a sum of the thickness of the first low dielectric layer 71 (equal to the thickness 54 of the second dielectric 65 block 52) and the thickness of the second low dielectric layer 72 is equal to the thickness 53 of the first dielectric block 51;

and (referring to FIG. 2C) removing the second low dielectric layer 72 within the second dielectric area 42 by using the exposure and development or etching such that there remains only the first low dielectric layer 71 within the second dielectric area 42, and the thickness of the first low dielectric layer 71 within the second dielectric layer 71 within the second dielectric layer 71 within the second dielectric block 52. The first low dielectric layer 71 and the second low dielectric layer 72 have the same material as the low dielectric material of the low dielectric block 50.

Please refer to FIGS. 2E and 2F, which show the crosssectional schematic views of the process steps of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. In another embodiment, the A4 step of forming the low dielectric block 50 comprises following steps of: (referring to FIG. 2E) forming the low dielectric block 50 within both the first dielectric area 41 and the second dielectric area 42, wherein the thickness 55 of the low dielectric block 50 is equal to the thickness 53 of the first dielectric block 51; and (referring to FIG. 2F) removing the low dielectric block 50 within the second dielectric area 42 by using the exposure and development or etching, such that the thickness of the low dielectric block 50 within the first dielectric area 41 is equal to the thickness 53 of the first dielectric block 51, and the thickness of the low dielectric block 50 within the second dielectric area 42 is equal to the thickness 54 of the second dielectric block 52.

Please refer to FIGS. 2E and 2F, which show the crosssectional schematic views of the process steps of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. In another embodiment, the A4 step of forming the low dielectric block 50 comprises following steps of: (referring to FIG. 2E) forming the low dielectric block 50 within both the first dielectric area 41 and the second dielectric area 42, wherein the thickness 55 of the low dielectric block 50 is greater than the thickness 53 of the first dielectric block 51; and (referring to FIG. 2F) removing the low dielectric block 50 within both the first dielectric area 41 and the second dielectric area 42 by using the exposure and development or etching, such that the thickness of the low dielectric block 50 within the first dielectric area 41 is equal to the thickness 53 of the first dielectric block 51, and the thickness of the low dielectric block 50 within the second dielectric area 42 is equal to the thickness 54 of the second dielectric block 52.

Please refer to FIGS. 2E and 2O which show the crosssectional schematic views of the process steps of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. In another embodiment, the B4 step of forming the first dielectric block 51 comprises following steps of: (referring to FIG. 2E) forming the low dielectric block 50 within both the first dielectric area 41 and the second dielectric area 42, wherein the thickness 55 of the low dielectric block 50 is equal to the thickness 53 of the first dielectric block 51; and (referring to FIG. 2G) removing the low dielectric block 50 within the second dielectric area 42 by using the exposure and development or etching, such that the thickness of the low dielectric block 50 within the first dielectric area 41 is equal to the thickness 53 of the first dielectric block 51, and the thickness of the low dielectric block 50 within the second dielectric area 42 is equal to zero.

Please refer to FIGS. 2E and 2Q which show the crosssectional schematic views of the process steps of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. In another embodiment, the B4 step of forming the first dielectric block **51** comprises following steps of: (referring to FIG. 2E) forming the low dielectric block **50** within both the first dielectric area **41** and the second dielectric area **42**, wherein the thickness **55** of the low dielectric block **50** is greater than 5 the thickness **53** of the first dielectric block **51**; and (referring to FIG. 2G) by using the exposure and development or etching the low dielectric block **50** within the first dielectric area **41**, and removing the low dielectric block **50** within the second dielectric area **42** by using the exposure and development or etching, such that the thickness of the low dielectric block **50** within the first dielectric block **50** within the first dielectric block **50** within the thickness of the low dielectric block **50** within the first dielectric block **50** within the first dielectric block **50** within the thickness of the low dielectric block **50** within the second dielectric block **50** within the first dielectric block **51**, and the thickness of the low dielectric block **50** within the second dielectric area **42** is equal to zero.

Please refer to FIG. 2H, which shows the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIGS. 1 and 1A, except that it further 20 comprises a lower insulating layer 75 formed on the compound semiconductor substrate 10, and the lower insulating layer 75 is formed below the first metal layer 61 and the low dielectric block 50. The lower insulating layer 75 is made of at least one material selected from the group consisting of 25 SiN and SiO<sub>2</sub>. The layout method is mostly similar to that of the embodiment shown in FIG. 2, except that before the step of A3 it further comprises a step of forming a lower insulating layer 75, such that the lower insulating layer 75 is formed on the compound semiconductor substrate 10, and 30 the lower insulating layer 75 is formed below the first metal layer 61 and the low dielectric block 50. In another embodiment, the structure may comprise a plural of lower insulating layers 75 (not shown in the Figure).

Please refer to FIG. 2I, which shows the cross-sectional 35 view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIG. 2H, except that the low dielectric block 50 is formed only within the first dielectric area 40 41. but there is no low dielectric block 50 in the second dielectric area 42. Hence, in current embodiment, there is only the first dielectric block 51, but no "second dielectric block 52". In another embodiment, the structure may comprise a plural of lower insulating layers 75 (not shown in the 45 Figure). The layout method is mostly similar to that of the embodiment shown in FIG. 2A, except that before the step of B3 it further comprises a step of forming a lower insulating layer 75, such that the lower insulating layer 75 is formed on the compound semiconductor substrate 10, and 50 the lower insulating layer 75 is formed below the first metal layer 61 and the first dielectric block 51.

Please refer to FIG. 2J, which shows the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. <sup>55</sup> The main structure is mostly similar to the structure of the embodiment shown in FIGS. 1 and 1A, except that it further comprises an upper insulating layer **76** formed on the compound semiconductor substrate **10** and the first metal layer **61**, and the upper insulating layer **76** is formed below <sup>60</sup> the low dielectric block **50**. The upper insulating layer **76** is mostly similar to that of the embodiment shown in FIG. **2**, except that between the step of A3 and the step of A4 it further <sup>65</sup> comprises a step of forming an upper insulating layer **76**, such that the upper insulating layer **76** is formed on the

compound semiconductor substrate 10 and the first metal layer 61, and the upper insulating layer 76 is formed below the low dielectric block 50. In another embodiment, the structure may comprise a plural of upper insulating layers 76 (not shown in the Figure).

Please refer to FIG. 2K, which shows the cross-sectional view of an embodiment of a layout method for compound semiconductor integrated circuits of the present invention. The main structure is mostly similar to the structure of the embodiment shown in FIG. 2J, except that the low dielectric block 50 is formed only within the first dielectric area 41, but there is no low dielectric block 50 in the second dielectric area 42. Hence, in current embodiment, there is only the first dielectric block 51, but no "second dielectric block 52". In another embodiment, the structure may comprise a plural of upper insulating layers 76 (not shown in the Figure). The layout method is mostly similar to that of the embodiment shown in FIG. 2A, except that between the step of B3 and the step of B4 it further comprises a step of forming an upper insulating layer 76, such that the upper insulating layer 76 is formed on the compound semiconductor substrate 10 and the first metal layer 61, and the upper insulating layer 76 is formed below the first dielectric block 51.