US009911782B2

# (12) United States Patent

## Tamura

## (54) SEMICONDUCTOR DEVICE AND METHOD FOR DRIVING THE SAME

- (71) Applicant: Semiconductor Energy Laboratory Co., Ltd., Atsugi-shi, Kanagawa-ken (JP)

- (72) Inventor: Hikaru Tamura, Zama (JP)

- (73) Assignee: Semiconductor Energy Laboratory Co., Ltd., Kanagawa-ken (JP)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 14/611,678

- (22) Filed: Feb. 2, 2015

#### (65) **Prior Publication Data**

US 2015/0145006 A1 May 28, 2015

## **Related U.S. Application Data**

(63) Continuation of application No. 13/543,146, filed on Jul. 6, 2012, now Pat. No. 8,952,313.

## (30) Foreign Application Priority Data

Jul. 15, 2011 (JP) ..... 2011-156679

(51) Int. Cl.

| H01L 27/146 | (2006.01) |

|-------------|-----------|

| H04N 5/355  | (2011.01) |

| H04N 5/374  | (2011.01) |

(52) U.S. Cl. CPC .. H01L 27/14643 (2013.01); H01L 27/14612 (2013.01); H01L 27/14641 (2013.01);

## (Continued)

(58) Field of Classification Search CPC . H01L 27/146; H01L 31/102; H01L 31/0232; H01L 27/14643; H01L 27/14612; H04N 5/355; H04N 5/374

(Continued)

## (10) Patent No.: US 9,911,782 B2

## (45) **Date of Patent:** Mar. 6, 2018

(56) **References Cited**

## U.S. PATENT DOCUMENTS

| 5,386,108 A * | 1/1995 | Arikawa H01L 27/14681            |

|---------------|--------|----------------------------------|

| 5,539,461 A * | 7/1996 | 250/208.1<br>Andoh H01L 27/14643 |

|               |        | 250/208.1                        |

(Continued)

## FOREIGN PATENT DOCUMENTS

| $\mathbf{EP}$ | 0757476 A   | 2/1997 |  |

|---------------|-------------|--------|--|

| JP            | 09-046596 A | 2/1997 |  |

|               | (Continued) |        |  |

## OTHER PUBLICATIONS

International Search Report (Application No. PCT/JP2012/067243) dated Aug. 7, 2012.

(Continued)

Primary Examiner — Georgia Y Epps Assistant Examiner — Don Williams (74) Attorney, Agent, or Firm — Robinson Intellectual Property Law Office; Eric J. Robinson

## (57) ABSTRACT

1 column

The semiconductor device includes a plurality of pixels arranged in rows and columns, and first transistors fewer than the number of the plurality of pixels. The plurality of pixels each includes a photodiode and an amplifier circuit. The amplifier circuit holds the accumulated charge and includes at least a second transistor electrically connected to a cathode of the photodiode. The cathode of the photodiode in the pixel in an n-th row and the cathode of the photodiode in the pixel in an (n+1)-th row are electrically connected to the first transistor. The number n is a natural number. The pixel in the n-th row and the pixel in the (n+1)-th row are in an identical column.

## 15 Claims, 12 Drawing Sheets

(52) **U.S. Cl.** CPC **H04N 5**/

CPC ...... **H04N 5/355** (2013.01); **H04N 5/374** (2013.01); H01L 27/14621 (2013.01); H01L 27/14627 (2013.01)

(58) **Field of Classification Search** USPC ...... 250/208.1, 214.1, 214 R; 348/294–312; 257/226, 257, 258, 290–293, 431; 327/210, 391, 493, 514, 515

See application file for complete search history.

## (56) **References Cited**

## U.S. PATENT DOCUMENTS

| 5,955,753    | Α   | 9/1999  | Takahashi       |

|--------------|-----|---------|-----------------|

| 6,043,478    | A * | 3/2000  | Wang 250/208.1  |

| 6,747,638    |     | 6/2004  | Yamazaki et al. |

| 7,514,690    | B2  | 4/2009  | Endo et al.     |

| 7,705,900    | B2  | 4/2010  | Guidash         |

| 7,872,218    | B2  | 1/2011  | Endo et al.     |

| 8,247,813    | B2  | 8/2012  | Koyama et al.   |

| 8,547,753    | B2  | 10/2013 | Takemura et al. |

| 8,748,881    | B2  | 6/2014  | Yamazaki        |

| 8,765,522    | B2  | 7/2014  | Yamazaki        |

| 8,779,420    | B2  | 7/2014  | Yamazaki        |

| 8,866,138    | B2  | 10/2014 | Koyama et al.   |

| 9,214,520    | B2  | 12/2015 | Yamazaki        |

| 9,721,971    | B2  | 8/2017  | Koyama et al.   |

| 2004/0042707 | A1  | 3/2004  | Imai et al.     |

| 2008/0054319 | A1  | 3/2008  | Mouli           |

| 2009/0101948 | A1  | 4/2009  | Park et al.     |

|              |     |         |                 |

| 2010/0182282 A1  | 7/2010  | Kurokawa et al.  |

|------------------|---------|------------------|

| 2011/0108836 A1  | 5/2011  | Koyama et al.    |

| 2011/0204371 A1  | 8/2011  | Kozuma et al.    |

| 2011/0278564 A1* | 11/2011 | Yoneda 257/43    |

| 2012/0002090 A1* | 1/2012  | Aoki G09G 3/3413 |

|                  |         | 348/297          |

| 2016/0163871 A1  | 6/2016  | Yamazaki         |

| 2017/0084638 A1  | 3/2017  | Koyama et al.    |

## FOREIGN PATENT DOCUMENTS

| TD | 2005 222250 4  | 10/2005 |

|----|----------------|---------|

| JP | 2005-333250 A  | 12/2005 |

| JP | 2008-546313    | 12/2008 |

| JP | 2009-105381 A  | 5/2009  |

| JP | 2009-141717 A  | 6/2009  |

| JP | 2011-044887 A  | 3/2011  |

| JP | 2011-119711 A  | 6/2011  |

| JP | 2011-135063 A  | 7/2011  |

| JP | 2011-135064 A  | 7/2011  |

| JP | 2011-139056 A  | 7/2011  |

| WO | WO-2006/130518 | 12/2006 |

| WO | WO-2011/055626 | 5/2011  |

| WO | WO-2011/065210 | 6/2011  |

| WO | WO-2011/065243 | 6/2011  |

| WO | WO-2011/068017 | 6/2011  |

|    |                |         |

## OTHER PUBLICATIONS

Written Opinion (Application No. PCT/JP2012/067243) dated Aug. 7, 2012.

## \* cited by examiner

-111 - 101

П

FIG. 1A <u>100</u> 107 π I 109 105 113~2 103 FIG. 1B 1 column R R R G G G R R G R 1 row В G G В G G R R G R

G

В

G

В

B

G

FIG. 6A

# FIG. 8

FIG. 12C

45

## SEMICONDUCTOR DEVICE AND METHOD FOR DRIVING THE SAME

#### TECHNICAL FIELD

The present invention relates to a semiconductor device and a method for driving the semiconductor device. Specifically, the present invention relates to a solid-state imaging device including a plurality of pixels provided with photosensors and to a method for driving the solid-state imaging device. Further, the present invention relates to an electronic device including the solid-state imaging device.

Note that a semiconductor device refers to a semiconductor element itself or a device including a semiconductor 15 element. Examples of semiconductor elements include thin film transistors. Therefore, semiconductor devices include display devices and memory devices.

## BACKGROUND ART

A photosensor utilizing an amplifying function of a MOS transistor, called a CMOS sensor, can be manufactured by a general CMOS process. Thus, manufacturing cost of a solid-state imaging device including a CMOS sensor in each 25 pixel can be low, and a semiconductor device having a photosensor and a display element formed over one substrate can be realized. In addition, a CMOS sensor requires lower driving voltage than a CCD sensor; therefore, power consumption of the solid-state imaging device can be sup- 30 pressed.

A solid-state imaging device including a CMOS sensor generally employs, for imaging, a rolling shutter method in which an operation to accumulate charge in a photodiode and an operation to read the charge are sequentially per-35 formed row by row (see Patent Document 1). In some cases, such a solid-state imaging device employs a global shutter method in which all the pixels are subjected to an operation to accumulate charge at a time, instead of the rolling shutter 40 method.

#### REFERENCE

#### Patent Document

[Patent Document 1] Japanese Published Patent Application No. 2009-141717

## DISCLOSURE OF INVENTION

When using either the rolling shutter method or global shutter method, a solid-state imaging device including a CMOS sensor requires improved dynamic range to perform imaging in various environments.

For example, in imaging under an environment where the 55 illuminance of external light is low (during the night or in a dark room), light entering a photodiode is weak (the amount of the light is small); therefore, exposure time needs to be extended. Moreover, during the exposure time, data of a distorted image of an object is generated when the object 60 moves or the solid-state imaging device is moved. Thus, extended exposure time may lead to generation of data of a distorted image of the object.

As the size of the solid-state imaging device is reduced, a region of the photodiode which is irradiated with light is 65 reduced, which further precludes imaging under an environment where the illuminance of external light is low.

Low power consumption is one of the important measures for evaluation of the performance of a solid-state imaging device. In particular, in a portable electronic device such as a mobile phone, high power consumption of a solid-state imaging device leads to a disadvantage of short continuous operation time.

It is an object of one embodiment of the present invention to provide a solid-state imaging device that enables improvement in dynamic range. It is another object of one embodiment of the present invention to provide a solid-state imaging device that enables improvement in the quality of an image. It is another object of one embodiment of the present invention to provide a low-power-consumption solid-state imaging device.

In view of the above problems, one embodiment of the present invention is a semiconductor device including a plurality of pixels arranged in rows and columns, and first transistors fewer than the number of the plurality of pixels. The plurality of pixels each includes a photodiode passing current having a value determined by an intensity of light entering the photodiode, and an amplifier circuit accumulating charge with an amount determined by the value of the current and generating an output signal containing the amount of the charge as data. The amplifier circuit holds the accumulated charge and includes at least a second transistor electrically connected to a cathode of the photodiode. The cathode of the photodiode in the pixel in an n-th row and the cathode of the photodiode in the pixel in an (n+1)-th row are electrically connected to the first transistor. The number n is a natural number. The pixel in the n-th row and the pixel in the (n+1)-th row are in an identical column.

One embodiment of the present invention is a semiconductor device including a plurality of pixels arranged in rows and columns, and first transistors fewer than the number of the plurality of pixels. The plurality of pixels each includes at least red, blue, and green sub-pixels each including a photodiode passing current having a value determined by an intensity of light entering the photodiode, and an amplifier circuit accumulating charge with an amount determined by the value of the current and generating an output signal containing the amount of the charge as data. The amplifier circuit holds the charge accumulated and includes at least a second transistor electrically connected to a cathode of the photodiode. The cathode of the photodiode in the sub-pixel in an n-th row and the cathode of the photodiode in the sub-pixel that is provided in an (n+1)-th row and is of a color identical with that of the sub-pixel in the n-th row are electrically connected to the first transistor. The number n is a natural number. The sub-pixel in the n-th row 50 and the sub-pixel in the (n+1)-th row are in an identical column.

In the above semiconductor devices, the off-state current density of the first transistor and the off-state current density of the second transistor are 10  $aA/\mu m$  or less, preferably 100 yA/µm or less. In the solid-state imaging device according to one embodiment of the present invention, a pixel in a pixel group provided in the n-th row and one column is connected to a pixel in a pixel group provided in the (n+1)-th row and that column by the first transistor. Therefore, by using a transistor with extremely low off-state current density as the first transistor, mixture of charge accumulated by imaging performed with a pixel group provided in the n-th row and charge accumulated during imaging performed with a pixel group provided in the (n+1)-th row can be suppressed. Moreover, by using a transistor with extremely low off-state current density as the second transistor and using the second transistor as a switching element for holding

charge accumulated by imaging, variations in grayscale level due to variations in the length of the charge holding period can be maintained at a low level. Thus, the quality of data of an image of the object can be improved.

A transistor can achieve extremely low off-state current <sup>5</sup> density when including, in a channel formation region, a semiconductor material whose band gap is wider than that of silicon and whose intrinsic carrier density is lower than that of silicon. An example of such a semiconductor material is an oxide semiconductor. In this specification, an oxide <sup>10</sup> semiconductor is a metal oxide having semiconductor properties.

By using transistors including an oxide semiconductor in their channel formation regions as transistors included in the solid-state imaging device, the leakage current of each transistor, drive voltage, and the power consumption of the solid-state imaging device can be reduced.

The solid-state imaging device can employ the rolling shutter method and the global shutter method. In the solid- 20 state imaging device, the on state and the off state of the first transistor are selected in accordance with the luminance of external light, and electrical continuity can be established between photodiodes in pixels sharing a wiring to which an output signal is supplied, or photodiodes in sub-pixels of the 25 same color sharing a wiring to which an output signal is supplied. For example, during imaging under an environment where the illuminance of external light is low, the first transistor in the solid-state imaging device is turned on to establish electrical continuity between photodiodes in pixels (or sub-pixels of the same color) sharing a wiring to which an output signal is supplied. Thus, a region of the photodiode which light enters during the imaging, the amount of charge accumulated, and the potential of an output signal corresponding to the amount of charge can be increased. Consequently, during imaging under an environment where the illuminance of external light is low, data of an image with less distortion can be obtained without extending the exposure time. In other words, the dynamic range of the solid- $_{40}$ state imaging device can be improved.

According to one embodiment of the present invention, a solid-state imaging device with improved dynamic range, a solid-state imaging device that enables improvement in the quality of an image, and a low-power-consumption solid- <sup>45</sup> state imaging device can be provided.

## BRIEF DESCRIPTION OF DRAWINGS

FIGS. **1**A and **1**B are diagrams illustrating a structure of <sup>50</sup> a solid-state imaging device according to one embodiment of the present invention.

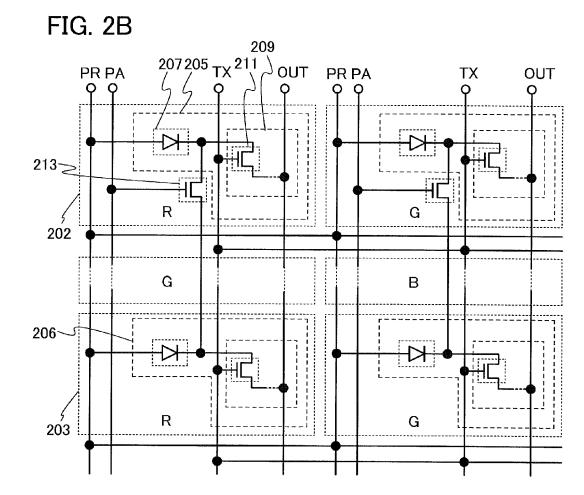

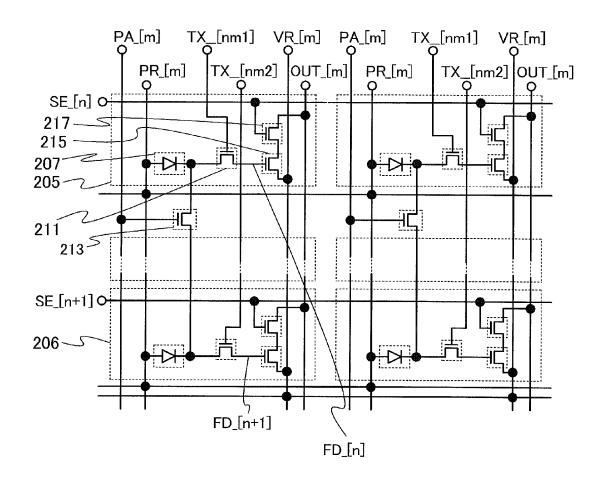

FIGS. 2A and 2B are circuit diagrams of a pixel portion.

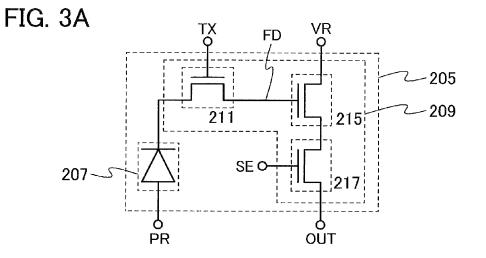

FIG. **3**A is a circuit diagram of a photosensor, and FIG. **3**B is a circuit diagram of a pixel portion including the photo- 55 sensor.

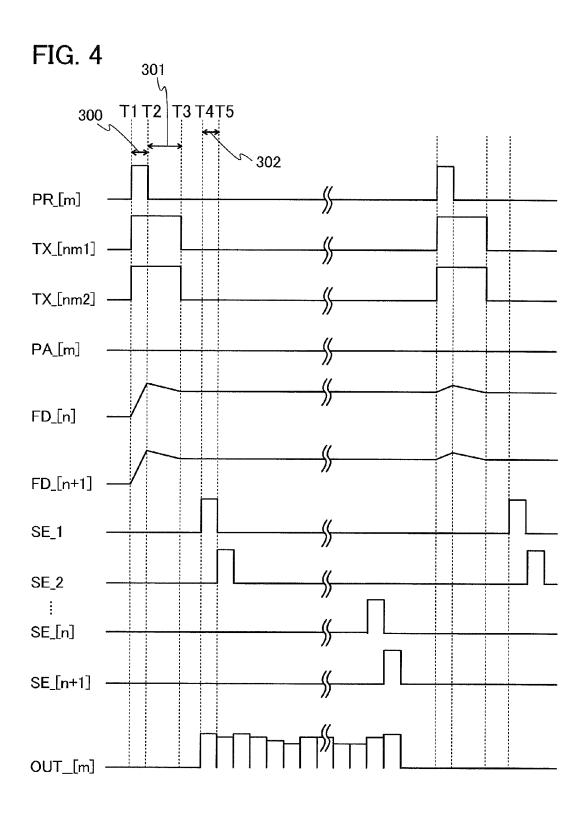

FIG. 4 is a timing chart of a photosensor.

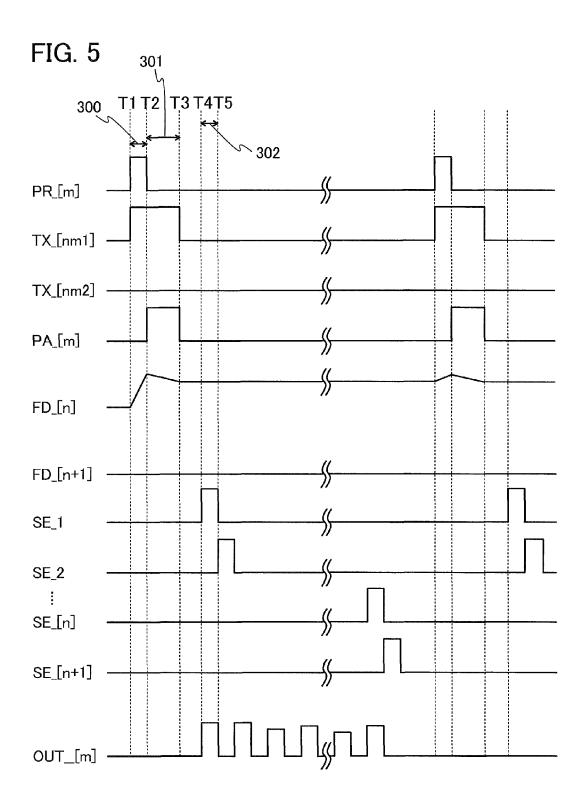

FIG. 5 is a timing chart of a photosensor.

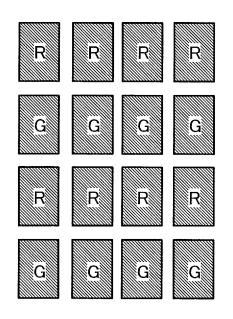

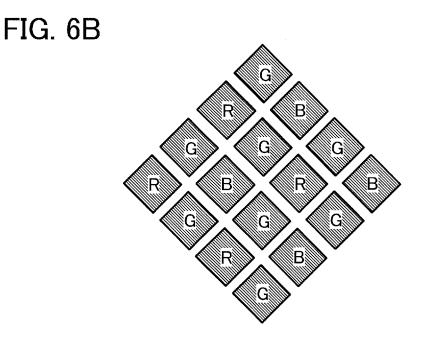

FIGS. **6**A and **6**B are diagrams illustrating one embodiment of color filters. 60

FIG. 7 is a circuit diagram of a pixel portion.

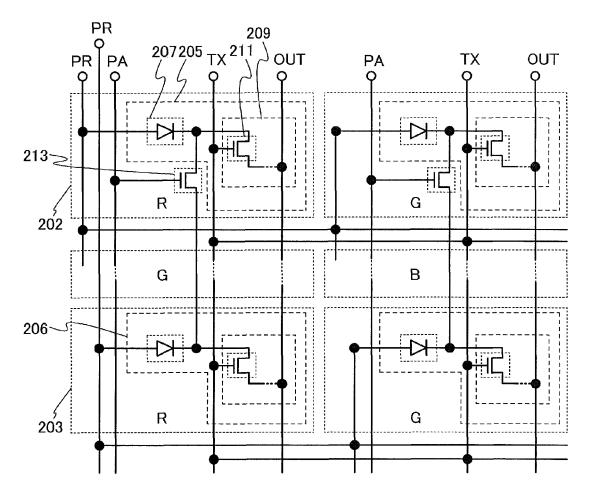

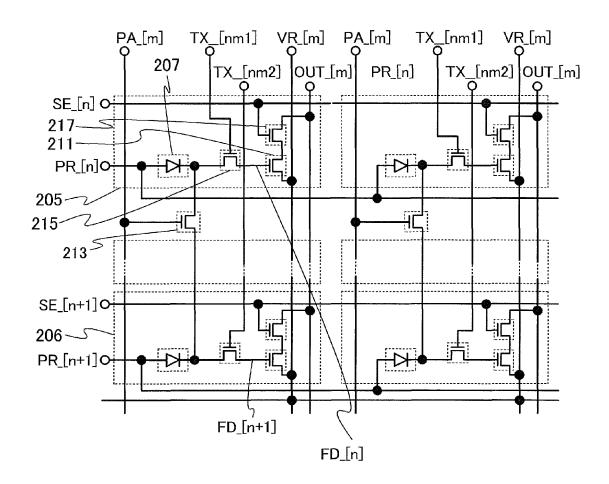

FIG. 8 is a circuit diagram of a pixel portion.

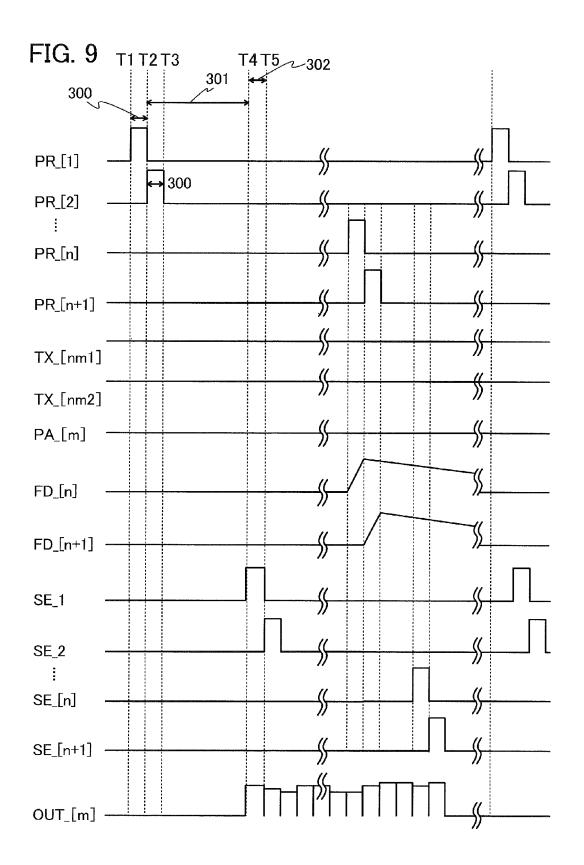

FIG. 9 is a timing chart of a photosensor.

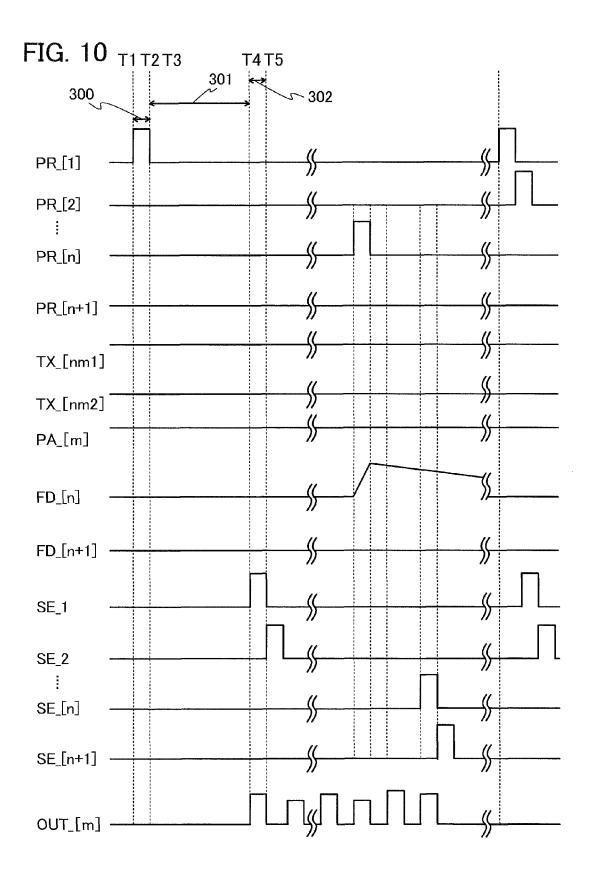

FIG. 10 is a timing chart of a photosensor.

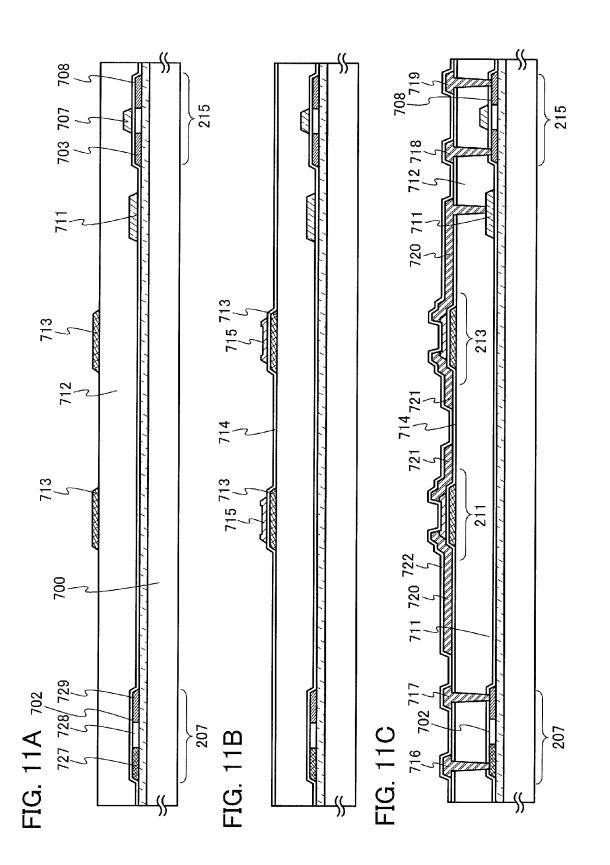

FIGS. **11**A to **11**C are cross-sectional views illustrating a 65 method for manufacturing a photodiode and transistors included in a photosensor.

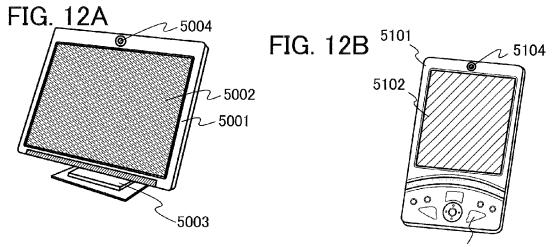

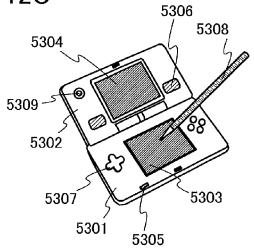

FIGS.  $12\mathrm{A}$  to  $12\mathrm{D}$  are diagrams illustrating electronic devices.

## BEST MODE FOR CARRYING OUT THE INVENTION

Embodiments of the present invention will be described below in detail with reference to the drawings. Note that the present invention is not limited to the following description and it will be readily appreciated by those skilled in the art that the modes and details of the present invention can be modified in various ways without departing from the spirit and scope thereof. Therefore, the present invention should not be interpreted as being limited to the description in the following embodiments.

In this specification, "connection" means electrical connection and corresponds to the state in which current, voltage, or potential can be supplied or transmitted. Therefore, a state of connection means not only a state of direct connection but also a state of indirect connection through a circuit element such as a wiring, a resistor, a diode, or a transistor, in which current, voltage, or potential can be supplied or transmitted.

## Embodiment 1

A description is given with reference to drawings of a structure of a solid-state imaging device according to one embodiment of the present invention, a structure of photosensors included in the solid-state imaging device, and connections between the photosensors. Note that this embodiment describes the case where the global shutter method is used.

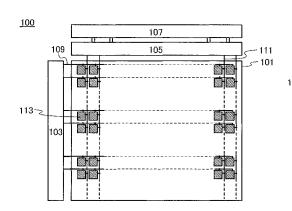

FIG. 1A illustrates an example of a structure of a solidstate imaging device 100 according to one embodiment of the present invention. The solid-state imaging device 100 includes at least a pixel portion 101, a horizontal selection circuit 103, a data output circuit 105, a data processing circuit 107, a plurality of selection lines 109 which are arranged in parallel or substantially parallel to one another and which are connected to the horizontal selection circuit 103 so that the potentials of the selection lines 109 are controlled, and a plurality of output lines 111 which are arranged in parallel or substantially parallel to one another and which are connected to the data output circuit 105 so that the potentials of output signals are supplied to the output lines 111. Note that the solid-state imaging device 100 may include another wiring in addition to the selection lines 109 and the output lines 111 illustrated in FIG. 1A.

Pixels 113 are arranged in a matrix in the pixel portion 101. Each selection line 109 is connected to a plurality of pixels 113 provided in one row. Each output line 111 is connected to a plurality of pixels 113 provided in one column.

The horizontal selection circuit **103**, the data output circuit **105**, and the data processing circuit **107** includes at least a logic circuit and a switch, or at least the logic circuit and a buffer. The data output circuit **105** performs amplification, conversion, and the like of an output signal supplied to the output line **111** and sends the amplified and converted signal to the data processing circuit **107**. The data processing circuit **107** controls the horizontal selection circuit **103**, controls exposure time, and obtains (or generates) image data by processing the output signal, for example.

The horizontal selection circuit 103, the data output circuit 105, and the data processing circuit 107 may be formed over the same substrate as the pixel portion 101.

Alternatively, the horizontal selection circuit **103**, the data output circuit **105**, and the data processing circuit **107** may be partly or fully implemented in a semiconductor device such as an IC.

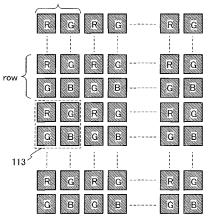

FIG. 1B is an enlarged view of the pixel portion 101. FIG. 5 1B does not illustrate the selection lines 109 and the output lines 111 for simplicity. In the solid-state imaging device 100, the pixel 113 may include sub-pixels provided with red (R), green (G), and blue (B) color filters for color imaging. Note that, in FIG. 1B, the pixel 113 includes four sub-pixels: 10 one red sub-pixel, one blue sub-pixel, and two green subpixels, but its composition is not limited to this. Here, a row pixel group and a column pixel group in which a pixel 113 including four sub-pixels is considered as one pixel are formed. Note that the selection line 109 and the output line 15 111 are branched so as to be connected to the sub-pixels in the pixel 113.

In addition, the solid-state imaging device **100** is not necessarily provided with the sub-pixels illustrated in FIG. **1B** when being designed to display black-and-white images. 20

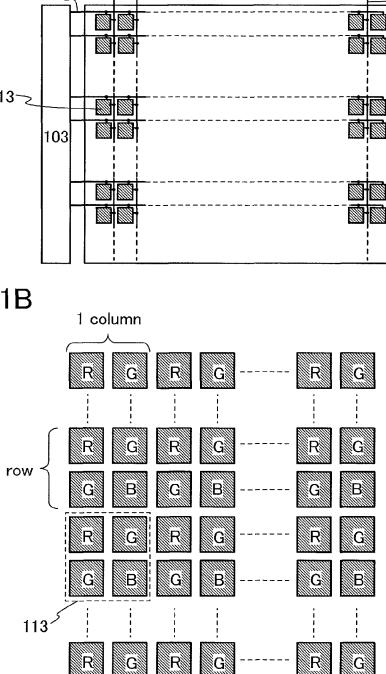

FIG. 2A is an example of a circuit diagram of the pixel portion 101. The RGB sub-pixels included in each pixel 113 are provided with photosensors. In a pixel group in an n-th row (n is a natural number) and a pixel group in an (n+1)-th row, the photosensors provided in sub-pixels which are in 25 the same column and of the same color are connected to each other through a switching element 201. Note that "a pixel group in an n-th row" can also be called "pixels in an n-th row" can also be called "pixels in an (n+1)-th row". 30

Specifically, the photosensor in an R sub-pixel **202** of the pixel **113** in the n-th row is connected to the photosensor in an R sub-pixel **203** of the pixel **113** in the (n+1)-th row with the switching element **201**. The photosensors in the B sub-pixels of the pixel **113** in the n-th row and the pixel **113** 35 in the (n+1)-th row are connected to each other with the switching element **201**. The photosensors in the G sub-pixels of the pixel **113** in the n-th row and the pixel **113** in the (n+1)-th row are connected to each other with the switching element **201**. The photosensors in the G sub-pixels of the pixel **113** in the n-th row and the pixel **113** in the (n+1)-th row are connected to each other with the switching element **201**. A transistor can be used as the switching 40 element **201**.

FIG. 2B is an example of a circuit diagram illustrating connections between the photosensors included in the pixels 113. Here, a description is given taking a connection between the R sub-pixel 202 and the R sub-pixel 203 as an 45 example. The photosensors included in the R sub-pixel 202 and the R sub-pixel 203 (in FIG. 2B, a photosensor 205 and a photosensor 206) each include a photodiode 207 and an amplifier circuit 209. The photodiode 207 is a photoelectric conversion element which generates current when a junction 50 of semiconductors is irradiated with light. The amplifier circuit 209 is a circuit which amplifies current obtained through light reception by the photodiode 207 or which holds charge accumulated due to the current. Since each pixel includes a photosensor and a photodiode, "pixel" can 55 also be called "photosensor" or "photodiode" as appropriate in this specification.

The amplifier circuit **209** may have any configuration as long as it can amplify current generated in the photodiode **207**; the amplifier circuit **209** includes at least a transistor 60 **211** which functions as a switching element. The switching element controls the supply of the current to the amplifier circuit **209**.

By switching between the on and off states of a transistor **213** serving as the switching element **201** with which the 65 photosensor **205** and the photosensor **206** are connected to each other, whether electrical continuity between the pho-

6

todiode 207 in the photosensor 205 and the photodiode 207 in the photosensor 206 is established can be selected. For example, during imaging under an environment where the illuminance of external light is low, electrical continuity between the photodiode 207 in the photosensor 205 and the photodiode 207 in the photosensor 206 is established by turning on the transistor 213. By establishing electrical continuity between the photodiode 207 in the photosensor 205 and the photodiode 207 in the photosensor 206, the photodiode 207 in the photosensor 205 and the photodiode 207 in the photosensor 205 and the photodiode 207 in the photosensor 206 are connected in parallel.

In one embodiment of the present invention, a channel formation region of the transistors 211 and 213 may include a semiconductor material whose band gap is wider than that of a silicon semiconductor and whose intrinsic carrier density is lower than that of silicon. As examples of the semiconductor material, a compound semiconductor such as silicon carbide (SiC) or gallium nitride (GaN), an oxide semiconductor including a metal oxide such as zinc oxide (ZnO), and the like can be given. Among the above semiconductors, an oxide semiconductor has an advantage such as high mass productivity because an oxide semiconductor can be formed by a sputtering method, a wet process (e.g., a printing method), or the like. A compound semiconductor such as silicon carbide or gallium nitride is required to be a single crystal, and in order to obtain a single crystal material, crystal growth at a temperature significantly higher than a process temperature for the oxide semiconductor is needed or epitaxial growth over a special substrate is needed. On the other hand, an oxide semiconductor has high mass productivity because a film thereof can be formed even at room temperature and therefore the film can be formed over a silicon wafer that can be obtained easily or a glass substrate which is inexpensive and can be applied when the size of a substrate is increased. In addition, it is possible to stack a semiconductor element including an oxide semiconductor over an integrated circuit including a normal semiconductor material such as silicon or gallium. Further, in the case where a crystalline oxide semiconductor is to be obtained in order to improve the performance of a transistor (e.g., field-effect mobility or reliability), the crystalline oxide semiconductor can be easily obtained by heat treatment at 200° C. to 800° C.

In the following description, the case in which an oxide semiconductor having the above advantages is used as the semiconductor having a wide band gap is given as an example.

When a semiconductor material having the above-described characteristics is included in a channel formation region, the transistors **211** and **213** can have extremely small off-state current density and high withstand voltage. Further, when the transistors **211** and **213** having the above-described structure are used as switching elements, leakage of charge accumulated in the amplifier circuit **209** can be prevented. Moreover, mixture of charge accumulated in the amplifier circuit **209** in the photosensor **205** in the n-th row and charge accumulated in the amplifier circuit **209** in the photosensor **206** in the (n+1)-th row can be prevented.

Note that it is preferable to use a semiconductor with a wide band gap such as an oxide semiconductor for active layers of the transistors **211** and **213**, but the present invention is not necessarily limited to this structure. It is possible to operate the solid-state imaging device **100** by a global shutter method even when a semiconductor other than an oxide semiconductor, such as amorphous silicon, microcrystalline silicon, polycrystalline silicon, single crystal silicon, amorphous germanium, microcrystalline germanium,

polycrystalline germanium, or single crystal germanium, is used for the active layers of the transistors 211 and 213.

Unless otherwise specified, in the case of an n-channel transistor, off-state current in this specification is a current which flows between a source electrode and a drain elec- 5 trode when, in the state where the potential of the drain electrode is higher than that of the source electrode and that of a gate electrode, the potential of the gate electrode is less than or equal to 0 V with respect to the potential of the source electrode. Furthermore, in this specification, in the 10 case of a p-channel transistor, off-state current is a current which flows between a source electrode and a drain electrode when, in the state where the potential of the drain electrode is lower than that of the source electrode or that of a gate electrode, the potential of the gate electrode is greater 15 than or equal to 0 V with respect to the potential of the source electrode.

The names of the "source electrode" and the "drain electrode" included in the transistor interchange with each other depending on the polarity of the transistor or the levels 20 of potentials applied to the respective electrodes. In general, in an n-channel transistor, an electrode to which a lower potential is applied is called a source electrode, and an electrode to which a higher potential is applied is called a drain electrode. Further, in a p-channel transistor, an elec- 25 trode to which a lower potential is applied is called a drain electrode, and an electrode to which a higher potential is applied is called a source electrode. One of a source electrode and a drain electrode is referred to as a first terminal and the other is referred to as a second terminal, and 30 connections in the photosensors 205 and 206 and a connection among the photodiodes 207 of the photosensors 205 and 206 and the transistor 213 will be described below (see FIG. 2B). The configuration of and connections in the sub-pixels of the other colors are also as described below.

In the photosensor 205, an anode of the photodiode 207 is connected to a wiring PR. A cathode of the photodiode 207 is connected to a first terminal of the transistor 211. A second terminal of the transistor 211 is connected to another semiconductor element included in the amplifier circuit 209; 40 thus, the connection of the second terminal of the transistor 211 differs depending on the configuration of the amplifier circuit 209. A gate electrode of the transistor 211 is connected to a wiring TX. The wiring TX is supplied with a potential of a signal for controlling the switching of the 45 transistor 211. The photosensor 205 is connected to a wiring OUT. The wiring OUT is supplied with a potential of an output signal which is output from the amplifier circuit 209. Note that the wiring OUT corresponds to the output line 111 of the solid-state imaging device 100 (see FIG. 1A).

The structure and connections of the photosensor 206 are the same as those of the photosensor 205 described above.

A first terminal of the transistor 213 is connected to the cathode of the photodiode 207 in the photosensor 205. A second terminal of the transistor 213 is connected to a 55 cathode of the photodiode 207 in the photosensor 206. A gate electrode of the transistor 213 is connected to a wiring PA. The wiring PA is supplied with the potential of a signal for controlling the switching of the transistor 213, in accordance with the luminance of external light. 60

Even when a circuit diagram illustrates independent components which are connected to each other, there is a case where one conductive film has functions of a plurality of components such as the case where part of a wiring functions as an electrode. In this specification, the term "con- 65 nection" also means a case where one conductive film has functions of a plurality of components.

8

FIG. 2B illustrates as an example the case where the wiring PR, the wiring TX, and the wiring OUT are connected to each of the photosensors; however, the number of wirings included in each of the photosensors in one embodiment of the present invention is not limited to the number in this example. In addition to the above wirings, a wiring supplied with a power supply potential, a wiring supplied with a signal for resetting the amount of charge held by the amplifier circuit 209, or the like may be connected to each of the photosensors.

In one embodiment of the present invention, one wiring OUT is connected to the photosensors in the pixels in the same column or in the sub-pixels in the same column, and these photosensors are not connected to a wiring OUT (another wiring OUT) connected to the photosensors in the pixels in another column or in the sub-pixels in another column and are electrically isolated therefrom. In addition, in one embodiment of the present invention, a first photosensor group includes a plurality of photosensors connected to one wiring OUT; a second photosensor group includes a plurality of photosensors connected to another wiring OUT; and a wiring TX connected to the first photosensor group may be connected to a wiring TX connected to the second photosensor group (see FIG. 2B). In one embodiment of the present invention, a wiring PR connected to the first photosensor group may be connected to a wiring PR connected to the second photosensor group (see FIG. 2B). In one embodiment of the present invention, a wiring PA connected to the first photosensor group may be connected to a wiring PA connected to the second photosensor group (they are not connected to each other in FIG. 2B).

In one embodiment of the present invention, the above configuration can suppress a potential decrease or a signal delay due to the resistance of the wirings PR, TX or PA. As 35 a result, it is possible to prevent a potential supplied to the anode of the photodiode 207, a potential of a signal for controlling the switching of the transistor 211, or a potential of a signal for controlling the switching of the transistor 213 from varying within the pixel portion 101. Accordingly, it is possible to prevent a potential of a signal to be output from the photosensors 205 and 206 from varying, and it is possible to improve the quality of an image.

Note that although FIG. 2B illustrates the configuration of the photosensors 205 and 206 in which the amplifier circuit 209 includes only one transistor 211 which functions as a switching element, the amplifier circuit 209 is not limited to this configuration. Although the configuration in which one transistor functions as one switching element is described, a plurality of transistors may function as one switching element in one embodiment of the present invention. In the case where a plurality of transistors functions as one switching element, the plurality of transistors may be connected to each other either in parallel, in series, or in parallel and series.

In this specification, the state in which transistors are connected to each other in series, for example, means a state in which only one of a first terminal and a second terminal of a first transistor is connected to only one of a first terminal and a second terminal of a second transistor. Further, the state in which transistors are connected to each other in parallel means a state in which a first terminal of a first transistor is connected to a first terminal of a second transistor and a second terminal of the first transistor is connected to a second terminal of the second transistor.

FIG. 2B illustrates the case where the transistors 211 and 213 each include the gate electrode only on one side of the active layer. When the transistors 211 and 213 each include a pair of gate electrodes having the active layer sandwiched therebetween, one of the gate electrodes is supplied with a signal for controlling switching, and the other of the gate electrodes may be in a floating state (i.e., electrically isolated) or may be supplied with a potential. In the latter case, 5 the pair of electrodes may be supplied with the same level of potential, or only the other of the gate electrodes may be supplied with a fixed potential such as a ground potential. By controlling the level of potential supplied to the other of the gate electrodes, the threshold voltage of the transistors 211 10 and 213 can be controlled.

Next, an example of a specific configuration of the photosensors 205 and 206 will be described. FIG. 3A is a circuit diagram of an example of the photosensors 205 and 206. Since the photosensor 206 has the same structure and 15 connections as the photosensor 205, only the photosensor 205 is described here.

In the photosensor 205 illustrated in FIG. 3A, the amplifier circuit 209 includes a transistor 215 and a transistor 217 in addition to the transistor 211. In the transistor 215, the 20 tosensors 205 connected to the wiring OUT [m] for the m-th current value or resistance value between a first terminal and a second terminal thereof is determined by a potential supplied to the second terminal of the transistor 211. The transistor 217 functions as a switching element for supplying a potential of an output signal determined by the current 25 value or resistance value, to the wiring OUT.

Specifically, in FIG. 3A, the second terminal of the transistor 211 is connected to a gate electrode of the transistor 215. The first terminal of the transistor 215 is connected to a wiring VR which is supplied with a high power 30 supply potential (VDD) (also called high power supply potential line). The second terminal of the transistor 215 is connected to a first terminal of the transistor 217. A second terminal of the transistor 217 is connected to the wiring OUT. A gate electrode of the transistor 217 is connected to 35 a wiring SE, and the wiring SE is supplied with a potential of a signal for controlling the switching of the transistor 217. Note that the wiring SE corresponds to the selection line 109 in the solid-state imaging device 100 (see FIG. 1A).

In FIG. 3A, a node where the second terminal of the 40 transistor 211 and the gate electrode of the transistor 215 are connected to each other is denoted by a node FD. The current value or resistance value between the first terminal and the second terminal of the transistor 215 is determined by the amount of charge accumulated at the node FD. In 45 addition to this, the potential of the output signal output from the second terminal of the transistor 217 is determined by a potential of a signal for controlling the switching of the transistor 217. In order to hold charge at the node FD more reliably, a storage capacitor may be connected to the node 50 FD.

FIG. 3B is a circuit diagram showing the case where the photosensors 205 and 206 in FIG. 2B have the abovedescribed structure.

The photosensor 205 in the n-th row is connected to a 55 wiring SE\_[n] among wirings SE. The photosensors 206 provided in the (n+1)-th row is connected to a wiring SE\_[n+1]. Note that the wirings SE are independently provided for the respective rows.

The photosensors provided in the m-th column (m is a 60 natural number) are connected to a wiring PR\_[m] among wirings PR, to a wiring OUT\_[m] among wirings OUT, and to a wiring VR\_[m] among wirings VR. Note that the wirings PR are preferably independently provided for the respective columns. The wirings VR may also be indepen- 65 dently provided for the respective columns. The wirings OUT are independently provided for the respective columns.

10

The photosensor 205 in the n-th row and the m-th column (n, m) is connected to a wiring TX [nm1] among wirings TX. The photosensor 206 in the (n+1)-th row and the m-th column (n+1, m) is connected to a wiring TX\_[nm2] among the wirings TX. Note that the wiring TX\_[nm1] and the wiring TX\_[nm2] are separately provided here, but the present invention is not limited to this; the wirings TX may be connected to each other as described above.

The cathode of the photodiode 207 of the photosensor 205 in the n-th row and the m-th column is connected to the first terminal of the transistor 213. The cathode of the photodiode 207 of the photosensor 206 in the (n+1)-th row and the m-th column is connected to the second terminal of the transistor 213. The gate electrode of the transistor 213 is connected to a wiring PA\_[m] among wirings PA. Note that the wirings PA may be independently provided for the respective columns. Alternatively, the wirings PA may be connected to each other as described above.

In the above-described configuration, a plurality of phocolumn and to the wiring VR\_[m] for the m-th column are not connected to the wirings OUT for columns other than the m-th column and to the wirings VR for columns other than the m-th column, and thus are electrically isolated from the photosensors in columns other than the m-th column (see FIG. 3B).

The above configuration can suppress a potential decrease or a signal delay due to the resistance of the wirings PR, TX or PA, as in the case shown in FIGS. 2A and 2B. As a result, it is possible to prevent a potential supplied to the anode of the photodiode 207, a potential of a signal for controlling the switching of the transistor 211, or a potential of a signal for controlling the switching of the transistor 213 from varying within the pixel portion 101. Accordingly, it is possible to prevent a potential of a signal to be output from the photosensors in the pixel portion 101 from varying, and it is possible to improve the quality of an image.

Note that in FIGS. 3A and 3B, oxide semiconductor films may be used for active layers of the transistors included in the amplifier circuit 209 except the transistors 211 and 213, that is, the transistors 215 and 217. When oxide semiconductor films are used for active layers of all of the transistors in the pixel portion 101, the manufacturing process can be simplified. Alternatively, a semiconductor other than an oxide semiconductor, such as amorphous silicon, microcrystalline silicon, polycrystalline silicon, single crystal silicon, amorphous germanium, microcrystalline germanium, polycrystalline germanium, or single crystal germanium, may be used for active layers of the transistors 215 and 217. When a semiconductor material providing higher mobility than an oxide semiconductor, such as polycrystalline or single crystal silicon is used for active layers of the transistors 215 and 217, image data can be read from the photosensors at high speed.

Next, a method for driving the pixel portion 101 is described. A description is given taking the pixels in the m-th column in the pixel portion 101 as an example. FIG. 4 is an example of a timing chart showing potentials applied to the wiring TX\_[nm1], the wiring TX\_[nm2], the wiring PA\_[m], the wiring PR\_[m], the wiring VR\_[m], and the wiring OUT\_[m]. FIG. 4 is also an example of a timing chart showing potentials applied to wirings SE\_[1] to SE\_[n+1] and potentials applied to a node FD\_[n] and a node FD\_ [n+1] in the pixels in rows in the pixel portion 101.

Note that in the timing chart in this embodiment, for easy understanding of the driving method, it is assumed that the above-described wirings are supplied with a high-level

potential and a low-level potential. Specifically, it is assumed that the wiring TX [nm1] and the wiring TX [nm2] are supplied with high-level potentials HTX\_[nm1] and HTX\_[nm2], respectively, and low-level potentials LTX\_[nm1] and LTX\_[nm2], respectively; the wirings SE\_ 5 [1] to SE\_[n+1] are supplied with high-level potentials HSE\_[1] to HSE\_[n+1], respectively, and low-level potentials LSE\_[1] to LSE\_[n+1], respectively; the wiring PA\_ [m] is supplied with a high-level potential HPA\_[m] and a low-level potential LPA\_[m]; the wiring PR\_[m] is supplied 10 with a high-level potential HPR [m] and a low-level potential LPR\_[m]; and the wiring OUT\_[m] is supplied with a high-level potential HOUT\_[m] and a low-level potential LOUT\_[m]. Note that the wiring VR\_[m] is assumed to be supplied with VDD, and thus is not shown in FIG. 4. 15

FIG. 4 is a timing chart showing the driving method in a condition where there is no electrical continuity between the photodiode 207 of the photosensor 205 in the n-th row and the photodiode 207 of the photosensor 206 in the (n+1)-th row, that is, a condition where the transistor **213** is in the off 20 state. In the driving method, the wiring PA\_[m] is always at a potential LPA\_[m].

First, at a time T1, the potential of the wiring PR\_[m] is changed from the potential LPR\_[m] to the potential HPR\_ [m]. Further, at the time T1, the potential of the wiring 25 TX\_[nm1] is changed from the potential LTX\_[nm1] to the potential HTX\_[nm1], and the potential of the wiring TX\_ [nm2] is changed from the potential LTX\_[nm2] to the potential HTX\_[nm2]. When the potentials of the wiring TX\_[nm1] and the wiring TX\_[nm2] are changed to the 30 potential HTX\_[nm1] and the potential HTX\_[nm2], respectively, the transistor 211 is turned on. At the time T1, the wirings SE\_[1] to SE\_[n+1] are supplied with the potentials LSE\_[1] to LSE\_[n+1], respectively.

changed from the potential HPR\_[m] to the potential LPR\_ [m]. At the time T2, the potentials of the wiring TX\_[nm1] and the wiring TX\_[nm2] are kept at the potential HTX\_ [nm1] and the potential HTX\_[nm2], respectively, and the potentials of the wirings SE\_[1] to SE\_[n+1] are kept at the 40 potentials LSE\_[1] to LSE\_[n+1], respectively. Accordingly, the node FD\_[n] and the node FD\_[n+1] are supplied with the potential HPR\_[m]; thus, the amounts of charge held at the node FD\_[n] and the node FD\_[n+1] are reset. A period from the time T1 to the time T2 is called "reset period 300" 45 and an operation during the reset period 300 is called "reset operation".

Here, for simplicity, the potential of the wiring PR\_[m] and the potentials of the wiring TX\_[nm1] and the wiring TX\_[nm2] are changed at the time T1. However, it is 50 acceptable that the potentials of the wiring TX\_[nm1] and the wiring TX [nm2] are changed before the potential of the wiring PR\_[m] is changed. By turning on the transistor 211 before the potential of the wiring PR\_[m] is changed, the node FD\_[n] and the node FD\_[n+1] can be reset com- 55 pletely.

Although not illustrated in FIG. 4, not only the amount of charge held at the node FD\_[n] and the node FD\_[n+1] but also the amount of charge held at the nodes FD in all the photosensors of the pixels in the m-th column (e.g., the node 60 FD\_[1] and the node FD\_[2]) are reset.

Then, at the time T2, the potential of the wiring PR\_[m] is changed to the potential LPR\_[m], so that a reverse bias voltage is applied to the photodiode 207. Then, when light enters the photodiode 207 in a state where a reverse bias 65 voltage is applied to the photodiode 207, current flows from the cathode of the photodiode 207 toward the anode thereof.

The value of the current varies depending on the intensity of light. In other words, as the intensity of light entering the photodiode 207 increases, the value of the current increases and the amount of charge leaking out from the node FD\_[n] and the node FD\_[n+1] also increases. In contrast, as the intensity of light entering the photodiode 207 decreases, the value of the current decreases and the amount of charge leaking out from the node FD\_[n] and the node FD\_[n+1] decreases. Therefore, the higher the intensity of light becomes, the larger the amount of change in the potential of the node FD\_[n] and the node FD\_[n+1] becomes; the lower the intensity of light becomes, the smaller the amount of change becomes.

Then, at a time T3, the potential of the wiring TX\_[nm1] is changed from the potential HTX\_[nm1] to the potential LTX\_[nm1] and the potential of the wiring TX\_[nm2] is changed from the potential HTX\_[nm2] to the potential LTX\_[nm2], so that the transistor 211 is turned off. Accordingly, the movement of charge from the node FD\_[n] and the node FD\_[n+1] to the photodiode 207 is stopped; thus, the potentials of the node FD\_[n] and the node FD\_[n+1] are determined. A period from the time T2 to the time T3 is called "exposure period 301" and an operation during the exposure period 301 is called "accumulation operation"

Next, at a time T4, the potential of the wiring SE\_[1] connected to the photosensor 205 of the pixel in the first row is changed from the potential LSE\_[1] to the potential HSE [1], so that the transistor 217 included in the photosensor 205 of the pixel in the first row is turned on. Then, depending on the potential of the node FD [1](not shown) in the photosensor 205 in the first row, charge is moved from the wiring VR\_[m] to the wiring OUT\_[m].

Next, at a time T5, the potential of the wiring SE [1] is Next, at a time T2, the potential of the wiring PR\_[m] is 35 changed from the potential HSE\_[1] to the potential LSE\_ [1], so that the movement of charge from the wiring VR\_[m] to the wiring OUT\_[m] in the pixel in the first row is stopped and the potential of the wiring OUT\_[m] in the pixel in the first row is determined. The potential of the wiring OUT\_ [m] in the pixel in the first row corresponds to the potential of the output signal of the photosensor 205 of the pixel in the first row and the m-th column. In addition, the potential of the output signal contains object image data generated by the pixel in the first row and the m-th column. A period from the time T4 to the time T5 is called "readout period 302" and an operation during the readout period 302 is called "read operation". The timing of when the wiring SE [1] is subjected to the read operation can be determined as appropriate.

> From the time T5, the wirings SE\_[2] to SE\_[n+1] are also subjected to the read operation in sequence, so that the potential of the wiring OUT\_[m] is determined in sequence as shown in FIG. 4. The potential of the wiring OUT\_[m] determined in sequence corresponds to the potential of an output signal of the photosensor 205 of the pixel in the m-th column. The potential of the output signal contains object image data generated by the pixel in the m-th column.

> The above-described series of operations includes a reset operation, an accumulation operation, and a read operation. In other words, object image data can be obtained by performing the reset operation, the accumulation operation, and the read operation on the pixels in all the columns.

> In the global shutter method, all the pixels are subjected to the reset operation and the accumulation operation at a time, so that the wirings TX for the pixels in all the columns change in potential at a time in the same manner as the wiring TX\_[nm1] and the wiring TX\_[nm2].

A period between the end of the accumulation operation and the start of the read operation, during which charge is held at the nodes FD in the pixels in each column, is called "charge holding period". In the global shutter method, all the pixels are subjected to the reset operation and the accumulation operation at a time; therefore, the timing of the end of the exposure period is the same in all the pixels; however, the pixels are sequentially subjected to the read operation row by row, so that the length of the charge holding period varies from one row to another. For example, the charge 10 holding period for the pixels in the first row is between the time T3 and the time T4, and the charge holding period for the pixels in the second row is between the time T3 and the time T5. The read operation is performed row by row; therefore, the timing of when the readout period is started 15 varies from one row to another. Thus, the length of the charge holding period for the photosensors in the pixels in the last row is the longest.

When an image of a uniform grayscale level is obtained, the photosensors in all the pixels ideally provide output 20 signals having potentials of the same level. However, in the case where the length of the charge holding period varies from one pixel row to another, if charge accumulated at the nodes FD in the pixels in each row leaks out over time, the potential of an output signal of a photosensor varies from 25 one row to another, and image data varies in grayscale level from one row to another.

However, in one embodiment of the present invention, the transistor **211** with significantly small off-state current can be used as a switching element for holding charge accumulated in the photosensor **205**, specifically, charge accumulated at the node FD. In that case, even when an image is taken by the global shutter method, it is possible to suppress variations in the grayscale level of image data due to variations in the length of the charge holding period, and it 35 is possible to improve the quality of an image.

Note that the driving method according to the timing chart in FIG. **4** is a general global shutter method, and thus is called "normal GS driving method".

In the case where the normal GS driving method is 40 performed using the circuit configuration illustrated in FIGS. 2A and 2B and FIGS. 3A and 3B, it is possible that image data of the n-th row and image data of the (n+1)-th row are mixed; however, the mixing of these image data can be prevented because the transistor 213 has extremely low 45 off-state current density.

In the case of imaging using the normal GS driving method, when the luminance of external light is low and the intensity of light entering the photodiode of each pixel is low, the amount of charge flowing out from the node FD 50 during the accumulation operation is small and a change in the potential of the node FD is small. The change can be increased by extending the exposure period; however, extending the exposure period may result in a reduction in the quality of an image, for example, obtainment of data of 55 a distorted image of an object.

By using the pixel configuration illustrated in FIGS. **2**A and **2**B and FIGS. **3**A and **3**B, a driving method that suppresses such possibility can be performed. A description will be now given of a driving method according to one 60 embodiment of the present invention, which is different from the normal GS driving method.

Specifically, in this driving method, the transistor **215** illustrated in FIGS. **2**A and **2**B and FIGS. **3**A and **3**B is turned on and electrical continuity between the photosensor 65 of the pixel in the n-th row and the photosensor of the pixel in the (n+1)-th row is established, so that a region of a

photodiode which light enters is increased and a change in the potential of the node FD (specifically, the node FD\_[n]) is increased without extending the exposure period.

Since electrical continuity between the photosensor of the pixel in the n-th row and the photosensor of the pixel in the (n+1)-th row is established, the resolution of obtained data of an image of an object is lower than that obtained in the case where such electrical continuity is not established. However, the driving method described below is preferable because, in the environment where the luminance of external light is low, imaging in which the resolution is reduced and the exposure period is not extended results in higher quality of an image than imaging in which the exposure period is extended. Note that the driving method described below is called "light-entrance-region-increasing GS driving method" such that it is distinguished from the normal GS driving method.

Like the normal GS driving method, the light-entranceregion-increasing GS driving method according to one embodiment of the present invention is described taking the pixels in the m-th column in the pixel portion **101** as an example. FIG. **5** is an example of a timing chart showing potentials applied to the wiring TX\_[nm1], the wiring TX\_ [nm2], the wirings SE\_[1] to SE\_[n+1], the wiring PA\_[m], the wiring PR\_[m], the wiring VR\_[m], and the wiring OUT\_[m] in the light-entrance-region-increasing GS driving method. FIG. **5** also shows the potentials of the node FD\_[n] and the node FD\_[n+1].

The light-entrance-region-increasing GS driving method is different from the driving method according to the timing chart of FIG. **4** in potentials applied to the wiring TX\_[nm2] and the wiring PA\_[m] and the potentials of the node FD\_[n] and the wiring OUT\_[m]. Here, the light-entrance-regionincreasing GS driving method is described with reference to the description of the normal GS driving method.

In the light-entrance-region-increasing GS driving method, in order to establish electrical continuity between the photosensor of the pixel in the n-th row and the photosensor of the pixel in the (n+1)-th row, the potential LTX\_[nm2] is always applied to the wiring TX\_[nm2]. Therefore, the node FD\_[n+1] is always at a low level.

First, the reset period **300** is described. At a time T1, the potential of the wiring PR\_[m] is changed from the potential LPR\_[m] to the potential HPR\_[m]. Further, only the wiring TX\_[nm1] for the photosensor of the pixel in the n-th row is changed from the potential LTX\_[nm1] to the potential HTX\_[nm1]. Accordingly, only the transistor **211** in the photosensor of the pixel in the n-th row is turned on. At the time T1, the potential LSE\_[1] to LSE\_[n+1] are applied to the wirings SE\_[1] to SE\_[n+1], respectively.

Next, at a time T2, the potential of the wiring PR\_[m] is changed from the potential HPR\_[m] to the potential LPR\_ [m]. At the time T2, the potential of the wiring TX\_[nm1] is kept at the potential HTX\_[nm1], and the potentials of the wirings SE\_[1] to SE\_[n+1] are kept at the potentials LSE\_[1] to LSE\_[n+1], respectively. Accordingly, the node FD\_[n] is supplied with the potential HPR\_[m]; thus, the amount of charge held at the node FD\_[n] is reset.

Here, for simplicity, the potential of the wiring PR\_[m] and the potential of the wiring TX\_[nm1] are changed at the time T1. However, it is acceptable that the potential of the wiring TX\_[nm1] is changed before the potential of the wiring PR\_[m] is changed. By turning on the transistor **211** before the potential of the wiring PR\_[m] is changed, the node FD\_[n] can be reset completely.

Although not illustrated in FIG. **5**, not only the amount of charge held at the node FD\_[n] but also the amount of charge

held at the nodes FD in the photosensors of the pixels in the m-th column and odd-numbered rows (e.g., the node FD\_[1] and the node FD\_[3]) are reset.

Next, the exposure period **301** is described. At the time T2, the potential of the wiring PR\_[m] is changed to the potential LPR\_[m]. Further, at the time T2, after the potential of the wiring PR\_[m] is changed, the potential of the wiring PA\_[m] is changed from the potential LPA\_[m] to the potential HPA\_[m]. Consequently, the transistor **213** is turned on, so that electrical continuity between the photosensor of the pixel in the n-th row and the photosensor of the pixel in the (n+1)-th row are connected in parallel. This produces the same effect as that produced by increasing a region of a photodiode which light enters, thereby increasing the amount of charge flowing out during a certain period from the node FD\_[n] reset.

At the time T3, the potential of the wiring TX\_[nm1] is 20 Thus, it is possible to suppress variations in the grayscale level of image data due to variations in the length of the charge holding period, and it is possible to improve the quality of an image. As described above, the solid-state imaging device 100 according to one embodiment of the present invention can employ the normal GS driving method and the light-entrance-region-increasing GS driving method in combination. For example, when the luminance of external light is high,

Next, the readout period **302** is described. From the time T4, the driving method is performed according to the timing 30 chart of FIG. **5** in the same manner as that indicated with the timing chart of FIG. **4**. The wirings SE\_[1] to SE\_[n+1] are subjected in sequence to the operation performed during the readout period **302**, so that the potential of the wiring OUT\_[m] is determined in sequence as shown in FIG. **5**. The 35 potential of the wiring OUT\_[m] determined in sequence corresponds to the potential of an output signal of the photosensor **205** of the pixel in the m-th column. The potential of the output signal contains object image data generated by the pixel in the m-th column.

Note that in the pixel in the n-th row, as in the normal GS driving method, the potential of the wiring OUT\_[m] in the pixel in the n-th row is determined. This potential contains image data generated by the pixel in the m-th column. Since in the pixel in the (n+1)-th row, the wiring TX\_[nm2] is 45 always at the potential LTX\_[nm2], the potential of the wiring OUT\_[m] in the (n+1)-th row is not changed even when the wiring SE\_[n+1] is changed to the potential HSE\_[n+1]. Therefore, the potential of the output signal is not output.

However, according to the timing chart of FIG. **5**, the wirings SE\_[1] to SE\_[n+1] are subjected in sequence to the operation performed during the readout period **302**; therefore, it is possible that the potential of the wiring OUT\_[m] for the pixel in the (n+1)-th row slightly changes. In other 55 words, it is possible that an output signal with a potential lower than the potential of the output signal of the n-th row is output from the (n+1)-th row; in such a case, image data corresponding to the potential of an output signal of the pixel in the n-th row is removed. For example, the data processing 60 circuit **107** in the solid-state imaging device **100** (see FIG. **1**A) is provided with a circuit for removing such image data. The timing of when the wiring SE\_[1] is subjected to the read operation can be determined as appropriate.

Object image data can be obtained by performing the reset 65 operation, the accumulation operation, and the read operation on the pixels in all the columns.

The light-entrance-region-increasing GS driving method employs the global shutter method like the normal GS driving method. Therefore, the length of the charge holding period varies from one row to another. Thus, the length of the charge holding period for the photosensors of the pixels in the last row is the longest. When an image of a uniform grayscale level is obtained, the photosensors in all the pixels ideally provide output signals having potentials of the same level. However, also in the light-entrance-region-increasing GS, in the case where the length of the charge holding period varies from one pixel row to another, if charge accumulated at the nodes FD in the pixels in each row leaks out over time, the potential of an output signal of a photosensor varies from one row to another, and image data varies in grayscale level from one row to another.

In view of the above problem, the transistor **211** with significantly small off-state current can be used as a switching element for holding charge accumulated in the photosensor **205**, specifically, charge accumulated at the node FD. Thus, it is possible to suppress variations in the grayscale level of image data due to variations in the length of the charge holding period, and it is possible to improve the quality of an image.

As described above, the solid-state imaging device **100** according to one embodiment of the present invention can employ the normal GS driving method and the light-entrance-region-increasing GS driving method in combination. For example, when the luminance of external light is high, the normal GS driving method is employed to determine, after imaging, whether image contains much data representing black (whether the imaging has been conducted in the dark) with the data processing circuit **107**. When it is determined that the image data contains much data representing black (whether the imaging has been conducted in the dark), the driving method can be switched to the light-entrance-region-increasing GS driving method. Note that the switching can be performed either automatically with the data processing circuit **107** or by a user.

The solid-state imaging device **100** according to one 40 embodiment of the present invention has the circuit configuration illustrated in FIGS. **2**A and **2**B and FIGS. **3**A and **3**B, enables adjustment of the exposure period, is capable of employing the normal GS driving method and the lightentrance-region-increasing GS driving method in combina-45 tion, and has improved dynamic range.

In FIGS. 2A and 2B and FIGS. 3A and 3B, in a group of the pixels in the same column, a photodiode of a pixel in one row and a photodiode of a pixel in the next row are connected to each other with a transistor (a switching element). In the solid-state imaging device 100 according to one embodiment of the present invention, the number of photodiodes connected to each other can be determined as appropriate. For example, in a pixel group in the same column, either three or four rows of photodiodes can be connected to one another.

Since the solid-state imaging device **100** according to one embodiment of the present invention can employ the normal GS driving method and the light-entrance-region-increasing GS driving method in combination, it is acceptable that only part of the region of the pixel portion **101** is operated by the light-entrance-region-increasing GS driving method, and the other region is operated by the normal GS driving method.

In the solid-state imaging device **100** according to one embodiment of the present invention, a plurality of pixels arranged in a matrix in the pixel portion **101** is provided with color filters. The arrangement and shape of the color filters are not particularly limited. For example, the color filters may have a rectangular shape as illustrated in FIG. **6**A or a diamond shape as illustrated in FIG. **6**B. Note that the arrangement and shape of wirings in the plurality of pixels and wirings in the photosensors of each pixel are changed as appropriate according to the arrangement and shape of the <sup>5</sup> color filters.

The solid-state imaging device **100** according to one embodiment of the present invention may perform imaging by using external light or by sequential emission of at least red light, blue light, and green light to obtain color image <sup>10</sup> data. By sequential emission of these lights, a plurality of pieces of image data corresponding to a plurality of colors can be obtained. Color image data can be obtained by addictive color mixture using the plurality of pieces of image data. <sup>15</sup>

Sequential emission of these lights eliminates the need for providing each pixel with color filters. By increasing the use efficiency of these lights, the power consumption of the solid-state imaging device can be reduced. Further, since image data corresponding to a plurality of colors can be 20 obtained or the grayscale levels of a plurality of colors can be produced with one pixel, high-definition image data can be obtained.

In the solid-state imaging device **100** according to one embodiment of the present invention, when light enters the <sup>25</sup> photodiode of the photosensor, an output signal generated from the light is output. Thus, the solid-state imaging device **100** can be operated utilizing not only visible light but also light with various wavelengths (e.g., infrared rays, ultraviolet rays, and X rays). For example, a solid-state imaging <sup>30</sup> device can utilize X rays when provided with a layer with which X rays can be converted into visible light, such as a phosphor.

This embodiment can be implemented in appropriate combination with any of the structures described in the other <sup>35</sup> embodiments.

## Embodiment 2

This embodiment describes the case where the solid-state 40 imaging device **100** employs the rolling shutter method.

The rolling shutter method is different from the global shutter method described in Embodiment 1 in that the potentials applied to the wirings PR for respective rows are sequentially varied; therefore, the wirings PR are indepen-45 dently provided for the respective rows. FIG. **7** illustrates an example of a circuit diagram of the pixel portion **101**. FIG. **7** illustrates the pixels in the n-th row and the (n+1)-th row.

In the case where the rolling shutter method is employed, the potentials applied to the wirings PR for respective rows 50 are sequentially varied; therefore, the solid-state imaging device **100** in FIG. **1**A to which a horizontal reset circuit is added is used. The horizontal reset circuit is connected to the wiring PR in each row and includes at least a logic circuit unit, a switch unit, or a buffer unit, like the horizontal 55 selection circuit **103**, the data output circuit **105**, and the data processing circuit **107**. The horizontal reset circuit can be formed over the same substrate as the pixel portion **101**. Alternatively, the horizontal reset circuit may be partly or fully implemented in a semiconductor device such as an IC. 60

Note that when the rolling shutter method is employed, the charge holding period described in Embodiment 1 is not used. Therefore, in the circuit configuration in FIG. 7, the transistor 211 is not necessarily provided in the amplifier circuit 209 as long as the amplifier circuit 209 amplifies 65 current generated by the photodiode 207. When the transistor 211 is not provided, the photosensors and the pixels can

be miniaturized, so that the solid-state imaging device can be miniaturized and manufacturing cost can be reduced.

FIG. 8 is a circuit diagram showing the case where the photosensors 205 and 206 in FIG. 7 having the same structure as the photosensor 205 in FIG. 3A are used. Note that FIG. 8 illustrates pixels in the n-th and (n+1)-th rows of the m-th column.

The wirings PR are independently provided for the respective rows as described above, so that the anode of the photodiode **207** of the photosensor **205** in the n-th row is connected to a wiring PR\_[n] among the wirings PR. The anode of the photodiode **207** of the photosensor **206** in the (n+1)-th row is connected to a wiring PR\_[n+1] among the wirings PR. Thus, when the rolling shutter method is employed, the wiring PR\_[n] and the wiring PR\_[n+1] are used instead of the wiring PR\_[m] in FIG. **3**B.

Next, a method for driving the pixel portion **101** by the rolling shutter method is described. FIG. **9** is an example of a timing chart showing potentials applied to the wiring  $TX_{[nm1]}$ , the wiring  $TX_{[nm2]}$ , the wiring  $PA_{[m]}$ , the wiring  $VR_{[m]}$ , and the wiring OUT\_[m] for the pixels in the m-th column in the pixel portion **101**. FIG. **9** is also an example of a timing chart showing potentials applied to the wirings  $SE_{[1]}$  to  $SE_{[n+1]}$  and the wirings  $PR_{[1]}$  to  $PR_{[n+1]}$  for the pixels in rows in the pixel portion **101**. FIG. **9** shows the potentials of the node  $FD_{[n]}$  and the node  $FD_{[n+1]}$ .

It is assumed that, in the timing chart shown in this embodiment, high or low level potentials are applied to the wirings as in Embodiment 1. This embodiment is different from Embodiment 1 in that the wirings PR\_[1] to PR\_[n+1] are supplied with high level potentials HPR\_[1] to HPR\_[n+1], respectively, and low level potentials LPR\_[1] to LPR\_[n+1], respectively. The potentials supplied to the other wirings are the same as those in Embodiment 1. The VR\_[m] is assumed to be supplied with VDD, which is not shown in FIG. **9**.

FIG. 9 is a timing chart of the driving method in a condition where there is no electrical continuity between the photodiode 207 in the photosensor 205 in the n-th row and the photodiode 207 in the photosensor 206 in the (n+1)-th row, that is, a condition where the transistor 213 is in the off state. In the driving method, the wiring PA\_[m] is always at a potential LPA\_[m]. Since the rolling shutter method is employed, the wirings TX\_[nm1] and TX\_[nm2] are always at potentials HTX\_[nm1] and HTX\_[nm2], respectively. Therefore, the transistor 211 in the photosensor 205 of the pixel in the n-th row and the transistor 211 in the photosensor 206 of the pixel in the (n+1)-th row are always in the on state.

First, at the time T1, the potential of the wiring PR\_[1] is changed from the potential LPR\_[1] to the potential HPR\_[1]. Further, at the time T1, low level potentials are supplied to the other wirings.

Next, at the time T2, the potential of the wiring PR\_[1] is changed to the potential HPR\_[1]. A period from the time T1 to the time T2 corresponds to the reset period **300** described in Embodiment 1. However, since the rolling shutter method is employed, unlike in the global shutter method shown in Embodiment 1, the rows are sequentially subjected to a reset operation in the reset period **300**. Thus, the potential of the wiring PR\_[2] is changed from the potential LPR\_[2] to the potential HPR\_[2] at the time T2 and the potential of the wiring PR\_[2] is changed from the potential HPR\_[2] to the potential LPR\_[2] at the time T3 to subject the photosensors

in the second row to a reset operation. Note that at the time T2 and the time T3, low level potentials are supplied to the other wirings.

FIG. 9 shows the timing of when the photosensor 205 in the n-th row and the photosensor 206 in the (n+1)-th row are 5 subjected to a reset operation when the sequential reset operation is performed.

Here, at the time T2, the potential of the wiring PR\_[1] is changed to the potential LPR\_[1], so that a reverse bias voltage is applied to the photodiode 207 in the first row. As 10 described in Embodiment 1, when light enters the photodiode 207, current flows from the cathode of the photodiode 207 toward the anode thereof. This current determines the potential of the node FD\_[1](not shown) of the photosensor 205 in the first row. Note that, as described in Embodiment 15 1, the higher the intensity of light entering the node FD\_[1] becomes, the larger the amount of change in the potential of the node FD\_[1] becomes; the lower the intensity of light entering the node FD\_[1] becomes, the smaller the amount of change in the potential of the node FD [1] becomes.

Next, at the time T4, the potential of the wiring SE\_[1] connected to the photosensors 205 of the pixels in the first row is changed from the potential LSE\_[1] to the potential HSE\_[1], so that the transistors 217 included in the photosensors 205 of the pixels in the first row are turned on. Then, 25 depending on the potentials of the node FD\_[1], charge is moved from the wiring VR\_[m] to the wiring OUT\_[m].

Since the wirings TX\_[nm1] and TX\_[nm2] are always at potentials HTX\_[nm1] and HTX\_[nm2], respectively, changing the potential of the wiring SE\_[1] from the poten- 30 tial LSE\_[1] to the potential HSE\_[1] determines the potential of the node FD\_[1]. Therefore, the exposure period 301 for the photosensor 205 in the first row corresponds to a period from the time T2 to the time T4, and the operation during the exposure period 301 is an accumulation opera- 35 illustrated in FIG. 7 and FIG. 8, a driving method that tion.

Next, at the time T5, the potential of the wiring SE [1] is changed from the potential HSE\_[1] to the potential LSE\_ [1], so that the movement of charge from the wiring VR\_[m] to the wiring OUT\_[m] in the pixel in the first row is stopped 40 and the potential of the wiring OUT\_[m] in the pixel in the first row is determined. The potential of the wiring OUT\_ [m] in the pixel in the first row corresponds to the potential of the output signal of the photosensor 205 of the pixel in the first row and the m-th column. In addition, the potential of 45 the output signal contains object image data generated by the pixel in the first row and the m-th column. The readout period 302 for the photosensor 205 in the first row corresponds to a period from the time T4 to the time T5, and the operation during the readout period 302 is referred to as a 50 read operation. The timing of when the wiring SE\_[1] is subjected to the read operation can be determined as appropriate.

From the time T5, the wirings SE\_[2] to SE\_[n+1] are also subjected to the read operation in sequence, so that the 55 potential of the wiring OUT\_[m] is determined in sequence as shown in FIG. 9. The potential of the wiring OUT\_[m] determined in sequence corresponds to the potential of an output signal of the photosensor 205 of the pixel in the m-th column. The potential of the output signal contains object 60 image data generated by the pixel in the m-th column.

From the time T1, the wirings PR\_[2] to PR\_[n+1] are subjected to the reset operation in sequence. From the time T5, the wirings SE\_[2] to SE\_[n+1] are also subjected to the read operation in sequence. Therefore, in a normal RS driving method, the exposure period 301 for the photosensor 206 in the (n+1)-th row corresponds to a period from the

time at which the potential of the PR\_[n+1] is changed from the potential HPR [n+1] to the potential LPR [n+1] to the time at which the potential of the wiring SE\_[n+1] is changed from the potential LSE [n+1] to the potential HSE\_[n+1].

Further, since the wirings TX\_[nm1] and TX\_[nm2] are always at the potentials HTX\_[nm1] and HTX\_[nm2], respectively, the potentials of the nodes FD\_[n] and FD\_ [n+1] decrease until the reset operation for the photosensor 205 in the n-th row and the photosensor 206 in the (n+1)-th row is performed again.

Object image data can be obtained by performing the reset operation, the accumulation operation, and the read operation on the pixels in all the columns.

Note that the driving method according to the timing chart in FIG. 9 is a general rolling shutter method, and thus is called "normal RS driving method".

In the case where the normal RS driving method is performed using the circuit configuration illustrated in FIG. 20 7 and FIG. 8, it is possible that image data of the n-th row and image data of the (n+1)-th row are mixed; however, the mixing of these image data can be prevented because the transistor 213 has significantly small off-state current.

In the case where the normal RS driving method is employed, when the luminance of external light is low and the intensity of light entering the photodiode of each pixel is low, the amount of charge flowing out from the node FD during the accumulation operation is small and a change in the potential of the node FD is small. The change can be increased by extending the exposure period; however, extending the exposure period may result in a reduction in the quality of an image, for example, obtainment of data of a distorted image of an object.

Like in Embodiment 1, by using the pixel configuration suppresses such possibility can be performed. A description will be now given of a driving method according to one embodiment of the present invention, which is different from the normal RS driving method.