US009859393B2

### (12) United States Patent

### Tak et al.

#### (54) INTEGRATED CIRCUIT DEVICE AND METHOD OF FABRICATING THE SAME

- (71) Applicant: Samsung Electronics Co., Ltd., Suwon-si (KR)

- (72) Inventors: Yong-suk Tak, Seoul (KR); Tae-jong Lee, Hwaseong-si (KR); Hyun-seung Kim, Bucheon-si (KR); Bon-young Koo, Suwon-si (KR); Ki-yeon Park, Hwaseong-si (KR); Gi-gwan Park, Hwaseong-si (KR); Mi-seon Park, Daegu (KR)

- (73) Assignee: SAMSUNG ELECTRONICS CO., LTD., Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do (KR)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 15/401,659

- (22) Filed: Jan. 9, 2017

#### (65) **Prior Publication Data**

US 2017/0222014 A1 Aug. 3, 2017

#### (30) Foreign Application Priority Data

Feb. 1, 2016 (KR) ..... 10-2016-0012452

(51) Int. Cl.

| <i>H01L 29/76</i> | (2006.01)   |

|-------------------|-------------|

| H01L 29/49        | (2006.01)   |

|                   | (Continued) |

(52) U.S. Cl.

CPC .... H01L 29/4983 (2013.01); H01L 21/76805 (2013.01); H01L 21/76843 (2013.01); H01L 21/76895 (2013.01); H01L 23/535 (2013.01);

### (10) Patent No.: US 9,859,393 B2

### (45) **Date of Patent:** Jan. 2, 2018

*H01L 23/5329* (2013.01); *H01L 21/823475* (2013.01); *H01L 29/7855* (2013.01); *H01L 29/7856* (2013.01); *H01L 29/7856* (2013.01)

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

8,586,487 B2 11/2013 Nguyen et al. 8,962,454 B2 2/2015 Takaba (Continued)

#### FOREIGN PATENT DOCUMENTS

| JP | 08-153786   | 6/1996  |

|----|-------------|---------|

| JP | 2011-171623 | 9/2011  |

| KR | 10-0772703  | 11/2007 |

Primary Examiner — David Vu

Assistant Examiner — Brandon Fox

(74) Attorney, Agent, or Firm - Muir Patent Law, PLLC

### (57) **ABSTRACT**

A device includes: a gate line on an active region of a substrate, a pair of source/drain regions in the active region on both sides of the gate line, a contact plug on at least one source/drain region out of the pair of source/drain regions; and a multilayer-structured insulating spacer between the gate line and the contact plug. The multilayer-structured insulating insulating layer covering a first surface of the oxide layer, adjacent to the gate line, and a second carbon-containing insulating layer covering a second surface of the oxide layer, opposite to the first surface of the oxide layer, adjacent to the contact plug.

#### 20 Claims, 41 Drawing Sheets

(51) Int. Cl.

| H01L 23/535  | (2006.01) |

|--------------|-----------|

| H01L 21/768  | (2006.01) |

| H01L 23/532  | (2006.01) |

| H01L 29/78   | (2006.01) |

| H01L 21/8234 | (2006.01) |

#### (56) **References** Cited

### U.S. PATENT DOCUMENTS

| 9,040,411    | B2     | 5/2015  | Grill et al.          |

|--------------|--------|---------|-----------------------|

| 9,117,664    |        | 8/2015  | Zhou                  |

| 9,184,046    |        | 11/2015 | Takeda et al.         |

| 9,196,542    | B2     | 11/2015 | Wang et al.           |

| 2009/0191706 | A1     | 7/2009  | Kubota                |

| 2015/0118865 | A1     | 4/2015  | Shimizu               |

| 2015/0243544 | A1 $*$ | 8/2015  | Alptekin H01L 21/7682 |

|              |        |         | 438/586               |

| 2015/0249036 | A1     | 9/2015  | Cai et al.            |

| 2015/0262876 | A1     | 9/2015  | Yang et al.           |

| 2016/0141381 | A1*    | 5/2016  | Kim H01L 29/66545     |

|              |        |         | 257/288               |

| 2016/0372567 | A1*    | 12/2016 | Tak H01L 29/6656      |

|              |        |         |                       |

\* cited by examiner

# FIG. 1A

## FIG. 1B

FIG. 3B

<u>200</u>

FIG. 4A

## FIG. 6A

FIG. 6B

FIG. 9B

<u>700</u>

# FIG. 10A

FIG. 10B

FIG. 11A

FIG. 12A

FIG. 12B

FIG. 13A

FIG. 13B

## FIG. 14A

FIG. 14B

FIG. 15A

FIG. 15B

FIG. 16A

## FIG. 17A

FIG. 17B

## FIG. 18A

# FIG. 19A

# FIG. 20A

# FIG. 20B

# FIG. 21A

FIG. 21B

FIG. 22

## INTEGRATED CIRCUIT DEVICE AND METHOD OF FABRICATING THE SAME

#### CROSS-REFERENCE TO RELATED APPLICATION

This application claims the benefit of priority under 35 U.S.C. §119 to Korean Patent Application No. 10-2016-0012452, filed on Feb. 1, 2016, in the Korean Intellectual Property Office, the disclosure of which is incorporated <sup>10</sup> herein in its entirety by reference.

## BACKGROUND

The present disclosure relates to an integrated circuit <sup>15</sup> device and a method of fabricating the same, and more particularly, to an integrated circuit device including a field effect transistor and to a method of fabricating the same.

In the rapidly developing electronics industry, demand for a high speed, high reliability and a multi-functional ability <sup>20</sup> has been increasing for semiconductor devices. In order to meet this demand, the structure of semiconductor devices has been getting more complex and the size of the semiconductor devices has been highly miniaturized. Recently, since semiconductor devices require fast operation speeds <sup>25</sup> and operation accuracy as well, various studies for optimizing structures of transistors included in the semiconductor devices are being carried out. In particular, as a gate length is increasingly reduced, etch resistance of layers for electrically insulating a gate line has an increasing influence on <sup>30</sup> leakage current properties.

#### SUMMARY

The inventive concept provides an integrated circuit 35 device having a structure capable of realizing optimal reliability and performance in a highly down-scaled transistor by providing required etch resistance during a fabrication process of an integrated circuit device.

The inventive concept also provides a method of fabri- 40 cating an integrated circuit device capable of realizing optimal reliability and performance in a highly down-scaled transistor by providing required etch resistance during a fabrication process of the integrated circuit device.

According to an aspect of the inventive concept, there is 45 provided a device including: a gate line on an active region of a substrate; a pair of source/drain regions in the active region on both sides of the gate line; a contact plug on at least one source/drain region out of the pair of source/drain regions; and a multilayer-structured insulating spacer 50 between the gate line and the contact plug, wherein the multilayer-structured insulating spacer comprises: an oxide layer; a first carbon-containing insulating layer covering a first surface of the oxide layer adjacent to the gate line; and a second carbon-containing insulating layer covering a sec- 55 ond surface of the oxide layer, opposite to the first surface of the oxide layer, adjacent to the contact plug, and wherein the first carbon-containing insulating layer and the second carbon-containing insulating layer have different carbon contents. 60

According to a further aspect of the inventive concept, there is provided a device including: a gate insulating spacer on a substrate, the gate insulating spacer including a first carbon-containing insulating layer; a gate line in a space defined by the gate insulating spacer; an oxide layer cover-55 ing a sidewall of the gate line, with the gate insulating spacer being interposed between the oxide layer and the gate line; 2

a contact hole on one side of the gate line, the contact hole penetrating the oxide layer and exposing an active region of the substrate; a contact insulating spacer in the contact hole, the contact insulating spacer including a second carboncontaining insulating layer having different carbon content from that of the first carbon-containing insulating layer; and a contact plug in the contact hole, the contact plug being surrounded by the contact insulating spacer.

According to a further aspect of the inventive concept, there is provided a device including: a gate line on an active region of a substrate; a pair of source/drain regions in the active region on both sides of the gate line; a contact plug on at least one source/drain region out of the pair of source/ drain regions; an oxide layer between the gate line and the contact plug; a first carbon-containing insulating layer covering a first sidewall of the oxide layer adjacent to the gate line; and a second carbon-containing insulating layer covering a second sidewall of the oxide layer, opposite to the first sidewall of the oxide layer, opposite to the first sidewall of the oxide layer, adjacent to the contact plug, wherein the first carbon-containing insulating layer and the second carbon-containing insulating layer have different carbon contents.

The integrated circuit device fabricated according to the inventive concept includes the multilayer-structured insulating spacer between the gate line and the contact plug. The multilayer-structured insulating spacer has a carbon content optimized to provide etch resistance sufficient to prevent an electrical short circuit between the gate line and the contact plug. Therefore, the multilayer-structured insulating spacer between the gate line and the contact plug can provide a sufficiently low dielectric constant and can prevent the occurrence of leakage currents between the gate line and the contact plug.

## BRIEF DESCRIPTION OF THE DRAWINGS

Embodiments of the inventive concept will be more clearly understood from the following detailed description taken in conjunction with the accompanying drawings in which:

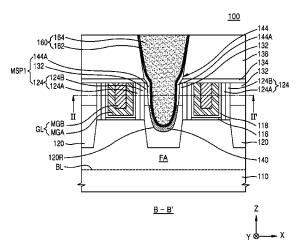

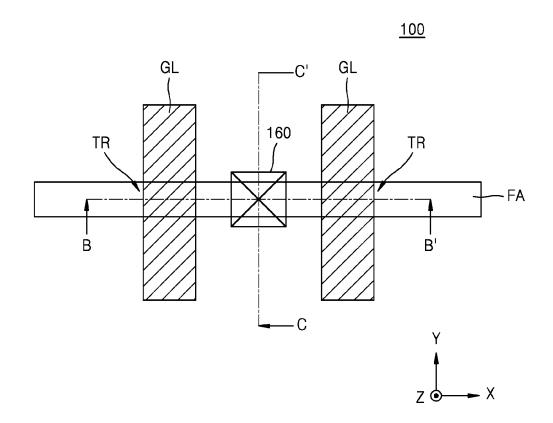

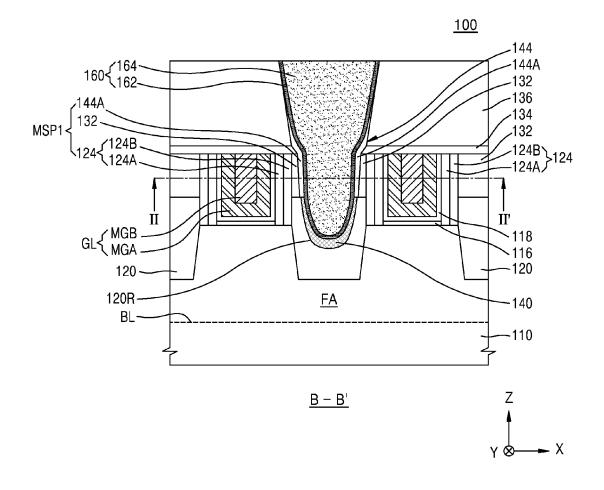

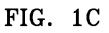

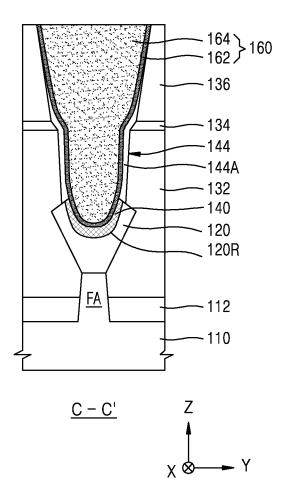

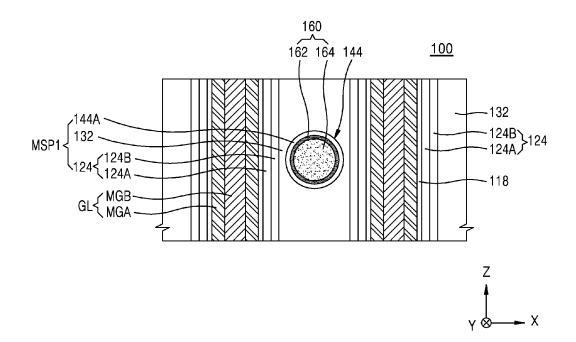

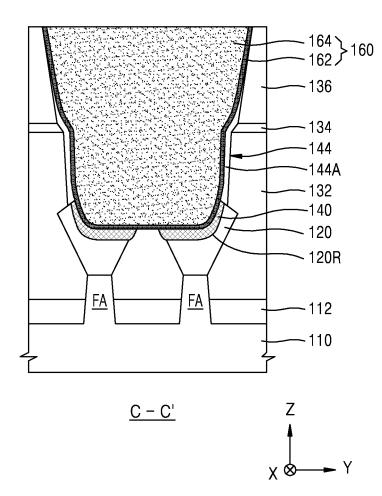

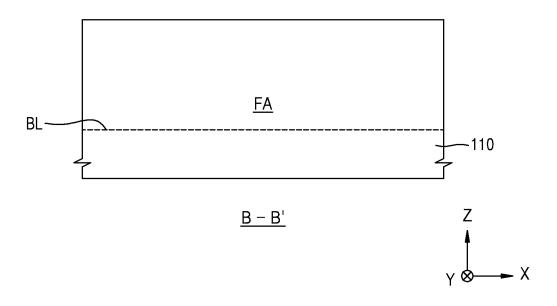

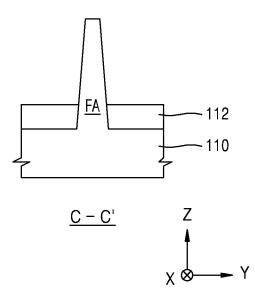

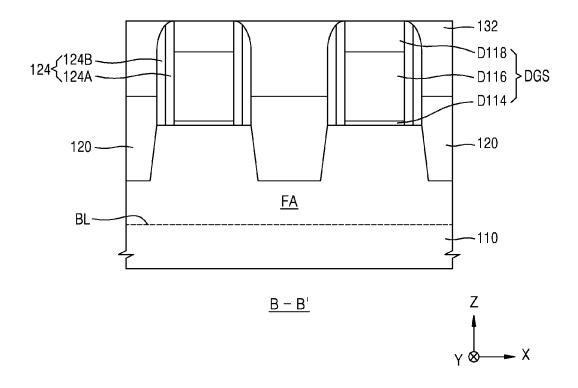

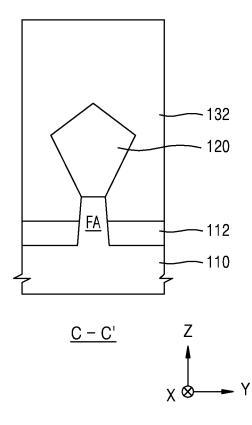

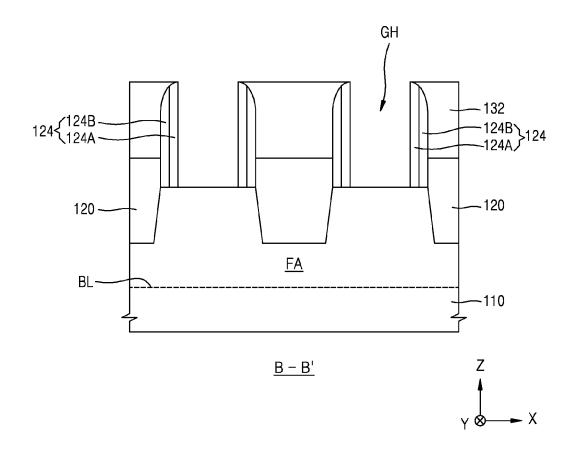

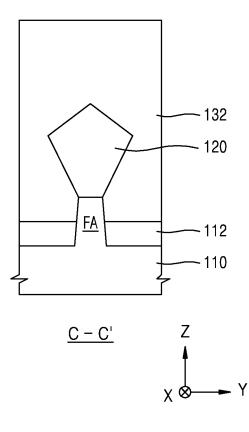

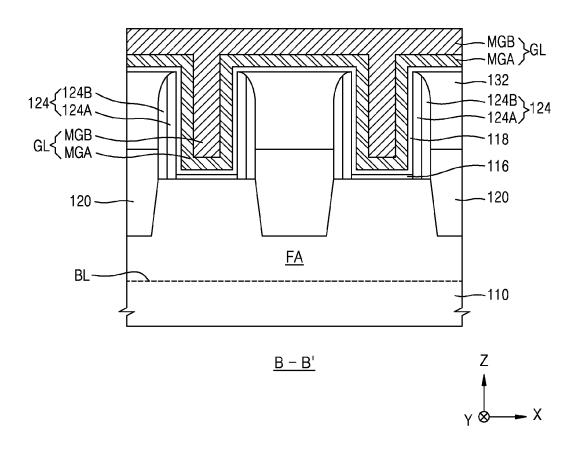

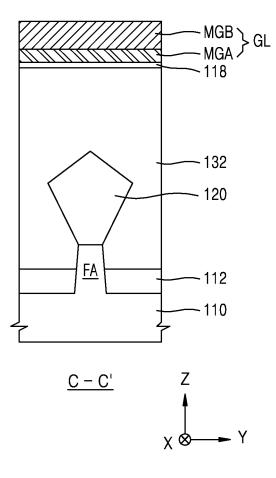

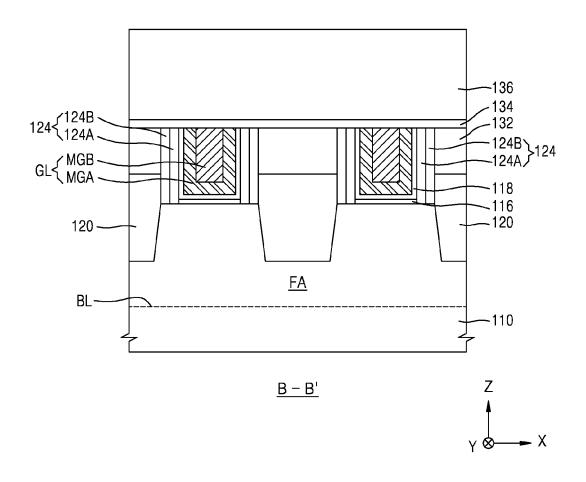

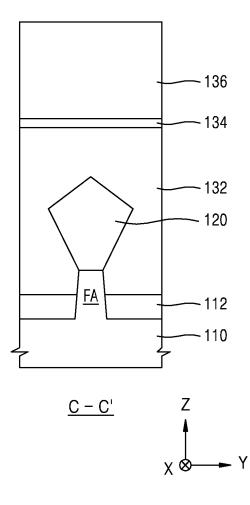

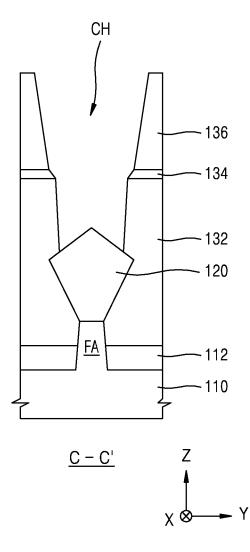

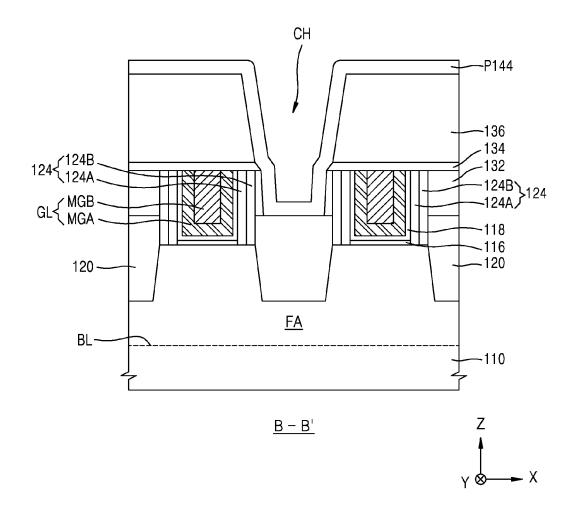

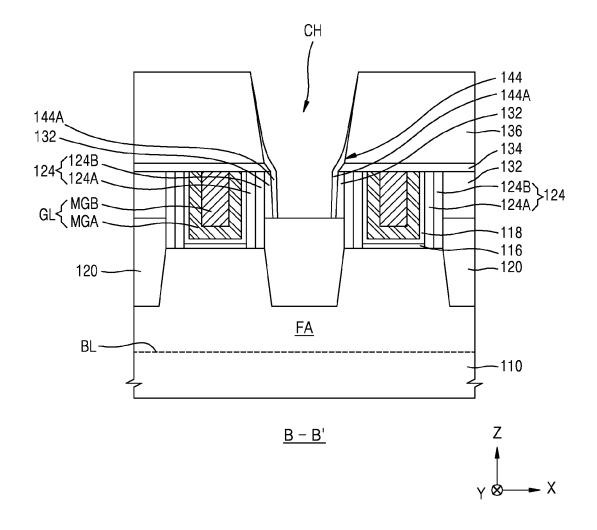

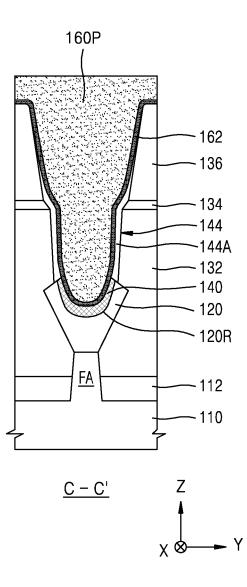

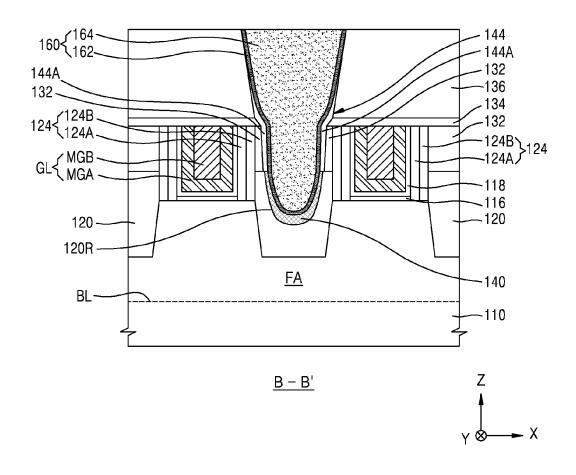

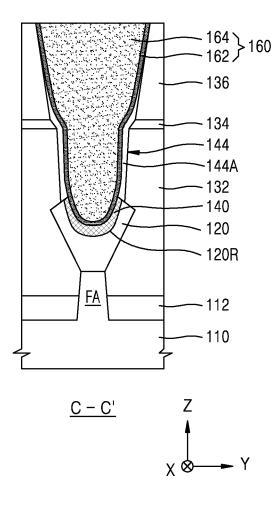

FIGS. 1A to 1C are diagrams for explaining an integrated circuit device according to exemplary embodiments, FIG. 1A is a layout diagram of the integrated circuit device, FIG. 1B is a cross-sectional view of the integrated circuit device taken along a line B-B' of FIG. 1A, and FIG. 1C is a cross-sectional view of the integrated circuit device taken along a line C-C' of FIG. 1A;

FIG. **2** is a plan view of the integrated circuit device according to exemplary embodiments, which is obtained by a cross-section taken along a line II-II' of FIG. **1**B;

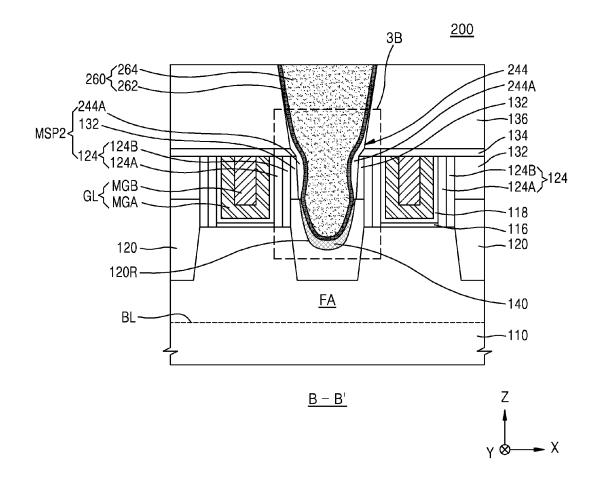

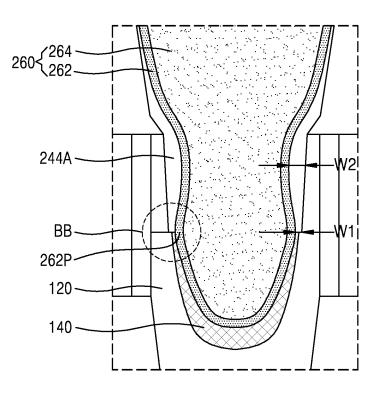

FIGS. **3**A and **3**B are diagrams for explaining an integrated circuit device according to other exemplary embodiments, FIG. **3**A is a cross-sectional view of the integrated circuit device, which corresponds to the cross-section taken along the line B-B' of FIG. **1**A, and FIG. **3**B is an enlarged view showing some components of the integrated circuit device included in a dashed-line area marked by **3**B in FIG. **3**A:

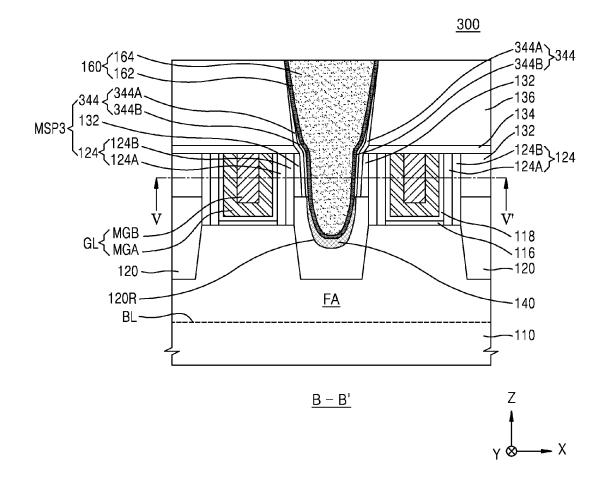

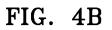

FIGS. 4A and 4B are diagrams for explaining an integrated circuit device according to further exemplary embodiments, FIG. 4A is a cross-sectional view of the integrated circuit device, which corresponds to the crosssection taken along the line B-B' of FIG. 1A, and FIG. 4B is a cross-sectional view of the integrated circuit device, which corresponds to the cross-section taken along the line C-C' of FIG. 1A;

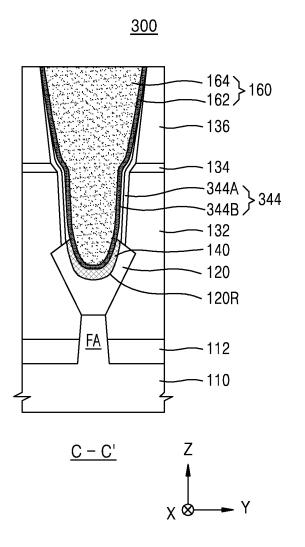

FIG. **5** is a plan view of the integrated circuit device according to exemplary embodiments, which is obtained by a cross-section taken along a line V-V' of FIG. **4**A;

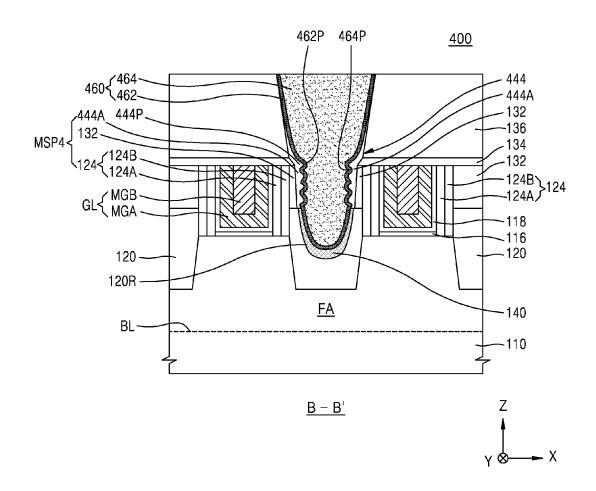

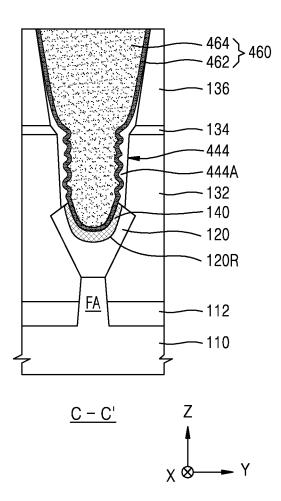

FIGS. **6**A and **6**B are diagrams for explaining an integrated circuit device according to yet other exemplary <sup>5</sup> embodiments, FIG. **6**A is a cross-sectional view of the integrated circuit device, which corresponds to the crosssection taken along the line B-B' of FIG. **1**A, and FIG. **6**B is a cross-sectional view of the integrated circuit device, which corresponds to the cross-section taken along the line <sup>10</sup> C-C' of FIG. **1**A;

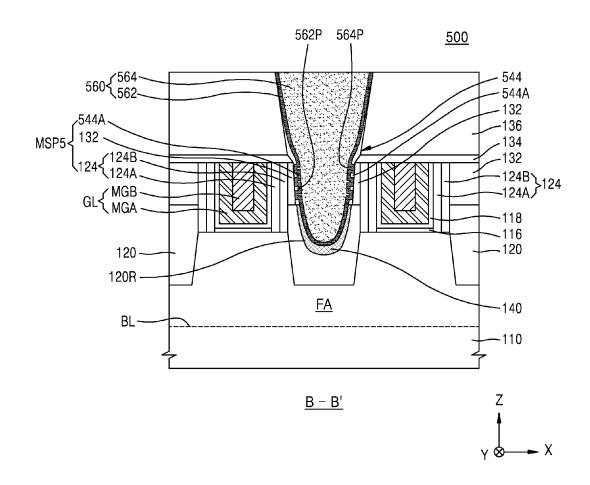

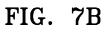

FIGS. 7A and 7B are diagrams for explaining an integrated circuit device according to yet other exemplary embodiments, FIG. 7A is a cross-sectional view of the integrated circuit device, which corresponds to the cross-<sup>15</sup> section taken along the line B-B' of FIG. 1A, and FIG. 7B is a cross-sectional view of the integrated circuit device, which corresponds to the cross-section taken along the line C-C' of FIG. 1A;

FIG. 8 is a cross-sectional view for explaining an inte-<sup>20</sup> grated circuit device according to yet other exemplary embodiments;

FIGS. **9**A and **9**B are diagrams for explaining an integrated circuit device according to yet other exemplary embodiments, FIG. **9**A is a layout diagram of the integrated <sup>25</sup> circuit device, and FIG. **9**B is a cross-sectional view of the integrated circuit device taken along a line C-C' of FIG. **9**A;

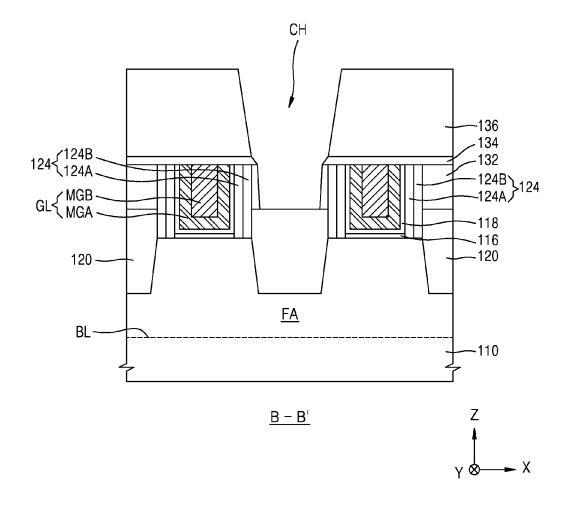

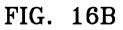

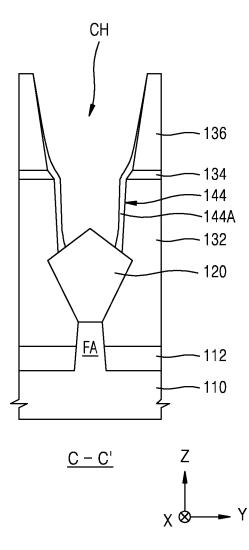

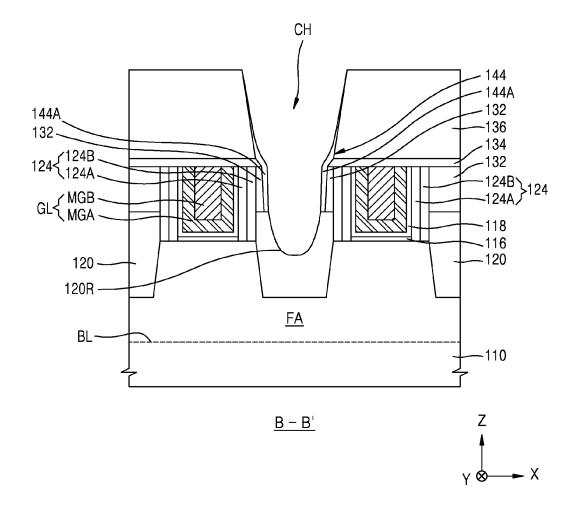

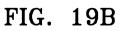

FIGS. **10**A to **21**B are cross-sectional views shown according to a process order in order to explain a method of fabricating an integrated circuit device, according to exem-<sup>30</sup> plary embodiments, FIGS. **10**A, **11**A, . . . , **21**A are cross-sectional views of the integrated circuit device, which correspond to the cross-section taken along the line B-B' of FIG. **1**A and are illustrated according to the process order, and FIGS. **10**B, **11**B, . . . , **21**B are cross-sectional views of <sup>35</sup> the integrated circuit device, which correspond to the cross-section taken along the line C-C' of FIG. **1**A and are illustrated according to the process order, and are illustrated according to the process order.

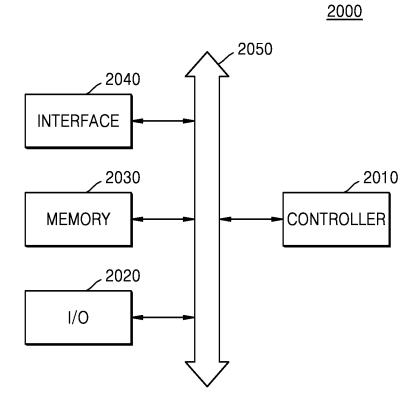

FIG. **22** is a block diagram of an electronic system according to exemplary embodiments. 40

## DETAILED DESCRIPTION OF THE EMBODIMENTS

The present disclosure now will be described more fully 45 hereinafter with reference to the accompanying drawings, in which various embodiments are shown. The invention may, however, be embodied in many different forms and should not be construed as limited to the example embodiments set forth herein. These example embodiments are just that- 50 examples-and many implementations and variations are possible that do not require the details provided herein. It should also be emphasized that the disclosure provides details of alternative examples, but such listing of alternatives is not exhaustive. Furthermore, any consistency of 55 detail between various examples should not be interpreted as requiring such detail-it is impracticable to list every possible variation for every feature described herein. The language of the claims should be referenced in determining the requirements of the invention.

In the drawings, the size and relative sizes of layers and regions may be exaggerated for clarity. Like numbers refer to like elements throughout. Though the different figures show variations of exemplary embodiments, these figures are not necessarily intended to be mutually exclusive from 65 each other. Rather, as will be seen from the context of the detailed description below, certain features depicted and 4

described in different figures can be combined with other features from other figures to result in various embodiments, when taking the figures and their description as a whole into consideration.

Although the figures described herein may be referred to using language such as "one embodiment," or "certain embodiments," these figures, and their corresponding descriptions are not intended to be mutually exclusive from other figures or descriptions, unless the context so indicates. Therefore, certain aspects from certain figures may be the same as certain features in other figures, and/or certain figures may be different representations or different portions of a particular exemplary embodiment.

It will be understood that, although the terms first, second, third etc. may be used herein to describe various elements, components, regions, layers and/or sections, these elements, components, regions, layers and/or sections should not be limited by these terms. Unless the context indicates otherwise, these terms are only used to distinguish one element, component, region, layer or section from another element, component, region, layer or section, for example as a naming convention. Thus, a first element, component, region, layer or section discussed below in one section of the specification could be termed a second element, component, region, layer or section in another section of the specification or in the claims without departing from the teachings of the present invention. In addition, in certain cases, even if a term is not described using "first," "second," etc., in the specification, it may still be referred to as "first" or "second" in a claim in order to distinguish different claimed elements from each other.

Embodiments described herein will be described referring to plan views and/or cross-sectional views by way of ideal schematic views. Accordingly, the exemplary views may be modified depending on manufacturing technologies and/or tolerances. Therefore, the disclosed embodiments are not limited to those shown in the views, but include modifications in configuration formed on the basis of manufacturing processes. Therefore, regions exemplified in figures may have schematic properties, and shapes of regions shown in figures may exemplify specific shapes of regions of elements to which aspects of the invention are not limited.

Spatially relative terms, such as "beneath," "below," "lower," "above," "upper" and the like, may be used herein for ease of description to describe one element's or feature's relationship to another element(s) or feature(s) as illustrated in the figures. It will be understood that the spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. For example, if the device in the figures is turned over, elements described as "below" or "beneath" other elements or features would then be oriented "above" the other elements or features. Thus, the term "below" can encompass both an orientation of above and below. The device may be otherwise oriented (rotated 90 degrees or at other orientations) and the spatially relative descriptors used herein interpreted accordingly.

Also these spatially relative terms such as "above" and 60 "below" as used herein have their ordinary broad meanings—for example element A can be above element B even if when looking down on the two elements there is no overlap between them (just as something in the sky is generally above something on the ground, even if it is not 65 directly above).

Contact plug may be, for example, conductive plugs formed of a conductive material such as a metal. The wiring

patterns described above may also be formed of a conductive material, for example, a metal, and each may be formed horizontally within the die.

It will be understood that when an element is referred to as being "connected" or "coupled" to or "on" another 5 element, it can be directly connected or coupled to or on the other element or intervening elements may be present. In contrast, when an element is referred to as being "directly connected" or "directly coupled" to another element, or as "contacting" or "in contact with" another element, there are 10 no intervening elements present. Other words used to describe the relationship between elements should be interpreted in a like fashion (e.g., "between" versus "directly between," "adjacent" versus "directly adjacent," etc.).

Terms such as "about" or "approximately" may reflect 15 amounts, sizes, orientations, or layouts that vary only in a small relative manner, and/or in a way that does not significantly alter the operation, functionality, or structure of certain elements. For example, a range from "about 0.1 to about 1" may encompass a range such as a 0%-5% deviation 20 around 0.1 and a 0% to 5% deviation around 1, especially if such deviation maintains the same effect as the listed range.

As used herein, the term "silicon oxide layer" may refer to a  $SiO_2$  layer, unless otherwise defined. As used herein, the term "silicon nitride layer" may refer to a  $Si_3N_4$  layer, unless 25 otherwise defined. As used herein, the term "width" may refer to a size along a length direction (X direction) of a fin-type active region FA, unless otherwise defined.

FIGS. 1A to 1C are diagrams for explaining an integrated circuit device according to exemplary embodiments, FIG. 30 1A is a layout diagram of an integrated circuit device 100 according to exemplary embodiments, FIG. 1B is a cross-sectional view of the integrated circuit device 100 taken along a line B-B' of FIG. 1A, and FIG. 1C is a cross-sectional view of the integrated circuit device 100 taken 35 along a line C-C' of FIG. 1A.

Referring to FIGS. 1A to 1C, the integrated circuit device 100 includes a substrate 110 having a fin-type active region FA extending in a first direction (X direction). In FIG. 1B, a level of a bottom surface (e.g., a bottom border or 40 boundary) of the fin-type active region FA is marked by a dashed line BL.

The substrate 110 may include a semiconductor such as Si or Ge, or a compound semiconductor such as SiGe, SiC, GaAs, InAs, or InP. In some embodiments, the substrate 110 45 may include at least one of a Group III-V material and a Group IV material. The Group III-V material may be a binary, ternary, or quaternary compound including at least one Group III element and at least one Group V element. The Group III-V material may be a compound including at least 50 one element of In, Ga, and Al as a Group III element and including at least one element of As, P, and Sb as a Group V element. For example, the Group III-V material may be selected from among InP,  $In_zGa_{1-z}As$  (0≤z≤1), and  $Al_zGa_{1-z}As$ zAs (0≤z≤1). The binary compound may be, for example, 55 one of InP, GaAs, InAs, InSb, and GaSb. The ternary compound may be, for example, one of InGaP, InGaAs, AlInAs, InGaSb, GaAsSb, and GaAsP. The Group IV material may be Si or Ge. However, the Group III-V material and the Group IV material, which can be used for the integrated 60 circuit device according to the inventive concept, are not limited to the examples set forth above. The Group III-V material and the Group IV material such as Ge may be used as a channel material with which a low-power high-speed transistor is made. A high-performance CMOS may be 65 formed by using a semiconductor substrate including a Group III-V material, for example, GaAs, which has a

6

higher electron mobility than Si, and using a semiconductor substrate including a semiconductor material, for example, Ge, which has a higher hole mobility than Si. In some embodiments, when an NMOS transistor is formed on the substrate **110**, the substrate **110** may include one of the exemplary Group III-V materials set forth above. In some other embodiments, when a PMOS transistor is formed on the substrate **110**, at least a portion of the substrate **110** may include Ge. In another example, the substrate **110** may have a silicon-on-insulator (SOI) structure. The substrate **110** may include a conductive region, for example, an impurity-doped well, or an impurity-doped structure.

A lower sidewall of the fin-type active region FA on the substrate **110** is covered with a device isolation layer **112**, and the fin-type active region FA protrudes in a fin shape upwards from the device isolation layer **112** along a third direction (Z direction) perpendicular to a main plane (X-Y plane) of the substrate **110**.

A plurality of interface layers **116**, a plurality of gate insulating layers **118**, and a plurality of gate lines GL extend, on the fin-type active region FA on the substrate **110**, in a second direction (Y direction) intersecting with a first direction (X direction).

The plurality of gate insulating layers **118** and the plurality of gate lines GL may extend while covering a top surface and both sidewalls of each fin-type active region FA and covering a top surface of the device isolation layer **112**. A plurality of transistors TR may be formed at points at which the fin-type active region FA intersects with the plurality of gate lines GL. Each of the plurality of transistors TR may include a 3-dimensional-structured metal oxide semiconductor (MOS) transistor in which a channel is formed on the top surface and both sidewalls of the fin-type active region FA.

Both sidewalls of each of the plurality of interface layers **116**, the plurality of gate insulating layers **118**, and the plurality of gate lines GL are covered with a gate insulating spacer **124**. In some embodiments, the gate insulating spacer **124** may include a first carbon-containing insulating layer **124**A and a silicon nitride layer **124**B on the first carbon-containing insulating layer **124**A, the first carbon-containing insulating layer **124**A contacting a gate insulating layer **118** on a sidewall of each gate line GL, and the silicon nitride layer **124**B covering the sidewall of each gate line GL. As used herein, the term "silicon nitride layer" may refer to a Si<sub>3</sub>N<sub>4</sub> layer.

Although the gate insulating spacer **124** is shown in FIG. 1B as having a double-layer structure including the first carbon-containing insulating layer **124**A and the silicon nitride layer **124**B, the inventive concept is not limited thereto. In some embodiments, the silicon nitride layer **124**B may be omitted. In this case, the gate insulating spacer **124** may have a single-layer structure including the first carbon-containing insulating layer **124**A.

Each of the plurality of interface layers **116** may be obtained by oxidizing an exposed surface of the fin-type active region FA, and may prevent interface defects between the fin-type active region FA and the gate insulating layers **118**. In some embodiments, the plurality of interface layers **116** may include a low-K material layer having a dielectric constant of 9 or less, for example, a silicon oxide layer, a silicon oxynitride layer, a Ga oxide layer, a Ge oxide layer, or combinations thereof. In some other embodiments, the plurality of interface layers **116** may include a silicate and the exemplary low-K material layer set forth above.

The plurality of gate insulating layers 118 may include a silicon oxide layer, a high-K dielectric layer, or combinations thereof. The high-K dielectric layer may include a material having a greater dielectric constant than a silicon oxide layer. For example, the gate insulating layers 118 may have a dielectric constant of about 10 to about 25. The high-K dielectric layer may include a material selected from among hafnium oxide, hafnium oxynitride, hafnium silicon oxide, lanthanum oxide, lanthanum aluminum oxide, zirconium oxide, zirconium silicon oxide, tantalum oxide, tita-10 nium oxide, barium strontium titanium oxide, barium titanium oxide, strontium titanium oxide, yttrium oxide, aluminum oxide, lead scandium tantalum oxide, lead zinc niobate, and combinations thereof, but the material included in the high-K dielectric layer is not limited to the examples 15 set forth above. The gate insulating layers 118 may be formed by an atomic layer deposition (ALD) process, a chemical vapor deposition (CVD) process, or a physical vapor deposition (PVD) process.

The plurality of gate lines GL extend, on the gate insu- 20 lating layers **118**, in a direction intersecting with the fin-type active region FA while covering the top surface and both sidewalls of each fin-type active region FA.

The gate lines GL may include a first metal-containing layer MGA and a second metal-containing layer MGB.

The first metal-containing layer MGA may adjust a work function. The second metal-containing layer MGB may fill a space formed above the first metal-containing layer MGA. In some embodiments, the first metal-containing layer MGA may include a metal including Ti, Ta, Al, and combinations 30 thereof. In some embodiments, the first metal-containing layer MGA may include a Ti layer, a TiN layer, a TiON layer, a TiO layer, a Ta layer, a TaN layer, a TaON layer, an oxygen-doped TiAlN (referred to as TiAlN(O) hereinafter) layer, an oxygen-doped TaAlN (referred to as TaAlN(O) 35 hereinafter) layer, or combinations thereof. In some other embodiments, the first metal-containing layer MGA may include a TiON layer, a TiO layer, a TaON layer, a TiAlN(O) layer, a TaAlN(O) layer, or combinations thereof. In some embodiments, the first metal-containing layer MGA may 40 include a single layer or multiple layers.

The second metal-containing layer MGB may include an upper work-function-adjusting layer, a conductive barrier layer, a gap-fill metal layer, or combinations thereof. The upper work-function-adjusting layer may include TiAl, 45 TiAlC, TiAlN, TiC, TaC, HfSi, or combinations thereof, without being limited thereto. The conductive barrier layer may include a metal nitride, for example, TiN, TaN, or combinations thereof, without being limited thereto. The gap-fill metal layer may fill a gate space remaining on the 50 conductive barrier layer. The gap-fill metal layer may include tungsten (W). Each of the upper work-functionadjusting layer, the conductive barrier layer, and the gap-fill metal layer may be formed by an ALD, CVD, or PVD process. In some embodiments, at least one of the upper 55 work-function-adjusting layer, the conductive barrier layer, and the gap-fill metal layer may be omitted.

In some embodiments, the gate lines GL may include a stacked structure of TiAlC/TiN/W, a stacked structure of TiN/TaN/TiAlC/TiN/W, or a stacked structure of TiN/TaN/ <sup>60</sup> TiN/TiAlC/TiN/W. In the stacked structures set forth above, a TiAlC layer or a TiN layer may serve as a metal-containing layer for adjusting work functions.

A source/drain region **120** is formed on the fin-type active region FA at one side of each gate line GL. The source/drain 65 region **120** may include a semiconductor layer epitaxially grown on the fin-type active region FA. In some embodi-

ments, the source/drain region **120** may have an embedded SiGe structure including a plurality of epitaxially grown SiGe layers. The plurality of SiGe layers may have different Ge contents. In some other embodiments, the source/drain region **120** may include an epitaxially grown Si layer or an epitaxially grown SiC layer. A recessed region **120**R may be formed in a top surface of the source/drain region **120**.

An inter-gate dielectric **132** is formed between the plurality of gate lines GL. The inter-gate dielectric **132** may be formed between two adjacent gate lines GL and cover the source/drain region **120**. The inter-gate dielectric **132** may include a silicon oxide layer, without being limited thereto.

A blocking insulating layer **134** is formed on the plurality of gate lines GL and the inter-gate dielectric **132**. An interlayer dielectric **136** is formed on the blocking insulating layer **134**.

The source/drain region **120** is connected to a contact plug **160**. The contact plug **160** extends from the recessed region **120**R of the source/drain region **120** in the third direction (Z direction) perpendicular to the main plane (X-Y plane) of the substrate **110**.

The contact plug 160 may penetrate the interlayer dielectric 136, the blocking insulating layer 134, and the inter-gate dielectric 132 and be electrically connected to the source/drain region 120.

The contact plug 160 includes a conductive barrier layer 162 and a conductive plug 164, which are formed on the source/drain region 120 in this stated order. The conductive barrier layer 162 may conformally surround an outer surface of the conductive plug 164. A cross-sectional shape of the contact plug 160 according to the X-Y plane may be a circular, elliptical, or polygonal shape, but the cross-sectional shape of the contact plug 160 is not limited thereto.

The conductive barrier layer **162** included in the contact plug **160** may include a conductive metal nitride layer. For example, the conductive barrier layer **162** may include TiN, TaN, AlN, WN, or combinations thereof. The conductive plug **164** included in the contact plug **160** may include W, Cu, Al, alloys thereof, or combinations thereof.

However, materials of the conductive barrier layer **162** and the contact plug **160** are not limited to the examples set forth above.

A contact insulating spacer 144 is formed on the source/ drain region 120 and surrounds a lower portion of the contact plug 160. The contact insulating spacer 144 may include a second carbon-containing insulating layer 144A contacting the conductive barrier layer 162 of the contact plug 160. Although the contact insulating spacer 144 is shown in FIGS. 1B and 1C as having a single-layer structure including only the second carbon-containing insulating layer 144A, the inventive concept is not limited to the example shown in FIGS. 1B and 1C. The contact insulating spacer 144 may have a multilayer structure which includes a plurality of insulating layers including different insulating materials.

The inter-gate dielectric **132** is between the contact insulating spacer **144** and the gate insulating spacer **124**.

The contact plug 160 is surrounded by the contact insulating spacer 144, the inter-gate dielectric 132, the gate insulating spacer 124, the blocking insulating layer 134, and the interlayer dielectric 136 and thus may be insulated from other surrounding conductive layers.

The gate insulating spacer **124**, the inter-gate dielectric **132**, and the contact insulating spacer **144** are located on the sidewalls of the gate lines GL in this stated order and between the gate lines GL and the contact plug **160**, and may constitute a multilayer-structured insulating spacer MSP1.

In some embodiments, the first carbon-containing insulating layer 124A may cover a surface of the inter-gate dielectric 132 which faces towards the gate lines GL away from the contact plug 160 and the second carbon-containing insulating layer 144A may cover a surface of the inter-gate dielec- 5 tric 132 which faces towards the contact plug 160 away from the gate lines GL. For example, in some embodiments, the inter-gate dielectric 132 may be provided between first carbon-containing insulating layer 124A and the second carbon-containing insulating layer 144A in a manner such 10 that the first carbon-containing insulating layer 124A of the gate insulating spacer 124 may contact a first sidewall of the inter-gate dielectric 132 adjacent to the gate lines GL and the second carbon-containing insulating layer 144A may contact a second sidewall of the inter-gate dielectric 132, opposite to 15 the first sidewall of the inter-date dielectric 132, adjacent to the contact plug 160. The insulating spacer MSP1 is between the gate lines GL and the contact plug 160, whereby the insulating spacer MSP1 may prevent an electrical short circuit therebetween, provide a sufficiently low dielectric 20 constant, and suppress the occurrence of leakage currents therebetween.

In some embodiments, the first carbon-containing insulating layer 124A of the gate insulating spacer 124, and the second carbon-containing insulating layer 144A of the con- 25 tact insulating spacer 144 may have different carbon contents. In some embodiments, the first carbon-containing insulating layer 124A may have a first carbon content, and the second carbon-containing insulating layer 144A may have a second carbon content that is greater than the first 30 carbon content. For example, the first carbon-containing insulating layer 124A may have a carbon content selected from a range of about 5 atom % to about 15 atom %, and the second carbon-containing insulating layer 144A may have a carbon content which is selected from a range of about 10 35 atom % to about 25 atom % and is greater than the carbon content in the first carbon-containing insulating layer 124A. For example, in some embodiments, a ratio of a carbon content of the first carbon-containing insulating layer 12A to a carbon content of the second carbon-containing insulating 40 layer 144A may be a value ranging from about 0.5 to about 0.6.

In some embodiments, each of the first carbon-containing insulating layer **124**A and the second carbon-containing insulating layer **144**A may include SiCN, SiOCN, or com-45 binations thereof. SiCN refers to a material containing silicon (Si), carbon (C), and nitrogen (N). SiOCN refers to a material containing silicon (Si), oxygen (O), carbon (C), and nitrogen (N).

In one embodiment, the first carbon-containing insulating 50 layer **124**A may include a SiOCN layer having a first carbon content selected from a range of about 5 atom % to about 15 atom %, and the second carbon-containing insulating layer **144**A may include a SiOCN or SiCN layer having a second carbon content that is greater than the first carbon content. 55

In another embodiment, the first carbon-containing insulating layer **124**A may include a SiOCN layer having a first oxygen content selected from a range of about 25 atom % to about 50 atom %, and the second carbon-containing insulating layer **144**A may include a SiOCN or SiCN layer 60 having a second oxygen content that is less than the first oxygen content.

The blocking insulating layer **134** and the interlayer dielectric **136** may surround the contact plug **160** while covering the gate lines GL and the multilayer-structured 65 insulating spacer MSP1. In some embodiments, the blocking insulating layer **134** may include the same material as a

material of one of the first carbon-containing insulating layer 124A and the second carbon-containing insulating layer 134 may include the same material as the first carbon-containing insulating layer 124A. In another embodiment, the blocking insulating layer 134 may include the same material as the second carbon-containing insulating layer 134 may include the same material as the second carbon-containing insulating layer 144A.

In some embodiments, a width of the second carboncontaining insulating layer 144A is less than a width of the first carbon-containing insulating layer 124A. A width of a portion of the inter-gate dielectric 132 may be less than the width of the first carbon-containing insulating layer 124A, the portion of the inter-gate dielectric 132 being between the contact insulating spacer 144 and the gate insulating spacer 124. For example, each of the first carbon-containing insulating layer 124A and the silicon nitride layer 124B may have a width of about 2 nm to about 10 nm. In some embodiments, the width of the first carbon-containing insulating layer 124A may be equal to the width of the silicon nitride layer 124B. In some other embodiments, the width of the first carbon-containing insulating layer 124A may be greater than the width of the silicon nitride layer 124B. In some embodiments, a sum of the widths of the first carboncontaining insulating layer 124A and the silicon nitride layer 124B may range from about 5 nm to about 20 nm. The width of the second carbon-containing insulating layer 144A may range from about 1 nm to about 5 nm. The width of the portion of the inter-gate dielectric 132 may range from about 1 nm to about 5 nm, the portion of the inter-gate dielectric 132 being between the contact insulating spacer 144 and the gate insulating spacer 124. However, the values of the widths set forth above are merely examples and may be variously modified and changed without departing from the spirit and scope of the inventive concept.

FIG. 2 is a plan view of the integrated circuit device 100, which is obtained by a cross-section taken along a line II-II' of FIG. 1B, and shows planar shapes of some components of the integrated circuit device 100 of FIGS. 1A to 1C.

As shown in FIG. 2, the first carbon-containing insulating layer 124A may linearly extend, on the sidewalls of the gate lines GL, along a length direction of the gate lines GL. In addition, the second carbon-containing insulating layer 144A may have a ring shape on the source/drain region 120, the ring shape surrounding the lower portion of the contact plug 160.

Although FIG. 2 shows an example in which the contact plug 160 approximately has a cross-sectional shape of a circle and the second carbon-containing insulating layer 144A surrounding the contact plug 160 approximately has a cross-sectional shape of a circular ring, the inventive concept is not limited to the shapes shown in FIG. 2. For example, the contact plug 160 may have a cross-sectional shape of an ellipse or polygon, and correspondingly, the second carbon-containing insulating layer 144A may have a cross-sectional shape of an elliptical or polygonal ring. In some embodiments, the second carbon-containing insulating layer 144A may have a varying thickness extending from an upper surface of the contact plug 160 towards the substrate 110 such that a first sidewall of the second carbon-containing insulating layer 144A with respect to a sidewall of the contact plug 160 may be concave and a second sidewall of the second carbon-containing insulating layer 144A with respect to the same sidewall of the contact plug 160 may be convex.

Referring again to FIGS. 1A to 1C, a metal silicide layer 140 may be formed between the source/drain region 120 and

the contact plug 160. The metal silicide layer 140 may be formed along an inner wall of recessed region 120R.

The metal silicide layer 140 may have a decreasing thickness with increasing distance from the substrate 110 in an upward direction (e.g., Z direction—perpendicular to the main plane of the substrate 110). In some embodiments, the metal silicide laver 140 may include a metal silicide laver including a dopant. The dopant may include at least one element selected from among carbon group elements and inert elements. For example, the metal silicide layer 140 may be represented by a compositional formula of MSi<sub>x</sub>D<sub>y</sub>. Here, M is a metal, D is an element that is different from M and Si,  $0 \le x \le 3$ , and  $0 \le y \le 1$ . In some embodiments, M may include Ti, W, Ru, Nb, Mo, Hf, Ni, Co, Pt, Yb, Tb, Dy, Er, 15 Pd, or combinations thereof. In some embodiments, D may include Ge, C, Ar, Kr, Xe, or combinations thereof.

In some embodiments, as shown in FIG. 1B, the metal silicide layer 140 may contact the conductive barrier layer **162**. However, the inventive concept is not limited thereto. 20 In some other embodiments, a metal layer (not shown) may be between the metal silicide layer 140 and the conductive barrier layer 162, the metal layer including the same material as a metal included in the metal silicide layer 140. For example, when the metal silicide layer 140 includes titanium <sup>25</sup> silicide, the metal layer may include titanium.

The source/drain region 120 may have a raised source/ drain (RSD) structure having a top surface that is at a higher level than a top surface of the fin-type active region FA.

The inter-gate dielectric 132 may be formed between two adjacent gate lines GL and cover the source/drain region 120.

The blocking insulating layer 134 prevents undesired foreign substances such as oxygen from penetrating into the 35 plurality of gate lines GL, thereby preventing an undesired change in threshold voltage in the gate lines GL, or a short circuit which may occur between the gate lines GL and the contact plug 160. The blocking insulating layer 134 is formed, thereby maintaining a constant threshold voltage in 40 the gate lines GL and preventing deterioration in electrical characteristics of a transistor including the gate lines GL. In some embodiments, the blocking insulating layer 134 may include a layer including silicon and nitrogen. For example, the blocking insulating layer 134 may include a silicon 45 nitride layer, a silicon oxynitride (SiON) layer, a silicon carbonitride (SiCN) layer, a carbon-containing silicon oxynitride (SiOCN) layer, or combinations thereof. In some embodiments, the blocking insulating layer 134 may have a thickness of about 20 Å to about 50 Å.

The interlayer dielectric 136 may include a silicon oxide layer, without being limited thereto.

In some embodiments, at least one of the inter-gate dielectric 132 and the interlayer dielectric 136 may include a tetraethyl orthosilicate (TEOS) layer. In some other 55 FIGS. 3A and 3B as having a single-layer structure including embodiments, at least one of the inter-gate dielectric 132 and the interlayer dielectric 136 may include an ultra-low-K (ULK) layer having an ultra-low dielectric constant K of about 2.2 to about 2.4, for example, one layer selected from a SiOC layer and a SiCOH layer. 60

FIGS. 3A and 3B are diagrams for explaining an integrated circuit device according to other exemplary embodiments, FIG. 3A is a cross-sectional view of the integrated circuit device, which corresponds to the cross-section taken along the line B-B' of FIG. 1A, and FIG. 3B is an enlarged 65 view showing some components of the integrated circuit device included in a dashed-line area marked by 3B in FIG.

3A. In FIGS. 3A and 3B, the same reference numerals as in FIGS. 1A to 1C denote the same members, and descriptions thereof will be omitted.

An integrated circuit device 200 shown in FIGS. 3A and 3B has mostly the same configuration as the integrated circuit device 100 described with reference to FIGS. 1A to 1C. However, the integrated circuit device 200 shown in FIGS. 3A and 3B differs from the integrated circuit device 100 of FIGS. 1A to 1C in that a shape of a second carbon-containing insulating layer 244A included in a contact insulating spacer 244 surrounding a lower portion of a contact plug 260 differs from the shape of the second carbon-containing insulating layer 144A included in the contact insulating spacer 144 shown in FIGS. 1B and 1C.

Referring to FIGS. 3A and 3B, the contact insulating spacer 244 is formed on the source/drain region 120 and surrounds the lower portion of the contact plug 260. The contact insulating spacer 244 includes the second carboncontaining insulating layer 244A contacting a conductive barrier layer 262 of the contact plug 260.

A width W1 of a bottom surface of the second carboncontaining insulating layer 244A is less than a maximum width of a middle portion of the second carbon-containing insulating layer 244A, the bottom surface of the second carbon-containing insulating layer 244A being closest to the substrate 110. For example, the width W1 of the bottom surface is less than a maximum width W2 of a portion of the second carbon-containing insulating layer 244A, which is surrounded by the inter-gate dielectric 132.

In addition, the contact plug 260 includes the conductive barrier layer 262 and a conductive plug 264, which are formed on the source/drain region 120 in this stated order. A portion of the conductive barrier layer 262 may extend along a surface profile of the second carbon-containing insulating layer 244A, the portion of the conductive barrier layer 262 contacting the second carbon-containing insulating layer 244A. Thus, as shown in a dashed-line area marked by BB in FIG. 3B, the conductive barrier layer 262 may have a protrusion 262P which protrudes in a direction away from the conductive plug 264 with decreasing distance from the bottom surface of the second carbon-containing insulating layer 244A. Further, similarly to the conductive barrier layer 262, the conductive plug 264 may also have a protrusion which protrudes outwards with decreasing distance from the bottom surface of the second carbon-containing insulating layer 244A.

More details of the second carbon-containing insulating layer 244A, the conductive barrier layer 262, and the conductive plug 264 are mostly the same as the details of the second carbon-containing insulating layer 144A, the conductive barrier layer 162, and the conductive plug 164, which have been described with reference to FIGS. 1A to 1C

Although the contact insulating spacer 244 is shown in only the second carbon-containing insulating layer 244A, the inventive concept is not limited to the example shown in FIGS. 3A and 3B. The contact insulating spacer 244 may have a multilayer structure which includes a plurality of insulating layers including different insulating materials.

In the integrated circuit device 200 shown in FIGS. 3A and 3B, a multilayer-structured insulating spacer MSP2 is between the gate lines GL and the contact plug 260, the multilayer-structured insulating spacer MSP2 including the gate insulating spacer 124, the inter-gate dielectric 132, and the contact insulating spacer 244, which are located on the sidewalls of the gate lines GL in this stated order. The insulating spacer MSP2 is between the gate lines GL and the contact plug 260, whereby the insulating spacer MSP2 may prevent an electrical short circuit therebetween, provide a sufficiently low dielectric constant, and suppress the occurrence of leakage currents therebetween.

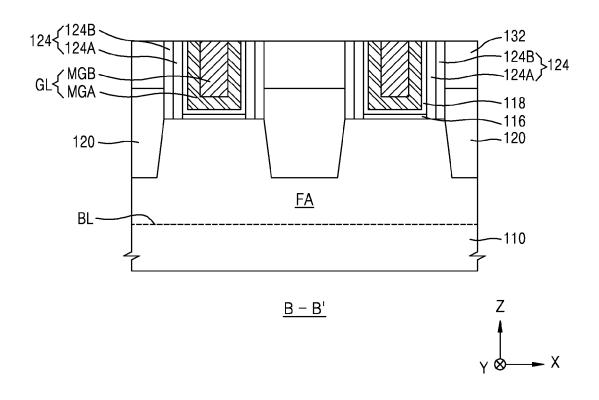

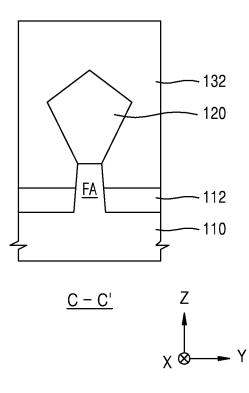

FIGS. 4A and 4B are diagrams for explaining an integrated circuit device according to further exemplary embodiments, FIG. 4A is a cross-sectional view of the integrated circuit device, which corresponds to the crosssection taken along the line B-B' of FIG. 1A, and FIG. 4B 10 is a cross-sectional view of the integrated circuit device, which corresponds to the cross-section taken along the line C-C' of FIG. 1A. In FIGS. 4A and 4B, the same reference numerals as in FIGS. 1A to 1C denote the same members, and descriptions thereof will be omitted. 15

An integrated circuit device **300** shown in FIGS. **4**A and **4**B has mostly the same configuration as the integrated circuit device **100** described with reference to FIGS. **1**A to **1**C. However, in the integrated circuit device **300** shown in FIGS. **4**A and **4**B, a contact insulating spacer **344** surrounding the lower portion of the contact plug **160** includes a silicon nitride layer **344**A and a second carbon-containing insulating layer **344**B, the silicon nitride layer **344**A covering the conductive barrier layer **162**, and the second carboncontaining insulating layer **344**B being between the conductive barrier layer **162** and the silicon nitride layer **344**A and contacting the conductive barrier layer **162**. The silicon nitride layer **344**A is between the inter-gate dielectric **132** and the second carbon-containing insulating layer **344**B and may surround the lower portion of the contact plug **160**. 30

In some embodiments, a thickness of the second carboncontaining insulating layer **344B** may be less than a thickness of the silicon nitride layer **344A**. In some other embodiments, the thickness of the second carbon-containing insulating layer **344B** may be equal to or greater than the 35 thickness of the silicon nitride layer **344A**. Each of the silicon nitride layer **344B** may have a thickness selected from a range of about 1 nm to about 5 nm, without being limited thereto. 40

FIG. 5 is a plan view of the integrated circuit device 300, which is obtained by a cross-section taken along a line V-V' of FIG. 4A, and shows planar shapes of some components of the integrated circuit device 300 of FIGS. 4A and 4B.

As shown in FIG. 5, the first carbon-containing insulating 45 layer 124A may linearly extend, on the sidewalls of the gate lines GL, along the length direction of the gate lines GL. In addition, the contact insulating spacer 344 including the silicon nitride layer 344A and the second carbon-containing insulating layer 344B may have a ring shape on the source/ 50 drain region 120, the ring shape surrounding the lower portion of the contact plug 160.

Although FIG. 5 shows an example in which the contact plug 160 approximately has a cross-sectional shape of a circle and the contact insulating spacer 344 surrounding the 55 contact plug 160 approximately has a cross-sectional shape of a circular ring, the cross-sectional shape is not limited to the shapes shown in FIG. 5. For example, the contact plug 160 may have a cross-sectional shape of an ellipse or polygon, and correspondingly, the contact insulating spacer 60 344 may have a cross-sectional shape of an elliptical or polygonal ring.

FIGS. **6**A and **6**B are diagrams for explaining an integrated circuit device according to yet other exemplary embodiments, FIG. **6**A is a cross-sectional view of the 65 integrated circuit device, which corresponds to the crosssection taken along the line B-B' of FIG. **1**A, and FIG. **6**B

is a cross-sectional view of the integrated circuit device, which corresponds to the cross-section taken along the line C-C' of FIG. 1A. In FIGS. 6A and 6B, the same reference numerals as in FIGS. 1A to 1C denote the same members, and descriptions thereof will be omitted.

An integrated circuit device 400 shown in FIGS. 6A and 6B has mostly the same configuration as the integrated circuit device 100 described with reference to FIGS. 1A to 1C. However, in the integrated circuit device 400 shown in 10 FIGS. 6A and 6B, a contact plug 460 includes a conductive barrier layer 462 and a conductive plug 464. A contact insulating spacer 444 surrounding a lower portion of the contact plug 460 includes a second carbon-containing insulating layer 444A contacting the conductive barrier layer 462 15 of the contact plug 460.

A surface of the second carbon-containing insulating layer 444A, which contacts the conductive barrier layer 462, has an uneven structure 444P. In addition, an uneven structure 462P is also formed in a portion of the conductive barrier layer 462, which faces the uneven structure 444P of the second carbon-containing insulating layer 444A. In some embodiments, like in the conductive barrier layer 462, an uneven structure 464P may also be formed in a portion of the conductive plug 464, which faces the uneven structure 444P of the second carbon-containing insulating layer 444A. In some other embodiments, unlike in the conductive barrier layer 462, the portion of the conductive plug 464 may have a relatively smooth surface instead of having an uneven structure, the portion of the conductive plug 464 facing the uneven structure 444P of the second carbon-containing insulating layer 444A. In some embodiments, the uneven structure 444P of the surface of the second carbon-containing insulating layer 444A may extend from the lower-most surface of the second carbon-containing insulating layer 444A to the upper-most surface of the inter-gate dielectric 132, but the disclosure is not limited thereto. For example, in some embodiments, the uneven structure 444P of the surface of the second carbon-containing insulating layer 444A may extend from the lower-most surface of the second 40 carbon-containing insulating layer 444A to the upper-most surface of the blocking insulating layer 134.

Although the contact insulating spacer **444** is shown in FIGS. **6**A and **6**B as having a single-layer structure including only the second carbon-containing insulating layer **444**A, the disclosure is not limited to the example shown in FIGS. **6**A and **6**B. The contact insulating spacer **444** may have a multilayer structure which includes a plurality of insulating layers including different insulating materials.

More details of the second carbon-containing insulating layer 444A, the conductive barrier layer 462, and the conductive plug 464 are mostly the same as the details of the second carbon-containing insulating layer 144A, the conductive barrier layer 162, and the conductive plug 164, which have been described with reference to FIGS. 1A to 1C.

In the second carbon-containing insulating layer **344**B included in the contact insulating spacer **344** of the integrated circuit device **300** shown in FIGS. **4**A and **4**B, like in the second carbon-containing insulating layer **444**A shown in FIGS. **6**A and **6**B, a surface of the second carbon-containing insulating layer **344**B, which contacts the conductive barrier layer **162**, may also have an uneven structure, although not shown. In this case, the silicon nitride layer **344**A and/or the conductive barrier layer **162** may also include a similar uneven structure due to the transfer of a shape of the uneven structure of the surface of the second carbon-containing insulating layer **344**B, or may have a

non-smooth surface due to deformation caused by the uneven structure of the surface of the second carbon-containing insulating layer **344**B.

FIGS. 7A and 7B are diagrams for explaining an integrated circuit device according to yet other exemplary 5 embodiments, FIG. 7A is a cross-sectional view of the integrated circuit device, which corresponds to the crosssection taken along the line B-B' of FIG. 1A, and FIG. 7B is a cross-sectional view of the integrated circuit device, which corresponds to the cross-section taken along the line 10 C-C' of FIG. 1A. In FIGS. 7A and 7B, the same reference numerals as in FIGS. 1A to 1C denote the same members, and descriptions thereof will be omitted.

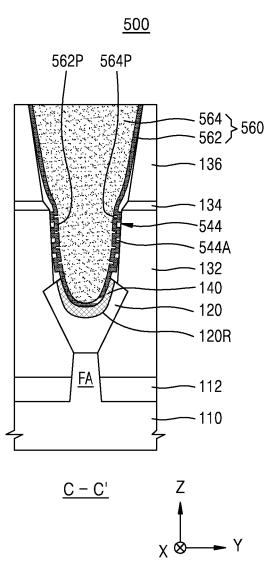

An integrated circuit device **500** shown in FIGS. **7A** and **7B** has mostly the same configuration as the integrated 15 circuit device **100** described with reference to FIGS. **1A** to **1C**. However, in the integrated circuit device **500** shown in FIGS. **7A** and **7B**, a contact plug **560** includes a conductive barrier layer **562** and a conductive plug **564**. A contact insulating spacer **544** surrounding a lower portion of the 20 contact plug **560** includes a second carbon-containing insulating layer **544**A contacting the conductive barrier layer **562** of the contact plug **560**.

At least a portion of the second carbon-containing insulating layer **544**A intermittently extends along an extension 25 direction of the contact plug **560** or along the third direction (Z direction) perpendicular to the main plane of the substrate **110**.

An uneven structure 562P is formed in a portion of the conductive barrier layer 562, which faces the intermittent 30 structure of the second carbon-containing insulating layer 544A. In some embodiments, like in the conductive barrier layer 562, an uneven structure 564P may be formed in a portion of the conductive plug 564, which faces the intermittent structure of the second carbon-containing insulating 35 layer 544A. In some embodiments, the uneven structure 562P of the conductive barrier layer 562 and the uneven structure 564P of the conductive plug 564 may extend from the lower-most surface of the second carbon-containing insulating layer 544A to the upper-most surface of the 40 inter-gate dielectric 132, but the disclosure is not limited thereto. For example, in some embodiments, the uneven structure 562P of the conductive barrier layer 562 and the uneven structure 564P of the conductive plug 564 may extend from the lower-most surface of the second carbon- 45 containing insulating layer 544A to the upper-most surface of blocking insulating layer 134. In some other embodiments, unlike in the example shown in FIGS. 7A and 7B, the portion of the conductive plug 564 may have a relatively smooth surface instead of having an uneven structure, the 50 portion of the conductive plug 464 facing the intermittent structure of the second carbon-containing insulating laver 544A.

Although the contact insulating spacer **544** is shown in FIGS. 7A and 7B as having a single-layer structure including 55 only the second carbon-containing insulating layer **544**A, the inventive concept is not limited to the example shown in FIGS. **5**A and **5**B. The contact insulating spacer **544** may have a multilayer structure which includes a plurality of insulating layers including different insulating materials. 60

More details of the second carbon-containing insulating layer 544A, the conductive barrier layer 562, and the conductive plug 564 are mostly the same as the details of the second carbon-containing insulating layer 144A, the conductive barrier layer 162, and the conductive plug 164, 65 which have been described with reference to FIGS. 1A to 1C.

Although not shown, similarly to the second carboncontaining insulating layer 544A shown in FIGS. 7A and 7B, at least one of the silicon nitride layer 344A and the second carbon-containing insulating layer 344B may intermittently extend along an extension direction of the contact plug 160 or along the third direction (Z direction) perpendicular to the main plane of the substrate 110, the silicon nitride layer 344B constituting the contact insulating spacer 344 of the integrated circuit device 300 shown in FIGS. 4A and 4B.

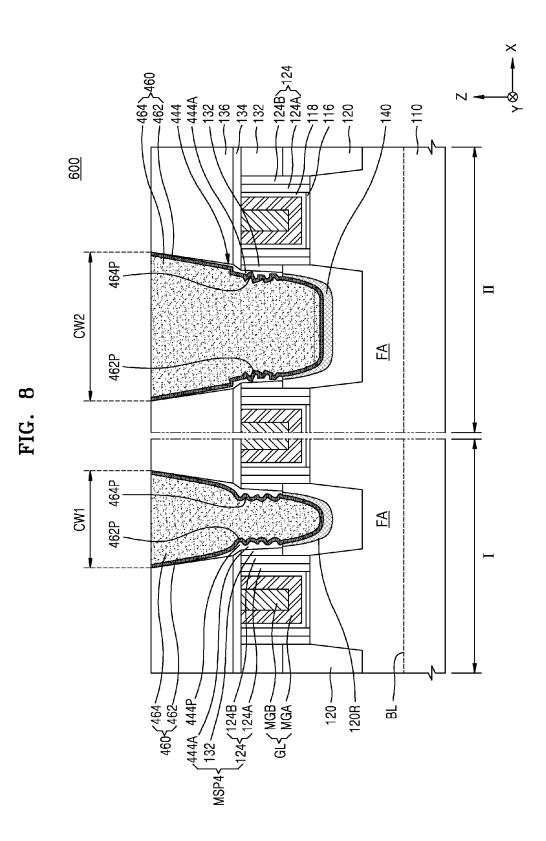

FIG. 8 is a cross-sectional view for explaining an integrated circuit device according to yet other exemplary embodiments. In FIG. 8, the same reference numerals as in FIGS. 1A to 1C denote the same members, and descriptions thereof will be omitted.

An integrated circuit device 600 shown in FIG. 8 has a mostly similar configuration to the integrated circuit device 400 shown in FIGS. 6A and 6B. However, in the integrated circuit device 600 shown in FIG. 8, a degree of unevenness of the uneven structure of the contact insulating spacer 444 varies with the width of the contact plug, the contact insulating spacer 444 surrounding the lower portion of the contact plug.

A specific example will be described in detail. The substrate **110** of the integrated circuit device **600** has a first device region I and a second device region II.

In some embodiments, the first device region I and the second device region II may be regions performing different functions. In some other embodiments, the first device region I may be a region in which devices operating in a low-power mode are formed, and the second device region II may be a region in which devices operating in a high-power mode are formed. In some further embodiments, the first device region I may be a region in which a memory device or a logic circuit is formed, and the second device region II may be a region in which a peripheral circuit such as an input/output (I/O) device is formed.

In the integrated circuit device 600 shown in FIG. 8, the first device region I and the second device region II may have mostly the same configuration. However, a pattern formation density in the second device region II may be less than a pattern formation density in the first device region I. Thus, a width of the source/drain region 120 in the second device region II may be greater than a width of the source/ drain region 120 in the first device region I. In addition, a width CW2 of the contact plug 460 in the second device region II may be greater than a width CW1 of the contact plug 460 in the first device region I. In this case, a degree of unevenness of the uneven structure 444P of the second carbon-containing insulating layer 444A surrounding the contact plug 460 in the second device region II may be greater than a degree of unevenness of the uneven structure 444P of the second carbon-containing insulating layer 444A surrounding the contact plug 460 in the first device region I, the contact plug 460 in the second device region II having the relatively large width CW2, the contact plug 460 in the first device region I having the relatively small width CW1.

In some embodiments, like in the example described with reference to FIGS. **6**A and **6**B, the uneven structure **444**P of the second carbon-containing insulating layer **444**A in each of the first device region I and the second device region II may continuously extend along the extension direction (Z direction) of the contact plug **460** rather than locally intermittently extending along the extension direction (Z direction) of the contact plug **460**. In some other embodiments, while the uneven structure **444**P of the second carbon-containing insulating layer **444**A in the first device region I

may continuously extend like in the example described with reference to FIGS. 6A and 6B, the uneven structure 444P of the second carbon-containing insulating layer 444A in the second device region II may intermittently extend like in the example described with reference to FIGS. 7A and 7B.

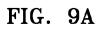

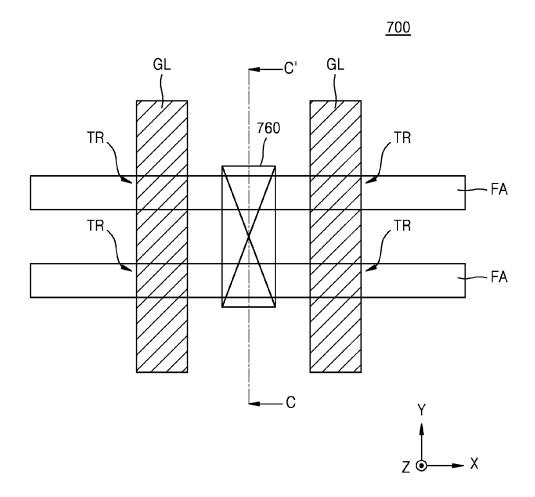

FIGS. 9A and 9B are diagrams for explaining an integrated circuit device according to yet other exemplary embodiments, FIG. 9A is a layout diagram of an integrated circuit device 700, and FIG. 9B is a cross-sectional view of the integrated circuit device 700 taken along a line C-C' of 10 FIG. 9A. In FIGS. 9A and 9B, the same reference numerals as in FIGS. 1A to 1C denote the same members, and descriptions thereof will be omitted.

The integrated circuit device 700 shown in FIGS. 9A and 9B has mostly the same configuration as the integrated 15 circuit device 100 described with reference to FIGS. 1A to 1C. However, the integrated circuit device 700 includes a plurality of fin-type active regions FA extending parallel to each other on the substrate 110. The plurality of gate lines GL extend parallel to each other in a direction (Y direction) 20 intersecting with the plurality of fin-type active regions FA.

The source/drain region 120 is formed in each of the plurality of fin-type active regions FA at both sides of each of the plurality of gate lines GL.

The contact plug 160 extends in the second direction (Y 25 direction) across two adjacent fin-type active regions FA out of the plurality of fin-type active regions FA. The contact plug 160 is formed on the source/drain regions 120 to be connected to each of the source/drain regions 120, the source/drain regions 120 being respectively formed in the 30 two adjacent fin-type active regions FA.

The contact plug 160 extends from recessed regions 120R on top surfaces of the source/drain regions 120 in the third direction (Z direction) perpendicular to the main plane of the substrate 110. The contact plug 160 may penetrate the 35 layer, a silicon nitride layer, a silicon oxynitride layer, or interlayer dielectric 136, the blocking insulating layer 134, and the inter-gate dielectric 132 and be electrically connected to the two adjacent source/drain regions 120.

The contact insulating spacer 144 is formed on the two adjacent source/drain regions 120 and surrounds the lower 40 portion of the contact plug 160.

The contact plug 160 includes the conductive barrier layer 162 and the conductive plug 164, which are formed on the two adjacent source/drain regions 120 in this stated order. The metal silicide layer 140 is formed between the conduc- 45 tive barrier layer 162 and the two adjacent source/drain regions 120.

The integrated circuit device 700 shown in FIGS. 9A and 9B may have a configuration that is the same as or similar to the configuration shown in FIG. 1B, in a cross-sectional 50 view taken along the extension direction (X direction) of the fin-type active regions FA.

In the integrated circuit device 700 shown in FIGS. 9A and 9B, although the contact plug 160 is shown as extending across the two source/drain regions 120 in the two fin-type 55 active regions FA, the inventive concept is not limited thereto. For example, one contact plug 160 may extend across three or more fin-type active regions FA, as needed, and correspondingly, the one contact plug 160 may be electrically connected to three or more source/drain regions 60 120.

FIGS. 10A to 21B are cross-sectional views shown according to a process order in order to explain a method of fabricating an integrated circuit device, according to exemplary embodiments. More specifically, FIGS. 10A, 65 11A, ..., 21A are cross-sectional views of the integrated circuit device, which correspond to the cross-section taken

along the line B-B' of FIG. 1A and are illustrated according to the process order. FIGS. 10B, 11B, . . . , 21B are cross-sectional views of the integrated circuit device, which correspond to the cross-section taken along the line C-C' of FIG. 1A and are illustrated according to the process order. A method of fabricating the integrated circuit device 100 shown in FIGS. 1A to 1C will be described in detail with reference to FIGS. 10A to 21B. In FIGS. 10A to 21B, the same reference numerals as in FIGS. 1A to 1C denote the same members, and descriptions thereof will be omitted.

Referring to FIGS. 10A and 10B, a substrate 110 is prepared.

In some embodiments, the substrate 110 may have a certain metal oxide semiconductor (MOS) region. For example, the substrate 110 may have a PMOS region or an NMOS region.

A fin-type active region FA is formed by etching some regions of the substrate 110, the fin-type active region FA protruding upwards (Z direction) from a main plane (X-Y plane) of the substrate 110 and extending in one direction (X direction).

In some embodiments, a portion of the substrate 110, which is shown in FIGS. 10A and 10B, may be a region for forming one of a PMOS transistor and an NMOS transistor. The fin-type active region FA may include P-type or N-type impurity-diffused regions (not shown) depending upon a channel type of a MOS transistor intended to be formed in the fin-type active region FA.

An insulating layer is formed on the substrate 110 to cover the fin-type active region FA, followed by forming a device isolation layer 112 by performing etch-back of the insulating layer. The fin-type active region FA protrudes upwards from a top surface of the device isolation layer 112 to be exposed.

The device isolation layer 112 may include a silicon oxide combinations thereof. The device isolation layer 112 may include an insulating liner (not shown) including a thermal oxide layer, and a buried insulating layer (not shown) formed on the insulating liner.

Referring to FIGS. 11A and 11B, a plurality of dummy gate structures DGS is formed on the fin-type active region FA and extends to intersect with the fin-type active region FA.

Each of the plurality of dummy gate structures DGS may include a dummy gate insulating layer D114, a dummy gate line D116, and a dummy gate capping layer D118, which are stacked on the fin-type active region FA in this stated order. In some embodiments, the dummy gate insulating layer D114 may include silicon oxide. The dummy gate line D116 may include polysilicon. The dummy gate capping layer D118 may include at least one of silicon oxide, silicon nitride, and silicon oxynitride.

Next, a gate insulating spacer 124 is formed on both sidewalls of each dummy gate structure DGS. The gate insulating spacer 124 may include a first carbon-containing insulating layer 124A and a silicon nitride layer 124B on the first carbon-containing insulating layer 124A, the first carbon-containing insulating layer 124A and the silicon nitride layer 124B covering the sidewalls of the dummy gate structures DGS.

In some embodiments, the first carbon-containing insulating layer 124A of the gate insulating spacer 124 may have a carbon content selected from a range of about 5 atom % to about 15 atom %. In some embodiments, the first carboncontaining insulating layer 124A may include SiCN, SiOCN, or combinations thereof. In one embodiment, the first carbon-containing insulating layer 124A may include a

SiOCN layer having a carbon content selected from a range of about 5 atom % to about 15 atom %. The first carbon-containing insulating layer **124**A may have a width of about 5 nm to about 20 nm.

To form the gate insulating spacer **124**, an ALD or CVD process may be used. In particular, to form the first carboncontaining insulating layer **124**A, a plasma enhanced ALD (PEALD) process may be used. A deposition process for forming the first carbon-containing insulating layer **124**A may be performed at a relatively low temperature of about 600° C. or less. The deposition process for forming the first carbon-containing insulating layer **124**A may be performed at a lower temperature of about 500° C. or less depending upon a kind of carbon precursor in use.

During an ALD process for forming the first carboncontaining insulating layer **124**A, at least one selected from among a C1 to C10 alkane, a C2 to C10 alkene, a C1 to C15 alkylamine, a C4 to C15 nitrogen-containing heterocyclic compound, a C1 to C20 alkylsilane, a C1 to C20 alkoxysilane, and a C1 to C20 alkylsiloxane may be used as a carbon precursor.

The C1 to C10 alkane may include methane, ethane, propane, butane, pentane, hexane, heptane, octane, nonane, decane, or mixtures thereof.

The C2 to C10 alkene may include ethylene, propylene, butene, pentene, hexene, heptene, octene, nonene, decene, or mixtures thereof.

The C1 to C15 alkylamine may include monomethylamine, dimethylamine, trimethylamine, monoethylamine, 30 diethylamine, triethylamine, monopropylamine, dipropylamine, tripropylamine, monobutylamine, dibutylamine, tributylamine, monopentylamine, dipentylamine, tripentylamine, monohexylamine, dihexylamine, monoheptylamine, diheptylamine, monooctylamine, monononylamine, 35 monodecylamine, monoundecylamine, monododecylamine, monotridecylamine, monotetradecylamine, monopentadecylamine, dimethyl(ethyl)amine, dimethyl(propyl)amine, dimethyl(butyl)amine, dimethyl(pentyl)amine, dimethyl dimethyl(heptyl)amine, (hexyl)amine, dimethyl(octyl) 40 amine, dimethyl(nonyl)amine, dimethyl(decyl)amine, dimethyl(undecyl)amine, dimethyl(dodecyl)amine, dimethyl (tridecyl)amine, diethyl(methyl)amine, diethyl(propyl) amine, diethyl(butyl)amine, diethyl(pentyl)amine, diethyl (hexyl)amine, diethyl(heptyl)amine, diethyl(octyl)amine, 45 diethyl(nonyl)amine, diethyl(decyl)amine, diethyl(undecyl) amine. dipropyl(methyl)amine, dipropyl(ethyl)amine, dipropyl(butyl)amine, dipropyl(pentyl)amine, dipropyl(hexyl)amine, dipropyl(heptyl)amine, dipropyl(octyl)amine, dipropyl(nonyl)amine, dibutyl(methyl)amine, dibutyl(ethyl) 50 amine, dibutyl(propyl)amine, dibutyl(pentyl)amine, dibutyl (hexyl)amine, dibutyl(heptyl)amine, dipentyl(methyl) dipentyl(ethyl)amine, dipentyl(propyl)amine, amine. dipentyl(butyl)amine, dihexyl(methyl)amine, dihexyl(ethyl) amine, dihexyl(propyl)amine, diheptyl(methyl)amine, dim- 55 ethyl(butenyl)amine, dimethyl(pentenyl)amine, dimethyl (hexenyl)amine, dimethyl(heptenyl)amine, dimethyl (octenyl)amine, dimethyl(cyclopentyl)amine, dimethyl (cyclohexyl)amine, dimethyl(cycloheptyl)amine, bis(methyl cyclopentyl)amine, (dimethyl cyclopentyl)amine, bis(dim- 60 ethyl cyclopentyl)amine, (ethyl cyclopentyl)amine, bis(ethylcyclopentyl)amine, (methylethyl cyclopentyl)amine, bis (methylethyl cyclopentyl)amine, N-methyl ethylenediamine, N-ethyl ethylenediamine, N-propyl ethylenediamine, N-butyl ethylenediamine, N-pentyl ethylenedi- 65 amine, N-hexyl ethylenediamine, N-heptyl ethylenediamine, N-octyl ethylenediamine, N-nonyl ethylenediamine,

N-decyl ethylenediamine, N-undecyl ethylenediamine, N-dodecyl ethylenediamine, or the like.

The C1 to C20 alkylsilane may include methylsilane, tetramethylsilane (TMS), tetraethylsilane (TES), tetrapropylsilane, tetrabutylsilane, dimethylsilane (DMS), diethylsilane (DES), dimethyldifluorosilane (DMDFS), dimethyldichlorosilane (DMDCS), diethyldichlorosilane (DEDCS), hexamethyldisilane, dodecamethylcyclohexasilane, dimethyldiphenylsilane, diethyldiphenylsilane, methyltrichlorosilane, methyltriphenylsilane, dimethyldiethylsilane, or the like.

The C1 to C20 alkoxysilane may include trimethoxysilane, dimethoxysilane, methoxysilane, methyldimethoxysilane, diethoxymethylsilane, dimethylethoxysilane, dimethylaminomethoxysilane, dimethylethoxysilane, dimethyltrimethoxysilane, dimethyldimethoxysilane, phenyltrimethoxysilane, diphenyldimethoxysilane, diphenyldiethoxysilane, triphenylmethoxysilane, triphenylethoxysilane, or the like.

The C1 to C20 alkylsiloxane may include hexamethylcyclotrisiloxane, tetramethylcyclotetrasiloxane, tetraethylcyclotetrasiloxane, octamethylcyclotetrasiloxane, hexamethyldisiloxane, or the like.

During the ALD process for forming the first carboncontaining insulating layer **124**A, an oxygen reactant may be used. The oxygen reactant may include O<sub>3</sub>, H<sub>2</sub>O, O<sub>2</sub>, NO<sub>2</sub>, NO, N<sub>2</sub>O, H<sub>2</sub>O, alcohol, a metal alkoxide, plasma O<sub>2</sub>, remote plasma O<sub>2</sub>, plasma N<sub>2</sub>O, plasma H<sub>2</sub>O, or combinations thereof.

During the ALD process for forming the first carboncontaining insulating layer **124**A, a nitrogen reactant may be used. The nitrogen reactant may include  $N_2$ ,  $NH_3$ , hydrazine ( $N_2H_4$ ), plasma  $N_2$ , remote plasma  $N_2$ , or combinations thereof.

Next, a semiconductor layer is formed, by an epitaxial growth process, on the fin-type active region FA exposed on both sides of each dummy gate structure DGS, thereby forming a source/drain region **120**. The source/drain region **120** may have a top surface that is at a higher level than a top surface of the fin-type active region FA.

Although the source/drain region **120** is shown in FIGS. **11**A and **11**B as having a specific cross-sectional shape, the cross-sectional shape of the source/drain region **120** according to the disclosed invention is not limited to the example shown in FIGS. **11**A and **11**B. For example, the cross-sectional shape of the source/drain region **120**, which is cut along a Y-Z plane, may be a circular shape, an elliptical shape, or a polygonal shape such as a quadrangle, a pentagon, and a hexagon.

The source/drain region **120** may include an impuritydoped semiconductor layer. In some embodiments, the source/drain region **120** may include impurity-doped Si, SiGe, or SiC.

Next, the inter-gate dielectric **132** is formed to cover the source/drain region **120**, the plurality of dummy gate structures DGS, and the gate insulating spacer **124**.

In some embodiments, to form the inter-gate dielectric **132**, an insulating layer may be formed to a sufficient thickness and cover the source/drain region **120**, the plurality of dummy gate structures DGS, and the gate insulating spacer **124**. Next, a result product including the insulating layer may be planarized to expose the plurality of dummy gate structures DGS, thereby forming the inter-gate dielectric **132** having a planarized top surface.

Referring to FIGS. **12**A and **12**B, the plurality of dummy gate structures DGS exposed by the inter-gate dielectric **132** are removed, thereby forming a plurality of gate spaces GH.

The gate insulating spacer 124 and the fin-type active region FA may be exposed by the plurality of gate spaces GH.

To remove the plurality of dummy gate structures DGS, a wet etching process may be used. For example, to perform 5 the wet etching process, an etching solution including nitric acid (HNO<sub>3</sub>), diluted fluoric acid (DHF), NH<sub>4</sub>OH, tetramethylammonium hydroxide (TMAH), potassium hydroxide (KOH), or combinations thereof may be used, without being limited thereto.